C<sup>2</sup>-MOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

#### GENERAL DESCRIPTION

The TCP4632BF is a C<sup>2</sup>MOS 4-bit single-chip microcomputer capable of directly driving liquid crystal display provided with 1/3 or 1/4 duty, and is most suitable for use in a wide range of application fields, such as a system requiring low power dissipation.

The TCP4632BF contains the controller and driver for driving the liquid crystal display (hereinafter referred to as LCD) to the TCP4630AP. For the use and study of this device, refer to the technical data for the TCP4630AP in addition to this technical data.

## FEATURES

- o C<sup>2</sup>MOS 4-bit single-chip microcomputer of low power dissipation

- o Memory capacity

Program region (ROM)3072 words x 8-bitData region (RAM)160 words x 4-bit (including RAM for display)

o Instruction execution time: 10 µs (400kHz ceramic oscillator/IFT)

o 52 instructions

- Built-in LCD controller

1/3 or 1/4 duty (designated by mask options)

- o Built-in LCD direct driver

| Common output  | 4 pins  |

|----------------|---------|

| Segment output | 24 pins |

o Input/Output port

I/O port l x 4-bit (I/O can be switched by programs.)

l x 4-bit (I/O can be designated by mask options.)

l x 4-bit (I/O can be designated by mask options.)

CHELTHINK .

Output port 3 x 4-bit (General purpose output port) Input port 1 x 4-bit (Pull-up/Pull-down resistor with input resistance,can be selected.) 1 x 4-bit o External power supply is available for LCD (V<sub>LCD</sub>) o Built-in display decoder (Can be designated by mask options with decoder data.) o Blanking operation o Hold operation (LCD can be displayed during hold operation.)

o Power-down mode (Display blanking)

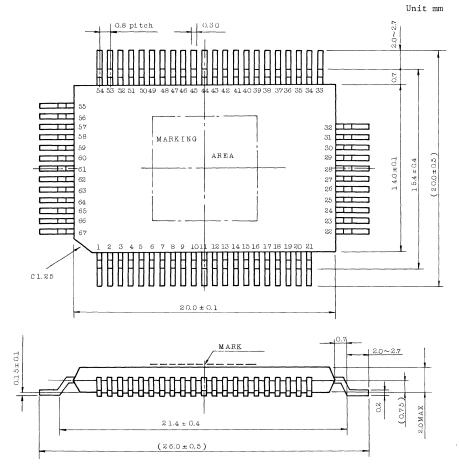

o 67-pin plastic package

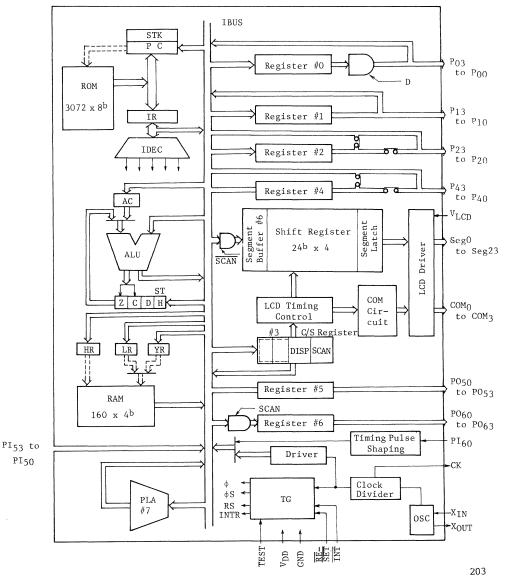

# BLOCK DIAGRAM

REAL

TCP4632BF

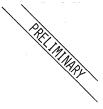

PIN CONNECTIONS (Top View)

#### PIN NAMES/PIN DESCRIPTION

|                  | Turnet           |               | TCP4620AP/30AP                            |               | TCP4632BF                                 |

|------------------|------------------|---------------|-------------------------------------------|---------------|-------------------------------------------|

| Pin Name         | Input/<br>Output | No.of<br>pins | Function ·                                | No.of<br>pins | Function                                  |

| TEST             | Input            | 1             | LSI test input (always<br>kept set at 0.) | 1             | LSI test input (always<br>kept set at 0.) |

| XIN              | Input            | 1             | Oscillator connecting<br>terminal         | 1             | Oscillator connecting<br>terminal         |

| X <sub>OUT</sub> | Output           | 1             | Oscillator connecting<br>terminal         | 1             | Oscillator connecting<br>terminal         |

| PI5              | Input            | 4             | General purpose input<br>port             | 4             | General purpose input<br>port             |

| RESET            | Input            | 1             | Reset input                               | 1             | Reset input                               |

| INT              | Input            | 1             | Interrupt input                           | 1             | Interrupt input                           |

| PI6              | Input            | 1             | General purpose input                     | 1             | General purpose input                     |

TCP4632BF

# TECHNICAL DATA

|                     | Input/           |               | TCP4620AP/30AP                        |               | TCP4632BF                               |

|---------------------|------------------|---------------|---------------------------------------|---------------|-----------------------------------------|

| Pin Name            | Output           | No.of<br>pins | Function                              | No.of<br>pins | Function                                |

| PO                  | 1/0              | 4             | I/O port                              | 4             | I/O port                                |

| P1                  | Output           | 4             | General purpose output<br>port        | 4             | General purpose output port             |

| P <sub>2</sub>      | Input/<br>Output | 4             | General purpose input/<br>output port | 4             | General purpose input/<br>output port   |

| Р4                  | Input/<br>Output | 4             | General purpose input/<br>output port | 4             | General purpose input/<br>output port   |

| VDD                 |                  | 1             | Power supply                          | 2             | Power supply                            |

| SEG0~23             | Output           | •             |                                       | 24            | LCD segment driver out-<br>put          |

| P06                 | Output           | 4             | PLA output port                       | 4             | General purpose output<br>port          |

| PO7                 | Output           | 4             | PLA output port                       |               |                                         |

| P05                 | Output           | 5             | Decode matrix output<br>port          | 4             | General purpose output<br>port          |

| сом <sub>0</sub> ∿3 |                  |               |                                       | 4             | LCD common driver output                |

| V <sub>LCD</sub>    |                  |               |                                       | 1             | LCD external power sup-<br>ply terminal |

| GND                 |                  | 1             | GND                                   | 1             | GND                                     |

| СК                  | Output           | 1             | External timing output                | 1             | External timing output                  |

TCP4632BF

RELEASE

TECHNICAL DATA

CONFIGURATION OF PORT AND REGISTER

|   | Name                     | Sym-<br>bol     | Pin Name                             | Reg.<br>No. | Function                 | Remarks                                                                                                                       |

|---|--------------------------|-----------------|--------------------------------------|-------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| * | I/O Port                 | Po              | P <sub>03</sub> to P <sub>00</sub>   | 0           | I/O Port                 | I/O switching is controlled by D flag<br>of ST.<br>This port can be designated as a<br>dedicated output port by mask options. |

|   | Output<br>Port           | Ρ,              | P <sub>13</sub> to P <sub>10</sub>   | 1           | Output<br>Port           | General purpose output port.<br>The contents of register can be re-<br>ferred to by a program.                                |

| * | Input/<br>Output<br>Port | P 2             | P <sub>23</sub> to P <sub>20</sub>   | 2           | Input/<br>Output<br>Port | Input/output can be designated by mask<br>options. The contents of register can<br>be referred to by a program.               |

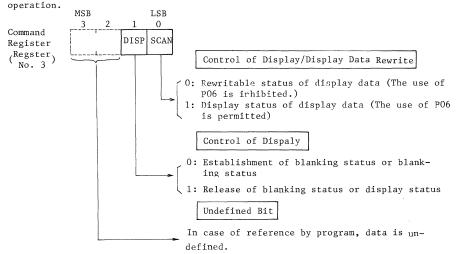

| * | Command<br>Register      | C/S             |                                      | 3           | Command<br>Register      | LCD display is controlled by a 2-bit<br>register. The contents of register<br>can be referred to by a program.                |

| * | Input/<br>Output<br>Port | Ρ4              | P43 to P40                           | 4           | Input/<br>Output<br>Port | Input/output can be designated by mask<br>options. The contents of register can<br>be referred to by a program.               |

|   | Input<br>Port            | PI <sub>5</sub> | PI <sub>53</sub> to PI <sub>50</sub> | - 5         | Input<br>Port            | General purpose input port with $150k\Omega$ (TYP.) resistance. Pull-up/Pull-down designation can be made by mask options.    |

| * | Output<br>Port           | PO5             | P053 to P050                         | _           | Output<br>Port           | General purpose output port.<br>The contents of register can not be re-<br>ferred to by a program.                            |

|   | Input<br>Port            | ΡΙ <sub>6</sub> | PI60                                 | 6           | Input<br>Port            | l-bit general purpose input port.<br>(Built-in Schmitt circuit).                                                              |

| * | Output<br>Port           | PO <sub>6</sub> | P0 <sub>63</sub> to P060             |             | Output<br>Port           | General purpose output port.<br>The contents of register can not be<br>referred to by a program.                              |

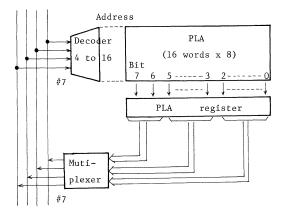

| * | PLA                      | PLA             |                                      | 7           | PLA                      | PLA. PLA can be used as a display data<br>decoder or a data decoder. The contents<br>of decode is designated by mask options. |

- Note The asterisk (\*) indicates the points of difference between TCP 4620AP/TCP4630AP and this device.

- (a) Neither command register nor PLA (available for reference by a program) is contained in the TCP4620AP/TCP4630AP.

- (b) Since PO<sub>5</sub> and PO<sub>6</sub> contain neither decode matrix nor PLA, the number of output pins of each port is 4.

- (c) Care should be taken to the fact that  $P_0$ ,  $P_2$ ,  $P_4$ ,  $PO_5$  and  $PO_6$  of this device are different from those of TCP4620AP/TCP4630AP in electrical characteristics.

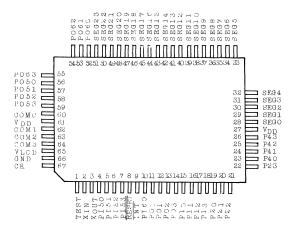

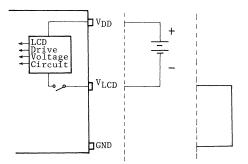

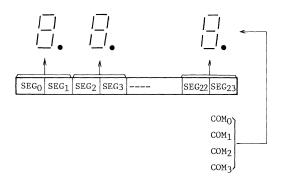

## LCD CONTROLLER/DRIVER

The TCP4632BF contains a driver circuit capable of directly, dynamically driving the LCD provided with 1/3 or 1/4 duty by the 1/3 bias method.

| LCD connection terminals amount to 29 in total as   | follows: |

|-----------------------------------------------------|----------|

| Common driver output (COMO to COM3)                 | 4        |

| Segment driver output (SEGO to SEG23)               | 24       |

| $V_{ m LCD}$ terminal as LCD driving power terminal | 1        |

The display ability makes it possible directly to drive the following LCDs according to the number of time divisions:

- (a) 1/4 duty (1/3 bias) LCD Max. 96 segments (12 digits x 8 segments)

- (b) 1/3 duty (1/3 bias) LCD

Max. 72 segments (8 digits x 9 segments)

BLOCK DIAGRAM OF LCD DRIVE CONTROLLER

# CONTROL OF DRIVE CIRCUIT

The operation of LCD drive circuit is controlled by the contents of command register. The command register is a 2-bit register and is accessed as register No. '3'. Both of two bits are reset to "0" by an initialize

DISPLAY OPERATION

SETUP OF DISPLAY DATA

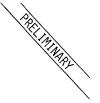

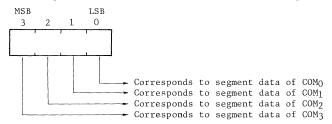

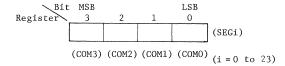

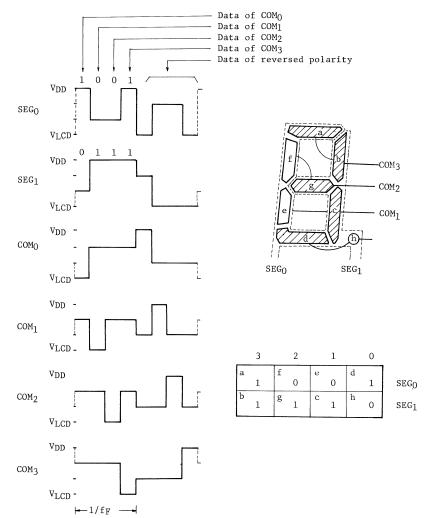

The TCP4632BF internal processing data corresponds to LCD drive terminal in such a way as bit 0, bit 1, bit 2 and bit 3 of the processing data correspond to each segment data of COM0, COM1, COM2, and COM3, respectively.

The conversion of LCD display data is arbitrarily set up by a program or by a built-in PLA register (setup of the contents by mask options).

# TRANSFER OF DISPLAY DATA

LCD display data setup by a program or PLA register is displayed by transferring it to the shift register of LCD driver by the program.

The transfer method is divided into two categories: one is that the converted data is transferred as it is, and another is that a displaying data region set up in the data memory (RAM) is transferred after it has been once stored. Even by either method, each bit of LCD segment (dot) and TCP4632BF internal processing data corresponds to each other by one to one.

TCP4632BF

- THE MARK

In case data memory is provided with display region

In case processing data intact is transferred

Each bit of display data expresses data of segment (dot) equivalent to (SEGi COMj :  $0 \le i \le 23$ ,  $0 \le j \le 3$ ). When the data displays "1", the display lights. In case of the use of LCD with 1/3 futy (COMO to COM2), the data of bit 3 (MSB) has no meaning as a LCD display data.

INTEGRATED CIRCUIT

## TECHNICAL DATA

Transfer and rewrite of display data is made by a program as follows: First, clear SCAN bit to '0'. (Immediately after initialization, the bit is at '0'.) Next, transfer 4-bit data equivalent to SEG. 23 to Register No. 6 (SAR 6), and then transfer 4-bit data equivalent to SEG 22. Continuously transfer 4-bit data in sequence by programs until the transfer of data equivalent to SEG. 0 is comleted.

This operation sllows 4×24-bit data to be written into the shift register within LCD drive circuit. After the data transfer of 24 words has been finished, SCAN bit is set to '1'. When SCAN bit goes to '1', writing into the shift register is inhibited, and LCD begins to be driven by the data newly held. Data switching is made from COMj to come next (data output equivalent to bit j to SEGi) and is automatically scanned to the next COMj+1.

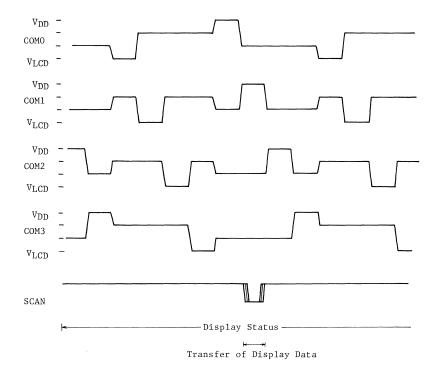

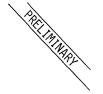

In the case that the period (period of SCAN = 0) of 24-word data transfer by means of a program is within the one COM period (1/4fF), the blank period does not come into the transfer period, and the display contents are switched. However, in the case that the period (period of SCAN = 0) of 24word data transfer by means of a program crosses switching of COM (this phenomenon presents by timing of data transfer period or it presents when the data transfer period becomes longer than one COM period), no correct display data is secured during the period; thus, a blank is automatically inserted in the period.

When the display data is transferred to a shift register equivalent to Register No.6 during the period of SCAN = 0, all of 24 words must be transferred to the shift register. However, if SEGO to SEGE-1 outputs only, not all of SEGO  $\sim$  SEG23 outputs, are used, k word only can be transferred.

CREAT AND A

TCP4632BF

PRE MINIS

TECHNICAL DATA

In case of SCAN = 0, write in Register No. 6 (SAR = 6) means write in the shift register as a display data. In case of SCAN = 1, however, it means write in output port  $PO_6$ .

As the display data transfer period is short, it does not come in the blanking period.

212

Joshiba INTEGRATED CIRCUIT

TCP4632BF

As the display data transfer period is long, it comes in the blanking period.

- THE MARK

#### LCD FRAME FREQUENCY

Frame frequency (LCD drive frequency) is given by the built-in devider. The frame frequency  $f_F$  is given from internal clock frequency  $f_{CP}$  by the following formula:

$$f_F = f_{CP} \times \frac{1}{2^m \times n}$$

Where, m is the number of divider stages. When fx = 400 kHz and f = 200 kHz, m is set to 9. n is the number of time division. Therefore,

In case of 1/3 duty  $f_F = 130 \text{ Hz}$ In case of 1/4 duty  $f_F = 98 \text{ Hz}$

The period equivalent to one COM is

$$\frac{2^{m}}{f_{CP}} \qquad (\Rightarrow \frac{2^{m-1}}{f_{CY}})$$

therefore, when m = 9, the period is equivalent to 256 steps.

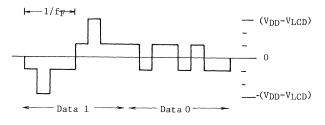

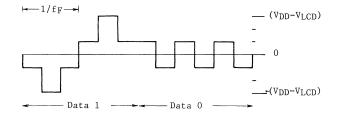

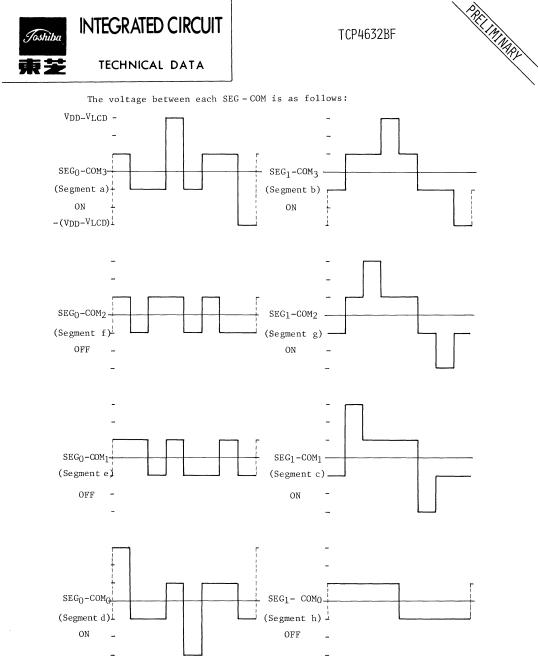

#### LCD DRIVE WAVEFORM

TCP4632BF is capable of directly, dynamically driving the LCD provided with 1/3 or 1/4 duty by 1/3 bias method.

In case of 1/3 or 1/4 duty, the voltage applied to LCD is + (V\_{DD} - V\_{LCD}) to -(V\_{DD} - V\_{LCD}).

1/4 duty (1/3 bias) drive

1/3 duty (1/3 bias) drive

(Note) f\_F : LCD frame frequency  $v_{LCD} \mbox{ terminal voltage }$

Each terminal waveform in case of displaying data "3" at  $1/4\ {\rm duty}$  is as follows:

216

LCD DRIVE VOLTAGE

$V_{\rm LCD}$  is an input terminal of LCD driving power. LCD drive voltage is required to be supplied between  $V_{\rm DD}-V_{\rm LCD}.$

If the operation voltage of the TCP4632BF is identical with the LCD drive voltage,  $V_{\rm LCD}$  is connected to GND.

The supply of drive voltage generated by LCD drive circuit is controlled within this device according to the operating status of CPU. In the following cases that there is a possibility of keeping LCD drive circuit stationary for a long period of time, the supply of LCD drive voltage is cut with the built-in switch.

- (1) Initialize operation

- 2 SCAN = 0 and H = 1

The switch turned off by initialize operation is turned on by setting the SCAN bit of command register to 'l', thus resulting in the supply of LCD drive voltage. After that, even if the SCAN bit of command register is reset to '0', LCD drive voltage is kept supplied.

For performing hold operation, H must be set to 'l' in a state of SCAN = l and at time of normal LCD display because rewrite of display data has been already finished. In this case, LCD drive circuit is still in operation to continue display. However, while display data is being rewritten, if H is set to 'l' at time of SCAN = 0, the supply of LCD drive voltage is cut.

When the supply of LCD drive voltage is cut with the built-in switch, all of SEG and COM outputs attain  $V_{\rm DD}$  lelvel.

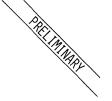

OUTPUT PORT (P05, P06)

PO5 and PO6 are 4-bit general purpose output ports. Each port is provided with a latch, and its contents are held until they are rewritten by a program. Each bit is reset to "O" by initialize operation, but the contents being held cannot be referred to by the program.

The authorization/inhibit of content rewrite by the program of PO6 is controlled by SCAN bit of command register.

| Command register<br>SCAN | Object of content rewrite by program           |

|--------------------------|------------------------------------------------|

| 0                        | Output to shift register<br>(LCD segment data) |

| 1                        | Output to PO6                                  |

Unlike PO5 and PO6 of TCP4630AP, those of TCP4632BF do not contain decode matrix, and PLA; therefore, there is difference between them in output timing.

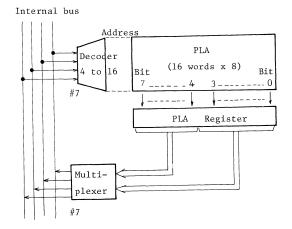

PLA

A program can make reference of PLA by use of a decoder for display data or the like. If 4-bit BCD data is written in PLA (Register No.7) by a program, one of sixteen addresses is selected by 4-to-16 decoder within PLA, and the corresponding 8-bit data is written in PLA register.

PLA contents of PLA register can be read out by executing the instruction for making reference of PLA. How to read out 8-bit data of PLA register varies with option designation of 1/3 duty or 1/4 duty. PLA register is not affected by reset operations.

(a) Designating 1/4 duty by options

The 8-bit data can be read out by executing the instruction for making reference of PLA register two times. In other words, 4-bit (bit 3 to 0) data on the lower level can be read out by the first execution of the instruction (LAR 7) for making reference of PLA

TCP4632BF

after BCD data has been written in PLA (SAR 7), and similarly 4-bit (bit 7 to 4) data on the higher level can be read out by the second execution of the same instruction.

When the same data is read out again, and when PLA register is required to be updated, the reabout must be performed after BCD data has been written in the PLA over again.

#### (b) Designating 1/3 duty by options

The 8-bit data can be read out by executing the instruction for making reference of PLA register three times. In other words, 3-bit (bit 2 to 0) data on the lower level can be read out by the first execution of the instruction (LAR 7) for making reference of PAL after BCD data has been written in PLA (SAR 7), and similarly 3-bit (bit 5 to 3) data on the intermediate level can be read out by the second execution of the same instruction, and also 2-bit (bit 7 to 6) data on the higher level by the third execution of the same instruction, respectively.

- THE MARK

While the reference instruction above mentioned is being executed, 1 bit (bit 3) on MSB side of the lower or intermediate level and 2 bits (bit 3 and 2) on MSB side of the higher level are always read out as zero. When the same data is read out again, and when PLA register is required to be updated, the readout is performed after BCD data has been written in the PLA over again.

#### Internal bus

222

TCP4632BF

Toshiba

TECHNICAL DATA

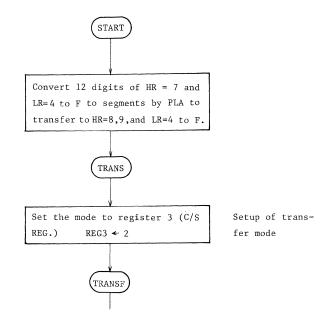

# LCD DATA TRANSFER PROGRAM - EXAMPLE

| LR<br>HR | 0 | 1 | 2 | 3 | 4          | 5  | 6  | 7  | 8  | 9  | A  | В | с | D  | Е  | F            |

|----------|---|---|---|---|------------|----|----|----|----|----|----|---|---|----|----|--------------|

| 7        |   |   |   |   | 1<br>Digit | 2  | 3  | 4  | 5  | 6  | 7  | 8 | 9 | 10 | 11 | 12-<br>digit |

| 8        |   |   |   |   | SEG23      | 21 | 19 | 17 | 15 | 13 | 11 | 9 | 7 | 5  | 3  | SEG 1        |

| 9        |   |   |   |   | SEG22      | 20 | 18 | 16 | 14 | 12 | 10 | 8 | 6 | 4  | 2  | SEG 0        |

Example of a program which the data of HR = 7 and LR = 4 to F are displayed on LCD through segment conversion

LCD: 1/4 duty, 12 digits (24 Seg.)

Setting of display mode

Toshiba 東芝

TECHNICAL DATA

TCP4632BF

|              |            | 10       |         | *** | TCP46      | 632BF  | LCE | DATA   | TRANSFE    | R PROGRAM |

|--------------|------------|----------|---------|-----|------------|--------|-----|--------|------------|-----------|

| 0100         |            | 20<br>30 | ;       |     | 000        | 1000   |     |        |            |           |

| 0100         | 64         | 30<br>40 | START   |     | ORG        | 100H   |     |        |            |           |

| 0100         | 77         | 50       | NEXT:   | •   | LLI        | 4      |     |        |            |           |

| 0101         | 04         | 60       | NEA1;   |     | LHI        | 7      |     |        |            |           |

| 0102         | 2F         | 70       |         |     | LAM        | 7      |     |        |            |           |

| 0104         | 78         | 80       |         |     | SAR<br>LHI | 8      |     |        |            |           |

| 0105         | 17         | 90       |         |     | LAR        | o<br>7 |     |        |            |           |

| 0106         | OC         | 100      |         |     | SAM        | 1      |     |        |            |           |

| 0107         | 79         | 110      |         |     | LHI        | 9      |     |        |            |           |

| 0107         | 17         | 120      |         |     | LAR        | 9<br>7 |     |        |            |           |

| 0100         | 0C         | 130      |         |     | SAM        | /      |     |        |            |           |

| 010A         | 02         | 140      |         |     | ICL        |        |     |        |            |           |

| 010B         | 06         | 150      |         |     | LAL        |        |     |        |            |           |

| 010C         | 90         | 160      |         |     | ADI        | 0      |     |        |            |           |

| 0100<br>010D | D110       | 170      |         |     | BCC        | NEXT   |     |        |            |           |

| 010F         | 42         | 180      | TRANS   |     | LAI        | 2      |     |        |            |           |

| 0110         | 2B         | 190      | 1 Iuliu |     | SAR        | 3      | ;   | DTSP=1 | .SCAN=0    | SET       |

| 0111         | 64         | 200      |         |     | LLI        | 4      | ,   | D101 1 | .,00/11/ 0 | 551       |

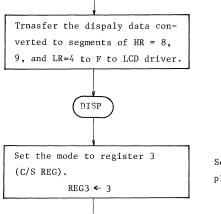

| 0112         | 78         | 210      | TRANS   |     | LHI        | 8      |     |        |            |           |

| 0113         | 04         | 220      |         |     | LAM        | -      |     |        |            |           |

| 0114         | 2E         | 230      |         |     | SAR        | 6      |     |        |            |           |

| 0115         | 79         | 240      |         |     | LHI        | 9      |     |        |            |           |

| 0116         | 04         | 250      |         |     | LAM        |        |     |        |            |           |

| 0117         | 2E         | 260      |         |     | SAR        | 6      |     |        |            |           |

| 0118         | 02         | 270      |         |     | ICL        |        |     |        |            |           |

| 0119         | 06         | 280      |         |     | LAL        |        |     |        |            |           |

| 011A         | 90         | 290      |         |     | ADI        | 0      |     |        |            |           |

| 011B         | D211       | 300      |         |     | BCC        | TRANS  | SF  |        |            |           |

| 011D         | 43         | 310      | DISP:   |     | LAI        | 3      |     |        |            |           |

| 011E         | 2 <b>B</b> | 320      |         |     | SAR        | 3      | ;   | DISP=S | CAN=1 S    | SET       |

|              |            | 330      | ;       |     |            |        |     |        |            |           |

|              |            | 340      | ;       |     |            |        |     |        |            |           |

TCP4632BF

REPART

TECHNICAL DATA

# TCP4632BF MASK OPTIONS

|                                                |          | :<br>I  |      | TYP032      |             |          |                    |

|------------------------------------------------|----------|---------|------|-------------|-------------|----------|--------------------|

| 0scillat                                       | ion      | 1       |      | 050         |             |          |                    |

| 1                                              |          | 0       | SC   | 400K        |             |          |                    |

| frequen                                        | cv       | ŕ       |      | ceramic     |             |          |                    |

| 1                                              | 5        |         |      | IFT         |             |          |                    |

| Dividing rat                                   | io for   |         | 0.7  | 0.0         |             |          |                    |

| internal clo                                   |          | :       | СР   | 02          |             |          |                    |

| External timi                                  | ngoutput |         | CK   | C1          |             |          |                    |

| Divider                                        | 1 Input  |         | PD   | CP          |             |          |                    |

| 5 Divider                                      | 3 Input  | COUNTER | PDR  | PD2         |             |          |                    |

| 0 0 Reset t                                    | iming    | -       | PDR  | N           |             |          |                    |

| H. Buffer                                      | 0 Input  |         | CO   | P160        |             |          |                    |

| + 0 Buffer                                     | 1 Input  | COUNTER | C1   | RD7         |             |          |                    |

| Buffer                                         | 2 Input  | BUFFER  | C2   | RDA         |             |          |                    |

| Buffer<br>Buffer<br>Buffer<br>Buffer<br>Buffer |          | -       | C3   | RDD         |             |          |                    |

| H flag                                         |          | Н       | IOLD | Н           |             |          |                    |

| Restart cond                                   | ition    | R       | STH  | C3          |             |          |                    |

| Input/Out-                                     | Port 0   |         | STD  | D(PROG)     | 1 (OUT)     |          |                    |

| put port                                       | Port U   |         | SID  | D(PROG)     |             |          | ·                  |

| Input/Out-                                     | Port 2   |         | P2   | /F/(OUT)    | /F/(OUT)    | /0/(IN)  | /0/(IN) /0/(IN)    |

| put port                                       | Port 4   |         | P4   | /F/(OUT)    | /3/(IN/OUT) | /F/(OUT) | /3/(IN/OUT)/0/(IN) |

| Input resist                                   |          |         | P15  | 0 (UP)      | 1 (DOWN)    |          |                    |

| (Input port                                    | 5)       |         | r13  | 0 (0F)      | I (DOWN)    |          |                    |

|                                                | Line O   |         | PLA0 | 1 1         |             |          |                    |

|                                                | Line 1   |         | 'LA1 | / /         |             |          |                    |

|                                                | Line 2   | Р       | PLA2 | 1 1         |             |          |                    |

|                                                | Line 3   | P       | PLA3 | / /         |             |          |                    |

|                                                | Line 4   | P       | LA4  | 1 1         |             |          |                    |

|                                                | Line 5   | P       | LA5  | 1 1         |             |          |                    |

|                                                | Line 6   | P       | LA6  | 1 1         | l           |          |                    |

| PLA                                            | Line 7   | D. T. P | LA7  | 1 1         | 1           |          |                    |

| (#7)                                           | Line 8   |         | LA8  | 1 1         | 1           |          |                    |

| (#/)                                           | Line 9   | P       | LA9  | 1 1         |             |          |                    |

|                                                | Line A   | P       | LAA  |             | 1           |          |                    |

|                                                | Line B   |         | LAB  | 1 1         | 1           |          |                    |

|                                                | Line C   |         | LAC  | 1 1         | 1           |          |                    |

|                                                | Line D   |         | LAD  | 1 1         |             |          |                    |

|                                                | Line E   |         | LAE  | 1 1         | 1           |          |                    |

|                                                | Line F   |         | LAF  | 1 1         |             |          |                    |

| Oscillation                                    |          | 1       |      | · · · · · · | 1           |          |                    |

| Control                                        | PI60     | F       | RSTX | N           |             |          |                    |

| GUILLUI                                        | 1 100    |         |      |             |             | 1        |                    |

| LCD Duty                                       |          | L I     | DUT  | 4           | 3           |          |                    |

| -                                              |          | 1       |      | 1           | 1           | 1        |                    |

TECHNICAL DATA

Toshiba **R Z**

TCP4632BF

# ABSOLUTE MAXIMUM RATINGS

| SYMBOL           | ITEM                       | RATING                       | UNIT |

|------------------|----------------------------|------------------------------|------|

| V <sub>DD</sub>  | Supply Voltage             | -0.3 to +7.0                 | v    |

| VIN              | Input Voltage              | -0.3 to V <sub>DD</sub> +0.3 | v    |

| V <sub>OUT</sub> | Output Voltage             | -0.3 to VDD+0.3              | V    |

| PD               | Power Dissipation          | 400                          | mW   |

| Tsol             | Soldering Temperature Time | 260 (10 SEC)                 | °C   |

| Tslg             | Storage Temperature        | -55 to +125                  | °C   |

| Topr             | Operating Temperature      | -20 to +70                   | °C   |

### ALLOWABLE OPERATING CONDITIONS

| SYMBOL           | ITEM                                                                         | RATING                   | UNIT |

|------------------|------------------------------------------------------------------------------|--------------------------|------|

| V <sub>DD</sub>  | Supply Voltage                                                               | 4 to 6                   | v    |

| Та               | Ambient Temperature                                                          | -20 to +70               | °C   |

| I <sub>OUT</sub> | Max. Output Current                                                          | ±3                       | mA   |

| fx               | X'tal Operating Frequency                                                    | 40 to 400                | kHz  |

| tCY              | Cycle Time                                                                   | 10 to 100                | μs   |

| VLCD             | LCD Supply Voltage<br>(V <sub>LCD</sub> is with respect to V <sub>DD</sub> ) | -V <sub>DD</sub> to -2.7 | V    |

TECHNICAL DATA

Joshiha

# TCP4632BF

# DC CHARACTERISTICS (Ta = -20 to +70°C, $V_{DD}$ = 4 to 6V)

| SYMBOL                                 | PARAMETER                                 | TEST CONDITION                 | MIN.                 | (Note 1)<br>TYP. | MAX.     | UNIT |

|----------------------------------------|-------------------------------------------|--------------------------------|----------------------|------------------|----------|------|

| VIH                                    | Input High Voltage                        |                                | V <sub>DDx</sub> 0.7 | -                | VDD      |      |

| VIHS                                   | Input High Voltage (Schmitt)              |                                | VDDx0.85             | -                | VDD      |      |

| VIHC                                   | Input High Voltage(x <sub>IN</sub> Input) |                                | VDDx0.75             | -                | VDD      | v    |

| VIL                                    | Input Low Voltage                         |                                | 0                    | -                | VDDx0.3  | v    |

| VILS                                   | Input Low Voltage (Schmitt)               |                                | 0                    | -                | VDDx0.15 |      |

| VILC                                   | Input Low Voltage (XIN Input)             |                                | Ō                    | -                | VDDx0.25 |      |

| IIH                                    | Input High Current                        | VDD=6V, VIN=6V                 | -                    | -                | 20       | μA   |

| IIL                                    | Input Low Current                         | VDD=6V, VIN=0V                 | -                    | -                | -20      | μΑ   |

| RIN                                    | Input Resistance (PI <sub>5</sub> )       | VDD=5V                         | 75                   | 150              | 350      | kΩ   |

| VOH                                    | Output High Voltage (Port)                | VDD=5V, Output open            | 4.7                  | 4.9              | -        | v    |

| VOL                                    | Output Low Voltage (Port)                 | VDD=5V, Output open            | -                    | 0.1              | 0.3      | v    |

| IOH                                    | Output High Current (P1)                  | VDD=4.5V,VOH=2.4V              | -0.7                 |                  | -        |      |

| I <sub>OH2</sub>                       | Output High Current $(P_0, P_2, P_4, CK)$ | VDD=4.5V,VOH=2.4V              | -0.35                | -                | -        |      |

| LOH3                                   | Output High Current (P5,P6)               | VDD=4.5V,VOH=2.4V              | -0.15                | -                | -        |      |

| IOL                                    | Output Low Current (P1)                   | VDD=4.5V,VOL=0.45V             | 1.6                  | -                | -        | mA   |

| IOL2                                   | Output Low Current<br>(Po,P2,P4,CK)       | VDD=4.5V,VOL=0.45V             | 0.8                  | -                | -        |      |

| 10L3                                   | Output Low Current (P5,P6)                | VDD=4.5V,VOL=0.45V             | 0.4                  |                  |          |      |

| ROS3,<br>ROSO                          | Output Impedance (SEG)                    | VDD=5V,VDD-VLCD=3V<br>(Note 5) | -                    | 2                | T.B.D    |      |

| R <sub>OC3</sub> ,<br>R <sub>OC0</sub> | Output Impedance (COM)                    | VOUT=VLCD+0.5V/<br>VDD-0.5V    | -                    | 2                | T.B.D    | kΩ   |

| R <sub>OS2</sub> ,<br>R <sub>OS1</sub> | Output Impedance (SEG)                    | VDD=5V,VDD-VLCD=3V<br>(Note 5) | -                    | 20               | T.B.D    | K71  |

| R <sub>OC2</sub> ,                     | Output Impedance (COM)                    | VOUT=3+0.5V/<br>4-0.5V         | -                    | 20               | T.B.D    |      |

| V <sub>OS1</sub>                       | Output Intermediate                       | VDD=5V,VDD-VLCD=3V             | 3 - 0.2              | 3                | 3+0.2    | v    |

| V <sub>OS2</sub>                       | Voltage (SEG,COM)                         | ייכ עעי דערי עעי עעי           | 4 - 0.2              | 4                | 4+0.2    | v    |

| IDD0                                   | VDD Supply Current in Normal<br>Operation | (Note 4)                       | -                    | 600              | T.B.D    | μA   |

| IDDH                                   | VDD Supply Current in Hold<br>operation   | $f_X = 400 \text{ kHz}$        | -                    | 250              | T.B.D    | μA   |

Note 1) Typical values are at Ta=25°C and VDD=5V.

2) Output characteristic excludes XOUT terminal.

- 3) Output current at the time when other terminals than those to be tested are open.

- 4) Test conditions of current dissipation VDD = 6V, VIN = VIH/VIL(all valid), PI5 Open, CL = 50pF XIN Input waveform

5) When supplying  $\ensuremath{\text{V}_{\text{LCD}}}$  power, When switching input/output.

;

TCP4632BF

OUTLINE DRAWINGS

229