# **TDA**7546

## Multichip module for TMC tuner applications

## Features

- High-performance FM receiver

- <sup>U</sup>∎<sup>o</sup> SW-Controlled world tuning

- Variable bandwidth IF filter (ISS, intelligent selectivity system)

- Programmable quality detectors

- High-speed PLL for RDS operation

- Full electronic alignment

- High-performance fully digital RDS/RBDS demodulator

- Integrated group and block synchronization

- Error detection and correction

- Full I<sup>2</sup>C-Bus control

## Description

The TDA7546 multichip module combines in a single compact (14X14mm) 80-pin package the functionalities of a state-of-the-art FM receiver and RDS processor, exploiting one single 10.25MHz crystal reference.

The following two devices are included

- TDA7512F, high performance car-radio FM tuner with high-speed on-chip PLL and variable-bandwidth IF filter (ISS)

- TDA7333N, fully digital RDS data decoder with with on-chip group and block synchronization and error detection/correction.

Both chips are  $I^2C$ -bus controlled.

## Order codes

| Part number | Package | Packing        |

|-------------|---------|----------------|

| TDA7546     | LQFP80  | Tray           |

| TDA7546TR   | LQFP80  | in Tape & Reel |

www.st.com

## Contents

| 1            | Bloc | ck diagra | ams7                                         |

|--------------|------|-----------|----------------------------------------------|

|              | 1.1  | TDA75     | 512F                                         |

|              | 1.2  | TDA73     | 833N                                         |

| 2            | Pin  | descript  | tion9                                        |

| aSheet4U.com | 2.1  | Therm     | al data                                      |

| 3            | Elec | trical sp | pecification                                 |

|              | 3.1  | Absolu    | Ite maximum ratings 12                       |

|              | 3.2  | Electri   | cal characteristics                          |

|              | 3.3  | Tuner     |                                              |

|              |      | 3.3.1     | Additional parameters16                      |

|              | 3.4  | RDS d     | ecoder                                       |

|              |      | 3.4.1     | General interface electrical characteristics |

|              |      | 3.4.2     | Electrical characteristics                   |

| 4            | Арр  | lication  | s and test circuit                           |

| 5            | Fun  | ctional o | description                                  |

|              | 5.1  | Tuner     |                                              |

|              |      | 5.1.1     | Mixer1, AGC and 1.IF                         |

|              |      | 5.1.2     | Mixer2, limiter and demodulator              |

|              |      | 5.1.3     | Quality detection and ISS21                  |

|              |      | 5.1.4     | PLL and IF counter section                   |

|              |      | 5.1.5     | I <sup>2</sup> C-bus interface               |

|              | 5.2  | RDS d     | ecoder 27                                    |

|              |      | 5.2.1     | Overview                                     |

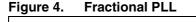

|              |      | 5.2.2     | Fractional PLL                               |

|              |      | 5.2.3     | Sigma delta converter                        |

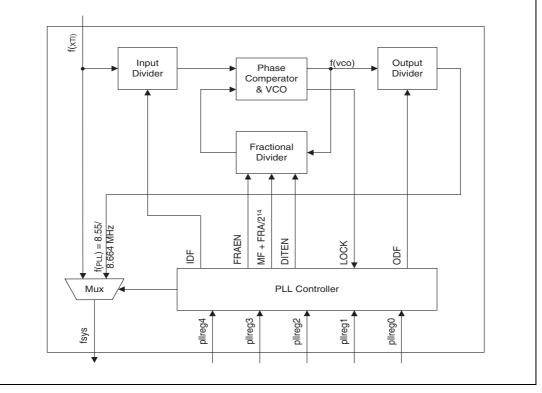

|              |      | 5.2.4     | Demodulator                                  |

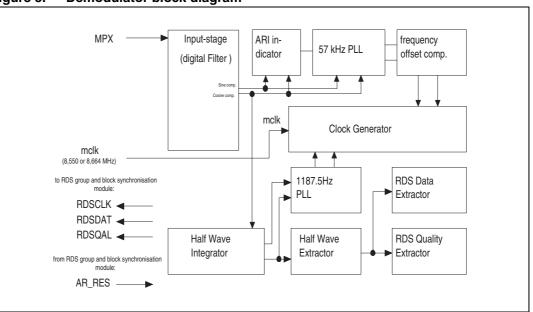

|              |      | 5.2.5     | Group and block synchronization module       |

|              |      | 5.2.5     |                                              |

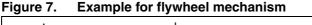

|              |      | 5.2.6     | Flywheel mechanism                           |

| 6              | Soft | ware sp   | ecifications                             |

|----------------|------|-----------|------------------------------------------|

|                | 6.1  | Tuner     | software specification                   |

|                | 6.2  | Data b    | byte specification                       |

|                | 6.3  | RDS o     | lecoder software specification           |

|                |      | 6.3.1     | Programming through serial bus interface |

|                |      | 6.3.2     | I <sup>2</sup> C transfer mode           |

|                |      | 6.3.3     | SPI mode                                 |

| ataSheet4U.com | Othe | er functi | ions detailed block diagrams62           |

| 8              | Appl | ication   | notes                                    |

|                | 8.1  | Typica    | I RDS data transfer: 65                  |

| 9              | Pack | age inf   | ormation                                 |

| 10             | Revi | sion his  | story                                    |

## List of tables

| Table 1.  | Pin configuration                                        | 9  |

|-----------|----------------------------------------------------------|----|

| Table 2.  | Thermal data                                             |    |

| Table 3.  | Absolute maximum ratings                                 | 12 |

| Table 4.  | General parameters                                       | 12 |

| Table 5.  | Tuner                                                    | 13 |

| Table 6.  | Additional parameters                                    | 16 |

| Table 7.  | General interface electrical characteristics             | 18 |

| Table 8.  | Electrical characteristics                               | 18 |

| Table 9.  | Address organization                                     | 36 |

| Table 10. | Control register function                                | 37 |

| Table 11. | Subaddress                                               | 39 |

| Table 12. | Addr 0 charge pump control                               | 40 |

| Table 13. | Addr 1 PLL counter 1 (LSB)                               | 40 |

| Table 14. | Addr 2 PLL counter 2 (MSB)                               | 40 |

| Table 15. | Addr 3,4 TV1,2 (offset refered to tuning voltage PIN 28) | 41 |

| Table 16. | Addr 5 IF counter control 1                              | 41 |

| Table 17. | Addr 6 IF counter control 2                              | 42 |

| Table 18. | Addr 7 not valid                                         | 42 |

| Table 19. | Addr 8 quality ISS filter                                | 43 |

| Table 20. | Addr 9 quality detection adjacent channel                | 43 |

| Table 21. | Addr 10 quality detection multipath                      | 44 |

| Table 22. | Addr 11 quality deviation detection                      | 44 |

| Table 23. | Addr 14 VCODIV/PLLREF                                    | 45 |

| Table 24. | Addr 15 FM AGC                                           | 45 |

| Table 25. | Addr 16 not valid                                        | 46 |

| Table 26. | Addr 17 FM demodulator fine adjust                       |    |

| Table 27. | Addr 18 s-meter slider                                   | 47 |

| Table 28. | Addr 19 IF gain/xtal adjust                              | 47 |

| Table 29. | Addr 20 tank adjust                                      | 48 |

| Table 30. | Addr 21 I/Q mixer1 adjust                                |    |

| Table 31. | Addr 22 test control 1                                   |    |

| Table 32. | Addr 23 test control 2                                   | 49 |

| Table 33. | Addr 24 test control 3                                   | 49 |

| Table 34. | Addr25 test control 4                                    | 49 |

| Table 35. | External pins alternate functions                        |    |

| Table 36. | Registers description                                    |    |

| Table 37. | rds_int register                                         |    |

| Table 38. | rds_qu register                                          | 51 |

| Table 39. | rds_corrp register                                       |    |

| Table 40. | rds_bd_h register                                        |    |

| Table 41. | rds_bd_l register                                        | 52 |

| Table 42. | rds_bd_ctrl register                                     | 53 |

| Table 43. | sinc4reg register                                        |    |

| Table 44. | testreg register                                         |    |

| Table 45. | pllreg4 register                                         |    |

| Table 46. | pllreg3 register                                         |    |

| Table 47. | pllreg2 register                                         |    |

| Table 48. | pllreg1 register                                         | 55 |

| Table 49. | pllreg0 register                                                             | 55 |

|-----------|------------------------------------------------------------------------------|----|

| Table 50. | Block diagram quality detection principle (without overdeviation correction) | 64 |

| Table 51. | Document revision history                                                    | 67 |

ww.DataSheet4U.com

# List of figures

|      | Figure 1.  | Tuner block diagram                                                                  | . 7 |

|------|------------|--------------------------------------------------------------------------------------|-----|

|      | Figure 2.  | RDS decoder block diagram                                                            | . 8 |

|      | Figure 3.  | Applications and test circuit                                                        | 20  |

|      | Figure 4.  | Fractional PLL.                                                                      | 27  |

|      | Figure 5.  | Demodulator block diagram                                                            | 29  |

|      | Figure 6.  | Group and block synchronization diagram                                              | 30  |

|      | Figure 7.  | Example for flywheel mechanism                                                       | 31  |

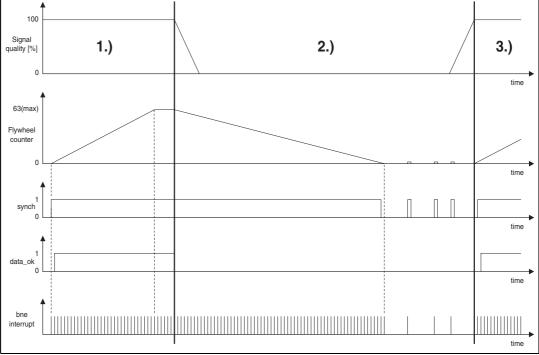

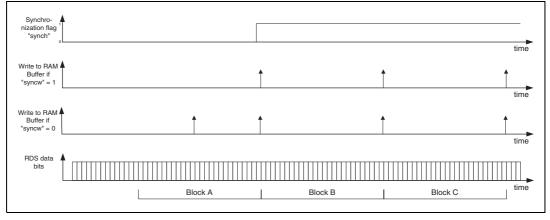

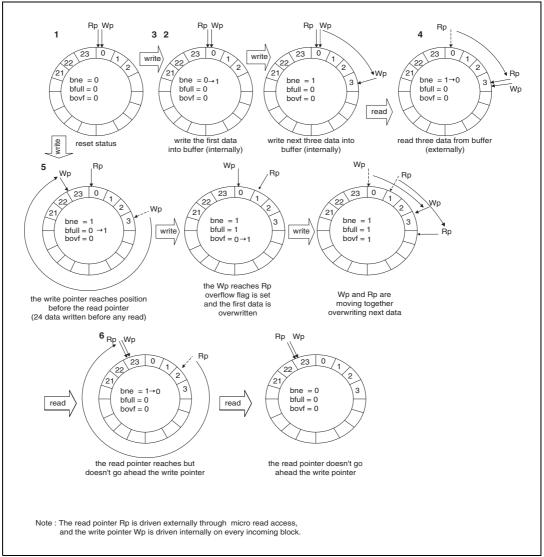

| - 64 | Figure 8.  | RAM buffer usage                                                                     | 33  |

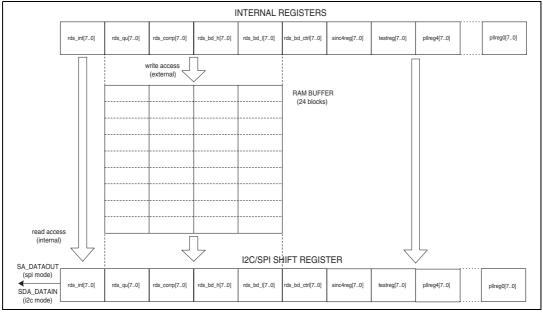

| et4  | Figure 9.  | RAM buffer update depends on "syncw" bit rds_bd_ctrl[0]                              | 33  |

|      | Figure 10. | RAM buffer states                                                                    |     |

|      | Figure 11. | Tuner software specification                                                         | 36  |

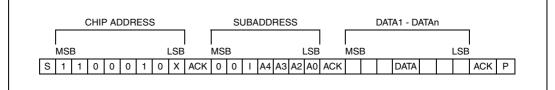

|      | Figure 12. | I <sup>2</sup> C data transfer                                                       | 56  |

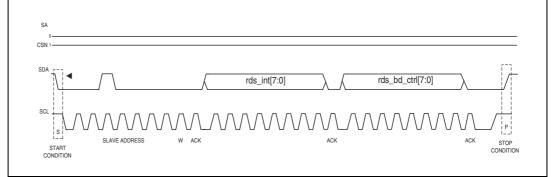

|      | Figure 13. | I <sup>2</sup> C write transfer                                                      | 56  |

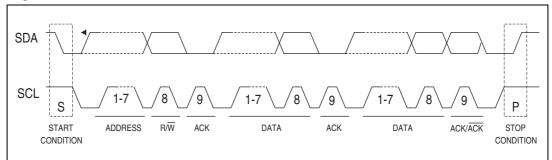

|      | Figure 14. | I <sup>2</sup> C write operation example: write of rds_int and rds_bd_ctrl registers | 57  |

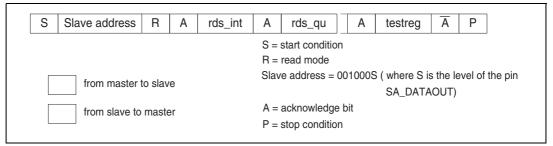

|      | Figure 15. | I <sup>2</sup> C read transfer                                                       |     |

|      | Figure 16. | I <sup>2</sup> C read access example 1: read of 5 bytes                              |     |

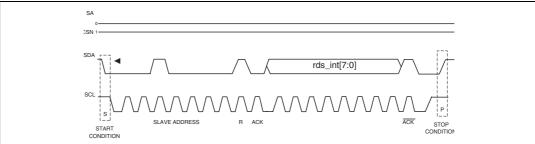

|      | Figure 17. | I <sup>2</sup> C read access example 2: read of 1 byte                               | 58  |

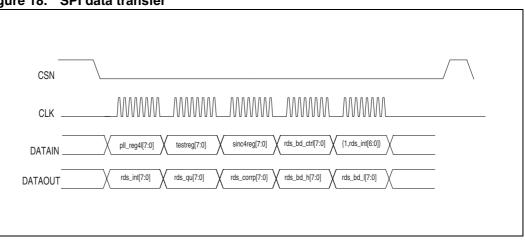

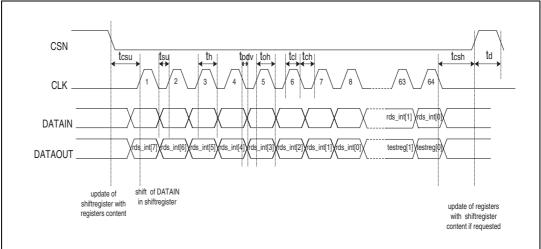

|      | Figure 18. | SPI data transfer.                                                                   | 59  |

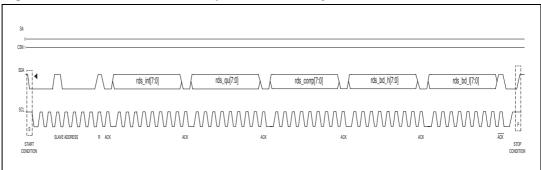

|      | Figure 19. | Write rds_int, rds_bd_ctrl and pll_reg4 registers in SPI mode                        | 60  |

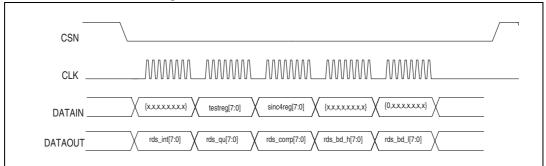

|      | Figure 20. | Read out RDS data and related flags, no update of rds_int and rds_bd_ctrl registers  | 60  |

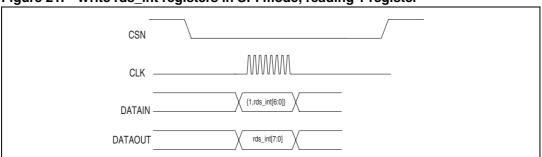

|      | Figure 21. | Write rds_int registers in SPI mode, reading 1 register                              | 61  |

|      | Figure 22. | Block diagram I/Q mixer                                                              | 62  |

|      | Figure 23. | Block diagram VCO                                                                    | 62  |

|      | Figure 24. | Block diagram keying AGC                                                             | 63  |

|      | Figure 25. | Block diagram ISS function.                                                          | 63  |

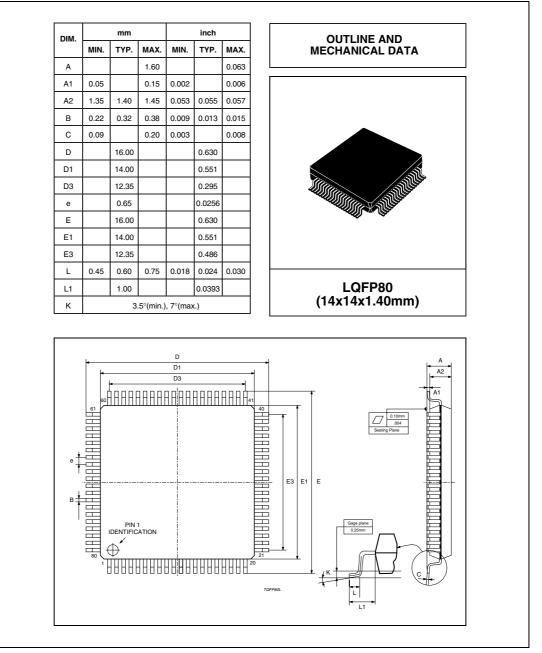

|      | Figure 26. | TQFP80LS mechanical data & package dimensions                                        | 66  |

|      |            |                                                                                      |     |

57

## 1 Block diagrams

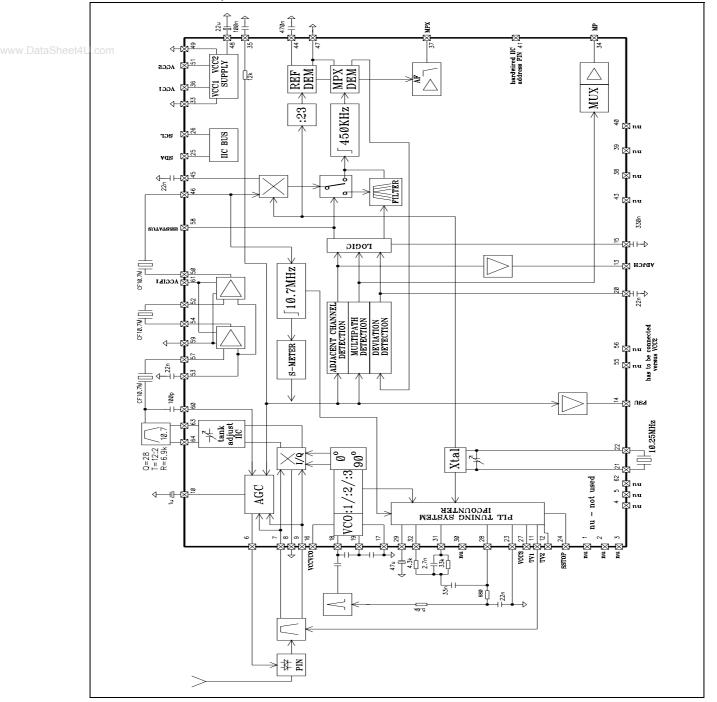

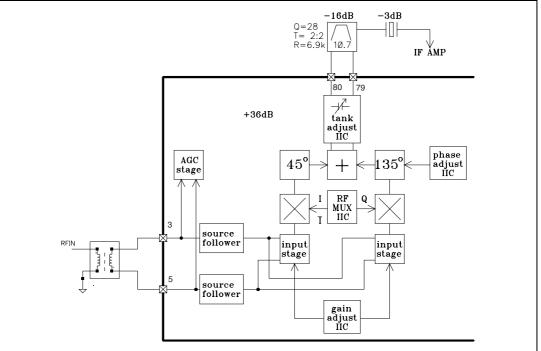

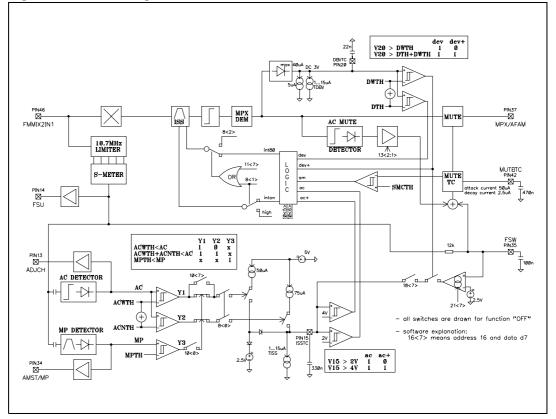

## 1.1 TDA7512F

#### Figure 1. Tuner block diagram

(Pin numbers are referred to the stand-alone device. Refer to *Table 1* for correspondance to TDA7546).

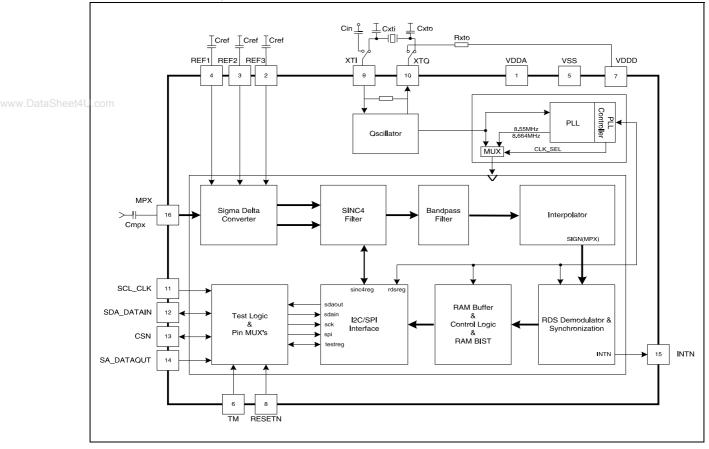

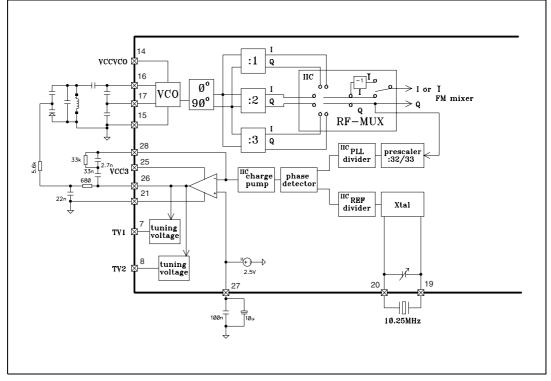

## 1.2 TDA7333N

#### Figure 2. RDS decoder block diagram

(Pin numbers are referred to the stand-alone device. Refer to *Table 1* for correspondance to TDA7546).

# 2 Pin description

| Ta     | ble 1.      | Pin configura | tion        |         |                                      |

|--------|-------------|---------------|-------------|---------|--------------------------------------|

|        | TDA7546     | FM Tuner      | RDS Decoder | Nama    | Function                             |

|        | I DA / 540  | TDA7512F      | TDA7333N    | Name    | Function                             |

|        | 1           |               |             |         | Not Connected                        |

|        | 2           | 6             |             | PINDR   | PIN Diode Driver Output              |

| t4U.co | om <b>3</b> | 7             |             | MIX1IN1 | Input1 Mixer1                        |

|        | 4           | 8             |             | GNDRF   | RF Ground                            |

|        | 5           | 9             |             | MIX1IN2 | Input2 Mixer1                        |

|        | 6           | 10            |             | AGCTC   | AGC Time Constant                    |

|        | 7           | 11            |             | TV1     | Tuning Voltage Preselection 1        |

|        | 8           | 12            |             | TV2     | Tuning Voltage Preselection 2        |

|        | 9           | 13            |             | ADJCH   | Adjacent Channel Detector Output     |

|        | 10          | 14            |             | FSU     | Unweighted Field Strength Output     |

|        | 11          | 15            |             | ISSTC   | Time Constant for ISS Ffilter Switch |

|        | 12          |               |             |         | Not Connected                        |

|        | 13          |               |             |         | Not Connected                        |

|        | 14          | 16            |             | VCCVCO  | VCO Supply                           |

|        | 15          | 17            |             | GNDVCO  | VCO Ground                           |

|        | 16          | 18            |             | VCOB    | VCO Input (base)                     |

|        | 17          | 19            |             | VCOE    | VCO Output (emitter)                 |

|        | 18          | 20            |             | DEVTC   | Deviation Detector Time Constant     |

|        | 19          | 21            |             | XTALG   | Crystal Oscillator Input (gate)      |

|        | 20          | 22            |             | XTALD   | Crystal Oscillator Output (drain)    |

|        | 21          | 23            |             | GNDVCC3 | VCC3 Ground                          |

|        | 22          | 24            |             | SSTOP   | Search Stop Output                   |

|        | 23          | 25            |             | SDA     | I <sup>2</sup> C Data                |

|        | 24          | 26            |             | SCL     | I <sup>2</sup> C Clock               |

|        | 25          | 27            |             | VCC3    | Tuning Section Supply                |

|        | 26          | 28            |             | LPOUT   | PLL Loop Filter Output               |

|        | 27          | 29            |             | VREF2   | PLL Loop Filter Reference            |

|        | 28          | 31            |             | LPF     | PLL Loop Filter Input                |

|        | 29          |               |             |         | Not Connected                        |

|        | 30          |               |             |         | Not Connected                        |

|        | 31          |               |             |         | Not Connected                        |

|        |             |               |             |         |                                      |

#### Table 1.Pin configuration

| TD 4 75 40 | FM Tuner | RDS Decoder         |                | Evention                                       |  |  |

|------------|----------|---------------------|----------------|------------------------------------------------|--|--|

| TDA7546    | TDA7512F | TDA7333N            | Name           | Function                                       |  |  |

| 32         |          | 8                   | RESETN         | Reset                                          |  |  |

| 33         |          | 9                   | XTI            | Oscillator Input                               |  |  |

| 34         | 34       |                     |                | Not Connected                                  |  |  |

| 35         |          | 10                  | ХТО            | Oscillator Output                              |  |  |

| 36         |          | 11                  | SCL_CLK        | I <sup>2</sup> C/SPI Clock                     |  |  |

| 37         |          | 12                  | SDA_DATAIN     | I <sup>2</sup> C Data/SPI Data Input           |  |  |

| 38         |          | 13                  | SA_DATAOUT     | I <sup>2</sup> C Slave Address/SPI Data Output |  |  |

| 39         |          | 14                  | CSN            | SPI Chip Select                                |  |  |

| 40         |          | 15                  | INTN           | Interrupt Output                               |  |  |

| 41         |          | 16                  | MPX            | Multiplex Input                                |  |  |

| 42         |          |                     |                | Not Connected                                  |  |  |

| 43         |          |                     |                | Not Connected                                  |  |  |

| 44         |          | 1                   | VDDA           | Analog Supply                                  |  |  |

| 45         |          |                     |                | Not Connected                                  |  |  |

| 46         |          |                     |                | Not Connected                                  |  |  |

| 47         |          | 2                   | REF3           | 2.65V Reference                                |  |  |

| 48         |          | 3                   | REF2           | 1.65V Reference                                |  |  |

| 49         |          | 4                   | REF1           | 0.65V Reference                                |  |  |

| 50         |          | 5                   | VSS            | Ground                                         |  |  |

| 51         |          | 6                   | ТМ             | Test Mode                                      |  |  |

| 52         |          | 7 VDDD Digital Supp | Digital Supply |                                                |  |  |

| 53         | 32       |                     | LPHC           | PLL Loop Filter High Current Input             |  |  |

| 54         | 33       |                     | GNDVCC1        | Digital Ground                                 |  |  |

| 55         | 34       |                     | MP             | Multipath Detector Output                      |  |  |

| 56         | 35       |                     | FSW            | Weighted Field Strength Output                 |  |  |

| 57         | 36       |                     | VCC1           | Digital Supply                                 |  |  |

| 58         | 37       |                     | MPX            | Multiplex Output                               |  |  |

| 59         |          |                     |                | Not Connected                                  |  |  |

| 60         |          |                     |                | Not Connected                                  |  |  |

| 61         | 44       |                     | REFDEMC        | Demodulator Reference                          |  |  |

| 62         | 45       |                     | MIX2IN2        | Mixer2 Input 2                                 |  |  |

| 63         | 46       |                     | MIX2IN1        | Mixer2 Input 1                                 |  |  |

| 64         | 47       |                     | GNDDEM         | Demodulator Ground                             |  |  |

#### Table 1. Pin configuration (continued)

| Table                    | 1.   | Pin configuration (continu |             | in configuration (continued) |                         |  |  |  |  |  |  |

|--------------------------|------|----------------------------|-------------|------------------------------|-------------------------|--|--|--|--|--|--|

| TDA                      | 7546 | FM Tuner                   | RDS Decoder | News                         | Function                |  |  |  |  |  |  |

| IDA                      | 7540 | TDA7512F                   | TDA7333N    | Name                         | Function                |  |  |  |  |  |  |

| 6                        | 5    | 48                         |             | VREF1                        | 5V Reference            |  |  |  |  |  |  |

| 6                        | 6    | 49                         |             | GNDVCC2                      | Analog Ground           |  |  |  |  |  |  |

| 6                        | 7    |                            |             |                              | Not Connected           |  |  |  |  |  |  |

| 6                        | 8    | 50                         |             | IF1AMP2OUT                   | IF1 Amplifier 2 Output  |  |  |  |  |  |  |

|                          | 9    | 51                         |             | VCC2                         | Analog Supply           |  |  |  |  |  |  |

| t4U <del>.com</del><br>7 | 0    | 52                         |             | IF1AMP2IN                    | IF1 Amplifier 2 Input   |  |  |  |  |  |  |

| 7                        | 1    | 53                         |             | IF1REF                       | IF1 Amplifier Reference |  |  |  |  |  |  |

| 7                        | 2    | 54                         |             | IF1AMP1OUT                   | IF1 Amplifier 1 Output  |  |  |  |  |  |  |

| 7                        | 3    | 55-56                      |             | VCC                          | Supply                  |  |  |  |  |  |  |

| 7                        | 4    | 57                         |             | IF1AMP1IN                    | IF1 Amplifier 1 Input   |  |  |  |  |  |  |

| 7                        | 5    | 58                         |             | ISS                          | ISS Filter Status       |  |  |  |  |  |  |

| 7                        | 6    | 59                         |             | GNDIF1                       | FM IF1 Ground           |  |  |  |  |  |  |

| 7                        | 7    | 60                         |             | IFAGCIN                      | IF AGC Input            |  |  |  |  |  |  |

| 7                        | 8    | 61                         |             | VCCIF1                       | IF1 Supply              |  |  |  |  |  |  |

| 7                        | 9    | 63                         |             | MIX1OUT2                     | Mixer1 Ouput 2          |  |  |  |  |  |  |

| 8                        | 0    | 64                         |             | MIX1OUT1                     | Mixer1 Ouput 1          |  |  |  |  |  |  |

|                          |      |                            |             |                              |                         |  |  |  |  |  |  |

#### Table 1. Pin configuration (continued)

Note: All NC pins can be connected to Ground.

## 2.1 Thermal data

#### Table 2.Thermal data

| Symbol                | Parameter                                                              | Value | Units |

|-----------------------|------------------------------------------------------------------------|-------|-------|

| R <sub>Th j-amb</sub> | Thermal Resistance junction to ambient – IC soldered on multilayer PCB | 53    | °C/W  |

**TDA7546**

## 3 Electrical specification

## 3.1 Absolute maximum ratings

|            |                      | Aboolato maximali fat     | ingo                                            |                 |       |

|------------|----------------------|---------------------------|-------------------------------------------------|-----------------|-------|

|            | Symbol               |                           | Parameter                                       | Value           | Units |

|            | V <sub>CC</sub>      | Supply Voltage (Tuner)    | 10.5                                            | V               |       |

| ataSheet4U | l.comV <sub>DD</sub> | Supply Voltage (RDS)      | 4                                               | V               |       |

|            | T <sub>amb</sub>     | Ambient Operating Tempera | -40 to 85                                       | °C              |       |

|            | T <sub>stg</sub>     | Storage Temperature       |                                                 |                 | °C    |

|            |                      |                           | Human Body Model                                | $\geq \pm 2000$ | V     |

|            |                      |                           | Machine Model                                   | $\geq \pm 200$  | V     |

|            | V <sub>ESD</sub>     | ESD Withstand Voltage     | Charged Device Model, all pins                  | $\geq \pm 250$  | V     |

|            | LOD                  |                           | Charged Device Model, all pins except #3 and #5 | $\geq \pm 500$  | V     |

|            |                      |                           | Charged Device Model, corner pins               | $\geq \pm 750$  | V     |

|            |                      |                           |                                                 |                 |       |

#### Table 3.Absolute maximum ratings

## 3.2 Electrical characteristics

#### Table 4.General parameters

| Symbol             | Parameter             | Test condition                                                                                                                                     | Min | Тур | Max | Units |

|--------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| F <sub>RF</sub>    | RF input frequency    |                                                                                                                                                    | 76  |     | 108 | MHz   |

| AS                 | Audio Sensitivity     | $f_c = 98.1MHz$ , ; $f_{dev} = 22.5KHz$ ;<br>$f_{mod} = 1KHz$ ; dummy antenna;<br>SNR = 26dB; CCIR filter; external<br>pre-emphasis = 50ms         |     |     | 17  | dBμV  |

| RS                 | RDS Sensitivity       | $f_c = 98.1MHz$ , ; $f_{dev} = 2KHz$ ; no audio<br>modulation; dummy antenna; Block<br>Error Rate = 50%                                            |     |     | 23  | dBμV  |

| S/N <sub>max</sub> | Maximum Audio (S+N)/N | $f_c = 98.1MHz$ , ; $f_{dev} = 22.5KHz$ ;<br>$f_{mod} = 1KHz$ ; dummy antenna; mono<br>signal; CCIR filter; external pre-<br>emphasis = 50 $\mu$ s | 55  | 60  |     | dB    |

## 3.3 Tuner

#### Table 5. Tuner

$\begin{array}{l} (T_{amb}=-40 \ to \ +85^{\circ}C, \ V_{CC1}=V_{CC2}=V_{CC3}=V_{CCVCO}=V_{CCMIX1}=V_{CCIF1}=8.5V, \\ f_{RF}=98.1MHz, \ dev.=40KHz, \ f_{MOD}=1KHz, \ f_{IF1}=10.7MHz, \ f_{IF2}=450KHz, \\ f_{Xtal}=10.25MHz, \ in \ application \ circuit, \ unless \ otherwise \ specified.) \end{array}$

| Symbol              | Parameter                       | Test Conditions                                                                                                                                                    | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply              |                                 |                                                                                                                                                                    |      | 1    |      |      |

| V <sub>CC1</sub>    | Digital supply voltage          |                                                                                                                                                                    | 7.7  | 8.5  | 10   | V    |

| V <sub>CC2</sub>    | Analog supply voltage           |                                                                                                                                                                    | 7.7  | 8.5  | 10   | V    |

| V <sub>CC3</sub>    | Tuning section voltage          |                                                                                                                                                                    | 7.7  | 8.5  | 10   | V    |

| V <sub>CCVCO</sub>  | VCO supply voltage              |                                                                                                                                                                    | 7.7  | 8.5  | 10   | V    |

| V <sub>CCMIX1</sub> | MIX1 supply voltage             |                                                                                                                                                                    | 7.7  | 8.5  | 10   | V    |

| V <sub>CCIF1</sub>  | IF1 supply voltage              |                                                                                                                                                                    | 7.7  | 8.5  | 10   | V    |

| I <sub>CC1</sub>    | Supply current                  |                                                                                                                                                                    |      | 7.5  | 10   | mA   |

| I <sub>CC2</sub>    | Supply current                  |                                                                                                                                                                    |      | 60   | 70   | mA   |

| I <sub>CC3</sub>    | Supply current                  |                                                                                                                                                                    |      | 2    | 3    | mA   |

| I <sub>CCVCO</sub>  | Supply current                  |                                                                                                                                                                    |      | 9.5  | 12   | mA   |

| I <sub>CCMIX1</sub> | Supply current                  |                                                                                                                                                                    |      | 8    | 10.5 | mA   |

| I <sub>CCIF1</sub>  | Supply current                  |                                                                                                                                                                    |      | 6    | 7.5  | mA   |

| Reference           | Voltages                        | ·                                                                                                                                                                  |      |      |      |      |

| V <sub>REF1</sub>   | Internal reference voltage      | I <sub>REF1</sub> = 0mA                                                                                                                                            | 4.8  | 5    | 5.2  | V    |

| V <sub>REF2</sub>   | Internal reference voltage      | I <sub>REF2</sub> = 0mA                                                                                                                                            | 2.3  | 2.5  | 2.7  | V    |

| Wide Band           | IRF AGC                         |                                                                                                                                                                    |      |      |      |      |

|                     | Lower threshold start           | V <sub>6</sub> = 2.5V                                                                                                                                              | 78   | 82   | 86   | dBµ∖ |

| V <sub>3-5</sub>    | Upper threshold start           | V <sub>6</sub> = 2.5V                                                                                                                                              | 90   | 94   | 98   | dBµ∖ |

| Narrow Ba           | nd IF & Keying AGC              |                                                                                                                                                                    |      | •    |      |      |

|                     | Lower threshold start           | $KAGC = off, V_{3-5} = 0mV_{RMS}$                                                                                                                                  | 82   | 86   | 90   | dBµ∖ |

| V <sub>77</sub>     | Upper threshold start           | KAGC = off, $V_{3-5} = 0mV_{RMS}$                                                                                                                                  | 94   | 98   | 102  | dBµ∖ |

| • 77                | Lower threshold start with KAGC | $\label{eq:KAGC} \begin{array}{l} KAGC = max, \ V_{3\text{-}5} = 0mV_{RMS,} \\ \Delta f_{IF} {=} 300KHz \end{array}$                                               | 94   | 98   | 102  | dBµ∖ |

| V <sub>56</sub>     | Startpoint KAGC                 | $\label{eq:KAGC} \begin{array}{l} KAGC = max,  V_{3\text{-}5} = 0mV_{RMS,} \\ \Delta f_{IF} = 300KHz \\ f_{IF1} \text{ generate FSW level at } V_{56} \end{array}$ |      | 3.6  |      | v    |

| Δ                   | Control range KAGC              | $\Delta V_{56} = +0.4 V$                                                                                                                                           |      | 16   |      | dB   |

| R <sub>IN</sub>     | Input resistance                |                                                                                                                                                                    | 10   | 13   | 16   | kΩ   |

#### Table 5. Tuner (continued)

$(T_{amb} = -40 \text{ to } +85^{\circ}\text{C}, V_{CC1} = V_{CC2} = V_{CC3} = V_{CCVCO} = V_{CCMIX1} = V_{CCIF1} = 8.5\text{V}, f_{RF} = 98.1\text{MHz}, \text{dev.} = 40\text{KHz}, f_{MOD} = 1\text{KHz}, f_{IF1} = 10.7\text{MHz}, f_{IF2} = 450\text{KHz}, f_{Xtal} = 10.25\text{MHz}, \text{ in application circuit, unless otherwise specified.}$

| Symbol                                 | Parameter                      | Min.                                                            | Тур.  | Max.     | Uni                                   |     |

|----------------------------------------|--------------------------------|-----------------------------------------------------------------|-------|----------|---------------------------------------|-----|

| AGC Time                               | Constant Output                |                                                                 |       | <u>.</u> |                                       |     |

| V <sub>6</sub> Max. AGC output voltage |                                | $V_{3-5} = 0mV_{RMS}$                                           |       |          | V <sub>REF1</sub><br>+V <sub>BE</sub> | v   |

|                                        | Min. AGC output voltage        |                                                                 |       | 0.5      | V                                     |     |

| <br>I                                  | Min. AGC charge current        | V <sub>3-5</sub> = 0mV <sub>RMS</sub> ,V <sub>10</sub> = 2.5V   | -16.5 | -12.5    | -8.5                                  | μA  |

| I <sub>6</sub>                         | Max. AGC discharge current     | $V_{3-5} = 50mV_{RMS}, V_{10} = 2.5V$                           | 0.9   | 1.25     | 1.6                                   | mA  |

| AGC PIN D                              | iode Driver Output             |                                                                 |       |          |                                       |     |

| 1                                      | AGC OUT, current min.          | V <sub>3-5</sub> = 0mV <sub>RMS</sub> , V <sub>2</sub> = 2.5V   | 9     | 12       | 15                                    | μA  |

| l <sub>2</sub>                         | AGC OUT, current max.          | V <sub>3-5</sub> = 50 mV <sub>RMS</sub> , V <sub>2</sub> = 2.5V | -22   | -17      | -13                                   | mA  |

| I/Q Mixer1                             | (10.7MHz)                      |                                                                 |       | L        |                                       |     |

| R <sub>IN</sub>                        | Input resistance               | differential                                                    |       | 10       |                                       | k۵  |

| R <sub>OUT</sub>                       | Output resistance              | differential                                                    | 100   |          |                                       | kΩ  |

| V <sub>3-5</sub>                       | Input dc bias                  |                                                                 | 2.4   | 2.65     | 2.9                                   | V   |

| 9 <sub>m</sub>                         | Conversion<br>transconductance |                                                                 |       | 17       |                                       | m   |

| F                                      | Noise figure                   | 400 $\Omega$ generator resistance <sup>(1)</sup>                |       | 3        |                                       | dE  |

| CP <sub>1dB</sub>                      | 1dB compression point          | referred to diff. mixer input                                   |       | 100      |                                       | dBµ |

| IIP3                                   | 3rd order intermodulation      | (1)                                                             |       | 122      |                                       | dBµ |

| IQG                                    | I/Q gain adjust                | G                                                               | -1    |          | +1                                    | %   |

| IQP                                    | I/Q phase adjust               | PH                                                              | -7    |          | +8                                    | 0   |

| IRR                                    | Image rejection ratio          | with gain and phase adjust                                      | 40    |          |                                       | dE  |

| IF1 Amplifi                            | er1,2 (10.7MHz)                |                                                                 |       |          |                                       |     |

| G1 <sub>min</sub>                      | Min. gain                      | IFG, referred to $330\Omega$                                    | 7.5   | 9        | 10.5                                  | dE  |

| G1 <sub>max</sub>                      | Max. gain                      | IFG, referred to $330\Omega$                                    | 13.5  | 15       | 16.5                                  | dE  |

| G2 <sub>min</sub>                      | Min. gain                      | IFG, referred to $330\Omega$                                    | 7.5   | 9        | 10.5                                  | dE  |

| G2 <sub>max</sub>                      | Max. gain                      | IFG, referred to $330\Omega$                                    | 9.5   | 11       | 13.5                                  | dE  |

| R <sub>IN</sub>                        | Input resistance               |                                                                 | 250   | 330      | 400                                   | Ω   |

| R <sub>OUT</sub>                       | Output resistance              |                                                                 | 250   | 330      | 400                                   | Ω   |

| CP <sub>1dB</sub>                      | 1dB compression point          | referred to $330\Omega$ input <sup>(1)</sup>                    |       | 105      |                                       | dBµ |

| IIP3                                   | 3rd order Intermodulation      | referred to $330\Omega$ input <sup>(1)</sup>                    |       | 126      |                                       | dBµ |

| Demodulat                              | or, Audio Output               |                                                                 |       |          |                                       |     |

| THD                                    | Total Harmonic Distortion      | dev. = 75kHz, V = Mix2 = 10 mVrms                               |       |          | 0.1                                   | %   |

#### Table 5.Tuner (continued)

$(T_{amb} = -40 \text{ to } +85^{\circ}\text{C}, V_{CC1} = V_{CC2} = V_{CC3} = V_{CCVCO} = V_{CCMIX1} = V_{CCIF1} = 8.5\text{V}, f_{RF} = 98.1\text{MHz}, \text{dev.} = 40\text{KHz}, f_{MOD} = 1\text{KHz}, f_{IF1} = 10.7\text{MHz}, f_{IF2} = 450\text{KHz}, f_{Xtal} = 10.25\text{MHz}, \text{ in application circuit, unless otherwise specified.}$

| Symbol              | Parameter                | Test Conditions                  | Min. | Тур. | Max. | Unit  |  |

|---------------------|--------------------------|----------------------------------|------|------|------|-------|--|

| V <sub>OUT</sub>    | Output Voltage           | dev. = 75kHz                     | 400  | 500  | 600  | mVrms |  |

| R <sub>OUT</sub>    | Output resistance        |                                  | 15   | 40   | 65   | Ω     |  |

| I∆VI <sub>min</sub> | DC offset fine adjust    | DEM, MENA=1                      |      | 8.5  |      | mV    |  |

| l∆VI <sub>max</sub> | DC offset fine adjust    | DEM, MENA=1                      |      | 264  |      | mV    |  |

| QUALITY D           | ETECTION                 |                                  |      |      |      |       |  |

| S-meter, U          | nweighted Fieldstrength  |                                  |      |      |      |       |  |

|                     | Fieldstrength output     | $V_{46} = 0V_{RMS}$              |      | 0.1  |      | V     |  |

| V <sub>14</sub>     | Fieldstrength output     | $V_{46} = 1V_{RMS}$              |      | 4.9  |      | V     |  |

|                     | voltage per decade       | SMSL = 0                         | 0.75 | 1    | 1.25 | V     |  |

| $\Delta V_{14}$     | voltage per decade       | SMSL = 1                         | 1.1  | 1.5  | 1.9  | V     |  |

|                     | S-meter offset           | SL, SMSL=1                       | -15  |      | 15   | dB    |  |

| R <sub>OUT</sub>    | Output resistance        |                                  | 300  | 450  | 650  | Ω     |  |

| S-meter, W          | eighted Fieldstrength    |                                  | ·    |      |      |       |  |

|                     | Fieldstrength output     | $V_{46} = 0V_{RMS}$              |      | 2.5  |      | V     |  |

| V <sub>35</sub>     | Fieldstrength output     | $V_{46} = 1V_{RMS}$              |      | 4.9  |      | V     |  |

| R <sub>OUT</sub>    | Output resistance        |                                  | 12   | 13.5 | 15   | kΩ    |  |

| Adjacent C          | Channel Output           |                                  |      |      |      | •     |  |

|                     | Output voltage low       |                                  |      | 0.1  | 0.2  | V     |  |

| V <sub>13</sub>     | Output voltage high      |                                  | 4.4  | 4.9  |      | V     |  |

| R <sub>OUT</sub>    | Output resistance        |                                  | 3.5  | 4.5  | 5.5  | kΩ    |  |

| Multipath           | Output                   |                                  |      |      |      |       |  |

|                     | Output voltage low       |                                  |      | 0.1  | 0.2  | V     |  |

| V <sub>34</sub>     | Output voltage high      |                                  | 4.4  | 4.9  |      | V     |  |

| R <sub>OUT</sub>    | Output resistance        |                                  | 2    | 3.5  | 5    | kΩ    |  |

| ISS (Intelliç       | gent Selectivity System) |                                  |      |      |      |       |  |

| Filter 450K         | Hz                       |                                  |      |      |      |       |  |

| f <sub>centre</sub> | Centre frequency         | f <sub>REF_intern</sub> = 450KHz |      | 450  |      | KHz   |  |

| BW 3dB              | Bandwidth, -3dB          | ISS80 = 1                        | 70   | 80   | 80   | KHz   |  |

| BW 20dB             | Bandwidth, -20dB         | ISS80 = 1                        | 135  | 150  | 165  | KHz   |  |

| BW 3dB              | Bandwidth, -3dB          | ISS80 = 0                        | 105  | 120  | 135  | KHz   |  |

| BW 20dB             | Bandwidth, -20dB         | ISS80 = 0                        | 220  | 250  | 280  | KHz   |  |

#### Table 5.Tuner (continued)

$\begin{array}{l} (T_{amb}=-40 \text{ to } +85^\circ\text{C}, \ V_{CC1}=V_{CC2}=V_{CC3}=V_{CCVCO}=V_{CCMIX1}=V_{CCIF1}=8.5\text{V}, \\ f_{RF}=98.1\text{MHz}, \ dev.=40\text{KHz}, \ f_{MOD}=1\text{KHz}, \ f_{IF1}=10.7\text{MHz}, \ f_{IF2}=450\text{KHz}, \\ f_{Xtal}=10.25\text{MHz}, \ in \ application \ circuit, \ unless \ otherwise \ specified.) \end{array}$

| Symbol                   | Parameter                  | Test Conditions  | Min. | Тур. | Max. | Unit |  |  |  |

|--------------------------|----------------------------|------------------|------|------|------|------|--|--|--|

| ISS Filter Time Constant |                            |                  |      |      |      |      |  |  |  |

|                          | Charge current low mid     | TISS, ISSCTL = 1 |      | -74  |      | μA   |  |  |  |

|                          | Charge current high mid    | TISS, ISSCTL = 1 | -80  | -60  | -40  | μA   |  |  |  |

| IU.com                   | Charge current low narrow  | TISS, ISSCTL = 1 |      | -124 |      | μA   |  |  |  |

| I <sub>15</sub>          | Charge current high narrow | TISS, ISSCTL = 1 | -140 | -110 | -80  | μA   |  |  |  |

|                          | Discharge current low      | TISS, ISSCTL = 0 | 0.5  | 1    | 2    | μA   |  |  |  |

|                          | Discharge current high     | TISS, ISSCTL = 0 | 10   | 15   | 20   | μA   |  |  |  |

| V                        | Low voltage                | ISSCTL = 0       |      | 0.1  | 0.2  | V    |  |  |  |

| V <sub>15</sub>          | High voltage               | ISSCTL = 1       | 4.6  | 4.9  |      | V    |  |  |  |

1. Guaranteed by design

#### 3.3.1 Additional parameters

#### Table 6.Additional parameters

| Symbol                   | Parameter                           | Test Conditions                  | Min. | Тур.  | Max.                      | Unit  |  |  |  |  |  |  |  |

|--------------------------|-------------------------------------|----------------------------------|------|-------|---------------------------|-------|--|--|--|--|--|--|--|

| Output of 7              | Dutput of Tuning Voltages (TV1,TV2) |                                  |      |       |                           |       |  |  |  |  |  |  |  |

| V <sub>OUT</sub>         | Output voltage                      | туо                              | 0.5  |       | V <sub>CC3</sub> -<br>0.5 | V     |  |  |  |  |  |  |  |

| R <sub>OUT</sub>         | Output impedance                    |                                  | 18   | 21.5  | 25                        | kΩ    |  |  |  |  |  |  |  |

| Xtal Refere              | ence Oscillator                     |                                  |      |       |                           |       |  |  |  |  |  |  |  |

| f <sub>LO</sub>          | Reference frequency                 | C <sub>Load</sub> = 15pF         |      | 10.25 |                           | MHz   |  |  |  |  |  |  |  |

| C <sub>Step</sub>        | Min. cap step                       | XTAL                             |      | 0.75  |                           | pF    |  |  |  |  |  |  |  |

| C <sub>max</sub>         | Мах. сар                            | XTAL                             |      | 23.25 |                           | pF    |  |  |  |  |  |  |  |

| Δf/f                     | Deviation versus VCC2               | $\Delta V_{CC2} = 1V^{(1)}$      |      | 1.5   |                           | ppm/V |  |  |  |  |  |  |  |

| $\Delta f/f$             | Deviation versus temp               | -40°C < T < +85°C <sup>(1)</sup> |      | 0.2   |                           | ppm/K |  |  |  |  |  |  |  |

| I <sup>2</sup> C-Bus int | erface                              |                                  |      |       |                           |       |  |  |  |  |  |  |  |

| f <sub>SCL</sub>         | Clock frequency                     |                                  |      |       | 400                       | KHz   |  |  |  |  |  |  |  |

| V <sub>IL</sub>          | Input low voltage                   |                                  |      |       | 1                         | V     |  |  |  |  |  |  |  |

| V <sub>IH</sub>          | Input high voltage                  |                                  | 2.5  |       |                           | V     |  |  |  |  |  |  |  |

| I <sub>IN</sub>          | Input current                       |                                  | -5   |       | 5                         | μA    |  |  |  |  |  |  |  |

| Vo                       | Output acknowledge voltage          | I <sub>O</sub> = 1.6mA           |      |       | 0.4                       | V     |  |  |  |  |  |  |  |

| Loop Filte               | Loop Filter Input/Output            |                                  |      |       |                           |       |  |  |  |  |  |  |  |

| Table 0.            | ible 6. Additional parameters (continued) |                                                           |                           |                            |      |      |  |  |

|---------------------|-------------------------------------------|-----------------------------------------------------------|---------------------------|----------------------------|------|------|--|--|

| Symbol              | Parameter                                 | Test Conditions                                           | Min.                      | Тур.                       | Max. | Unit |  |  |

| -I <sub>IN</sub>    | Input leakage current                     | V <sub>IN</sub> = GND, PD <sub>OUT</sub> = Tristate       | -0.1                      |                            | 0.1  | μA   |  |  |

| I <sub>IN</sub>     | Input leakage current                     | V <sub>IN</sub> = VREF1<br>PD <sub>OUT</sub> = Tristate   | -0.1                      |                            | 0.1  | mA   |  |  |

| V <sub>OL</sub>     | Output voltage Low                        | I <sub>OUT</sub> = -0.2mA                                 |                           | 0.05                       | 0.5  | V    |  |  |

| V <sub>OH</sub>     | Output voltage High                       | I <sub>OUT</sub> = 0.2mA                                  | V <sub>CC3</sub> -<br>0.5 | V <sub>CC3</sub> -<br>0.05 |      | V    |  |  |

|                     | Output current, sink                      | $V_{OUT} = 1V$ to $V_{CC3}$ -1V                           |                           |                            | 10   | mA   |  |  |

| IU.comlout          | Output current, source                    | $V_{OUT} = 1V$ to $V_{CC3}$ -1V                           | -10                       |                            |      | mA   |  |  |

| Voltage C           | ontrolled Oscillator (VCO)                |                                                           |                           |                            |      |      |  |  |

| f <sub>VCOmin</sub> | Minimum VCO frequency <sup>(2)</sup>      |                                                           | 50                        |                            |      | MHz  |  |  |

| f <sub>VCOmax</sub> | Maximum VCO frequency <sup>(2)</sup>      |                                                           |                           |                            | 260  | MHz  |  |  |

| C/N                 | Carrier to Noise                          | f <sub>VCO</sub> = 200MHz, ∆f=1KHz,<br>B=1Hz, closed loop |                           | 80                         |      | dBc  |  |  |

| SSTOP Ou            | itput (Open Collector)                    |                                                           |                           |                            |      |      |  |  |

| N                   | Output voltage low                        | I <sub>24</sub> = -200μA                                  |                           | 0.2                        | 0.5  | V    |  |  |

| V <sub>24</sub>     | Output voltage high                       |                                                           |                           |                            | 5    | V    |  |  |

| -I <sub>24</sub>    | Output leakage current                    | V <sub>24</sub> = 5V                                      | -0.1                      |                            | 0.1  | μA   |  |  |

| I <sub>24</sub>     | Output current, sink                      | $V_{24} = 0.5V-5V$                                        |                           |                            | 1    | mA   |  |  |

| ISSSTATU            | S Output (Open Drain)                     |                                                           |                           |                            |      |      |  |  |

| V                   | Output voltage low, ISS-Filter<br>"ON"    | I <sub>24</sub> = -200μA                                  |                           | 0.2                        | 0.5  | V    |  |  |

| V <sub>58</sub>     | Output voltage high, ISS-<br>Filter "OFF" |                                                           |                           |                            | 5    | V    |  |  |

| -I <sub>58</sub>    | Output leakage current                    | V <sub>24</sub> = 5V                                      | -0.1                      |                            | 0.1  | μA   |  |  |

| I <sub>58</sub>     | Output current, sink                      | V <sub>24</sub> = 0.5V-5V                                 |                           |                            | 300  | μA   |  |  |

#### Table 6. Additional parameters (continued)

1. Guaranteed by design

2. Depending on external application circuit.

## 3.4 RDS decoder

### 3.4.1 General interface electrical characteristics

#### Table 7. General interface electrical characteristics

|        | Symbol               | Parameter                                     | Test Conditions                 |      | Unit |      |      |

|--------|----------------------|-----------------------------------------------|---------------------------------|------|------|------|------|

|        |                      | Falameter                                     | Test Conditions                 | Min. | Тур. | Max. | Unit |

|        | l <sub>il</sub>      | Low Level Input Current                       | V <sub>i</sub> =0V              |      |      | 1    | μA   |

| heet4U | .com l <sub>ih</sub> | High Level Input Current                      | V <sub>i</sub> =V <sub>DD</sub> |      |      | 1    | μA   |

|        |                      |                                               | $V_{o} = 0V \text{ or } V_{DD}$ |      |      | 1    | μA   |

|        | I <sub>ozFT</sub>    | Output Leakage Without Pull<br>Up/Down Device | V <sub>o</sub> =5.5V            |      | 1    | 3    | μA   |

### 3.4.2 Electrical characteristics

#### Table 8.Electrical characteristics

$(T_{amb} = -40 \text{ to } +85 \text{ °C}, V_{DDA}/V_{DDD} = 3.0 \text{ to } 3.6 \text{ V}, f_{osc} = 10.25 \text{ MHz}$ , unless otherwise specified  $V_{DDD}$  and  $V_{DDA}$  must not differ more than 0.15V).

| Symbol              | Parameter                         | Min.                                                                         | Тур. | Max. | Unit |    |  |  |  |  |  |  |  |

|---------------------|-----------------------------------|------------------------------------------------------------------------------|------|------|------|----|--|--|--|--|--|--|--|

| Supply (p           | Supply (pin 44, 50, 52)           |                                                                              |      |      |      |    |  |  |  |  |  |  |  |

| V <sub>DDD</sub>    | Digital Supply Voltage            |                                                                              | 3.0  | 3.3  | 3.6  | V  |  |  |  |  |  |  |  |

| V <sub>DDA</sub>    | Analog Supply Voltage             |                                                                              | 3.0  | 3.3  | 3.6  | V  |  |  |  |  |  |  |  |

|                     | Digital Supply Current            | Normal mode                                                                  |      | 14   | 16   | mA |  |  |  |  |  |  |  |

| IDDD                |                                   | Power down mode                                                              |      | <1   |      | μA |  |  |  |  |  |  |  |

|                     | Analog Supply Current             | Normal mode                                                                  |      | 11   | 14   | mA |  |  |  |  |  |  |  |

| I <sub>DDA</sub>    | Power down mode                   | Power down mode                                                              |      | <1   |      | mA |  |  |  |  |  |  |  |

| Digital Inp         | outs (pin 51, 32, 36, 37, 38, 39) |                                                                              |      |      |      |    |  |  |  |  |  |  |  |

| V <sub>il</sub>     | Low level input voltage           |                                                                              |      |      | 0.8  | V  |  |  |  |  |  |  |  |

| V <sub>ih</sub>     | High level input voltage          |                                                                              | 2.0  |      |      | V  |  |  |  |  |  |  |  |

| V <sub>ilhyst</sub> | Low level threshold input falling |                                                                              | 1.0  |      | 1.15 | V  |  |  |  |  |  |  |  |

| V <sub>ihhyst</sub> | High level threshold input rising |                                                                              | 1.5  |      | 1.7  | V  |  |  |  |  |  |  |  |

| V <sub>hst</sub>    | Schmitt trigger hysteresis        |                                                                              | 0.4  |      | 0.7  | V  |  |  |  |  |  |  |  |

| Digital Ou          | tputs (pin 37,38,40) are open d   | rains                                                                        | -    |      |      |    |  |  |  |  |  |  |  |

| V <sub>ol</sub>     | Low level output Voltage          | I <sub>ol</sub> =4mA, takes into account 200mV<br>drop in the supply voltage |      |      | 0.4  | V  |  |  |  |  |  |  |  |

57

### Table 8. Electrical characteristics (continued)

$(T_{amb} = -40 \text{ to } +85 \text{ °C}, V_{DDA}/V_{DDD} = 3.0 \text{ to } 3.6 \text{ V}, f_{osc} = 10.25 \text{ MHz}$ , unless otherwise specified  $V_{DDD}$  and  $V_{DDA}$  must not differ more than 0.15V).

| Symbol                  | Parameter                                | Test Conditions     | Min. | Тур. | Max.            | Unit |

|-------------------------|------------------------------------------|---------------------|------|------|-----------------|------|

| Analog In               | puts (pin 41)                            |                     |      |      |                 |      |

|                         | Input Range of MPX Signal                |                     |      |      | 0.75            | Vrms |

| V <sub>MPX</sub>        | Input Impedance of MPX pin               |                     | 45k  | 55k  | 65k             | Ohm  |

| M                       | Internal Reference Voltage               |                     | 0.5  |      | 0.9             | V    |

| V <sub>REF1</sub>       | Internal Reference Impedance             |                     | 1.3  |      | 2               | kΩ   |

| V                       | Internal Reference Voltage               |                     | 1.5  |      | 2.1             | V    |

| V <sub>REF2</sub>       | Internal Reference Impedance             |                     | 2.15 |      | 2.95            | kΩ   |

| V                       | Internal Reference Voltage               |                     | 2.6  |      | 3.2             | V    |

| V <sub>REF3</sub>       | Internal Reference Impedance             |                     | 1.3  |      | 2.0             | kΩ   |

| PLL parar               | neters                                   |                     |      | •    |                 |      |

| f <sub>vco</sub>        | VCO Range                                |                     | 150  |      | 250             | MHz  |

| f <sub>vin</sub>        | VCO Input Range                          |                     | 4    |      | 21              | MHz  |

| t <sub>lock</sub>       | PLL Lock Time                            |                     |      |      | 500             | μs   |

| I <sub>DF</sub>         | Input Divide Factor                      |                     | 1    |      | 32              |      |

| O <sub>DF</sub>         | Output Divide Factor                     |                     | 2    |      | 32              |      |

| M <sub>F</sub>          | Integer Multiplication Factor            |                     | 9    |      | 128             |      |

| FRA                     | Fractional Multiplication Factor         | FRA/2 <sup>14</sup> | 0    | -    | 2 <sup>14</sup> |      |

| l <sup>2</sup> C (@ fsy | s = 8.55/8.664MHz)                       |                     |      |      |                 |      |

| f <sub>I2C</sub>        | clock frequency in I <sup>2</sup> C mode |                     |      |      | 400             | KHz  |

| SPI (@ fsy              | /s = 8.55/8.664MHz)                      |                     | •    |      |                 |      |

| f <sub>SPI</sub>        | clock frequency in SPI mode              |                     |      |      | 1               | MHz  |

| t <sub>ch</sub>         | clock high time                          |                     | 450  |      |                 | ns   |

| t <sub>cl</sub>         | clock low time                           |                     | 450  |      |                 | ns   |

| t <sub>csu</sub>        | chip select setup time                   |                     | 500  |      |                 | ns   |

| t <sub>csh</sub>        | chip select hold                         |                     | 500  |      |                 | ns   |

| t <sub>odv</sub>        | output data valid                        |                     |      |      | 250             | ns   |

| t <sub>oh</sub>         | output hold                              |                     | 0    |      |                 | ns   |

| t <sub>d</sub>          | deselect time                            |                     | 1000 |      |                 | ns   |

| t <sub>su</sub>         | data setup time                          |                     | 200  |      |                 | ns   |

| t <sub>h</sub>          | data hold time                           |                     | 200  |      |                 | ns   |

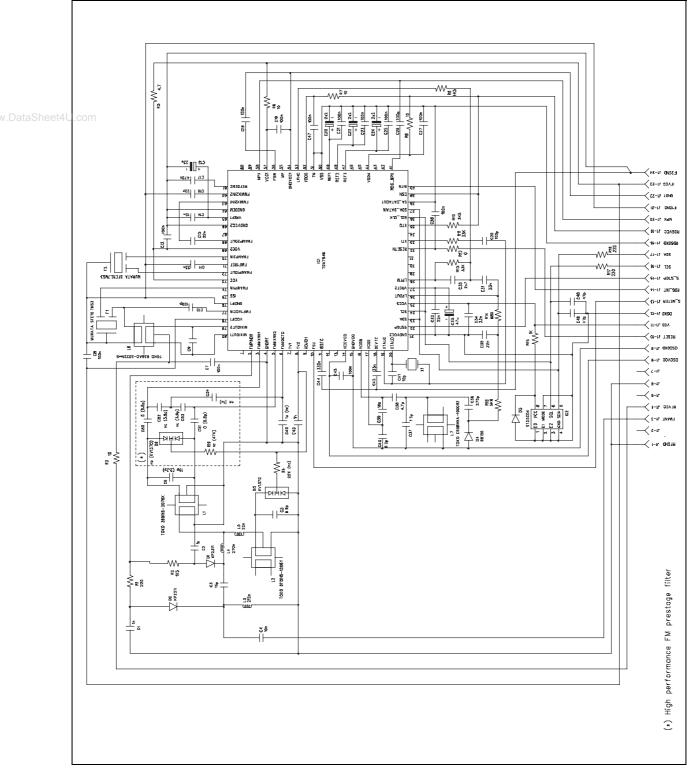

## 4 Applications and test circuit

#### Figure 3. Applications and test circuit

57

## 5 Functional description

### 5.1 Tuner

### 5.1.1 Mixer1, AGC and 1.IF

The FM quadrature I/Q-mixer converts RF to IF1 of 10.7MHz. The mixer provides inherent image rejection and wide dynamic range with low noise and large input signal performance. The mixer1 tank can be adjusted by software (IF1T). For accurate image rejection the gainand phase-error generated as well in mixer as VCO stage can be compensated by software (G,PH)

It is capable of tuning the US FM, US weather, Europe FM, Japan FM and East Europe FM bands

- US FM = 87.9 to 107.9 MHz

- US weather = 162.4 to 162.55 MHz

- Europe FM = 87.5 to 108 MHz

- Japan FM = 76 to 91 MHz

- East Europe FM = 65.8 to 74 MHz

The AGC operates on different sensitivities and bandwidths in order to improve the input sensitivity and dynamic range. AGC thresholds are programmable by software (RFAGC,IFAGC,KAGC). The output signal is a controlled current for double pin diode attenuator. Two 10.7MHz programmable amplifiers (IFG1, IFG2) correct the IF ceramic insertion loss and the costumer level plan application.

#### 5.1.2 Mixer2, limiter and demodulator

In this 2. mixer stage the first 10.7MHz IF is converted into the second 450KHz IF. A multistage limiter generates signals for the complete integrated demodulator without external tank. MPX output DC offset versus noise DC level is correctable by software (DEM).

### 5.1.3 Quality detection and ISS

#### Fieldstrength

Parallel to mixer2 input a 10.7MHz limiter generates a signal for digital IF counter and a fieldstrength output signal. This internal unweighted fieldstrength is used for keying AGC, adjacent channel and multipath detection and is available at PIN14 (FSU) after +6dB buffer stage. The behaviour of this output signal can be corrected for DC offset (SL) and slope (SMSL). The internal generated unweighted fieldstrength is filtered at PIN35 and used for softmute function and generation of ISS filter switching signal for weak input level (sm).

#### Adjacent channel detector

The input of the adjacent channel detector is AC coupled from internal unweighted fieldstrength. A programmable highpass or bandpass (ACF) and amplifier (ACG) as well as rectifier determines the influences. This voltage is compared with adjustable comparator1 thresholds (ACWTH, ACNTH). The output signal of this comparator generates a DC level at PIN15 by programmable time constant. Time control (TISS) for a present adjacent channel is made by charge and discharge current after comparator1 in an external capacitance. The

charge current is fixed and the discharge current is controlled by I<sup>2</sup>C Bus. This level produces digital signals (ac, ac+) in an additional comparator4. The adjacent channel information is available as analog output signal after rectifier and +8dB output buffer.

#### **Multipath detector**

The input of the multipath detector is AC coupled from internal unweighted fieldstrength. A programmable bandpass (MPF) and amplifier (MPG) as well as rectifier determines the influences. This voltage is compared with an adjustable comparator2 thresholds (MPTH). The output signal of this comparator2 is used for the "Milano" effect. In this case the adjacent channel detection is switched off. The "Milano" effect is selectable by I<sup>2</sup>C Bus (MPOFF). The multipath information is available as analog output signal after rectifier and +8dB output buffer.

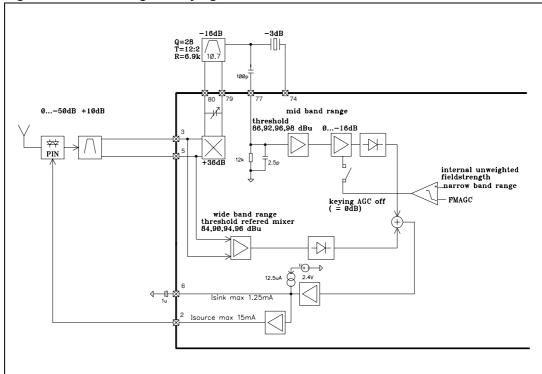

#### 450KHz IF narrow bandpass filter (ISS filter)

The device gets an additional second IF narrow bandpass filter for suppression of noise and adjacent channel signal influences. This narrow filter has three switchable bandwidthes, narrow range of 80KHz, mid range of 120KHz and 30KHz for weather band information.

Without ISS filter the IF bandwidth (wide range) is defined only by ceramic filter chain. The filter is switched in after mixer2 before 450KHz limiter stage. The centre frequency is matching to the demodulator center frequency.

#### **Deviation detector**

In order to avoid distortion in audio output signal the narrow ISS filter is switched OFF for present overdeviation. Hence the demodulator output signal is detected.

A lowpass filtering and peak rectifier generates a signal that is defined by software controlled current (TDEV) in an external capacitance. This value is compared with a programmable comparator3 thresholds (DWTH, DTH) and generates two digital signals (dev, dev+). For weak signal condition deviation threshold is proportinal to FSU.

#### **ISS switch logic**

All digital signals coming from adjacent channel detector, deviation detector and softmute are acting via switching matrix on ISS filter switch. The IF bandpass switch mode is controlled by software (ISSON, ISS30, ISS80, CTLOFF).

The switch ON of the IF bandpass is also available by external manipulation of the voltage at PIN15.

Two application modes are available (APPM). The conditions are described in Table 50.

#### 5.1.4 PLL and IF counter section

#### PLL frequency synthesizer block

This part contains a frequency synthesizer and a loop filter for the radio tuning system. Only one VCO is required to build a complete PLL system for FM world tuning . For auto search stop operation an IF counter system is available.

The counter works in a two stages configuration. The first stage is a swallow counter with a two modulus (32/33) precounter. The second stage is an 11-bit programmable counter.

The circuit receives the scaling factors for the programmable counters and the values of the reference frequencies via an  $I^2$ C-Bus interface. The reference frequency is generated by an adjustable internal (XTAL) oscillator followed by the reference divider. The main reference and step-frequencies are free selectable (RC, PC).

Output signals of the phase detector are switching the programmable current sources. The loop filter integrates their currents to a DC voltage.

The values of the current sources are programmable by 6 bits also received via the  $I^2C$  Bus (A, B, CURRH).

To minimize the noise induced by the digital part of the system, a special guard configuration is implemented. The loop gain can be set for different conditions by setting the current values of the chargepump generator.

#### Frequency generation for phase comparison

The RF signals applies a two modulus counter (32/33) pre-scaler, which is controlled by a 5bit A-divider. The 5-bit register (PC0 to PC4) controls this divider. In parallel the output of the prescaler connects to an 11-bit B-divider. The 11-bit PC register (PC5 to PC15) controls this divider

Dividing range:

$f_{VCO} = [33 \text{ x A} + (B + 1 - A) \text{ x 32}] \text{ x } f_{REF}$

$f_{VCO} = (32 \text{ x B} + \text{A} + 32) \text{ x } f_{REF}$

Important: For correct operation: A  $\leq$  32; B  $\geq$  A

#### Three state phase comparator

The phase comparator generates a phase error signal according to phase difference between  $f_{SYN}$  and  $f_{REF}$ . This phase error signal drives the charge pump current generator.

#### Charge pump current generator

This system generators signed pulses of current. The phase error signal decides the duration and polarity of those pulses. The current absolute values are programmable by A register for high current and B register for low current.

#### Inlock detector

Switching the chargepump in low current mode can be done either via software or automatically by the inlock detector, by setting bit LDENA to "1".

After reaching a phase difference about lower than 40nsec the chargepump is forced in low current mode. A new PLL divider alternation by I<sup>2</sup>C-Bus will switch the chargepump in the high current mode.

#### Low noise CMOS op-amp

An internal voltage divider at pin VREF2 connects the positive input of the low noise opamp. The charge pump output connects the negative input. This internal amplifier in cooperation with external components can provide an active filter.

While the high current mode is activated LPHC output is switched on.

#### **IF counter block**

The aim of IF counter is to measure the intermediate frequency of the tuner. The input signal is the 10.7MHz IF level after limiter.

The grade of integration is adjustable by eight different measuring cycle times. The tolerance of the accepted count value is adjustable, to reach an optimum compromise for search speed and precision of the evaluation.

#### Sampling timer

A sampling timer generates the gate signal for the main counter. The basically sampling time are in FM mode 6.25KHz ( $t_{TIM}$ =160 $\mu$ s).

This is followed by an asynchronous divider to generate several sampling times.

#### Intermediate frequency main counter

This counter is a 11 - 21-bit synchronous autoreload down counter. Five bits (CF) are programmable to have the possibility for an adjust to the centre frequency of the IF-filter. The counter length is automatic adjusted to the chosen sampling time.

At the start the counter will be loaded with a defined value which is an equivalent to the divider value ( $t_{Sample} \ge f_{IF}$ ).

If a correct frequency is applied to the IF counter frequency input at the end of the sampling time the main counter is changing its state from 0h to 1FFFFFh.

This is detected by a control logic and an external search stop output is changing from LOW to HIGH. The frequency range inside which a successful count result is adjustable by the EW bits.

$$CNT = \frac{CF + 1696}{f_{IF}}$$

$\begin{array}{l} Counter \ result \ succeeded: \\ t_{TIM} \geq t_{CNT} \ \ t_{ERR} \\ t_{TIM} \leq t_{CNT} \ \ \ t_{ERR} \\ Counter \ result \ failed: \\ t_{TIM} > t_{CNT} \ \ \ \ t_{ERR} \\ t_{TIM} < t_{CNT} \ \ \ \ t_{ERR} \\ \end{array}$

t<sub>TIM</sub> = IF timer cycle time (sampling time)

$t_{CNT} = IF$  counter cycle time

t<sub>ERB</sub> = discrimination window (controlled by the EW registers)

The IF counter is only started by inlock information from the PLL part. It is enabled by software (IFENA).

#### Adjustment of the measurement sequence time

The precision of the measurements is adjustable by controlling the discrimination window. This is adjustable by programming the control registers EW.

The measurement time per cycle is adjustable by setting the registers IFS.

#### Adjust of the frequency value

The center frequency of the discrimination window is adjustable by the control registers CF.

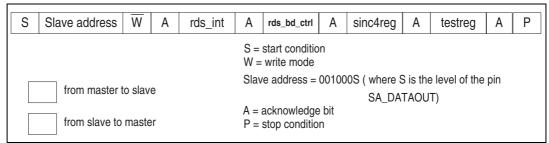

### 5.1.5 I<sup>2</sup>C-bus interface

The TDA7512F supports the  $I^2$ C-Bus protocol. This protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the receiver. The device that controls the transfer is a master and device being controlled is the slave. The master will always initiate data transfer and provide the clock to transmit or receive operations.

#### **Data transition**

Data transition on the SDA line must only occur when the clock SCL is LOW. SDA transitions while SCL is HIGH will be interpreted as START or STOP condition.

#### Start condition

A start condition is defined by a HIGH to LOW transition of the SDA line while SCL is at a stable HIGH level. This "START" condition must precede any command and initiate a data transfer onto the bus.