Digital global standard low IF demodulator for analog TV and FM radio

Rev. 01 — 4 February 2008

**Product data sheet**

# 1. General description

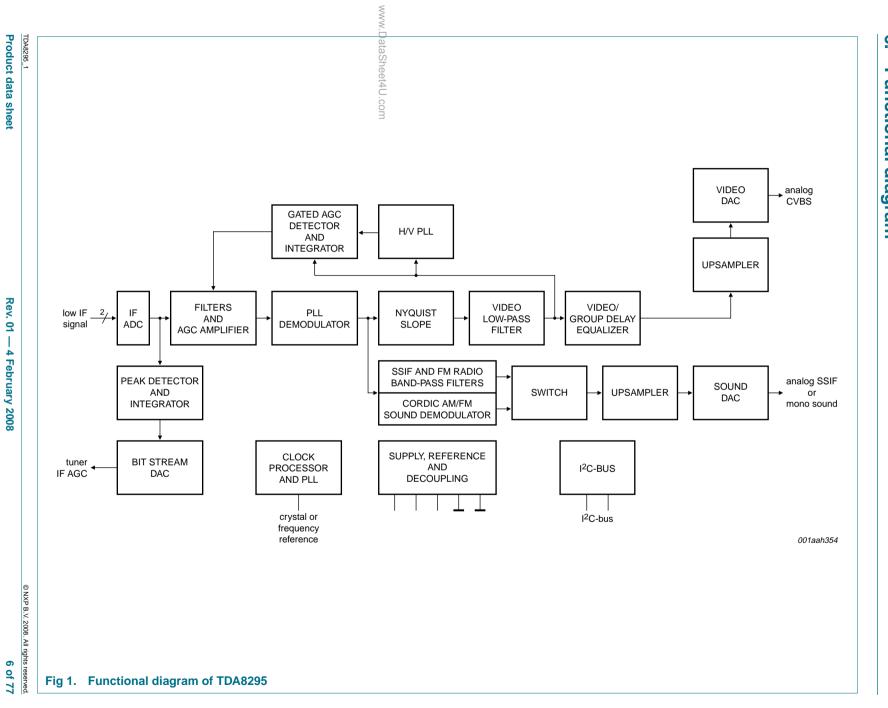

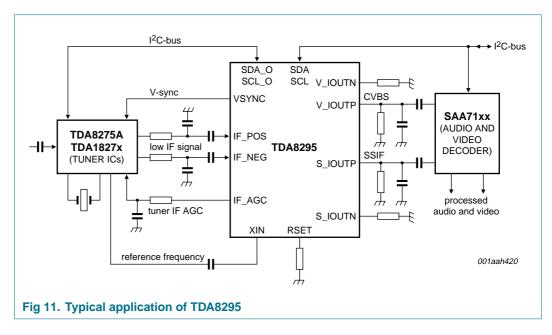

The TDA8295 is an alignment-free digital multistandard vision and sound low IF signal PLL demodulator for positive and negative video modulation including AM and FM mono sound processing. It can be used in all countries worldwide for M/N, B/G/H, I, D/K, L and L-accent standard. CVBS and SSIF/mono audio is provided via two DACs. FM radio preprocessing is included for simple interfacing with demodulator/stereo decoder backends.

The IC is especially suited for the application with the NXP Silicon Tuner TDA8275A or TDA1827x.

All the processing is done in the digital domain.

The chip has an 'easy programming' mode to make the I<sup>2</sup>C-bus protocol very simple. In principle, only one bit sets the proper standard with recommended content. However, if this is not suitable, free programming is always possible.

# 2. Features

www.DataSheet4U.com

- Digital IF demodulation for all analog TV standards worldwide (M/N, B/G/H, D/K, I, L and L-accent standard)

- Multistandard true synchronous demodulation with active carrier regeneration

- Alignment-free

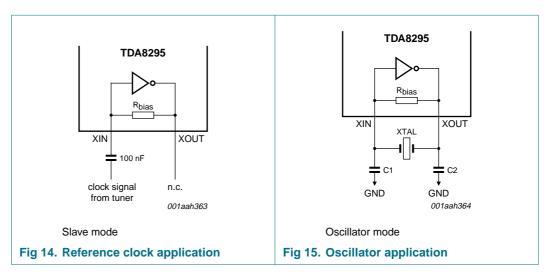

- 16 MHz typical reference frequency input (from low IF tuner) or operating as crystal oscillator

- Internal PLL synthesizer which allows the use of a low-cost crystal (typically 16 MHz)

- Especially suited for the NXP Silicon Tuner TDA8275A or TDA1827x

- No SAW filter needed

- Low application effort and external component count in combination with the TDA8275A or TDA1827x

- Pin compatible with predecessor TDA8290

- Simple upgrade of TDA8290 possible

- 12-bit IF ADC on chip running with 54 MHz or 27 MHz

- Two 10-bit DACs on chip for CVBS and SSIF or audio

- Easy programming for I<sup>2</sup>C-bus

- High flexibility due to various l<sup>2</sup>C-bus programming registers

- I<sup>2</sup>C-bus interface and I<sup>2</sup>C-bus feed-through for tuner programming

- Four I<sup>2</sup>C-bus addresses selectable via two external pins

# **NXP Semiconductors**

**TDA8295**

#### Digital global standard low IF demodulator for analog TV and FM radio

- Gated IF AGC acting on black level by using H/V PLL or peak IF AGC (I<sup>2</sup>C-bus selectable)

- Internal digital logarithmic IF AGC amplifier with up to 48 dB gain and 68 dB control range

- Peak search tuner IF AGC for optimal adaptive drive of the IF ADC

- Switchable IF PLL and IF AGC loop bandwidths

- Precise AFC and lock detector

- Accurate group delay equalization for all standards

- Very robust IF demodulator coping with adverse field conditions

- Wide PLL pull-in range up to ±1660 kHz (l<sup>2</sup>C-bus selectable)

- CVBS and SSIF or audio output with simple postfilter (capacitor only)

- CVBS gain levelling stage to provide nearly constant signal amplitude during overmodulation

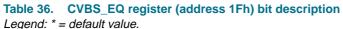

- Video equalizer with eight settings

- Nyquist filter in video baseband

- Excellent video S/N (typically 62 dB weighted)

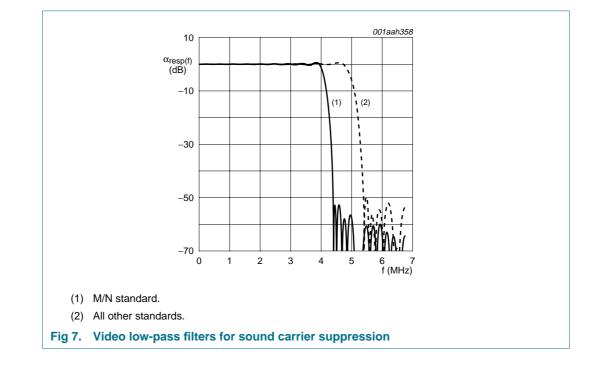

- High selectivity video low-pass filter for all standards

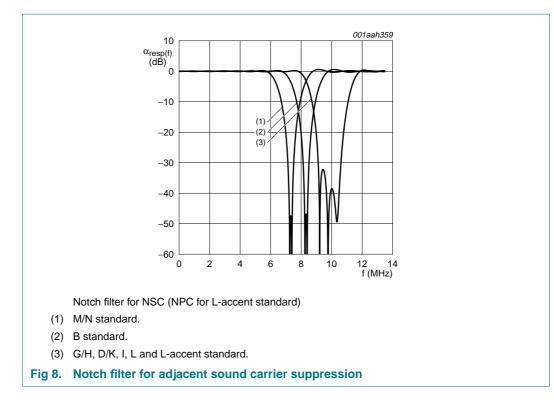

- Low video into sound crosstalk

- Sound performance comparable to QSS single reference concepts

- AM/FM mono sound demodulator

- Switchable de-emphasis

- Excellent FM sound

- Good AM sound

- High FM Deviation mode for China

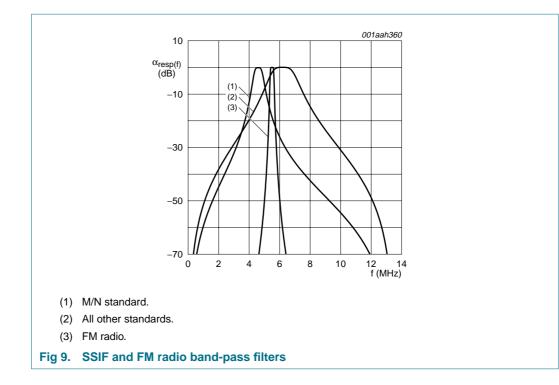

- Preprocessing of FM radio (mono and stereo) with highly selective digital band-pass filter

- No ceramic filter or external components needed for FM radio

- FM radio available in mono

- Automatic or forced mute for mono sound

- Automatic or forced blank for video

- Mostly digital FIR filter implementation (NSC notches and video low-pass filters)

- Three GPIO pins

- Low total power dissipation (typically 324 mW)

- Standby mode (typically 7 mW)

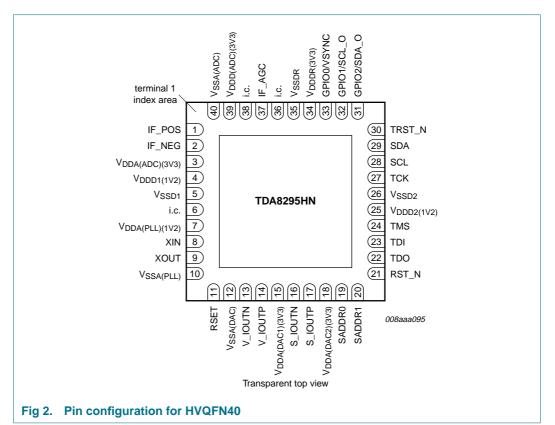

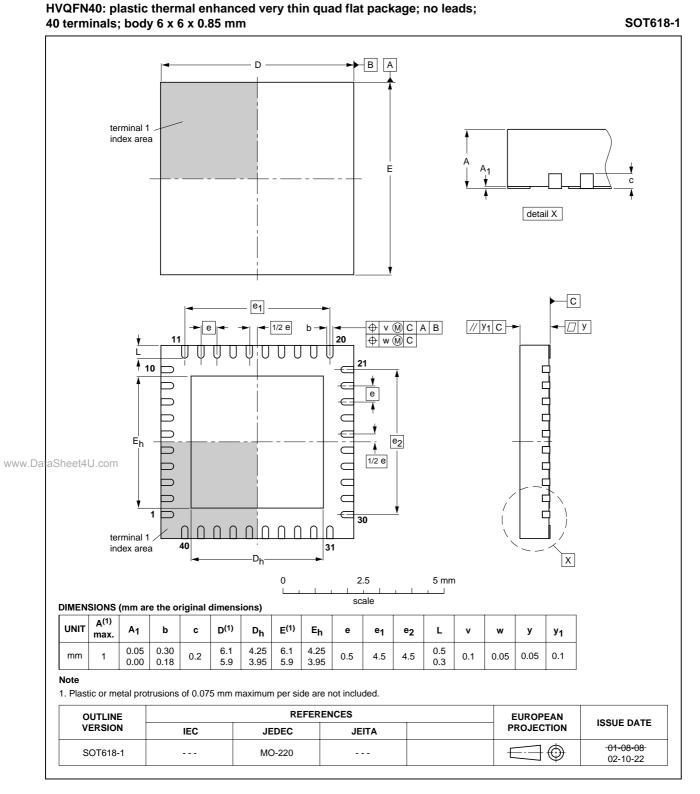

- 40-pin HVQFN package

- CMOS technology (0.12 µm 1.2 V and 3.3 V)

# 3. Applications

www.DataSheet4U.com

- PC TV applications

- DVD recorders

# **NXP Semiconductors**

#### Digital global standard low IF demodulator for analog TV and FM radio

# 4. Quick reference data

#### Table 1. Quick reference data

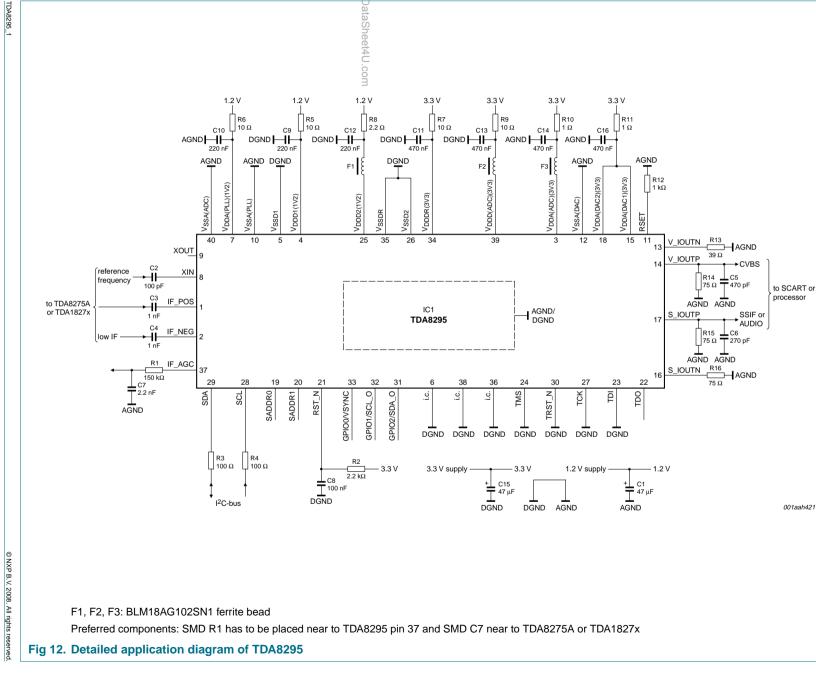

Power supplies 3.3 V, 1.2 V;  $T_{amb} = 25 \circ C$ ; PC / SC1 for L and M = 10 dB, all others 13 dB; residual picture carrier for L = 3 %, all others 10 %; FM/AM modulation = 54 %, 1 kHz modulation frequency; measured in application PCB (see Figure 12) with 16 MHz crystal frequency, loaded with 75  $\Omega$  (CVBS) and 1 k $\Omega$  (SSIF/audio). Values are meant for 'easy programming' settings (recommended) except internal mono audio and IF demodulation. The low IF spectrum is delivered by a professional downconverter.

| Symbol                      | Parameter                               | Conditions                                                                                                                       | Mi              | n Typ     | Max  | Unit |

|-----------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|------|------|

| Power supp                  | bly                                     |                                                                                                                                  |                 |           |      |      |

| V <sub>DD(1V2)</sub>        | supply voltage (1.2 V)                  | digital and analog                                                                                                               | 1.0             | 8 1.2     | 1.32 | V    |

| V <sub>DD(3V3)</sub>        | supply voltage (3.3 V)                  | digital and analog                                                                                                               | 2.9             | 3.3       | 3.63 | V    |

| I <sub>DD(tot)(1V2)</sub>   | total supply current (1.2 V)            |                                                                                                                                  | -               | 28        | 33   | mA   |

| I <sub>DD(tot)(3V3)</sub>   | total supply current (3.3 V)            |                                                                                                                                  | <u>[1]</u> _    | 125       | 136  | mA   |

| P <sub>tot</sub>            | total power dissipation                 | default settings; 75 $\Omega$ drive;<br>f <sub>s</sub> = 54 MHz at ADC; including DAC<br>loads; R <sub>RSET</sub> = 1 k $\Omega$ | <u>[1]</u> _    | 434       | 490  | mW   |

|                             |                                         | Power-save mode; $f_s = 54$ MHz at ADC; including DAC loads;<br>R <sub>RSET</sub> = 2 k $\Omega$ ; see Section 13.6              | [2] _           | 324       | 369  | mW   |

|                             |                                         | Standby mode                                                                                                                     | -               | 7         | 10   | mW   |

| IF input                    |                                         |                                                                                                                                  |                 |           |      |      |

| V <sub>i(p-p)</sub>         | peak-to-peak input voltage              | for full-scale ADC input (0 dBFS)                                                                                                | 1.8             | 2.0       | 2.2  | V    |

| Vi                          | input voltage                           | operational input related to ADC full scale; all standards; sum of all signals                                                   | -3              | -3        | -3   | dBF  |

| f <sub>i</sub>              | input frequency                         | PC / SC1                                                                                                                         |                 |           |      |      |

|                             |                                         | M/N standard                                                                                                                     | -               | 5.75 / 1. | 25 - | MH   |

|                             |                                         | B standard                                                                                                                       | -               | 6.75 / 1. | 25 - | MH   |

| v.DataS                     | h e e                                   | G/H standard                                                                                                                     | -               | 7.75 / 2. | 25 - | MH   |

|                             |                                         | I standard                                                                                                                       | -               | 7.75 / 1. | 75 - | MH   |

|                             |                                         | DK and L standard                                                                                                                | -               | 7.75 / 1. | 25 - | MH   |

|                             |                                         | L-accent standard                                                                                                                | -               | 1.25 / 7. | 75 - | MH   |

|                             |                                         | FM radio                                                                                                                         | -               | 1.25      | -    | MH:  |

| Carrier reco                | overy FPLL                              |                                                                                                                                  |                 |           |      |      |

| B <sub>-3dB(cl)</sub>       | closed-loop −3 dB<br>bandwidth          | wide                                                                                                                             | 60              | 60        | 60   | kHz  |

| $\Delta f_{\text{pullin}}$  | pull-in frequency range                 |                                                                                                                                  | [ <u>3]</u> ±8: | 30 ±830   | ±830 | kHz  |

| m <sub>over(PC)</sub>       | picture carrier<br>overmodulation index | black for L/L-accent standard; flat field white else                                                                             | 11              | 5 117     | -    | %    |

| IF demodul                  | ation (video equalizer in Fla           | at mode)                                                                                                                         |                 |           |      |      |

| $\alpha_{\text{sup(stpb)}}$ | stop-band suppression                   | video low-pass filter (M/N, B/G/H, I,<br>D/K, L/L-accent standard)                                                               |                 | -60       | -    | dB   |

| t <sub>ripple(GDE)</sub>    | group delay equalizer ripple time       | peak value for B/G/H half, D/K half,<br>I flat, M (FCC) full, L/L-accent full<br>standard                                        | -               | 20        | 40   | ns   |

# **NXP Semiconductors**

**TDA8295**

# Digital global standard low IF demodulator for analog TV and FM radio

# Table 1. Quick reference data ...continued

Power supplies 3.3 V, 1.2 V;  $T_{amb} = 25 \circ C$ ; PC / SC1 for L and M = 10 dB, all others 13 dB; residual picture carrier for L = 3 %, all others 10 %; FM/AM modulation = 54 %, 1 kHz modulation frequency; measured in application PCB (see Figure 12) with 16 MHz crystal frequency, loaded with 75  $\Omega$  (CVBS) and 1 k $\Omega$  (SSIF/audio). Values are meant for 'easy programming' settings (recommended) except internal mono audio and IF demodulation. The low IF spectrum is delivered by a professional downconverter.

| ency response<br>rential gain<br>rential phase<br>hted signal-to-noise                             | negative PC modulation (all standards except L/L-accent); 75 Ω DC load; sync-white modulation         90 % (nominal)         positive PC modulation (L/L-accent standard); 75 Ω DC load; sync-white modulation         97 % (nominal)         overall video response; CVBS equalizer flat         all standards except M/N         M/N standard         video equalizer; 8 equally spaced settings; value at 3.9 MHz         "ITU-T J.63 line 330"         "ITU-T J.63 line 330"         all standards; unified weighting filter | 0.8<br>0.8<br>4.8<br>3.9<br>-5<br>-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.0<br>1.0<br>4.85<br>4.05<br>-<br>1.5<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.2<br>1.2<br>-<br>-<br>+4.5<br>3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V<br>V<br>MHz<br>MHz<br>dB                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ge<br>B video bandwidth<br>lency response<br>rential gain<br>rential phase<br>hted signal-to-noise | except L/L-accent); 75 Ω DC load;<br>sync-white modulation<br>90 % (nominal)<br>positive PC modulation (L/L-accent<br>standard); 75 Ω DC load; sync-white<br>modulation<br>97 % (nominal)<br>overall video response; CVBS<br>equalizer flat<br>all standards except M/N<br>M/N standard<br>video equalizer; 8 equally spaced<br>settings; value at 3.9 MHz<br><i>"ITU-T J.63 line 330"</i><br><i>"ITU-T J.63 line 330"</i><br>all standards; unified weighting filter                                                            | 0.8<br>4.8<br>3.9<br>-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0<br>4.85<br>4.05<br>-<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2<br>-<br>-<br>+4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V<br>MHz<br>MHz<br>dB                                                                                                                                                                                                                                                                                                                                       |

| ency response<br>rential gain<br>rential phase<br>hted signal-to-noise                             | positive PC modulation (L/L-accent<br>standard); 75 Ω DC load; sync-white<br>modulation97 % (nominal)overall video response; CVBS<br>equalizer flatall standards except M/NM/N standardvideo equalizer; 8 equally spaced<br>settings; value at 3.9 MHz"ITU-T J.63 line 330""ITU-T J.63 line 330"all standards; unified weighting filter                                                                                                                                                                                          | 0.8<br>4.8<br>3.9<br>-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0<br>4.85<br>4.05<br>-<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.2<br>-<br>-<br>+4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V<br>MHz<br>MHz<br>dB                                                                                                                                                                                                                                                                                                                                       |

| ency response<br>rential gain<br>rential phase<br>hted signal-to-noise                             | standard); 75 Ω DC load; sync-white<br>modulation97 % (nominal)overall video response; CVBS<br>equalizer flatall standards except M/NM/N standardvideo equalizer; 8 equally spaced<br>settings; value at 3.9 MHz"ITU-T J.63 line 330""ITU-T J.63 line 330"all standards; unified weighting filter                                                                                                                                                                                                                                | 4.8<br>3.9<br>–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.85<br>4.05<br>-<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -<br>-<br>+4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MHz<br>MHz<br>dB                                                                                                                                                                                                                                                                                                                                            |

| ency response<br>rential gain<br>rential phase<br>hted signal-to-noise                             | overall video response; CVBS<br>equalizer flat<br>all standards except M/N<br>M/N standard<br>video equalizer; 8 equally spaced<br>settings; value at 3.9 MHz<br><i>"ITU-T J.63 line 330"</i><br><i>"ITU-T J.63 line 330"</i><br>all standards; unified weighting filter                                                                                                                                                                                                                                                         | 4.8<br>3.9<br>–5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.85<br>4.05<br>-<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -<br>-<br>+4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MHz<br>MHz<br>dB                                                                                                                                                                                                                                                                                                                                            |

| ency response<br>rential gain<br>rential phase<br>hted signal-to-noise                             | equalizer flat<br>all standards except M/N<br>M/N standard<br>video equalizer; 8 equally spaced<br>settings; value at 3.9 MHz<br><i>"ITU-T J.63 line 330"</i><br><i>"ITU-T J.63 line 330"</i><br>all standards; unified weighting filter                                                                                                                                                                                                                                                                                         | 3.9<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.05<br>-<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -<br>+4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MHz<br>dB                                                                                                                                                                                                                                                                                                                                                   |

| rential gain<br>rential phase<br>hted signal-to-noise                                              | M/N standard<br>video equalizer; 8 equally spaced<br>settings; value at 3.9 MHz<br><i>"ITU-T J.63 line 330"</i><br><i>"ITU-T J.63 line 330"</i><br>all standards; unified weighting filter                                                                                                                                                                                                                                                                                                                                       | 3.9<br>5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4.05<br>-<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -<br>+4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MHz<br>dB                                                                                                                                                                                                                                                                                                                                                   |

| rential gain<br>rential phase<br>hted signal-to-noise                                              | video equalizer; 8 equally spaced<br>settings; value at 3.9 MHz<br><i>"ITU-T J.63 line 330"</i><br><i>"ITU-T J.63 line 330"</i><br>all standards; unified weighting filter                                                                                                                                                                                                                                                                                                                                                       | -5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -<br>1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | dB                                                                                                                                                                                                                                                                                                                                                          |

| rential gain<br>rential phase<br>hted signal-to-noise                                              | settings; value at 3.9 MHz<br><i>"ITU-T J.63 line 330"</i><br><i>"ITU-T J.63 line 330"</i><br>all standards; unified weighting filter                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                             |

| rential phase<br>hted signal-to-noise                                                              | <i>"ITU-T J.63 line 330"</i> all standards; unified weighting filter                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | %                                                                                                                                                                                                                                                                                                                                                           |

| hted signal-to-noise                                                                               | all standards; unified weighting filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                             |

| -                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | deg                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                    | ( <i>"ITU-T J.61"</i> ); PC at –6 dBFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dB                                                                                                                                                                                                                                                                                                                                                          |