# Monolithic Video A/D Converter

8-bit, 20MSPS

The TDC1007 is an 8-bit fully parallel (flash) analog-to-digital converter, capable of digitizing an input signal at rates up to 20MSPS (MegaSamples Per Second). It will operate accurately without the use of an external sample-and-hold amplifier, with analog input signals having frequency components up to 7MHz.

A single CONVert (CONV) signal controls the conversion operation of the device which consists of 255 sampling comparators, encoding logic, and a latched output buffer register. The device will recover from a full-scale input step in 20ns. Control inputs are provided to format the output in binary, two's complement, or inverse data coding formats.

The TDC1007 is patented under U.S. Patent No. 3283170 with other patents pending.

#### **Features**

- 8-Bit Resolution

- Conversion Rates Up to 20MSPS

- Sample-And-Hold Amplifier Not Required

- Bipolar Monolithic Construction

- TTL Compatible Inputs and Outputs

- Binary or Two's Complement Mode

- Differential Phase = 1.0 Degrees

- Differential Gain = 1.7%

- Evaluation Boards Available: TDC1007E1C or TDC1007P1C

# **Applications**

- Video Systems 3x or 4x Subcarrier, NTSC or PAL

- Radar Systems

- High-Speed Multiplexed Data Acquisition

- Digital Signal Processing

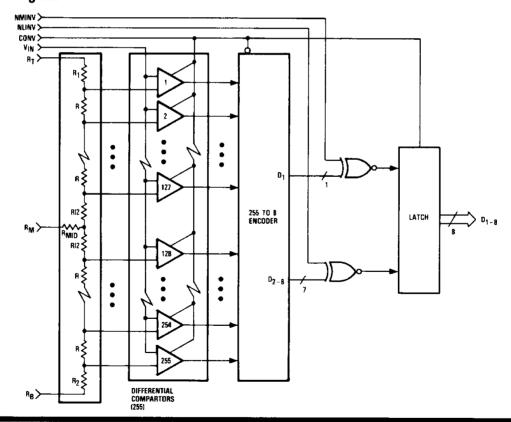

# **Functional Block Diagram**

LSI Products Division

TRW Electronic Components Group P.O. Box 2472 La Jolla, CA 92038 Phone: (619) 457 - 1000 Telex: 697 - 957 TWX: 910 - 335 - 1571 ©TRW Inc. 1985 40G00276 Rev. D~1/85 Printed in the U.S.A.

# **Functional Block Diagram**

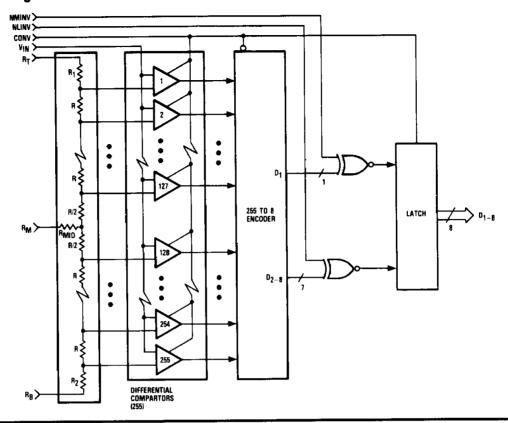

# **Pin Assignments**

64 Lead DIP - J1 Package

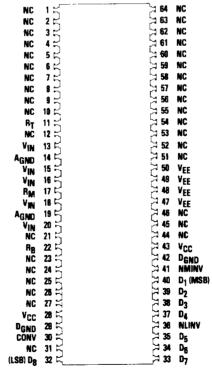

# Pin Assignments

68 Contact Or Leaded Chip Carrier - C1, L1 Package

# **Functional Description**

#### **General Information**

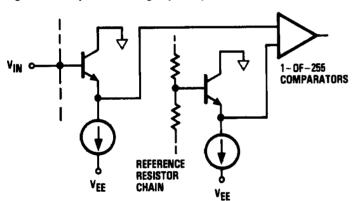

The TDC1007 has three major functional sections: a comparator array, encoding logic, and output data latches. The input voltage is compared with 255 separate reference voltage points tapped from the reference resistor chain. The 255 comparator outputs form a code (sometimes referred to as a "thermometer" code, as all the comparators referred to voltages more positive than the input signal will be off, and

those referred to voltages more negative than the input signal will be on). The "thermometer" code from the comparator array is encoded into an eight—bit binary word by the encoding logic section. Each of these eight results is sent through an exclusive—OR gate where they are inverted by use of the NMINV or NLINV inputs. This allows operation in binary, two's complement, or inverted data formats.

## **Power**

The TDC1007 operates from two supply voltages, +5.0V and -6.0V. The return for I<sub>CC</sub>, the current drawn from the +5.0V supply, is D<sub>GND</sub>. The return path for I<sub>EE</sub>, the current drawn

from the  $-6.0\mathrm{V}$  supply, is AGND. All power and ground pins must be connected.

| Name             | Function                | Value         | C1, L1 Package      | J1 Package          |  |  |

|------------------|-------------------------|---------------|---------------------|---------------------|--|--|

| V <sub>CC</sub>  | Positive Supply Voltage | +5.0V         | Pins 23, 41         | Pins 28, 43         |  |  |

| VEE              | Negative Supply Voltage | -6. <b>0V</b> | Pins 14, 18, 19, 21 | Pins 47, 48, 49, 50 |  |  |

| D <sub>GND</sub> | Digital Ground          | 0.0V          | Pins 25, 40         | Pins 29, 42         |  |  |

| AGND             | Analog Ground           | 0.0V          | Pins 48, 55         | Pins 14, 19         |  |  |

[D]

#### Reference

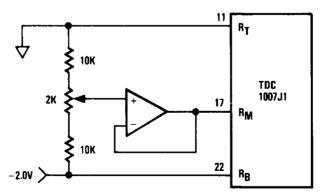

The TDC1007 converts analog signals in the range  $V_{RB} \leq V_{IN} \leq V_{RT}$  into digital form.  $V_{RT}$  (the voltage applied to the pin at the top of the reference resistor chain), and  $V_{RB}$  (the voltage applied to the pin at the bottom of the reference resistor chain) should be between +0.1V and -2.1V, with the difference between them less than 2.1V.  $V_{RT}$  should be more positive than  $V_{RB}$  within that range. In order to insure optimum operation of the TDC1007, these points should be driven by low-impedance sources capable of providing the

necessary reference resistor chain current. The voltages on R<sub>T</sub> and R<sub>B</sub> may be varied dynamically up to 7MHz. Due to variations in reference current with clock and input signals, R<sub>T</sub> and R<sub>B</sub> should be low-impedance-to-ground points. For circuits in which the reference is not varied, a bypass capacitor to ground is recommended. If the reference inputs are varied dynamically (as in an AGC application) a low-impedance reference source is required.

| Name Function  |                             | Value  | C1, L1 Package | J1 Package |  |

|----------------|-----------------------------|--------|----------------|------------|--|

| R <sub>T</sub> | Reference Resistor (Top)    | 0.0V   | Pin 60         | Pin 11     |  |

| RM             | Reference Resistor (Middle) | - 1.0V | Pin 51         | Pin 17     |  |

| R <sub>B</sub> | Reference Resistor (Bottom) | -2.0V  | Pin 44         | Pin 22     |  |

#### Control

Two control inputs are provided on the TDC1007 for changing the format of the output data. When NMINV is tied to a logic "0", the most significant bit of the output data is inverted; when NLINV is tied to a logic "0", the seven least significant bits of the output are inverted. By using these controls, the

output data format can be binary, inverted binary, two's complement, or inverted two's complement. Output data versus input voltage and control input state is illustrated in the Output Coding table.

| Name  | Function                         | Value | C1, L1 Package | J1 Package |

|-------|----------------------------------|-------|----------------|------------|

| NMINV | Not Most Significant Bit INVert  | TTL   | Pin 29         | Pin 41     |

| NLINV | Not Least Significant Bit INVert | ΠL    | Pin 34         | Pin 36     |

#### Convert

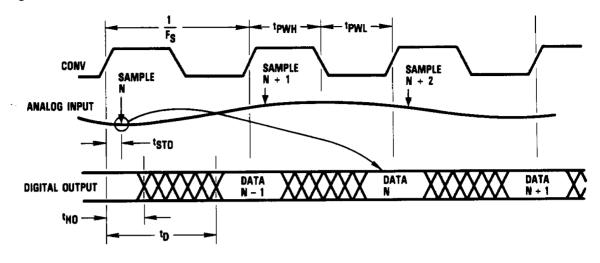

The analog input to the TDC1007 is sampled (comparators are latched) approximately 10ns after the rising edge of the CONV Signal. This time delay is the sampling time offset ( $t_{STO}$ ) and varies only by a few nanoseconds from device to device and as a function of temperature. The short-term uncertainty (jitter) in sampling time offset is approximately 30 picoseconds.

The output data is encoded from the 255 comparators on the falling edge of the CONV signal. The coded result is transferred to the output latches on the next rising edge of the CONV signal. Note that there are minimum pulse width (tpwH, tpwL) requirements on the waveshape of the CONV signal.

| Name | Function | Value | C1, L1 Package | J1 Package |  |

|------|----------|-------|----------------|------------|--|

| CONV | Convert  | TTL   | Pin 39         | Pin 30     |  |

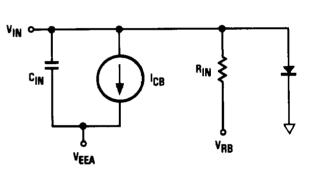

The input impedance of the TDC1007 varies with input signal level. As the signal varies, the comparator input transistors change from active to cut—off, causing the net input resistance and capacitance to change. To prevent this action from degrading the integrity or accuracy of the output data, it is desirable to drive the TDC1007 inputs from a low—impedance source (less than 25 Ohms). The input signal level should remain within the range of VEE to +0.5V in order to prevent damage to the device. When the input is at a level between VRT and VRB reference voltages, the output data value will be

signal. When the analog input is beyond the range of the reference voltage, the output data will be the appropriate full—scale value. Note that there are two components to the input bias current flowing into the V<sub>IN</sub> pins. One component is constant for constant input voltage and is the sum of the bias currents of the subset of comparators that are active (ICB). The other component is related to the action of the CONV signal on the comparator chain (ISB). All analog input pins of the TDC1007 must be used in order to insure operation over the full input range.

| Name | Function            | Value     | C1, L1 Package          | J1 Package              |

|------|---------------------|-----------|-------------------------|-------------------------|

| VIN  | Analog Input Signal | 0V to −2V | Pins 46, 50, 52, 54, 58 | Pins 13, 15, 16, 18, 20 |

## Outputs

The outputs of the TDC1007 are TTL compatible and capable of driving four low-power Schottky unit loads (54/74 LS). The outputs hold the previous data a minimum time ( $t_{HO}$ ) after the

directly proportional to the amplitude of the analog input

rising edge of the CONV signal, and the new data becomes valid after a maximum time of tp. For optimum performance, 2.2 kOhm pull—up resistors are recommended.

|                | 110        |       |                |            |

|----------------|------------|-------|----------------|------------|

| Name           | Function   | Value | C1, L1 Package | J1 Package |

| D <sub>1</sub> | MSB Output | ΠL    | Pin 30         | Pin 40     |

| D <sub>2</sub> |            | ΠTL   | Pin 31         | Pin 39     |

| 03             |            | ΠL    | Pin 32         | Pin 38     |

| D <sub>4</sub> |            | πι    | Pin 33         | Pin 37     |

| D <sub>5</sub> |            | TTL   | Pin 35         | Pin 35     |

| 06             |            | ΠL    | Pin 36         | Pin 34     |

| D <sub>7</sub> |            | πL    | Pin 37         | Pin 33     |

| D <sub>8</sub> | LSB Output | TTL   | Pin 38         | Pin 32     |

|                |            |       |                |            |

#### **No Connects**

There are several pins labeled No Connect (NC), which have no connections to the chip. These pins may be left open.

| Name | Function   | Value | C1, L1 Package                 | J1 Package            |

|------|------------|-------|--------------------------------|-----------------------|

| NC   | No Connect | Open  | Pins 1-13, 15-17, 20, 22, 24,  | Pins 1-10, 12, 24-27, |

|      |            |       | 26-28, 42, 43, 45, 47, 49, 53, | 31, 44-46, 51-64      |

|      |            |       | 56, 57, 59, 61, 62-68          |                       |

Figure 1. Timing Diagram

Figure 2. Simplified Analog Input Equivalent Circuit

$c_{\text{IN}}$  is a nonlinear junction capacitance  $v_{RB}$  is a voltage equal to the voltage on Pin  $\mathbf{R}_B$

Figure 4. Output Circuits Figure 3. Digital Input Equivalent Circuit +Vcc ACC VCC . 810  $\Omega$ 10K **380** Ω 5K TO OUTPUT PIN INPUT O 1N3062 OUTPUT 40pF LOAD 1 = TEST LOAD FOR DELAY MEASUREMENTS OUTPUT EQUIVALENT CIRCUIT

**LSI Products Division**

TRW Electronic Components Group

Absolute maximum ratings (beyond which the device will be damaged) 1

| Supply Voltag | 185                                                                                                                                                                                                                                                 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | V <sub>CC</sub> (measured to D <sub>GND</sub> )                                                                                                                                                                                                     |

|               | V <sub>EE</sub> (measured to A <sub>GND</sub> )+0.5 to -7.0V                                                                                                                                                                                        |

|               | AGND (measured to DGND)                                                                                                                                                                                                                             |

| Input Voltage |                                                                                                                                                                                                                                                     |

|               | CONV, NMINV, NLINV (measured to DGND)                                                                                                                                                                                                               |

|               | V <sub>IN</sub> , V <sub>RT</sub> , V <sub>RB</sub> (measured to A <sub>GND</sub> )                                                                                                                                                                 |

|               | CONV, NMINV, NLINV (measured to DGND)       -0.5 to +5.5V         V <sub>IN</sub> , V <sub>RT</sub> , V <sub>R8</sub> (measured to AGND)       +0.5 to V <sub>EE</sub> V         V <sub>RT</sub> (measured to V <sub>RB</sub> )       +2.2 to -2.2V |

| Output        |                                                                                                                                                                                                                                                     |

|               | Applied voltage (measured to D <sub>GND</sub> )                                                                                                                                                                                                     |

|               | Applied voltage (measured to D <sub>GND</sub> )                                                                                                                                                                                                     |

|               | Short circuit duration (single output in high state to ground)                                                                                                                                                                                      |

| Temperature   |                                                                                                                                                                                                                                                     |

|               | Operating, ambient                                                                                                                                                                                                                                  |

|               | junction                                                                                                                                                                                                                                            |

|               | Lead, soldering (10 seconds)                                                                                                                                                                                                                        |

|               | Storage                                                                                                                                                                                                                                             |

Notes:

- Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions.

Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as positive when flowing into the device.

# **Operating conditions**

|                                  |                                                                                                                                                                              |                 |      | Tempera         | ture Range      | •     |                 |       |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|-----------------|-------|-----------------|-------|

|                                  |                                                                                                                                                                              | Standard        |      |                 | Extended        |       |                 | 1     |

| Paramete                         | EE Negative Supply Voltage (Measured to AGND)  AGND Analog Ground Voltage (Measured to DGND)  PWL CONV Pulse Width, LOW  CONV Pulse Width, HIGH  IL Input Voltage, Logic LOW |                 | Nom  | Max             | Min             | Nom   | Max             | Units |

| VCC                              | Positive Supply Voltage (Measured to DGND)                                                                                                                                   | 4.75            | 5.0  | 5.25            | 4.5             | 5.0   | 5.5             | ٧     |

| VEE                              | Negative Supply Voltage (Measured to AGND)                                                                                                                                   | -5.75           | -6.0 | -6.25           | -5.75           | -6.0  | -6.25           | ٧     |

| VAGND                            | Analog Ground Voltage (Measured to DGND)                                                                                                                                     | -0.1            | 0.0  | 0.1             | -0.1            | 0.0   | 0.1             | ٧     |

| <sup>t</sup> PWL                 | CONV Pulse Width, LOW                                                                                                                                                        | 25              |      |                 | 25              |       |                 | ns    |

| <sup>t</sup> PWH                 | CONV Pulse Width, HIGH                                                                                                                                                       | 15              |      |                 | 15              | -     | -               | ns    |

| VIL                              | Input Voltage, Logic LOW                                                                                                                                                     |                 |      | 0.8             |                 |       | 0.8             | ٧     |

| VIH                              | Input Voltage, Logic HIGH                                                                                                                                                    | 2.0             |      |                 | 2.0             |       | -               | ٧     |

| OL                               | Output Current, Lagic LOW                                                                                                                                                    |                 |      | 4.0             |                 |       | 4.0             | mΑ    |

| ОН                               | Output Current, Logic HIGH                                                                                                                                                   |                 |      | -400            |                 | •     | -400            | μΑ    |

| V <sub>RT</sub>                  | Most Positive Reference Input <sup>1</sup>                                                                                                                                   | -1.1            | 0.0  | 0.1             | -1.1            | 0.0   | 0.1             | ν     |

| V <sub>RB</sub>                  | Most Negative Reference Input                                                                                                                                                | -0.9            | -2.0 | -2.1            | -0.9            | - 2.0 | -2.1            | V     |

| V <sub>RT</sub> -V <sub>RB</sub> | Voltage Reference Differential                                                                                                                                               | 1.0             | 2.0  | 2.2             | 1.0             | 2.0   | 2.2             | T v   |

| V <sub>IN</sub>                  | Input Voltage                                                                                                                                                                | V <sub>RT</sub> |      | V <sub>RB</sub> | V <sub>RT</sub> |       | V <sub>RB</sub> | ٧     |

| TA                               | Ambient Temperature, Still Air                                                                                                                                               | 0               |      | 70              |                 |       |                 | °C    |

| T <sub>C</sub>                   | Case Temperature                                                                                                                                                             |                 |      |                 | -55             |       | 125             | °C    |

Note:

LSI Products Division

TRW Electronic Components Group

<sup>1.</sup>  $V_{\mbox{RT}}$  must be more positive than  $V_{\mbox{RB}}$ , and voltage reference differential must be within specified range.

# Electrical characteristics within specified operating conditions

|                 |                                  |                                                                             |          | Temperati | ire Range |      |       |

|-----------------|----------------------------------|-----------------------------------------------------------------------------|----------|-----------|-----------|------|-------|

|                 |                                  |                                                                             | Stan     | dard      | Exte      | nded |       |

| Parameter       |                                  | Test Conditions                                                             | Min      | Max       | Min       | Max  | Units |

| lcc             | Positive Supply Current          | V <sub>CC</sub> - MAX, Static <sup>1</sup>                                  |          | 30        |           | 35   | mA    |

| I <sub>EE</sub> | Negative Supply Current          | V <sub>EE</sub> - MAX, Static <sup>1</sup>                                  |          |           |           |      |       |

|                 |                                  | T <sub>A</sub> - 0°C to 70°C                                                |          | -400      |           |      | mA    |

|                 | Į                                | T <sub>A</sub> = 70°C                                                       |          | -350      |           |      | mA    |

|                 | i                                | T <sub>C</sub> = -55°C to 125°C                                             |          |           |           | -470 | mA    |

|                 |                                  | T <sub>C</sub> - 125°C                                                      | <u> </u> |           |           | -320 | mA    |

| REF             | Reference Current                | V <sub>RT</sub> , V <sub>RB</sub> - NOM                                     |          | 35        |           | 40   | mA    |

| RREF            | Total Reference Resistance       |                                                                             | 57       |           | 50        |      | Ohms  |

| R <sub>IN</sub> | Input Equivalent Resistance      | V <sub>RT</sub> , V <sub>RB</sub> - NOM, V <sub>IN</sub> - V <sub>RB</sub>  | 5        |           | 5         |      | kOhms |

| CIN             | Input Capacitance                |                                                                             |          | 250       |           | 250  | pF    |

| I <sub>CB</sub> | Input Constant Bias Current      | V <sub>EE</sub> - MAX                                                       |          | 400       |           | 500  | μА    |

| Ī <sub>SB</sub> | Input Clock Synchronous Bias     |                                                                             |          | 200       |           | 200  | μА    |

| ī <sub>lL</sub> | Input Current, Logic LOW         | V <sub>CC</sub> - MAX, V <sub>1</sub> - 0.5V                                |          | -2.0      |           | -2.0 | mA    |

| I <sub>IH</sub> | Input Current, Logic HIGH        | V <sub>CC</sub> - MAX, V <sub>I</sub> - 2.4V                                |          | 75        |           | 75   | μΑ    |

| <del>///</del>  | Input Current, Max Input Voltage | V <sub>CC</sub> - MAX, V <sub>I</sub> - 5.5V                                |          | 1.0       |           | 1.0  | mA    |

| VOL             | Output Voltage, Logic LOW        | V <sub>CC</sub> - MIN, I <sub>DL</sub> - MAX                                |          | 0.5       |           | 0.5  | ٧     |

| VOH             | Output Voltage, Logic HIGH       | ·                                                                           | 2.4      |           | 2.4       |      | ٧     |

| los             | Short Circuit Output Current     | V <sub>CC</sub> = MAX, Output HIGH, one pin to ground, one second duration. |          | -25       |           | - 25 | mA    |

| c <sub>l</sub>  | Digital Input Capacitance        | T <sub>A</sub> = 25°C, F = 1MHz                                             |          | 15        |           | 15   | pF    |

Note:

# Switching characteristics within specified operating conditions

|                |                         |                                                      |      | Temperature Range |      |       |       |  |

|----------------|-------------------------|------------------------------------------------------|------|-------------------|------|-------|-------|--|

|                |                         |                                                      | Star | ndard             | Exte | ended |       |  |

| Paran          | neter                   | Test Conditions                                      | Min  | Max               | Min  | Max   | Units |  |

| FS             | Maximum Conversion Rate | V <sub>CC</sub> - MIN; V <sub>EE</sub> - MIN         | 20   |                   | 20   |       | MSPS  |  |

| tst0           | Sampling Time Offset    | V <sub>CC</sub> - MIN, V <sub>EE</sub> - MIN         | 0    | 10                | 0    | 10    | ПS    |  |

| t <sub>D</sub> | Output Delay Time       | V <sub>CC</sub> - MIN, V <sub>EE</sub> - MIN, Load 1 |      | 40                |      | 45    | ns    |  |

| <u></u> -      | Output Hold Time        | V <sub>CC</sub> - MIN, V <sub>EE</sub> - MIN, Load 1 | 10   |                   | 10   |       | ns    |  |

<sup>1.</sup> Worst case, all digital inputs and outputs LOW.

# System performance characteristics within specified operating conditions

|                 |                                       |                                         |      | Temperature Range                                |      |         |           |  |

|-----------------|---------------------------------------|-----------------------------------------|------|--------------------------------------------------|------|---------|-----------|--|

|                 |                                       |                                         | Sta  | ndard                                            |      | ended   | 1         |  |

| Para            | meter                                 | Test Conditions                         | Min  | Max                                              | Min  | Max     | Units     |  |

| ELI             | Linearity Error Integral, Independent | V <sub>RT</sub> , V <sub>RB</sub> - NOM |      | 0.3                                              |      | 0.3     | %         |  |

| EFD             | Linearity Error Differential          | V <sub>RT</sub> , V <sub>RB</sub>       |      | 0.3                                              | İ    | 0.3     | %         |  |

| a               | Code Size                             | V <sub>RT</sub> , V <sub>RB</sub> - NOM | 15   | 185                                              | 15   | 185     | % Nominal |  |

| EOT             | Offset Error Top                      | V <sub>IN</sub> - V <sub>RT</sub>       |      | 35                                               |      | 45      | mV        |  |

| E <sub>OB</sub> | Offset Error Bottom                   | V <sub>IN</sub> - V <sub>RB</sub>       |      | -22                                              |      | -24     | mV        |  |

| T <sub>CO</sub> | Offset Error Temperature Coefficient  |                                         |      | ±50                                              | 1    | ±50     | μV/°C     |  |

| BW              | Bandwidth, Full Power Input           |                                         | 7    | <del>                                     </del> | 5    |         | MHz       |  |

| tTR             | Transient Response, Full Scale        |                                         |      | 20                                               |      | 20      | ns        |  |

| SNR             | Signal-to-Noise Ratio                 | 10MHz Bandwidth                         |      | <del>                                     </del> |      | <u></u> |           |  |

|                 |                                       | 20MSPS Conversion Rate                  |      |                                                  |      |         |           |  |

|                 | Peak Signal/RMS Noise                 | 1.248MHz Input                          | 53   |                                                  | 52   |         | dB        |  |

|                 |                                       | 2.438MHz Input                          | 50   |                                                  | 49   |         | ₫₿        |  |

|                 | RMS Signal/RMS Noise                  | 1.248MHz Input                          | 44   |                                                  | 43   |         | dB        |  |

|                 |                                       | 2.438MHz Input                          | 41   |                                                  | 40   |         | dB        |  |

| NPR             | Noise Power Ratio                     | DC to 8MHz White Noise Bandwidth        | 36.5 | <u> </u>                                         | 36.5 |         | dB        |  |

|                 |                                       | 4 Sigma Loading                         | 1    |                                                  |      |         |           |  |

|                 |                                       | 1.248MHz Slot                           | ŀ    |                                                  |      |         |           |  |

|                 |                                       | 20MSPS Conversion Rate                  |      |                                                  |      |         |           |  |

| E <sub>AP</sub> | Aperture Error                        |                                         |      | 60                                               |      | 60      | ps        |  |

| DP              | Differential Phase                    | NTSC @ 4x Color Subcarrier              |      | 1.0                                              | -    | 1.0     | Degree    |  |

| DG              | Differential Gain                     | NTSC @ 4x Color Subcarrier              |      | 1.7                                              |      | 1.7     | %         |  |

Output Coding (Input range from 0.000 to -2.000V)

|                 | Binary    | Offset Two's Complement |          |          |

|-----------------|-----------|-------------------------|----------|----------|

| Input Voltage   | True      | Inverted                | True     | Inverted |

| (-7.84 mV/Step) | NMINV - 1 | 0                       | 0        | 1        |

|                 | NLINV - 1 | 0                       | 1        | 0        |

| 0.000           | 00000000  | 11111111                | 10000000 | 01111111 |

| •               | •         | •                       | •        | •        |

| •               | •         | •                       | •        | •        |

| -0.0078         | 00000001  | 11111110                | 10000001 | 01111110 |

| •               | •         | •                       | •        | •        |

| •               | •         | •                       | •        | •        |

| •               | •         | •                       | •        | •        |

| •               | •         | •                       | •        | •        |

| -0.9960         | 01111111  | 10000000                | 11111111 | 00000000 |

| - 1.0039        | 10000000  | 01111111                | 00000000 | 11111111 |

| •               | •         | •                       | •        | •        |

| •               | •         | •                       | •        | •        |

| •               | •         | •                       | •        | •        |

| •               | •         | •                       | •        | •        |

| -1.9921         | 11111110  | 00000001                | 01111110 | 10000001 |

| •               |           | •                       | •        | •        |

| •               |           | •                       | •        | •        |

| -2.000          | 11111111  | 0000000                 | 01111111 | 10000000 |

#### Calibration

To calibrate the TDC1007, the top of the reference resistor chain,  $R_T$ , is connected to analog ground. The reference voltage is then set up by adjusting the bottom of the resistor chain to -2.0V. When this technique is used, offset errors are generated by the inherent parasitic resistance between the package pin and the actual resistor chain on the A/D. These parasitic resistors are shown as  $R_1$  and  $R_2$  in the Functional Block Diagram. The offset voltage error is the result of the resistor chain current flowing through the parasitic resistance. These errors can be compensated for by applying an equal offset to the analog input signal or by adjusting the voltages on  $R_T$  and  $R_B$ .

The effect of the offset error at the bottom of the resistor chain manifests itself in the form of a slight gain error which can be compensated for by varying the voltage applied to  $R_B$ . This voltage will necessarily be more negative than the desired reference level of -2.0V. The actual operating range of the A/D converter will be:

(VAGND - (IBEE x R1)) to (VRB + (IREE x R2).

However, if both ends of the resistor chain are driven by transistor—buffered operational amplifiers, the voltages on  $R_T$  and  $R_B$  could then be adjusted to remove the effect of the parasitic resistances and therefore eliminate the need to apply a compensating offset voltage to the analog input signal. Here the operating range of the A/D will be:

Since both  $V_{RT}$  and  $V_{RB}$  are adjustable, the offset voltage error effect can be cancelled and the A/D operated with gain and offset errors removed.

The TDC1007 provides access to the mid-point of the reference resistor chain,  $R_M$ . This point can be sensed by external circuitry for temperature compensation or gain tracking functions in the system. It can also be driven in the manner shown in Figure 6 for fine linearity correction.

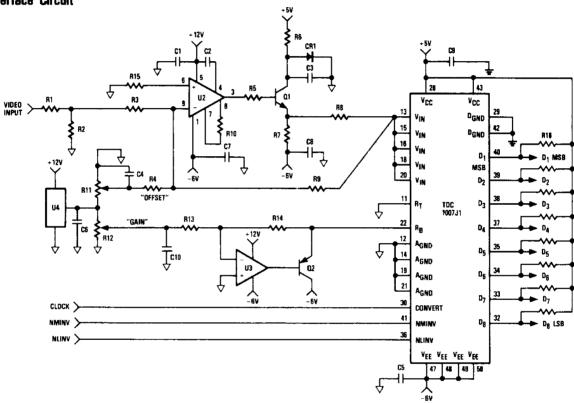

#### **Typical Application**

Figure 5 shows a typical interface circuit for a TDC1007, an input buffer amplifier, and the reference voltage source. The reference voltage is supplied by an inverting amplifier that has been buffered with a PNP transistor. The transistor sinks the current flowing through the reference resistor chain and keeps the driving impedance at the bottom end of the resistor chain low. The gain of the overall circuit is adjusted by varying the input voltage to the operational amplifier.

The input amplifier is a bipolar wideband operational amplifier followed by an NPN transistor buffer. The transistor drives the input capacitance of the A/D converter and keeps the overall circuit frequency stable. The offset error is compensated by varying the current into the summing junction of the op-amp. Note that all five  $V_{IN}$  points are connected together and the buffer amplifier feedback loop is closed at that point. The buffer amplifier has a gain of two, raising the  $1V_{IN}$  points are converted together. The A/D converter operates with a  $2V_{IN}$  full-scale.

Figure 6. Method For Driving Mid-Point Of Resistor Chain

LSI Products Division

TRW Electronic Components Group

www.DataSheet4U.com

## Parts List

| Resistors |      | Capacitors |         | Integrated Circuits |                    |     |             |                |

|-----------|------|------------|---------|---------------------|--------------------|-----|-------------|----------------|

| R1        | t    | 1/4W       |         | C1                  | 0.1 <sub>4</sub> F | 50V | UI          | TDC1007J1      |

| R2        | t    | 1/4W       |         | C2                  | • "                | 50V | U2          | Plessey SL541C |

| R3        | 1K   | 1/4W       | 5%      | C3                  | 0.1µF              | 50V | U3          | μ <b>Α</b> 741 |

| R4        | 4.3K | 1/4W       | 5%      | C4                  | 0.1µF              | 50V | U4          | MC1403         |

| R5        | 10   | 1/4W       | 5%      | C5                  | 0.1µF              | 50V |             |                |

| R6        | 56   | 1/2W       | 5%      | C6                  | 1.0 <i>u</i> F     | 15V |             |                |

| R7        | 240  | 2W         | 5%      | C7                  | 0.1uF              | 50V |             |                |

| R8        | 6.8  | 1/2W       | 5%      | C8                  | 0.1µF              | 50V | Diode       | S              |

| R9        | 2K   | 1/2W       | 5%      | C9                  | 0.1µF              | 50V | CD1         | 1314001        |

| R10       | •    | 1/4W       | 5%      | C10                 | 0.1µF              | 50V | CR1         | 1N4001         |

| R11       | 2K   | 1/4W       | 10-turn |                     |                    |     |             |                |

| R12       | 2K   | 1/4W       | 10-turn |                     |                    |     |             |                |

| R13       | 1.3K | 1/4W       | 5%      |                     |                    |     | Transistors |                |

| R14       | 2.2K | 1/4W       | 5%      |                     |                    |     |             |                |

| R15       | 680  | 1/4W       | 5%      |                     |                    |     | <b>Q</b> 1  | 2N5836         |

| R16       | 2.2K | SIP        | 5%      |                     |                    |     | 02          | 2N2907         |

<sup>†</sup> Indicates input terminator/divider

# **Ordering Information**

| Product<br>Number | Temperature Range                   | Screening                     | Package                 | Package<br>Marking |

|-------------------|-------------------------------------|-------------------------------|-------------------------|--------------------|

| TDC1007C1F        | EXT-T <sub>C</sub> = -55°C to 125°C | Commercial                    | 68 Contact Chip Carrier | 1007C1F3           |

| TDC1007C1A        | EXT-T <sub>C</sub> = -55°C to 125°C | High Reliability <sup>1</sup> | 68 Contact Chip Carrier | 1007C1A3           |

| TDC1007J1C        | STD-T <sub>A</sub> = 0°C to 70°C    | Commercial                    | 64 Lead DIP             | 1007J1C3           |

| TDC1007J1G        | STD-TA - 0°C to 70°C                | Commercial With Burn-In       | 64 Lead DIP             | 1007J1G3           |

| TDC1007L1F        | EXT-T <sub>C</sub> = -55°C to 125°C | Commercial                    | 68 Leaded Chip Carrier  | 1007L1F3           |

| TDC1007L1A        | EXT-T <sub>C</sub> = -55°C to 125°C | High Reliability 1            | 68 Leaded Chip Carrier  | 1007L1A3           |

TRW reserves the right to change products and specifications without notice. This information does not convey any license under patent rights of TRW Inc. or others.

Note:

<sup>\*</sup> Indicates amplifier compensation

<sup>1.</sup> Per TRW document 70Z01757.