# **TDC1049**

# High-Speed A/D Converter 9-Bit, 30 Msps

### **Features**

- 30 Msps conversion rate, 15 MHz analog bandwidth

- 9-Bit resolution and linearity

- · Sample-and-hold circuit not required

- Differential phase 0.5 degrees

- www.DataSheet4U.com Differential gain 1.0%

- · Overflow flag

- Single -5.2V power supply

- · Differential ECL outputs

- Available in a 64-pin DIP, 68-contact LCC and 68-pin ceramic pin grid array

# **Applications**

- · Video data conversion

- · Radar data conversion

- · High-speed data acquisition

# **Description**

The TDC1049 is a flash (full-parallel) analog-to-digital converter capable of converting analog signals with full-power frequency components up to 15 MHz into 9-bit words at rates up to 30 Msps (Megasamples Per Second). A sample-and-hold circuit is not required. All digital inputs and outputs are differential ECL.

The TDC1049 consists of 512 latching comparators, encoding logic and an output register. A differential convert signal controls the conversion operation. The outputs can be connected to give either true or inverted binary or offset two's complement formats.

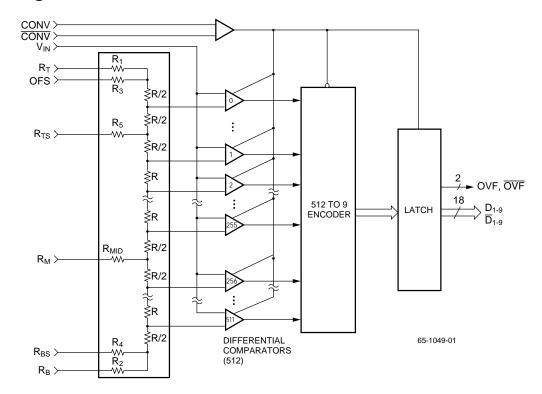

# **Block Diagram**

# **Functional Description**

### **General Information**

The TDC1049 has three functional sections: a comparator array, encoding logic and output register. The comparator array compares the input signal with 512 reference voltages to produce an N-of-512 code or "thermometer" code. The comparators referenced to voltages less than the input signal will be on and those referenced to voltages greater than the input signal will be off. The encoding logic converts the N-of-512 code into 9-bit binary data. The output register holds the output between updates.

### **Power**

For optimum performance, separate analog and digital power, VEEA and VEED should be supplied to the TDC1049. Separate analog and digital power supplies or a common supply with separate analog and digital paths and highfrequency decoupling can be used. The return path for the current drawn from VEEA and VEED is AGND and DGND, respectively. The returns AGND and DGND should also be kept separate and connected together at the power supply terminals. It is recommended that provisions be made on the printed circuit board for shorting jumpers between analog and digital ground as close to the A/D converter as possible. The installation of the jumpers depends upon the printed circuit board layout and overall system performance once the system is in operation. The voltage difference between VEEA and VEED must be less than +0.1V. The same voltage difference limit applies to the difference between AGND and DGND. All power and ground inputs to the converter must be connected.

### Reference

The TDC1049 converts analog signals in the range VRB < VIN < VRT into digital form. VRB (the voltage applied to RB) at the bottom of the reference resistor chain, and VRT (the voltage applied to RT) at the top of the reference resistor chain, should both be between +0.1V and -2.1V. Within that range, VRT must be more positive than VRB. The linearity specification is based upon a 2.0V difference between VRT and VRB. The nominal voltages are VRT = 0.0V and VRB = -20V. To avoid damage to the converter, the voltage across VRT and VRB must not exceed 2.2V. A decoupling capacitor is recommended between RB and AGND. Noise introduced at this point, as well as the other reference inputs (RT, RTS, RM, RBS, OFS), may result in encoding errors.

A midpoint tap, RM, allows the converter to be adjusted for optimum integral linearity. It can also be used to achieve a nonlinear transfer function, but adjustment of RM is not required to meet 9-bit linearity. If this node is driven by external circuitry, it should be driven from a low-impedance source; if not used, it must be left open.

Parasitic resistances, R1 and R2, introduce offset errors at the top and bottom of the reference resistor chain. Sense points, RTS, RBS and OFS, may be used to reduce the effect of these offset errors. Overflow Sense (OFS) may be used to reduce the effect of the offset at the overflow (most positive) comparator whenever the Overflow (OVF,  $\overline{OVF}$ ) flags are used. Sense points are not required for 9-bit linearity and, if not used, they must be left open.

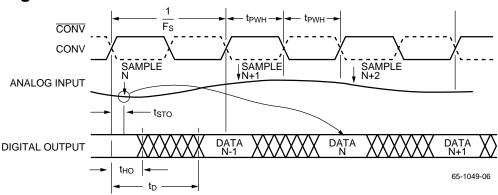

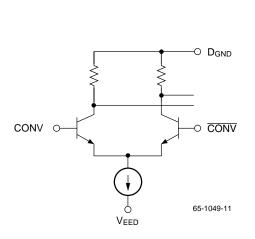

### Convert

The TDC1049 requires a differential ECL clock (CONV and  $\overline{\text{CONV}}$ ) signal. The conversion occurs (the comparators are latched) within tSTO (Sampling Time Offset) of the rising edge of CONV. The 512 to 9 encoding is performed on the falling edge of the CONV signal. The coded result is transferred to the output register on the next rising edge of CONV. Data for sample N is available at the output tD (Output Delay Time) after the rising edge of sample N+1.

### **Analog Input**

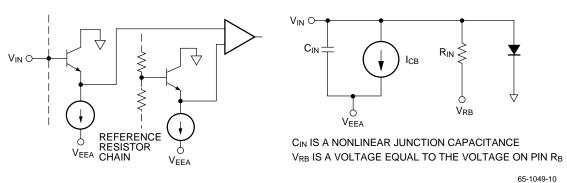

The TDC1049 uses latching comparators which are connected to the analog inputs  $V_{\rm IN}$ . For optimal performance, the source impedance of the driver amplifier should be less than  $25\Omega$ . The input signal will not damage the TDC1049 if it remains within the range of  $V_{\rm EEA}$  to +0.5V. If the input signal is between the  $V_{\rm RT}$  and  $V_{\rm RB}$ , the output will be a binary number between 0 and 511 inclusive. All five analog inputs must be connected.

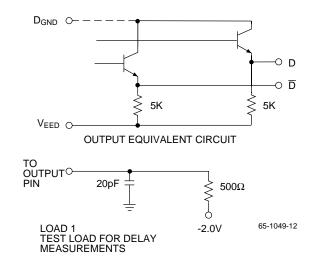

### **Outputs**

The outputs of the TDC1049 are differential ECL. The recommended pull-down resistance is  $500\Omega$  to -2V, or a  $220/330\Omega$  termination between DGND and VEED. The OVF signal indicates that the analog input has exceeded the threshold of the most positive comparator. Data is held valid at the output register for at least tHO (Output Hold Time) after the rising edge of CONV. New data becomes valid tD after the rising edge of CONV.

### No Connects

There are several pins labeled NC (No Connect). These pins are not connected internally and may be either left open or connected to analog ground to aid heat transfer from the package and to reduce electrical noise.

# **Pin Assignments**

### 64 Lead Sidebrazed Ceramic DIP

| Pin | Name               | Pin | Name             | Pin | Name                   | Pin | Name                 |

|-----|--------------------|-----|------------------|-----|------------------------|-----|----------------------|

| 1   | D <sub>8</sub>     | 17  | V <sub>EEA</sub> | 33  | D <sub>2</sub>         | 49  | V <sub>IN</sub>      |

| 2   | D <sub>7</sub>     | 18  | NC               | 34  | $\overline{D}_1$ (MSB) | 50  | V <sub>IN</sub>      |

| 3   | $\overline{D}_7$   | 19  | V <sub>EEA</sub> | 35  | D <sub>1</sub> (MSB)   | 51  | A <sub>GND</sub>     |

| 4   | D <sub>6</sub>     | 20  | NC               | 36  | OVF                    | 52  | A <sub>GND</sub>     |

| 5   | $\overline{D}_{6}$ | 21  | NC               | 37  | OVF                    | 53  | V <sub>IN</sub>      |

| 6   | D <sub>5</sub>     | 22  | V <sub>EED</sub> | 38  | D <sub>GND</sub>       | 54  | NC                   |

| 7   | $\overline{D}_{5}$ | 23  | NC               | 39  | D <sub>GND</sub>       | 55  | R <sub>T</sub>       |

| 8   | A <sub>GND</sub>   | 24  | NC               | 40  | R <sub>BS</sub>        | 56  | OFS                  |

| 9   | NC                 | 25  | A <sub>GND</sub> | 41  | R <sub>B</sub>         | 57  | R <sub>TS</sub>      |

| 10  | NC                 | 26  | NC               | 42  | NC                     | 58  | D <sub>GND</sub>     |

| 11  | V <sub>EED</sub>   | 27  | NC               | 43  | V <sub>IN</sub>        | 59  | CONV                 |

| 12  | NC                 | 28  | $\overline{D}_4$ | 44  | NC                     | 60  | CONV                 |

| 13  | NC                 | 29  | D <sub>4</sub>   | 45  | A <sub>GND</sub>       | 61  | D <sub>GND</sub>     |

| 14  | V <sub>EEA</sub>   | 30  | $\overline{D}_3$ | 46  | A <sub>GND</sub>       | 62  | D <sub>9</sub> (LSB) |

| 15  | NC                 | 31  | D <sub>3</sub>   | 47  | V <sub>IN</sub>        | 63  | D <sub>9</sub> (LSB) |

| 16  | NC                 | 32  | $\overline{D}_2$ | 48  | R <sub>M</sub>         | 64  | $\overline{D}_{8}$   |

65-1049-02

### 64 Lead Bottombraze Ceramic DIP

| Pin | Name                 | Pin | Name                   | Pin | Name             | Pin | Name               |

|-----|----------------------|-----|------------------------|-----|------------------|-----|--------------------|

| 1   | $\overline{D}_{8}$   | 17  | R <sub>M</sub>         | 33  | $\overline{D}_2$ | 49  | NC                 |

| 2   | D <sub>9</sub> (LSB) | 18  | V <sub>IN</sub>        | 34  | D <sub>3</sub>   | 50  | NC                 |

| 3   | D <sub>9</sub> (LSB) | 19  | A <sub>GND</sub>       | 35  | $\overline{D}_3$ | 51  | V <sub>EEA</sub>   |

| 4   | D <sub>GND</sub>     | 20  | A <sub>GND</sub>       | 36  | D <sub>4</sub>   | 52  | NC                 |

| 5   | CONV                 | 21  | NC                     | 37  | $\overline{D}_4$ | 53  | NC                 |

| 6   | CONV                 | 22  | V <sub>IN</sub>        | 38  | NC               | 54  | V <sub>EED</sub>   |

| 7   | D <sub>GND</sub>     | 23  | NC                     | 39  | NC               | 55  | NC                 |

| 8   | R <sub>TS</sub>      | 24  | R <sub>B</sub>         | 40  | A <sub>GND</sub> | 56  | NC                 |

| 9   | OFS                  | 25  | R <sub>BS</sub>        | 41  | NC               | 57  | A <sub>GND</sub>   |

| 10  | R <sub>T</sub>       | 26  | D <sub>GND</sub>       | 42  | NC               | 58  | D <sub>5</sub>     |

| 11  | NC                   | 27  | D <sub>GND</sub>       | 43  | V <sub>EED</sub> | 59  | $\overline{D}_{5}$ |

| 12  | V <sub>IN</sub>      | 28  | OVF                    | 44  | NC               | 60  | D <sub>6</sub>     |

| 13  | A <sub>GND</sub>     | 29  | OVF                    | 45  | NC               | 61  | $\overline{D}_{6}$ |

| 14  | A <sub>GND</sub>     | 30  | D <sub>1</sub> (MSB)   | 46  | V <sub>EEA</sub> | 62  | D <sub>7</sub>     |

| 15  | V <sub>IN</sub>      | 31  | $\overline{D}_1$ (MSB) | 47  | NC               | 63  | $\overline{D}_7$   |

| 16  | V <sub>IN</sub>      | 32  | $D_2$                  | 48  | $V_{FFA}$        | 64  | D <sub>8</sub>     |

65-1049-03

# Pin Assignments (continued)

### 68 Lead LCC

| Pin | Name               | Pin | Name             | Pin | Name                   | Pin | Name                 |

|-----|--------------------|-----|------------------|-----|------------------------|-----|----------------------|

| 1   | D <sub>8</sub>     | 18  | V <sub>EEA</sub> | 35  | $\overline{D}_2$       | 52  | R <sub>M</sub>       |

| 2   | $\overline{D}_7$   | 19  | NC               | 36  | D <sub>2</sub>         | 53  | V <sub>IN</sub>      |

| 3   | D <sub>7</sub>     | 20  | V <sub>EEA</sub> | 37  | $\overline{D}_1$ (MSB) | 54  | V <sub>IN</sub>      |

| 4   | $\overline{D}_{6}$ | 21  | V <sub>EEA</sub> | 38  | D <sub>1</sub> (MSB)   | 55  | A <sub>GND</sub>     |

| 5   | D <sub>6</sub>     | 22  | V <sub>EED</sub> | 39  | OVF                    | 56  | NC                   |

| 6   | $\overline{D}_{5}$ | 23  | NC               | 40  | OVF                    | 57  | A <sub>GND</sub>     |

| 7   | D <sub>5</sub>     | 24  | NC               | 41  | D <sub>GND</sub>       | 58  | V <sub>IN</sub>      |

| 8   | NC                 | 25  | NC               | 42  | NC                     | 59  | R <sub>T</sub>       |

| 9   | A <sub>GND</sub>   | 26  | NC               | 43  | R <sub>BS</sub>        | 60  | NC                   |

| 10  | NC                 | 27  | A <sub>GND</sub> | 44  | R <sub>B</sub>         | 61  | OFS                  |

| 11  | NC                 | 28  | NC               | 45  | NC                     | 62  | R <sub>TS</sub>      |

| 12  | NC                 | 29  | NC               | 46  | V <sub>IN</sub>        | 63  | CONV                 |

| 13  | V <sub>EED</sub>   | 30  | NC               | 47  | NC                     | 64  | CONV                 |

| 14  | V <sub>EEA</sub>   | 31  | $\overline{D}_4$ | 48  | A <sub>GND</sub>       | 65  | D <sub>GND</sub>     |

| 15  | NC                 | 32  | D <sub>4</sub>   | 49  | A <sub>GND</sub>       | 66  | D <sub>9</sub> (LSB) |

| 16  | V <sub>EEA</sub>   | 33  | $\overline{D}_3$ | 50  | V <sub>IN</sub>        | 67  | D <sub>9</sub> (LSB) |

| 17  | NC                 | 34  | D <sub>3</sub>   | 51  | NC                     | 68  | $\overline{D}_{8}$   |

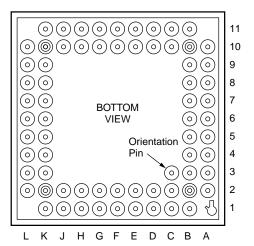

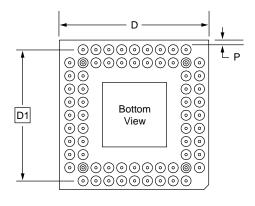

### 68 Lead Ceramic Pin Grid Array

| Pin        | Name             | Pin | Name                        | Pin | Name                   | Pin | Name             |

|------------|------------------|-----|-----------------------------|-----|------------------------|-----|------------------|

| A2         | NC               | В9  | V <sub>EEA</sub>            | F10 | D <sub>8</sub>         | K4  | A <sub>GND</sub> |

| A3         | V <sub>EED</sub> | B10 | NC                          | F11 | $\overline{D}_7$       | K5  | V <sub>IN</sub>  |

| A4         | NC               | B11 | A <sub>GND</sub>            | G1  | $\overline{D}_1$ (MSB) | K6  | V <sub>IN</sub>  |

| <b>A</b> 5 | NC               | C1  | NC                          | G2  | D <sub>1</sub> (MSB)   | K7  | NC               |

| A6         | NC               | C2  | NC                          | G10 | D <sub>9</sub> (LSB)   | K8  | A <sub>GND</sub> |

| A7         | NC               | C10 | $D_5$                       | G11 | $\overline{D}_8$       | К9  | V <sub>IN</sub>  |

| A8         | NC               | C11 | NC                          | H1  | OVF                    | K10 | R <sub>TS</sub>  |

| A9         | NC               | D1  | D <sub>4</sub>              | H2  | OVF                    | K11 | CONV             |

| A10        | V <sub>EED</sub> | D2  | $\overline{D}_4$            | H10 | D <sub>GND</sub>       | L2  | NC               |

| B1         | NC               | D10 | D <sub>6</sub>              | H11 | D <sub>9</sub> (LSB)   | L3  | NC               |

| B2         | A <sub>GND</sub> | D11 | $\overline{D}_{5}$          | J1  | NC                     | L4  | A <sub>GND</sub> |

| В3         | V <sub>EEA</sub> | E1  | D <sub>3</sub>              | J2  | D <sub>GND</sub>       | L5  | R <sub>M</sub>   |

| B4         | NC               | E2  | $\overline{D}_3$            | J10 | CONV                   | L6  | NC               |

| B5         | V <sub>EEA</sub> | E10 | D <sub>7</sub>              | J11 | D <sub>GND</sub>       | L7  | V <sub>IN</sub>  |

| B6         | V <sub>EEA</sub> | E11 | $\overline{D}_{6}$          | K1  | R <sub>BS</sub>        | L8  | A <sub>GND</sub> |

| В7         | V <sub>EEA</sub> | F1  | D <sub>2</sub>              | K2  | R <sub>B</sub>         | L9  | R <sub>T</sub>   |

| B8         | NC               | F2  | $\overline{\overline{D}}_2$ | К3  | V <sub>IN</sub>        | L10 | OFS              |

65-1049-05

65-1049-04

www.DataSheet4U.com

www.DataSheetz

# **Pin Definitions**

|                    |                                                                               | Pin Nun                                                                  | nber                                                                                            |                                      |              |                                  |

|--------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------|--------------|----------------------------------|

| Pin<br>Name        | Bottom-<br>brazed DIP                                                         | Sidebrazed<br>DIP                                                        | LCC                                                                                             | PGA                                  | Value        | Pin Function Description         |

| VEEA               | 46, 48, 51                                                                    | 14,17,19                                                                 | 14, 16, 18,<br>20, 21                                                                           | B9, B7, B6,<br>B5                    | -5.2V        | Analog Supply Voltage            |

| VEED               | 43, 54                                                                        | 11, 22                                                                   | 13, 22                                                                                          | A3, A10                              | -5.2V        | Digital Supply Voltage           |

| DGND               | 4, 7, 26, 27                                                                  | 38, 39, 58,<br>61                                                        | 41, 65                                                                                          | J2, J11,<br>H10                      | 0.0V         | Digital Ground                   |

| AGND               | 13, 14, 19,<br>20, 40, 57                                                     | 8, 25, 45, 46,<br>51, 52                                                 | 9, 27, 48,<br>49, 55, 57                                                                        | B2, K4, L4,<br>K8, L8,               | 0.0V         | Analog Ground                    |

| .RT                | 10                                                                            | 55                                                                       | 59                                                                                              | L9                                   | 0.0V         | Reterence Resistor, Top          |

| RTS                | 8                                                                             | 57                                                                       | 62                                                                                              | K10                                  | 0.0V         | Reference Resistor, Top Sense    |

| RB                 | 24                                                                            | 41                                                                       | 44                                                                                              | K2                                   | -2.0V        | Reference Resistor, Bottom       |

| RBS                | 25                                                                            | 40                                                                       | 43                                                                                              | K1                                   | -2 0V        | Reference Resistor, Bottom Sense |

| RM                 | 17                                                                            | 48                                                                       | 52                                                                                              | L5                                   | -1.0V        | Reference Resistor, Midpoint     |

| OFS                | 9                                                                             | 56                                                                       | 61                                                                                              | L10                                  | 0.0V         | Overflow Sense                   |

| CONV               | 5                                                                             | 60                                                                       | 64                                                                                              | J10                                  | ECL          | Convert                          |

| CONV               | 6                                                                             | 59                                                                       | 63                                                                                              | K11                                  | ECL          | Convert, Complement              |

| VIN                | 12, 15, 16,<br>18, 22                                                         | 43, 47, 49,<br>50, 53                                                    | 46, 50, 53,<br>54, 58                                                                           | K3, K5, K6,<br>L7, K9                | 0V to<br>-2V | Analog Signal Input              |

| D <sub>1</sub> MSB | 30                                                                            | 35                                                                       | 38                                                                                              | G1                                   | ECL          | Most Significant Bit             |

| D2-D8              | 32, 34, 36,<br>58, 60, 62,<br>64                                              | 33, 31, 29,<br>7, 5, 3, 1                                                | 36, 34, 7,<br>5, 3, 1                                                                           | F1, E1, D1,<br>C10, D10,<br>E10, F10 | ECL          |                                  |

| D <sub>9</sub> LSB | 2                                                                             | 63                                                                       | 67                                                                                              | G10                                  | ECL          | Least Significant Bit            |

| D  1 MSB           | 31                                                                            | 34                                                                       | 37                                                                                              | G2                                   | ECL          | Most Significant Bit Complement  |

| D̄2-D̄8            | 33, 35, 37,<br>59, 61, 63, 1                                                  | 32, 30, 28, 6,<br>4, 2, 64                                               | 35, 33, 31,<br>6, 4, 2, 68                                                                      | F2, E2, D2,<br>D11, E11,<br>F11, G11 | ECL          |                                  |

| D <sub>9</sub> LSB | 3                                                                             | 62                                                                       | 66                                                                                              | H11                                  | ECL          | Least Significant Bit Complement |

| OVF                | 28                                                                            | 37                                                                       | 40                                                                                              | H2                                   | ECL          | Ovedlow Output                   |

| OVF                | 29                                                                            | 36                                                                       | 39                                                                                              | H1                                   | ECL          | Overflow Output Complement       |

| NC                 | 11, 21, 23,<br>38, 39, 41,<br>42, 44, 45,<br>47, 49, 50,<br>52, 53, 55,<br>56 | 9, 10, 12, 13,<br>15,16, 18,<br>20, 21, 23,<br>24, 26, 27,<br>42, 44, 54 | 8, 10, 11,<br>12, 15, 17,<br>19, 23, 24,<br>25, 26, 28,<br>29, 30, 42,<br>45, 47, 51,<br>56, 60 | C1, J1, L2,<br>L3, L6, K7,           | Open         | No Connect                       |

nany DataShoot

# Absolute Maximum Ratings (beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                      | Min. | Max.     | Unit |

|----------------------------------------------------------------|------|----------|------|

| Supply Voltages                                                | •    |          | •    |

| VEED (measured to DGND)                                        | -7.0 | +0.5     | V    |

| VEEA (measured to AGND)                                        | 7.0  | +0.5     | V    |

| AGND (measured to DGND)                                        | -1.0 | +1.0     | V    |

| VEEA (measured to VEED)                                        | -0.5 | +0.5     | V    |

| Input Voltages <sup>2</sup>                                    |      |          | •    |

| CONV, CONV (measured to DGND)                                  | +0.5 | VEE      | V    |

| VIN, VRT, VRB (measured to AGND)                               | +0.5 | VEE      | V    |

| V <sub>RT</sub> (measured to V <sub>RB</sub> )                 | -2.5 | +2.5     | V    |

| Output                                                         |      |          |      |

| Short-circuit duration (single output in HIGH state to ground) |      | Infinite |      |

| Temperature                                                    |      |          |      |

| Operating, case                                                | -60  | +140     | °C   |

| junction                                                       |      | +175     | °C   |

| Lead, soldering (10 seconds)                                   |      | 300      | °C   |

| Storage                                                        | - 65 | +150     | °C   |

#### Notes:

- 1. Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range.

# **Operating Conditions**

|           |                                             |      | Temperature Range |      |      |        |      |       |

|-----------|---------------------------------------------|------|-------------------|------|------|--------|------|-------|

|           |                                             | S    | Standar           | d    | E    | xtende | d    |       |

| Parameter | Parameter                                   |      |                   | Max. | Min. | Nom.   | Max. | Units |

| VEED      | Digital Supply Voltage (measured to DGND)   | -4.9 | -5.2              | -5.5 | -4.9 | -5.2   | -5.5 | V     |

| VEEA      | Analog Supply Voltage (measured to AGND)    | -4.9 | -5.2              | -5.5 | -4.9 | -5.2   | -5.5 | V     |

| VAGND     | Analog Ground Voltage (measured to DGND)    | -0.1 | 0.0               | +0.1 | -0.1 | 0.0    | +0.1 | V     |

| VEEA-VEED | Supply Voltage Differential                 | -0.1 | 0.0               | +0.1 | -0.1 | 0.0    | +0.1 | V     |

| tpWL      | CONV Pulse Width, LDW                       | 12   |                   |      | 12   |        |      | ns    |

| tpwH      | CONV Pulse Width, HIGH                      | 15   |                   |      | 15   |        |      | ns    |

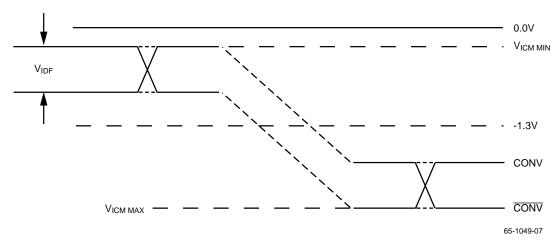

| VICM      | Input Voltage, Common Mode                  | -0.5 |                   | -2.5 | -0.5 |        | -2.5 | V     |

| VIDF      | Input Voltage, Differential                 | 0.3  |                   | 1.2  | 0.3  |        | 1.2  | V     |

| VIN       | Input Voltage Range                         | VRB  |                   | VRT  | VRB  |        | VRT  | V     |

| VRT       | Most Positive Reference Inputs <sup>1</sup> | -0.1 | 0.0               | 0.1  | -0.1 | 0.0    | +0.1 | V     |

| VRB       | Most Negative Reference Input <sup>1</sup>  | -1.9 | -2.0              | -2.1 | -1.9 | -2.0   | -2.1 | V     |

| VRT-VRB   | Voltage Reference Differential              | 1.8  | 2.0               | 2.2  | 1.8  | 2.0    | 2.2  | V     |

| TA        | Ambient Temperature, Still Air              | 0    |                   | 70   |      |        |      | °C    |

| TC        | Case Temperature                            |      |                   |      | -55  |        | 125  | °C    |

### Note:

<sup>1.</sup> VRT must be more postive than VRB, and the voltage reference differential must be within the specified range.

### **DC Electrical Characteristics**

|                |                                         |                                 | Temperature Range |      |      |       |       |

|----------------|-----------------------------------------|---------------------------------|-------------------|------|------|-------|-------|

|                |                                         |                                 | Standard Extended |      | nded |       |       |

| Param          | eter                                    | Test Conditions                 | Min. Max.         |      | Min. | Max.  | Units |

| IEE            | Supply Current                          | VEED, VEEA = Max                | !                 |      | •    | •     |       |

|                |                                         | TA = 0°C to 70°C                |                   | -950 |      |       | mA    |

|                |                                         | T <sub>A</sub> = 70°C           |                   | -750 |      |       | mA    |

|                |                                         | IC = - 55°C to 125° C           |                   |      |      | -1090 | mA    |

|                |                                         | T <sub>C</sub> = 125°C          |                   |      |      | -750  | mA    |

| IREF           | Reference Current                       | VRT, VRB = Nom                  | 10                | 36   | 10   | 36    | mA    |

| RREF           | Total Reference Resistance              |                                 | 56                | 200  | 56   | 200   | Ω     |

| RIN            | Input Equivalent Resistance             | VRT, VRB = Nom, VIN = VRB       | 16                |      | 16   |       | ΚΩ    |

| CIN            | Analog Input Capacitance                | VRT, VRB = Nom, VIN = VRB       |                   | 160  |      | 160   | pF    |

| ICB            | Inpul Constant Bias Current             | VEEA = Max, VIN = 0V            |                   | 500  |      | 750   | μΑ    |

| l <sub>l</sub> | Input Current, CONV, CONV               | VEED = Max, VI = -0.7V          |                   | 150  |      | 180   | μΑ    |

| VoL            | Output Voltage, Logic LOW1              | VEED = Nom                      |                   | -1.6 |      | -1.5  | V     |

| Voн            | Output Voltage, Logic HIGH <sup>1</sup> | VEED = Nom                      | -0.95             |      | -1.1 |       | V     |

| Cı             | Digital Input Capacitance               | T <sub>A</sub> = 25°C, f = 1MHz |                   | 20   |      | 20    | pF    |

### Note:

# **AC Electrical Characteristics**

|      |                               |                  | Temperature Range |      |          |      |       |

|------|-------------------------------|------------------|-------------------|------|----------|------|-------|

|      |                               |                  | Standard          |      | Extended |      |       |

| Para | meter                         | Test Conditions  | Min.              | Max. | Min.     | Max. | Units |

| Fs   | Maximum Conversion Rate       | VEED, VEEA = Min | 30                |      | 30       |      | Msps  |

| tsto | Sampling Time Offset          | VEED, VEEA = Min | -2                | 6    | -2       | 6    | ns    |

| tD   | Output Delay <sup>1</sup>     | VEED, VEEA = Min |                   | 27   |          | 27   | ns    |

| tHO  | Output Hold Time <sup>1</sup> | VEED, VEEA = Min | 3                 |      | 3        |      | ns    |

### Note:

1. Test Load =  $500\Omega$  to -2V on each output,  $C_{LOAD}$  = 20pF.

# **Timing Diagrams**

Figure 1. Timing Diagram

...... Data Cl

<sup>1.</sup> Test Load =  $500\Omega$  to -2v on each output.

# Timing Diagrams (continued)

Figure 2. CONVert, CONVert Switching Levels

# **System Performance Characteristics**

|       |                                       |                                                                   | Temperature Range |      |      |      |              |

|-------|---------------------------------------|-------------------------------------------------------------------|-------------------|------|------|------|--------------|

|       |                                       |                                                                   | Stan              | dard | Exte | nded |              |

| Param | eter                                  | Test Conditions                                                   | Min.              | Max. | Min. | Max. | Units        |

| ELI   | Linearity Error Integral,             | VRT, VRB = Nom                                                    |                   | 0.15 |      | 0.20 | %            |

|       | Independent                           | V <sub>RT</sub> , V <sub>RB</sub> = Nom, V <sub>RM</sub> Adjusted |                   | 0.10 |      | 0.10 | %            |

| ELD   | Linearity Error Differential          | VRT, VRB = Nom                                                    |                   | 0.1  |      | 0.1  | %            |

| Q     | Code Size                             | V <sub>RT</sub> , V <sub>RB</sub> = Nom                           | 15                | 185  | 15   | 185  | %<br>Nominal |

| Eots  | Offset Error, Top                     | VIN = VRT, RTS Connected                                          |                   | ±4   |      | ±4   | mV           |

| Еот   | Offset Error, Top                     | VIN = VRT                                                         |                   | 30   |      | 30   | mV           |

| Eobs  | Offset Error, Bottom                  | VIN = VRB, RBS Connected                                          |                   | ±4   |      | ±4   | mV           |

| Еов   | Offset Error, Bottom                  | VIN = VRB                                                         |                   | -30  |      | -30  | mV           |

| Tco   | Offset Error, Temperature Coefficient |                                                                   |                   | 20   |      | 20   | μV/°C        |

| tTR   | Transient Response,<br>Full-Scale     |                                                                   |                   | 20   |      | 20   | ns           |

| BW    | Bandwidth, Full Power Input           | ±0.9dB Frequency Response                                         | 15                |      | 15   |      | MHz          |

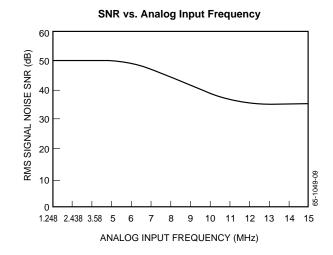

| SNR   | Signal-to-Noise Ratio                 | 30Msps Conversion Rate, 10MHz I                                   | Bandwi            | dth  |      | •    |              |

|       | Peak Signal/RMS Noise                 | 1.25MHz Input                                                     | 57                |      | 57   |      | dB           |

|       |                                       | 5.0MHz Input                                                      | 53                |      | 53   |      | dB           |

|       | RMS Signal/RMS Noise                  | 1.25MHz Input                                                     | 48                |      | 48   |      | dB           |

|       |                                       | 5.0MHz Input                                                      | 44                |      | 44   |      | dB           |

| EAP   | Aperture Error                        |                                                                   |                   | 50   |      | 50   | ps           |

| DP    | Differential Phase Error              | F <sub>S</sub> = 4 x NTSC                                         |                   | 0.5  |      | 0.5  | Degree       |

| DG    | Differential Gain Error               | Fs = 4 x NTSC                                                     |                   | 1.5  |      | 1.5  | %            |

# **Typical Performance Curves**

### Power Supply Current vs. Temperature POWER SUPPLY CURRENT (mA) -450 -500 -550 -600 -650 -700 -750 -800 -850 -55° -25° 0° 25° 50° 75° 100° 125° CASE TEMPERATURE (°C)

Figure 3. Power Supply Current vs. Temperature

Figure 4. SNR vs. Analog Input Frequency

# **Equivalent Circuits**

Figure 5. Simplified Analog Input Equivalent Circuits

Figure 6. Digital Input Equivalent Circuit

Figure 7. Output Circuits

# **Output Coding Table<sup>1</sup>**

|          |     | D1        | D9    |  |

|----------|-----|-----------|-------|--|

| VIN      | OVF | MSB       | LSB   |  |

| +0.0039V | 1   | 000000000 |       |  |

| 0.0000V  | 0   | 00000     | 00000 |  |

| -0.0039V | 0   | 00000     | 00001 |  |

| •        | •   |           | ,     |  |

| •        | •   |           | ;     |  |

| •        |     |           |       |  |

| -0.9980V | 0   | 01111     | 11111 |  |

| -1.0020V | 0   | 10000     | 00000 |  |

| -1.0059V | 0   | 10000     | 00001 |  |

| l.com    | •   |           | ,     |  |

| •        | :   |           | :     |  |

| •        |     | _         |       |  |

| -1.9961V | 0   | 11111     | 11110 |  |

| -2.0000V | 0   | 11111     | 11111 |  |

### Note:

1. Voltages are code midpoints.

# **Standard Military Drawing**

These devices are also available as products manufactured, tested, and screened in compliance with Standard Military Drawings (SMDs). The nearest vendor equivalent product is shown on the back page of this document; however, the applicable SMD is the sole controlling document defining the SMD product.

### **Notes:**

### **Mechanical Dimensions**

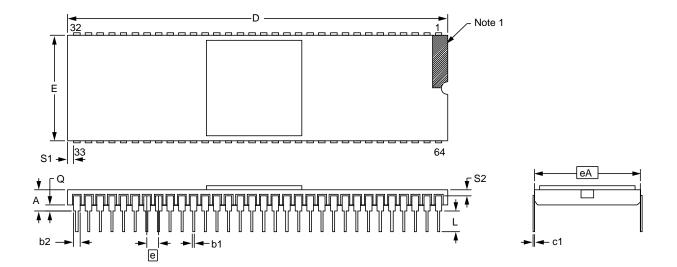

### 64 Lead Sidebrazed Ceramic DIP

| Symbol | Inches |       | Millin | neters | Notes |  |

|--------|--------|-------|--------|--------|-------|--|

| Symbol | Min.   | Max.  | Min.   | Max.   | Notes |  |

| Α      | .120   | .175  | 3.05   | 4.44   |       |  |

| B1     | .015   | .023  | .38    | .58    | 7     |  |

| B2     | .040   | .065  | 1.02   | 1.65   | 2     |  |

| C1     | .008   | .015  | .20    | .38    | 7     |  |

| D      | 3.170  | 3.240 | 80.52  | 82.30  |       |  |

| E      | .880   | .910  | 14.60  | 15.48  |       |  |

| е      | .100   | BSC   | 2.54   | BSC    | 4, 8  |  |

| eAn    | .900   | BSC   | 22.86  | BSC    | 6     |  |

| L      | .125   | .175  | 3.18   | 4.45   |       |  |

| Q      | .025   | .065  | .63    | 1.65   | 3     |  |

| S1     | .005   | _     | .13    | _      | 5     |  |

| S2     | .005   | _     | .13    | _      |       |  |

#### Notes:

- Index area: a notch or a pin one identification mark shall be located adjacent to pin one. The manufacturer's identification shall not be used as pin one identification mark.

- 2. The minimum limit for dimension "b2" may be .023(.58mm) for leads number 1, 32, 33, and 64 only.

- 3. Dimension "Q" shall be measured from the seating plane to the base plane.

- The basic pin spacing is .100 (2.54mm) between centerlines. Each pin centerline shall be located within ±.010 (.25mm) of its exact longitudinal position relative to pins 1 and 64.

- 5. Applies to all four corners (leads number 1, 32, 33, and 64).

- 6. "eA" shall be measured at the centerline of the leads.

- 7. All leads Increase maximum limit by .003(.08mm) measured at the center of the flat when lead finish is applied.

- 8. Sixty-two spaces.

# **Mechanical Dimensions** (continued)

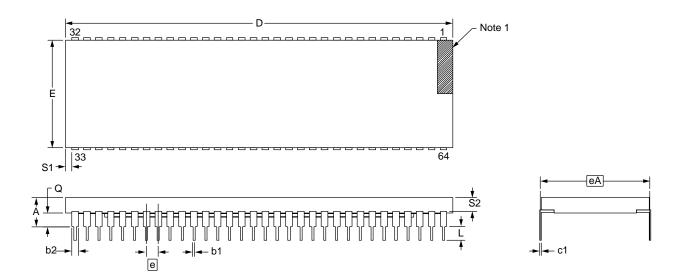

### 64 Lead Bottombrazed Ceramic DIP

| Symbol | Inches   |       | Millimeters |       | Neter |

|--------|----------|-------|-------------|-------|-------|

|        | Min.     | Max.  | Min.        | Max.  | Notes |

| Α      | .125     | .200  | 3.18        | 5.08  |       |

| B1     | .015     | .023  | .38         | .58   | 7     |

| B2     | .040     | .065  | 1.02        | 1.65  | 2     |

| C1     | .008     | .015  | .20         | .38   | 7     |

| D      | 3.110    | 3.240 | 80.00       | 82.30 |       |

| E      | .790     | .810  | 20.07       | 20.57 |       |

| е      | .100 BSC |       | 2.54        | BSC   | 4, 8  |

| eAn    | .900 BSC |       | 22.86 BSC   |       | 6     |

| L      | .125     | .175  | 3.18        | 4.45  |       |

| Q      | .050     | .100  | 1.27        | 2.54  | 3     |

| S1     | .005     | _     | .13         | _     | 5     |

| S2     | .005     | _     | .13         | _     |       |

#### Notes:

- Index area: a notch or a pin one identification mark shall be located adjacent to pin one. The manufacturer's identification shall not be used as pin one identification mark.

- 2. The minimum limit for dimension "b2" may be .023(.58mm) for leads number 1, 32, 33, and 64 only.

- 3. Dimension "Q" shall be measured from the seating plane to the base plane.

- 4. The basic pin spacing is .100 (2.54mm) between centerlines. Each pin centerline shall be located within  $\pm$ .010 (.25mm) of its exact longitudinal position relative to pins 1 and 64.

- 5. Applies to all four corners (leads number 1, 32, 33, and 64).

- 6. "eA" shall be measured at the centerline of the leads.

- All leads Increase maximum limit by .003(.08mm) measured at the center of the flat when lead finish is applied.

- 8. Sixty-two spaces.

### **Mechanical Dimensions** (continued)

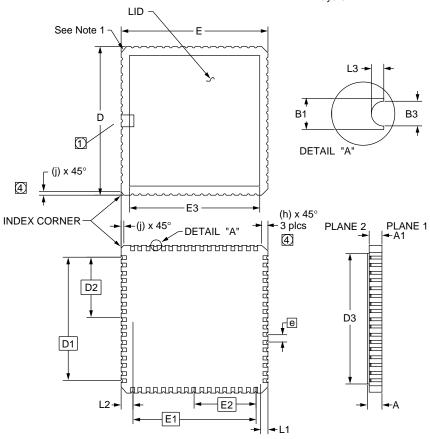

### 68 Lead LCC

| Cumbal    | Inches   |      | Millimeters |       | Neter |

|-----------|----------|------|-------------|-------|-------|

| Symbol    | Min.     | Max. | Min.        | Max.  | Notes |

| Α         | .082     | .110 | 2.08        | 2.79  | 3, 6  |

| A1        | .071     | .093 | 1.83        | 2.39  | 3, 6  |

| B1        | .022     | .028 | .560        | .710  | 2     |

| В3        | .006     | .022 | .150        | .560  | 2,5   |

| D/E       | .938     | .962 | 23.82       | 24.43 |       |

| D1/E1     | .800 BSC |      | 20.32 BSC   |       |       |

| D2/E2     | .400 BSC |      | 10.16 BSC   |       |       |

| .com<br>e | .050 BSC |      | 1.27        | BSC   |       |

| h         | .040 BSC |      | 1.02 BSC    |       | 4     |

| j         | .020 BSC |      | .510 BSC    |       | 4     |

| L1        | .045     | .055 | 1.14        | 1.40  |       |

| L2        | .075     | .095 | 1.91        | 2.41  |       |

| L3        | .003     | .015 | .080        | .380  | 5     |

| ND/NE     | 17       |      | 17          |       |       |

| N         | 68       |      | 68          |       |       |

#### Notes:

- The index feature for terminal 1 identification, optical orientation or handling purposes, shall be within the shaded index areas shown on planes 1 and 2. Plane 1 terminal 1 identification may be an extension of the length of the metallized terminal which shall not be wider than the B1 dimension.

- Unless otherwise specified, a minimum clearance of .015 inch (0.38mm) shall be maintained between all metallized features (e.g., lid, castellations, terminals, thermal pads, etc.).

- 3. Dimension "A" controls the overall package thickness. The maximum "A" dimension is the package height before being solder dipped.

- The corner shape (square, notch, radius, etc.) may vary at the manufacturer's option, from that shown on the drawing. The index corner shall be clearly unique.

- 5. Dimension "B3" minimum and "L3" minimum and the appropriately derived castellation length define an unobstructed three dimensional space traversing all of the ceramic layers in which a castellation was designed. Dimension "B3" maximum and "L3" maximum define the maximum width and depth of the castellation at any point on its surface. Measurement of these dimensions may be made prior to solder dripping.

- 6. Chip carriers shall be constructed of a minimum of two ceramic layers.

/ww.DataShee

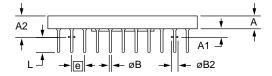

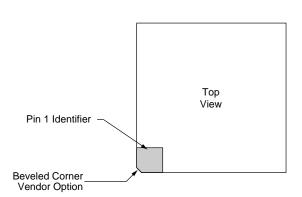

# **Mechanical Dimensions** (continued)

# 68 Lead Plastic Grid Array

| Cumbal | Inches    |       | Millimeters |       | Notes |

|--------|-----------|-------|-------------|-------|-------|

| Symbol | Min.      | Max.  | Min.        | Max.  | Notes |

| А      | .080      | .125  | 2.03        | 3.18  |       |

| A1     | .025      | .060  | 0.64        | 1.52  |       |

| A2     | .105      | .180  | 2.67        | 4.57  |       |

| øΒ     | .017      | .020  | 0.43        | 0.51  |       |

| øB2    | .050 NOM. |       | 1.27 NOM.   |       |       |

| D      | 1.140     | 1.180 | 28.96       | 29.97 |       |

| D1     | 1.000 BSC |       | 25.40 BSC   |       |       |

| .com   | .100 BSC  |       | 2.54 BSC    |       |       |

| L      | .120      | .140  | 3.05        | 3.56  |       |

| М      | 11        |       | 11          |       | 2     |

| N      | 68        |       | 68          |       | 3     |

| Р      | .003      | _     | .076        | _     |       |

### Notes:

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Dimension "M" defines matrix size.

- 3. Dimension "N" defines the maximum possible number of pins.

- 4. Controlling dimension: inch.

www.DataSheet4U:

# **Ordering Information**

| Product<br>Number | Temperature Range                     | Screening                   | Package                           | Package<br>Marking |

|-------------------|---------------------------------------|-----------------------------|-----------------------------------|--------------------|

| TDC1049J0C        | STD - TA = 0°C to 70°C                | Commercial                  | 64 Lead Sidebrazed<br>Ceramic DIP | 1049J0C            |

| TDC1049J0V        | EXT - $T_C$ = -55°C to 125°C          | MIL-STD-883                 | 64 Lead Sidebrazed<br>Ceramic DIP | 1049J0V            |

| 5962-8853201XA    | EXT - T <sub>C</sub> = -55°C to 125°C | Per Standard<br>Mil Drawing | 64 Lead Sidebrazed<br>Ceramic DIP | 5962-8853201XA     |

| TDC1049C1C        | STD - TA = 0°C to 70°C                | Commercial                  | 68-Lead LCC                       | 1049C1C            |

| TDC1049C1V        | EXT - $T_C$ = -55°C to 125°C          | MIL-STD-883                 | 68-Lead LCC                       | 1049C1V            |

| 5962-8853201ZA    | EXT - T <sub>C</sub> = -55°C to 125°C | Per Standard<br>Mil Drawing | 68-Lead LCC                       | 5962-8853201ZA     |

| TDC1049G8C        | STD - T <sub>A</sub> = 0°C to 70°C    | Commercial                  | 68 Lead Ceramic PGA               | 1049G8C            |

| TDC1049G8V        | EXT - Tc = -55°C to 125°C             | MIL-STD-B83                 | 68 Lead Ceramic PGA               | 1049G8V            |

| Standard Military Drawing | Nearest Equivalent Fairchild Product No. | Package                             |

|---------------------------|------------------------------------------|-------------------------------------|

| 5962-8853201XA            | TDC1049J0V                               | 64 Lead Sidebrazed<br>Ceramic DIP   |

| 5962-8853201YA            | TDC1049J3V                               | 64 Lead Bottombrazed<br>Ceramic DIP |

| 5962-8853201ZA            | TDC1049C1V                               | 68-Lead LCC                         |

| 5962-8853201UA            | TDC1049L1V                               | 68-Lead LCC                         |

### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com