July 14, 2005

**TGA2511**

# **X-Band Low Noise Amplifier**

## **Product Description**

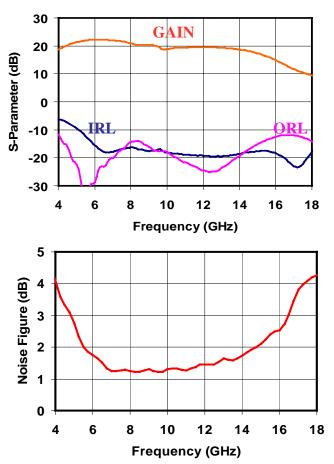

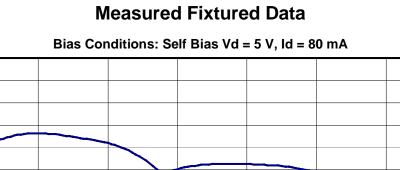

The TriQuint TGA2511 is a wideband LNA with AGC amplifier for EW, ECM, and RADAR receiver or driver amplifier applications. Offering high gain 20dB typical from 6-14GHz, the TGA2511provides excellent noise performance with typical midband NF 1.3dB, while the balanced topology offers good return loss typically 15dB.

The TGA2511 is designed for maximum ease of use. The large input FETs can handle up to 21dBm input power reliably. The part is also assembled in self-biased mode, using a single +5V supply connection from either side of the chip, or in gate biased mode, allowing the user to control the current for a particular applications.

In self-biased mode the TGA2511 offers 6dBm typical P1dB, while in gate-biased mode the typical P1dB is over 12dBm. The small size of 2.46mm<sup>2</sup> allows ease of compaction into Multi-Chip-Modules (MCMs).

The TGA2511 is 100% DC and RF tested onwafer to ensure performance compliance.

Lead-Free & RoHS compliant.

## **Key Features**

- Typical Frequency Range: 6 14 GHz

- 1.3 dB Nominal Noise Figure

- 20 dB Nominal Gain

- Bias: 5 V, 160 mA Gate Bias 5 V, 80 mA Self Bias

- 0.15 um 3MI pHEMT Technology

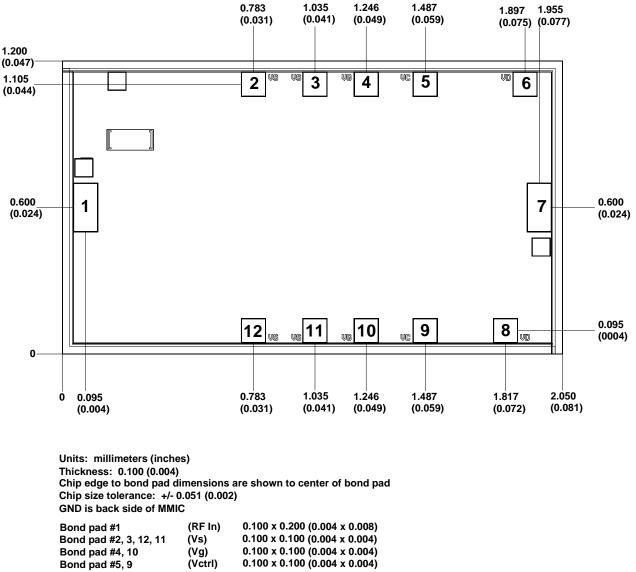

- Chip Dimensions 2.05 x 1.20 x 0.10 mm (0.081 x 0.047 x 0.004 in)

## **Primary Applications**

- X-Band Radar

- EW, ECM

- Point-to-Point Radio

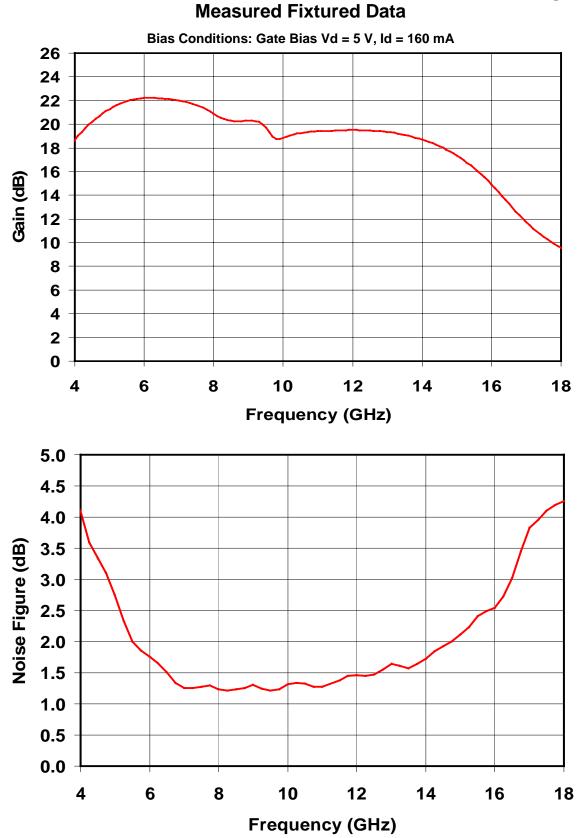

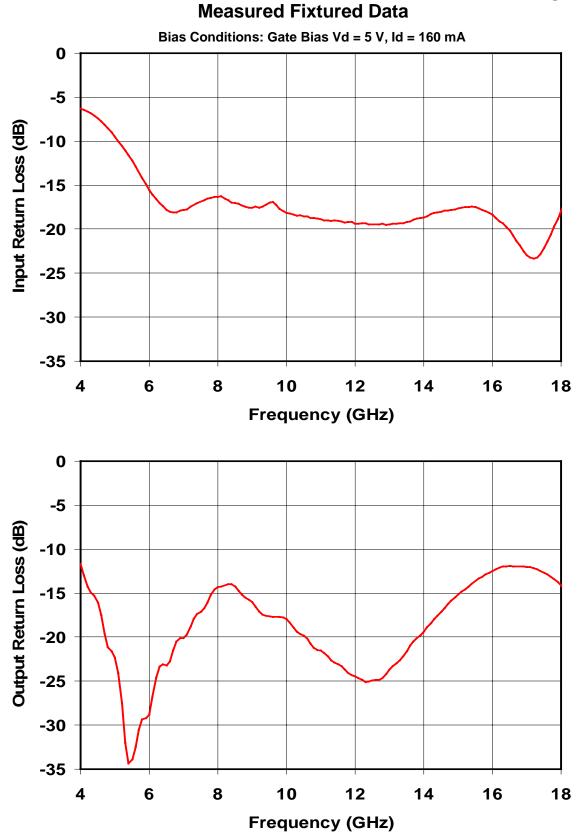

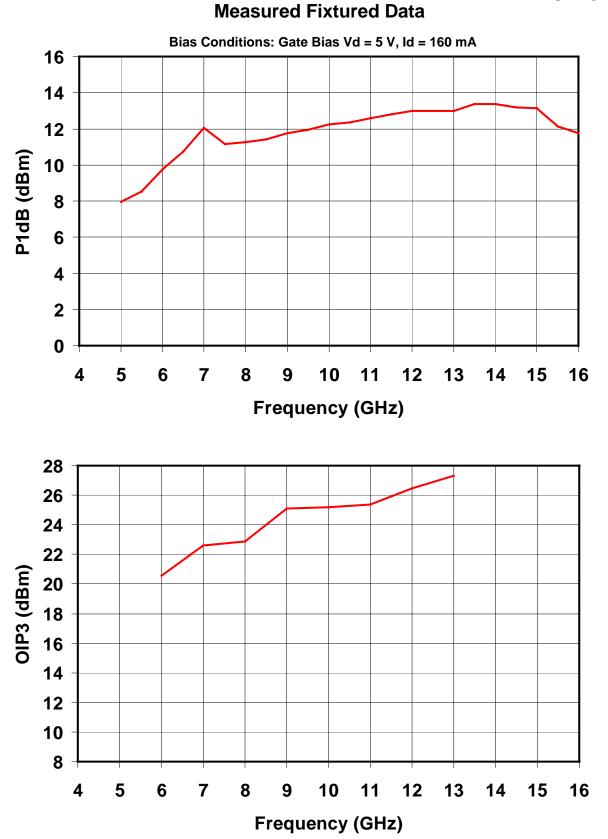

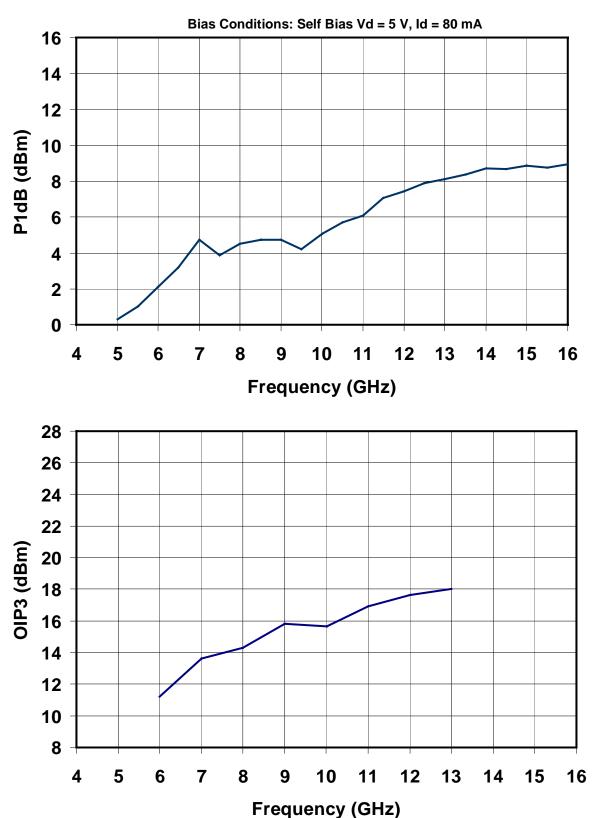

## **Measured Fixtured Data**

Bias Conditions: Gate Bias Vd = 5 V, Id = 160 mA

Note: Devices is early in the characterization process prior to finalizing all electrical specifications. Specifications are subject to change without notice

TriQuint Semiconductor Texas: Phone (972)994-8465 Fax (972)994-8504 Email: Info-mmw@tqs.com Web: www.triquint.com

July 14, 2005

TGA2511

#### TABLE I MAXIMUM RATINGS <u>1</u>/

| SYMBOL           | PARAMETER                         | VALUE                     | NOTES                 |

|------------------|-----------------------------------|---------------------------|-----------------------|

| Vd               | Drain Voltage                     | [3.5 + (0.0125)(ld)] V    | <u>2</u> / <u>3</u> / |

| Vg               | Gate Voltage Range                | -1 TO +0.5 V              |                       |

| ld               | Drain Current (gate biased)       | 240 mA                    | <u>2/ 4</u> /         |

| Ig               | Gate Current                      | 14 mA                     | <u>4</u> /            |

| P <sub>IN</sub>  | Input Continuous Wave Power       | 21 dBm                    |                       |

| P <sub>D</sub>   | Power Dissipation                 | See note <u>5</u> /       | <u>2</u> /            |

| Т <sub>сн</sub>  | Operating Channel Temperature     | 117 <sup>0</sup> C        | <u>6</u> / <u>7</u> / |

| Т <sub>м</sub>   | Mounting Temperature (30 Seconds) | 320 <sup>0</sup> C        |                       |

| T <sub>STG</sub> | Storage Temperature               | -65 to 150 <sup>0</sup> C |                       |

<u>1</u>/ These ratings represent the maximum operable values for this device.

- $\underline{2}$ / Combinations of supply voltage, supply current, input power, and output power shall not exceed  $P_{D}$ .

- 3/ Unit for Id is A

- <u>4</u>/ Total current for the entire MMIC.

- 5/ For a median life time of 1E+6 hrs, Power dissipation is limited to:

$$P_{D}(max) = (117 \ ^{0}C - T_{BASE} \ ^{0}C) / \theta_{JC} (^{0}C/W)$$

Where  $T_{BASE}$  is the base plate temperature,  $\theta_{JC}$  is on Table IV.

- <u>6</u>/ Junction operating temperature will directly affect the device median time to failure (MTTF). For maximum life, it is recommended that junction temperatures be maintained at the lowest possibl levels.

- <u>7</u>/ These ratings apply to each individual FET.

# TABLE IIDC PROBE TESTS(Ta = 25 °C, Nominal)

| SYMBOL                   | PARAMETER                         | MIN. | TYP. | MAX. | UNITS |

|--------------------------|-----------------------------------|------|------|------|-------|

| V <sub>BVGS, Q1</sub>    | Breakdown Voltage Gate-<br>Source | -30  |      | -5   | V     |

| V <sub>P, Q1,2,5,6</sub> | Pinch-Off Voltage                 | -0.7 |      | -0.1 | V     |

Q1, Q2, Q5, Q6 are 400 um FET.

#### TABLE III ELECTRICAL CHARACTERISTICS

(Ta = 25 °C Nominal)

| PARAMETER                                 | Gate Bias | Self Bias | UNITS |

|-------------------------------------------|-----------|-----------|-------|

| Frequency Range                           | 6 - 14    | 6 - 14    | GHz   |

| Drain Voltage, Vd                         | 5.0       | 5.0       | V     |

| Drain Current, Id                         | 160       | 80        | mA    |

| Gate Voltage, Vg                          | -0.1      | -         | V     |

| Small Signal Gain, S21                    | 20        | 17        | dB    |

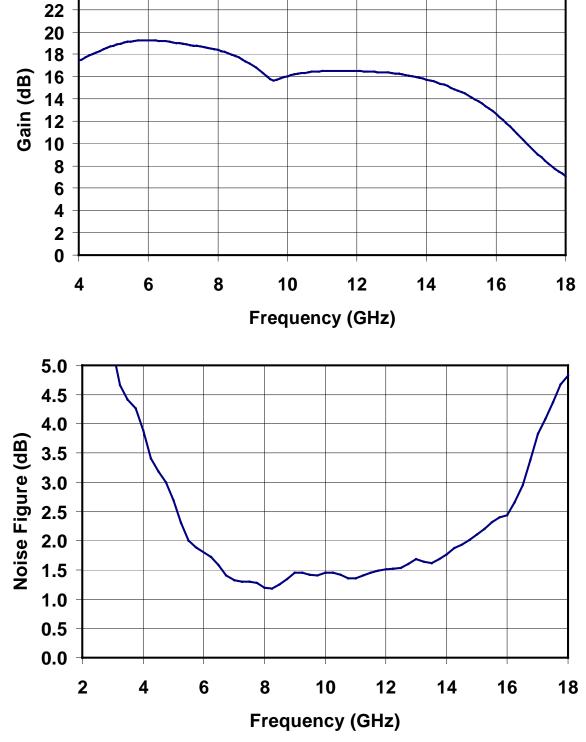

| Input Return Loss, S11                    | 18        | 18        | dB    |

| Output Return Loss, S22                   | 18        | 18        | dB    |

| Noise Figure, NF                          | 1.3       | 1.4       | dB    |

| Output Power @ 1dB Gain Compression, P1dB | 12        | 6         | dBm   |

| OIP3                                      | 24        | 15        | dBm   |

#### TABLE IV THERMAL INFORMATION

| PARAMETER                                               | TEST CONDITIONS                                     | Т <sub>сн</sub><br>( <sup>о</sup> С) | θ <sub>JC</sub><br>(°C/W) | T <sub>M</sub><br>(HRS) |

|---------------------------------------------------------|-----------------------------------------------------|--------------------------------------|---------------------------|-------------------------|

| θ <sub>JC</sub> Thermal Resistance<br>(channel to Case) | Vd = 5 V<br>Id = 160 mA Gate Bias<br>Pdiss = 0.80 W | 103.9                                | 42.4                      | 3.8E+6                  |

| θ <sub>JC</sub> Thermal Resistance<br>(channel to Case) | Vd = 5 V<br>Id = 80 mA Self Bias<br>Pdiss = 0.40 W  | 82.7                                 | 31.7                      | 4.1E+7                  |

Note: Assumes eutectic attach using 1.5 mil 80/20 AuSn mounted to a 20 mil CuMo Carrier at 70°C baseplate temperature. Worst case condition with no RF applied, 100% of DC power is dissipated.

TriQuint Semiconductor Texas: Phone (972)994-8465 Fax (972)994-8504 Email: Info-mmw@tqs.com Web: www.triquint.com

**TriQuint** () SEMICONDUCTOR®

**Advance Product Information**

July 14, 2005

July 14, 2005

July 14, 2005

26 24 July 14, 2005

July 14, 2005

**TGA2511**

### **Measured Fixtured Data**

July 14, 2005

**TGA2511**

Measured Fixtured Data

July 14, 2005

**TGA2511**

# **Mechanical Drawing**

Bond pad #6, 8

(Vd)

0.100 x 0.100 (0.004 x 0.004)

Bond pad #7

(RF Out)

0.100 x 0.200 (0.004 x 0.008)

GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.

10 TriQuint Semiconductor Texas: Phone (972)994-8465 Fax (972)994-8504 Email: Info-mmw@tqs.com Web: www.triquint.com

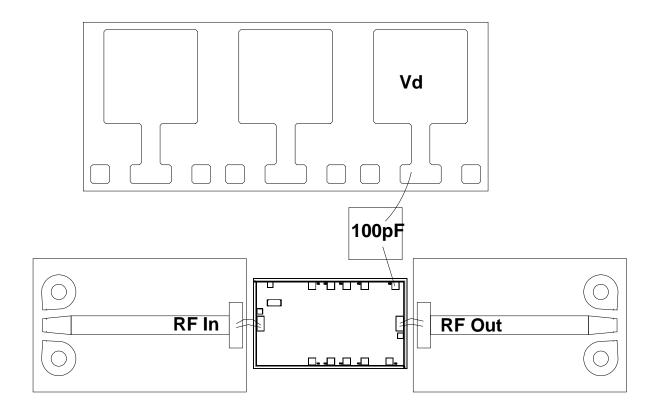

# **Recommended Chip Assembly Diagram**

#### **Option 1: Self Bias - No Gain Control**

All DC connections may be brought in from either side of the chip (Use Pad 6 or 8) 0.01uF external Cap is recommended on Drain Bias: Vd = 5V (Id = ~80mA)

GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.

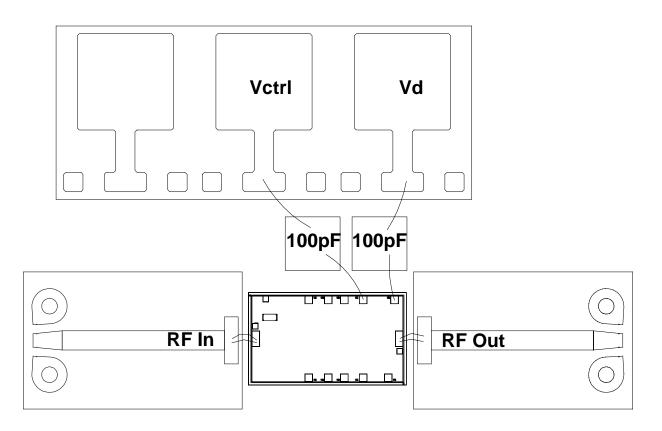

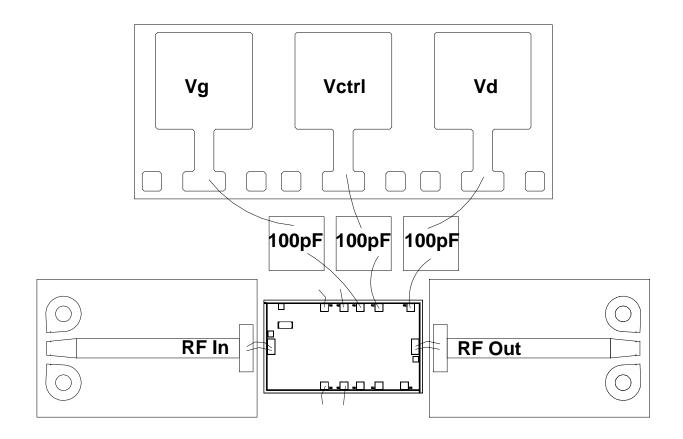

# **Recommended Chip Assembly Diagram (Con't)**

#### **Option 2: Self Bias - With Gain Control**

All DC connections may be brought in from either side of the chip (Use Pad 5 or 9, and Pad 6 or 8) 0.01uF external Caps are recommended on Drain line Bias: Vd = 5V (Id = ~80mA), VctrI = 0 to +5V for Gain adjustment

12

# Recommended Chip Assembly Diagram (Con't)

#### **Option 3: Gate Bias - With Gain Control**

All DC connections may be brought in from either side of the chip (Use Pad 4 or 10, Pad 5 or 9, and Pad 6 or 8) 0.01uF external Caps are recommended on Drain, Gate line, 10 ohm external series R between 100pF cap and 0.01uF cap is recommended for Gate line Source connections (Pad 2, 3, 11, 12) are bonded to ground Bias: Vd = 5V, Vctrl = 0 to +5V for Gain adjustment Vg = Range, -0.5 to 0, typically ~ -0.1 will provide ~160mA of Id.

#### Advance Product Information July 14, 2005

TGA2511

## Assembly Process Notes

Reflow process assembly notes:

- Use AuSn (80/20) solder with limited exposure to temperatures at or above 300<sup>o</sup>C (30 seconds max).

- An alloy station or conveyor furnace with reducing atmosphere should be used.

- No fluxes should be utilized.

- Coefficient of thermal expansion matching is critical for long-term reliability.

- Devices must be stored in a dry nitrogen atmosphere.

Component placement and adhesive attachment assembly notes:

- Vacuum pencils and/or vacuum collets are the preferred method of pick up.

- Air bridges must be avoided during placement.

- The force impact is critical during auto placement.

- Organic attachment can be used in low-power applications.

- Curing should be done in a convection oven; proper exhaust is a safety concern.

- Microwave or radiant curing should not be used because of differential heating.

- Coefficient of thermal expansion matching is critical.

Interconnect process assembly notes:

- Thermosonic ball bonding is the preferred interconnect technique.

- Force, time, and ultrasonics are critical parameters.

- Aluminum wire should not be used.

- Maximum stage temperature is 200<sup>o</sup>C.

GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.