### **FEATURES**

- Works with 1.25V  $\sim$  5.5V  $V_{IN}$

- Ultra Low Dropout Voltage

- Low Quiescent Current

- Excellent Line and Load Regulation

- Guaranteed Output Current of 3.0A

- Adjustable Output Voltage Down to 0.8V

- V<sub>OUT</sub> Power OK Signal

- Logic Controlled Shutdown Option

- Over-Temperature/Over-Current Protection

- -40 °C to 125 °C Junction Temperature Range

### **APPLICATION**

- Motherboards and Graphic Cards

- Microprocessor and Chipset Power Supplies

- Peripheral Cards

- Low Voltage Digital ICs

- High Efficiency Linear Regulators

### **DESCRIPSION**

The TJ47300 is a 3.0A high performance ultra lowdropout linear regulator ideal for powering core voltages of low-power microprocessors. The TJ47300 implements a dual supply configuration allowing for very low output impedance. The TJ47300 requires a bias input supply and a main input supply, allowing for ultra-low input voltages on the main supply rail. The input supply operates from 1.25V to 5.5V and the bias supply requires between 3V and 5.5V for proper operation. The TJ47300 delivers high current and ultra-low-dropout output voltage as low as 0.8V for applications where V<sub>OUT</sub> is very close to  $V_{\rm IN}$ . The TJ47300 is developed on a CMOS technology which allows low guiescent current operation independent of output current. This technology also allows the TJ47300 to operate under extremely low dropout conditions.

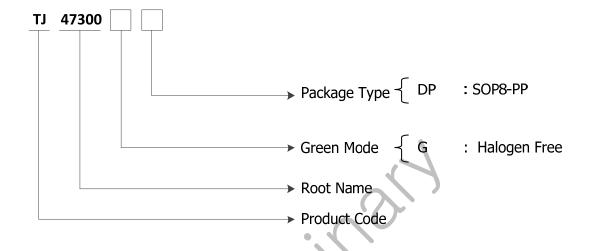

### ORDERING INFORMATION

| Device     | Package |

|------------|---------|

| TJ47300GDP | SOP8-PP |

### ABSOLUTE MAXIMUM RATINGS

| CHARACTERISTIC                       | SYMBOL                  | MIN. | MAX.                 | UNIT         |

|--------------------------------------|-------------------------|------|----------------------|--------------|

| Input Supply Voltage (Survival)      | V <sub>IN</sub>         | -0.3 | 6                    | V            |

| Enable Input Voltage (Survival)      | V <sub>EN</sub>         | -0.3 | 6                    | V            |

| Bias Supply Voltage (Survival)       | $V_{BIAS}$              | -0.3 | 6                    | V            |

| Output Voltage (Survival)            | V <sub>OUT</sub>        | -0.3 | V <sub>IN</sub> +0.3 | V            |

| Lead Temperature (Soldering, 5 sec)  | T <sub>SOL</sub>        |      | 260                  | $^{\circ}$ C |

| Storage Temperature Range            | T <sub>STG</sub>        | -65  | 150                  | $^{\circ}$ C |

| Operating Junction Temperature Range | $T_{JOPR}$              | -40  | 125                  | $^{\circ}$ C |

| Package Thermal Resistance *         | Θ <sub>JA-SOP8-PP</sub> | 68   |                      | °C/W         |

<sup>\*</sup> Calculated from package in still air, mounted to 2.6mm X 3.5mm(minimum foot print) 2 layer PCB without thermal vias per JESD51 standards.

# **ORDERING INFORMATION**

| Package | Order No.  | Description                           | Package Marking | Compliance         | Supplied As |

|---------|------------|---------------------------------------|-----------------|--------------------|-------------|

| SOP8-PP | TJ47300GDP | 3.0A, Enable,<br>Adjustable, Power OK | TJ47300G        | RoHS, Halogen Free | Reel        |

# **ORDERING INFORMATION (Continued)**

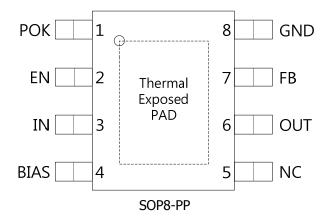

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin No. | Pin Name            | Pin Function                                                                                                                             |

|---------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | POK                 | Power OK Indication. This pin is an Open-drain output and is set high impedance once $V_{\text{OUT}}$ reaches 92% of its rating voltage. |

| 2       | EN                  | Enable Input. Pulling this pin below 0.4V turns the regulator off. Do not float                                                          |

| 3       | IN                  | Power Input. This pin is the drain input to the power device that supply current to output pin.                                          |

| 4       | BIAS                | Supply Input for Internal Circuit. Input Bias Voltage for powering all circuitry on the regulator except the output power TR.            |

| 5       | NC                  | No Connection.                                                                                                                           |

| 6       | OUT                 | Power Output. This pin is power output of the device.                                                                                    |

| 7       | FB                  | Feedback Voltage. A resistor divider from the output to GND is used to set the regulation voltage as $V_{\text{OUT}}$ = 0.8V x (1+R2/R1) |

| 8       | GND                 | Ground                                                                                                                                   |

| -       | Thermal Exposed PAD | Connect to Ground.                                                                                                                       |

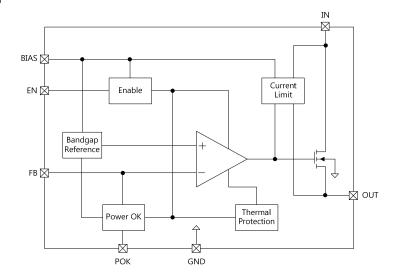

# **BLOCK DIAGRAM**

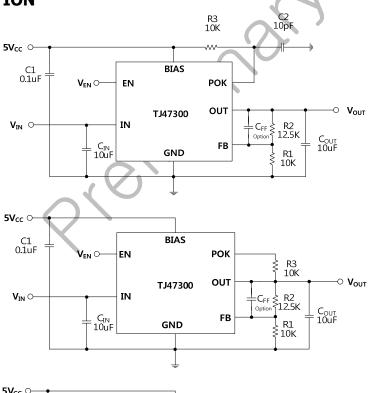

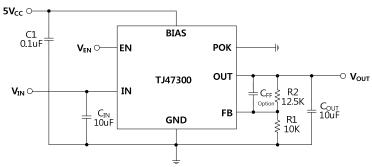

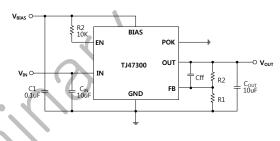

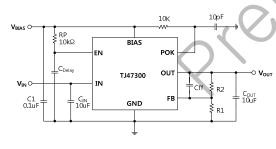

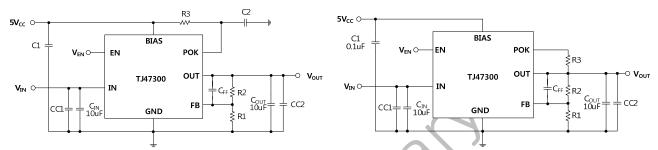

# **TYPICAL APPLICATION**

### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified:  $V_{BIAS} = 5V$ ,  $V_{IN} = V_{O(NOM)} + 1V$ ,  $V_{EN} = V_{BIAS}$ ,  $I_L = 10$  mA,  $T_A = 25$  °C.

| PARAMETER                                     |                                        | SYMBOL                  | TEST CONDITION                                                                                                                                                            | MIN.  | TYP. | MAX.  | UNIT |

|-----------------------------------------------|----------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| Power Input Voltage                           |                                        | V <sub>IN</sub>         | V <sub>OUT</sub> =V <sub>REF</sub>                                                                                                                                        | 1.25  | -    | 5.5   | ٧    |

| Bias Input Voltage                            |                                        | V <sub>BIAS</sub>       | V <sub>OUT</sub> =V <sub>REF</sub>                                                                                                                                        | 3.0   | -    | 5.5   | ٧    |

| Reference Voltage                             |                                        | V <sub>REF</sub>        | V <sub>BIAS</sub> =V <sub>IN</sub> =V <sub>EN</sub> =5.0V, I <sub>OUT</sub> =10mA,<br>V <sub>OUT</sub> =V <sub>REF</sub>                                                  | 0.784 | 0.8  | 0.816 | V    |

| V <sub>IN</sub> Line Regulation <sup>()</sup> | Note 1)                                | $\Delta V_{LINE(IN)}$   | V <sub>OUT</sub> +1V <v<sub>IN&lt;5.5V, I<sub>OUT</sub>=10mA</v<sub>                                                                                                      | -     | 0.02 | 0.10  | %/V  |

| V <sub>BIAS</sub> Line Regulation             | ງ <sup>(Note 2)</sup>                  | $\Delta V_{LINE(BIAS)}$ | V <sub>IN</sub> =3.3V, I <sub>OUT</sub> =10mA, V <sub>OUT</sub> =V <sub>REF</sub>                                                                                         | -     | 0.02 | 0.10  | %/V  |

| Load Regulation <sup>(Note 1, 3)</sup>        |                                        | $\Delta V_{LOAD}$       | $ \begin{array}{lll} 10\text{mA} < I_{L} < 3\text{A}, & V_{\text{CNTL}} = V_{\text{IN}} = V_{\text{EN}} = 5.0\text{V}, \\ V_{\text{OUT}} = V_{\text{REF}} & \end{array} $ | -     | 0.20 | 0.75  | %    |

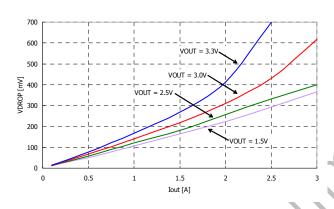

| Dropout Voltage                               |                                        |                         | $I_L = 1.0A$ , $V_{BIAS} = V_{EN} = 5.0V$ , $V_{OUT} = V_{REF}$                                                                                                           | -     | 120  | 150   | mV   |

|                                               |                                        | $V_{DROP}$              | $I_L = 2.0A$ , $V_{BIAS} = V_{EN} = 5.0V$ , $V_{OUT} = V_{REF}$                                                                                                           | -     | 240  | 300   |      |

|                                               |                                        |                         | $I_L = 3.0A$ , $V_{BIAS} = V_{EN} = 5.0V$ , $V_{OUT} = V_{REF}$                                                                                                           | -     | 380  | 450   |      |

|                                               |                                        | $I_{GND1}$              | I <sub>L</sub> = 10mA                                                                                                                                                     | -     | 0.1  | 1.0   | mA   |

| Ground Pin Current <sup>(</sup>               | Ground Pin Current <sup>(Note 4)</sup> |                         | I <sub>L</sub> = 3.0 A                                                                                                                                                    | -     | 0.1  | 1.0   | mA   |

|                                               |                                        |                         | V <sub>EN</sub> < 0.4 V, POK=open <sup>(Note5)</sup>                                                                                                                      | -     | -    | 150   | uA   |

| Enable Threshold                              | Logic High                             | V <sub>IH</sub>         | Output=High                                                                                                                                                               | 2.0   | ı    | -     | V    |

| Enable Threshold                              | Logic Low                              | V <sub>IL</sub>         | Output=Low                                                                                                                                                                | -     | -    | 0.4   | V    |

| EN Input Current I                            |                                        | I <sub>EN</sub>         | V <sub>EN</sub> =V <sub>CNTL</sub> =5.0V                                                                                                                                  | -     | -    | 0.5   | uA   |

| FB Power OK Threshold V <sub>POKTH</sub>      |                                        | V <sub>POKTH</sub>      | I <sub>OUT</sub> =0A, V <sub>CNTL</sub> =V <sub>IN</sub> =V <sub>EN</sub> =5.0V, V <sub>OUT</sub> =V <sub>REF</sub>                                                       | -     | 90   | -     | %    |

| Power OK Hysteresis V <sub>POKHYS</sub>       |                                        | V <sub>POKHYS</sub>     | I <sub>OUT</sub> =0A, V <sub>CNTL</sub> =V <sub>IN</sub> =V <sub>EN</sub> =5.0V, V <sub>OUT</sub> =V <sub>REF</sub>                                                       | -     | 10   | -     | %    |

| OCP Threshold Level I <sub>OCP</sub>          |                                        | I <sub>OCP</sub>        | V <sub>CNTL</sub> =V <sub>IN</sub> =V <sub>EN</sub> =5.0V, V <sub>OUT</sub> =V <sub>REF</sub>                                                                             | -     | 4.5  | -     | Α    |

| Thermal Shutdown Temperature T <sub>SD</sub>  |                                        | T <sub>SD</sub>         |                                                                                                                                                                           | -     | 165  | -     | °C   |

| Thermal Shutdown Hysteresis $\Delta T_{SD}$   |                                        | $\Delta T_{SD}$         |                                                                                                                                                                           | -     | 10   | -     | C    |

Note 1. Output voltage line regulation is defined as the change in output voltage from the nominal value due to change in the input line voltage. Output voltage load regulation is defined as the change in output voltage from the nominal value due to change in load current.

Note 2. Output voltage line regulation is defined as the change in output voltage from the nominal value due to change in the bias line voltage.

Note 3. Regulation is measured at constant junction temperature by using a 10ms current pulse. Devices are tested for load regulation in the load range from 10mA to 3.0A

Note 4.  $I_{\text{GND}} = I_{\text{BIAS}} + (I_{\text{IN}} - I_{\text{OUT}})$ . The total current drawn from the supply is the sum of the load current plus the ground current.

Note 5. When POK pin is applied to  $V_{BIAS}$  through the resistor R3,  $I_{GND2}$  should be added to the bias current ( $V_{BIAS} - V_{POK}$ ) / R3.

# **TYPICAL OPERATING CHARACTERISTICS**

# - TEST Circuit

Circuit #3

Circuit #4

Circuit #5

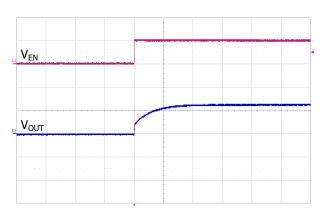

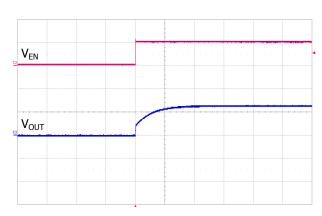

VEN: 5V/div, VOUT: 2V/div, 200us/div

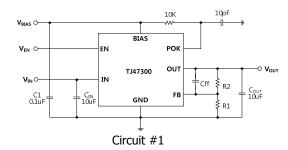

### Start Up @ Iout=10mA, Circuit #1

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V, V<sub>BIAS</sub>=5.0V)

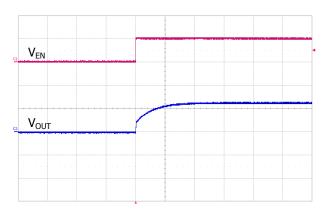

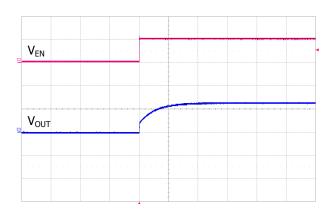

VEN: 5V/div, VOUT: 2V/div, 200us/div

# Start Up @ Iout=3.0A, Circuit #1

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V, V<sub>BIAS</sub>=5.0V)

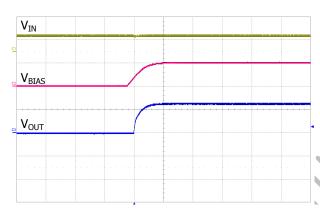

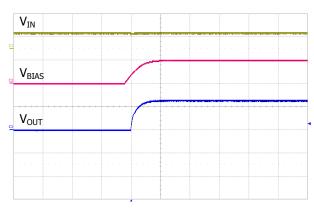

VIN: 5V/div, VBIAS: 5V/div, VOUT: 2V/div, 500us/div

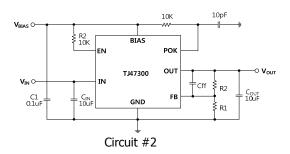

# Start Up with $V_{\text{BIAS}}$ @ Iout=10mA, Circuit #2

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V)

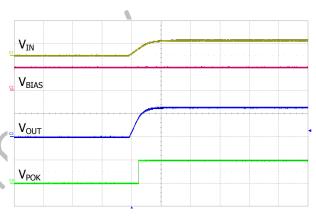

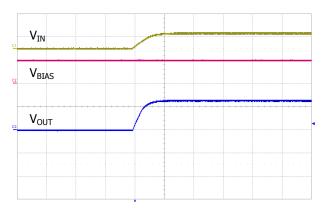

VIN: 5V/div, VBIAS: 5V/div, VOUT: 2V/div, VPOK: 5V/div, 500us/div

# Start Up with V<sub>IN</sub> @ Iout=10mA, Circuit #2

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>BIAS</sub>=5.0V)

VEN: 5V/div, VOUT: 2V/div, 200us/div

### Start Up @ Iout=10mA, Circuit #3

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V, V<sub>BIAS</sub>=5.0V)

VEN: 5V/div, VOUT: 2V/div, 200us/div

### Start Up @ Iout=3.0A, Circuit #3

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V, V<sub>BIAS</sub>=5.0V)

VIN: 5V/div, VBIAS: 5V/div, VOUT: 2V/div, 500us/div

# Start Up with V<sub>BIAS</sub> @ Iout=10mA, Circuit #4

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V)

VIN: 5V/div, VBIAS: 5V/div, VOUT: 2V/div, 500us/div

### Start Up with V<sub>IN</sub> @ Iout=10mA, Circuit #4

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>BIAS</sub>=5.0V)

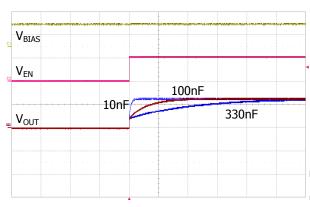

VBIAS: 5V/div, VEN: 5V/div, OUT: 2V/div, 2ms/div

### Start Up @ Iout=10mA, Circuit #1

(Cff is varied, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V, V<sub>BIAS</sub>=5.0V)

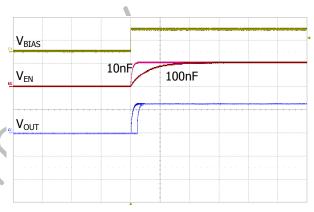

VBIAS: 5V/div, VEN: 5V/div, OUT: 2V/div, 2ms/div

### Start Up @ Iout=10mA, Circuit #5

(Cdelay is varied, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V)

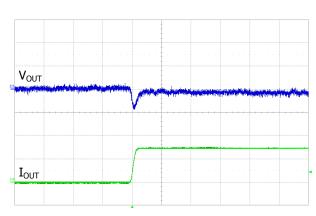

VOUT: 20mV/div, IOUT: 2A/div, 100us/div

### **Load Transient Response**

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V, V<sub>BIAS</sub>=5.0V)

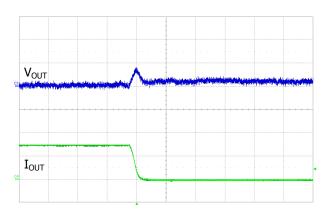

VOUT: 20mV/div, IOUT: 2A/div, 100us/div

### **Load Transient Response**

(Cff=10nF, R2=10k $\Omega$ , R1=4.7k $\Omega$ , V<sub>IN</sub>=3.5V, V<sub>BIAS</sub>=5.0V)

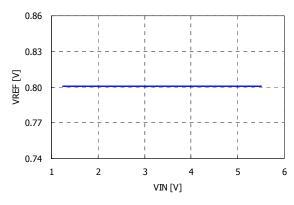

$V_{REF}$  vs.  $V_{IN}$  @  $V_{BIAS}$ =5.5V

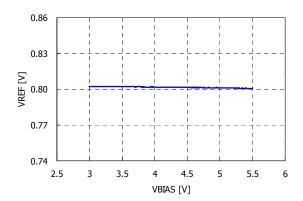

$V_{REF}$  vs.  $V_{BIAS}$  @  $V_{IN}$ =5.5V

**Dropout Voltage**

### APPLICATION INFORMATION

The TJ47300 is a high performance, low dropout linear regulator, designed for high current application that requires fast transient response. The TJ47300 operates from two input supply voltages, significantly reducing dropout voltage. The TJ47300 is designed so that a minimum of external component are necessary.

### **Bias Supply Voltage**

The TJ47300 control circuitry is supplied by the BIAS pin which requires a very low bias current even at the maximum output current level. A bypass capacitor on the bias pin is recommended to improve the performance of the TJ47300 during line and load transient. A small ceramic capacitor from BIAS pin to ground reduces high frequency noise that could be injected into the control circuitry from the bias rail. In practical applications, a 1uF capacitor and smaller valued capacitors such as 0.01uF or 0.001uF in parallel with that larger capacitor may be used to decouple the bias supply. The BIAS input voltage must be 2.1V above the output voltage, with a minimum BIAS input voltage of 3.0V.

### **Adjustable Regulator Design**

An adjustable output device has output voltage range of 0.8V to 3.3V. To obtain a desired output voltage, the following equation can be used two external resistors as presented in the typical application circuit. The resistor values are given by;

$$R_1 = R_2 \times \left( \frac{V_{OUT}}{0.8} - 1 \right)$$

It is suggested to use R1 values lower than  $10k\Omega$  to obtain better load transient performances. Even, higher values up to  $100~k\Omega$  are suitable.

### **Enable**

The TJ47300 feature an active high Enable input (EN) that allows on/off control of the regulator. The enable function of TJ47300 has hysteresis characteristics. Pulling  $V_{EN}$  lower than 0.4V disables the chip. Pulling  $V_{EN}$  higher than 2.0V enables the output voltage.

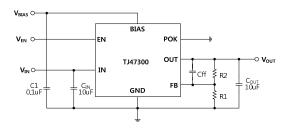

### **Supply Power Sequencing**

In common applications where the power on transient of  $V_{IN}$  and  $V_{BIAS}$  voltages are not particularly fast (Tr > 100us), no power sequencing is required. Where voltage transient input is very fast(Tr<100us), it is recommended to have the  $V_{IN}$  voltage present before or, at least, at the same time as the  $V_{BIAS}$  voltage in order to avoid over voltage spikes during the power on transient.

### **Output Capacitors**

The TJ47300 requires an of output capacitance to maintain stability. The output capacitor must meet both requirements for minimum amount of capacitance and ESR in all LDOs application. The TJ47300 is designed specifically to work with low ESR ceramic output capacitor in space-saving and performance consideration. Using a ceramic capacitor which value is at least 10uF on the TJ47300 output ensures stability. Output capacitor of larger capacitance can reduce noise and improve load transient response, stability, and PSRR. A minimum ceramic capacitor over than 10uF should be very closely placed to the output voltage pin of the TJ47300.

### **Input Capacitor**

A large bulk capacitance over than 10uF should be closely placed to the input supply pin of the TJ47300 to ensure that the input supply voltage does not sag. Also a minimum of 10uF ceramic capacitor is recommended to be placed directly next to the IN pin. It allows for the device being some distance from any bulk capacitor on the rail. Additionally, input droop due to load transients is reduced, improving load transient response. Additional capacitance may be added if required by the application.

# **Decoupling (Bypass) Capacitor**

In very electrically noisy environments, it is recommended that additional ceramic capacitors be placed from VIN to GND. The use of multiple lower value ceramic capacitors in parallel with output capacitor also allows to achieve better transient performance and stability if required by the application. (See Fig.1)

### **Feed-Forward Capacitor**

To get the higher PSRR than the inherent performance of TJ47300, it is recommended that additional ceramic feed-forward capacitor be placed from OUT pin to FB pin. The capacitance of feed-forward capacitor with range of 10pF to 1uF allows to achieve better PSRR performance when required by the application. (See Fig.1)

Fig. 1 Application with Decoupling & Feed-Forward Capacitor

### **Maximum Output Current Capability**

The TJ47300 can deliver a continuous current of 3.0A over the full operating junction temperature range. However, the output current is limited by the restriction of power dissipation which differs from packages. A heat sink may be required depending on the maximum power dissipation and maximum ambient temperature of application. With respect to the applied package, the maximum output current of 3.0A may be still undeliverable due to the restriction of the power dissipation of TJ47300. Under all possible conditions, the junction temperature must be within the range specified under operating conditions. The temperatures over the device are given by:

$$T_C = T_A + P_D X \theta_{CA} / T_J = T_C + P_D X \theta_{JC} / T_J = T_A + P_D X \theta_{JA}$$

where  $T_J$  is the junction temperature,  $T_C$  is the case temperature,  $T_A$  is the ambient temperature,  $P_D$  is the total power dissipation of the device,  $\theta_{CA}$  is the thermal resistance of case-to-ambient,  $\theta_{JC}$  is the thermal resistance of junction-to-case, and  $\theta_{JA}$  is the thermal resistance of junction to ambient.

The total power dissipation of the device is given by:

$$P_D = P_{IN} - P_{OUT} = \{(V_{IN} X I_{IN}) + (V_{BIAS} X I_{BIAS})\} - (V_{OUT} X I_{OUT})$$

The maximum allowable temperature rise ( $T_{Rmax}$ ) depends on the maximum ambient temperature ( $T_{Amax}$ ) of the application, and the maximum allowable junction temperature ( $T_{Jmax}$ ):

$$T_{Rmax} = T_{Jmax} - T_{Amax}$$

The maximum allowable value for junction-to-ambient thermal resistance,  $\theta_{JA}$ , can be calculated using the formula:

$$\theta_{1A} = T_{Rmax} / P_D = (T_{1max} - T_{Amax}) / P_D$$

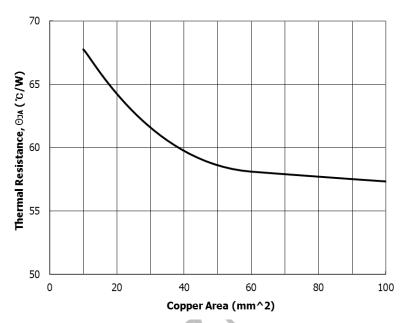

TJ47300 is available in SOP8-PP package. The thermal resistance depends on amount of copper area or heat sink, and on air flow.

If proper cooling solution such as heat sink, copper plane area, air flow is applied, the maximum allowable power dissipation could be increased. However, if the ambient temperature is increased, the allowable power dissipation would be decreased.

The  $\theta_{JA}$  could be decreased with respect to the copper plane area. So, the specification of maximum power dissipation for an application is fixed, the proper copper plane area could be estimated by following graphs. Wider copper plane area leads lower  $\theta_{JA}$ .

The maximum allowable power dissipation is also influenced by the ambient temperature. With the above  $\theta_{JA}$ -Copper plane area relationship, the maximum allowable power dissipation could be evaluated with respect to the ambient temperature. As shown in graph, the higher copper plane area leads  $\theta_{JA}$ . And the higher ambient temperature leads lower maximum allowable power dissipation.

# 2 1.8 1.6 1.4 2 1.2 1.2 0 0 0 0 0 0 0 100 120 Ambient Temperature, T<sub>A</sub>(°C)

Power Disspation(PD) vs. Ambient Temperature(TA)

The graph above is valid for the thermal impedance specified in the Absolute Maximum Ratings section on page 1.

The  $\theta_{JA}$  could be decreased with respect to the copper plane area. So, the specification of maximum power dissipation for an application is fixed, the proper plane area could be estimated by following graphs. Wider copper plane area leads lower  $\theta_{JA}$ .

# Thermal Resistance( $\Theta JA$ ) vs. Copper Area

The maximum allowable power dissipation is also influenced by the ambient temperature. With the  $\theta_{JA}$ -Copper plane area relationship, the maximum allowable power dissipation could be evaluated with respect to the ambient temperature. As shown in graph, the higher copper plane area leads  $\theta_{JA}$ . And the higher ambient temperature leads lower maximum allowable power dissipation.

# **PRELIMINARY REVISION NOTICE**

The information in this datasheet can be revised without any notice.