SBVS127E -MARCH 2009-REVISED JULY 2017

TLC5951

# TLC5951 24-Channel, 12-Bit PWM LED Driver With 7-Bit Dot Correction and 3-Group, 8-Bit Global Brightness Control

#### **Features**

- 24-Channel Constant-Current Sink Output

- Current Capability: 40 mA

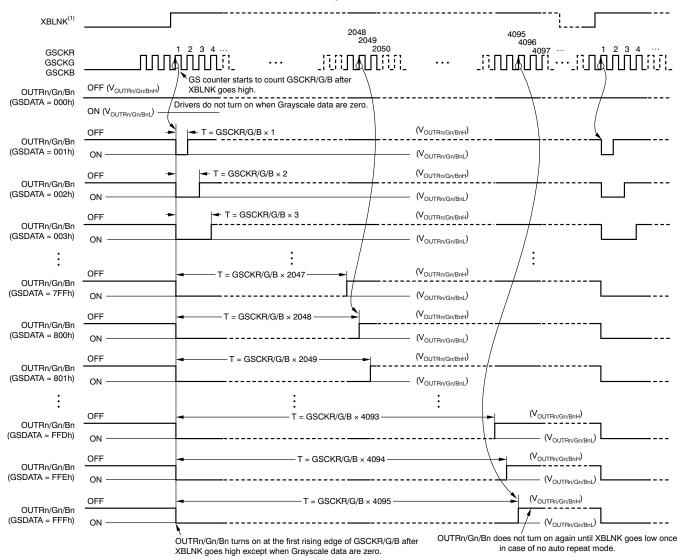

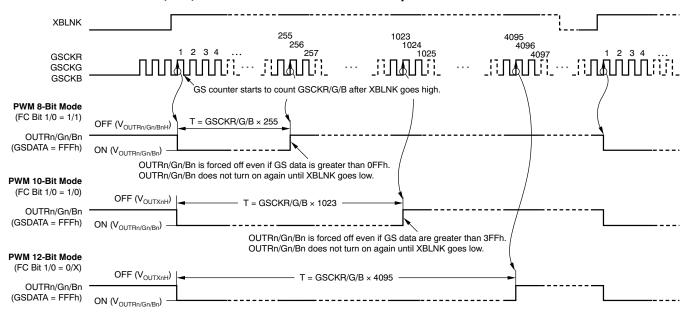

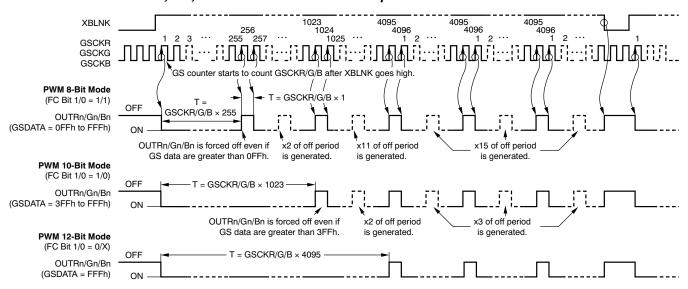

- Selectable Grayscale (GS) Control With PWM: 12-Bit (4096 Step), 10-Bit (1024 Step), 8-Bit (256

- Three Independent Grayscale Clocks for Three Color Groups

- Dot Correction (DC): 7-Bit (128 Step)

- Global Brightness Control (BC) for Each Color Group: 8-Bit (256 Step)

- Auto Display Repeat Function

- Independent Data Port for GS and BC and DC Data

- Communication Path Between Each Data Port

- LED Power-Supply Voltage up to 15 V

- $V_{CC} = 3 \text{ V to } 5.5 \text{ V}$

- Constant-Current Accuracy:

- Channel-to-Channel = ±1.5%

- Device-to-Device = ±3%

- CMOS Logic Level I/O

- Data Transfer Rate: 30 MHz

- 33-MHz Grayscale Control Clock

- Continuous Base LED-Open Detection (LOD)

- Continuous Base LED-Short Detection (LSD)

- Thermal Shutdown (TSD) With Auto Restart

- Grouped Delay to Prevent Inrush Current

- Operating Ambient Temperature: -40°C to 85°C

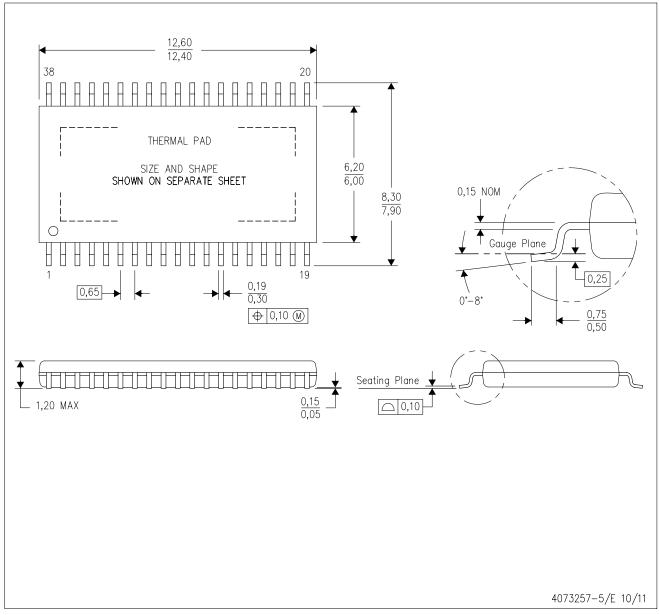

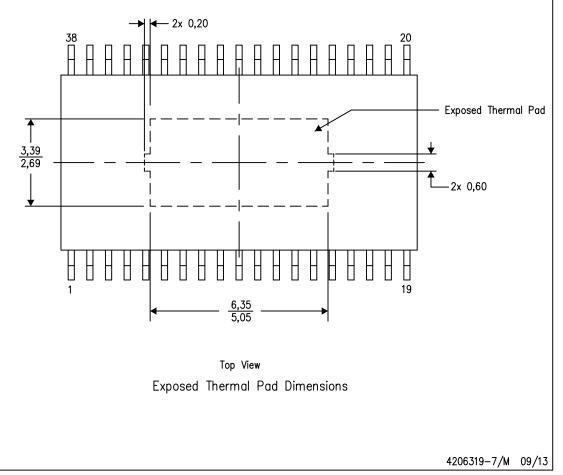

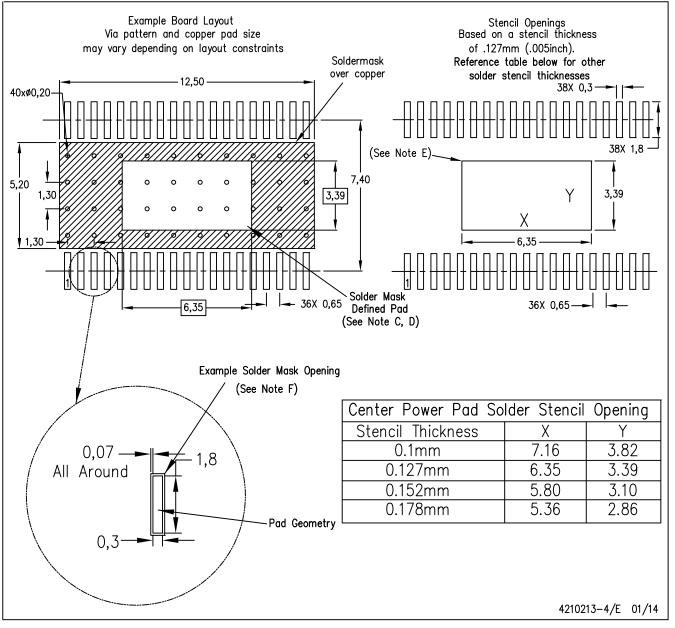

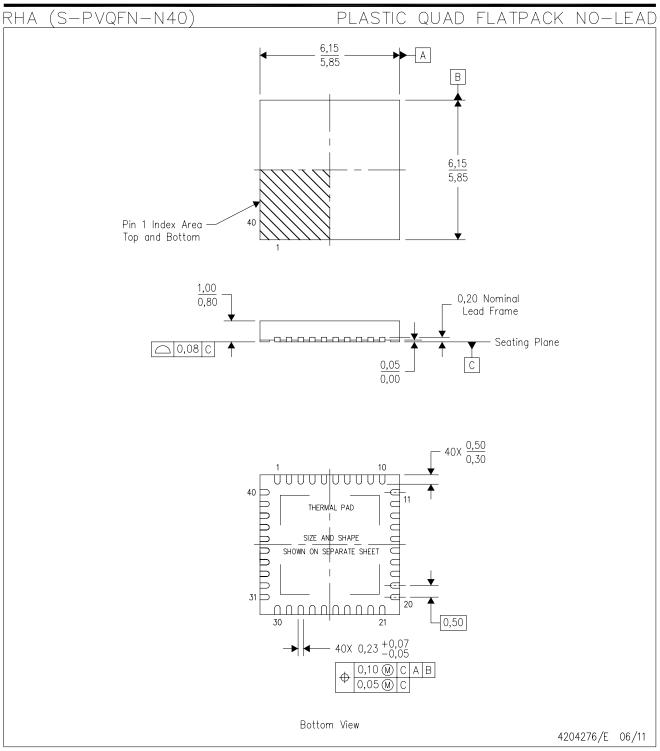

- Packages: HTSSOP-38, QFN-40

# **Applications**

- Full-Color LED Displays

- LED Signboards

# 3 Description

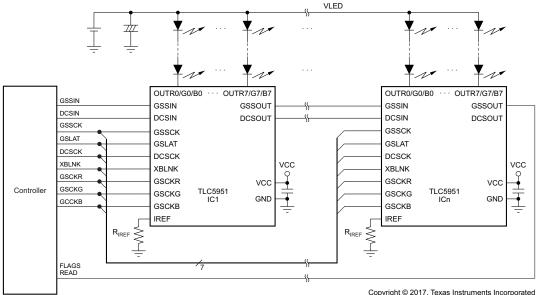

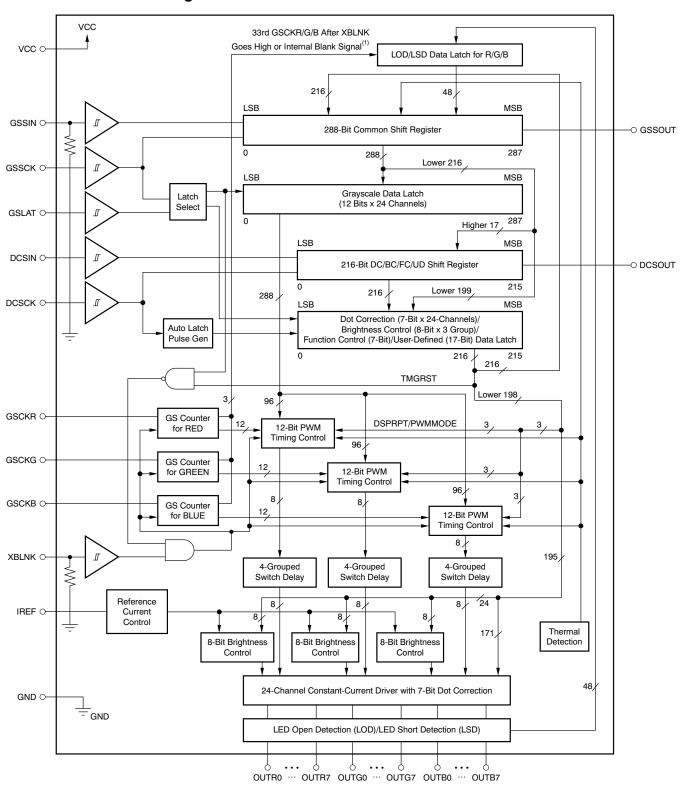

The TLC5951 device is a 24-channel, constantcurrent sink driver. Each channel has an individuallyadjustable, 4096-step, pulse-width modulation (PWM) grayscale (GS) brightness control and 128-step constant-current dot correction (DC). The dot correction adjusts brightness deviation between channels and other LED drivers. The output channels are grouped into three groups of eight channels. Each channel group has a 256-step global brightness control (BC) function and an individual grayscale clock input.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)    |  |  |

|-------------|-------------|--------------------|--|--|

|             | HTSSOP (38) | 12.50 mm × 6.20 mm |  |  |

| TLC5951     | VQFN (40)   | 6.00 × 6.00 mm     |  |  |

|             | WQFN (40)   | 6.00 × 6.00 mm     |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

# Typical Application Circuit (Multiple Daisy-Chained TLC5951 Devices)

## **Table of Contents**

| 1      | Features                                                                                                                      |    | 8.1 Pin Equivalent Input and Output Schematic Diagrams                     | 20             |

|--------|-------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------|----------------|

| 3      | Applications                                                                                                                  | 9  | 8.2 Test Circuits                                                          | 20             |

| 5      | Revision History                                                                                                              | ·  | 9.1 Overview                                                               | 2 <sup>,</sup> |

| 6<br>7 | Pin Configuration and Functions                                                                                               |    | 9.3 Feature Description                                                    | 23             |

|        | 7.2 ESD Ratings                                                                                                               | 10 | 10.1 Receiving Notification of Documentation Upda 10.2 Community Resources | ates 3         |

|        | 7.4 Thermal Information       7         7.5 Electrical Characteristics       8         7.6 Switching Characteristics       10 |    | 10.3 Trademarks                                                            | 3              |

| 8      | 7.7 Typical Characteristics                                                                                                   | 11 | Mechanical, Packaging, and Orderable Information                           |                |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

|    |                                                                                                                                                                                                               | Page            |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| •  | Added WQFN package to the Device Information table                                                                                                                                                            | 1               |

| •  | Changed Typical Application Circuit diagram                                                                                                                                                                   | 1               |

| •  | Changed ordering of the OUTxy pin numbers in the Pin Functions table to match the pinout diagram                                                                                                              | 5               |

| •  | Deleted ESD rating specifications from the Absolute Maximum Ratings table                                                                                                                                     | 6               |

| •  | Added ESD Ratings table to the data sheet                                                                                                                                                                     | 6               |

| •  | Added Thermal Information table to the data sheet                                                                                                                                                             | 7               |

| •  | Deleted Dissipation Ratings table from the data sheet                                                                                                                                                         | <mark>7</mark>  |

|    |                                                                                                                                                                                                               |                 |

| Cr | anges from Revision C (August 2013) to Revision D                                                                                                                                                             | Page            |

| •  | Added $\Delta I_{OLC5}$ and $\Delta I_{OLC6}$ parameters to Electrical Characteristics table                                                                                                                  | 9               |

| •  | Added footnote 6 to footnote 9 in Electrical Characteristics table                                                                                                                                            | _               |

|    | Added 100thole 6 to 100thole 9 III Electrical Characteristics table                                                                                                                                           | 9               |

| Ch | anges from Revision B (December 2009) to Revision C                                                                                                                                                           |                 |

| Ch |                                                                                                                                                                                                               | Page            |

| _  | anges from Revision B (December 2009) to Revision C                                                                                                                                                           | Page 7          |

| •  | anges from Revision B (December 2009) to Revision C  Changed AC Characteristics, t <sub>WH0</sub> and t <sub>WL0</sub> parameter associated pin names                                                         | Page 7          |

| •  | anges from Revision B (December 2009) to Revision C  Changed AC Characteristics, t <sub>WH0</sub> and t <sub>WL0</sub> parameter associated pin names  Updated Figure 3.                                      | Page 7 12 13    |

| •  | anges from Revision B (December 2009) to Revision C  Changed AC Characteristics, t <sub>WH0</sub> and t <sub>WL0</sub> parameter associated pin names  Updated Figure 3.  Updated Figure 4                    | Page 7 12 13 15 |

| •  | anges from Revision B (December 2009) to Revision C  Changed AC Characteristics, t <sub>WH0</sub> and t <sub>WL0</sub> parameter associated pin names  Updated Figure 3.  Updated Figure 4.  Updated Figure 7 | Page            |

Submit Documentation Feedback

Changes from Revision A (April 2009) to Revision B

Copyright © 2009–2017, Texas Instruments Incorporated

**Page**

| Changed description for bits 175–168, 183–176, and 191–184 in Table 13  Changes from Original (March 2009) to Revision A                             | 36               |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| Changes from Original (March 2009) to Revision A                                                                                                     | Page             |

|                                                                                                                                                      | · ug             |

| Changed T <sub>SU3</sub> minimum specification to 40 ns in the Recommended Operating Conditions table                                                | 7                |

| <ul> <li>Changed V<sub>O</sub> minimum specification to maximum specification in the Recommended Operating Conditions table</li> </ul>               |                  |

| <ul> <li>Changed I<sub>OH</sub> minimum specification to maximum specification in the Recommended Operating Conditions table</li> </ul>              |                  |

| <ul> <li>Changed I<sub>OL</sub> minimum specification to maximum specification in the Recommended Operating Conditions table</li> </ul>              | 7                |

| <ul> <li>Changed I<sub>OLC</sub> minimum specification to maximum specification in the Recommended Operating Conditions table</li> </ul>             | 7                |

| • Changed f <sub>CLK</sub> (SCLK) minimum specification to maximum specification in the Recommended Operating Conditions tab                         | e <mark>7</mark> |

| Changed f <sub>CLK (GSCKR/G/B)</sub> minimum specification to maximum specification in the <i>Recommended Operating Conditions</i> table             | 3                |

| Changed I <sub>CC2</sub> typical value to 6 mA in the <i>Electrical Characteristics</i> table                                                        | 8                |

| <ul> <li>Changed I<sub>CC3</sub> typical value to 12 mA and maximum value to 27 mA in the Electrical Characteristics table</li> </ul>                | 8                |

| <ul> <li>Changed I<sub>CC4</sub> typical value to 21 mA and maximum value to 55 mA in the Electrical Characteristics table</li> </ul>                | 8                |

| <ul> <li>Changed ∆I<sub>OLC2</sub> typical value to ±1% in the Electrical Characteristics table</li> </ul>                                           | 8                |

| Changed ∆I <sub>OLC3</sub> typical value to ±0.5% in the <i>Electrical Characteristics</i> table                                                     | 8                |

| Changed fourth paragraph of Maximum Constant Sink Current Value section to reference correct graph                                                   | 24               |

| Changed DC function adjustment range description to reflect proper adjustment range for each control in <i>Dot Correction (DC) Function</i> section  | 24               |

| Changed brightness control to dot correction data in 288-Bit Common Shift Register section                                                           | 30               |

| <ul> <li>Corrected number of bits contained within the DC, BC, FC, and UD shift register in the DC, BC, FC, and UD Shift Register section</li> </ul> | 32               |

| Corrected typo about which bits are written in the DC, BC, FC, and UD Data Latch section                                                             | 32               |

| Corrected percentage of adjustment rage selected in the Dot Correction Data Latch section                                                            | 32               |

| Deleted second paragraph of Status Information Data (SID) section                                                                                    | 34               |

| Updated LOD bit = 1 condition description in the Continuous Base LOD, LSD, and TEF section                                                           | 37               |

DCSCK

XBLNK

VCC

IREF

Not to scale

22

GND

# 5 Description (Continued)

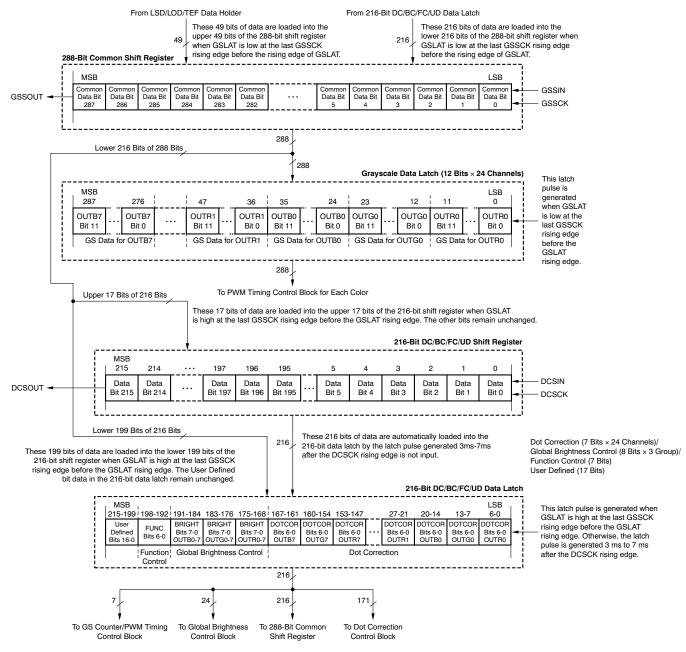

GS, DC, and BC data are accessible via a serial interface port. DC and BC can be programmed via a dedicated serial interface port.

The TLC5951 device has three error-detection circuits for LED-open detection (LOD), LED-short detection (LSD), and thermal error flag (TEF). LOD detects a broken or disconnected LED, LSD detects a shorted LED, and TEF indicates an overtemperature condition.

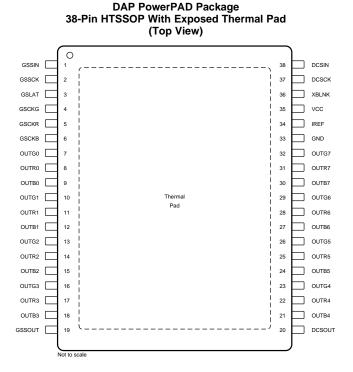

# 6 Pin Configuration and Functions

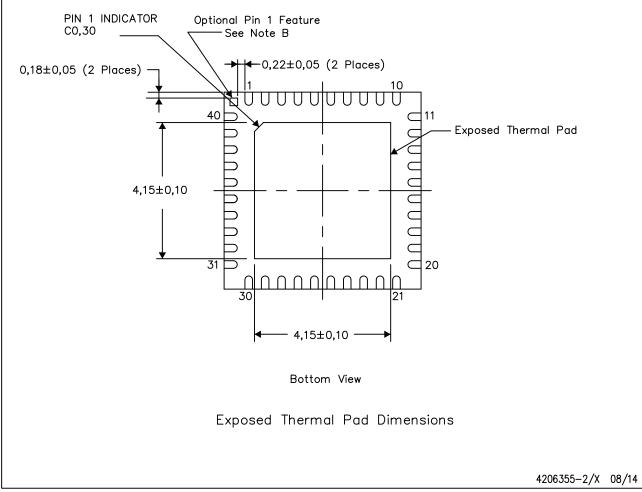

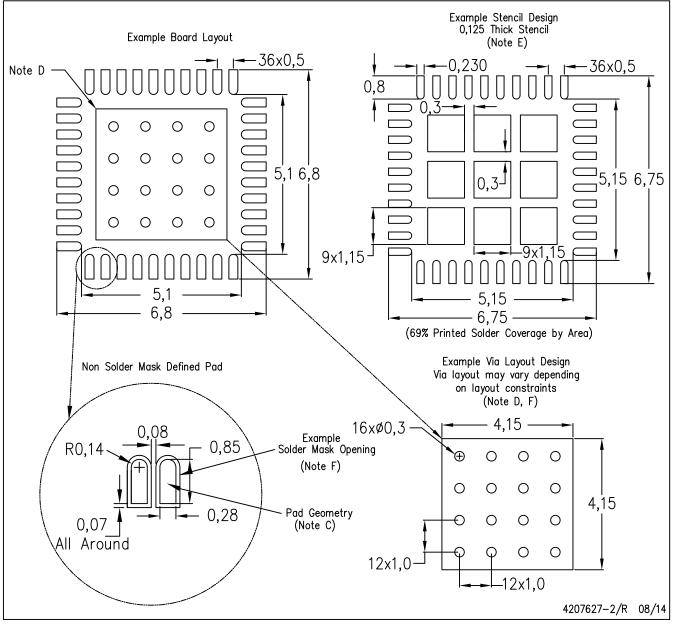

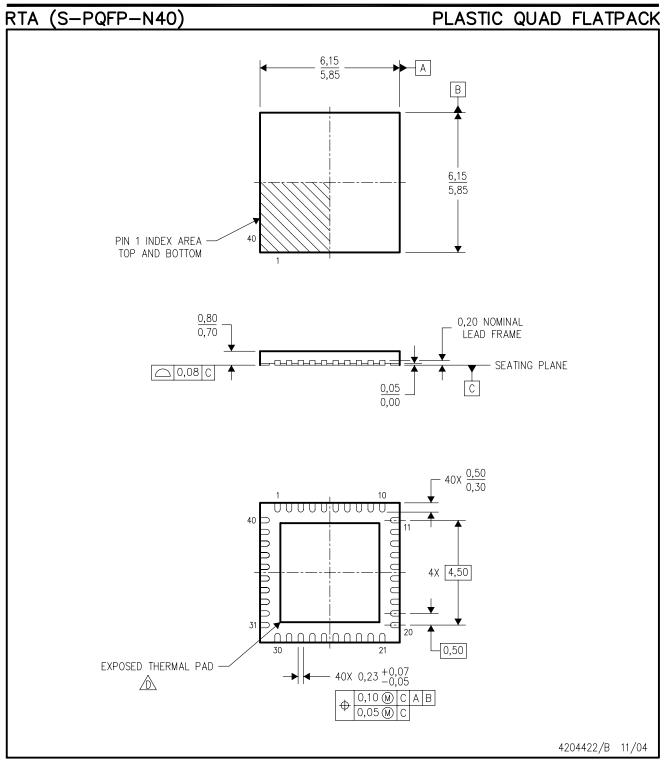

#### RHA and RTA Packages 40-Pin VQFN and WQFN With Exposed Thermal Pads (Top View) OUTR2 OUTB2 OUTG2 OUTB1 OUTB0 **OUTRO** OUTG0 GSCKB OUTR1 OUTG1 35 34 33 32 36 OUTG3 30 [ GSCKR OUTR3 GSCKG 29 OUTB3 GSLAT NC GSSCK GSSOUT GSSIN DCSOUT

15

OUTB6

19 19 20

OUTB7

NC = no internal connection

NC

OUTB4

OUTR4

OUTG4

#### **Pin Functions**

| PIN      |     |          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|----------|-----|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. |     | 0.       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| NAIVIE   | DAP | RHA, RTA |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| DCSCK    | 37  | 24       | I   | Serial-data shift clock for the 216-bit DC, BC, FC, and UD shift register. Data present on DCSIN are shifted into the LSB of the shift register with the DCSCK rising edge. Data in the shift register are shifted toward the MSB at each DCSCK rising edge. The MSB data of the register appear on DCSOUT. The 216-bit data in the shift register are automatically copied to the DC, BC, FC, and UD data latch 3 ms to 7 ms following the last rising edge after DCSCK stops switching. |  |  |

| DCSIN    | 38  | 25       | I   | Serial data input for the 216-bit DC, BC, FC, and UD shift register. DCSIN is connected to the LSB of the shift register.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| DCSOUT   | 20  | 6        | 0   | Serial data output of the 216-bit shift register. DCSOUT is connected to the MSB of the shift register. Data are clocked out at the rising edge of DCSCK.                                                                                                                                                                                                                                                                                                                                 |  |  |

| GND      | 33  | 20       | _   | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| GSCKB    | 6   | 31       | I   | Reference clock for the GS PWM control for the BLUE LED output group. When XBLNK is high, each GSCKR rising edge increments the BLUE LED GS counter for PWM control.                                                                                                                                                                                                                                                                                                                      |  |  |

| GSCKG    | 4   | 29       | I   | Reference clock for the GS PWM control for the GREEN LED output group. When XBLNK is high, each GSCKR rising edge increments the GREEN LED GS counter for PWM control.                                                                                                                                                                                                                                                                                                                    |  |  |

# Pin Functions (continued)

| PIN             |                                     |                                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-----------------|-------------------------------------|-------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME            | N                                   | 0.                                  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| INAIVIE         | DAP                                 | RHA, RTA                            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| GSCKR           | 5                                   | 30                                  | I   | Reference clock for the GS pulse-width modulation (PWM) control for the RED LED output group. When XBLNK is high, each GSCKR rising edge increments the RED LED GS counter for PWM control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| GSLAT           | 3                                   | 28                                  | I   | Data in the 288-bit common shift register are copied to the GS data latch or to the DC, BC, and FC data latch at the rising edge of GSLAT. The level of GSLAT at the last GSSCK before the GSLAT rising edge determines which of the two latches the data are transferred into. When GSLAT is low at the last GSSCK rising edge, all 288 bits in the common shift register are copied to the GS data latch. When GSLAT is high at the last GSSCK rising edge, bits 0–198 are copied to the DC, BC, and FC data latch and bits 199–215 are copied to the 216-bit DC, BC, FC, and UD shift register. The GSLAT rising edge for a DC, BC, FC, and UD data write must be input more than 7 ms after a data write through the DCSIN pin. |  |

| GSSCK           | 2                                   | 27                                  | I   | Serial data shift clock for the 288-bit common shift register for GS, DC, BC, and F data. Data present on GSSIN are shifted into the LSB of the shift register with the rising edge of GSSCK. Data in the shift register are shifted toward the MSB at each rising edge of GSSCK. The MSB data of the shift register appear on GSSOUT.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| GSSIN           | 1                                   | 26                                  | I   | Serial data input for the 288-bit common shift register for grayscale (GS), dot correction (DC), global brightness control (BC), and function control (FC) data. GSSIN is connected to the LSB of the 288-bit common shift register. This pin is internally pulled to GND with a 500-k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| GSSOUT          | 19                                  | 5                                   | 0   | Serial data output of the 288-bit common shift register. LED-open detection (LOD), LED-short detection (LSD), thermal error flag (TEF), and 199-bit data in the DC, BC, and FC data latch can be read via GSSOUT. GSSOUT is connected to the MSB of the shift register. Data are clocked out at the rising edge of GSSCK.                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| IREF            | 34                                  | 21                                  | I/O | A resistor connected between IREF and GND sets the maximum current for all constant-current outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| NC              | _                                   | 4, 7                                | _   | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| OUTB0-<br>OUTB7 | 9, 12, 15,<br>18, 21, 24,<br>27, 30 | 34, 37, 40,<br>3, 8, 11, 14,<br>17  | 0   | Constant-current outputs for the BLUE LED group. These outputs are controlled with the GSCKB clock signal.  The BLUE LED group is divided into four subgroups: OUTB0 and OUTB4, OUTB1and OUTB5, OUTB2 and OUTB6, and OUTB3 and OUTB7.  Each paired output turns on or off with 24 ns (typ) time delay between other paired outputs. Multiple outputs can be tied together to increase the constant-current capability. Different voltages can be applied to each output.                                                                                                                                                                                                                                                            |  |

| OUTG0-<br>OUTG7 | 7, 10, 13,<br>16, 23, 26,<br>29, 32 | 32, 35, 38,<br>1, 10, 13,<br>16, 19 | 0   | Constant-current outputs for the GREEN LED group. These outputs are controlled with the GSCKG clock signal.  The GREEN LED group is divided into four subgroups: OUTG0 and OUTG4, OUTG1 and OUTG5, OUTG2 and OUTG6, and OUTG3 and OUTG7.  Each paired output turns on or off with 24 ns (typ) time delay between other paired outputs. Multiple outputs can be tied together to increase the constant-current capability. Different voltages can be applied to each output.                                                                                                                                                                                                                                                         |  |

| OUTR0-<br>OUTR7 | 8, 11, 14,<br>17, 22, 25,<br>28, 31 | 33, 36, 39,<br>2, 9, 12, 15,<br>18  | 0   | Constant-current outputs for the RED LED group. These outputs are controlled with the GSCKR clock signal.  The RED LED group is divided into four subgroups: OUTR0 and OUTR4, OUTR1 and OUTR5, OUTR2 and OUTR6, and OUTR3 and OUTR7.  Each paired output turns on or off with 24 ns (typ) time delay between other paired outputs. Multiple outputs can be tied together to increase the constant-current capability. Different voltages can be applied to each output.                                                                                                                                                                                                                                                             |  |

| VCC             | 35                                  | 22                                  | _   | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| XBLNK           | 36                                  | 23                                  | I   | When XBLNK is low, all constant-current outputs (OUTR0–OUTR7, OUTG0–OUTG7, and OUTB0–OUTB7) are forced off. The grayscale counters for each color group are reset to 0, and the grayscale PWM timing controller is initialized. When XBLNK is high, all constant-current outputs are controlled by the grayscale PWM timing controller for each color LED. This pin is internally pulled to GND with a 500-kΩ resistor.                                                                                                                                                                                                                                                                                                             |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup> (2)

Over operating ambient temperature range, unless otherwise noted.

|                     |                                |                                                                     | MIN  | MAX                   | UNIT |

|---------------------|--------------------------------|---------------------------------------------------------------------|------|-----------------------|------|

| $V_{CC}$            | Supply voltage                 | VCC                                                                 | -0.3 | 6                     | V    |

| I <sub>OUT</sub>    | Output current (dc)            | OUTR0-OUTR7, OUTG0-OUTG7, OUTB0-OUTB7                               |      | 50                    | mA   |

| V <sub>IN</sub>     | Input voltage range            | GSSIN, GSSCK, GSLAT, GSCKR, GSCKG, GSCKB, DCSIN, DCSCK, XBLNK, IREF | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V                   |                                | GSSOUT, DCSOUT                                                      | -0.3 | $V_{CC} + 0.3$        | V    |

| V <sub>OUT</sub>    | Output voltage range           | OUTR0-OUTR7, OUTG0-OUTG7, OUTB0-OUTB7                               | -0.3 | 16                    | V    |

| T <sub>J(max)</sub> | Operation junction temperature |                                                                     | -40  | 150                   | °C   |

| T <sub>stg</sub>    | Storage temperature            |                                                                     | -55  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

At  $T_A = -40$ °C to 85°C, unless otherwise noted.

|                                       | PARA                                      | METER                                                                                     | MIN                 | NOM | MAX               | UNIT |

|---------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------|---------------------|-----|-------------------|------|

| DC CHARACT                            | TERISTICS: V <sub>CC</sub> = 3 V to 5.5 V |                                                                                           |                     |     |                   |      |

| V <sub>CC</sub>                       | Supply voltage                            |                                                                                           | 3                   |     | 5.5               | V    |

| Vo                                    | Voltage applied to output                 | OUTR0-OUTR7, OUTG0-OUTG7,<br>OUTB0-OUTB7                                                  |                     |     | 15                | V    |

| V <sub>IH</sub>                       | High level input voltage                  |                                                                                           | $0.7 \times V_{CC}$ |     | $V_{CC}$          | V    |

| $V_{IL}$                              | Low level input voltage                   |                                                                                           | GND                 | 0.3 | × V <sub>CC</sub> | V    |

| I <sub>OH</sub>                       | High level output current                 | GSSOUT, DCSOUT                                                                            |                     |     | -1                | mA   |

| I <sub>OL</sub>                       | Low level output current                  | GSSOUT, DCSOUT                                                                            |                     |     | 1                 | mA   |

| I <sub>OLC</sub>                      | Constant output sink current              | OUTR0-OUTR7, OUTG0-OUTG7,<br>OUTB0-OUTB7                                                  |                     |     | 40                | mA   |

| T <sub>A</sub>                        | Operating ambient temperature             |                                                                                           | -40                 |     | 85                | °C   |

| T <sub>J</sub>                        | Operating junction temperature            |                                                                                           | -40                 |     | 125               | °C   |

| AC CHARACT                            | ERISTICS, V <sub>CC</sub> = 3 V to 5.5 V  |                                                                                           |                     |     |                   |      |

| f <sub>CLK (SCK)</sub>                | Data-shift clock frequency                | GSSCK, DCSCK                                                                              |                     |     | 30                | MHz  |

| f <sub>CLK</sub><br>(GSCKR/G/B)       | Grayscale clock frequency                 | GSCKR, GSCKG, GSCKB                                                                       |                     |     | 33                | MHz  |

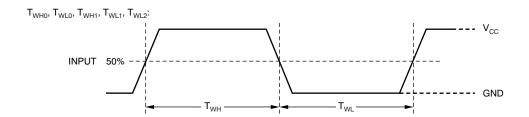

| t <sub>WH0</sub> and t <sub>WL0</sub> |                                           | GSSCK, DCSCK, GSCKR, GSCKG, GSCKB                                                         | 10                  |     |                   | ns   |

| t <sub>WH1</sub> and t <sub>WL1</sub> | Pulse duration                            | GSLAT                                                                                     | 30                  |     |                   | ns   |

| t <sub>WL2</sub>                      |                                           | XBLNK                                                                                     | 30                  |     |                   | ns   |

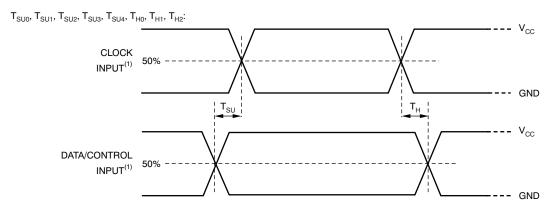

| t <sub>SU0</sub>                      |                                           | $GSSIN \to GSSCK{\uparrow},DCSIN \to DCSCK{\uparrow}$                                     | 5                   |     |                   | ns   |

| t <sub>SU1</sub>                      |                                           | $XBLNK\!\!\uparrow\toGSCKR\!\!\uparrow,GSCKG\!\!\uparrow,or\;GSCKB\!\!\uparrow$           | 10                  |     |                   | ns   |

| t <sub>SU2</sub>                      |                                           | $GSLAT\!\!\uparrow\toGSSCK\!\!\uparrow$                                                   | 150                 |     |                   | ns   |

| t <sub>SU3</sub>                      | Setup time                                | GSLAT↑ for GS data → GSCKR↑, GSCKG↑, or GSCKB↑ when display timing reset mode is disabled | 40                  |     |                   | ns   |

| t <sub>SU4</sub>                      |                                           | GSLAT↑ for GS data → GSCKR↑, GSCKG↑, or GSCKB↑ when display timing reset mode is enabled  | 100                 |     |                   | ns   |

| t <sub>H0</sub>                       |                                           | $GSSIN \to GSSCK \!\!\uparrow, DCSIN \to DCSCK \!\!\uparrow$                              | 5                   |     |                   | ns   |

| t <sub>H1</sub>                       | Hold time                                 | $GSLAT\!\!\uparrow \to GSSCK\!\!\uparrow$                                                 | 35                  |     |                   | ns   |

| t <sub>H2</sub>                       |                                           | $GSLAT \downarrow \to GSSCK \uparrow$                                                     | 5                   |     |                   | ns   |

#### 7.4 Thermal Information

| <i>1</i>             |                                                                   |              |            |            |      |

|----------------------|-------------------------------------------------------------------|--------------|------------|------------|------|

|                      |                                                                   |              |            |            |      |

|                      | THERMAL METRIC <sup>(1)</sup>                                     | DAP (HTSSOP) | RHA (VQFN) | RTA (WQFN) | UNIT |

|                      |                                                                   | 38 PINS      | 40 PINS    | 40 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistanceDeleted Dissipation Ratings | 27.8         | 28         | 27.2       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                         | 14.7         | 27.7       | 12.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                              | 6.7          | 9.3        | 8.7        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter                        | 0.2          | 0.2        | 0.1        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter                      | 6.8          | 9.3        | 8.6        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance                      | 0.6          | 1.3        | 0.9        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics.

#### 7.5 Electrical Characteristics

At  $T_A = -40$ °C to 85°C,  $V_{CC} = 3$  V to 5.5 V, and  $V_{LED} = 5$  V, unless otherwise noted. Typical values are at  $T_A = 25$ °C and  $V_{CC} = 3.3$  V.

|                   | PARAMETER                                                                               | TEST CONDITIONS                                                                                                                                                                                                                                                                                                               | MIN                   | TYP   | MAX             | UNIT |

|-------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------|------|

| V <sub>OH</sub>   | High-level output voltage                                                               | At GSSOUT, DCSOUT, I <sub>OH</sub> = -1 mA                                                                                                                                                                                                                                                                                    | V <sub>CC</sub> - 0.4 |       | V <sub>CC</sub> | V    |

| V <sub>OL</sub>   | Low-level output voltage                                                                | At GSSOUT, DCSOUT, I <sub>OL</sub> = 1 mA                                                                                                                                                                                                                                                                                     |                       |       | 0.4             | V    |

| l <sub>l</sub>    | Input current                                                                           | At GSSCK, GSLAT, DCSIN, DCSCK, GSCKR, -G, -B with $V_I = V_{CC}$ , At GSSIN, GSSCK, GSLAT, DCSIN, XBLNK, DCSCK, GSCKR, -G, -B with $V_I = \text{GND}$                                                                                                                                                                         | -1                    |       | 1               | μА   |

| I <sub>CC1</sub>  |                                                                                         | GSSIN, GSSCK, GSLAT, DCSIN, DCSCK = low, XBLNK = low, GSCKR, -G, -B = low, $V_{OUTRn/Gn/Bn} = 1$ V, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $R_{IREF} = 24$ k $\Omega$ ( $I_{OUTRn/Gn/Bn} = 2$ mA target)                                                                                      |                       | 1     | 3               | mA   |

| I <sub>CC2</sub>  |                                                                                         | GSSIN, GSSCK, GSLAT, DCSIN, DCSCK = low, XBLNK = low, GSCKR, -G, -B = low, $V_{OUTRn/Gn/Bn}$ = 1 V, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $R_{IREF}$ = 2.4 k $\Omega$ ( $I_{OUTRn/Gn/Bn}$ = 20 mA target)                                                                                    |                       | 6     | 10              | mA   |

| I <sub>CC3</sub>  | Supply current                                                                          | GSSIN, GSSCK, GSLAT, DCSIN, DCSCK = low, XBLNK = high, GSCKR, -G, -B = 33 MHz, $V_{OUTRn/Gn/Bn}$ = 1 V, GSRn, -Gn, -Bn = FFFh, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $R_{IREF}$ = 2.4 k $\Omega$ ( $I_{OUTRn/Gn/Bn}$ = 20 mA target), auto repeat on                                         |                       | 12    | 27              | mA   |

| I <sub>CC4</sub>  |                                                                                         | GSSIN, GSSCK, GSLAT, DCSIN, DCSCK = low, XBLNK = high, GSCKR, -G, -B = 33 MHz, $V_{OUTRn/Gn/Bn}$ = 1 V, GSRn, -Gn, -Bn = FFFh, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $R_{IREF}$ = 1.2 k $\Omega$ ( $I_{OUTRn/Gn/Bn}$ = 40 mA target), auto repeat on                                         |                       | 21    | 55              | mA   |

| I <sub>OLC</sub>  | Constant output current                                                                 | At OUTR0–OUTR7, OUTG0–OUTG7, OUTB0–OUTB7, All OUTRn, -Gn, -Bn = on, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{OUTRn/Gn/Bn} = 1 \text{ V, } V_{OUTfix} = 1 \text{ V, } R_{IREF} = 1.2 \text{ k}\Omega \left(I_{OUTRn/Gn/Bn} = 40 \text{ mA target}\right)$                                    | 35                    | 40    | 45              | mA   |

| I <sub>OLKG</sub> | Leakage output current                                                                  | At OUTR0–OUTR7, OUTG0–OUTG7 and OUTB0–OUTB7, XBLNK = low, $V_{OUTRn/Gn/Bn} = V_{OUTfix} = 15 \text{ V}$ , $R_{IREF} = 1.2 \text{ k}\Omega$                                                                                                                                                                                    |                       |       | 0.1             | μΑ   |

| Δl <sub>OLC</sub> | Constant-current error <sup>(1)</sup><br>(channel-to-channel in<br>same color group)    | At OUTR0–OUTR7, OUTG0–OUTG7 and OUTB0–OUTB7, All OUTRn, -Gn, -Bn = on, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{\text{OUTRn/Gn/Bn}} = 1 \text{ V, } V_{\text{OUTfix}} = 1 \text{ V,} \\ R_{\text{IREF}} = 1.2 \text{ k}\Omega \left( I_{\text{OUTRn/Gn/Bn}} = 40 \text{ mA target} \right)$ |                       | ±1.5% | ±4%             |      |

| $\Delta I_{OLC1}$ | Constant-current error <sup>(2)</sup><br>(color group to color<br>group in same device) | At OUTR0–OUTR7, OUTG0–OUTG7 and OUTB0–OUTB7, All OUTRn, -Gn, -Bn = on, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{\text{OUTRn/Gn/Bn}} = 1 \text{ V, } V_{\text{OUTfix}} = 1 \text{ V, } R_{\text{IREF}} = 1.2 \text{ k}\Omega \left( I_{\text{OUTRn/Gn/Bn}} = 40 \text{ mA target} \right)$   |                       | ±1%   | ±3%             |      |

(1) The deviation of each output in the same color group from the average of the same color group (OUTR0-OUTR7, OUTG0-OUTG7, or

$$\Delta \text{ (\%)} = \left[ \frac{I_{\text{OUTXn}} \text{ (N = 0-7)}}{\frac{(I_{\text{OUTX0}} + I_{\text{OUTX1}} + \dots + I_{\text{OUTX6}} + I_{\text{OUTX7}})}{8}} - 1 \right] \times 100$$

OUTB0–OUTB7) constant current. The deviation is calculated by the formula where (X = R, G, or B; n = 0–7).

(2) The deviation of each color group in the same device from the average of all constant current. The deviation is calculated by the formula

$$\Delta \text{ (\%)} = \left[ \begin{array}{c} \frac{\frac{\left( I_{\text{OUTX0}} + I_{\text{OUTX1}} + \dots + I_{\text{OUTX6}} + I_{\text{OUTX7}} \right)}{8}}{8} \\ -\frac{\frac{\left( I_{\text{OUTR0}} + \dots + I_{\text{OUTR7}} + I_{\text{OUTG7}} + I_{\text{OUTB0}} + \dots + I_{\text{OUTB7}} \right)}{24}}{24} \\ \end{array} \right] \times 100 \\ \text{, where (X = R, G, or B)}.$$

# **Electrical Characteristics (continued)**

At  $T_A = -40$ °C to 85°C,  $V_{CC} = 3$  V to 5.5 V, and  $V_{LED} = 5$  V, unless otherwise noted. Typical values are at  $T_A = 25$ °C and  $V_{CC} = 3.3$  V.

|                    | PARAMETER                                                                             | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                 | MIN | TYP  | MAX | UNIT |

|--------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Δl <sub>OLC2</sub> | Constant-current error <sup>(3)</sup> (device to device)                              | At OUTR0–OUTR7, OUTG0–OUTG7 and OUTB0–OUTB7, All OUTRn, -Gn, -Bn = on, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{OUTRn/Gn/Bn} = 1 \text{ V}, V_{OUTfix} = 1 \text{ V}, \\ R_{IREF} = 1.2 \text{ k}\Omega \left(I_{OUTRn/Gn/Bn} = 40 \text{ mA target}\right)$                                  |     | ±1%  | ±6% |      |

| ΔI <sub>OLC3</sub> | Line regulation <sup>(4)</sup>                                                        | At OUTR0–OUTR7, OUTG0–OUTG7 and OUTB0–OUTB7, All OUTRn, -Gn, -Bn = on, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{OUTRn/Gn/Bn} = 1 \text{ V}, V_{OUTfix} = 1 \text{ V}, \\ R_{IREF} = 1.2 \text{ k}\Omega \left(I_{OUTRn/Gn/Bn} = 40 \text{ mA target}\right)$                                  |     | ±0.5 | ±2  | %/V  |

| $\Delta I_{OLC4}$  | Load regulation <sup>(5)</sup>                                                        | At OUTR0–OUTR7, OUTG0–OUTG7 and OUTB0–OUTB7, All OUTRn, -Gn, -Bn = on, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{OUTRn/Gn/Bn} = 1 \text{ V}, V_{OUTfix} = 1 \text{ V}, \\ R_{IREF} = 1.2 \text{ k}\Omega \left(I_{OUTRn/Gn/Bn} = 40 \text{ mA target}\right)$                                  |     | ±1   | ±3  | %/V  |

| Δl <sub>OLC5</sub> | Constant-current<br>error <sup>(6)(7)</sup><br>(channel-to-channel in<br>same device) | At OUTR0-OUTR7, OUTG0-OUTG7, and OUTB0-OUTB7, All OUTRn, -Gn, -Bn = On, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{\text{OUTRn/Gn/Bn}} = 0.5 \text{ V, } T_{\text{A}} = 25^{\circ}\text{C,} \\ R_{\text{IREF}} = 9.6 \text{ k}\Omega \left(I_{\text{OUTRn/Gn/Bn}} = 5 \text{ mA target}\right)$ |     |      | 10% |      |

| Δl <sub>OLC6</sub> | Constant-current<br>error <sup>(7)(8)(9)</sup><br>(device-to-device)                  | At OUTR0-OUTR7, OUTG0-OUTG7, and OUTB0-OUTB7, All OUTRn, -Gn, -Bn = On, BCR, -G, -B = FFh, DCRn, -Gn, -Bn = 7Fh with DC high adjustment range, $V_{\text{OUTRn/Gn/Bn}} = 0.5 \text{ V, } T_{\text{A}} = 25^{\circ}\text{C,} \\ R_{\text{IREF}} = 9.6 \text{ k}\Omega \left(I_{\text{OUTRn/Gn/Bn}} = 5 \text{ mA target}\right)$ |     |      | 12% |      |

(3) The devigition of the constant-current average from the ideal constant-current value. The deviation is calculated by the formula

$$\Delta \text{ (\%) = } \left[ \frac{\frac{\text{(I_{OUTR0}^{+} \dots + I_{OUTR7}^{+} + I_{OUTR0}^{+} \dots + I_{OUTR7}^{+} + I_{OUTR0}^{+} \dots + I_{OUTR7}^{+} + I_{OUTR0}^{+} \dots + I_{OUTR1}^{+}}{24} - \text{(Ideal Output Current)} \right] \times 100$$

Ideal current is calculated by the formula  $\Delta \text{ (\%/V)} = \begin{cases} I_{\text{OUT}(\text{IDEAL, mA})} = 40 \times \left(\frac{1.20}{\text{R}_{\text{IREF}}} \text{ (\Omega)}\right) \\ \left(I_{\text{OUTXn}} \text{ at } V_{\text{CC}} = 5.5 \text{ V}\right) - \left(I_{\text{OUTXn}} \text{ at } V_{\text{CC}} = 3.0 \text{ V}\right) \\ \left(I_{\text{OUTXn}} \text{ at } V_{\text{CC}} = 3.0 \text{ V}\right) \\ \left(I_{\text{OUTXn}} \text{ at } V_{\text{CC}} = 3.0 \text{ V}\right) \\ \Delta \text{ (\%/V)} = \begin{cases} \left(I_{\text{OUTXn}} \text{ at } V_{\text{OUTXn}} = 3 \text{ V}\right) - \left(I_{\text{OUTXn}} \text{ at } V_{\text{OUTXn}} = 1 \text{ V}\right) \\ \left(I_{\text{OUTXn}} \text{ at } V_{\text{OUTXn}} = 1 \text{ V}\right) \end{cases} \times \frac{100}{3 \text{ V} - 1 \text{ V}}, \text{ where } (X = R, G, \text{ or B; n} = 0-7).$ (5) Load regulation is calculated by

$$\Delta \text{ (\%)} = \frac{\frac{1}{(I_{\text{OUT}}R0 + ... + I_{\text{OUT}}R7 + I_{\text{OUT}}G0 + ... + I_{\text{OUT}}G7 + I_{\text{OUT}}B0 + ... + I_{\text{OUT}}B7)}{24}$$

- (7) Applicable only to QFN-40 package.

- (8) The deviation of the maximum of all 24 channels of 30 devices from the minimum of all 24 channels of 30 devices. The deviation is calculated by  $\Delta \text{ (\%)} = \frac{\text{Max [I_{OUT}D1 (24 Ch), I_{OUT}D2 (24 Ch)...I_{OUT}D30 (24 Ch)]} \text{Min [I_{OUT}D1 (24 Ch), I_{OUT}D2 (24 Ch)...I_{OUT}D30 (24 Ch)]}}{\text{Average [I_{OUT}D1 (24 Ch), I_{OUT}D2 (24 Ch)...I_{OUT}D30 (24 Ch)]}}$

- (9) Not production tested, verified by characterization.

## **Electrical Characteristics (continued)**

At  $T_A = -40$ °C to 85°C,  $V_{CC} = 3$  V to 5.5 V, and  $V_{LED} = 5$  V, unless otherwise noted. Typical values are at  $T_A = 25$ °C and  $V_{CC} = 3.3$  V.

|                   | PARAMETER                          | TEST CONDITIONS                  | MIN  | TYP  | MAX  | UNIT |

|-------------------|------------------------------------|----------------------------------|------|------|------|------|

| T <sub>TEF</sub>  | Thermal error flag threshold (10)  | Junction temperature             | 150  | 163  | 175  | °C   |

| T <sub>HYS</sub>  | Thermal error flag hysteresis (10) | Junction temperature             | 5    | 10   | 20   | °C   |

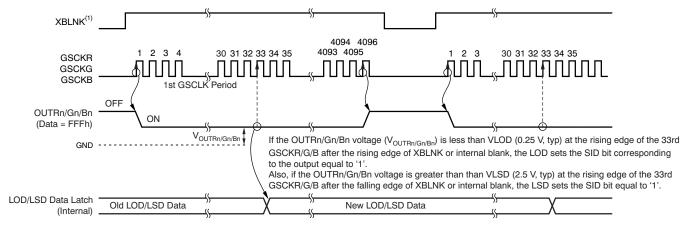

| V <sub>LOD</sub>  | LED open-detection threshold       | All OUTRn, -Gn, -Bn = on         | 0.2  | 0.25 | 0.3  | V    |

| V <sub>LSD</sub>  | LED short-detection threshold      | All OUTRn, -Gn, -Bn = on         | 2.4  | 2.5  | 2.6  | V    |

| V <sub>IREF</sub> | Reference voltage output           | $R_{IREF} = 1.2 \text{ k}\Omega$ | 1.17 | 1.2  | 1.23 | V    |

| R <sub>PDWN</sub> | Pulldown resistor                  | At XBLNK, GSSIN                  | 250  | 500  | 750  | kΩ   |

<sup>(10)</sup> Not tested; specified by design.

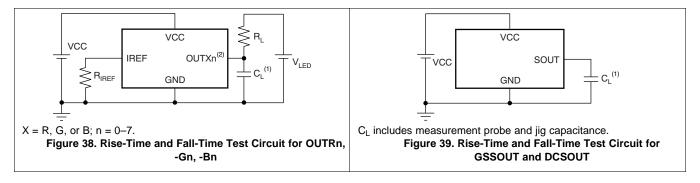

## 7.6 Switching Characteristics

At  $T_A = -40^{\circ}\text{C}$  to 85°C,  $V_{CC} = 3$  V to 5.5 V,  $C_L = 15$  pF,  $R_L = 100~\Omega$ ,  $R_{IREF} = 1.2~k\Omega$ , and  $V_{LED} = 5$  V, unless otherwise noted. Typical values are at  $T_A = 25^{\circ}\text{C}$  and  $V_{CC} = 3.3$  V.

|                     | PARAMETER                                                 | TEST CONDITIONS                                                                                                                                                                   | MIN | TYP | MAX | UNIT |

|---------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>R0</sub>     |                                                           | GSSOUT, DCSOUT                                                                                                                                                                    |     | 6   | 15  | ns   |

| t <sub>R1</sub>     | Rise time                                                 | OUTR0-OUTR7, OUTG0-OUTG7, OUTB0-OUTB7, with BCR, -G, -B = FFh and DCRn, -Gn, -Bn = 7Fh with DC high adjustment range                                                              |     | 10  | 30  | ns   |

| t <sub>F0</sub>     |                                                           | GSSOUT, DCSOUT                                                                                                                                                                    |     | 6   | 15  | ns   |

| t <sub>F1</sub>     | Fall time                                                 | OUTR0-OUTR7, OUTG0-OUTG7, OUTB0-OUTB7, with BCR, -G, -B = FFh and DCRn, -Gn, -Bn = 7Fh with dc high adjustment range                                                              |     | 10  | 30  | ns   |

| t <sub>D0</sub>     |                                                           | GSSCK↑ to GSSOUT, DCSCK↑ to DCSOUT                                                                                                                                                |     | 15  | 25  | ns   |

| t <sub>D1</sub>     |                                                           | GSLAT↑ to GSSOUT                                                                                                                                                                  |     | 50  | 100 | ns   |

| t <sub>D2</sub>     |                                                           | XBLNK↓ to OUTR0, OUTG0, OUTB0, OUTR4, OUTG4, OUTB4 off                                                                                                                            |     | 20  | 40  | ns   |

| t <sub>D3</sub>     |                                                           | GSCKR, -G, -B↑ to OUTR0/G0/B0, OUTR4/G4/B4 on, with BCR, -G, -B = FFh and DCRn, -Gn, -Bn = 7Fh with DC high adjustment range                                                      | 5   | 18  | 40  | ns   |

| t <sub>D4</sub>     |                                                           | GSCKR, -G, -B↑ to OUTR1/G1/B1, OUTR5/G5/B5 on, with BCR, -G, -B = FFh and DCRn, -Gn, -Bn = 7Fh with DC high adjustment range                                                      | 20  | 42  | 73  | ns   |

| t <sub>D5</sub>     | Propagation delay                                         | GSCKR, -G, -B↑ to OUTR2/G2/B2, OUTR6/G6/B6 on, with BCR, -G, -B = FFh and DCRn, -Gn, -Bn = 7Fh with DC high adjustment range                                                      | 35  | 66  | 106 | ns   |

| t <sub>D6</sub>     |                                                           | GSCKR, -G, -B↑ to OUTR3/G3/B3, OUTR7/G7/B7 on, with BCR, -G, -B = FFh and DCRn, -Gn, -Bn = 7Fh with DC high adjustment range                                                      | 50  | 90  | 140 | ns   |

| t <sub>D7</sub>     |                                                           | Internal latch pulse generation delay from DCSCK                                                                                                                                  | 3   | 5   | 7   | ms   |

| t <sub>D8</sub>     |                                                           | GSLAT↑ to $I_{OUTRn/Gn/Bn}$ changing by dot correction control (control data are $0Ch \rightarrow 72h$ or $72h \rightarrow 0Ch$ with dc high adjustment range), BCR, -G, -B = FFh |     | 30  | 50  | ns   |

| t <sub>D9</sub>     |                                                           | GSLAT↑ to I <sub>OUTRn/Gn/Bn</sub> changing by global brightness control (control data are 19h ≥ E6h or E6h ≥ 19h with DCRn, -Gn, -Bn = 7Fh with DC high adjustment range)        |     | 100 | 300 | ns   |

| t <sub>ON_ERR</sub> | Output on-time error, tout_on - tgsckr/g/B <sup>(1)</sup> | GS <sub>DATA</sub> = 001h, GSCKR, -G, -B = 33 MHz, with BCR, -G, -B = FFh and DCRn, -Gn, -Bn = 7Fh with DC high adjustment range                                                  | -15 |     | 5   | ns   |

<sup>(1)</sup> Output on-time error (t<sub>ON\_ERR</sub>) is calculated by the formula t<sub>ON\_ERR</sub> (ns) = t<sub>OUT\_ON</sub> - t<sub>GSCKR/G/B</sub>. t<sub>OUT\_ON</sub> indicates the actual on-time of the constant current driver. t<sub>GSCKR</sub> is the period of GSCKR, t<sub>GSCKG</sub> is the period of GSCKG, and t<sub>GSCKB</sub> is the period of GSCKB.

(1) Input-pulse rise and fall times are 1 ns to 3 ns.

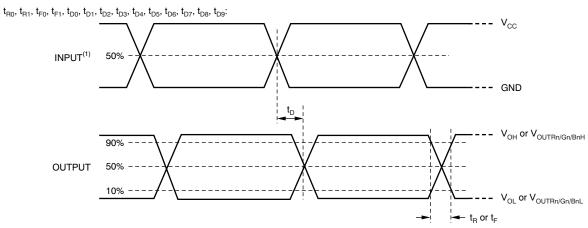

Figure 1. Input Timing

(2) Input-pulse rise and fall times are 1 ns to 3 ns.

Figure 2. Output Timing

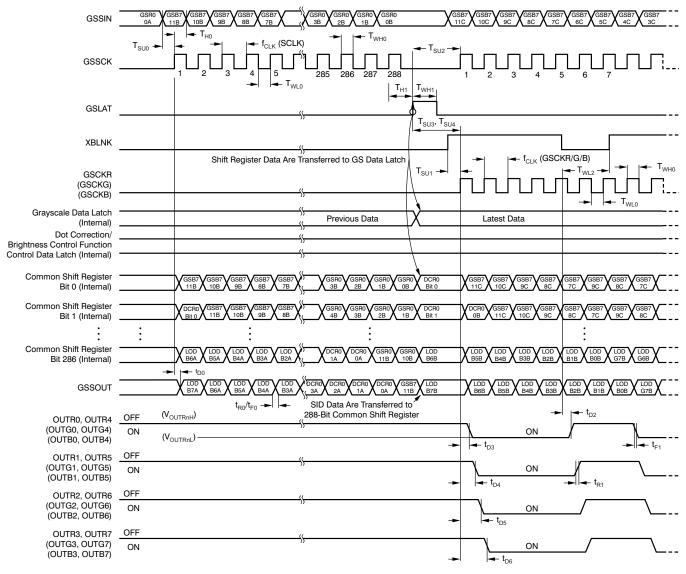

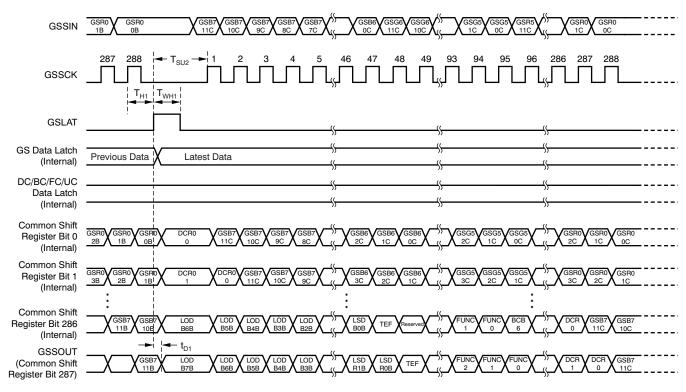

Figure 3. Grayscale Data-Write Timing

Submit Documentation Feedback

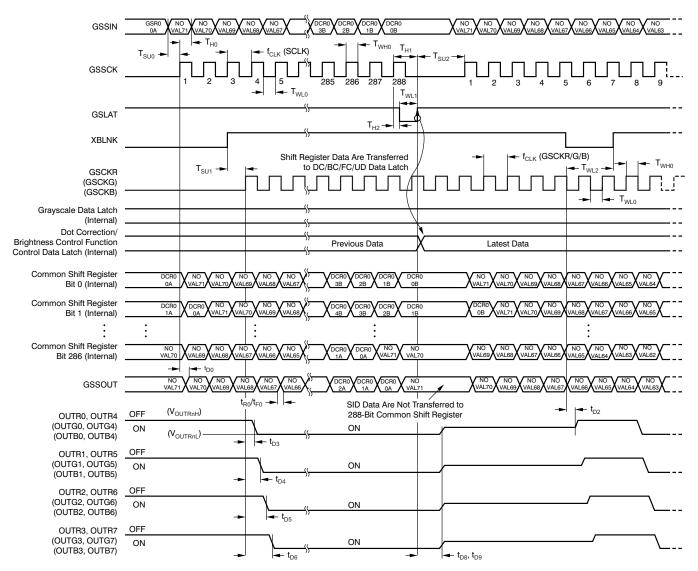

Figure 4. Dot Correction, Global Brightness Control, Function Control, and User-Defined Data-Write Timing From GS Data Path

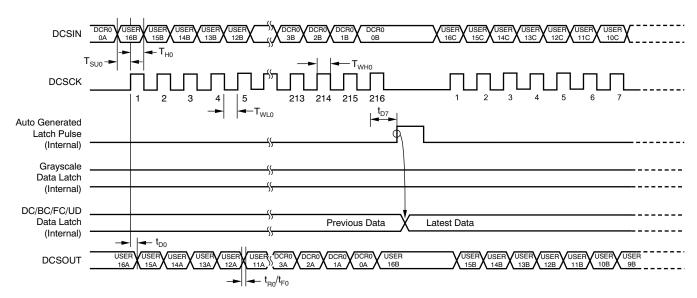

Figure 5. Dot Correction, Global Brightness Control, and Function Control

Data-Write Timing From DC Data Path

Figure 6. Status Information Data-Read Timing

Submit Documentation Feedback

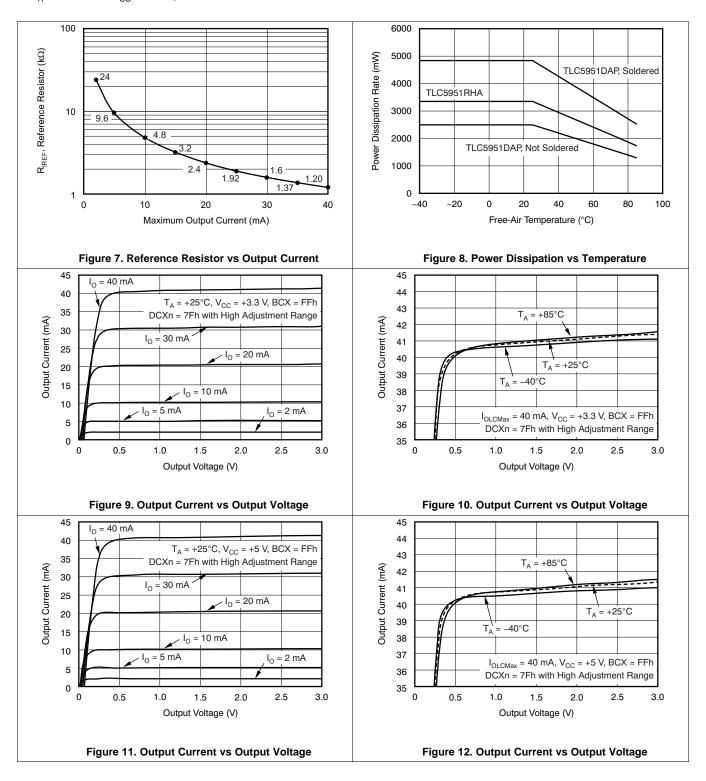

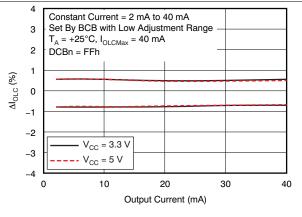

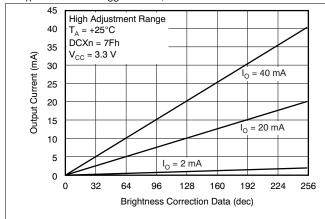

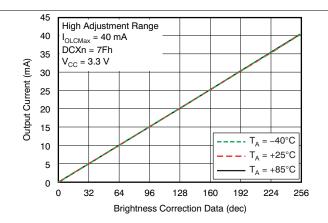

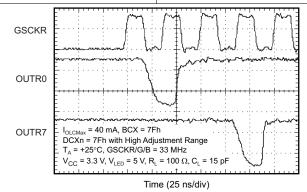

# 7.7 Typical Characteristics

at  $T_A = 25^{\circ}\text{C}$  and  $V_{\text{CC}} = 3.3 \text{ V}$ , unless otherwise noted

Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

# TEXAS INSTRUMENTS

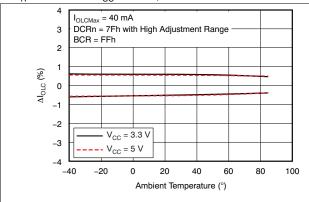

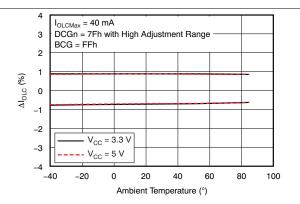

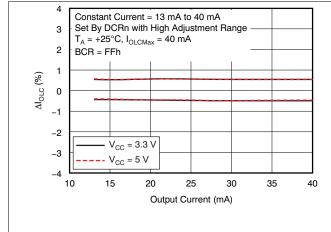

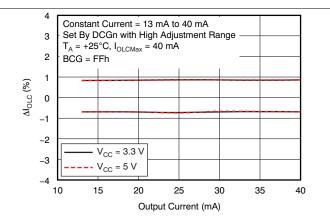

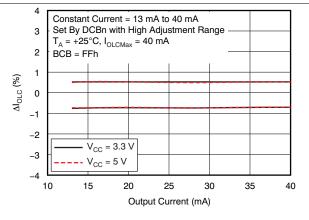

# **Typical Characteristics (continued)**

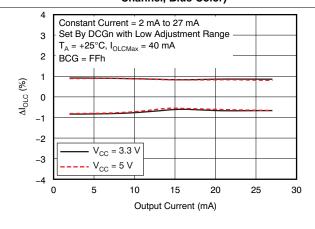

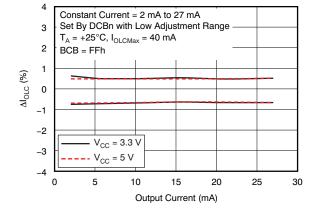

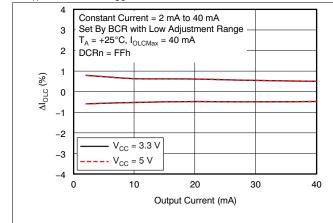

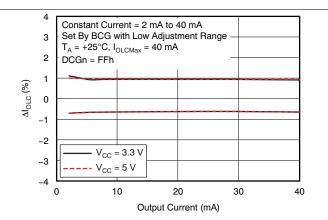

at  $T_A = 25$ °C and  $V_{CC} = 3.3$  V, unless otherwise noted

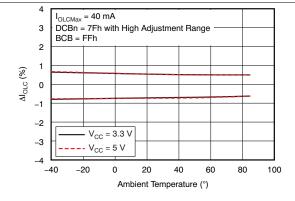

Figure 13. Constant-Current Error vs Ambient Temperature (Channel-to-Channel, Red Color)

Figure 14. Constant-Current Error vs Ambient Temperature (Channel-to-Channel, Green Color)

Figure 15. Constant-Current Error vs Ambient Temperature (Channel-to-Channel, Blue Color)

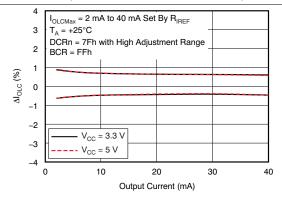

Figure 16. Constant-Current Error vs Output (Channel-to-Channel, Red Color)

Figure 17. Constant-Current Error vs Output (Channel-to-Channel, Green Color)

Figure 18. Constant-Current Error vs Output (Channel-to-Channel, Blue Color)

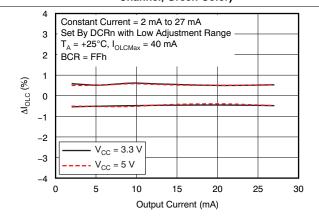

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and  $V_{CC} = 3.3$  V, unless otherwise noted

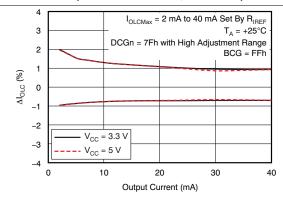

Figure 19. Constant-Current Error vs Output (Channel-to-Channel, Red Color)

Figure 20. Constant-Current Error vs Output (Channel-to-Channel, Green Color)

Figure 21. Constant-Current Error vs Output (Channel-to-Channel, Blue Color)

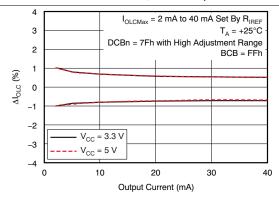

Figure 22. Constant-Current Error vs Output (Channel-to-Channel, Red Color)

Figure 23. Constant-Current Error vs Output (Channel-to-Channel, Green Color)

Figure 24. Constant-Current Error vs Output (Channel-to-Channel, Blue Color)

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

at  $T_A = 25$ °C and  $V_{CC} = 3.3$  V, unless otherwise noted

Figure 25. Constant-Current Error vs Output (Channel-to-Channel, Red Color)

Figure 26. Constant-Current Error vs Output (Channel-to-Channel, Green Color)

Figure 27. Constant-Current Error vs Output (Channel-to-Channel, Blue Color)

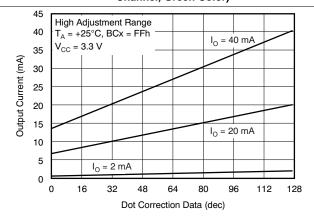

Figure 28. Dot Correction Linearity (I<sub>OLCMax</sub> With Upper Range)

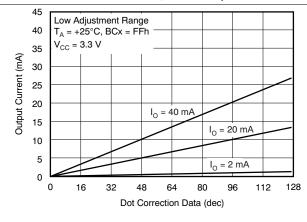

Figure 29. Dot Correction Linearity (I<sub>OLCMax</sub> With Lower Range)

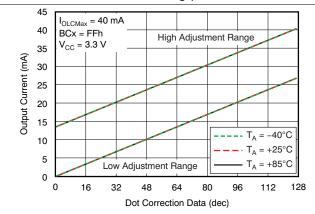

Figure 30. Dot Correction Linearity (I<sub>OLCMax</sub> With Upper And Lower Range)

# **Typical Characteristics (continued)**

at  $T_A$  = 25°C and  $V_{CC}$  = 3.3 V, unless otherwise noted

Figure 31. Global Brightness Control Linearity (I<sub>OLCMax</sub> With Upper Range)

Figure 32. Global Brightness Control Linearity (Ambient Temperature With Upper Range)

Figure 33. Constant-Current Output-Voltage Waveform

Copyright © 2009–2017, Texas Instruments Incorporated

Product Folder Links: *TLC5951*

### 8 Parameter Measurement Information

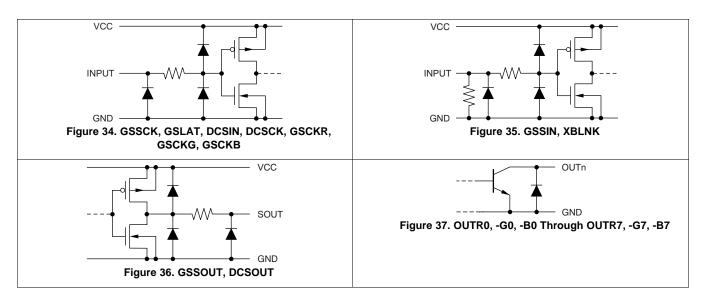

## 8.1 Pin Equivalent Input and Output Schematic Diagrams

#### 8.2 Test Circuits

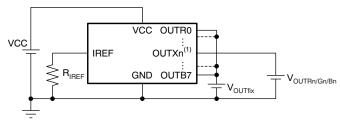

(1) X = R, G, or B; n = 0-7.

Figure 40. Constant-Current Test Circuit for OUTRn, -Gn, -Bn

# 9 Detailed Description

#### 9.1 Overview

The TLC5951 device is a 24-channel, constant-current sink driver. Each channel has an individually-adjustable, 4096-step, pulse-width modulation (PWM) grayscale (GS) brightness control and 128-step constant-current dot correction (DC). The dot correction adjusts brightness deviation between channels and other LED drivers. The output channels are grouped into three groups of eight channels. Each color group has a 256-step global brightness control (BC) function and an individual grayscale clock input. GS, DC, and BC data are accessible via a serial interface port. DC and BC can be programmed via a dedicated serial interface port.

The TLC5951 has a 40-mA current capability. One external resistor determines the maximum current limit that applies to all channels.

The TLC5951 device has three error-detection circuits for LED-open detection (LOD), LED-short detection (LSD), and thermal error flag (TEF). LOD detects a broken or disconnected LED, LSD detects a shorted LED, and TEF indicates an overtemperature condition.

## 9.2 Functional Block Diagram

#### 9.3 Feature Description

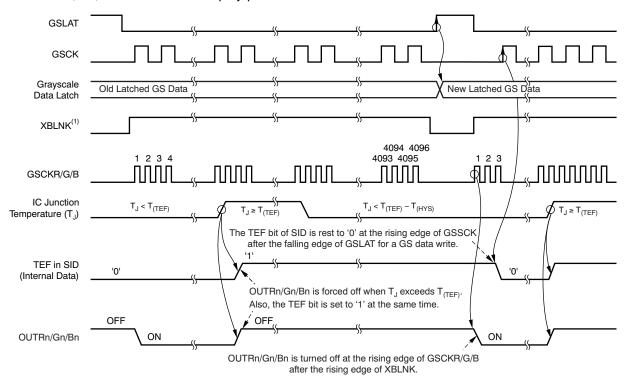

#### 9.3.1 Thermal-Shutdown and Thermal-Error Flags

The thermal shutdown (TSD) function turns off all constant-current outputs on the device when the junction temperature  $(T_J)$  exceeds the threshold  $(T_{TEF} = 163^{\circ}C, typ)$  and sets the thermal error flag (TEF) to 1. All outputs are latched off when TEF is set to 1 and remain off until the next grayscale cycle after XBLNK goes high and the junction temperature drops below  $(T_{TEF} - T_{HYST})$ . TEF remains as 1 until GSLAT is input with low temperature. TEF is set to 0 once the junction temperature drops below  $(T_{TEF} - T_{HYST})$ , but the output does not turn on until the first GSCKR, -G, or -B in the next display period even if TEF is set to 0.

(1) An internal signal also works to turn the constant outputs, the same as the XBLNK input. The internal blank signal is generated at the rising edge of the GSLAT input signal for GS data with the display-timing reset enabled. Also, the signal is generated at the 4096th GSCKR, -G, or -B when auto repeat mode is enabled. XBLNK can be connected to VCC when the display timing reset or auto repeat is enabled.

Figure 41. TEF and TSD Timing

#### 9.3.2 Noise Reduction

Large surge currents may flow through the device and the board on which the device is mounted if all 24 outputs turn on simultaneously at the start of each grayscale cycle. These large current surges could induce detrimental noise and electromagnetic interference (EMI) into other circuits. The TLC5951 device turns the outputs on in a series delay for each group independently to provide a circuit soft-start feature. The output current sinks are grouped into four groups in each color group. For example, for the RED color output, the first grouped outputs that are turned on or off are OUTR0 and OUTR4. The second grouped outputs that are turned on or off are OUTR1 and OUTR5. The third grouped outputs are OUTR2 and OUTR6, and the fourth grouped outputs are OUTR3 and OUTR7. Each grouped output is turned on and off sequentially with a small delay between groups. However, each color output on and off is controlled by the color grayscale clock.

#### 9.4 Device Functional Modes

#### 9.4.1 Maximum Constant Sink-Current Value

The TLC5951 maximum constant sink-current value for each channel,  $I_{OLCMax}$ , is determined by an external resistor,  $R_{IRFF}$ , placed between  $R_{IRFF}$  and GND. The  $R_{IRFF}$  resistor value is calculated with Equation 1.

### **Device Functional Modes (continued)**

$$R_{IREF} (k\Omega) = \frac{V_{IREF} (V)}{I_{OLCMax} (mA)} \times 40$$

where:

• V<sub>IREE</sub> = the internal reference voltage on IREF (1.2 V, typically)

(1)

$I_{OLCMax}$  is the largest current for each output. Each output sinks the  $I_{OLCMax}$  current when it is turned on, the dot correction is set to the maximum value of 7Fh (127d), and the global brightness control data are set to the maximum value of FFh (255d). Each output sink current can be reduced by lowering the output dot correction or brightness control value.

$R_{IREF}$  must be between 1.2 k $\Omega$  and 24 k $\Omega$  to keep  $I_{OLCMax}$  between 40 mA (typ) and 2mA (typ); the output may be unstable when  $I_{OLCMax}$  is set lower than 2 mA. Output currents lower than 2 mA can be achieved by setting  $I_{OLCMax}$  to 2 mA or higher and then using dot correction and global brightness control to lower the output current.

Figure 7 and Table 1 show the constant sink current versus external resistor,  $R_{IREF}$ , characteristics. Multiple outputs can be tied together to increase the constant-current capability. Different voltages can be applied to each output.

Table 1. Maximum Constant-Current Output Versus External Resistor Value

| I <sub>OLCMax</sub> (mA, Typical) | R <sub>IREF</sub> (kΩ) |

|-----------------------------------|------------------------|

| 40                                | 1.2                    |

| 35                                | 1.371                  |

| 30                                | 1.6                    |

| 25                                | 1.92                   |

| 20                                | 2.4                    |

| 15                                | 3.2                    |

| 10                                | 4.8                    |

| 5                                 | 9.6                    |

| 2                                 | 24                     |

#### 9.4.2 Dot Correction (DC) Function

The TLC5951 device has the capability to adjust the output current of each channel (OUTR0–OUTR7, OUTG0–OUTG7, and OUTB0–OUTB7) individually. This function is called dot correction (DC). The DC function allows the brightness and color deviations of LEDs connected to each output to be individually adjusted. Each output DC is programmed with a 7-bit word for each channel output. Each channel output current is adjusted in 128 steps within one of two adjustment ranges. The dot-correction high-adjustment range allows the output current to be adjusted from 33.3% to 100% of the maximum output current, I<sub>OLCMax</sub>. The dot-correction-low adjustment range allows the output current to be adjusted from 0% to 66.7% of I<sub>OLCMax</sub>. The range control bits in the function control latch select the high or low adjustment range. Equation 2 and Equation 3 calculate the actual output current as a function of R<sub>IREF</sub>, DC value, adjustment range, and brightness control value. There are three range control bits that control the DC adjustment range for three groups of outputs: OUTR0–OUTR7, OUTG0–OUTG7, and OUTB0–OUTB7. DC data are programmed into the TLC5951 device via the serial interface.

When the device is powered on, the DC data in the 216-bit common shift register and data latch contain random data. Therefore, DC data must be written to the DC latch before turning the constant-current output on. Additionally, XBLNK should be low when the device turns on to prevent the outputs from turning on before the proper grayscale values can be written. All constant-current outputs are off when XBLNK is low.

#### 9.4.3 Global Brightness Control (BC) Function

The TLC5951 device has the capability to adjust the output current of each color group simultaneously. This function is called global brightness control (BC). The global brightness control for each of the three color groups, (OUTR0–OUTR7, OUTG0–OUTG7, and OUTB0–OUTB7), is programmed with a separate 8-bit word. The BC of each group is adjusted with 256 steps from 0% to 100%. 0% corresponds to 0 mA. 100% corresponds to the maximum output current programmed by  $R_{IREF}$  and each output DC value. Note that even though the BC values for all color groups are identical, the output currents can be different if the DC values are different. Equation 2 and Equation 3 calculates the actual output current as a function of  $R_{IREF}$ , the DC adjustment range, and the brightness control value. BC data are programmed into the TLC5951 device via the serial interface.

When the device is powered on, the BC data in the 216-bit common shift register and data latch contain random data. Therefore, BC data must be written to the BC latch before turning the constant-current output on. Additionally, XBLNK should be low when the device turns on to prevent the outputs from turning on before the proper grayscale values can be written. All constant-current outputs are off when XBLNK is low.

Equation 2 determines the output sink current for each color group when the dot-correction high-adjustment range is chosen.

$$I_{OUT} (mA) = \left[ \frac{1}{3} I_{OLCMax} (mA) + \frac{2}{3} I_{OLCMax} (mA) \times \left[ \frac{DC}{127} \right] \right] \times \left[ \frac{BC}{255} \right]$$

(2)

Equation 3 determines the output sink current for each color group when the dot-correction low-adjustment range is chosen.

$$I_{OUT}$$

(mA) =  $\left[\frac{2}{3}I_{OLCMax}$  (mA)  $\times \left[\frac{DC}{127}\right]\right] \times \left[\frac{BC}{255}\right]$

#### where:

- I<sub>OLCMax</sub> = the maximum channel current for each channel determined by R<sub>IREF</sub>

- DC = the decimal dot correction value for the output. This value ranges between 0 and 127.

- BC = the decimal brightness control value for the output color group. This value ranges between 0 and 255. (3)

Table 2. Output Current vs DC Data and I<sub>OLCMax</sub> With Dot-Correction High-Adjustment Range (BC Data = FFh)

| DC DATA<br>(Binary) | DC DATA<br>(Decimal) | DC DATA<br>(Hex) | BC DATA<br>(Hex) | PERCENTAGE<br>OF I <sub>OLCMax</sub> (%) | I <sub>OUT</sub> , mA<br>(I <sub>OLCMax</sub> = 40 mA) | I <sub>OUT</sub> , mA<br>(I <sub>OLCMax</sub> = 2 mA) |

|---------------------|----------------------|------------------|------------------|------------------------------------------|--------------------------------------------------------|-------------------------------------------------------|

| 000 0000            | 0                    | 00               | FF               | 33.3                                     | 13.33                                                  | 0.67                                                  |

| 000 0001            | 1                    | 01               | FF               | 33.9                                     | 13.54                                                  | 0.68                                                  |

| 000 0010            | 2                    | 02               | FF               | 34.4                                     | 13.75                                                  | 0.69                                                  |

| _                   | _                    | _                | _                | _                                        | _                                                      | _                                                     |

| 111 1101            | 125                  | 7D               | FF               | 99                                       | 39.58                                                  | 1.98                                                  |

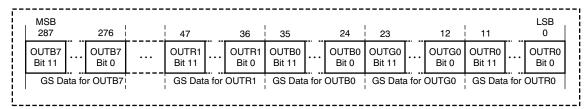

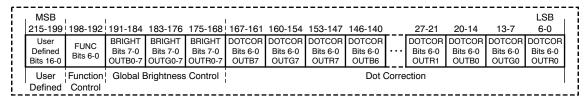

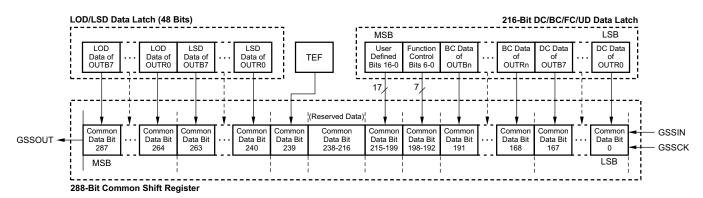

| 111 1110            | 126                  | 7E               | FF               | 99.5                                     | 39.79                                                  | 1.99                                                  |