**TLC5958**

SLVSCE7A - MAY 2014-REVISED SEPTEMBER 2014

# TLC5958 48-Channel, 16-Bit ES-PWM LED Driver with Pre-Charge FET, LED Open **Detection and Display Data Memory Support 32-Multiplexing**

#### **Features**

- 48 Channels Constant Current Sink Output

- Sink Current Capability with Max BC/CC data:

- 25mA at 5VCC

- 20mA at 3.3VCC

- Global Brightness Control (BC): 3-Bit (8 Step)

- Color Brightness Control (CC) for Each Color Group:

- 9-Bit (512 Step), Three Groups

- Grayscale(GS) Control with Multiplexed Enhanced Spectrum(ES) PWM: 16bit

- 48K bit Grayscale Data Memory Support 32multiplexing

- LED Power Supply Voltage Up To 10V

- Vcc = 3.0V to 5.5V

- **Constant Current Accuracy**

- Channel to Channel = ±1%(Typ), ±3%(Max)

- Device to Device =  $\pm 1\%$ (Typ),  $\pm 2\%$ (Max)

- Data Transfer Rate: 25MHz

- Gray Scale Clock: 33MHz

- LED Open Detection (LOD)

- Thermal Shut Down (TSD)

- I<sub>RFF</sub> Resistor Short Protection (ISP)

- Power-Save Mode (PSM) with high speed recovery

- Delay Switching to Prevent Inrush Current

- Pre-charge FET to Avoid Ghosting Phenomenon

- Operating Temperature: -40°C to +85°C

#### 2 Applications

- LED Video Displays with Multiplexing System

- LED Signboards with Multiplexing system

- High Refresh Rate & High density LED Panel

### Description

The TLC5958 is a 48 channels constant-current sink driver for multiplexing system with 1 to 32 duty ratio. Each channel has an individually-adjustable, 65536step, pulse width modulation (PWM) grayscale (GS).

48K bit display memory is implemented to increase the visual refresh rate and to decrease the GS data writing frequency.

The output channels are grouped into three groups, each group has 16 channels. Each group has a 512step color brightness control (CC) function. The maximum current value of all 48 channels can be set by 8-step global brightness control (BC) function. CC and BC can be used to adjust the brightness deviation between LED drivers. GS, CC, and BC data are accessible via a serial interface port.

Send request via email for Application Note: Build High Density, High Refresh Rate, Multiplexing LED Panel with TLC5958.

#### Device Information(1)

|             |           | <b>\</b> /        |

|-------------|-----------|-------------------|

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

| TLC5958     | VQFN (56) | 8.00 mm × 8.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

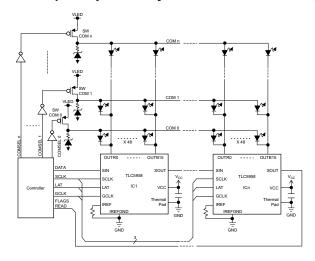

## Typical Application Circuit (Multiple Daisy-Chained TLC5958s)

# **Table of Contents**

| 1 | Features 1                                   |    | Diagrams                                         | 1 <sup>.</sup> |

|---|----------------------------------------------|----|--------------------------------------------------|----------------|

| 2 | Applications 1                               |    | 9.2 Timing Diagrams                              | 1              |

| 3 | Description 1                                | 10 | Detailed Description                             | 14             |

| 4 | Typical Application Circuit (Multiple Daisy- |    | 10.1 Overview                                    | 14             |

|   | Chained TLC5958s) 1                          |    | 10.2 Functional Block Diagram                    | 1              |

| 5 | Revision History2                            |    | 10.3 Device Functional Modes                     | 10             |

| 6 | Description (Continued)3                     | 11 | Application and Implementation                   | 20             |

| 7 | Pin Configuration and Functions              | 12 | Power Supply Recommendations                     | 20             |

| 8 | Specifications5                              | 13 | Layout                                           | 20             |

|   | 8.1 Absolute Maximum Ratings 5               |    | 13.1 Layout Guidelines                           | 20             |

|   | 8.2 Handling Ratings5                        |    | 13.2 Layout Example                              | 20             |

|   | 8.3 Recommended Operating Conditions         | 14 | Device and Documentation Support                 | 2 <sup>-</sup> |

|   | 8.4 Thermal Information                      |    | 14.1 Trademarks                                  | 2 <sup>.</sup> |

|   | 8.5 Electrical Characteristics               |    | 14.2 Electrostatic Discharge Caution             | 2              |

|   | 8.6 Typical Characteristics                  |    | 14.3 Glossary                                    | 2 <sup>2</sup> |

| 9 | Parameter Measurement Information            | 15 | Mechanical, Packaging, and Orderable Information | 2 <sup>-</sup> |

# 5 Revision History

| Ch | Changes from Original (May 2014) to Revision A                         |  |  |  |

|----|------------------------------------------------------------------------|--|--|--|

| •  | Deleted Product Preview banner - set to Production Data; global change |  |  |  |

#### 6 Description (Continued)

The TLC5958 has one error flag: LED open detection (LOD), which can be read via a serial interface port. The TLC5958 also has a power-save mode that sets the total current consumption to 0.8mA (typ) when all outputs are off.

### 7 Pin Configuration and Functions

56 Pin RTQ (TOP VIEW)

#### **Pin Functions**

| PIN       |                                                                         | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------|-------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME      | NO.                                                                     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                        |  |  |  |  |

| GCLK      | 29                                                                      | 1   | Grayscale(GS) pulse width modulation (PWM) reference clock control for OUTXn. Each GCLK rising edge increase the GS counter by1 for PWM control.                                                                                                                                   |  |  |  |  |

| GND       | ThermalPad                                                              | _   | Power ground. The thermal pad must be soldered to GND on PCB.                                                                                                                                                                                                                      |  |  |  |  |

| IREF      | 1                                                                       | _   | Maximum constant-current value setting. The OUTR0 to OUTB15 maximum constant output current are set to the desired values by connecting an external resistor between IREF and IREFGND. See equation 1 for more detail. The external resistor should be placed close to the device. |  |  |  |  |

| IREFGND   | 56                                                                      | _   | Analog ground. Dedicated ground pin for the external IREF resistor. This pin should be connected to analog ground trace which is connected to power ground near the common GND point of board.                                                                                     |  |  |  |  |

| LAT       | 27                                                                      | 1   | The LAT falling edge latches the data from the common shift register into the GS data memory or Function control(FC) register FC1 or FC2.                                                                                                                                          |  |  |  |  |

| OUTR0-R15 | 8, 11, 14, 17,<br>20, 23, 30,<br>33, 36, 39,<br>44, 47, 50,<br>53, 2, 5 | 0   | Constant current output for RED LED. Multiple outputs can be tied together to increase the constant current capability. Different voltages can be applied to each output. These outputs are turned on-off by GCLK signal and the data in GS data memory.                           |  |  |  |  |

### Pin Functions (continued)

| Р         | IN                                                                       | I/O | DECODINE                                                                                                                                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME      | AME NO.                                                                  |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |

| OUTG0-G15 | 9, 12, 15, 18,<br>21, 24, 31,<br>34, 37, 40,<br>45, 48, 51,<br>54, 3, 6  | 0   | Constant current output for GREEN LED. Multiple outputs can be tied together to increase the constant current capability. Different voltages can be applied to each output. These outputs are turned on-off by GCLK signal and the data in GS data memory.                                                                         |

| OUTB0-B15 | 10, 13, 16,<br>19, 22, 25,<br>32, 35, 38,<br>41, 46, 49,<br>52, 55, 4, 7 | 0   | Constant current output for BLUE LED. Multiple outputs can be tied together to increase the constant current capability. Different voltages can be applied to each output. These outputs are turned on-off by GCLK signal and the data in GS data memory.                                                                          |

| SCLK      | 28                                                                       | I   | Serial data shift clock. Data present on SIN are shifted to the 48-bit common shift register LSB with the SCLK rising edge. Data in the shift register are shifted towards the MSB at each SCLK rising edge. The common shift register MSB appears on SOUT.                                                                        |

| SIN       | 26                                                                       | I   | Serial data input of the 48-bit common shift register. When SIN is high level, the LSB is set to '1' for only one SCLK input rising edge. If two SCLK rising edges are input while SIN is high, then the 48-bit shift register LSB and LSB+1 are set to '1'. When SIN is low, the LSB is set to '0' at the SCLK input rising edge. |

| SOUT      | 42                                                                       | 0   | Serial data output of the 48-bit common shift register. SOUT is connected to the MSB of the register.                                                                                                                                                                                                                              |

| VCC       | 43                                                                       | _   | Power-supply voltage.                                                                                                                                                                                                                                                                                                              |

#### 8 Specifications

#### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                      | PARAME                         | MIN                        | MAX  | UNIT                 |    |

|----------------------|--------------------------------|----------------------------|------|----------------------|----|

| V <sub>CC</sub> (2)  | Supply voltage                 | VCC                        | 0.3  | 6.0                  | V  |

| I <sub>OUT</sub>     | Output current (dc)            | OUTx0 to OUTx15, x=R, G, B |      | 30                   | mA |

| V <sub>IN</sub> (2)  | Input voltage                  | SIN, SCLK, LAT, GCLK, IREF | -0.3 | V <sub>CC</sub> +0.3 | V  |

| v (2)                | Outrot valtage                 | SOUT                       | -0.3 | V <sub>CC</sub> +0.3 | V  |

| V <sub>OUT</sub> (2) | Output voltage                 | OUTx0 to OUTx15, x=R, G, B | -0.3 | 11                   |    |

| T <sub>J(MAX)</sub>  | Operating junction temperature |                            |      | 150                  | °C |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 8.2 Handling Ratings

|                        |                         |                                                                               | MIN         | MAX  | UNIT |

|------------------------|-------------------------|-------------------------------------------------------------------------------|-------------|------|------|

| T <sub>stg</sub>       | Storage temperature ra  | ange                                                                          | <b>-</b> 55 | 150  | °C   |

| V <sub>(ESD)</sub> (1) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(2)</sup>   |             | 4000 | V    |

|                        |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (3) | 0           | 1000 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) measures device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

#### 8.3 Recommended Operating Conditions

At  $T_A = -40$ °C to +85°C, unless otherwise noted

|                                    |                                |                                                    | MIN     | NOM | MAX    | UNIT |  |  |  |

|------------------------------------|--------------------------------|----------------------------------------------------|---------|-----|--------|------|--|--|--|

| DC CHARACTERISTICS, VCC=3V to 5.5V |                                |                                                    |         |     |        |      |  |  |  |

| V <sub>CC</sub>                    | Supply voltage                 |                                                    | 3       |     | 5.5    | V    |  |  |  |

| Vo                                 | Voltage applied to output      | OUTx0 to OUTx15, x=R, G, B                         |         |     | 10     | V    |  |  |  |

| V <sub>IH</sub>                    | High level input voltage       | SIN,SCLK,LAT,GCLK                                  | 0.7×VCC |     | VCC    | V    |  |  |  |

| V <sub>IL</sub>                    | Low level input voltage        | SIN,SCLK,LAT,GCLK                                  | GND     | 0.  | .3×VCC | V    |  |  |  |

| I <sub>OH</sub>                    | High level output current      | SOUT                                               |         |     | -2     | mA   |  |  |  |

| I <sub>OL</sub>                    | Low level output current       | SOUT                                               |         |     | 2      | mA   |  |  |  |

|                                    | Constant output sink current   | OUTx0 to OUTx15, x=R, G, B, $3V \le VCC \le 3.6V$  |         |     | 20     | m Λ  |  |  |  |

| lolc                               |                                | OUTx0 to OUTx15, x=R, G, B,<br>$4V < VCC \le 5.5V$ |         | 25  |        | mA   |  |  |  |

| T <sub>A</sub>                     | Operating free air temperature |                                                    | -40     |     | 85     | °C   |  |  |  |

| TJ                                 | Operation junction temperature |                                                    | -40     |     | 125    | °C   |  |  |  |

<sup>(2)</sup> All voltage values are with respect to device ground terminal.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions (continued)**

At  $T_A = -40$ °C to +85°C, unless otherwise noted

|                        |                                           |                                                                                                | MIN  | NOM | MAX      | UNIT |

|------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------|------|-----|----------|------|

| AC CHARA               | CTERISTICS, VCC=3V to 5.5V <sup>(1)</sup> | ,                                                                                              |      |     | <u>'</u> |      |

| F <sub>CLK(SCLK)</sub> | Data shift clock frequency                | SCLK                                                                                           |      |     | 25       | MHz  |

| F <sub>CLK(GCLK)</sub> | Grayscale control clock frequency         | GCLK                                                                                           |      |     | 33       | MHz  |

| t <sub>WH0</sub>       |                                           | SCLK                                                                                           | 10   |     |          |      |

| t <sub>WL0</sub>       | Dulas duration                            | SCLK                                                                                           | 10   |     |          |      |

| t <sub>WH1</sub>       | Pulse duration                            | GCLK                                                                                           | 15   |     |          | ns   |

| t <sub>WL1</sub>       |                                           | GCLK                                                                                           | 10   |     |          |      |

| t <sub>SU0</sub>       | Setup time                                | SIN - SCLK↑                                                                                    | 2    |     |          |      |

| t <sub>SU1</sub>       |                                           | LAT↑ - SCLK↑                                                                                   | 3    |     |          |      |

|                        |                                           | LAT↓ - SCLK↑                                                                                   | 5    |     |          | ns   |

| t <sub>SU2</sub>       |                                           | LAT↓ - SCLK↑, for READSID, READFC1, and READFC2                                                | 50   |     |          | 110  |

| t <sub>SU3</sub>       | - Cottap time                             | LAT↓ (Vsync command) - GCLK↑                                                                   | 2500 |     |          |      |

| t <sub>SU4</sub>       |                                           | The last LAT↓ for no all '0' data latching to resume normal mode – GCLK↑, PSAVE_ENA bit = '1b' | 50   |     |          | μS   |

| t <sub>SU5</sub>       |                                           | The last GCLK↑ - the 1st GCLK↑ of next line                                                    | 20   | ·   |          | ns   |

| t <sub>H0</sub>        | Hold time                                 | SCLK↑ - SIN                                                                                    | 2    |     |          |      |

| t <sub>H1</sub>        |                                           | SCLK↑ - LAT↑                                                                                   | 2    |     |          | ns   |

| t <sub>H2</sub>        |                                           | SCLK↑ - LAT↓                                                                                   | 13   |     |          |      |

<sup>(1)</sup> Specified by design

#### 8.4 Thermal Information

|                       |                                              | TLC5958 |      |

|-----------------------|----------------------------------------------|---------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTQ     | UNIT |

|                       |                                              | 56 PINS |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 27.4    |      |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 13.6    |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.5     | 9000 |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.2     | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 5.5     |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.8     |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 8.5 Electrical Characteristics

At  $V_{CC}$ = 3.0V to 5.5V and  $T_A$ = -40°C to 85°C, VLED=5.0V, Typical values are at  $V_{CC}$ = 3.3V,  $T_A$ = 25°C (unless otherwise

|                    | PARAMETER                                  |                                       | TEST CONDITIONS                                                                                                                                                                           | MIN                  | TYP   | MAX             | UNIT |

|--------------------|--------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|-----------------|------|

| V <sub>OH</sub>    | 0                                          | High                                  | I <sub>OH</sub> = -2mA at SOUT                                                                                                                                                            | V <sub>CC</sub> -0.4 |       | V <sub>CC</sub> | V    |

| V <sub>OL</sub>    | Output voltage                             | Low                                   | I <sub>OL</sub> = 2 mA at SOUT                                                                                                                                                            |                      |       | 0.4             | V    |

| $V_{LOD0}$         |                                            |                                       | LODVTH = 00b                                                                                                                                                                              | 0.06                 | 0.11  | 0.16            |      |

| V <sub>LOD1</sub>  | 1.55                                       |                                       | LODVTH = 01b                                                                                                                                                                              | 0.2                  | 0.25  | 0.3             |      |

| $V_{LOD2}$         | LED open detection thre                    | esnoia                                | LODVTH = 10b                                                                                                                                                                              | 0.34                 | 0.39  | 0.44            | V    |

| $V_{LOD3}$         |                                            |                                       | LODVTH = 11b                                                                                                                                                                              | 0.44                 | 0.49  | 0.54            |      |

| V <sub>IREF</sub>  | Reference voltage output                   | ıt                                    | $R_{IREF} = 6.2 \text{ k}\Omega$ (1mA target), BC=0h, CCR/G/B=81h                                                                                                                         | 1.19                 | 1.209 | 1.228           | V    |

| I <sub>IN</sub>    | Input current (SIN, SCLI                   | <)                                    | $V_{IN} = V_{CC}$ or GND                                                                                                                                                                  | -1                   |       | 1               | μA   |

| I <sub>CC0</sub>   |                                            |                                       | SIN/SCLK/LAT/GSCLK=GND, GSn=0000h, BC=0h, CCR/G/B=81h, VOUTn = Vcc, RIREF=OPEN                                                                                                            |                      | 5.5   | 7               |      |

| I <sub>CC1</sub>   |                                            |                                       | SIN/SCLK/LAT/GSCK=GND, GSn=0000h, BC=4h, CCR/G/B=137h,VOUTn=Vcc, RIREF=7.5kΩ (lo=10mA target)                                                                                             |                      | 7     | 9               |      |

| I <sub>CC2</sub>   | Supply current (Vcc)                       |                                       | SIN/SCLK/LAT=GND, GCLK=33MHz, $T_{SU5}$ = 200nS, 8+8 mode, GSn=FFFFh, BC=4h, CCR/G/B=137h, VOUTn=Vcc-1V when channel on, VOUTn=Vcc when channel off. RIREF=7.5k $\Omega$ (Io=10mA target) |                      | 25    | 31              | mA   |

| I <sub>CC3</sub>   |                                            |                                       | SIN/SCLK/LAT=GND, GCLK=33MHz, TSU5=200nS, 8+8 mode, GSn=FFFFh, BC=7h, CCR/G/B=1F5h, VOUTn=Vcc-2.5V when channel on, VOUTn=Vcc when channel off. RIREF=7.5kΩ (Io=25mA target)              |                      | 28    | 33              |      |

| I <sub>CC4</sub>   |                                            |                                       | In power save mode                                                                                                                                                                        |                      | 0.9   | 1.5             |      |

| Δl <sub>OLC0</sub> | Constant current error (OUTx0-15, x=R/G/B) | Channel-to-<br>channel <sup>(1)</sup> | All OUTn=on, BC=0h, CCR/G/B=81h, VOUTn=VOUTfix=1V, RIREF=6.2kΩ(1mA target), T <sub>A</sub> = +25°C, at same color grouped output of OUTR0-15, OUTG0-15 and OUTB0-15                       |                      | ±1%   | ±3%             |      |

| ΔI <sub>OLC1</sub> | Constant current error (OUTx0-15, x=R/G/B) | Device-to-<br>device <sup>(2)</sup>   | All OUTn=on, BC=0h, CCR/G/B=81h, VOUTn=VOUTfix=1V, RIREF=6.2kΩ(1mA target), T <sub>A</sub> =+25°C, at same color grouped output of OUTR0-15, OUTG0-15 and OUTB0-15                        |                      | ±1%   | ±2%             |      |

| ΔI <sub>OLC2</sub> | Line regulation <sup>(3)</sup>             |                                       | VCC=3.0 to 5.5V, All OUTn=on, BC=0h, CCR/G/B=81h, VOUTn=VOUTfix=1V, RIREF=6.2kΩ (1mA target)                                                                                              |                      | ±1    | ±1.5            | %/V  |

| ΔI <sub>OLC3</sub> | Load regulation <sup>(4)</sup>             |                                       | All OUTn=on, BC=0h, CCR/G/B=81h, VOUTn=1 to 3V, VOUTfix=1V, RIREF=6.2kΩ (1mA target)                                                                                                      |                      | ±1    | ±1.5            | %/V  |

The deviation of each outputs in same color group (OUTR0~15 or OUTG0~15 or OUTB0~15) from the average of same color group constant current. The deviation is calculated by the formula. (X=R or G or B, n=0~15)

$$\Delta(\%) = \left| \frac{IOUTXn}{\frac{(IOUTX0 + IOUTX1 + ... + IOUTX14 + IOUTX15)}{16}} - 1 \right| \times 100$$

The deviation of the average of constant-current in each color group from the ideal constant-current value. (X = R or G or B):

$$\Delta(\%) = \begin{bmatrix} \frac{\text{(IOUTX0 + IOUTX1 + ... + IOUTX15)}}{16} - \frac{\text{(Ideal Output Current)}}{16} \\ & \text{Ideal Output Current} \end{bmatrix} \times 100$$

Ideal current is calculated by the following equation:

Ideal Output (mA) = Gain

$$\times \left[ \frac{V_{IREF}}{R_{IREF}(\Omega)} \right] \times CCR$$

(or CCG, CCB)/511d, VIREF = 1.209V (Typ),

Refer to Table 1 for the Gain at chosen BC.

(3) Line regulation is calculated by the following equation. (X=R or G or B, n=0~15):

$$\Delta \text{(\%V)} = \left[\frac{\text{(IOUTXn at VCC} = 5.5V)}{\text{(IOUTXn at VCC} = 3.0V)}\right] \times \frac{100}{5.5V - 3V}$$

Load regulation is calculated by the following equation. (X=R or G or B, n=0~15):

$$\Delta(\%V) = \left[\frac{\text{(IOUTXn at VOUTXn = 3V)} - \text{(IOUTXn at VOUTXn = 1V)}}{\text{(IOUTXn at VOUTXn = 1V)}}\right] \times \frac{100}{3V - 1V}$$

### **Electrical Characteristics (continued)**

At  $V_{CC}$ = 3.0V to 5.5V and  $T_A$ = -40°C to 85°C, VLED=5.0V, Typical values are at  $V_{CC}$ = 3.3V,  $T_A$ = 25°C (unless otherwise noted).

|                       | PARAMETER                                  |                                       | TEST CONDITIONS                                                                                                                                                                | MIN   | TYP   | MAX   | UNIT |

|-----------------------|--------------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| ΔI <sub>OLC4</sub>    | Constant current error (OUTx0-15, x=R/G/B) | Channel-to-<br>channel <sup>(1)</sup> | All OUTn=on, BC=7h, CCR/G/B=1F7h, VOUTn=VOUTfix=1V, RIREF=7.5k $\Omega$ (25mA target), T <sub>A</sub> =+25°C, at same color grouped output of OUTR0-15, OUTG0-15 & OUTB0-15    | Milit | ±1%   | ±3%   | ONIT |

| $\Delta I_{OLC5}$     | Constant current error (OUTx0-15, x=R/G/B) | Device-to-<br>device <sup>(2)</sup>   | All OUTn=on, BC=7h, CCR/G/B=1F7h, VOUTn=VOUTfix=1V, RIREF=7.5k $\Omega$ (25mA target), T <sub>A</sub> = +25°C, at same color grouped output of OUTR0-15, OUTG0-15 and OUTB0-15 |       | ±1%   | ±2%   |      |

| $\Delta I_{OLC6}$     | Line regulation <sup>(3)</sup>             |                                       | VCC=3.0 to 5.5V, All OUTn=on, BC=7h, CCR/G/B=1F7h, VOUTn=VOUTfix=1V, RIREF=7.5Kohm (25mA target)                                                                               |       | ±1    | ±1.5  | %/V  |

| ΔI <sub>OLC7</sub>    | Load regulation <sup>(4)</sup>             |                                       | All OUTn=on, BC=7h, CCR/G/B=1F7h, VOUTn=1 to 3V, VOUTfix=1V, RIREF=7.5kΩ (25mA target)                                                                                         |       | ±1    | ±1.5  | %/V  |

| T <sub>TSD</sub>      | Thermal shutdown thres                     | shold <sup>(5)</sup>                  |                                                                                                                                                                                | 160   | 170   | 180   | °C   |

| T <sub>HYS</sub>      | Thermal shutdown hyste                     | erisis                                |                                                                                                                                                                                |       | 10    |       | °C   |

| V <sub>ISP(in)</sub>  | IREF resistor short prote                  | ection threshold                      |                                                                                                                                                                                | 0.135 | 0.19  |       | V    |

| V <sub>ISP(out)</sub> | IRFF resistor short-protection release     |                                       |                                                                                                                                                                                |       | 0.325 | 0.375 | V    |

| R <sub>PDWN</sub>     | Pull-down resistor                         |                                       | LAT                                                                                                                                                                            | 250   | 500   | 750   | kΩ   |

| R <sub>PUP</sub>      | Pull-up resistor                           |                                       | GCLK                                                                                                                                                                           | 250   | 500   | 750   | kΩ   |

| V <sub>knee</sub> (5) | Knee voltage (OUTX 0~                      | 15), X=R/G/B                          | All OUTn=on, BC=4h, CCR/G/B=137h, Riref=7.5kΩ. (Io=10mA target)                                                                                                                |       | 0.32  | 0.35  | V    |

<sup>(5)</sup> Specified by design.

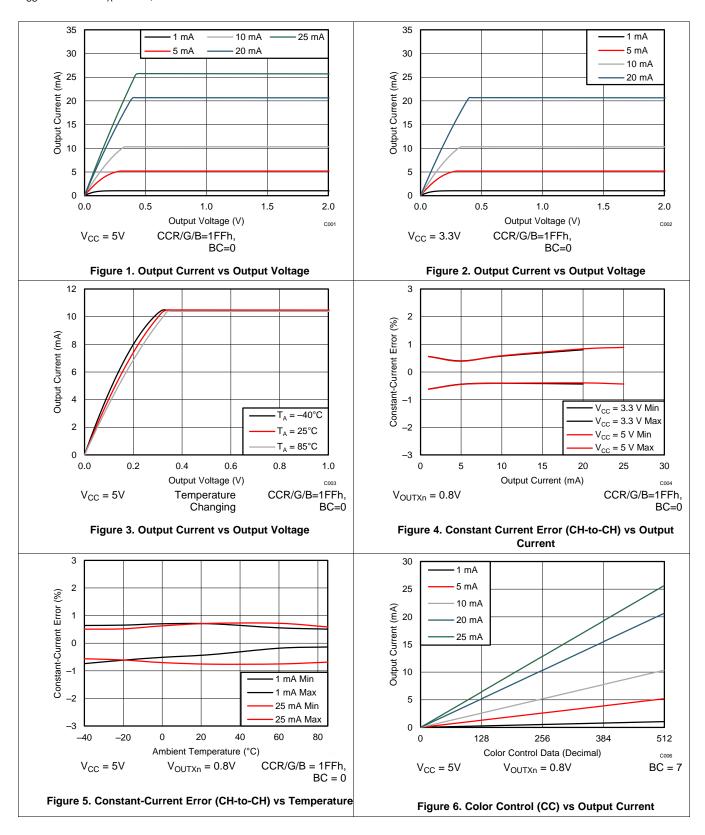

### 8.6 Typical Characteristics

$V_{CC}$ = 3.3V and  $T_A$ = 25°C, unless otherwise noted.

# TEXAS INSTRUMENTS

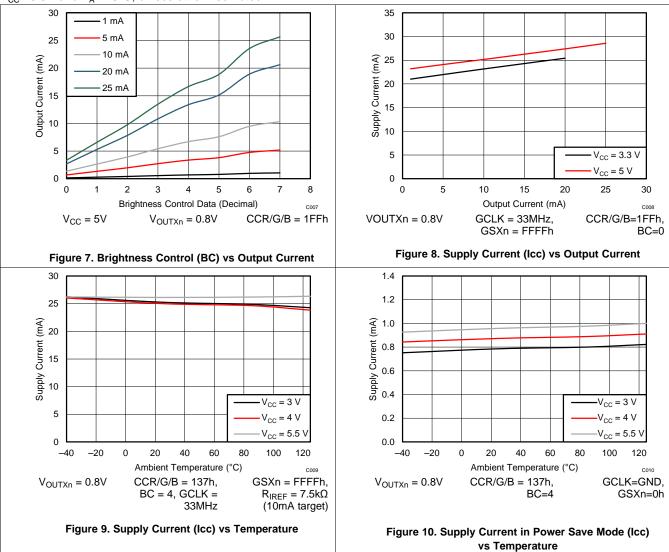

#### **Typical Characteristics (continued)**

$V_{CC}$ = 3.3V and  $T_A$ = 25°C, unless otherwise noted.

### 9 Parameter Measurement Information

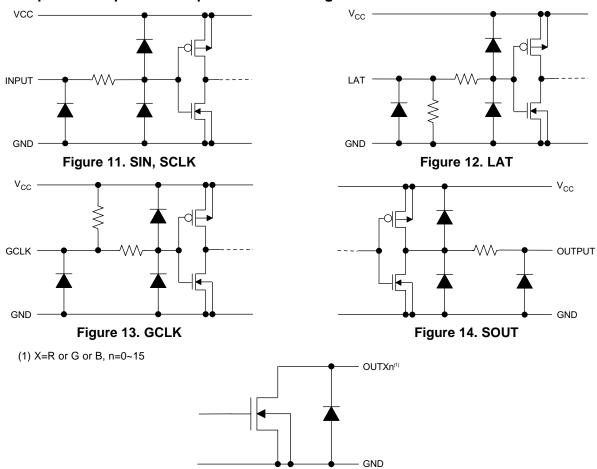

### 9.1 Pin Equivalent Input and Output Schematic Diagrams

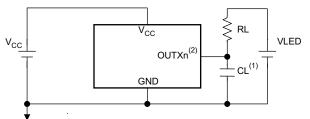

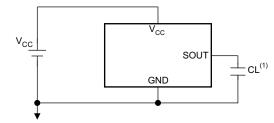

Figure 15. OUTR0/G0/B0 Through OUTR15/G15/B15

### Pin Equivalent Input and Output Schematic Diagrams (continued)

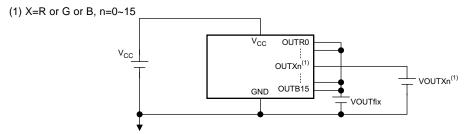

#### 9.1.1 Test Circuits

- (1) CL includes measurement probe and jig capacitance.

- (2) X=R or G or B, n=0~15

- (1) CL includes measurement probe and jig capacitance.

Figure 16. Rise Time and Fall Time Test Circuit for OUTXn

Figure 17. Rise Time and Fall Time Test Circuit for SOUT

Figure 18. Constant Current Test Circuit for OUTXn

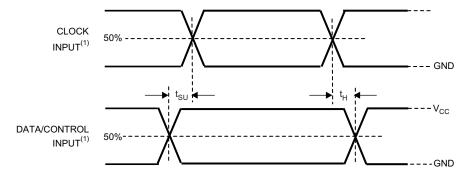

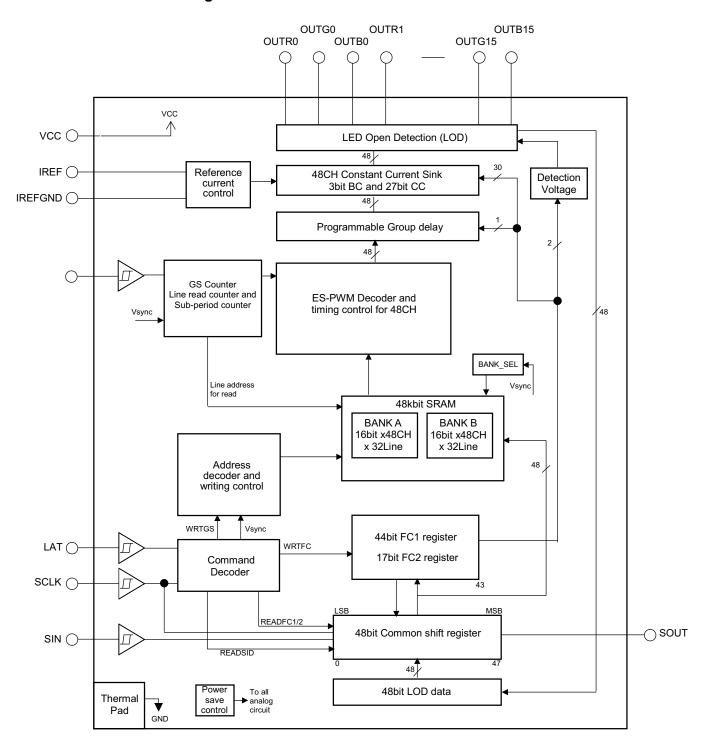

### 9.2 Timing Diagrams

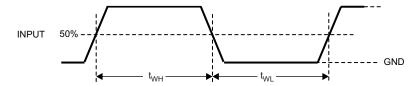

$\mathbf{t}_{\mathrm{WH0}}, \mathbf{t}_{\mathrm{WL0}}, \mathbf{t}_{\mathrm{WH1}}, \mathbf{t}_{\mathrm{WL1}}, \mathbf{t}_{\mathrm{WH2}}$

$t_{{\rm SU0},}t_{{\rm SU1},}t_{{\rm SU2},}t_{{\rm SU3},}t_{{\rm SU4},}t_{{\rm H0},}t_{{\rm H1},}t_{{\rm H2}}$

- (1) Input pulse rise and fall time is 1~3ns

- (2) 8 + 8 mode (SEL\_PWM=0)

Figure 19. Timing Diagrams

#### 10 Detailed Description

#### 10.1 Overview

The TLC5958 is a 48 channels constant-current sink driver for multiplexing system with 1 to 32 duty ratio. Each channel has an individually-adjustable, 65536-step, pulse width modulation (PWM) grayscale (GS).

48K bit display memory is implemented to increase the visual refresh rate and to decrease the GS data writing frequency.

The TLC5958 support output current range from 1mA to 25mA, channel-to-channel accuracy is 3% max, device-to-device accuracy is 2% max in all current range. Besides, it implement Low Gray Scale Enhancement (LGSE™) technology to improve the display quality at low grayscale condition. These features make TLC5958 more suitable for high-density multiplexing application.

The output channels are grouped into three groups, each group has 16 channels. Each group has a 512-step color brightness control (CC) function. The maximum current value of all 48 channels can be set by 8-step global brightness control (BC) function. CC and BC can be used to adjust the brightness deviation between LED drivers. GS, CC, and BC data are accessible via a serial interface port.

The TLC5958 has one error flag: LED open detection (LOD), which can be read via a serial interface port. Besides, The TLC5958 also have Thermal shut down(TSD) and Iref resistor short protection(ISP), which make sure a higher system reliability. The TLC5958 also has a power-save mode that sets the total current consumption to 0.8mA (typ) when all outputs are off.

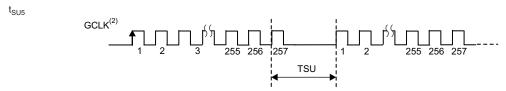

#### 10.2 Functional Block Diagram

(1)

#### 10.3 Device Functional Modes

After power on, all OUTXn of the TLC5958 are turned off. All the internal counters and function control registers (FC1/FC2) are initialized. The following list is a brief summary of the sequence to operate the TLC5958, to give users a general idea how the device works. After that, the function block related to each step is detailed in the following sections.

- 1. According to required LED current, choose BC & CC code, select the current programming resistor RIREF.

- 2. Send WRTFC command to set FC1/2 register value if the default value need be changed.

- 3. Write GS data of all lines (max 32 lines) into one of the two memory BANKs.

- 4. Send Vsync command, the BANK with the GS data written just now will be displayed.

- 5. Input GCLK continuously, 257GCLK (or 513GCLK) as a segment. Between the interval of two segments, supply voltage should be switched from one line to next line accordingly.

- 6. During the same period of step 5, GS data for next frame should be written into another BANK.

- 7. When the time of one frame ends, Vsync command should be input to swap the purpose of the two BANKs.

Repeat step 5 through 7.

#### 10.3.1 Brightness Control (BC) Function

The TLC5958 is able to adjust the output current of all constant-current outputs simultaneously. This function is called global brightness control (BC). The global BC for all outputs is programmed with a 3-bit word, thus all output currents can be adjusted in 8 steps from 12.9% to 100% for a given current-programming resistor,  $R_{IREF}$  (See Table 2).

BC data can be set via the serial interface. When the BC data changes, the output current also changes immediately. When the device is powered on, the BC data in the function control (FC) register FC1 is set to 4h as the initial value.

#### 10.3.2 Color Brightness Control (CC) Function

The TLC5958 is able to adjust the output current of each of the three color groups OUTR0-OUTR15, OUTG0-OUTG15, and OUTB0-OUTB15 separately. This function is called color brightness control (CC). For each color, it has 9-bit data latch CCR,CCG, or CCB in FC1 register . Thus, all color group output currents can be adjusted in 512 steps from 0% to 100% of the maximum output current, I<sub>OLCMax</sub>. (See the next section for more detail about I<sub>OLCMax</sub>). The CC data are entered via the serial interface. When the CC data change, the output current also changes immediately.

When the IC is powered on, the CC data are set to '100h'. Equation 1 calculates the actual output current.

Where:

$I_{OLCMax}$  = the maximum channel current for each channel, determined by BC data and  $R_{IREF}$  (See Equation 2) CCR/G/B = the color brightness control value for each color group in the FC1 register (000h to 1FFh)

Table 1 shows the CC data versus the constant-current against I<sub>OLCMax</sub>.

#### **Device Functional Modes (continued)**

Table 1. CC Data vs Current Ratio and Set Current Value

| CC DA                    | ATA (CCR or CCG or C | CCB)             | RATIO OF OUTPUT<br>CURRENT<br>TO I <sub>olcMax</sub> (%, typical) |                            | (mA, R <sub>IREF</sub> = 7.41 kΩ) |

|--------------------------|----------------------|------------------|-------------------------------------------------------------------|----------------------------|-----------------------------------|

| BINARY                   | DECIMAL              | HEX              |                                                                   | BC = 7h<br>(lolcMax =25mA) | BC = 0h<br>(lolcMax=3.2mA)        |

| 0 0000 0000              | 0                    | 00               | 0                                                                 | 0                          | 0                                 |

| 0 0000 0001              | 1                    | 01               | 0.2                                                               | 0.05                       | 0.006                             |

| 0 0000 0010              | 2                    | 02               | 0.4                                                               | 0.10                       | 0.013                             |

|                          |                      |                  |                                                                   |                            |                                   |

| 1 0000 0000<br>(Default) | 256<br>(Default)     | 100<br>(Default) | 50.1                                                              | 12.52                      | 1.621                             |

|                          |                      |                  |                                                                   |                            |                                   |

| 1 1111 1101              | 509                  | 1FD              | 99.6                                                              | 24.90                      | 3.222                             |

| 1 1111 1110              | 510                  | 1FE              | 99.8                                                              | 24.95                      | 3.229                             |

| 1 1111 1111              | 511                  | 1FF              | 100.0                                                             | 25                         | 3.235                             |

#### 10.3.3 Select R<sub>IREF</sub> For a Given BC

The maximum output current per channel,  $I_{OLCMax}$ , is determined by resistor  $R_{IREF}$ , placed between the IREF and IREFGND pins, and the BC code in FC1 register. The voltage on IREF is typically 1.209V.  $R_{IREF}$  can be calculated by Equation 2.

$$Riref(k\Omega) = Viref(V) / IOLCMax(mA) \times Gain$$

(2)

#### Where:

$V_{IREF}$  = the internal reference voltage on IREF (1.209V, typical)

I<sub>OLCMax</sub> is the largest current for each output at CCR/G/B=1FFh.

Gain = the current gain at a selected BC code (See Table 2)

Table 2. Current Gain Versus BC Code

| BC DA                 | ATA                                  |                            | RATIO OF                                   |

|-----------------------|--------------------------------------|----------------------------|--------------------------------------------|

| BINARY                | HEX                                  | GAIN                       | GAIN / GAIN_MAX (AT MAX<br>BC)             |

| 000 (recommend)       | 0 (recommend                         | 20.4                       | 12.9%                                      |

| 001                   | 1                                    | 40.3                       | 25.6%                                      |

| 010                   | 2                                    | 59.7                       | 52.4%                                      |

| 011                   | 3                                    | 82.4                       | 12.9%                                      |

| 100 (default)         | 4 (default)                          | 101.8                      | 64.7%                                      |

| 101                   | 5                                    | 115.4                      | 73.3%                                      |

| 110                   | 6                                    | 144.3                      | 91.7%                                      |

| 111                   | 7                                    | 157.4                      | 100%                                       |

| NOTE: Recommend using | a smaller BC code for better perform | ance. For noise immunity p | urposes, suggest R <sub>IREF</sub> < 60 kΩ |

#### 10.3.4 Choosing BC/CC For a Different Application

BC is mainly used for global brightness adjustment between day and night. Suggested BC is 4h, which is in the middle of the range, thus, one can change brightness up and down flexibly.

CC can be used to fine tune the brightness in 512 steps, this is suitable for white balance adjustment between RGB color group. To get a pure white color, the general requirement for the luminous intensity ratio of R, G, B LED is 3:6:1. Depending on the characteristics of the LED (Electro-Optical conversion efficiency), the current ratio of R, G, B LED will be much different from this ratio. Usually, the Red LED needs the largest current. One can choose 511d (the max value) CC code for the color group that needs the largest initial current, then choose proper CC code for the other two color groups according to the current ratio requirement of the LED used.

#### 10.3.4.1 Example 1: Red LED Current is 20mA, Green LED Needs 12mA, Blue LED needs 8mA

- 1. Red LED needs the largest current, so choose 511d for CCR

- 2. 511 x 12mA / 20mA = 306.6, thus choose 307d for CCG. With same method, choose 204d for CCB.

- 3. According to the required red LED current, choose 7h for BC.

- 4. According to Equation 2,  $R_{IREF} = 1.209V/20mA \times 157.4 = 9.5 k\Omega$

In this example, we choose 7h for BC, instead of using the default 4h. This is because the Red LED current is 20mA, approaching the upper limit of current range. To prevent the constant output current from exceeding the upper limit in case a larger BC code is input accidently, we choose the maximum BC code here.

#### 10.3.4.2 Example 2: Red LED Current is 5mA, Green LED Needs 2mA, Blue LED Needs 1mA.

- 1. Red LED needs the largest current, so choose 511d for CCR.

- 2. 511 x 2mA / 5mA = 204.4, thus choose 204d for CCG. With same method, choose 102d for CCB.

- 3. According to the required blue LED current, choose 0h for BC.

- 4. According to Equation 2,  $R_{IREF} = 1.209V / 5mA \times 20.4 = 4.93 \text{ k}\Omega$

In this example, we choose 0h for BC, instead of using the default 4h. This is because the Blue LED current is 1mA, is approaching the lower limit of current range. To prevent the constant output current from exceeding the lower limit in case a lower BC code is input accidently, we choose the minimum BC code here. In general, if LED current is in the middle of the range (i.e, 10mA), one can just use the default 4h as BC code.

#### 10.3.5 LED Open Detection (LOD)

The LOD function detects faults caused by an open circuit in any LED string; or, a short from OUTXn to ground with low impedance. It does this by comparing the OUTXn voltage to the LOD detection threshold voltage level set by LODVLT in the FC1 register. If the OUTXn voltage is lower than the programmed voltage, the corresponding output LOD bit will be set to '1' to indicate a open LED. Otherwise, the output of that LOD bit is '0'. LOD data output by the detection circuit are valid only during the 'on' period of that OUTXn output channel. The LOD data are always '0' for outputs that are turned off.

#### 10.3.6 Power Save Mode (PSM)

The power-save mode (PSM) is enabled by setting PSAVE\_ENA (bit5 of FC2 register) to '1'. When power on, this bit default is '0'.

When this function is enabled, if the GS data received for next frame is all '0', IC will enter power save mode at the moment Vsync command input.

When the IC is in power-save mode, it resumes normal mode when it detects non-zero GS data input. In power-save mode all analog circuits such as constant current output and the LOD circuit are not operational; the device total current consumption, Icc, is below 1mA.

#### 10.3.7 Internal Pre-Charge FET

The internal pre-charge FET can prevent ghosting of multiplexed LED modules. One cause of this phenomenon is the charging current for parasitic capacitance of the OUTXn through the LED when the supply voltage switches from one common line to the next common line.

To prevent this unwanted charging current, TLC5958 uses an internal FET to pull OUTXn up to VCC -1.4V during the common line switching period. Thus, no charging current flows through LED and ghosting is eliminated.

#### 10.3.8 Thermal Shutdown (TSD)

The thermal shutdown (TSD) function turns off all IC constant-current outputs when the junction temperature (T<sub>J</sub>) exceeds 170°C (typ). It resumes normal operation when T<sub>I</sub> falls below 160°C (typ).

#### 10.3.9 IREF Resistor Short Protection (ISP)

The Iref resistor short protection (ISP) function prevents unwanted large currents from flowing though the constant-current output when the Iref resistor is shorted accidently. The TLC5958 turns off all output channels when the Iref pin voltage is lower than 0.19V (typ). When the Iref pin voltage goes higher than 0.325V (typ), the TLC5958 resumes normal operation.

#### 10.3.10 Noise Reduction

Large surge currents may flow through the IC and the board on which the device is mounted if all 48 LED channels turned on simultaneously at the 1st GCLK rising edge. This large surge current could induce detrimental noise and electromagnetic interference (EMI) into other circuits.

The TLC5958 separates the LED channels into 12 groups. Each group turns on sequentially with some delay between one group and the next group. By this operation, a soft-start feature provides for minimal inrush current.

### 11 Application and Implementation

Send request via email for Application Note: Build High Density, High Refresh Rate, Multiplexing LED Panel with TLC5958

#### 12 Power Supply Recommendations

The  $V_{CC}$  power supply voltage should be decoupled by placing a 0.1  $\mu$ F ceramic capacitor close to VCC pin and GND plane. Depending on panel size, several electrolytic capacitors must be placed on board equally distributed to get a well regulated LED supply voltage (VLED). VLED voltage ripple should be less than 5% of its nominal value. Furthermore, the VLED should be set to the voltage calculated by equation:

Where: Vf = maximum forward voltage of LED

### 13 Layout

#### 13.1 Layout Guidelines

- 1. Place the decoupling capacitor near the VCC pin and GND plane.

- 2. Place the current programming resistor Riref close to IREF pin and IREFGND pin.

- Route the GND pattern as widely as possible for large GND currents. Maximum GND current is approximately 1.2A

- 4. Routing between the LED cathode side and the device OUTXn pin should be as short and straight as possible to reduce wire inductance.

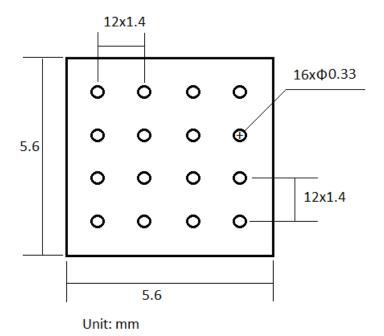

- 5. The PowerPAD™ must be connected to GND plane because the pad is used as power ground pin internally, there will be large current flow through this pad when all channels turn on. Furthermore, this pad should be connected to a heat sink layer by thermal via to reduce device temperature. One suggested thermal via pattern is shown as below. For more information about suggested thermal via pattern and via size, see "PowerPAD Thermally Enhanced Package", SLMA002G.

#### 13.2 Layout Example

### 14 Device and Documentation Support

#### 14.1 Trademarks

LGSE, PowerPAD are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

#### 14.2 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 14.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 15 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### PACKAGE OPTION ADDENDUM

6-Sep-2014

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|----------------------------|------------------|---------------------|--------------|----------------------|---------|

| TLC5958RTQR      | ACTIVE | QFN          | RTQ                | 56   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | TLC5958              | Samples |

| TLC5958RTQT      | ACTIVE | QFN          | RTQ                | 56   | 250            | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | TLC5958              | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead/Ball Finish Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# **PACKAGE OPTION ADDENDUM**

6-Sep-2014

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### PACKAGE MATERIALS INFORMATION

www.ti.com 23-Jun-2015

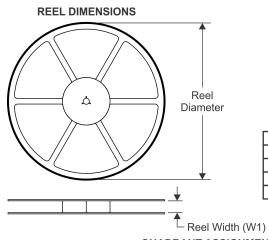

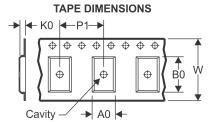

### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

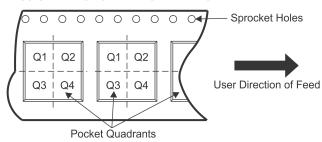

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| 7 til dillionolono aro nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|--------------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TLC5958RTQR                    | QFN             | RTQ                | 56 | 2000 | 330.0                    | 16.4                     | 8.3        | 8.3        | 1.1        | 12.0       | 16.0      | Q2               |

| TLC5958RTQT                    | QFN             | RTQ                | 56 | 250  | 180.0                    | 16.4                     | 8.3        | 8.3        | 1.1        | 12.0       | 16.0      | Q2               |

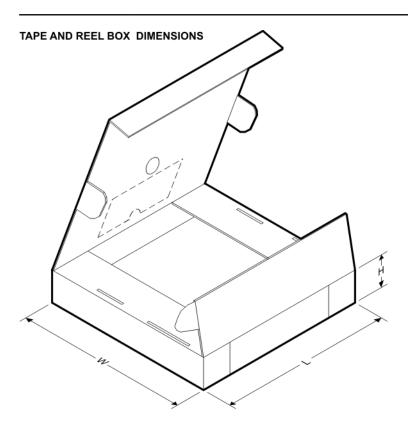

www.ti.com 23-Jun-2015

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLC5958RTQR | QFN          | RTQ             | 56   | 2000 | 367.0       | 367.0      | 38.0        |

| TLC5958RTQT | QFN          | RTQ             | 56   | 250  | 210.0       | 185.0      | 35.0        |

8 x 8, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224653/A

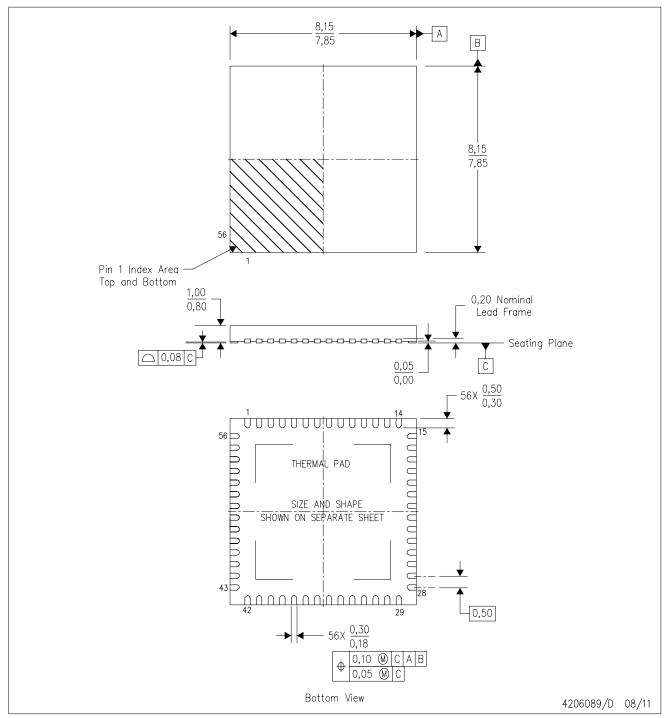

### RTQ (S-PVQFN-N56)

### PLASTIC QUAD FLATPACK NO-LEAD

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5—1994.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) Package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Package complies to JEDEC MO-220.

# RTQ (S-PVQFN-N56)

### PLASTIC QUAD FLATPACK NO-LEAD

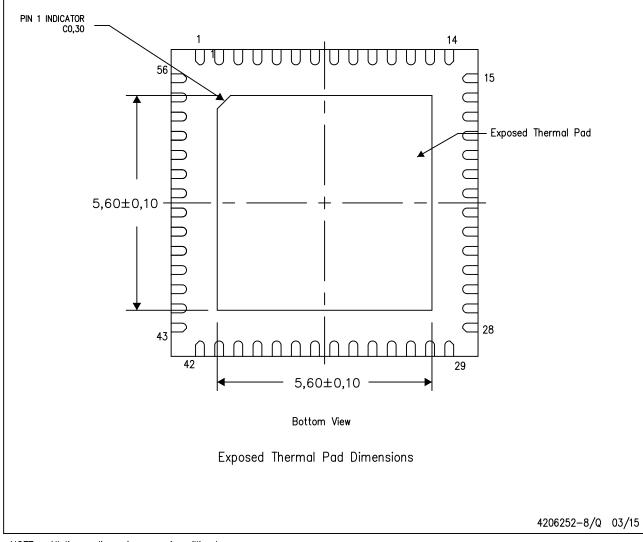

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated