## Multitopology single-channel DC-DC controller

#### **Features**

- Wide input voltage (up to 58 V) and output voltage range (up to 70 V)

- Switching frequency range from 100 kHz to 500 kHz and synchronization at 2.2 MHz with an external clock source

- EMC optimized device

- Analog adjust input

- Overvoltage, Short to ground, overcurrent, open feedback and overtemperature diagnostic output

- PMOS gate driver for dimming and protection with enhanced dimming features

- LED current accuracy ±3.5%

| Product type | Package     | Marking   |

|--------------|-------------|-----------|

| TLD6098-1EP  | PG-TSDSO-14 | TLD6098-1 |

## **Potential applications**

- LED driver for: front light module, rear light module, interior light

- Voltage regulator

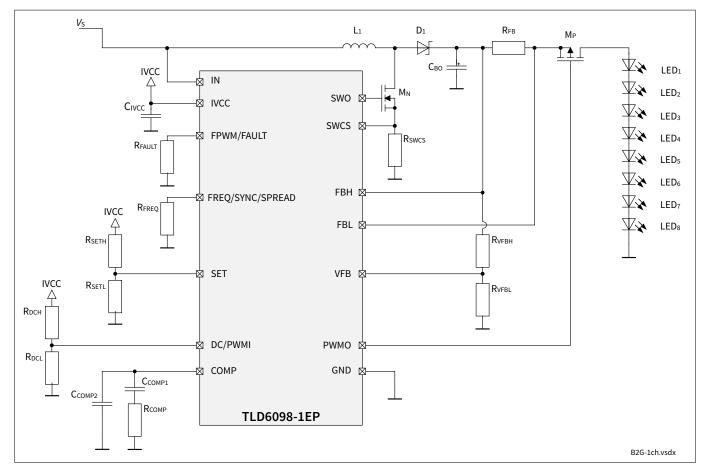

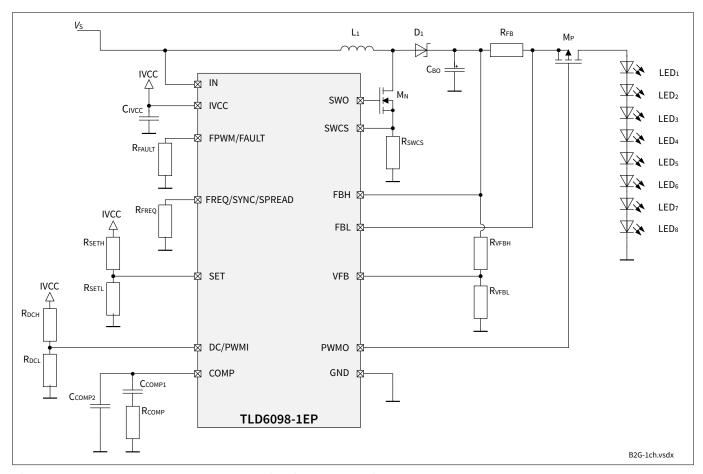

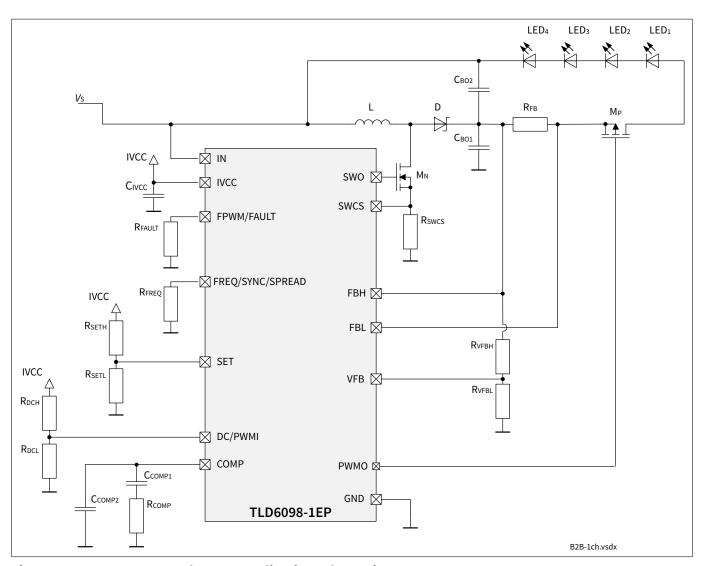

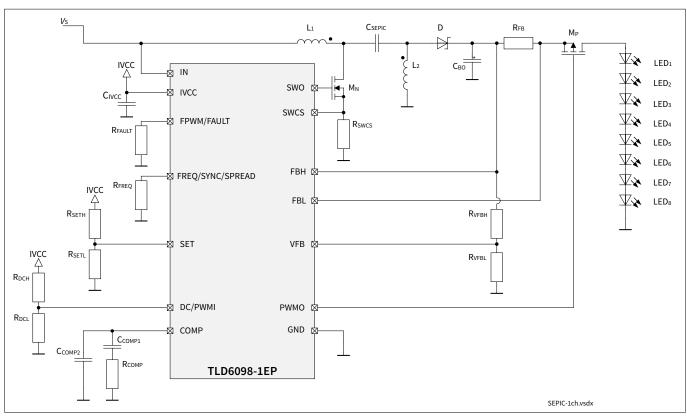

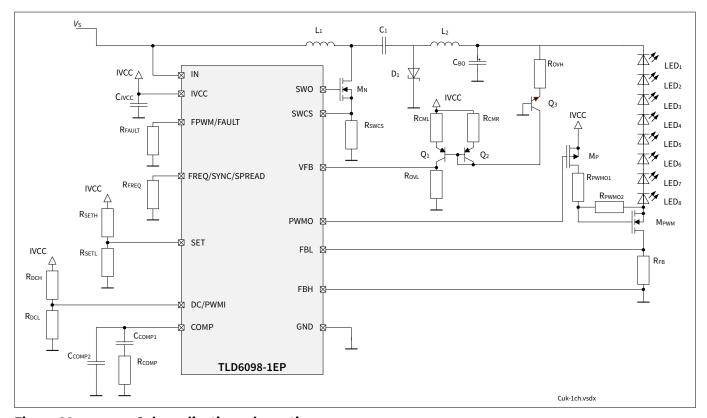

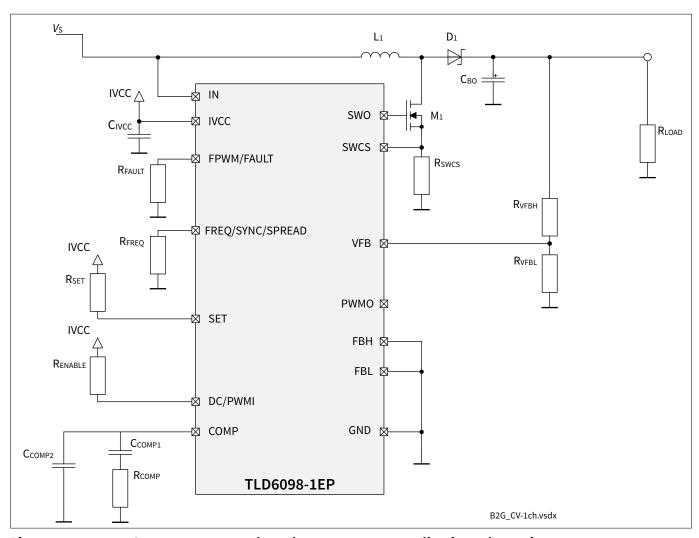

Figure 1 Application diagram

#### Multitopology single-channel DC-DC controller

**Description of TLD6098-1EP**

## **Description of TLD6098-1EP**

TLD6098-1EP is a multi-topology DC-DC controller designed for LED applications with built-in protection features to implement a compact LED driver.

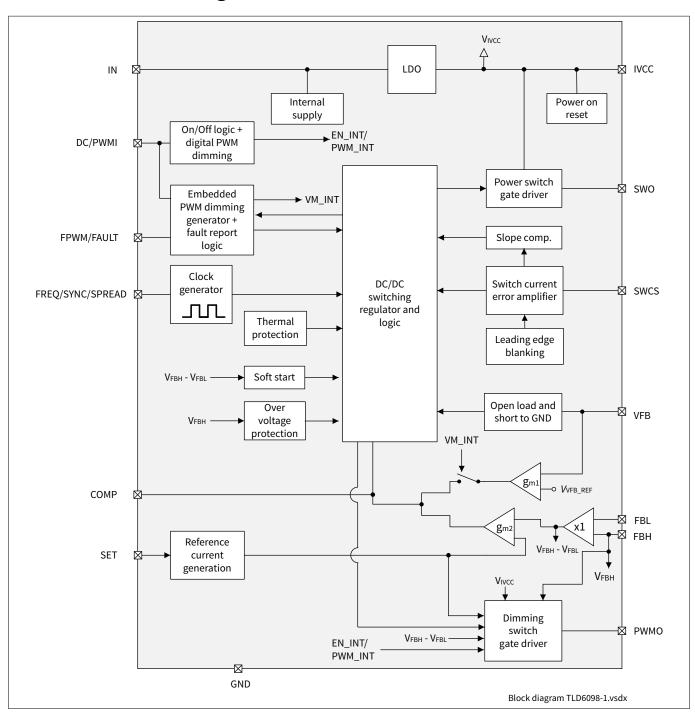

The output current is regulated by means of peak current control loop. An internal slope compensation is used to avoid sub-harmonic oscillation at high duty cycle (e.g. higher than 50%).

The current accuracy is better than 3.5% (with no analog adjustment applied) over the operating temperature range. A rail to rail current sense amplifier provides flexibility on the topology choice needed to supply LED string with more than 20 white LED (up to 70 V at output).

The switching frequency can be adjusted from 100 kHz to 500 kHz using an external resistor. A synchronization with an external clock is also possible. The device incorporates even a spread spectrum modulator to achieve easy fulfilment of electromagnetic emission standards.

TLD6098-1EP can drive an external PMOS for dimming and protection.

For this purpose the device incorporates even a PWM generator controlled by an analog voltage on DC/PWMI pin. The generated PWM signal has the duty cycle adjustable from 0 to 100% with 10 bits of resolution and the frequency range programmable from 150 Hz to 750 Hz. On the same DC/PWMI pin the digital PWM signal can also be used.

#### **Product validation**

Qualified for automotive applications.

Product validation according to AEC-Q100.

## Multitopology single-channel DC-DC controller

## **Table of contents**

## **Table of contents**

|                 | Table of contents                                          |    |

|-----------------|------------------------------------------------------------|----|

| 1               | Block diagram                                              | 5  |

| 2               | Pin configuration                                          | 6  |

| 3               | General product characteristics                            | 8  |

| 3.1             | Absolute maximum ratings                                   | 8  |

| 3.2             | Functional range                                           | 9  |

| 3.3             | Thermal resistance                                         | 10 |

| 4               | Switching regulator                                        | 11 |

| 4.1             | Soft start                                                 | 11 |

| 4.2             | Electrical characteristics                                 | 14 |

| 5               | Linear regulator                                           | 17 |

| 5.1             | Undervoltage protection for the external switching MOSFET  |    |

| 5.2             | Electrical characteristics                                 |    |

|                 | Switching frequency setup and synchronization              |    |

| <b>6</b><br>6.1 | Switching frequency setup with external resistor           |    |

| 6.1.1           | Electrical characteristics                                 |    |

| 6.1.2           | Spread Spectrum                                            |    |

| 6.1.2.1         | Electrical characteristics                                 |    |

| 6.2             | Synchronization with external clock (low frequency mode)   |    |

| 6.2.1           | Electrical characteristics                                 |    |

| 6.3             | Synchronization with external clock (high frequency range) |    |

| 7               | Analog output adjustment                                   |    |

| <b>.</b><br>7.1 | Electrical characteristics                                 |    |

| 8               | Dimming functions                                          |    |

| 8.1             | Electrical characteristics                                 |    |

| 8.2             | Digital PWM dimming                                        |    |

| 8.2.1           | Electrical characteristics                                 |    |

| 8.3             | Embedded PWM engine                                        |    |

| 8.3.1           | Electrical characteristics                                 |    |

| 9               | Protections and fault management                           | 31 |

| 9.1             | Electrical characteristics                                 |    |

| 9.2             | Short to ground                                            |    |

| 9.2.1           | Electrical characteristics                                 |    |

| 9.3             | Output overvoltage and voltage regulation                  |    |

| 9.3.1           | Electrical characteristics                                 |    |

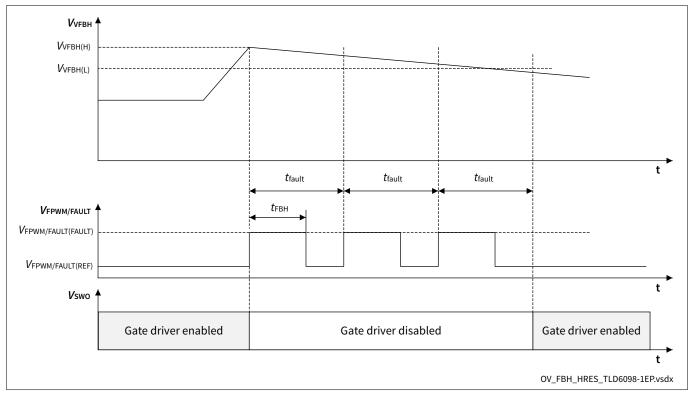

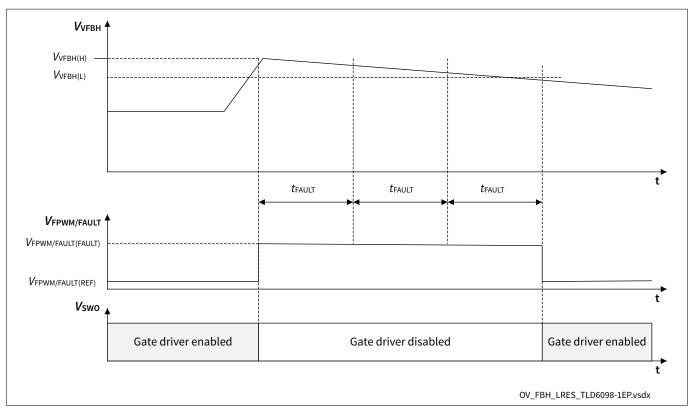

| 9.4             | Overvoltage on FBH pin                                     | 34 |

| 9.4.1           | Electrical characteristics                                 | 36 |

## Multitopology single-channel DC-DC controller

## **Table of contents**

| 9.5   | Output overcurrent         | 37 |

|-------|----------------------------|----|

| 9.5.1 | Electrical characteristics | 40 |

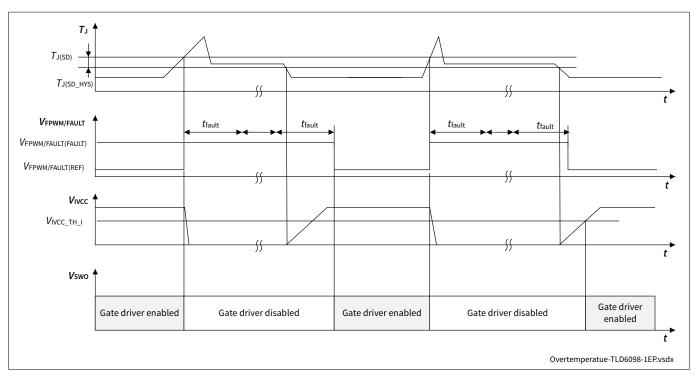

| 9.6   | Overtemperature            | 40 |

| 9.6.1 | Electrical characteristics | 41 |

| 10    | Application information    | 42 |

| 11    | Package                    | 46 |

| 12    | Revision history           | 47 |

|       | Disclaimer                 | 48 |

#### Multitopology single-channel DC-DC controller

#### 1 Block diagram

## 1 Block diagram

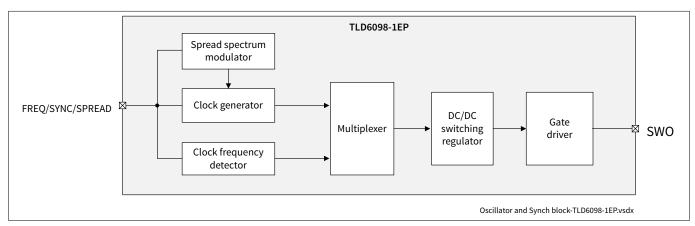

Figure 2 Block diagram

## Multitopology single-channel DC-DC controller

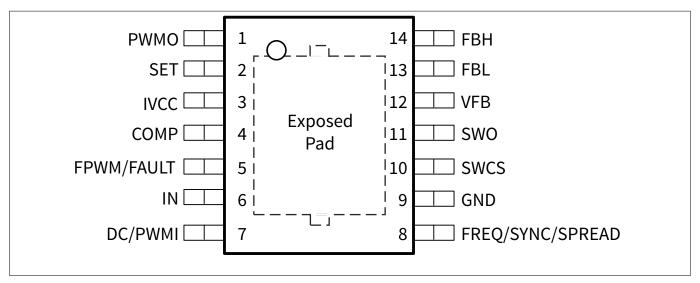

#### 2 Pin configuration

## 2 Pin configuration

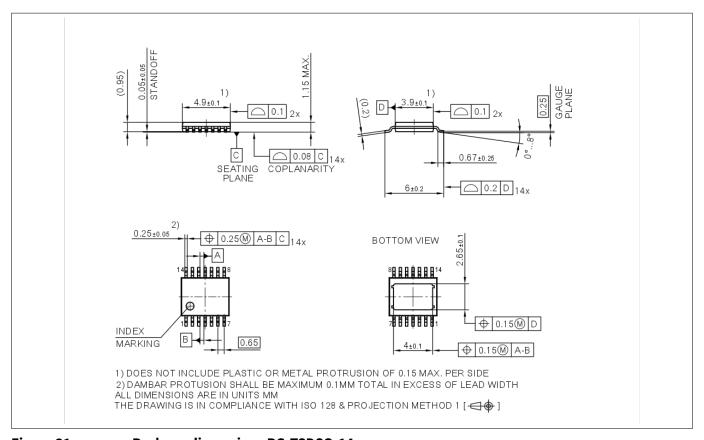

Figure 3 Pin configuration PG-TSDSO-14

Table 1 Pin configuration PG-TSDSO-14

| Name       | Pos. | Description                                                   | Direction |

|------------|------|---------------------------------------------------------------|-----------|

| PWMO       | 1    | PMOS driver for dimming and protection                        | Output    |

|            |      | Connect to gate of external MOSFET                            |           |

|            |      | Pin must be left open if external MOSFET is not used          |           |

| SET        | 2    | Analog adjustment                                             | Input     |

|            |      | Load current adjustment pin                                   |           |

|            |      | Pin must not be left open                                     |           |

|            |      | If analog adjustment is not used, connect to IVCC pin         |           |

| IVCC       | 3    | Internal linear voltage regulator                             | Output    |

|            |      | Used for internal biasing and gate drive                      |           |

|            |      | Bypass with external capacitor                                |           |

|            |      | Pin must not be left open                                     |           |

| СОМР       | 4    | Compensation                                                  | Input     |

|            |      | Connect R and C network for stability                         |           |

| FPWM/FAULT | 5    | PWM frequency selector/Fault                                  | Input/    |

|            |      | Connect external R to set PWM frequency                       | Output    |

|            |      | Faults are reported by raising the voltage on this pin        |           |

| IN         | 6    | Supply                                                        | Input     |

|            |      | Supply for internal biasing                                   |           |

| DC/PWMI    | 7    | PWM adjustment                                                | Input     |

|            |      | Set duty cycle of PWM engine or digital input for PWM dimming |           |

(table continues...)

## Multitopology single-channel DC-DC controller

## 2 Pin configuration

#### (continued) Pin configuration PG-TSDSO-14 Table 1

| Name             | Pos. | Description                                                                                                 | Direction |

|------------------|------|-------------------------------------------------------------------------------------------------------------|-----------|

| FREQ/SYNC/SPREAD | 8    | Frequency selector or synchronization                                                                       | Input     |

|                  |      | Connect external resistor to GND to set switching frequency                                                 |           |

|                  |      | Apply square waveform for synchronization                                                                   |           |

| GND              | 9    | Ground                                                                                                      | _         |

| SWCS             | 10   | Current sense/Power ground                                                                                  | Input     |

|                  |      | Detects peak current through power switch                                                                   |           |

|                  |      | Power ground of gate driver of SWO                                                                          |           |

| SWO              | 11   | Switch gate driver                                                                                          | Output    |

|                  |      | Connect to gate of external switching power n-channel MOSFET                                                |           |

| VFB              | 12   | Overvoltage/Voltage loop reference                                                                          | Input     |

|                  |      | Connect to resistive voltage divider to set the maximum voltage at output and the short to ground threshold |           |

| FBL              | 13   | Voltage feedback negative                                                                                   | Input     |

|                  |      | Inverting input (-)                                                                                         |           |

| FBH              | 14   | Voltage feedback positive                                                                                   | Input     |

|                  |      | Non inverting input (+)                                                                                     |           |

| Exposed pad      | EP   | Exposed pad                                                                                                 | _         |

|                  |      | Used only for heat dissipation                                                                              |           |

|                  |      | Connect to pin 9 (GND)                                                                                      |           |

## Multitopology single-channel DC-DC controller

#### 3 General product characteristics

## **3** General product characteristics

## 3.1 Absolute maximum ratings

#### Table 2 Absolute maximum ratings

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

Not subject to production test, specified by design

| Parameter                           | Symbol                           |      | Values |      | Unit | Note or condition                                                                                       | P-<br>Number |

|-------------------------------------|----------------------------------|------|--------|------|------|---------------------------------------------------------------------------------------------------------|--------------|

|                                     |                                  | Min. | Тур.   | Max. |      |                                                                                                         |              |

| Power supply input voltage          | V <sub>IN</sub>                  | -0.3 | _      | 60   | V    | -                                                                                                       | PRQ-31       |

| Voltage at pin SET                  | V <sub>SET</sub>                 | -0.3 | -      | 5.5  | V    | -                                                                                                       | PRQ-44       |

| Voltage at pin DC/<br>PWMI          | V <sub>DC/PWMI</sub>             | -0.3 | -      | 60   | V    | -                                                                                                       | PRQ-32       |

| Voltage at pin FBH                  | $V_{FBH}$                        | -1   | -      | 75   | V    | -                                                                                                       | PRQ-33       |

| Voltage at pin FBL                  | $V_{FBL}$                        | -1   | -      | 75   | V    | -                                                                                                       | PRQ-34       |

| Differential input<br>voltage       | V <sub>REF(MAX)</sub>            | -75  | -      | 75   | V    | $V_{\text{REF(MAX)}} = V_{\text{FBH}} - V_{\text{FBL}}$<br>Differential signal (not referred to ground) | PRQ-35       |

| Current at pin FBH, FBL             | $I_{\text{FBH}}, I_{\text{FBL}}$ | -7.5 | _      | 7.5  | mA   | $V_{\text{FBH}}$ - $V_{\text{FBL}}$ = 150 mV                                                            | PRQ-36       |

| Voltage at pin VFB                  | $V_{FB}$                         | -0.3 | _      | 5.5  | V    | -                                                                                                       | PRQ-37       |

| Voltage at pin SWCS                 | $V_{\rm SWCS}$                   | -0.3 | _      | 0.3  | V    | -                                                                                                       | PRQ-38       |

| Voltage at pin SWO                  | $V_{\rm SWO}$                    | -0.3 | _      | 5.5  | V    | -                                                                                                       | PRQ-39       |

| Voltage at pin FPWM/<br>FAULT       | V <sub>FPWM/FAULT</sub>          | -0.3 | _      | 5.5  | V    | -                                                                                                       | PRQ-40       |

| Voltage at pin COMP                 | $V_{COMP}$                       | -0.3 | -      | 5.5  | ٧    | -                                                                                                       | PRQ-41       |

| Voltage at pin FREQ/<br>SYNC/SPREAD | V <sub>FREQ/SYNC</sub>           | -0.3 | _      | 5.5  | V    | -                                                                                                       | PRQ-42       |

| Voltage at pin PWMO                 | $V_{PWMO}$                       | -0.3 | _      | 75   | V    | -                                                                                                       | PRQ-43       |

| PMOS output voltage                 | V <sub>PMOS</sub>                | -1   | -      | 10   | V    | V <sub>PMOS</sub> = V <sub>FBH</sub> - V <sub>PWMO</sub> Differential signal (Not referred to ground)   | PRQ-579      |

| Voltage at pin IVCC                 | V <sub>IVCC</sub>                | -0.3 | _      | 5.5  | V    | -                                                                                                       | PRQ-45       |

| Temperature                         |                                  |      | •      | •    | •    |                                                                                                         |              |

| Junction temperature                | TJ                               | -40  | -      | 150  | °C   | _                                                                                                       | PRQ-46       |

| Storage temperature                 | $T_{\rm stg}$                    | -40  | _      | 150  | °C   | _                                                                                                       | PRQ-47       |

(table continues...)

#### Multitopology single-channel DC-DC controller

#### 3 General product characteristics

#### Table 2 (continued) Absolute maximum ratings

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

Not subject to production test, specified by design

| Parameter                      | Symbol                  |       | Values |      | Unit | Note or condition                                                                         | P-     |

|--------------------------------|-------------------------|-------|--------|------|------|-------------------------------------------------------------------------------------------|--------|

|                                |                         | Min.  | Тур.   | Max. |      |                                                                                           | Number |

| ESD susceptibility             |                         | ·     |        |      |      |                                                                                           |        |

| ESD susceptibility             | V <sub>ESD_HBM</sub>    | -2    | _      | 2    | kV   | HBM: ESD<br>susceptibility, Human<br>Body Model "HBM"<br>according to AEC<br>Q100-002     | PRQ-48 |

| ESD susceptibility inner pins  | V <sub>ESD_CDM</sub>    | -0.5  | -      | 0.5  | kV   | CDM: ESD<br>susceptibility, Charged<br>Device Model "CDM"<br>according to AEC<br>Q100-011 | PRQ-49 |

| ESD susceptibility corner pins | V <sub>ESD_CDM_CR</sub> | -0.75 | -      | 0.75 | kV   | CDM: ESD<br>susceptibility, Charged<br>Device Model "CDM"<br>according to AEC<br>Q100-011 | PRQ-50 |

#### Attention:

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the datasheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for repetitive operation.

## 3.2 Functional range

#### Table 3 Functional range

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                  | Symbol              |      | Values |      |   | Note or condition             | P-     |

|--------------------------------------------|---------------------|------|--------|------|---|-------------------------------|--------|

|                                            |                     | Min. | Тур.   | Max. |   |                               | Number |

| Extended power supply input voltage range  | V <sub>IN_EXT</sub> | 4.5  | _      | 58   | V | Parameter deviations possible | PRQ-51 |

| Power supply input voltage operating range | V <sub>IN_OP</sub>  | 8    | -      | 36   | V | _                             | PRQ-52 |

(table continues...)

#### Multitopology single-channel DC-DC controller

#### 3 General product characteristics

#### Table 3 (continued) Functional range

$T_J$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                    | Symbol Values                         |      |      |      | Unit | Note or condition | P-      |

|----------------------------------------------|---------------------------------------|------|------|------|------|-------------------|---------|

|                                              |                                       | Min. | Тур. | Max. |      |                   | Number  |

| Operating voltage at pin FBH                 | V <sub>FBH_OP</sub>                   | 0    | _    | 70   | V    | -                 | PRQ-581 |

| Operating voltage at pin FBL                 | V <sub>FBL_OP</sub>                   | -0.3 | _    | 70   | V    | -                 | PRQ-53  |

| Switching frequency adjustment range         | $f_{\sf SWO}$                         | 100  | -    | 500  | kHz  | -                 | PRQ-85  |

| Synchronization low frequency capture range  | f <sub>FREQ/SYNC/</sub> SPREAD(LF)    | 100  | -    | 500  | kHz  | -                 | PRQ-90  |

| Synchronization high frequency capture range | f <sub>FREQ/SYNC/</sub><br>SPREAD(HF) | 2    | -    | 2.4  | MHz  | -                 | PRQ-132 |

| PWMO frequency range                         | $f_{PWMO}$                            | 150  | _    | 750  | Hz   | _                 | PRQ-113 |

<sup>1)</sup> Not subject to production test, specified by design

Attention: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 3.3 Thermal resistance

#### Table 4 Thermal resistance

Not subject to production test, specified by design

| Parameter           | Symbol            |      | Values |      |     | Note or condition                        | P-     |

|---------------------|-------------------|------|--------|------|-----|------------------------------------------|--------|

|                     |                   | Min. | Тур.   | Max. |     |                                          | Number |

| Junction to case    | R <sub>thJC</sub> | _    | 20.9   | _    | K/W | 1)                                       | PRQ-54 |

| Junction to ambient | R <sub>thJA</sub> | _    | 57.2   | _    | K/W | <sup>2)</sup> 2s2p                       | PRQ-55 |

| Junction to ambient | R <sub>thJA</sub> | _    | 73.2   | _    | K/W | <sup>2)</sup> 1s0p + 600 mm <sup>2</sup> | PRQ-56 |

| Junction to ambient | R <sub>thJA</sub> | _    | 85.5   | _    | K/W | <sup>2)</sup> 1s0p + 300 mm <sup>2</sup> | PRQ-57 |

<sup>1)</sup> Specified  $R_{thJC}$  value is simulated at natural convection on a cold plate setup (all pins and exposed pads are fixed to ambient temperature)  $T_A$  = 25°C dissipates 1 W

**Note**: This thermal data was generated in accordance with JEDEC JESD51 standards. For further information visit https://www.jedec.org

<sup>2)</sup> Specified  $R_{thJA}$  value is according JEDEC 2s2p (JESD 51-7) + (JESD 51-5) and JEDEC 1s0p (JESD 51-3) + heatsink area at natural convection on FR4 board. The device was simulated on 76.2 x 114.3 x 1.5 mm board. The 2s2p board has 2 outer copper layers (2 x 70  $\mu$ m Cu) and 2 inner copper layer (2 x 35  $\mu$ m Cu). A thermal via (diameter = 0.3 mm and 25  $\mu$ m plating) array was applied under the exposed pad and connected the top layer and the inner layers to bottom layers of JEDEC PCB.  $T_A$  = 25°C; IC dissipates 1 W

#### Multitopology single-channel DC-DC controller

#### 4 Switching regulator

## 4 Switching regulator

TLD6098-1EP implements a regulator suitable for Boost-to-ground, Boost-to-battery, Buck-to-battery, SEPIC, Flyback and Cuk configurations.

The device has two distinct control loops:

- A current control loop (always enabled)

- A voltage control loop (optional)

If the voltage loop is enabled the device regulates the output current as long as the feedback voltage on the VFB pin is below the VFB voltage mode ON threshold ( $V_{\text{VFB\_VM(ON)}}$ ). The voltage control loop takes over and regulates the output voltage once the VFB reference voltage  $V_{\text{VFB\_REF}}$  is reached.

The controller generates a PWM signal by sensing the inductor peak current and the output of the internal error amplifier. The control signal is applied to the internal gate driver connected to SWO pin to drive the external n-channel MOSFET

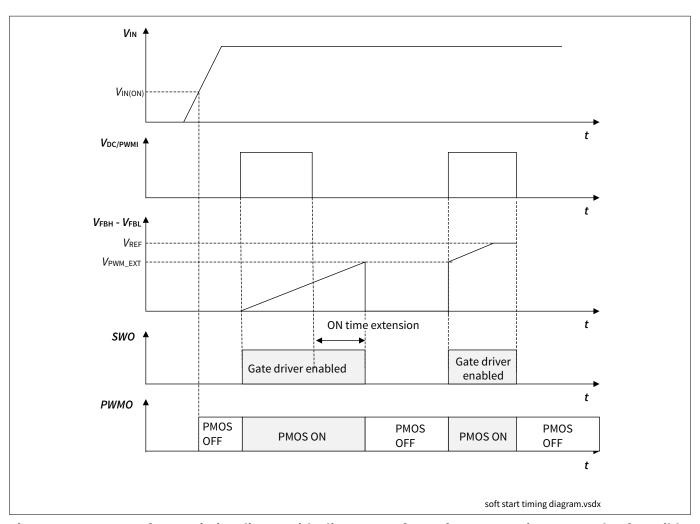

#### 4.1 Soft start

The soft start routine has 2 functionalities:

- Limiting the input current and output overshoot

- Guaranteeing that the system output reaches the target value in a reasonable time even when being operated in PWM dimming with low duty cycles

The first rising edge on DC/PWMI pin or the first cycle of the embedded PWM engine enables the soft start routine.

It is then performed in the following cases:

- At start-up

- After an overvoltage on FBH pin

- After an overvoltage on VFB pin

- After an overtemperature fault

- After an undervoltage on IVCC pin

The soft start is applied after a short to ground fault and retriggered every  $t_{\text{FAULT}}$  in case of continuous presence of the fault.

The operation of the soft start is conditioned by the analog output adjustment.

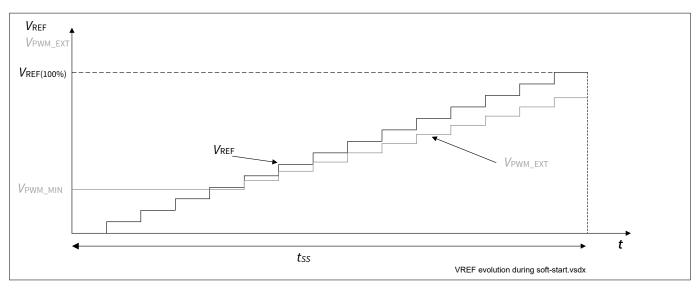

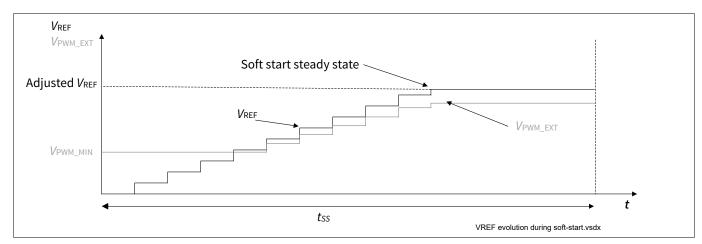

During the soft start the switching regulator adjusts the PWM signal to make the voltage between FBH and FBL evolve from 0 to  $V_{\text{REF}(100\%)}$  in  $t_{\text{SS}}$  time. The evolution is performed in 15 steps if the analog adjustment is not applied, otherwise the intended steady-state is reached before the soft start ends.

An ON time extension of the PWM dimming pulses is applied to ensure a reasonable power-up time when a low duty cycle dimming is applied.

#### Multitopology single-channel DC-DC controller

#### 4 Switching regulator

Figure 4 Soft start timing diagram (the linear waveform of  $V_{VFBH}$ - $V_{VFBL}$  is an example of possible scenario)

The ON time extension is triggered if:

The applied PWM dimming signal (or the signal generated by the PWM engine) has an ON time shorter than

t<sub>SS</sub> during the soft start

and

• The voltage across FBH and FBL is lower than the reference voltage during PWM extension  $V_{\text{PWM\_EXT}}$  at the end of the ON time of the PWM signal

The ON time extension lasts as long as the voltage across FBH and FBL reaches the  $V_{\rm PWM-EXT.}$

The  $V_{\text{PWM\_EXT}}$  is limited by the analog output adjustment down to a minimum reference voltage during ON time extension  $V_{\text{PWM\_MIN}}$ .

For the first 3 steps of the  $V_{REF}$  signal, the  $V_{PWM}$  EXT is higher than  $V_{REF}$ .

If the reference voltage across FBH and FBL adjusted by analog adjustment feature is lower than the  $V_{\text{PWM\_MIN}}$  the ON time extension ends after  $t_{\text{SS}}$ .

#### Multitopology single-channel DC-DC controller

#### 4 Switching regulator

Figure 5  $V_{\text{REF}}$  and  $V_{\text{PWM\_EXT}}$  waveforms during the soft start routine without analog output adjustment

Figure 6  $V_{\text{REF}}$  and  $V_{\text{PWM\_EXT}}$  waveforms during the soft start routine with analog output adjustment

If the ON time extension ends before  $t_{SS}$  elapsed, the ON time extension is retriggered in the following PWM cycle, in case the voltage between FBH and FBL is once again lower than  $V_{PWM-EXT}$

When the ON time extension ends, the remaining part of the soft start is allowed to evolve during the following ON time of the PWM dimming signal. In this case the actual duration of soft start could be longer than  $t_{SS}$ .

## Multitopology single-channel DC-DC controller

#### 4 Switching regulator

#### 4.2 Electrical characteristics

#### Table 5 Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                                            | Symbol                 |        | Values                              |        | Unit | Note or condition                                                                                                              | P-      |

|------------------------------------------------------|------------------------|--------|-------------------------------------|--------|------|--------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                      |                        | Min.   | Тур.                                | Max.   |      |                                                                                                                                | Number  |

| Regulator                                            |                        |        | 1                                   |        | '    |                                                                                                                                | 1       |

| VFB reference voltage<br>(voltage loop)              | $V_{ m VFB\_REF}$      | 1.568  | 1.6                                 | 1.632  | V    | _                                                                                                                              | PRQ-142 |

| Current loop reference<br>voltage                    | V <sub>REF(100%)</sub> | 144.75 | 150                                 | 155.25 | mV   | Differential signal (not referred to ground) $V_{\text{REF}} = V_{\text{FBH}} - V_{\text{FBL}}$ $V_{\text{SET}} = 5 \text{ V}$ | PRQ-66  |

| Current loop reference<br>voltage                    | V <sub>REF(40%)</sub>  | 54.6   | 60                                  | 65.4   | mV   | Differential signal (not referred to ground)  V <sub>SET</sub> = 940 mV                                                        | PRQ-67  |

| Current loop reference<br>voltage                    | V <sub>REF(0%)</sub>   | -      | -                                   | 10     | mV   | Differential signal (not referred to ground)  V <sub>SET</sub> = 100 mV                                                        | PRQ-68  |

| Transconductance<br>error amplifier voltage<br>loop  | g <sub>m1</sub>        | _      | 0.95                                | _      | mS   | 1) 2)                                                                                                                          | PRQ-600 |

| Transconductance<br>error amplifier current<br>loop  | $g_{m2}$               | -      | 1.6                                 | _      | mS   | 2) 1)                                                                                                                          | PRQ-463 |

| Switch current limit<br>threshold                    | V <sub>SWCS_TH</sub>   | 80     | 100                                 | 120    | mV   | _                                                                                                                              | PRQ-69  |

| Maximum duty cycle in adjust. freq. mode             | D <sub>MAX</sub>       | 91     | -                                   | -      | %    | $R_{\text{FREQ/SYNC/}}$<br>SPREAD = 27 k $\Omega$                                                                              | PRQ-70  |

| Maximum duty cycle in<br>ow frequency sync<br>mode   | D <sub>MAX(LF)</sub>   | 88     | -                                   | _      | %    | f <sub>SW</sub> = 500 kHz                                                                                                      | PRQ-71  |

| Maximum duty cycle in<br>nigh frequency sync<br>mode | D <sub>MAX(HF)</sub>   | 80     | _                                   | _      | %    | f <sub>SW</sub> = 2.2 MHz                                                                                                      | PRQ-289 |

| Soft start time                                      | $t_{SS}$               | 1.8    | 2                                   | 2.2    | ms   | 2) 1)                                                                                                                          | PRQ-72  |

| Reference voltage<br>during PWM extension            | V <sub>PWM_EXT</sub>   | -      | 0.8* <i>V</i> <sub>RE</sub><br>F1,2 | -      | V    | 1) 2) $V_{\text{PWM\_EXT}} > V_{\text{PWM\_MIN}}$                                                                              | PRQ-588 |

(table continues...)

## Multitopology single-channel DC-DC controller

#### 4 Switching regulator

#### Table 5 (continued) Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                                            | Symbol               |      | Values |      | Unit | Note or condition                                                                                                                                                     | P-      |

|------------------------------------------------------|----------------------|------|--------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                      |                      | Min. | Тур.   | Max. |      |                                                                                                                                                                       | Number  |

| Minimum reference<br>voltage during PWM<br>extension | V <sub>PWM_MIN</sub> | -    | 31.5   | -    | mV   | 2) 1)                                                                                                                                                                 | PRQ-589 |

| Input current at pin<br>FBH                          | I <sub>FBH</sub>     | _    | 550    | 800  | μΑ   | $V_{\text{FBH}} - V_{\text{FBL}} = 0.15 \text{ V}$<br>$V_{\text{FBH}} = 60 \text{ V}$                                                                                 | PRQ-73  |

| Input current at pin<br>FBL                          | I <sub>FBL</sub>     | _    | 50     | 70   | μΑ   | $V_{\text{FBH}}$ - $V_{\text{FBL}}$ = 0.15 V<br>$V_{\text{FBH}}$ = 60 V                                                                                               | PRQ-74  |

| Input current at pin<br>FBH                          | I <sub>FBH</sub>     | -    | 50     | 70   | μΑ   | $V_{\text{FBH}}$ - $V_{\text{FBL}}$ = 0.15 V<br>$V_{\text{FBL}}$ = 0 V<br>Current flows out of pin                                                                    | PRQ-75  |

| Input current at pin<br>FBL                          | I <sub>FBL</sub>     | -    | 50     | 70   | μΑ   | $V_{\text{FBH}}$ - $V_{\text{FBL}}$ = 0.15 V<br>$V_{\text{FBL}}$ = 0 V<br>Current flows out of pin                                                                    | PRQ-76  |

| Threshold voltage high side sensing                  | V <sub>FBH_HSS</sub> | -    | 2.55   | 2.8  | V    | 2) V <sub>FBH</sub> increasing                                                                                                                                        | PRQ-267 |

| Threshold voltage low side sensing                   | $V_{FBH\_LSS}$       | 2.1  | 2.3    | -    | V    | 2)<br>V <sub>FBH</sub> decreasing                                                                                                                                     | PRQ-268 |

| Power supply<br>undervoltage<br>shutdown             | V <sub>IN(OFF)</sub> | 2.5  | -      | 4.5  | V    | V <sub>IN</sub> decreasing                                                                                                                                            | PRQ-77  |

| Power supply<br>minimum startup<br>voltage           | V <sub>IN(ON)</sub>  | -    | -      | 5.5  | V    | V <sub>IN</sub> increasing                                                                                                                                            | PRQ-78  |

| Power supply current consumption                     | / <sub>IN</sub>      | -    | 5      | 8    | mA   | $V_{\rm DC/PWMI}$ = 0 V<br>$V_{\rm SET}$ = $V_{\rm IVCC}$<br>$R_{\rm FREQ/SYNC/SPREAD}$ = 33 k $\Omega$<br>$R_{\rm FPWM/FAULT}$ = 57 k $\Omega$<br>no faults detected | PRQ-426 |

(table continues...)

## Multitopology single-channel DC-DC controller

#### 4 Switching regulator

#### (continued) Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                        | Symbol              |      | Values |      | Unit | Note or condition                                                                  | P-      |

|----------------------------------|---------------------|------|--------|------|------|------------------------------------------------------------------------------------|---------|

|                                  |                     | Min. | Тур.   | Max. |      |                                                                                    | Number  |

| Gate driver for extern           | al switch           |      |        |      | •    |                                                                                    |         |

| Gate driver peak output current  | I <sub>SWO</sub>    | 1    | _      | -    | A    | V <sub>SWO</sub> increasing 1 V to                                                 | PRQ-79  |

|                                  |                     |      |        |      |      | Current flows out of pin                                                           |         |

| Gate driver peak output current  | / <sub>SWO</sub>    | 1    | _      | -    | A    | V <sub>SWO</sub> decreasing 4 V to 1 V                                             | PRQ-80  |

| Gate driver output rise time     | t <sub>R_SWO</sub>  | -    | -      | 20   | ns   | 2) $C_{L\_SWO} = 3.3 \text{ nF}$ $V_{SWO} \text{ increasing 1 V to}$ $4 \text{ V}$ | PRQ-81  |

| Gate driver output fall time     | t <sub>F_SWO</sub>  | -    | -      | 20   | ns   | $C_{L_SWO} = 3.3 \text{ nF}$ $V_{SWO}$ decreasing 4 V to 1 V                       | PRQ-82  |

| Gate driver high side resistance | R <sub>SWO_HS</sub> | -    | 1      | 3    | Ω    | 2) 1)<br>$I_{SWO} = -10 \text{ mA}$                                                | PRQ-83  |

| Gate driver low side resistance  | R <sub>SWO_LS</sub> | -    | 1      | 3    | Ω    | 2) 1)<br>I <sub>SWO</sub> = 10 mA                                                  | PRQ-196 |

<sup>1)</sup> 2) Not subject to production test, specified by design

Not subject to production test, specified by design

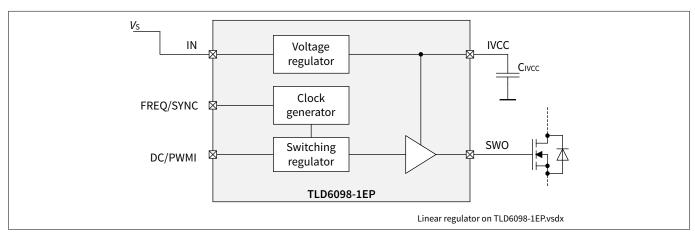

5 Linear regulator

#### **Linear regulator** 5

The device incorporates a linear regulator to generate a 5 V output used to supply the internal gate drivers and, through IVCC pin, other auxiliary devices on the PCB (for example a microcontroller and resistor dividers).

The maximum output current of the linear regulator is limited to the IVCC output current limit  $I_{IVCC}$ .

If the load on IVCC (gate drivers plus connected devices on PCB) draws more than I<sub>IVCC</sub> the linear regulator output voltage decreases.

The linear regulator starts to deliver current to IVCC pin when the input voltage  $V_{\rm IN}$  goes above the power supply minimum start up voltage  $V_{\rm IN~(ON)}$  for a time longer than IVCC start time  $t_{\rm ST}$

A low ESR capacitor has to be connected from IVCC to ground (C<sub>IVCC</sub> in the figure) to stabilize the output voltage of the linear regulator.

The ESR of the capacitor  $C_{IVCC}$  has to be lower than IVCC buffer capacitor ESR  $R_{IVCC(ESR)}$ .

Figure 7 Block diagram of the linear regulator

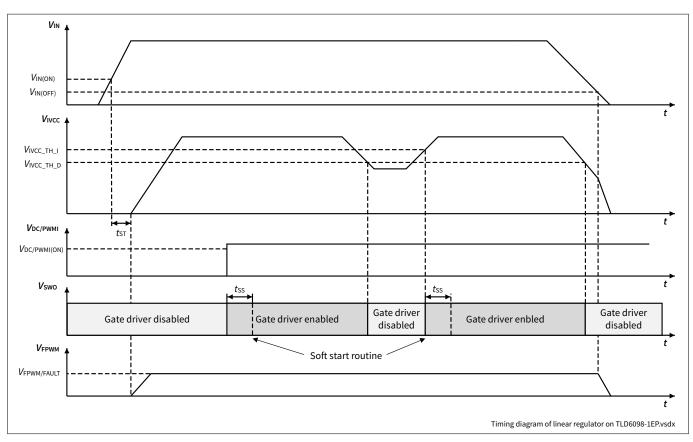

#### **Undervoltage protection for the external switching MOSFET** 5.1

During the ON time of the switching PWM signal, the gate driver has to bias the switching NMOS in deep ohmic region to avoid the overheating of the MOSFET itself during the conduction time. This is ensured by choosing a logic level MOSFET with a maximum threshold voltage lower than IVCC undervoltage switch-off threshold  $V_{\text{IVCC\_TH\_D}}$ .

TLD6098-1EP has an integrated undervoltage reset threshold circuit to disable the gate driver if the  $V_{\rm IVCC}$  drops below the  $V_{IVCC\ TH\ D}$ . The gate driver is then enabled again when the  $V_{IVCC}$  goes above the IVCC undervoltage switch-on threshold  $V_{IVCC\ TH\ I}$ .

## Multitopology single-channel DC-DC controller

#### 5 Linear regulator

Figure 8 Thresholds and timing diagram related to the linear regulator

## **5.2 Electrical characteristics**

#### Table 6 Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                 | Symbol               |      | Values |      | Unit | Note or condition                                                                                           | P-<br>Number |

|---------------------------|----------------------|------|--------|------|------|-------------------------------------------------------------------------------------------------------------|--------------|

|                           |                      | Min. | Тур.   | Max. |      |                                                                                                             |              |

| IVCC output voltage       | V <sub>IVCC</sub>    | 4.85 | 5      | 5.15 | V    | $8 \text{ V} \le V_{\text{IN}} \le 36 \text{ V}; 0.1 \text{ mA}$<br>$\le I_{\text{IVCC}} \le 40 \text{ mA}$ | PRQ-58       |

| IVCC output current limit | I <sub>IVCC</sub>    | 51   | _      | 100  | mA   | 8 V < V <sub>IN</sub> < 13.5 V; V <sub>IVCC</sub> < 4.5 V; Current flows out of pin                         | PRQ-59       |

| IVCC dropout voltage      | V <sub>IVCC_DV</sub> | _    | _      | 0.5  | V    | V <sub>IN</sub> = 5 V; I <sub>IVCC</sub> < 20 mA                                                            | PRQ-60       |

| IVCC start time           | t <sub>ST</sub>      | -    | -      | 300  | μs   | <i>I)</i> V <sub>IN</sub> slew rate higher than 1 V/10 μs                                                   | PRQ-285      |

(table continues...)

## Multitopology single-channel DC-DC controller

#### 5 Linear regulator

#### Table 6 (continued) Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                              | Symbol                 |      | Values |      | Unit | Note or condition                                                    | P-<br>Number |

|----------------------------------------|------------------------|------|--------|------|------|----------------------------------------------------------------------|--------------|

|                                        |                        | Min. | Тур.   | Max. |      |                                                                      |              |

| IVCC buffer capacitor                  | C <sub>IVCC</sub>      | 1    | 4.7    | 10   | μF   | If embedded PWM engine is used, 4.7 μF has to be chosen as a minimum | PRQ-61       |

| IVCC buffer capacitor<br>ESR           | R <sub>IVCC(ESR)</sub> | -    | -      | 0.2  | Ω    | Maximum value given for regulator stability                          | PRQ-62       |

| IVCC undervoltage switch-off threshold | V <sub>IVCC_TH_D</sub> | 3.6  | -      | 4.0  | V    | V <sub>IVCC</sub> decreasing                                         | PRQ-64       |

| IVCC undervoltage switch-on threshold  | V <sub>IVCC_TH_I</sub> | -    | -      | 4.5  | V    | V <sub>IVCC</sub> increasing                                         | PRQ-65       |

<sup>1)</sup> Not subject to production test, specified by design

Attention: Select external switching MOSFET with worst case threshold voltage  $V_{\rm GS(th)}$  lower than minimum  $V_{\rm IVCC\_TH\_D}$

# **(infineon**

6 Switching frequency setup and synchronization

## 6 Switching frequency setup and synchronization

The DC-DC switching frequency is adjusted by a resistor placed from FREQ/SYNC/SPREAD pin to ground or by providing to this pin a digital clock. The device incorporates also a spread spectrum modulator to reduce the design effort to fulfill the EMI compliance.

By using a resistor, the switching frequency of the regulator is adjusted in the switching frequency adjustment range  $f_{SWO}$ .

If an external clock is provided, the device accepts a digital clock in these two working windows:

- Synchronization low frequency capture range  $f_{\text{FREO/SYNC/SPREAD(LF)}}$  (low frequency synchronization mode)

- Synchronization high frequency capture range  $f_{\mathsf{FREQ/SYNC/SPREAD(HF)}}$  (high frequency synchronization mode) Outside these ranges, the device does not recognize a valid clock and then the behavior of the regulator can be out of specification.

Figure 9 Diagram of switching frequency adjustment and synchronization blocks

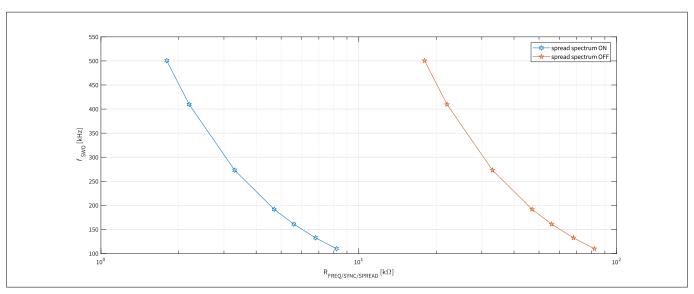

## 6.1 Switching frequency setup with external resistor

The resistor placed on FREQ/SYNC/SPREAD pin adjusts the frequency of the DC-DC and enables or disables the spread spectrum modulator.

The relationship between the biasing resistor and switching frequency with spread spectrum activated is

$$f_{SW} = \frac{1}{\left(1.11 \cdot 10^{-9} \cdot R_{FREQ/SYNC/SPREAD}\right)} \tag{1}$$

The relationship between the biasing resistor and the switching frequency with the spread spectrum not active is

$$f_{SW} = \frac{1}{\left(1.11 \cdot 10^{-10} \cdot R_{FREQ/SYNC/SPREAD}\right)} \tag{2}$$

#### Multitopology single-channel DC-DC controller

#### 6 Switching frequency setup and synchronization

Figure 10 Switching frequency versus  $R_{FREQ/SYNC/SPREAD}$

#### **6.1.1** Electrical characteristics

#### **Table 7 Electrical characteristics**

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                       | Symbol                                  |      | Values |      | Unit | Note or condition                                                    | P-      |

|---------------------------------|-----------------------------------------|------|--------|------|------|----------------------------------------------------------------------|---------|

|                                 |                                         | Min. | Тур.   | Max. |      |                                                                      | Number  |

| Switching frequency             | f <sub>SWO_SSM(OFF)</sub>               | 288  | 333    | 378  | kHz  | $R_{\text{FREQ/SYNC/SPREAD}} = 27 \text{ k}\Omega$                   | PRQ-277 |

| FREQ/SYNC/SPREAD output current | I <sub>FREQ/SYNC/</sub> SPREAD          | -    | _      | 3    | mA   | V <sub>FREQ/SYNC/SPREAD</sub> = 0 V<br>Current flowing out of<br>pin | PRQ-86  |

| FREQ/SYNC/SPREAD output voltage | V <sub>FREQ/SYNC/</sub> SPREAD_SSM(OFF) | 0.72 | 0.8    | 0.88 | V    | $R_{\text{FREQ/SYNC/SPREAD}} = 27 \text{ k}\Omega$                   | PRQ-87  |

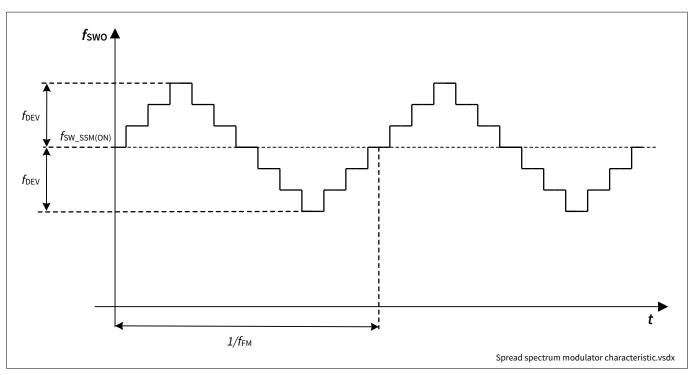

## **6.1.2** Spread Spectrum

The spread spectrum modulation technique significantly reduces the electromagnetic harmonics emission at the lower frequency range of the spectrum (f < 30 MHz).

This technique is enabled by changing the switching frequency over the time. The final result is the movement over a broad band of the energy associated with the peaks of the electromagnetic harmonics emission.

The switching frequency is modulated with a triangular shape digitalized in 7 steps equally distributed over the entire frequency span (2 times the frequency deviation  $f_{DEV}$ ).

#### Multitopology single-channel DC-DC controller

#### 6 Switching frequency setup and synchronization

Figure 11 Spread spectrum modulator characteristic

#### **6.1.2.1** Electrical characteristics

#### Table 8 Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                       | Symbol                                 |                           | Values                    |      | Unit | Note or condition                                                                          | P-      |

|---------------------------------|----------------------------------------|---------------------------|---------------------------|------|------|--------------------------------------------------------------------------------------------|---------|

|                                 |                                        | Min.                      | Тур.                      | Max. |      |                                                                                            | Number  |

| Average switching frequency     | f <sub>SWO_SSM(ON)</sub>               | 288                       | 333                       | 378  | kHz  | 1) $R_{\text{FREQ/SYNC/SPREAD}} = 2.7 \text{ k}\Omega$                                     | PRQ-84  |

| Modulation frequency            | f <sub>FM</sub>                        | 13.5                      | 15                        | 16.5 | kHz  | 1) $1.8 \text{ k}\Omega \leq R_{\text{FREQ/SYNC/}}$ $\text{SPREAD} \leq 9 \text{ k}\Omega$ | PRQ-88  |

| Frequency deviation             | $f_{DEV}$                              | 0.09*f <sub>S</sub><br>wo | 0.15*f <sub>S</sub><br>wo | _    | kHz  | 1) $1.8 \text{ k}\Omega \leq R_{\text{FREQ/SYNC/}}$ $\text{SPREAD} \leq 9 \text{ k}\Omega$ | PRQ-89  |

| FREQ/SYNC/SPREAD output voltage | V <sub>FREQ/SYNC/</sub> SPREAD_SSM(ON) | 0.72                      | 0.8                       | 0.88 | V    | $R_{\text{FREQ/SYNC/SPREAD}} = 2.7 \text{ k}\Omega$                                        | PRQ-385 |

<sup>1)</sup> Not subject to production test, specified by design

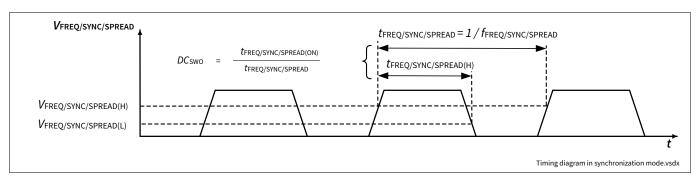

## 6.2 Synchronization with external clock (low frequency mode)

The switching frequency is synchronized with an external clock source applied on FREQ/SYNC/SPREAD pin if the frequency is in the synchronization low frequency capture range  $f_{\text{FREQ/SYNC/SPREAD(LF)}}$  and the duty cycle is in the synchronization input duty cycle range  $DC_{\text{FREQ/SYNC/SPREAD}}$ .

#### Multitopology single-channel DC-DC controller

#### 6 Switching frequency setup and synchronization

The device detects the external clock source if the voltage on FREQ/SYNC/SPREAD exceeds the two thresholds:

- The synchronization input high voltage  $V_{\text{FREO/SYNC/SPREAD(H)}}$  during the positive pulse,

- The synchronization input low voltage  $V_{\text{FREO/SYNC/SPREAD(L)}}$  during the negative pulse.

Figure 12 Timing diagram when synchronization mode is enabled

#### **6.2.1** Electrical characteristics

#### Table 9 Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                              | Symbol                            |      | Values |      | Unit | Note or condition | P-<br>Number |

|----------------------------------------|-----------------------------------|------|--------|------|------|-------------------|--------------|

|                                        |                                   | Min. | Тур.   | Max. |      |                   |              |

| Synchronization input high voltage     | V <sub>FREQ/SYNC/</sub> SPREAD(H) | 3.0  | _      | _    | V    | -                 | PRQ-91       |

| Synchronization input low voltage      | V <sub>FREQ/SYNC/</sub> SPREAD(L) | -    | _      | 0.8  | V    | -                 | PRQ-92       |

| Synchronization input duty cycle range | DC <sub>FREQ/SYNC/</sub> SPREAD   | 40   | -      | 60   | %    | 1)                | PRQ-94       |

<sup>1)</sup> Not subject to production test, specified by design

## 6.3 Synchronization with external clock (high frequency range)

$High \ switching \ frequency \ enables \ a \ system \ cost \ down \ due \ to \ reduced \ value \ for \ the \ reactive \ components.$

The high frequency synchronization is enabled if the input clock is in the synchronization high frequency capture range  $f_{\text{FREQ/SYNC/SPREAD(HF)}}$ .

Voltage threshold levels on FREQ/SYNC/SPREAD pin are the same as in the low frequency synchronization mode.

#### Multitopology single-channel DC-DC controller

#### 7 Analog output adjustment

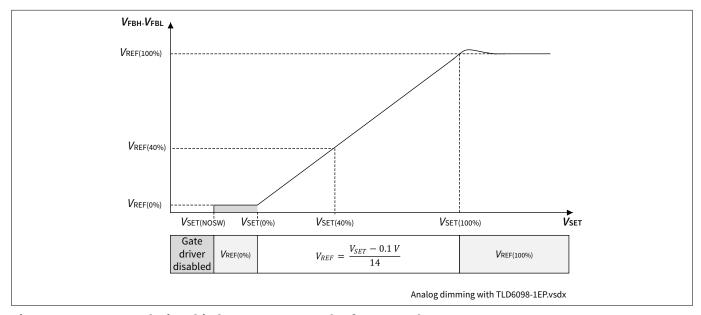

## 7 Analog output adjustment

The device adjusts the reference voltage  $V_{REF}$  across FBH and FBL pins (thus adjusting the output current) by monitoring the analog voltage on SET pin ( $V_{SFT}$ ).

The SWO NMOS gate driver is disabled if the voltage applied on the SET pin is lower than SET input voltage no switching activity  $V_{\text{SET(NOSW)}}$ .

The SET pin has to be connected to a voltage higher than  $V_{\text{SET(100\%)}}$  (e.g. connecting SET pin to IVCC pin) to exclude the output current adjustment feature.

Figure 13 Relationship between  $V_{SET}$  and reference voltage  $V_{REF}$

The SET pin can also be wired to an external thermistor (usually mounted on the LED module) to perform a thermal protection.

## 7.1 Electrical characteristics

#### Table 10 Electrical characteristics

$V_{IN}$  = 8 V to 36 V;  $T_{J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                               | Symbol                 |      | Values |      | Unit | Note or condition | P-<br>Number |

|-----------------------------------------|------------------------|------|--------|------|------|-------------------|--------------|

|                                         |                        | Min. | Тур.   | Max. |      |                   |              |

| SET input voltage<br>100%               | V <sub>SET(100%)</sub> | _    | 2.2    | _    | V    | 1)                | PRQ-95       |

| SET input voltage 40%                   | V <sub>SET(40%)</sub>  | _    | 940    | _    | mV   | 1)                | PRQ-429      |

| SET input voltage 0%                    | V <sub>SET(0%)</sub>   | _    | 100    | _    | mV   | 1)                | PRQ-428      |

| SET input voltage no switching activity | V <sub>SET(NOSW)</sub> | -    | -      | 50   | mV   | -                 | PRQ-368      |

<sup>1)</sup> Not subject to production test, specified by design

#### Multitopology single-channel DC-DC controller

# infineon

#### **8 Dimming functions**

## 8 Dimming functions

The TLD6098-1EP offers a dimming input for pulse width modulating (PWM) the output current.

This modulation is beneficial to reduce the average current at output (and then the brightness of the LEDs), without showing color shift on the light produced by the LEDs.

The output current modulation is operated by the device as function of the voltage on DC/PWMI pin

- A digital clock signal imposes the duty cycle and the frequency

- An analog voltage is translated to a duty cycle and the frequency is adjusted with a resistor on FPWM/ FAULT pin.

Different voltage levels on DC/PWMI pin activates different functions, as described below:

- If the voltage is higher than DC/PWMI input voltage high threshold  $V_{\rm DC/PWMI(ON)}$  the dimming duty cycle is set to 100%

- If the voltage is in between the two digital thresholds ( $V_{\rm DC/PWMI(100\%)}$  and  $V_{\rm DC/PWMI(0\%)}$ ), the embedded PWM dimming function is activated

- If the voltage is lower than DC/PWMI input voltage low threshold  $V_{\rm DC/PWMI(OFF)}$  the dimming duty cycle is 0%

When a dimming function is activated, the PWM signal controls the switching regulator gate driver and the PMOS gate driver

To allow fast transitions of the dimming PMOS even at low output voltage, the positive power supply of the PWMO gate driver is connected to FBH pin if its voltage  $V_{\text{FBH}}$  is higher than  $V_{\text{IVCC}}$ , otherwise the gate driver is supplied by the IVCC pin.

During the ON state of the PWM dimming, the PMOS is biased with a PWMO output voltage ON state  $V_{\text{PWMO,ON}}$  (minimum  $V_{\text{PWMO,ON}}$  cannot go below 0 V).

#### 8.1 Electrical characteristics

#### Table 11 Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                   | Symbol            |      | Values |      | Unit | Note or condition                                                                                                                                                        | P-<br>Number |

|-----------------------------|-------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|                             |                   | Min. | Тур.   | Max. |      |                                                                                                                                                                          |              |

| PWMO peak output<br>current | І <sub>РШМО</sub> | 2    | 5      | -    | mA   | $V_{\rm FBH} = 14V$ $V_{\rm PWMO}$ increasing $V_{\rm PWMO(ON)} + 0.5  V$ to $V_{\rm PWMO(ON)} + 3.5  V$ $C_{\rm L,PWMO} = 3.3  \rm nF$ current flows out of pin         | PRQ-102      |

| PWMO peak output<br>current | І <sub>РШМО</sub> | 2    | 5      | -    | mA   | $V_{\text{FBH}} = 14V$ $V_{\text{PWMO}}$ decreasing $V_{\text{PWMO(OFF)}} = 0.5 \text{ V to } V_{\text{PWMO(OFF)}} = 3.5 \text{ V}$ $V_{\text{L,PWMO}} = 3.3 \text{ nF}$ |              |

(table continues...)

#### Multitopology single-channel DC-DC controller

#### **8 Dimming functions**

#### Table 11 (continued) Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                         | Symbol                 |      | Values                        |                      | Unit | Note or condition                                                                                           | P-      |

|-----------------------------------|------------------------|------|-------------------------------|----------------------|------|-------------------------------------------------------------------------------------------------------------|---------|

|                                   |                        | Min. | Тур.                          | Max.                 |      |                                                                                                             | Number  |

| PWMO gate driver output rise time | t <sub>R_PWMO</sub>    | -    | 2                             | 6                    | μs   | 1)<br>V <sub>FBH</sub> = 14V                                                                                | PRQ-104 |

|                                   |                        |      |                               |                      |      | $V_{\text{PWMO}}$ increasing $V_{\text{PWMO(ON)}} + 0.5 \text{ V to}$ $V_{\text{PWMO(ON)}} + 3.5 \text{ V}$ |         |

|                                   |                        |      |                               |                      |      | $C_{L,PWMO} = 3.3 \text{ nF}$                                                                               |         |

| PWMO gate driver output fall time | t <sub>F_PWMO</sub>    | -    | 2                             | 6                    | μs   | 1)<br>V <sub>FBH</sub> = 14 V                                                                               | PRQ-105 |

|                                   |                        |      |                               |                      |      | $V_{\text{PWMO}}$ decreasing $V_{\text{PWMO(OFF)}}$ - 0.5 V to $V_{\text{PWMO(OFF)}}$ - 3.5 V               |         |

|                                   |                        |      |                               |                      |      | $C_{\text{PWMO}} = 3.3 \text{ nF}$                                                                          |         |

| PWMO output voltage<br>ON state   | V <sub>PWMO(ON)</sub>  | _    | <i>V</i> <sub>FBH</sub> - 6.5 | V <sub>FBH</sub> - 5 | V    | 1)<br>V <sub>FBH</sub> > 7.5 V                                                                              | PRQ-106 |

| PWMO output voltage               | V <sub>PWMO(OFF)</sub> | -    | V <sub>FBH</sub>              | _                    | V    | 1)                                                                                                          | PRQ-107 |

| OFF state                         |                        |      |                               |                      |      | V <sub>FBH</sub> = 14 V                                                                                     |         |

<sup>1)</sup> Not subject to production test, specified by design

## 8.2 Digital PWM dimming

The TLD6098-1EP has a dedicated input pin to modulate the average current in a LED string with a digital pattern.

The device recognizes a digital PWM dimming signal on DC/PWMI pin if:

- The minimum voltage on DC/PWMI is lower than  $V_{\text{DC/PWMI}(OFF)}$

- The maximum voltage on DC/PWMI is higher than V<sub>DC/PWMI(ON)</sub>

- The maximum frequency on DC/PWMI is less than 1 kHz

- · No faults are detected

If a valid pattern is recognized and the  $V_{\rm DC/PWMI}$  is higher than  $V_{\rm DC/PWMI(ON)}$  the NMOS gate driver is enabled and the voltage of PWMO pin is  $V_{\rm PWMO(OFF)}$ ; else the NMOS gate driver is disabled and the voltage of PWMO pin is  $V_{\rm PWMO(OFF)}$

#### **8 Dimming functions**

#### 8.2.1 Electrical characteristics

#### Table 12 Electrical Characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                            | Symbol                    |      | Values |      | Unit | Note or condition                   | P-<br>Number |

|--------------------------------------|---------------------------|------|--------|------|------|-------------------------------------|--------------|

|                                      |                           | Min. | Тур.   | Max. |      |                                     |              |

| DC/PWMI input voltage high threshold | V <sub>DC/PWMI(ON)</sub>  | 4.0  | -      | -    | V    | _                                   | PRQ-97       |

| DC/PWMI input voltage low threshold  | V <sub>DC/PWMI(OFF)</sub> | -    | -      | 0.8  | V    | -                                   | PRQ-98       |

| DC/PWMI input current                | I <sub>DC/PWMI</sub>      | _    | _      | 200  | μΑ   | $V_{\rm DC/PWMI} = V_{\rm IN}$      | PRQ-99       |

| DC/PWMI input current                | I <sub>DC/PWMI</sub>      | -    | _      | 1    | μΑ   | <i>V</i> <sub>DC/PWMI</sub> = 0.8 V | PRQ-100      |

| DC/PWMI minimum ON time              | t <sub>DC/PWMI(ON)</sub>  | 6    | -      | -    | μs   | -                                   | PRQ-101      |

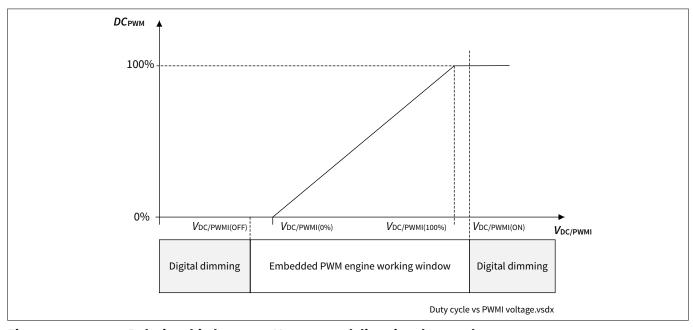

## 8.3 Embedded PWM engine

The embedded PWM engine helps to reduce the color shift when a LED string is dimmed down without using timer or microcontroller. It generates a pulse width modulation (PWM) adjustable in frequency and duty cycle. A possible application is the daytime running light dimmed down to position light without using microcontroller or timer.

The embedded PWM dimming function is enabled if the voltage on DC/PWMI pin is in between DC/PWMI input voltage 0% dimming  $V_{\rm DC/PWM~0\%}$  and DC/PWMI input voltage 100% dimming  $V_{\rm DC/PWM~100\%}$ .

This voltage is translated in the duty cycle of the PWM signal with DC/PWMI duty cycle resolution  $n_{\rm DC/PWMI}$ .

Figure 14 Relationship between  $V_{\rm DC/PWMI}$  and dimming duty cycle

If the embedded PWM dimming function is enabled, the behavior of PWMO pin is the following:

• The PWMO voltage switches between PWMO output voltage ON state  $V_{\text{PWMO(ON)}}$  and PWMO output voltage OFF state  $V_{\text{PWMO(OFF)}}$

#### Multitopology single-channel DC-DC controller

#### **8 Dimming functions**

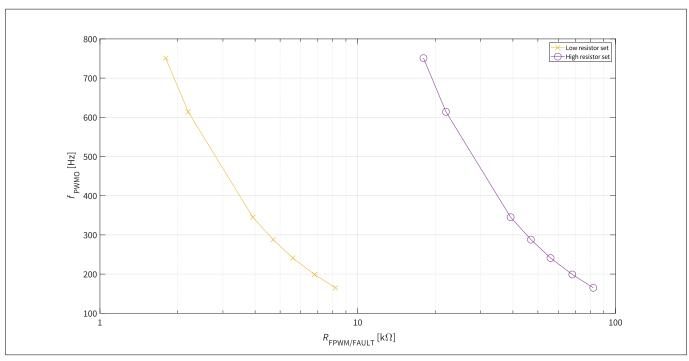

- The PWMO switching frequency depends on the resistor value placed on FPWM/FAULT pin

- The PWM duty cycle is linearly adjusted with the voltage on DC/PWMI pin

Any faults disables the embedded PWM engine and forces the voltage on PWMO pin to  $V_{\text{PWMO}(\text{OFF})}$ .

The resistor connected on FPWM/FAULT is used to:

- Adjust the frequency of the embedded PWM engine

- Enable two different reactions on FPWM/FAULT pin during the fault report

- Enable or disable the voltage control loop

If the resistor on FPWM/FAULT pin is in FPWM/FAULT high resistor range  $R_{\text{FPWM/FAULT}(H)}$  the device has the following behavior:

- The frequency of PWM engine is adjusted in  $f_{PWMO}$  range

- In case a fault is detected, it is reported on FPWM/FAULT pin with proper duty cycle

- The voltage loop is disabled and the overvoltage is detected with a comparator (detailed information are described in Protection and fault management chapter)

While if resistor on FPWM/FAULT pin is in FPWM/FAULT low resistor range  $R_{\text{FPWM/FAULT}(1)}$

- The frequency of PWM engine is adjusted in  $f_{PWMO}$  range

- The faults are reported on FPWM/FAULT1,2 pin without a specific indication

- Voltage regulation loop is enabled and concurrent to current regulation loop

The frequency of embedded PWM generator can be calculated by:

$$f_{PWMO\_HR} = \frac{1}{\left(7.4 \cdot 10^{-8} \cdot R_{FPWM/FAULT}\right)}$$

(3)

for resistor R<sub>FPWM/FAULT(H)</sub> range

$$f_{PWMO\_LR} = \frac{1}{(7.4 \cdot 10^{-7} \cdot R_{FPWM/FAULT})} \tag{4}$$

for resistor  $R_{\text{FPWM/FAULT(L)}}$  range.

## Multitopology single-channel DC-DC controller

#### **8 Dimming functions**

Relationship between  $R_{\mathrm{FPWM/FAULT}}$  and the frequency of PWMO Figure 15

The table below summarizes the differences between two resistor sets on FPWM/FAULT pin

Table 13 Resistor differences on fault pin

|              | R <sub>FPWM/FAULT(H)</sub>                                    | R <sub>FPWM</sub> /FAULT(L)                                                                         |

|--------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Fault report | Each fault reported with a dedicated duty cycle on FPWM/FAULT | The faults are reported by raising the voltage on FPWM/FAULT pin until the faulty status is removed |

| Voltage loop | Disabled                                                      | Enabled                                                                                             |

## Multitopology single-channel DC-DC controller

#### **8 Dimming functions**

#### 8.3.1 Electrical characteristics

#### **Table 14 Electrical characteristics**

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                             | Symbol                        |       | Values |       | Unit | Note or condition                                     | P-      |

|---------------------------------------|-------------------------------|-------|--------|-------|------|-------------------------------------------------------|---------|

|                                       |                               | Min.  | Тур.   | Max.  |      |                                                       | Number  |

| DC/PWMI input voltage<br>0% dimming   | V <sub>DC/PWMI(0%)</sub>      | 0.965 | 1      | 1.035 | V    | V <sub>IVCC</sub> = 5 V                               | PRQ-110 |

| DC/PWMI input voltage<br>100% dimming | V <sub>DC/PWMI(100%)</sub>    | 3.53  | 3.6    | 3.67  | V    | V <sub>IVCC</sub> = 5 V                               | PRQ-111 |

| DC/PWMI equivalent pull down resistor | R <sub>DC/PWMI</sub>          | 1.5   | 2.5    | 3.5   | ΜΩ   | V <sub>DC/PWMI</sub> = 4 V<br>2)                      | PRQ-433 |

| PWMO duty cycle                       | DC <sub>PWMO</sub>            | 8     | 10     | 12    | %    | V <sub>PWMI</sub> = 1.26 V<br>V <sub>IVCC</sub> = 5 V | PRQ-112 |

| FPWM/FAULT reference voltage          | V <sub>FPWM/</sub> FAULT(REF) | 0.72  | 0.8    | 0.88  | V    | -                                                     | PRQ-114 |

| FPWM/FAULT output current             | I <sub>FPWM/FAULT</sub>       | -     | _      | 3     | mA   | V <sub>FPWM/FAULT</sub> = 0 V                         | PRQ-115 |

| PWMO dimming frequency                | $f_{PWMO}$                    | 315   | 345    | 375   | Hz   | $R_{\text{FPWM/FAULT}} = 3.92 \text{ k}\Omega$        | PRQ-116 |

| PWMO dimming frequency                | $f_{PWMO}$                    | 315   | 345    | 375   | Hz   | $R_{\text{FPWM/FAULT}} = 39.2 \text{ k}\Omega$        | PRQ-370 |

| DC/PWMI duty cycle resolution         | n <sub>DC/PWMI</sub>          | _     | 10     | _     | bit  | 1) 2)                                                 | PRQ-313 |

| FPWM/FAULT high range resistor        | R <sub>FPWM/FAULT(H)</sub>    | 18    | _      | 90    | kΩ   | 1) 2)                                                 | PRQ-590 |

| FPWM/FAULT low range resistor         | R <sub>FPWM/FAULT(L)</sub>    | 1.8   | _      | 9     | kΩ   | 1) 2)                                                 | PRQ-591 |

<sup>1)</sup> Not subject to production test, specified by design

<sup>2)</sup> Not subject to production test, specified by design

#### Multitopology single-channel DC-DC controller

# **(infineon**

#### 9 Protections and fault management

## 9 Protections and fault management

The fault conditions are identified by checking the status of PWMO, IVCC and FPWM/FAULT pins.

The device disables the gate driver and reports fault on FPWM/FAULT pin if the following faults are detected:

- · Short to ground

- Overvoltage on VFB pin

- Overtemperature

- Overvoltage on FBH pin

- Overcurrent

The faults are reported by raising the voltage on FPWM/FAULT pin to V<sub>FPWM/FAULT</sub>(FAULT).

The output waveform of the fault reporting depends on the resistor connected to FPWM/FAULT pin.

The status of FPWM/FAULT pin can be monitored by a microcontroller. In this case a series resistor (10 k $\Omega$  minimum) has to be used between FPWM/FAULT and the input pin of the microcontroller.

The PWMO gate driver biases the PMOS in OFF state to disconnect the load from the DC-DC output during:

- Overvoltage on VFB pin,

- Overvoltage on FBH pin

- Overtemperature

- Overcurrent

During a short to ground, the PMOS is biased in OFF state during the  $t_{\rm S2G}$  and it is biased in ON state every  $t_{\rm FAULT}$  for a  $(t_{\rm SS})$  to detect if the fault has been removed.

#### 9.1 Electrical characteristics

#### Table 15 Electrical characteristics

$V_{IN}$  = 8 V to 36 V;  $T_{J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                            | Symbol                          |      | Values |      |    | Note or condition | P-      |

|--------------------------------------|---------------------------------|------|--------|------|----|-------------------|---------|

|                                      |                                 | Min. | Тур.   | Max. |    |                   | Number  |

| FPWM/FAULT output voltage with fault | V <sub>FPWM/</sub> FAULT(FAULT) | 4    | -      | -    | V  | 1)                | PRQ-117 |

| Fault period                         | $t_{FAULT}$                     | 9    | 10     | 11   | ms | 1) 2)             | PRQ-133 |

<sup>1)</sup> Not subject to production test, specify by design

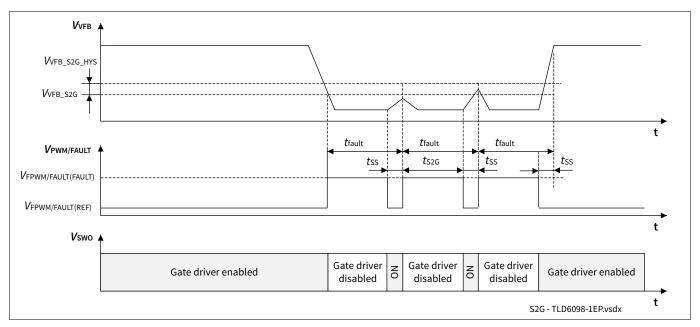

#### 9.2 Short to ground

The short to ground detection feature protects the LED driver from an excess of current during a short circuit.

This fault is detected if the voltage of VFB pin is lower than short to ground voltage threshold  $V_{\rm FB\_S2G}$  for a time longer than short to ground reaction time  $t_{\rm S2G\_RT}$ .

After a fault time with short to ground  $t_{S2G}$  a soft start routine is triggered. The fault is released if the voltage on VFB pin is higher than ( $V_{FB\_S2G}+V_{FB\_S2G\_HYST}$ ) at the end of the soft start.

During soft-start routine, the short to ground detection is disabled and the voltage of FPWM/FAULT pin is kept at  $V_{\text{FPWM/FAULT(REF)}}$ .

The reaction to short to ground is:

- 1. The voltage on FPWM/FAULT pin is raised to  $V_{\text{FPWM/FAULT}}$  for  $t_{\text{S2G}}$  time

- 2. After a  $t_{S2G}$  time the soft-start routine is performed

- **3.** At the end of soft-start routine, the check on the voltage  $V_{VFB}$  is redone

<sup>2)</sup> Not subject to production test, specify by design

#### Multitopology single-channel DC-DC controller

#### 9 Protections and fault management

If the fault is still present, the procedure is repeated, otherwise the driver restarts. This routine is valid whatever resistor used on FPWM/FAULT pin.

Figure 16 Timing diagram during short to ground detection

A short to ground event simultaneous with an overcurrent event is detected once even the voltage on DC/PWMI pin is lower than  $V_{\text{DC/PWMI(OFF)}}$ .

In all the other cases, the short to ground is not detected when the voltage on DC/PWMI pin is lower than  $V_{\rm DC/PWMI(OFF)}$ .

#### 9.2.1 Electrical characteristics

#### Table 16 Electrical characteristics

$V_{\rm IN}$  = 8 V to 36 V;  $T_{\rm J}$  = -40°C to +150°C; all voltages with respect to ground, positive current flowing into pin; (unless otherwise specified)

| Parameter                          | Symbol                   | Values |      |      | Unit | Note or condition  | P-      |

|------------------------------------|--------------------------|--------|------|------|------|--------------------|---------|

|                                    |                          | Min.   | Тур. | Max. |      |                    | Number  |

| Fault time with short to ground    | t <sub>S2G</sub>         | 7.2    | 8    | 8.8  | ms   | 1)                 | PRQ-134 |

| Short to ground reaction time      | t <sub>S2G_RT</sub>      | 4      | _    | 20   | μs   | -                  | PRQ-121 |

| Short to ground voltage threshold  | $V_{FB\_S2G}$            | 93     | 100  | 107  | mV   | Voltage decreasing | PRQ-119 |

| Short to ground voltage hysteresis | V <sub>FB_S2G_HYST</sub> | -      | 5    | 10   | mV   | 1)                 | PRQ-120 |

<sup>1)</sup> Not subject to production test, specified by design

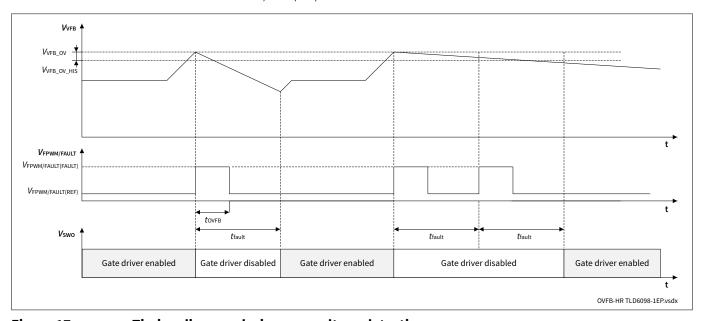

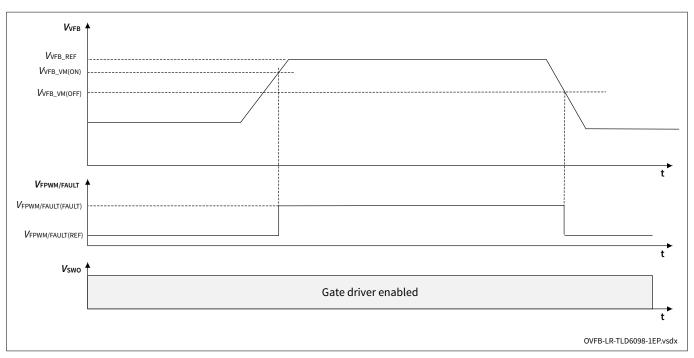

## 9.3 Output overvoltage and voltage regulation

Based on the resistor used on FPWM/FAULT pin the device implements an overvoltage detection with a comparator or enabling a voltage regulation by using the internal voltage loop.

#### Multitopology single-channel DC-DC controller

#### 9 Protections and fault management

If the resistor connected to FPWM/FAULT pin is in the  $R_{\text{FPWM/FAULT(H)}}$  range, the overvoltage comparator is enabled with VFB overvoltage threshold  $V_{\text{VFB\_OV.}}$  The fault is detected when the VFB voltage is above this threshold.

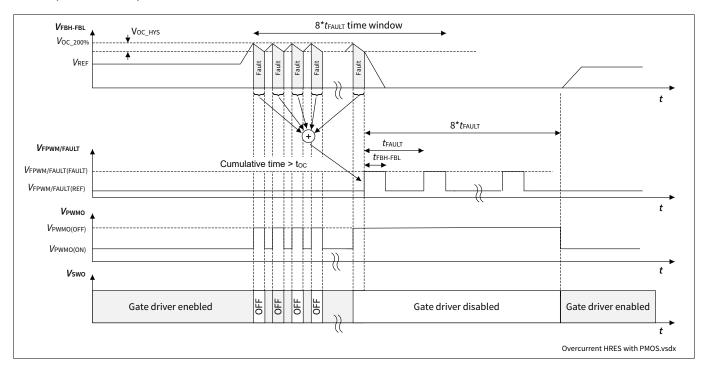

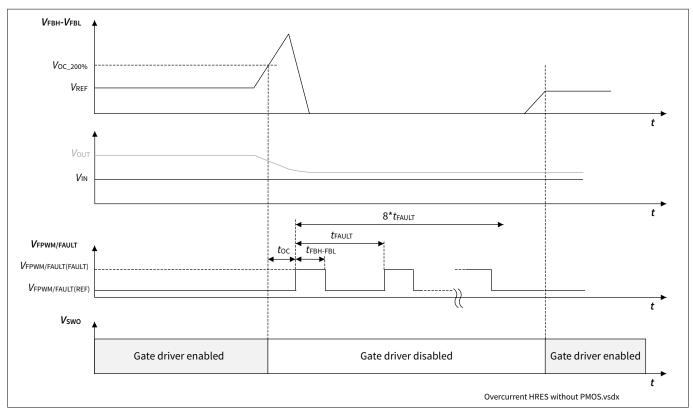

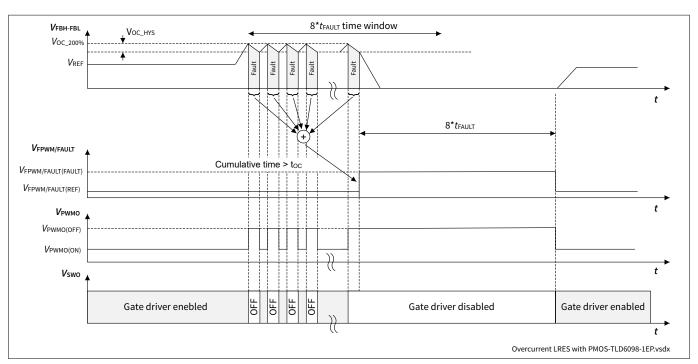

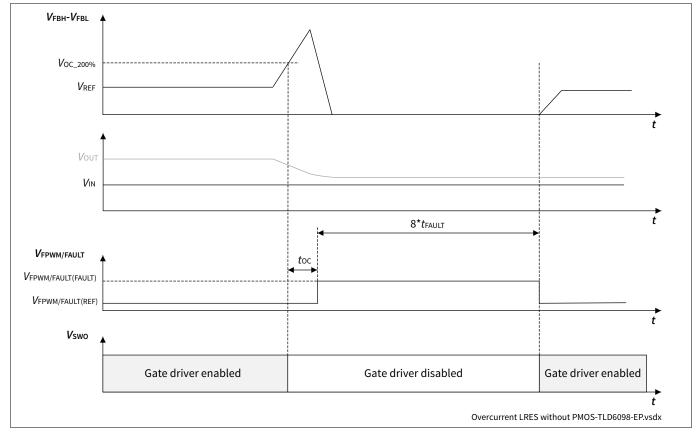

The device reacts by: