# Infineon<sup>®</sup> LIN LED Driver

# TLD7396EK

High Side Driver IC 3 channels

## Data Sheet

Rev. 1.0, 2012-067-02

## Automotive Power

#### **Table of Contents**

## **Table of Contents**

| 1              | Overview                                                             | . 4 |

|----------------|----------------------------------------------------------------------|-----|

| 2              | Block Diagram                                                        | 6   |

| 3              | Pin Configuration                                                    | . 7 |

| 3.1            | Pin Assignment                                                       |     |

| 3.2            | Pin Definitions and Functions                                        | 7   |

| 4              | General Product Characteristics                                      | . 8 |

| 4.1            | Absolute Maximum Ratings                                             | . 8 |

| 4.2            | Functional Range                                                     | . 9 |

| 4.3            | Thermal Resistance                                                   | 9   |

| 5              | State Machine and Operating Modes                                    | 10  |

| 5.1            | Operating Modes                                                      |     |

| 5.1.1          | Normal Mode                                                          | 11  |

| 5.1.2          | Programming Mode (Flash-Mode)                                        | 11  |

| 5.1.3          | Sleep Mode                                                           | 11  |

| 5.2            | Internal Supply Unit                                                 |     |

| 5.2.1          | Power-On Reset                                                       |     |

| 5.2.2          | Low Voltage Behavior                                                 |     |

| 5.3            | Electrical Characteristics Internal Supply                           |     |

| 6              | LIN-Interface                                                        |     |

| 6.1            | LIN-Basics                                                           |     |

| 6.2            | Physical Layer                                                       |     |

| 6.2.1          | LIN-Specifications 2.1                                               |     |

| 6.2.2          | Wake-Up via LIN-bus                                                  |     |

| 6.2.3          | LIN Operation During Low $V_{\rm S}$ Voltage                         |     |

| 6.2.4          | LIN-bus Driver Over Temperature Protection                           |     |

| 6.2.5<br>6.2.6 | LIN message Idle Time                                                |     |

| 6.3            | Oscillator Tolerance                                                 |     |

| 6.4            | Protocol Handler (Data Link Layer)                                   |     |

| 6.4.1          | LIN Communication Error Detection                                    |     |

| 6.5            | LIN Message Decoder (Application Layer)                              |     |

| 6.5.1          | Frame Identifiers                                                    |     |

| 6.5.2          | Slave Published Frame-IDs                                            |     |

| 6.5.3          | Master Published Frame-IDs                                           |     |

| 6.5.4          | Location Identifier                                                  | 22  |

| 6.6            | Message Frame Decoding                                               | 23  |

| 6.6.1          | MSTR_L1_P00 Message Frame (Set color and intensity)                  | 23  |

| 6.6.2          | MSTR_L1_P01 Message Frame (LED calibration, direct intensity access) | 24  |

| 6.6.3          | MSTR_L1_P02 Message Frame (Write Non-Volatile Memory)                |     |

| 6.6.4          | MSTR_L1_P03 Message Frame (Set custom dim-times)                     |     |

| 6.6.5          | MSTR_L1_P04 and LED_L1_P02 Message Frame (Go to sleep command)       |     |

| 6.6.5.1        | Go to sleep command                                                  |     |

| 6.6.5.2        | Read by Identifier                                                   |     |

| 6.6.5.3        | Assign Frame Identifier range                                        |     |

| 6.6.6          | LED_L1_P00 Message Frame (Diagnostic Response)                       |     |

| 6.6.7          | LED_L1_P01 Message Frame (Read NVM content)                          | 31  |

#### **Table of Contents**

| 7               | Intensity Generation Unit                            |    |

|-----------------|------------------------------------------------------|----|

| 7.1<br>7 1 1    | Intensity Calculation                                |    |

| 7.1.1           | Global Intensity                                     |    |

| 7.1.2           | Sets of Output Intensities                           |    |

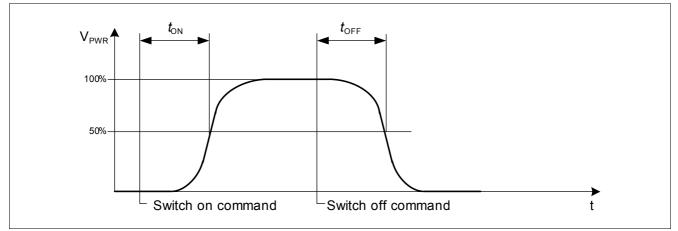

| 7.1.3           | Dimming                                              |    |

| 7.2.1           | Custom Dim Times                                     |    |

| 722             | Color Transitioning                                  |    |

| 7.3             | Variable Off-time Generator                          |    |

| 7.4             | Electrical Characteristics Intensity Generation Unit |    |

| •               |                                                      |    |

| <b>8</b><br>8.1 | Non-Volatile Memory                                  |    |

| 8.2             | Non Volatile Memory Map                              |    |

| 8.2.1           | NVM Programming Procedure                            |    |

| 8.3             | NVM Frase                                            |    |

| 8.4             | NVM Lease                                            |    |

| 8.4.1           | NVM Fror                                             |    |

| 8.5             | Electrical Characteristics NVM                       |    |

| 9               |                                                      |    |

| <b>9</b><br>9.1 | Power Stage                                          |    |

| 9.1             | SENSE Input                                          |    |

| 9.2             | Electrical Characteristics Power Stage               |    |

| 9.4             | Protection and Diagnosis                             |    |

| 9.4.1           | Over Load Behavior                                   |    |

| 9.5             | Electrical Characteristics Protection and Diagnosis  |    |

| 10              |                                                      |    |

| 10.1            | Further Application Information                      |    |

|                 |                                                      |    |

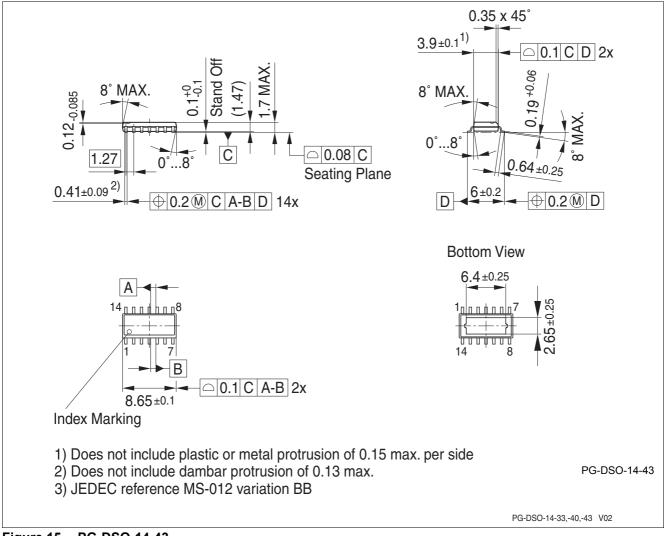

| 11              | Package Outlines                                     | 47 |

| 12              | Revision History                                     | 48 |

## High Side Driver IC 3 channels

## TLD7396EK

## 1 Overview

#### Features

- 3 channel device with integrated output stages (current sources), optimized to drive LEDs

- Communication via integrated LIN-transceiver

- LIN-transceiver compatible to LIN 2.1 (20 kbit/s)

- Integrated state machine for LIN protocol handling and LIN-message decoding

- 16 sets of output currents (e.g. color points when using RGB LEDs) can be stored in the integrated non volatile memory (NVM)

- · Device Node ID (address) can be stored in the integrated NVM

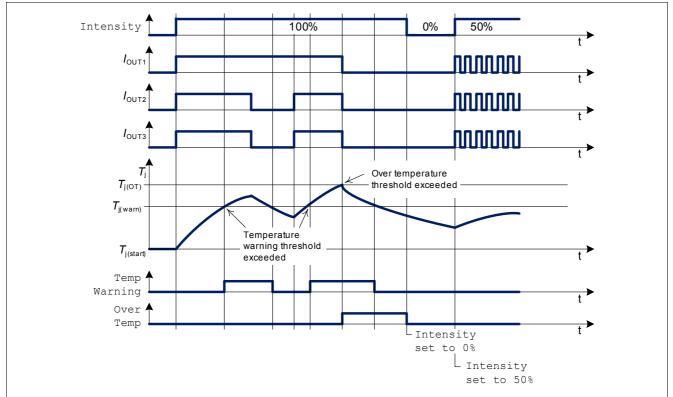

- Autonomous intensity variation of outputs for theater dimming effects with 12 bit resolution and smooth color transitionings with 10 bit resolution provided by integrated intensity generation unit

- · Low current consumption in sleep mode Wake up via LIN-bus

- · Overload protection and under voltage detection

- Wide temperature range: -40 °C < T<sub>i</sub> < 150 °C</li>

- 150mil exposed heatslug DSO-package

- Green Product (RoHS compliant)

- AEC Qualified

#### Description

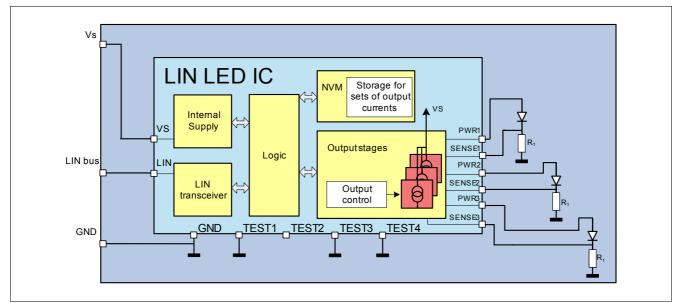

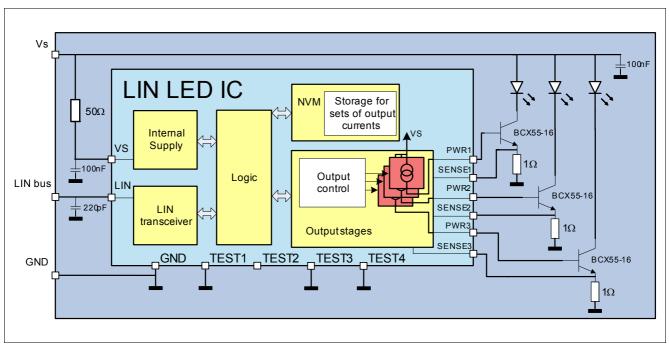

The Infineon LIN LED Driver IC is a three channel highside driver IC optimized to drive external NPN-transistors. The output current is controlled practically independent of load and supply voltage changes.

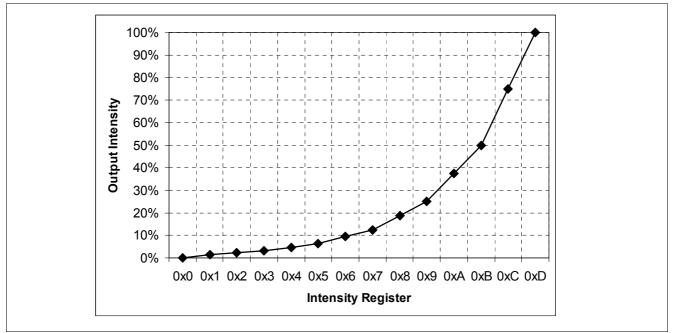

The average output current of each channel can be controlled by an 8-bit intensity setting. 16 different sets of intensity settings (i.e. 16 triplets of intensities or average output currents) can be stored in an on-chip non-volatile memory. This is especially useful, when driving a Red-Green-Blue (RGB) LED, where each triplet of intensities represents one color. In addition to these sets of average output currents, the intensities can be dimmed down in 14 steps. The IC also supports theater dimming with a dim-time of up to multiple seconds.

Configuration and diagnosis are done via the integrated LIN interface. LIN 2.1 standard is supported. The integrated state machine supports the LIN protocol handling and command decoding.

| Туре      | Package      | Marking   |

|-----------|--------------|-----------|

| TLD7396EK | PG-DSO-14-43 | TLD7396EK |

PG-DSO-14-43

#### Overview

#### Table 1 Product Summary

| Operating voltage                                                                    | V <sub>S(nom)</sub>                         | 7 V 18 V |

|--------------------------------------------------------------------------------------|---------------------------------------------|----------|

| Extended operating voltage (LIN-transceiver active)                                  | V <sub>S(ext)</sub>                         | 6 V 34V  |

| Minimum supply voltage range for operation,<br>(Outputs active, LIN-transceiver off) | V <sub>S(PD)</sub>                          | 4.8 V    |

| Maximum voltage                                                                      | V <sub>S(max),</sub> V <sub>OUTx(max)</sub> | 40 V     |

| Maximum output current to drive external NPN-<br>transistors                         | I <sub>PWR(nom,max)</sub>                   | 40 mA    |

| Current consumption in sleep mode                                                    | $I_{\rm S(sleep,typ)}$                      | 16 μΑ    |

#### **Protective functions**

- ESD protection

- Under voltage lock out

- Over Load protection

- Over temperature prewarning

- Over temperature protection

#### **Diagnostic functions**

- LIN communication error detection

- Over load detection via LIN message

#### Applications

Designed for standard LED lighting applications such as ambient lighting, exterior lighting, interior illumination, dome light, and dash board. Especially well suited for RGB color mixing applications.

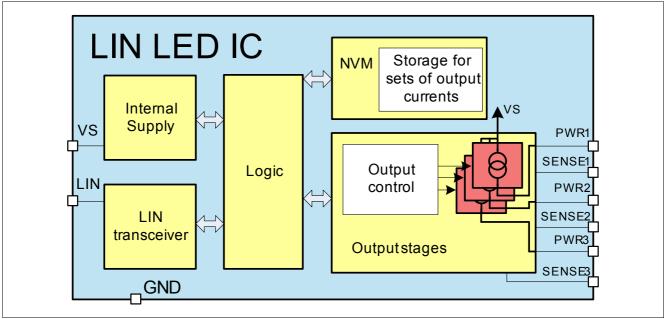

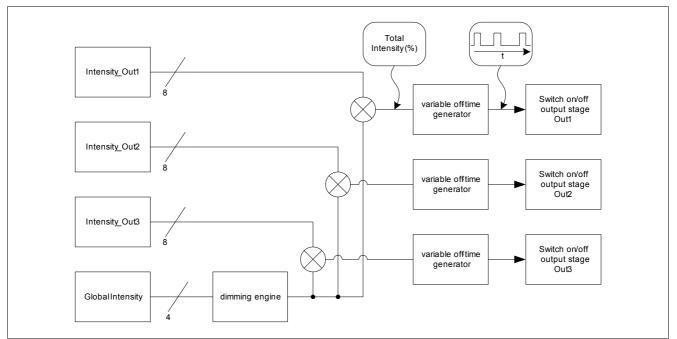

**Block Diagram**

## 2 Block Diagram

Figure 1 Basic Block Diagram

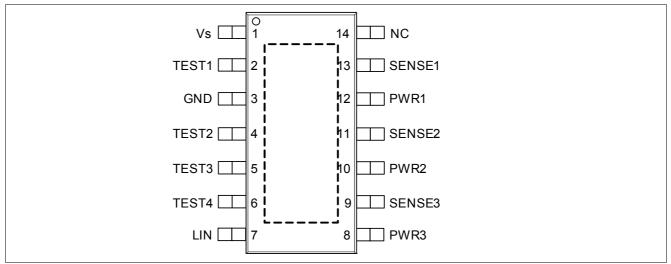

**Pin Configuration**

## 3 Pin Configuration

## 3.1 Pin Assignment

Figure 2 Pin Configuration

## 3.2 Pin Definitions and Functions

| Pin            | Symbol |                                                                                                                                           |

|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | Vs     | Supply Voltage; battery supply, connect an Reverse polarity protection and a decoupling capacitor (100nF - $1\mu$ F), see also Figure 14  |

| 2              | TEST1  | Test Pin; used for Infineon end of line test, connect to GND in application                                                               |

| 3              | GND    | Ground                                                                                                                                    |

| 4              | TEST2  | Test Pin; used for Infineon end of line test, leave unconnected in application                                                            |

| 5              | TEST3  | Test Pin; used for Infineon end of line test, connect to GND in application                                                               |

| 6              | TEST4  | Test Pin; used for Infineon end of line test, connect to GND in application                                                               |

| 7              | LIN    | <b>LIN Input;</b> Connected to LIN-master with a filter capacitor (e.g. 220pF) and an external over voltage protection (e.g. MMBZ27VALT1) |

| 8              | PWR3   | Base Driver Output 3                                                                                                                      |

| 9              | SENSE3 | Sense Input 3                                                                                                                             |

| 10             | PWR2   | Base Driver Output 2                                                                                                                      |

| 11             | SENSE2 | Sense Input 2                                                                                                                             |

| 12             | PWR1   | Base Driver Output 2                                                                                                                      |

| 13             | SENSE1 | Sense Input 1                                                                                                                             |

| 14             | NC     | Not Connected                                                                                                                             |

| Exposed<br>Pad | GND    | Exposed Pad; connect to GND in application                                                                                                |

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings <sup>1)</sup>

$T_j$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                         | Symbol           | Lim  | it Values | Unit     | Conditions                                                                 |

|---------|-----------------------------------|------------------|------|-----------|----------|----------------------------------------------------------------------------|

|         |                                   |                  | Min. | Max.      |          |                                                                            |

| Voltage | S                                 | ŀ                | -    |           |          | -                                                                          |

| 4.1.1   | Supply Voltage                    | Vs               | -0.3 | 40        | V        | -                                                                          |

| 4.1.2   | Input Voltage LIN                 | $V_{LIN}$        | -40  | 40        | V        | -                                                                          |

| 4.1.3   | Sense Input Voltage               | $V_{SENSEx}$     | -0.3 | 6         | V        | -                                                                          |

| 4.1.4   | Base Driver Output Voltage        | $V_{PWRx}$       | -0.3 | 6         | V        | -                                                                          |

| Current | S                                 |                  | -    |           |          |                                                                            |

| 4.1.5   | Base Driver Output Current        | $I_{PWRx}$       | -    | 60        | mA       | -                                                                          |

| 4.1.6   | LIN Current                       | $I_{LIN}$        | -    | 150       | mA       | internally limited                                                         |

| Temper  | atures                            |                  | -    |           |          |                                                                            |

| 4.1.7   | Junction Temperature              | $T_{\rm j}$      | -40  | 150       | °C       | -                                                                          |

| 4.1.8   | Ambient Operating Temperature     | Ta               | -40  | 85        | °C       | -                                                                          |

| 4.1.9   | Storage Temperature               | $T_{\rm stg}$    | -55  | 150       | °C       | -                                                                          |

| ESD Su  | sceptibility                      |                  |      |           | <b>I</b> |                                                                            |

| 4.1.10  | ESD Resistivity (all pins)        | V <sub>ESD</sub> | -2   | 2         | kV       | all pins<br>Human Body<br>Model (100 pF via<br>$1.5 \text{ k}\Omega)^{2)}$ |

| 4.1.11  | ESD Resistivity Vs and LIN to GND | V <sub>ESD</sub> | -6   | 6         | kV       | Human Body<br>Model (100 pF via $1.5 \text{ k}\Omega)^{2)}$                |

| 4.1.12  | ESD Resistivity all pins          | $V_{ESD}$        | -500 | 500       | V        | CDM <sup>3)</sup>                                                          |

| 4.1.13  | ESD Resistivity corner pins       | $V_{ESD}$        | -750 | 750       | V        | CDM <sup>3)</sup>                                                          |

1) Not subject to production test, specified by design

2) ESD susceptibility, Human Body Model "HBM" according to ANSI/ESDA/JEDEC JS-001-2011

3) ESD susceptibility, Charged Device Model "CDM" according to JESD22-C101E

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **General Product Characteristics**

## 4.2 Functional Range

|        |                                                                                         |                         | Limit Values       |      | Unit | Conditions                                                         |

|--------|-----------------------------------------------------------------------------------------|-------------------------|--------------------|------|------|--------------------------------------------------------------------|

|        |                                                                                         |                         | Min.               | Max. |      |                                                                    |

|        | Supply Voltage Range for<br>Normal Operation                                            | $V_{\rm S(nom)}$        | 7                  | 18   | V    | -                                                                  |

|        | Extended Supply Voltage Range<br>for Operation, LIN-transceiver<br>active               | $V_{S(ext)}$            | 6                  | 34   | V    | Parameter deviations possible, see also Figure 4                   |

|        | Extended Supply Voltage Range<br>for Operation, Outputs active; LIN-<br>transceiver off | $V_{\rm S(ext,noLI}$ N) | V <sub>S(PD)</sub> | -    | V    | Parameter deviations possible, see <b>Spec</b> . <b>Pos. 5.3.6</b> |

| 4.2.17 | Supply Voltage transients slew rate                                                     | $dV_S/dt$               | 5                  | 5    | V/μs | 1)                                                                 |

| 4.2.18 | Junction Temperature                                                                    | $T_{\rm j}$             | -40                | 150  | °C   | _                                                                  |

1) Not subject to production test, specified by design

## 4.3 Thermal Resistance

| Pos.  | Parameter                      | Symbol              | Limit Values |      |      | Unit | Conditions                                |

|-------|--------------------------------|---------------------|--------------|------|------|------|-------------------------------------------|

|       |                                |                     | Min.         | Тур. | Max. |      |                                           |

| 4.3.1 | Junction to Case               | R <sub>thJC</sub>   | -            | 6    | -    | K/W  | <sup>1)</sup> based on simulation results |

| 4.3.2 | Junction to Ambient 1s0p board | R <sub>thJA</sub>   | _            | 65   | -    | K/W  | 1) 2)                                     |

| 4.3.3 | Junction to Ambient 2s2p board | $R_{\mathrm{thJA}}$ | -            | 38   | -    | K/W  | 1) 3)                                     |

1) Not subject to production test, specified by design

2) The  $R_{\text{thJA}}$  values are according to Jedec JESD51-3 at natural convection on 1s0p FR4 board. The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5 mm<sup>3</sup> board with 70µm Cu, 300 mm<sup>2</sup> cooling area.  $T_a$  = 85°C, total power dissipation 1.5 W distributed statically and homogeneously over all output stages.

3) The  $R_{\text{thJA}}$  values are according to Jedec JESD51-5,-7 at natural convection on 2s2p FR4 board. The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm<sup>3</sup> board with 2 inner copper layers (outside 2 x 70 µm Cu, inner 2 x 35µm Cu). Where applicable, a thermal via array under the exposed pad contacted the first inner copper layer.  $T_a = 85^{\circ}$ C, total power dissipation 1.5 W distributed statically and homogeneously over all output stages.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

## TLD7396EK

#### **State Machine and Operating Modes**

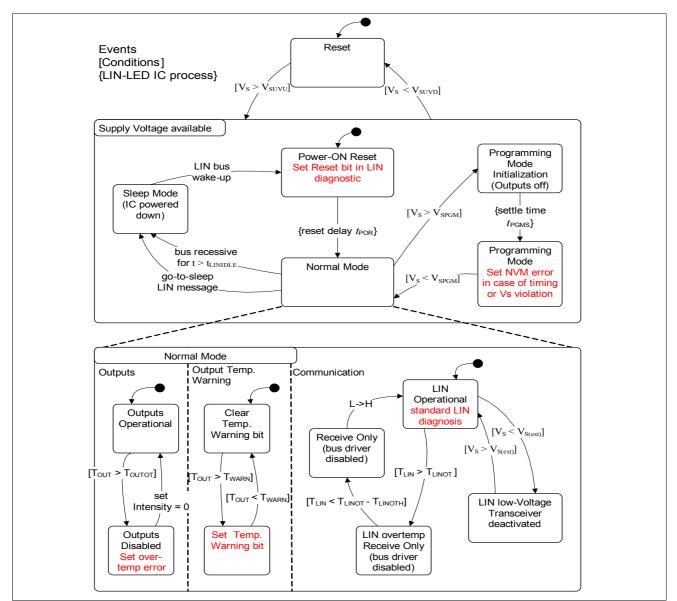

## 5 State Machine and Operating Modes

Figure 3 State-Chart, diagnostic features are highlighted in red

| State-Chart Legenu                             |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comment                                        | Symbol                                                                                                                                                                                                                      | Comment                                                                                                                                                                                                                                        |

| Supply Voltage at Vs pin                       | t <sub>PGM(s)</sub>                                                                                                                                                                                                         | Programming mode settle time, Pos. 8.5.3                                                                                                                                                                                                       |

| Extended Supply Voltage range,<br>Pos. 4.2.15  | $T_{LIN}$                                                                                                                                                                                                                   | Temperature of LIN-bus driver                                                                                                                                                                                                                  |

| Power-Up Voltage, Pos. 5.3.5                   | $T_{\text{LIN(OT)}}$                                                                                                                                                                                                        | LIN over temperature protection, Pos. 6.3.25                                                                                                                                                                                                   |

| Power-Down Voltage, Pos. 5.3.6                 | $T_{\text{LIN(OT,H)}}$                                                                                                                                                                                                      | LIN over temperature protection hysteresis, <b>Pos. 6.3.26</b>                                                                                                                                                                                 |

| Programming Voltage, Pos. 8.5.1 and Pos. 8.5.2 | T <sub>j</sub>                                                                                                                                                                                                              | Temperature of Output power stages                                                                                                                                                                                                             |

|                                                | Comment         Supply Voltage at Vs pin         Extended Supply Voltage range,         Pos. 4.2.15         Power-Up Voltage, Pos. 5.3.5         Power-Down Voltage, Pos. 5.3.6         Programming Voltage, Pos. 8.5.1 and | CommentSymbolSupply Voltage at Vs pin $t_{PGM(s)}$ Extended Supply Voltage range,<br>Pos. 4.2.15 $T_{LIN}$ Power-Up Voltage, Pos. 5.3.5 $T_{LIN(OT)}$ Power-Down Voltage, Pos. 5.3.6 $T_{LIN(OT,H)}$ Programming Voltage, Pos. 8.5.1 and $T_j$ |

#### Table 2State-Chart Legend

#### State Machine and Operating Modes

#### Table 2 State-Chart Legend

| Symbol                 | Comment                                 | Symbol        | Comment                                    |

|------------------------|-----------------------------------------|---------------|--------------------------------------------|

| t <sub>LIN(idle)</sub> | LIN communication time out, Pos. 6.3.23 | $T_{j(OT)}$   | Output deactivation threshold, Pos. 9.5.11 |

| t <sub>POR</sub>       | Power-ON Reset delay, Pos. 5.3.4        | $T_{i(warn)}$ | Output prewarning threshold, Pos. 9.5.10   |

## 5.1 Operating Modes

## 5.1.1 Normal Mode

Normal Mode is the default operating state and is automatically entered after the device goes through a power-on reset.

During normal mode the device interprets LIN bus messages in order to control the set of intensities (color points) and intensity of the RGB diode. The interpreted LIN instructions include:

- Selection of 1 of 16 average current set points stored in the integrated NVM

- Intensity setting

- Intensity ramp up/down for theater dimming effects

- Selection of the individual (RGB) intensities (e.g. for calibration)

- Request to respond to LIN-master with status and error diagnostic information

- Go to sleep mode

Note: A LIN-communication at frequencies around  $f_{\text{FLASH}}$  during normal mode ( $V_{\text{S}} < V_{\text{S}(\text{PGM,L})}$ ) or in programming mode ( $V_{\text{S}(\text{PGM,L})} < V_{\text{S}} < V_{\text{S}(\text{PGM,U})}$ , (Pos. 8.5.1 and Pos. 8.5.2)) without being the subscriber, brings the device into a stop-mode. A LIN-communication of the device is not possible any more until the LIN communication time out  $f_{\text{LIN(idle)}}$  (Pos. 6.3.23) is exceeded and the device enters the sleep mode, or a power-on reset is done.

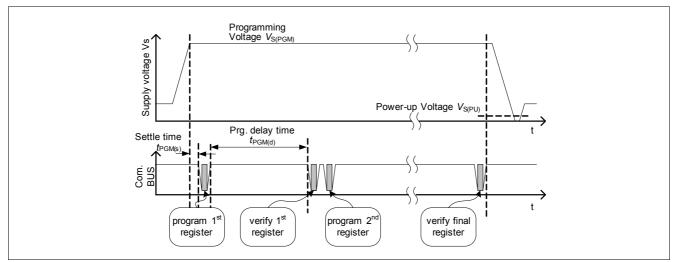

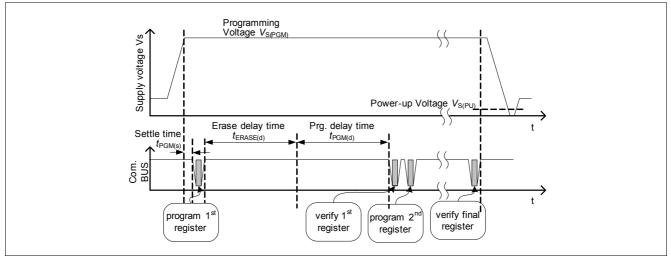

## 5.1.2 Programming Mode (Flash-Mode)

This mode is used to program the NVM. More details on the NVM programming can be found in **Chapter 8.2**. To enter this mode the user has to apply a supply voltage  $V_{\rm S}$  within the programming voltage range  $V_{\rm S(PGM,L)} < V_{\rm S} < V_{\rm S(PGM,U)}$  (**Pos. 8.5.1** and **Pos. 8.5.2**) for longer than the programming settle time  $t_{\rm PGM(s)}$  (**Pos. 8.5.3**). This also enables the LIN-transceiver flash-mode for higher speed data transmission. The maximum transmission rate on the LIN-bus can be increased to  $f_{\rm FLASH}$  (**Pos. 6.3.24**). In this operation mode all three output stages are turned off. *Note: Please consider the important note in Chapter 5.1.1*.

## 5.1.3 Sleep Mode

In order to reduce the current consumption the LIN LED Driver IC offers a sleep mode. In sleep mode the quiescent current on  $V_{s}$  and the leakage current on the pin LIN are cut back to a minimum.

To switch the LIN LED Driver IC from normal operation mode to sleep mode, the LIN-message "Go to Sleep" has to be received by the LIN LED Driver IC.

While the LIN LED Driver IC is in sleep mode the following functions are available:

- The output stage is disabled and the internal LIN-bus terminations are switched off (high impedance on the pin LIN). The internal current source on the LIN-pin ensures that the levels on the pin LIN remains recessive and protects the LIN-network against accidental bus Wake-Up events.

- The receiver stage is turned off.

The LIN-bus wake-up comparator is active and turns the LIN LED Driver IC to normal operation mode in case of a bus wake-up event.

#### **State Machine and Operating Modes**

## 5.2 Internal Supply Unit

## 5.2.1 Power-On Reset

In case  $V_{\rm S}$  is dropping below the Power-On reset level  $V_{\rm S} < V_{\rm S(PD)}$ , the LIN LED Driver IC is in Reset condition. In Reset condition the output stages of the LIN LED Driver IC are disabled and no communication is possible.

If the power supply  $V_{S}$  reaches a higher level as the minimum operating voltage level  $V_{S} > V_{S(PU)}$ , the LIN LED Driver IC will become active again. The Error bit "Reset" is set to 1 and cleared after the next valid diagnosis request frame (LED\_L1\_P00 or LED\_L1\_P01).

During a Power-On Reset all registers are set to their default value. The settings programmed in the NVM will not be changed during a Power-On Reset.

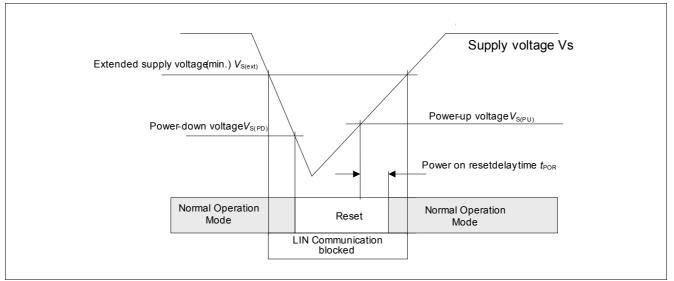

## 5.2.2 Low Voltage Behavior

The LIN LED Driver IC has under voltage detection and shut-off integrated in order to prevent erroneous operation at low supply voltages.

With Vs below  $V_{\text{S(nom)min}}$  (Pos. 4.2.14) but above  $V_{\text{S(ext)min}}$  (Pos. 4.2.15) the device functions, but specification parameter deviations are possible, the integrated LIN-transceiver is active. With Vs below  $V_{\text{S(ext)min}}$  (Pos. 4.2.15) but above  $V_{\text{S(PD)}}$  (Pos. 5.3.6) the output stages remain on, the internal logic will be active and the content of the internal registers is not cleared. The integrated LIN-transceiver is deactivated (communication is blocked). As soon as the supply voltage is above  $V_{\text{S(ext)min}}$  (Pos. 4.2.15) again the integrated LIN-transceiver is activated again without generating any diagnostic error.

Figure 4 Power-on reset / Low voltage behavior

#### State Machine and Operating Modes

## 5.3 Electrical Characteristics Internal Supply

#### **Electrical Characteristics: Supply**

$V_{\rm S}$  = 7 V to 18 V,  $T_{\rm j}$  = -40 °C to 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.  | Parameter                                                   | Symbol                          | Limit Values |      |      | Unit | Conditions                                                                               |

|-------|-------------------------------------------------------------|---------------------------------|--------------|------|------|------|------------------------------------------------------------------------------------------|

|       |                                                             |                                 | Min.         | Тур. | Max. |      |                                                                                          |

| 5.3.1 | Supply current consumption in sleep mode                    | $I_{\rm S(sleep)}$              | -            | -    | 18   | μA   | $V_{\rm S}$ = 16 V;<br>$V_{\rm LIN}$ = $V_{\rm s}$                                       |

| 5.3.2 | Typical supply current consumption<br>in sleep mode         | $I_{\rm S(sleep,typ)}$          | -            | -    | 16   | μA   | <sup>1)</sup> $T_{\rm j}$ < 85 °C<br>$V_{\rm S}$ = 13.5 V<br>$V_{\rm LIN}$ = $V_{\rm S}$ |

| 5.3.3 | Current consumption at $V_{\rm S}$ in normal operation mode | Is                              | -            | -    | 8    | mA   | $I_{PWRx} = 0 \text{ mA}$<br>outputs off                                                 |

| 5.3.4 | Power on reset delay time                                   | t <sub>POR</sub>                | -            | _    | 5    | ms   | <sup>1)</sup> see Figure 4                                                               |

| 5.3.5 | Power-up voltage                                            | $V_{\rm S(PU)}$                 | 4            | -    | 5    | V    | see Figure 4                                                                             |

| 5.3.6 | Power-down voltage                                          | V <sub>S(PD)</sub>              | -            | -    | 4.8  | V    | see Figure 4                                                                             |

| 5.3.7 | Under-voltage hysteresis                                    | $V_{\rm S(PU)} - V_{\rm S(PD)}$ | 100          | -    | -    | mV   | 1)                                                                                       |

1) Not subject to production test, specified by design

## 6 LIN-Interface

The LIN LED Driver IC provides a LIN-transceiver and LIN protocol handler. The specification supports LIN 2.1 standard. The IC also contains an application specific message decoder. It decodes messages from the LIN-master and provides commands for configuration, control, and diagnosis of the LIN LED Driver IC via the LIN-interface.

## 6.1 LIN-Basics

The LIN-bus (Local Interconnect Network) is a one-wire bus system. The data is transmitted via a single data line between one LIN-master and multiple LIN-slave devices (up to 16). All LIN-slaves are connected in parallel to the LIN-bus, which reduces the wiring effort to a minimum. The LIN-bus uses the supply voltage as reference voltage.

The LIN-master initiates every communication. Therefore, the master sends out a header with a defined message content. According to this header the addressed slave-devices perform the requested action or provide their information on the bus (via putting the LIN-bus to recessive state (high potential, close to the supply voltage) or dominant state (low potential)). The default state of the LIN-bus is high potential.

The LIN-messages are called LIN-frames. LIN-frames, which requests only an action (e.g. switch on a channel) at the slave devices, are called master published frame-IDs. LIN-frames, which request an answer of the slave device, start with the slave frame-ID and are called slave published frame-IDs.

## 6.2 Physical Layer

The integrated LIN-transceiver is the physical layer interface between the protocol handler and the physical bus. It is especially suited to drive the bus line in LIN-systems in automotive and industrial applications. The device acts as a LIN-slave on the network. The logical values stored in the registers of the protocol handler are driven to the physical LIN-bus when data is requested from the LIN-master. Physical LIN-bus information from the master is transferred into the registers of the protocol handler for command and control of the LIN LED Driver IC. The transceiver offers excellent EMC performance within a broad frequency range independent of battery voltage. This is achieved by implementing a slope control mechanism based on a constant slew rate.

## 6.2.1 LIN-Specifications 2.1

The TLD7396EK IC fulfills the Physical Layer Specification LIN 2.1.

## 6.2.2 Wake-Up via LIN-bus

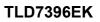

The LIN-bus Wake-Up event, often called remote Wake-Up, changes the operation mode from sleep mode to normal operation mode. A falling edge on the LIN-bus, followed by a dominant bus signal t >  $t_{WK(LIN)}$  (Pos. 6.3.20) results in a bus Wake-Up event.

The mode change to normal operation mode becomes active with the following rising edge on the LIN-bus (see also **Figure 5**). This rising edge starts the Power-On Reset. After the time  $t_{\text{START}(\text{LIN})}$  (**Pos. 6.3.21**) the Power-On Reset is completed and the device is able to receive LIN messages.

## TLD7396EK

#### LIN-Interface

Figure 5 LIN Wake-Up behavior

## 6.2.3 LIN Operation During Low V<sub>S</sub> Voltage

If the supply voltage at the Vs pin drops below the extended operating voltage range  $V_{\text{S(ext)min}}$  (Pos. 4.2.15), the integrated LIN-transceiver terminates communication. This feature is implemented to avoid any permanent dominant or erroneous signals on the LIN-bus. When the supply voltage rises above the detection threshold  $V_{\text{LIN(wk)}}$  (Pos. 6.3.7), communication is re-enabled. The LIN-bus termination remains active during under voltage operation. When the supply voltage is removed, the LIN-bus output is switched to high impedance in order to not disrupt bus communication.

## 6.2.4 LIN-bus Driver Over Temperature Protection

The LIN-bus driver within the transceiver has an integrated over temperature sensor to protect the driver from thermal overstress. If the integrated LIN driver temperature reaches a critical temperature  $T_{\text{LIN}(\text{OT})}$  (Pos. 6.3.25) the LIN-bus driver will be deactivated and the transceiver will be switched to receive only mode. If the chip has cooled down more than the temperature hysteresis  $\Delta T_{\text{LIN}(\text{OT})}$  (Pos. 6.3.26) below  $T_{\text{LIN}(\text{OT})}$  the LIN-bus driver will be activated again. To avoid a bit failure after cooling down, the bus driver remains off till the next dominant to recessive transmission initiated by the LIN LED Driver IC state machine.

The failure is not indicated in the LIN diagnostic response.

## 6.2.5 LIN message Idle Time

If the LIN-bus is recessive for more than  $t_{\text{LIN(idle)}}$  (Pos. 6.3.23) between two LIN messages, the device will change from normal operation mode to sleep mode.

## 6.2.6 Oscillator Tolerance

The LIN LED Driver IC uses the sync field to synchronize its internal clock for LIN communication. According to the LIN calculation table, an oscillator clock tolerance < 2% with respect to the master sync signal is maintained within one LIN frame.

## 6.3 Electrical Characteristics LIN-transceiver

#### **Electrical Characteristics: LIN-transceiver**

$V_{\rm S}$  = 7 V to 18 V,  $T_{\rm j}$  = -40 °C to 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                    | Symbol                            | Limit Values             |                         |                          | Unit | Conditions                                                              |

|--------|--------------------------------------------------------------|-----------------------------------|--------------------------|-------------------------|--------------------------|------|-------------------------------------------------------------------------|

|        |                                                              |                                   | Min.                     | Тур.                    | Max.                     |      |                                                                         |

| LIN-bu | s Receiver                                                   |                                   |                          | 1                       | _                        |      |                                                                         |

| 6.3.1  | Receiver threshold voltage,                                  | $V_{\rm LINth(R,do}$              | 0.4 ×                    | $0.45 \times$           |                          | V    | -                                                                       |

|        | recessive to dominant edge                                   | m)                                | Vs                       | $V_{S}$                 |                          |      |                                                                         |

| 6.3.2  | Receiver dominant state                                      | V <sub>LIN(R,dom)</sub>           | -                        | -                       | $0.4 \times V_{\rm S}$   | V    | LIN Spec 2.1 (Par.<br>17)                                               |

| 5.3.3  | Receiver threshold voltage, dominant to recessive edge       | $V_{\text{LINth}(R, \text{rec}})$ |                          | $0.55 \times V_{\rm S}$ | $0.6 \times V_{S}$       | V    | -                                                                       |

| 6.3.4  | Receiver recessive state                                     | V <sub>LIN(R,rec)</sub>           | $0.6 \times V_{S}$       | -                       | 1.15 x<br>V <sub>S</sub> | V    | <sup>1)</sup> LIN Spec 2.1<br>(Par. 18)                                 |

| 6.3.5  | Receiver center voltage                                      | $V_{\rm LIN(R,CNT)}$              | 0.475×<br>V <sub>S</sub> | -                       | 0.525×<br>V <sub>S</sub> | V    | <sup>2)</sup> LIN Spec 2.1<br>(Par. 19)                                 |

| 6.3.6  | Receiver hysteresis                                          | $\Delta V_{\rm LIN(R)}$           | $0.07 \times V_{\rm S}$  | 0.12                    | $0.175 \times V_{\rm S}$ | V    | <sup>3)</sup> LIN Spec 2.1<br>(Par. 20)                                 |

| 6.3.7  | Wake-up threshold voltage                                    | $V_{LIN(wk)}$                     | $0.4 \times V_{S}$       | $0.5 \times V_{S}$      | $0.6 \times V_{\rm S}$   | V    | -                                                                       |

| LIN-bu | s Transmitter                                                | 1                                 | l                        | 1                       | -1                       |      |                                                                         |

| 6.3.8  | Bus short circuit current                                    | I <sub>LIN(LIM)</sub>             | 40                       | 100                     | 150                      | mA   | V <sub>LIN</sub> = 13.5 V<br>LIN Spec 2.1 (Par.<br>12)                  |

| 6.3.9  | Leakage current during loss of GND                           | I <sub>LIN(no GND)</sub>          | -1000                    | -                       | 5                        | μA   | $V_{\rm S} = 0 V$<br>$V_{\rm LIN} = -12 V$<br>LIN Spec 2.1 (Par.<br>15) |

| 6.3.10 | Leakage current during loss of Vs                            | I <sub>LIN(no Vs)</sub>           | -                        | -                       | 5                        | μA   | $V_{\rm S} = 0 V$<br>$V_{\rm LIN} = 18 V$<br>LIN Spec 2.1 (Par.<br>16)  |

| 6.3.11 | Leakage current during LIN transmitter off and bus dominant  | I <sub>LIN(PAS</sub><br>dom)      | -1                       | -                       | -                        | mA   | $V_{\rm S}$ = 18 V<br>$V_{\rm LIN}$ = 0 V<br>LIN Spec 2.1 (Par.<br>13)  |

| 6.3.12 | Leakage current during LIN transmitter off and bus recessive | I <sub>LIN(PAS</sub><br>rec)      | -                        | -                       | 20                       | μA   | $V_{\rm S}$ = 8 V<br>$V_{\rm LIN}$ = 18 V<br>LIN Spec 2.1 (Par<br>14)   |

| 6.3.13 | Bus pull-up resistance                                       | R <sub>slave</sub>                | 20                       | 30                      | 47                       | kΩ   | Normal Mode<br>LIN Spec 2.1 (Par.<br>26)                                |

#### Electrical Characteristics: LIN-transceiver (cont'd)

$V_{\rm S}$  = 7 V to 18 V,  $T_{\rm j}$  = -40 °C to 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                           | Symbol               | L     | .imit Val | ues    | Unit | Conditions                                                                                                                                                                                                                            |

|--------|-------------------------------------|----------------------|-------|-----------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                     |                      | Min.  | Тур.      | Max.   |      |                                                                                                                                                                                                                                       |

| 6.3.14 | Propagation delay<br>LIN-bus to RxD |                      |       |           | 0      |      | <sup>4)</sup> LIN Spec 2.1<br>(Par. 31)<br>R <sub>RxD</sub> = 2.4 kΩ                                                                                                                                                                  |

|        | Dominant to RxD Low                 | $t_{rx(pdf)}$        | -     | 1         | 6<br>6 | μS   | $C_{\text{RxD}} = 20 \text{ pF}$                                                                                                                                                                                                      |

| 0.0.45 | Recessive to RxD High               | t <sub>rx(pdr)</sub> | -     | 1         |        | μS   |                                                                                                                                                                                                                                       |

| 6.3.15 | Receiver delay symmetry             | t <sub>rx(sym)</sub> | -2    | -         | 2      | μS   | <sup>4)</sup> LIN Spec 2.1<br>(Par. 32)<br>$t_{rx(sym)} = t_{rx(pdf)} - t_{rx(pdr)}$<br>$R_{RxD} = 2.4 \text{ k}\Omega$<br>$C_{RxD} = 20 \text{ pF}$                                                                                  |

| 6.3.16 | Duty cycle D1                       | D <sub>1</sub>       | 0.396 | _         | -      |      | <sup>5)</sup> duty cycle 1<br>$TH_{Rec}(max) = 0.744$<br>$\times V_S$<br>$TH_{Dom}(max) = 0.581$<br>$\times V_S$<br>$V_S = 7.018 V$<br>$t_{bit} = 50 \ \mu S$<br>$D_1 = t_{LIN\_rec(min)}/(2$<br>$t_{bit})$<br>LIN Spec 2.1 (Par. 27) |

| 6.3.17 | Duty cycle D2                       | D <sub>2</sub>       | -     | -         | 0.581  |      | <sup>5)</sup> duty cycle 2<br>$TH_{Rec}(min)= 0.422$<br>$\times V_S$<br>$TH_{Dom}(min)= 0.284$<br>$\times V_S$<br>$V_S = 7.618 V$<br>$t_{bit} = 50 \mu S$<br>$D_2 = t_{LIN_{rec}(max)}/(2$<br>$t_{bit})$<br>LIN Spec 2.1 (Par. 28)    |

| 6.3.18 | Duty cycle D3                       | D <sub>3</sub>       | 0.417 | -         | -      |      | <sup>5)</sup> duty cycle 3<br>$TH_{Rec}(max) = 0.778$<br>$\times V_S$<br>$TH_{Dom}(max) = 0.616$<br>$\times V_S$<br>$V_S = 7.018 V$<br>$t_{bit} = 96 \mu S$<br>$D_3 = t_{LIN\_rec(min)}/(2$<br>$t_{bit})$<br>LIN Spec 2.1 (Par. 29)   |

#### Electrical Characteristics: LIN-transceiver (cont'd)

$V_{\rm S}$  = 7 V to 18 V,  $T_{\rm j}$  = -40 °C to 150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                  | Symbol                      | L     | imit Val | ues   | Unit   | Conditions                                                                                                                                                                                                                          |

|--------|--------------------------------------------|-----------------------------|-------|----------|-------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                            |                             | Min.  | Тур.     | Max.  |        |                                                                                                                                                                                                                                     |

| 6.3.19 | Duty cycle D4                              | <i>D</i> <sub>4</sub>       | -     | -        | 0.590 |        | <sup>5)</sup> duty cycle 4<br>$TH_{Rec}(min) = 0.389$<br>$\times V_S$<br>$TH_{Dom}(min) = 0.251$<br>$\times V_S$<br>$V_S = 7.6 18 V$<br>$t_{bit} = 96\mu S$<br>$D_4 = t_{LIN\_rec(max)}/(2$<br>$t_{bit})$<br>LIN Spec 2.1 (Par. 30) |

| 6.3.20 | Dominant time for LIN-bus Wake-<br>Up      | t <sub>WK(LIN)</sub>        | 30    | -        | 150   | μS     | _                                                                                                                                                                                                                                   |

| 6.3.21 | LIN start-up time                          | t <sub>START(LIN)</sub>     | -     | -        | 5     | ms     | <sup>4)</sup> time from $V_{\text{LIN}} > V_{\text{LIN(wk)}}$ until LIN<br>message can be<br>received, see<br><b>Figure 5</b>                                                                                                       |

| 6.3.22 | Internal BUS dominant time out             | t <sub>timeout</sub>        | 6     | 9        | 12    | ms     | -                                                                                                                                                                                                                                   |

| 6.3.23 | LIN communication time out                 | t <sub>LIN(idle)</sub>      | 4     | 8        | 10    | S      | -                                                                                                                                                                                                                                   |

| 6.3.24 | LIN flash mode speed                       | f <sub>FLASH</sub>          | 112.7 | 115      | 117.3 | kbit/s | <sup>4)</sup> –                                                                                                                                                                                                                     |

| 6.3.25 | LIN over temperature protection            | $T_{\text{LIN(OT)}}$        | 150   | -        | -     | °C     | <sup>4)</sup> _                                                                                                                                                                                                                     |

| 6.3.26 | LIN over temperature protection hysteresis | $\Delta T_{\text{LIN(OT)}}$ | -     | 15       | -     | °C     | 4)                                                                                                                                                                                                                                  |

| 6.3.27 | LIN clock tolerance                        | k <sub>lin(CLK)</sub>       | 0.98  | -        | 1.02  | -      | $\frac{f_{\text{LIN(CLK)}} = k_{\text{LIN(CLK)}} *}{f_{\text{MSTR-Sync}}}$                                                                                                                                                          |

1) Maximum limit not subject to production test, specified by design

2)  $V_{\text{LIN}(R,\text{CNT})} = (V_{\text{LINth}(R,\text{dom})} + V_{\text{LINth}(R,\text{rec})})/2$ ; see LIN spec. for variable definition

3)  $\Delta V_{\text{LIN}(\text{R})} = V_{\text{LIN}(\text{R,rec})} - V_{\text{LIN}(\text{R,dom})}$

4) Not subject to production test, specified by design

5) Bus load concerning LIN Spec 2.1: Load 1 = 1 nF / 1 k $\Omega$  =  $C_{\text{LIN}}$  /  $R_{\text{LIN}}$ Load 2 = 6.8 nF / 660  $\Omega$  =  $C_{\text{LIN}}$  /  $R_{\text{LIN}}$

Load 3 = 10 nF / 500  $\Omega$  =  $C_{\rm LIN}$  /  $R_{\rm LIN}$

## 6.4 Protocol Handler (Data Link Layer)

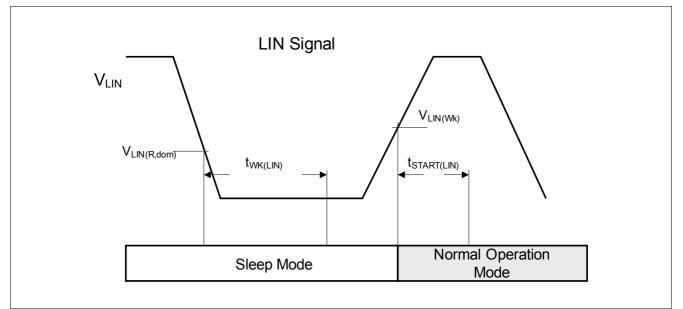

Every data transfer is initiated from the master by sending a header. This header contains a sync-break field, a sync byte and a protected identifier byte (PID). The PID contains the frame identifier (frame-ID) and the parity. The frame-ID defines the response, which is sent by the master or the slave immediately after the header. The response contains 1 to 8 data bytes and one checksum byte (end of frame). The producer of any information is called "Publisher" and the consumer of this information is called "Subscriber".

Except the sync-break field, LIN frames are byte oriented and the LIN specification allows a delay between bytes (interbyte delay). Every byte has a start bit, 8 data bits and one stop bit. The bits are encoded with value 0 (dominant) or 1 (recessive). The LSB is the first bit and the MSB the last bit in a bit stream of a data byte.

Figure 6 shows a complete LIN frame for an identifier using 4 data bytes in the response field. The sync-break reinitializes the receiver and marks in any case the start of a frame.

Figure 6 LIN Frame

The value of the checksum byte is calculated following the LIN 2.1 standard (enhanced checksum). The checksum contains the inverted eight bit sum with carry over all data bytes and the protected identifier. The frame-ID 0x3C (go to sleep command) uses the classic checksum, which contains the inverted eight bit sum with carry over all data bytes (but not the protected identifier). This is in line with LIN 2.1 that requests classic checksum for the diagnostic frames for downward compatibility and with J2602, which specifies enhanced checksum.

## 6.4.1 LIN Communication Error Detection

The LIN LED Driver IC has an integrated monitoring functions to detect errors in the LIN communication between the master and the slaves. These errors include:

- Data Error

- Checksum Error

- Byte Field Framing Error

- ID Parity Error

If the LIN-bus is recessive for more than  $t_{\text{timeout}}$  during the transmission of a LIN message the receiver is reinitialized. That means, the synchronization delimiter or any interbyte space must not exceed  $t_{\text{timeout}}$  otherwise the frame is lost.

The status on the LIN-bus can be read out using the register LEDLINStatus of the LIN frame LED\_L1\_P00. If there are errors in the LIN communication the LIN driver stage remains active.

## 6.5 LIN Message Decoder (Application Layer)

The LIN LED Driver IC understands seven communication frames (messages). Five frames are for master-toslave data transfer (i.e. TLD7304EK is the subscriber) and two frames are for slave-to-master data transfer (i.e. LIN LED Driver IC is the publisher). **Table 3** gives an overview over the used message frames.

Note: The frame identifiers for master-to-slave and slave-to-master data transfers are not supposed to overlap!

| Frame Symbol | frame-ID                        | LIN LED<br>Driver IC is | Checksum | Description                                                                                                                                                                                                                |

|--------------|---------------------------------|-------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSTR_L1_P00  | frame_ID_mstr<br>e.g. 0x00      | Subscriber              | enhanced | Master sends color, intensity and intensity<br>ramp setting to slave. This is the standard<br>command used in the application                                                                                              |

| MSTR_L1_P01  | frame_ID_mstr + 1<br>e.g. 0x01  | Subscriber              | enhanced | Master sends direct intensity information per<br>output (Out1, 2, 3) to slave. This command<br>can be used for LED calibration or direct<br>output control independent of the sets of<br>output currents stored in the NVM |

| MSTR_L1_P02  | frame_ID_mstr + 2<br>e.g. 0x02  | Subscriber              | enhanced | Master erases or writes data into NVM of slave. This command should not be used once the LIN LED Driver IC is connected to an application LIN network.                                                                     |

| MSTR_L1_P03  | frame_ID_mstr + 3<br>e.g. 0x03  | Subscriber              | enhanced | Master sends dim-time setting to slave. This<br>is an optional command that can be used in<br>the application in case alternative dim-times<br>are required                                                                |

| MSTR_L1_P04  | 0x3C                            | Subscriber              | classic  | Master Request frame                                                                                                                                                                                                       |

| LED_L1_P00   | frame_ID_slave<br>e.g. 0x0D     | Publisher               | enhanced | LIN LED Driver IC sends diagnostic<br>information back to master. This command is<br>used for network diagnostic, e.g. a roll-call at<br>system start-up                                                                   |

| LED_L1_P01   | frame_ID_slave + 1<br>e.g. 0x0E | Publisher               | enhanced | LIN LED Driver IC sends content of NVM<br>back to master. This command can be used<br>to verify successful NVM                                                                                                             |

| LED_L1_P02   | 0x3D                            | Publisher               | classic  | Slave Response frame                                                                                                                                                                                                       |

#### Table 3 Frame Overview

## 6.5.1 Frame Identifiers

The LIN LED Driver IC is intended to be used multiple times as a slave in the same LIN network. To differentiate different slaves (different LIN LED-devices), it is necessary to assign specific frame-IDs to the slave published frames.

## 6.5.2 Slave Published Frame-IDs

The frame-IDs for the two slave published frames are defined by the 6-bit register frame\_ID\_slave in the non-volatile memory. The frame\_ID\_slave has to be programmed into the device prior to being connected to the physical LIN network. The first frame-ID for the message LED\_L1\_P00 is the content of this register. The frame-

ID for the message LED\_L1\_P01 is set to frame\_ID\_slave + 1. The NVM register is set to the default value of 0x34. In order to detect not properly programmed devices, the user may leave the Frame ID 0x34 unassigned in his network configuration.

Frame\_ID\_slave values between 0x00 and 0x38 can be used unrestricted (except the master published frame-IDs). The LIN 2.1 spec reserves the frame-IDs 0x3E - 0x3F for diagnostic purposes. Therefore, frame\_ID\_slave values higher than 0x3A, which should be programmed to the NVM, are not stored in the NVM. The protocol handler uses in such cases the default value of 0x34 to avoid a conflict with the reserved frame-IDs. This is also shown in Table 4.

Note: In the NVM programming mode the LIN LED device answers with 1 stop-bit on slave frame-IDs.

| Frame ID for LED_L1_P01<br>(generated by LIN LED Driver IC) |

|-------------------------------------------------------------|

| 0x01                                                        |

| 0x05                                                        |

| 0x09                                                        |

| 0x0D                                                        |

| 0x11                                                        |

| 0x15                                                        |

| 0x19                                                        |

| 0x1D                                                        |

| 0x21                                                        |

| 0x25                                                        |

| 0x29                                                        |

| 0x2D                                                        |

| 0x31                                                        |

| 0x35 (default)                                              |

|                                                             |

Table 4

Slave Published Frame ID Examples

## 6.5.3 Master Published Frame-IDs

To increase the flexibility of the LIN LED Driver IC, the frame IDs for the four master published frames MSTR\_L1\_P00 - P03 are also configurable using the same scheme. The frame-ID for MSTR\_L1\_P00 is the content of the NVM register frame\_ID\_mstr, which has to be programmed into the device prior to being connected to the physical LIN network. The default frame-IDs are 0x00 - 0x03, the other frame-ID options are shown in **Table 5**. Values of frame-ID\_mstr, which lead to assignment of reserved frame-IDs (e.g. values higher than 0x38), are ignored and the default value is used.

The go to sleep command MSTR\_L1\_P04 has a fixed frame-ID of 0x3C, (data byte 0 has to contain value 0x00). In order to avoid bus conflicts, the user has to program frame\_ID\_slave and frame\_ID\_mstr to values, which do not overlap.

Note: In the NVM programming mode master published frame-IDs have to use 2 or more stop-bits.

| Frame ID for    | Frame ID for   | Frame ID for   | Frame ID for   | Frame ID for    |

|-----------------|----------------|----------------|----------------|-----------------|

| MSTR_L1_P00     | MSTR_L1_P01    | MSTR_L1_P02    | MSTR_L1_P03    | MSTR_L1_P04     |

| (= NVM register |                |                |                |                 |

| frame_ID_mstr)  |                |                |                |                 |

| 0x00 (default)  | 0x01 (default) | 0x02 (default) | 0x03 (default) | 0x3C (fixed ID) |

| 0x01            | 0x02           | 0x03           | 0x04           |                 |

| 0x02            | 0x03           | 0x04           | 0x05           |                 |

|                 |                |                |                |                 |

| 0x37            | 0x38           | 0x39           | 0x3A           |                 |

| 0x38            | 0x39           | 0x3A           | 0x3B           | _               |

#### Table 5Master Published Frame-IDs

## 6.5.4 Location Identifier

In addition to the frame-IDs discussed in the previous sections, LIN LED Driver IC offers an additional ID to increase the flexibility of usage. This ID is called location ID. It allows to build up groups of devices, which can be dressed by a single command. Therefore, multiple LIN LED devices can be programmed at the same time. This allows a reduced communication effort on the LIN-bus and does not cause any unwanted switch on delays of devices caused by sequential LIN-messages.

The location ID has to be programmed into the device prior to being connected to the physical LIN network. The location ID is 8 bit long and is subdivided into a 4 bit zone information and a 4 bit location information. This is shown in detail in **Table 6**. For instance, the slave with the location ID 0x73 can be addressed by a master-frame with the location IDs 0x73, 0x70, 0x40 and 0x00. The default location ID is set to 0xFF. In order to detect not properly programmed devices, the user shall leave the location ID 0xFF unassigned in his network configuration. A 0xFF location ID in the NVM generates a "not configured" error in the diagnostic frame (see **Chapter 6.6.6**)

| Broadcast "All" | Super-Zone | Zone | Location IDs                   |

|-----------------|------------|------|--------------------------------|

| 0x00            | -          | 0x10 | 0x11, 0x12, 0x1F               |

|                 | -          | 0x20 | 0x21, 0x22, 0x2F               |

|                 | -          | 0x30 | 0x31, 0x32, 0x3F               |

|                 | 0x40       | 0x50 | 0x51, 0x52, 0x5F               |

|                 |            | 0x60 | 0x61, 0x62, 0x6F               |

|                 |            | 0x70 | 0x71, 0x72, 0x7F               |

|                 |            | 0x80 | 0x81, 0x82, 0x8F               |

|                 | -          | 0x90 | 0x91, 0x92, 0x9F               |

|                 | -          | 0xA0 | 0xA1, 0xA2, 0xAF               |

|                 | -          | 0xB0 | 0xB1, 0xB2, 0xBF               |

|                 | -          | 0xC0 | 0xC1, 0xC2, 0xCF               |

|                 | -          | 0xD0 | 0xD1, 0xD2, 0xDF               |

|                 | -          | 0xE0 | 0xE1, 0xE2, 0xEF               |

|                 | -          | 0xF0 | 0xF1, 0xF2, 0xFF <sup>1)</sup> |

#### Table 6 Location Identifier

The Location ID 0xFF shall not be used in the application. A Location ID of 0xFF generates an ApInfo3 error (slave not configured)

## 6.6 Message Frame Decoding

## 6.6.1 MSTR\_L1\_P00 Message Frame (Set color and intensity)

This is the standard command used in the application to set and change colors (from the predefined color points in the NVM) and intensities of the LIN LED Driver IC slaves in the network. This frame uses enhanced checksum.

#### Table 7 Frame MSTR\_L1\_P00

| Frame Symbol                          |   |   |    |       |      |    |   |   |                   |              | MS | ſR_   | L1_  | P00 | )                        |                                        |                  |   |                   |                   |                                |   |   |   |

|---------------------------------------|---|---|----|-------|------|----|---|---|-------------------|--------------|----|-------|------|-----|--------------------------|----------------------------------------|------------------|---|-------------------|-------------------|--------------------------------|---|---|---|

| Data field within frame               |   |   | da | ata I | byte | 1  |   |   |                   |              | da | ata I | byte | 2   |                          |                                        |                  |   | da                | ata I             | oyte                           | 3 |   |   |

| Data bit within field                 | 7 | 6 | 5  | 4     | 3    | 2  | 1 | 0 | 7                 | 6            | 5  | 4     | 3    | 2   | 1                        | 0                                      | 7                | 6 | 5                 | 4                 | 3                              | 2 | 1 | 0 |

| Information field<br>symbol (signal)  |   |   | Lc | ocati | ion_ | ID |   |   | Color_Trans_Time0 | Update_Color |    | Cc    | olor |     | Color_Transistion_Enable | Intensity_Dimming_Enable <sup>1)</sup> | Update_Intensity |   | Color_Trans_Time2 | Color_Trans_Time1 | Global_Intensity <sup>2)</sup> |   |   |   |

| Bit within information field (signal) | 7 | 6 | 5  | 4     | 3    | 2  | 1 | 0 | 0                 | 0            | 3  | 2     | 1    | 0   | 0                        | 0                                      | 1                | 0 | 2                 | 1                 | 3                              | 2 | 1 | 0 |

1) Must not be changed during activated outputs or intensities > 0.

2) A changing of the intensity during an active dimming process leads to different dimming times than programmed.

| Symbol (signal)              | Bits | Value | Description                                                                                                               |

|------------------------------|------|-------|---------------------------------------------------------------------------------------------------------------------------|

| Global_Intensity             | 3:0  | 0:0xF | Global output intensity setting between 0 (OFF) and 0xF (100%), see <b>Chapter 7.1.1</b> for details. Default value is 0. |

| Color_Trans_Time1            | 4    | 0:1   | Color transitioning time bit 1                                                                                            |

| Color_Trans_Time2            | 5    | 0:1   | Color transitioning time bit 2 (MSB)                                                                                      |

| Update_Intensity             | 7:6  | 0     | Update intensity to new value transmitted in this frame.                                                                  |

|                              |      | 1     | Store intensity value transmitted in this frame, but the intensity at the outputs it not changed.                         |

|                              |      | 2     | Update intensity to stored value, ignore intensity data transmitted in this frame.                                        |

|                              |      | 3     | Ignore intensity data transmitted in this frame, the intensity at the outputs it not changed.                             |

| Intensity_Dimming_<br>Enable | 0    | 0     | After frame transmission LIN LED Driver IC switches to new intensity without dimming.                                     |

|                              |      | 1     | After frame transmission LIN LED Driver IC ramps to new intensity within dim-up/dim-down time.                            |

#### Table 8 Information Fields of Frame MSTR\_L1\_P00

## TLD7396EK

#### LIN-Interface

| Symbol (signal)             | Bits | Value  | Description                                                                                                                                             |

|-----------------------------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Color_Transition_<br>Enable | 1    | 0      | After frame transmission LIN LED Driver IC switches to new color without smooth transitioning.                                                          |

|                             |      | 1      | After frame transmission LIN LED Driver IC changes to new color within selected color transition time.                                                  |

| Color                       | 5:2  | 0:0xF  | Set of output intensities as defined in the NVM. If a value of $0xY$ is written into the frame, the color point with the NVM address $0x(Y+1)$ is used. |

| Update_Color                | 6    | 0      | Ignore defined color data in Color-Bits, do not change color.                                                                                           |

|                             |      | 1      | Update color (set of intensities) to new set of output intensities according to data transmitted in this frame.                                         |

| Color_Trans_Time0           | 7    | 0:1    | Color transitioning time bit 0 (LSB)                                                                                                                    |

| Location _ID                | 7:0  | 0:0xFF | Location_ID defines which individual slave or zone of slaves is addressed with this command, according to <b>Table 6</b> .                              |

### Table 8 Information Fields of Frame MSTR\_L1\_P00

## 6.6.2 MSTR\_L1\_P01 Message Frame (LED calibration, direct intensity access)

This command allows to set the absolute intensities of the three output channels without using the sets of output currents stored in the NVM. This frame uses enhanced checksum. It can be used for two different applications:

- After assembly on a LIN LED slave PCB, the LIN LED driver IC needs to be calibrated according to the brightness and wavelength characteristics of the individual LED. During this calibration process an individual set of output intensities is required. This individual set of output intensities can be applied by using the MSTR\_L1\_P01 message frame.

- For setting individual colors or intensities (independent of the 16 calibrated sets of output intensities in the NVM) the MSTR\_L1\_P01 message frame can be used as well.

After successful transmission of this frame, the output intensities are changed according to the transmitted data. The change (parameters for color transitioning) is done according to the settings of the MSTR\_L1\_P00 message frame. This means that any previously programmed color setting by MSTR\_L1\_P00 frame transmission is overwritten. This new set of output intensities remains valid until either a new MSTR\_L1\_P01 frame is transmitted, or a new MSTR\_L1\_P00 frame with Update\_Color = 1 is transmitted.

Note: For an output activation by the MSTR\_L1\_P01 message frame without using the calibrated NVM intensity sets the global intensity setting in the MSTR\_L1\_P00 message frame needs to be set after the MSTR\_L1\_P01 message frame. The update color bit must be 0.

## Table 9 Frame MSTR\_L1\_P01

| Frame Symbol                          |   |   |   |        |      |   | MS | TR_ | L1_F | P01  |       |        |      |     |     |   |

|---------------------------------------|---|---|---|--------|------|---|----|-----|------|------|-------|--------|------|-----|-----|---|

| Data field within frame               |   |   | C | lata I | oyte | 1 |    |     |      |      | C     | lata I | byte | 2   |     |   |

| Data bit within field                 | 7 | 6 | 5 | 4      | 3    | 2 | 1  | 0   | 7    | 6    | 5     | 4      | 3    | 2   | 1   | 0 |

| Information field symbol (signal)     |   | 1 | L | ocati  | on_l | D | 1  |     |      | Inte | nsity | _Ou    | t1_C | omm | and |   |

| Bit within information field (signal) | 7 | 6 | 5 | 4      | 3    | 2 | 1  | 0   | 7    | 6    | 5     | 4      | 3    | 2   | 1   | 0 |

|   |      |       |        |      |     | MS  | TR_ | L1_F | <b>P</b> 01 |       |       |      |     |     |   |

|---|------|-------|--------|------|-----|-----|-----|------|-------------|-------|-------|------|-----|-----|---|

|   |      | d     | lata I | oyte | 3   |     |     |      |             | d     | ata I | oyte | 4   |     |   |

| 7 | 6    | 5     | 4      | 3    | 2   | 1   | 0   | 7    | 6           | 5     | 4     | 3    | 2   | 1   | 0 |

|   | Inte | nsity | _Out   | 2_C  | omm | and |     |      | Inte        | nsity | _Out  | :3_C | omm | and |   |

| 7 | 6    | 5     | 4      | 3    | 2   | 1   | 0   | 7    | 6           | 5     | 4     | 3    | 2   | 1   | 0 |

#### Table 10 Information Fields of Frame MSTR\_L1\_P01

| Symbol                     | Bits | Value  | Description                                                                                                                |

|----------------------------|------|--------|----------------------------------------------------------------------------------------------------------------------------|

| Intensity_Out3_Co<br>mmand | 7:0  | 0:0xFF | Set output intensity of Out3 to this value.                                                                                |

| Intensity_Out2_Co<br>mmand | 7:0  | 0:0xFF | Set output intensity of Out2 to this value.                                                                                |