## TLE42364G

Low Dropout Linear Voltage Regulator

TLE42364G

## Data Sheet

Rev. 1.0, 2010-02-08

## Automotive Power

## Low Dropout Linear Voltage Regulator

### TLE42364G

#### 1 Overview

#### Features

- Output voltage 5 V

- Output voltage tolerance  $\leq \pm 2\%$

- 100 mA current capability

- Very low current consumption

- Low dropout voltage

- Overtemperature shutdown

- Reverse polarity protection

- Output current limitation

- Wide temperature range

- · Suitable for use in automotive electronics

- Enable

- Green Product (RoHS compliant)

- AEC Qualified

#### **Functional Description**

TLE42364G is a low dropout voltage regulator for 5 V supply in a PG-SOT223-4 SMD package. The IC regulates an input voltage  $V_{\rm I}$  in the range of 5.5 V <  $V_{\rm I}$  < 45 V to  $V_{\rm Q,nom}$  = 5 V. The maximum output current is more than 100 mA. The IC can be switched off via the enable input, which causes the current consumption to drop below 10  $\mu$ A. The IC is protected against shortcircuit and overheat by the incorporated output current limitation and the overtemperature shutdown.

#### **Choosing External Components**

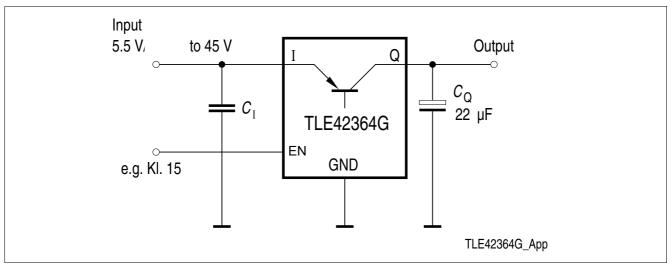

The input capacitor  $C_{l}$  is necessary for compensating line influences. The output capacitor  $C_{Q}$  is necessary for the stability of the regulating circuit. Stability is guaranteed at values  $C_{Q} \ge 10 \ \mu\text{F}$  and an ESR  $\le 10 \ \Omega$  within the whole operating temperature range.

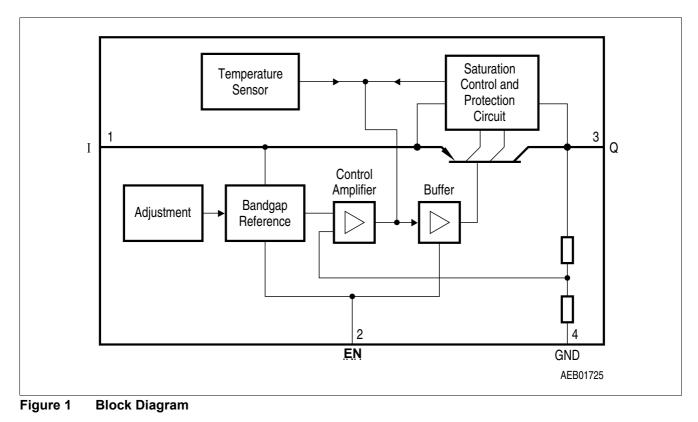

#### **Circuit Description**

The device includes a precise reference voltage, which is very accurate due to resistor adjustment. A control amplifier compares the divided output voltage to this reference voltage and drives the base of the PNP series transistor through a buffer. Saturation control as a function of the load current prevents any oversaturation of the power element.

| Туре      | Package     | Marking |

|-----------|-------------|---------|

| TLE42364G | PG-SOT223-4 | 42364   |

PG-SOT223-4

TLE42364G

**Block Diagram**

## 2 Block Diagram

#### **Pin Configuration**

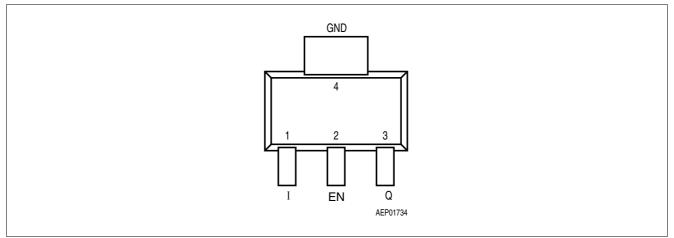

## 3 Pin Configuration

### 3.1 Pin Assignment

Figure 2 Pin Configuration

### 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                        |

|-----|--------|-------------------------------------------------------------------------------------------------|

| 1   | I      | Input voltage; block to ground directly at the IC with a ceramic capacitor.                     |

| 2   | EN     | <b>Enable;</b> connect to $V_{\text{batt}}$ to enable the IC, connect to GND to disable the IC. |

| 3   | Q      | <b>Output voltage;</b> block to ground with a capacitor $C_Q \ge 10 \ \mu\text{F}$ .            |

| 4   | GND    | Ground                                                                                          |

### 4 General Product Characteristics

#### 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings <sup>1)</sup>

$T_j$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter Sy                             | Symbol                  | Lim  | it Values | Unit     | Conditions        |

|----------|------------------------------------------|-------------------------|------|-----------|----------|-------------------|

|          |                                          |                         | Min. | Max.      |          |                   |

| Input, E | Enable                                   |                         |      |           |          | -                 |

| 4.1.1    | Voltage                                  | $V_{\rm I}, V_{\rm EN}$ | -30  | 45        | V        | -                 |

| Output   |                                          |                         |      |           | <b>I</b> |                   |

| 4.1.2    | Voltage                                  | V <sub>Q</sub>          | -1   | 32        | V        | -                 |

| Tempe    | ratures                                  |                         |      |           | <b>I</b> |                   |

| 4.1.3    | Junction Temperature                     | T <sub>i</sub>          | -40  | 150       | °C       | -                 |

| 4.1.4    | Storage Temperature                      | T <sub>stg</sub>        | -50  | 150       | °C       | -                 |

| ESD Su   | usceptibility                            |                         | 4    | 4         |          |                   |

| 4.1.5    | ESD Resistivity to GND                   | $V_{ESD}$               | -4   | 4         | kV       | HBM <sup>2)</sup> |

| 4.1.6    | ESD Resistivity to GND                   | V <sub>ESD</sub>        | -1.5 | 1.5       | kV       | CDM <sup>3)</sup> |

| 1) Not   | subject to production text, aposified by | logian                  |      |           | 1        |                   |

1) Not subject to production test, specified by design.

2) ESD susceptibility, HBM according to EIA/JESD 22-A114B

3) ESD susceptibility, Charged Device Model "CDM" EIA/JESD22-C101 or ESDA STM5.3.1

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 4.2 Functional Range

#### Table 1Functional Range

| Pos.  | Parameter            | Symbol | Limit Values |      | Limit Values Unit |   |

|-------|----------------------|--------|--------------|------|-------------------|---|

|       |                      |        | Min.         | Max. |                   |   |

| 4.2.1 | Input voltage        | $V_1$  | 5.5          | 45   | V                 | - |

| 4.2.2 | Junction temperature | Tj     | -40          | 150  | °C                | - |

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

#### **General Product Characteristics**

#### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                         | Symbol            | Limit Values |      |      | Unit | Conditions                          |

|-------|-----------------------------------|-------------------|--------------|------|------|------|-------------------------------------|

|       |                                   |                   | Min.         | Тур. | Max. |      |                                     |

| 4.3.1 | Junction to Case <sup>1)</sup>    | R <sub>thJC</sub> | -            | 17   | -    | K/W  | measured to heat slug               |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | R <sub>thJA</sub> | -            | 54   | _    | K/W  | 2)                                  |

| 4.3.3 |                                   |                   | _            | 139  | _    | K/W  | footprint only <sup>3)</sup>        |

| 4.3.4 |                                   |                   | -            | 73   | -    | K/W  | 300 mm² heatsink area <sup>3)</sup> |

| 4.3.5 |                                   |                   | -            | 64   | -    | K/W  | 600 mm² heatsink area <sup>3)</sup> |

1) Not subject to production test, specified by design.

Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm<sup>3</sup> board with 2 inner copper layers (2 x 70µm Cu, 2 x 35µm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

3) Specified  $R_{thJA}$  value is according to Jedec JESD 51-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 1 copper layer (1 x 70µm Cu).

#### 5 **Electrical Characteristics**

#### 5.1 **Electrical Characteristics Voltage Regulator**

#### **Electrical Characteristics:**

$V_{\rm I}$  = 13.5 V,  $T_{\rm i}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                | Symbol                   | Limit Values |      |      | Unit | Conditions                                                                                         |  |

|--------|------------------------------------------|--------------------------|--------------|------|------|------|----------------------------------------------------------------------------------------------------|--|

|        |                                          |                          | Min.         | Тур. | Max. |      |                                                                                                    |  |

| 5.1.1  | Output voltage                           | V <sub>Q</sub>           | 4.9          | 5.0  | 5.1  | V    | $5 \text{ mA} \le I_{\text{Q}} \le 100 \text{ mA}$ $6 \text{ V} \le V_{\text{I}} \le 28 \text{ V}$ |  |

| 5.1.2  | Output current limitation                | IQ                       | 120          | 150  | -    | mA   | -                                                                                                  |  |

| 5.1.3  | Current consumption<br>$I_q = I_1 - I_Q$ | Iq                       | -            | -    | 10   | μA   | $V_{\rm EN}$ = 0 V;<br>$T_{\rm j} \leq$ 100 °C                                                     |  |

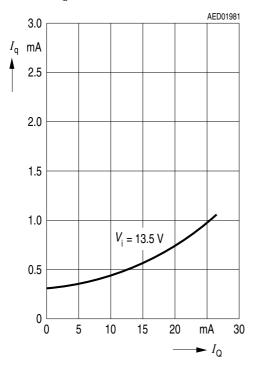

| 5.1.4  | Current consumption<br>$I_q = I_1 - I_Q$ | Iq                       | -            | -    | 400  | μA   | $I_{\rm Q}$ = 1 mA<br>Enable ON                                                                    |  |

| 5.1.5  | Current consumption<br>$I_q = I_1 - I_Q$ | Iq                       | -            | 10   | 15   | mA   | $I_{\rm Q}$ = 100 mA<br>Enable ON                                                                  |  |

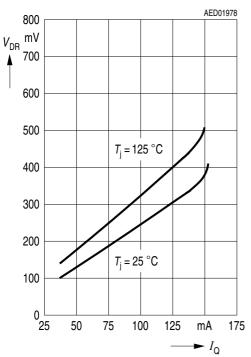

| 5.1.6  | Dropout voltage                          | $V_{\rm dr}$             | -            | 0.25 | 0.5  | V    | $I_{\rm Q}$ = 100 mA <sup>1)</sup>                                                                 |  |

| 5.1.7  | Load regulation                          | $\Delta V_{\rm Q\_load}$ | -            | -    | 40   | mV   | $I_{\rm Q}$ = 5 to 100 mA<br>$V_{\rm I}$ = 6 V                                                     |  |

| 5.1.8  | Line regulation                          | $\Delta V_{\rm Q\_line}$ | -            | 15   | 30   | mV   | $V_1$ = 6 to 28 V<br>$I_Q$ = 5 mA                                                                  |  |

| 5.1.9  | Power Supply ripple rejection            | PSRR                     | -            | 54   | -    | dB   | $f_{\rm r}$ = 100 Hz<br>$V_{\rm r}$ = 0.5 Vpp                                                      |  |

| Enable |                                          | 4                        |              |      |      | ·    |                                                                                                    |  |

| 5.1.10 | Enable on voltage                        | $V_{\rm EN, \ on}$       | 3.5          | -    | -    | V    | -                                                                                                  |  |

| 5.1.11 | Enable off voltage                       | $V_{\rm EN,  off}$       | -            | _    | 0.8  | V    | -                                                                                                  |  |

|        |                                          |                          |              |      |      |      |                                                                                                    |  |

$\begin{array}{|c|c|c|c|c|c|c|c|} \hline - & 0.8 & V & - \\ \hline 15 & 25 & \mu A & V_{\rm EN} = 5 V \\ \hline \end{array}$ 5  $I_{\mathsf{EN}}$ Dropout voltage =  $V_{l}$  -  $V_{Q}$  (measured when the output voltage  $V_{Q}$  has dropped 100 mV from the nominal 1) value obtained at  $V_1 = 13.5$  V).

5.1.12

Enable current

#### TLE42364G

#### **Electrical Characteristics**

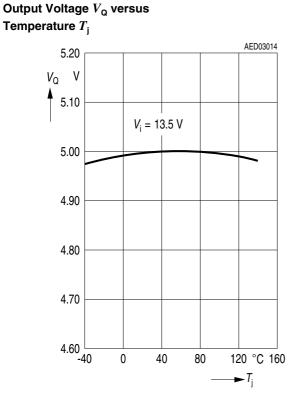

### 5.2 Typical Performance Characteristics Voltage Regulator

## Dropout Voltage $V_{\rm DR}$ versus Output Current $I_{\rm Q}$

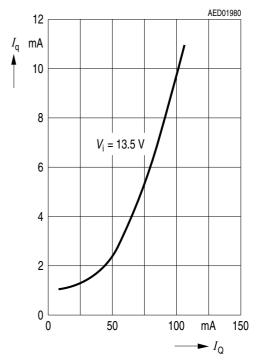

#### Current Consumption $I_q$ versus Output Current $I_Q$

# Current Consumption $I_{\rm q}$ versus Output Current $I_{\rm Q}$

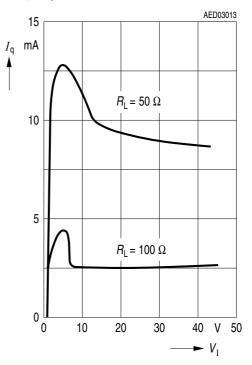

Current Consumption  $I_q$  versus Input Voltage  $V_l$

#### **Electrical Characteristics**

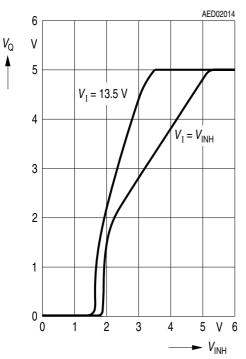

Output Voltage  $V_{\rm q}$  versus Enable Voltage  $V_{\rm EN}$

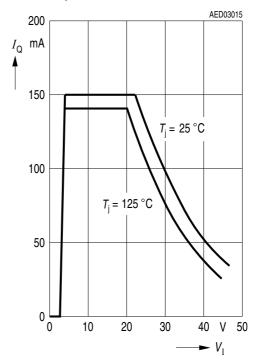

Output Current  $I_q$  versus Input Voltage  $V_1$

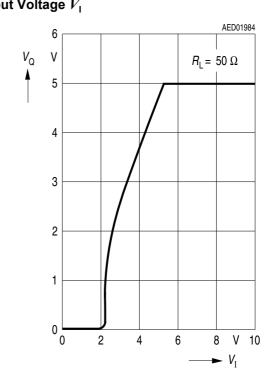

# Output Voltage $V_{\rm q}$ versus Input Voltage $V_{\rm l}$

#### **Application Information**

## 6 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

#### Figure 3 Application Diagram

Note: This is a very simplified example of an application circuit. The function must be verified in the real application.

#### 6.1 Further Application Information

• For further information you may contact http://www.infineon.com/

**Package Outlines**

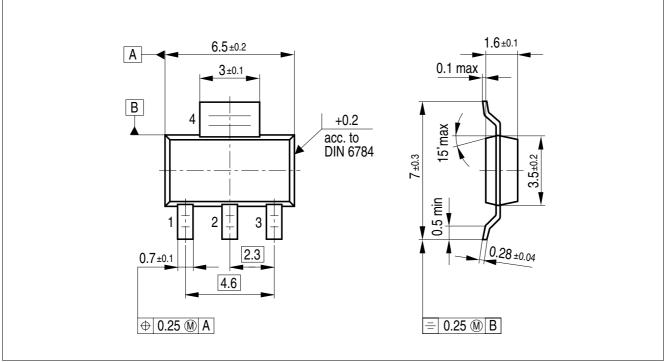

## 7 Package Outlines

Figure 4 PG-SOT223-4 (Plastic Small Outline Transistor)

#### Green Product (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: http://www.infineon.com/packages.

#### **Revision History**

## 8 Revision History

| Revision | Date       | Changes            |

|----------|------------|--------------------|

| 1.0      | 2010-02-08 | Initial data sheet |

Edition 2010-02-08

Published by Infineon Technologies AG 81726 Munich, Germany © 2010 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.