# **TLE 6710** Airbag **Combined Power-Supply** and Firing Circuit Datasheet

Copying of this document, and giving it to others and the use or communication of the contents thereof, are forbidden without express authority. Offenders are liable to the payment of damages. All rights are reserved in the event of the grant of a patent or the registration of a utility model. www.Doto

May 04, 2001

# TLE 6710

## Table of Content:

| A. I               | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| B. (               | Circuit Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3          |

|                    | Supply and Reference:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3          |

|                    | Low Battery Detection on pin UBALT:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3          |

|                    | Oscillator for Boost (30V)-, Buck (5V)-Converter and Watchdog:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3          |

|                    | Boost Converter (CVV):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4          |

|                    | Supply and Reference:<br>Low Battery Detection on pin UBATT:<br>Oscillator for Boost (30V)-, Buck (5V)-Converter and Watchdog:<br>Boost Converter (30V):<br>Buck Converter (5 V):<br>Power On Reset of VCC5:<br>Watchdog Operation and Generation of the Squib Driver Enable Signal ZKEN:<br>ISO 9141 - Serial Interface:<br>Serial Peripheral Interface (SPI) and Decoder Logic:<br>Alarm Warning Lamp Driver (AWL1):<br>Alarm Warning Lamp and Multifunction Driver 2 (AWL2):<br>Voltage-/ Current Sources:<br>Squib Drivers:<br>Squib Resistance Measurement:<br>Squib Leakage Measurement: | 5          |

|                    | Power On Reset of VCC3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4          |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6          |

|                    | Sorial Derinder and Interface (SPI) and Decoder Logic:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9          |

|                    | Serial reinfried a micrae (Sr) and Decoder Logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11         |

|                    | Alarm Warning Lamp and Multifunction Driver 2 (AWL 2):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12         |

|                    | Voltage/ Current Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13         |

|                    | Souib Drivers:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14         |

|                    | Squib Resistance Measurement:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16         |

|                    | Squib Leakage Measurement:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17         |

|                    | Supply Voltage Measurements:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19         |

|                    | Supply Voltage Measurements:<br>Detection of Safing Sensor Closure:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19         |

|                    | Average Chip Temperature Measurement:<br>Grounding Requirements for External Components on PCB:<br>Package Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22         |

|                    | Grounding Requirements for External Components on PCB:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22         |

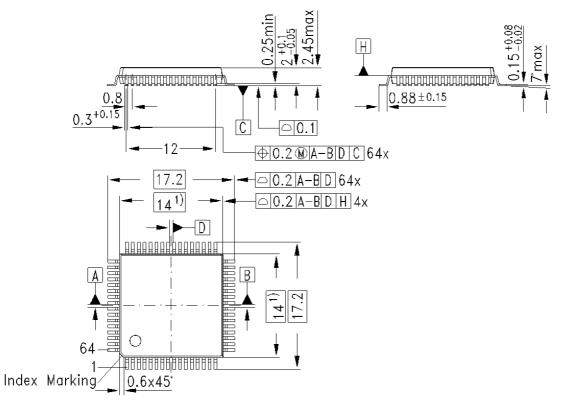

| C.                 | Package Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23         |

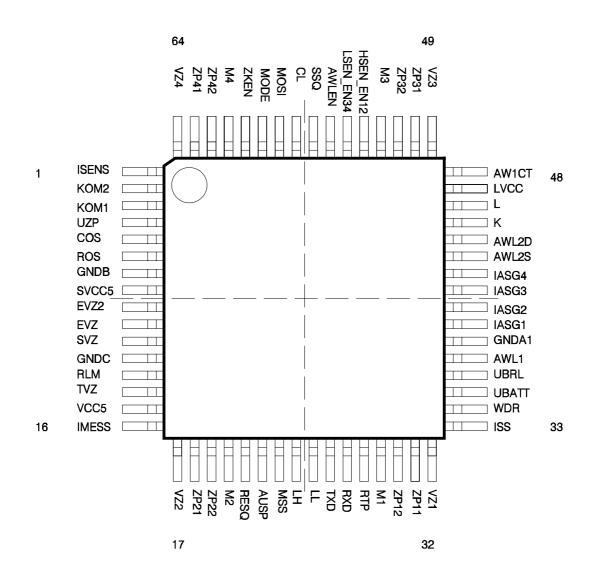

| D.                 | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24         |

| <u>E</u> . <u></u> | Pin Definitions and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 25         |

| F. E               | Block Diagram and Application Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27         |

| G                  | Pin Definitions and Functions<br>Block Diagram and Application Circuit<br>Absolute Maximum Ratings<br>Functional Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28         |

| Η.                 | Functional Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31         |

| I. A               | C/DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32         |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|                    | Logic Inputs and Outputs:<br>Low Battery Detection on pin UBATT (EVZ):<br>Oscillator for Boost (30V)-, Buck (5V)-Converter and Watchdog<br>Boost Converter (30V):<br>Buck Converter (5V):<br>Power On Reset of VCC5 & EVZ and Watchdog:<br>ISO 9141 - Serial Interface:                                                                                                                                                                                                                                                                                                                        | 33         |

|                    | Low Ballery Detection on plin ODAT $\Gamma(EVZ)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34         |

|                    | Baset Converter (30V)-, Buck (3V)-Converter and Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34         |

|                    | Buck Converter (507).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37         |

|                    | Bower On Reset of VCC5 & EVZ and Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30         |

|                    | ISO 9141 - Serial Interface:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40         |

|                    | Alarm Warning Lamp Driver (AWI 1):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41         |

|                    | Alarm Warning Lamp and Multifunction Driver 2 (AWL2):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42         |

|                    | Voltage-/ Current-Sources (V/I):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43         |

|                    | Squib Driver: Highside:A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 44         |

|                    | ISO 9141 - Serial Interface:<br>Alarm Warning Lamp Driver (AWL1):<br>Alarm Warning Lamp and Multifunction Driver 2 (AWL2):<br>Voltage-/ Current-Sources (V/I):<br>Squib Driver: Highside:A)<br>Squib Driver: Lowside:A)<br>Squib Driver: Highside and Lowside:<br>Squib Leakage Measurement:<br>Squib Leakage Measurement:                                                                                                                                                                                                                                                                     | 44         |

|                    | Squib Driver: Highside and Lowside:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45         |

|                    | Squib Resistance Measurement:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46         |

|                    | Squib Leakage Measurement:<br>Internal Dummy Squib Resistance:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49         |

|                    | Internal Dummy Squib Resistance:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50         |

|                    | Supply Voltage measurements:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50         |

|                    | Supply Voltage Measurements:<br>Detection of Safing Sensor Closure:<br>Average Chip Temperature Measurement:<br>Serial Peripheral Interface (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51         |

|                    | Average Chip Temperature Measurement:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52         |

| J. 3               | Serial Peripheral Interface (SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53         |

|                    | J.1: SPI Timing Characteristics:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53         |

|                    | J.2: SPI Commands:<br>J.2.1: General Information on SPI Command Structure:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54         |

|                    | J.2.2: Summary of SPI Commands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54         |

|                    | 1.2.3: Firing Commands: (8XXX)H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55         |

|                    | J.2.3: Firing Commands: (8XXX)H<br>J.2.4: Squib Resistance Measurement-, Squib Voltage Measurement-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 00         |

|                    | and INESS-pin Voltage Measurement Commands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56         |

|                    | J.2.5: Firing Voltage Measurement Commands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Š</b> 7 |

|                    | J.2.5: Firing Voltage Measurement Commands:<br>J.2.6: Squib Leakage Measurement Commands with one of eight squib switches in ON-st.:.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58         |

|                    | J.2.7: Voltage-/ Current-Sources (V/I) Commands:<br>J.2.8: Supply Voltage-, Lamp-Measurement and Squib Leakage Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59         |

|                    | J.2.8: Supply Voltage-, Lamp-Measurement and Squib Leakage Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -          |

|                    | with caulb switches in ()EE-state ('ommande' (1XXX)H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 60         |

|                    | J.2.9: Control Commands for Lamps, Watchdog and Safing Sensor Detection:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61         |

|                    | J.2.10: Oscillator Frequency Test Mode Command: (5555)H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62         |

|                    | J.2.9: Control Commands for Lamps, Watchdog and Safing Sensor Detection:<br>J.2.10: Oscillator Frequency Test Mode Command: (5555)H<br>J.2.11: 2.8V Reference Test Mode Command: (AAAA)H                                                                                                                                                                                                                                                                                                                                                                                                       | 62         |

|                    | J.2.12: Reset by SPI Command: (FFFF)H<br>J.2.13: Average Chip Temperature Test Mode Command: (9XXX)H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 62         |

|                    | J.2.13: Average Chip Temperature Test Mode Command: (9XXX)H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63         |

# **Combined Power-Supply and Firing Circuit for Airbag Applications**

# A. Features

- Step up converter 30V (Boost Converter) with a maximum duty cycle of 90% and a 700mA minimum current limitation of the power transistor

- Step down converter 5V (Buck Converter) Improvement of the efficiency of the buck converter by external supply (EVZ2)

- Four independent firing squib drivers

- Highside and lowside switch for each firing circuit Firing current limitation to maximum 3.25A for each firing circuit

- Digital output for firing current detection of minimum 1.75A for two squib drivers

- Squib resistance measurement with analogue outputs

- Switchable gain factor (10 or 30) for an improved accuracy of the squib resistance measurement

- Programmable squib leakage measurement to ground or to battery supply with digital outputs

- Several supply voltage measurements on external pins

- Digital output for detection of safing sensor closure

- Watch dog circuit

- Precise 100kHz oscillator

- Power on/off reset generator

- Serial interface line driver (ISO 9141 and TTL-level)

- Four voltage/current sources for diagnostic purposes

- Diagnostic lamp driver

- Diagnostic driver for inductive loads or lamps

- Serial peripheral interface (SPI) for direct driving from a micro controller

- Logic and analogue output signals for direct sensing and diagnostics by a  $\mu C$

- Package P-MQFP-64-1

| Туре     | Ordering Code | Package     |

|----------|---------------|-------------|

| TLE 6710 | on request    | P-MQFP-64-1 |

| Version B | May 05, 2001 | page 2 |

|-----------|--------------|--------|

|-----------|--------------|--------|

# **B. Circuit Description**

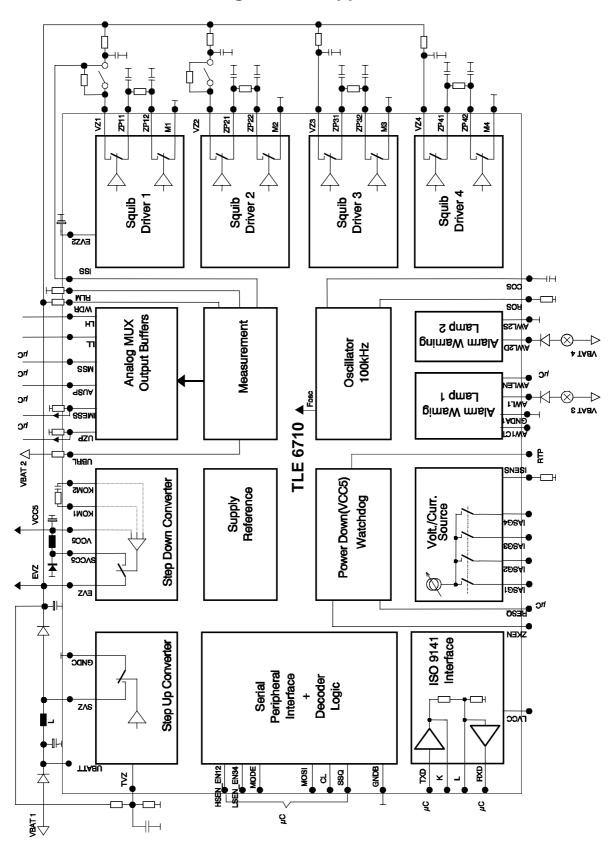

A description of each section of the IC is given below with the representative block diagram and the application circuit.

## Supply and Reference:

Internal supply and biasing of the sections is provided by a supply module which is driven by voltage EVZ of the boost converter (30V). During start up, EVZ is charged by the battery voltage UBATT via external inductance and diode. The voltage reference is based on a temperature-compensated bandgap circuit and has an accuracy of  $\pm$  1% at room temperature.

## Low Battery Detection on pin UBATT:

A comparator has been incorporated to guarantee that the modules i.e. reference voltage, internal supply and 100kHzoscillator, are fully functional before the boost converter (30V) and the logic output AUSP are enabled. It prevents the possibility of start up glitches. The internal reference voltage is monitored by a comparator which disables the output stage AUSP when the voltage on input pin UBATT drops below 5V. To prevent erratic output switching as the threshold is crossed, 200mV of hysteresis is provided.

## Oscillator for Boost (30V)-, Buck (5V)-Converter and Watchdog:

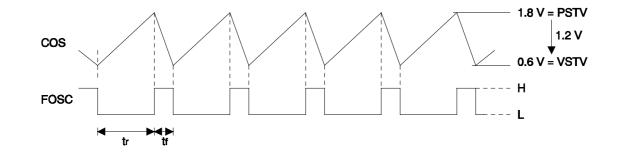

The oscillator frequency is externally programmed to 100kHz by the capacitor COS = 1nF on pin COS and a current source determined by the fixed resistor ROS = 5 k $\Omega$  on the pin ROS. The nominal voltage value on pin ROS is 1.2V.

Current calculation:

$$I_{ROS} = \frac{1.2 \text{ V}}{5 \text{ k}\Omega} = 240 \ \mu\text{A}$$

The charge to discharge ratio is controlled to yield a 90 % maximum duty cycle at the switch output of the boost converter (30V). During the discharge of COS, the oscillator generates an internal blanking pulse (FOSC) to disable the switch output of the boost converter (30V) and to enable the switch output of the buck converter (5V) as well as to provide a clock signal to the watchdog function. The nominal peak and valley saw tooth thresholds of the oscillator are VSTV = 0.6V and PSTV = 1.8V respectively.

| Version BMay 05, 2001page 3 |

|-----------------------------|

|-----------------------------|

Calculation formulas:

Capacitor charge current:

$$Icosc = \frac{7}{12} \times Iros = \frac{7}{12} \times \frac{Vros}{Rros} = 140 \,\mu\text{A}$$

Capacitor discharge current: $Icosd = -\frac{7}{2} \times Iros = -\frac{7}{2} \times \frac{Vros}{Rros} = 840 \,\mu\text{A}$ Peak to peak voltage on pin COS: $Vcospp = Vros = 1.2 \,V$ Saw tooth rise time: $tr = \frac{Vcospp \times Ccos}{Icosc} = \frac{12}{7} \times Rros \times Ccos$ Saw tooth fall time: $tr = \frac{Vcospp \times Ccos}{Icosd} = \frac{2}{7} \times Rros \times Ccos$ Oscillator frequency calculation: $fos = \frac{1}{t_r + t_f} + foffset \pm 5\% = \frac{1}{2 \times Ccos \times Rros} + foffset \pm 5\%$

$f_{\text{offset}}$  ...Frequency offset of the PCB depending on the layout of each application.

## Boost Converter (30V):

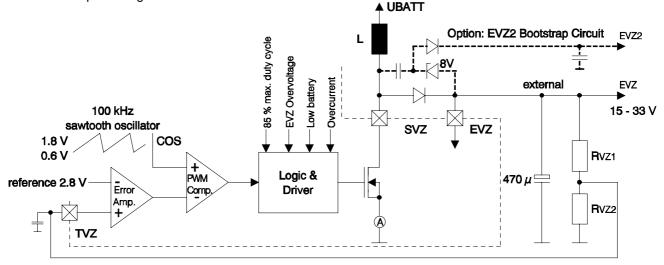

A boost converter generates a supply voltage for the airbag firing system, adjustable via external resistors between 15V and 33V. An inductance L is PWM-switched by an integrated current limited DMOS-power-transistor with a frequency of 100kHz. The reference section provides a 2.8V voltage for the regulation loop. An error amplifier compares the reference voltage with the feedback signal TVZ, which comes from an external divider network used to determine the output voltage EVZ.

Application note for programming the output voltage on pin EVZ:

$$V_{EVZ} = 2.8V \times \frac{R_{VZ1} + R_{VZ2}}{R_{VZ2}}$$

Version B

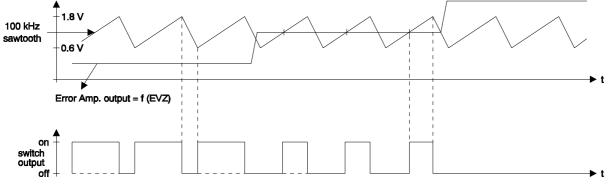

With a PWM comparator, the output of the error amplifier is then compared with a periodic linear ramp provided by the saw tooth signal of the oscillator. A logic signal with variable pulse width is generated, which passes through logic and driver circuits to the power switching FET. A duty cycle of typ. 86 % is determined by the duration of the falling ramp of the saw tooth oscillator.

The output transistor conduction is suppressed immediately if the current through the power FET exceeds typ. 800mA, low battery voltage or overvoltage on pin EVZ is detected. In case of short spikes, the logic circuit inhibits multiple pulses during one oscillating period.

<u>Warning:</u> A short from EVZ to ground can damage the external diode or the inductance, due to non existing overcurrent limitation in that path. The output transistor is designed to switch a maximum of 40V, with a drain current limitation of typically 800mA.

During start up, EVZ is charged by the battery voltage UBATT via external inductance and diode, so the voltage on pin EVZ is too low and the PWM-comparator requires a duty cycle of more than 85 %. Due to an increasing inductance current after several periods, the overcurrent sensor becomes active and reduces the maximum duty cycle to improve magnetic energy transfer.

<u>NOTE</u>: The pin GNDC chip internally is separated from the analog ground GNDB. On PCB these pins need to be connected for standard applications. If a boost converter application with higher power capability is needed, the pin GNDC can drive the gate of an external logic level power FET. The maximum output voltage on pin GNDC will be 7.5V (0mA) and minimum 5.5V driving 10mA. An external overcurrent detection circuit should switch off the external power FET and lead to a current spike on pin GNDC (900mA) to shut down the boost converter output driver stage of the TLE 6710.

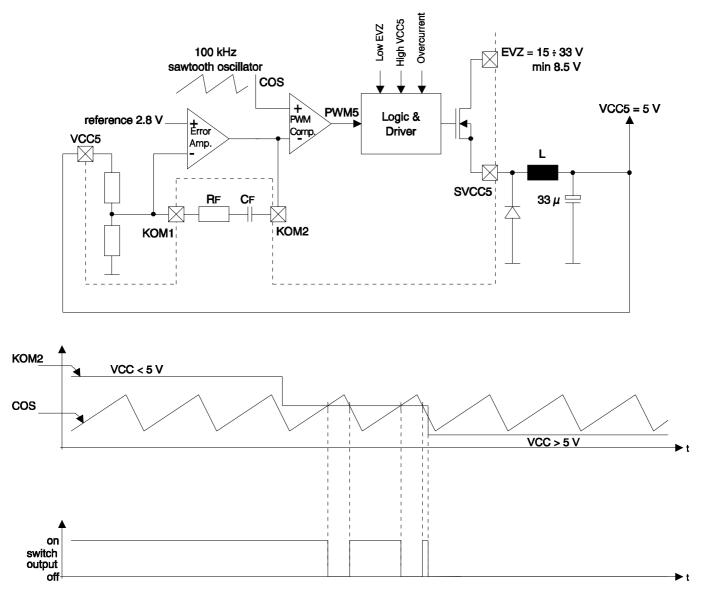

## Buck Converter (5 V):

A stabilised 5V-supply for general purpose in the airbag system is realised by a buck converter. An external inductance L is PWM switched with a frequency of 100kHz via a high side DMOS-power transistor. The regulator module is supplied by the boost converter output (15-33V), and uses the stored energy of the boost converter capacitor if battery power-down occurs.

The basis for the regulation loop is a temperature compensated 2.8V bandgap reference voltage, generated in the reference section and linked to the non inverting input of the 'Error Amplifier' with a high voltage gain (> 60dB). The reference voltage is compared with the internally divided output voltage VCC5.

External loop compensation is required for converter stability, and is formed by connecting a series resistor-capacitor ( $R_F$ ,  $C_F$ ) between pins KOM1 and KOM2. The simplest way to optimise the compensation network is to observe the response of the output voltage VCC5 to a step load change, while adjusting  $R_F$  and  $C_F$  for critical damping. The final circuit should be verified for stability under four boundary conditions. These conditions are minimum input voltages, with minimum and maximum loads.

| Version B | May 05, 2001 | page 5 |

|-----------|--------------|--------|

|-----------|--------------|--------|

The error amplifier output is applied to the inverting input of the 'Pulse Width Modulator' (PWM) and is compared with the oscillator ramp voltage COS. Output switch conduction is initiated when the error amplifier output voltage exceeds the sawtooth peak voltage, due to less VCC5 voltage.

The duration of the output transistor conduction depends on VCC5 level and conduction is suppressed immediately if the current through the power FET exceeds typically 400mA or the voltage on pin VCC5 reaches typically 6V. The logic circuit inhibits in the case of short spikes, multiple pulse operation in one oscillating period.

During start up procedure the buck converter will be enabled, if the voltage on pin TVZ is greater than 1.85V.

So the EVZ voltage of the boost converter has to reach 60 % of its final value to enable the buck converter (5V). The buck converter will be disabled, only when a power down of EVZ occurs to less than about 7 % of the nominal voltage value on pin EVZ.

The output power FET works as a source follower and is designed to switch a maximum of 40V with a drain current limitation of typ. 400mA. To make the power dissipation of the output FET smaller, the voltage drop across the device can be reduced by increasing the gate voltage. This improvement can be executed by adding an external supply voltage to the pin EVZ2, which should be approximately 8V greater than the voltage on pin EVZ and realized by a bootstrap circuit.

| Version B | May 05, 2001 | page 6 |

|-----------|--------------|--------|

|-----------|--------------|--------|

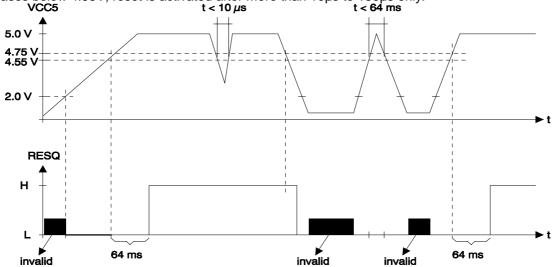

#### Power On Reset of VCC5:

In order to avoid any system malfunction, a sequence of several conditions has to be passed. In case of VCC5 (5V)power down a logic LOW output signal on pin RESQ is generated to disable an external microcontroller. When a voltage of VCC5  $\ge$  4.75V is reached, the RESQ signal remains LOW for another 64ms before switching to HIGH. If VCC5 decreases below 4.55V, reset is activated after more than 10µs to 150µs only. VCC5 t < 10 µs t < 64 ms

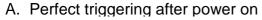

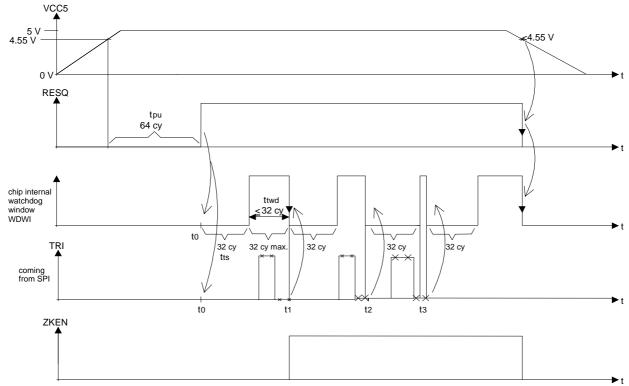

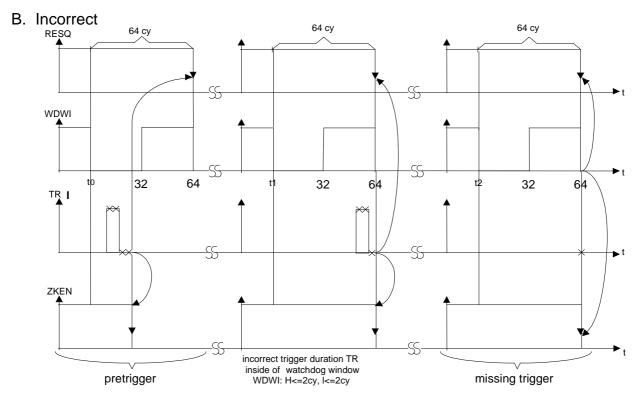

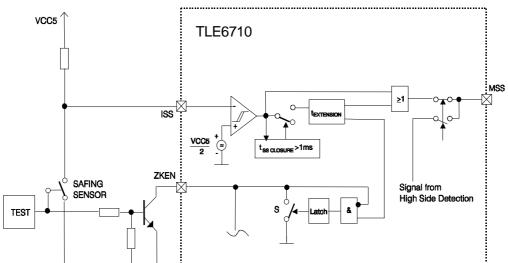

#### Watchdog Operation and Generation of the Squib Driver Enable Signal ZKEN:

The watchdog is driven by the oscillator frequency divided by 100 (= 1kHz). After power on, the LOW-signal on output RESQ for  $\mu$ C-reset is extended by 64 cycles. 32 clock cycles after the rising edge of RESQ, a chip internal trigger window (WDWI) begins. It ends after 32 cycles at the latest. If a trigger pulse (TRI) - coming via the serial peripheral interface (SPI) - occurs within the trigger window (or if a power-down occurs) the watchdog window signal is reset. The TRI pulse must be active for at least two rising clock edges and must return to zero for two clock edges. If no TRI pulse occurs in the trigger window, or if TRI pulse is outside of the trigger window, a reset (LOW) is generated on pin RESQ after 64 cycles and lasts for a further 64 cycles.

Correct triggering also will be executed, if after the falling edge of the TRI pulse signal only the sampling of the second 'low' occurs inside of the watchdog window. The beginning of the TRI pulse starts outside of the trigger window.

The TRI trigger pulse is set and latched by the SPI command WDTRH and reset by WDTRL. So the microcontroller is allowed to do measurements with the TLE 6710 during the TRI pulse is active.

In addition to the  $\mu$ C-reset signal RESQ, there exists an enable signal ZKEN for the internal squib drivers and for external firing circuits. If RESQ is high, the signal ZKEN goes to active high with the first valid trigger pulse TRI. It returns to low immediately if pretriggering, missing triggering or an incorrect trigger duration, as well as power down reset occurs. ZKEN is designed as an open drain output. If ZKEN is used as an input and held to 'low' by an external device, firing of the squibs can not be activated.

| VVCC5    | VRTP                      | AW1C | RESQ             | ZKEN             | fwd [kHz] | TWD [ms] | Remarks     |

|----------|---------------------------|------|------------------|------------------|-----------|----------|-------------|

|          |                           |      |                  |                  |           |          |             |

| < 4.55 V | Х                         | Х    | 0                | 0                | 0         | -        | -           |

| >4.75V   | $-0.3V \le VRTP \le 0.8V$ | Х    | normal operating | Normal operating | 1         | 1        |             |

|          |                           |      | mode             | mode             |           |          |             |

| >4.75V   | $2.4V \le VRTP \le$       | 1    | 1                | 1                | 1         | 1        | test mode A |

|          | VVCC5+ + 0.3V             |      |                  |                  |           |          |             |

| >4.75V   | $2.4V \le VRTP \le$       | 0    | normal operating | normal operating | 25        | 0.04     | test mode B |

|          | VVCC5+ + 0.3V             |      | mode             | mode             |           |          |             |

| >4.75V   | VVCC5 + 1.7V              | 1    | 1                | 1                | 25        | 0.04     | test mode C |

|          | $\leq$ VRTP $\leq$ 7.1V   |      |                  |                  |           |          |             |

Accelerated testing via pin RTP and AW1CT:

fwD Frequency of the internal used 'Watchdog' - clock (fwD = fos / 100; fos = 100kHz typ.) For test mode B and C: fwD = fos / 4

For test mode B and C: IWD = IOS / 4

TwD Period of the internal used 'Watchdog' - clock ( = 1 / fwD)

| Version B | May 05, 2001 | page 7 |

|-----------|--------------|--------|

|           |              | P-9-   |

## Watchdog

<u>Note:</u> After 'key ON' and sending the first correct SPI trigger command the output signal ZKEN is expected to transit to 'high' immediately. However it may stay 'low' longer depending on the voltage on pin ISS (Input Safing Sensor). This one time event happens only after a RESQ 'low' to 'high' transition in case of VISS = 0V to VVCC5/2 (Spec. 20.4A), pin ISS = open or VISS  $\geq$  VVCC5 + 1.2V (Spec.20.1). The time prolongation to achieve the rising edge on ZKEN will be 9800/fos (98ms typ.) starting from the rising edge of RESQ, if a SPI trigger command was successful at that time.

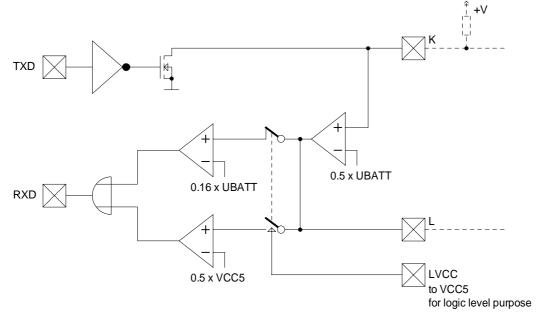

## **ISO 9141 - Serial Interface:**

Serial data communication from external to the  $\mu$ C of the airbag board is provided by a 12V/5V-level-interface. The transmission signal TXD is transferred via an open drain output buffer to pin K. The external line signal K is linked to the receiving pin RXD. If the input pin L is not connected, the typ. threshold voltage on pin K is 0.5 x VUBATT. If the input pin L is connected, the typical threshold voltage on pin L is 0.16 x VUBATT. If it is necessary to handle a logic level input signal on pin L, the input pin LVCC has to be connected to VCC5. In this case the threshold voltage on pin L is 0.5 x VVCC5.

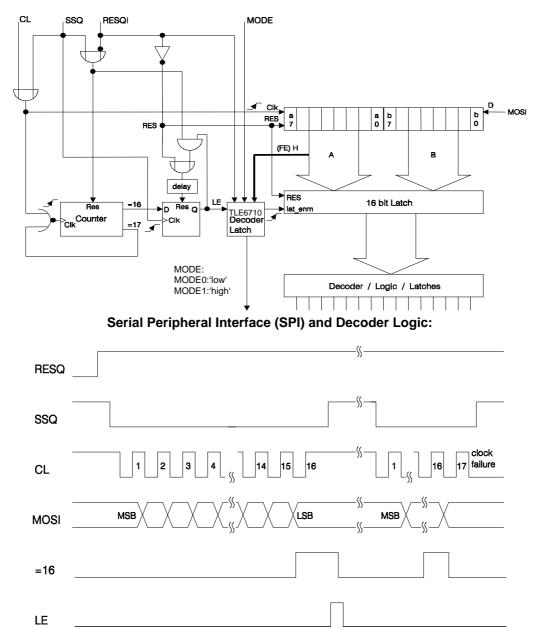

## Serial Peripheral Interface (SPI) and Decoder Logic:

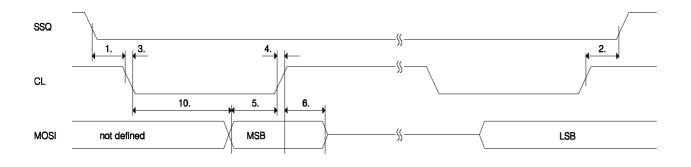

The slave select pin SSQ allows the individual selection of different slave SPI devices. Slave devices that are not selected do not interfere with SPI bus activities. The SPI logic is selected by the slave select signal SSQ for the transmission of instructions like control and diagnostic commands.

(See chapter: 'J. Serial Peripheral Interface SPI')

The master-out slave-in pin MOSI is the input signal for the serial data from the  $\mu$ C, synchronously clocked by clock input CL, which operates at a maximum transmission rate of **4** Mbits/sec.

All commands, no matter which function, consist of 16 bits, so the TLE 6710 SPI includes a 16 bit input shift register, a 16 bit latch and a decoder logic block for the generation of the SPI command signals.

With the rising edge of CL the data via MOSI is shifted into the first bit of the shift register.

To suppress data transfer errors in the event that the clock signal includes spikes or glitches, a counter for 16 clock cycles is provided. Only after occurring of 16 clock cycles, the rising edge of SSQ causes an internal signal 'lat\_enm' (latch enable) to transfer the data from the shift register to the 16 bit latch. A CMOS logic block decodes the 16 bit word of the latch to address the desired functional block.

<u>Mode definition:</u> The TLE 6710 can be configured in two modes. The difference between the two modes are the definitions of the hardware pins HSEN\_EN12, LSEN\_EN34 and MODE for the functions of firing and squib measurements (see chapter J.2). A Mode1 operation requires an initializing SPI 'Mode command' (FExx)H and a 'high' on pin MODE before starting with SPI instructions. Otherwise the control and diagnostic commands will not be decoded. A MODE0 operation requires no SPI 'Mode command' however a 'low' or 'open' on pin MODE (due to a pull down resistor). With a hardware reset RESQ=0 the ASIC will return to its default state of the MODE0.

| The following table shows the principle: | : |

|------------------------------------------|---|

|------------------------------------------|---|

| Mode  | pin: MODE | SPI: Mode command |

|-------|-----------|-------------------|

| MODE0 | 0 or open |                   |

| MODE1 | 1         | (FExx)H           |

#### Timing of the Serial Peripheral Interface (SPI):

| Version B May 05, 2001 | page 10 |

|------------------------|---------|

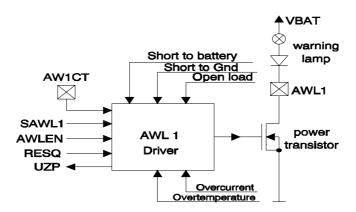

## Alarm Warning Lamp Driver (AWL1):

The driver AWL1 is designed as a low side switch. Its logical behavior can be programmed via the control pin AW1CT. If AW1CT is not connected, the lamp driver AWL1 is ON as default. If AW1CT is connected to ground (0V), the lamp driver AWL1 is <u>off</u> as default. In case of missing EVZ or VCC5 the warning lamp is supplied via pin AWL1 with a typical saturation voltage of 2V, independent of the IC-supply voltage.

| AW1CT | EVZ     | VCC5    | RESQ | AWLEN | SPI-bit | Driver AWL1 |

|-------|---------|---------|------|-------|---------|-------------|

| open  | ok      | ok      | 0    | Х     | Х       | ON          |

| gnd   | ok      | ok      | 0    | Х     | Х       | OFF         |

| open  | ok      | ok      | Х    | 0     | Х       | ON          |

| gnd   | ok      | ok      | Х    | 0     | Х       | OFF         |

| open  | ok      | ok      | 1    | 1     | SAWL1B  | ON          |

| open  | ok      | ok      | 1    | 1     | SAWL1D  | OFF         |

| gnd   | ok      | ok      | 1    | 1     | SAWL1B  | OFF         |

| gnd   | ok      | ok      | 1    | 1     | SAWL1D  | ON          |

| open  | ok      | missing | Х    | Х     | Х       | ON          |

| gnd   | ok      | missing | Х    | Х     | Х       | OFF         |

| open  | missing | ok      | Х    | Х     | Х       | ON          |

| gnd   | missing | ok      | Х    | Х     | Х       | OFF         |

| open  | missing | missing | Х    | Х     | Х       | ON          |

| gnd   | missing | missing | Х    | Х     | Х       | OFF         |

The following table defines all possible conditions:

If AWL1 is on and the voltage on pin AWL1 is greater than typically 2V, the lamp current is limited. To protect the integrated power switch against overtemperature, a thermal limitation circuit is provided. This feature prevents catastrophic failures from accidental device overheating. The temperature limitation circuit starts to work, if the voltage drop across the power transistor is greater than typically 2V. The lamp status is reported as an information of the voltage or of the current on pin AWL1 to the general analogue measurement output pin UZP.

1. Voltage measurement on pin AWL1:

Via SPI command UAWL1 the voltage on pin AWL1 is measured and linked to the measurement pin UZP with a voltage ratio of 5 to 1.

Following detections are possible:

- Short to battery if lamp is switched on

- Over temperature if lamp is switched on

- Short to ground if lamp is switched off

- Open load if lamp is switched off

#### 2. Current measurement on pin AWL1:

Via SPI command IAWL1 a current level on pin AWL1 is detected and reported to the measurement pin UZP as a digital information for 'open load if lamp is switched on'.

| Lamp switched to | Lamp current | Vuzp           |

|------------------|--------------|----------------|

| on               | ≤10 mA       | 0 to 0.4 V     |

| on               | ≥30 mA       | 1.5 V to VVCC5 |

| Version B | May 05, 2001 | page 11 |

|-----------|--------------|---------|

|-----------|--------------|---------|

## Datasheet

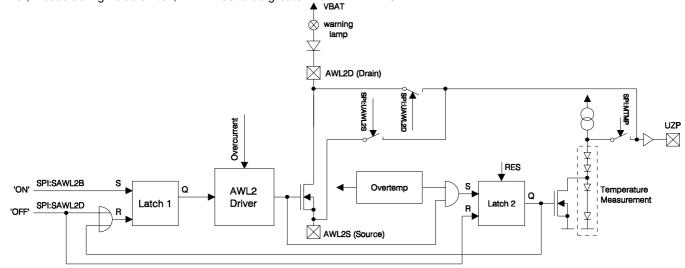

## Alarm Warning Lamp and Multifunction Driver 2 (AWL2):

A second warning lamp block (AWL2) is provided to drive high side or low side loads.

The default state of the driver is "off". The driver can be switched on via SPI control bits. To obtain minimum on resistance of the driver, if used as high side switch, VEVZ has to be greater than VAWL2D+6V

In case of missing the voltage EVZ or VCC5 the driver is switched off. The pin AW1CT has no influence to the status of the AWL2driver.

| EVZ     | VCC5    | RESQ | SPI | driver awl2 |

|---------|---------|------|-----|-------------|

| ok      | ok      | 0    | Х   | OFF         |

| ok      | ok      | 1    | on  | ON          |

| ok      | ok      | 1    | off | OFF         |

| missing | ok      | Х    | Х   | OFF         |

| ok      | missing | Х    | Х   | OFF         |

| missing | missing | Х    | Х   | OFF         |

The load current is limited to 250 to 600 mA.

The load status is reported as an information for the voltage on pins AWL2S and AWL2D to the general analogue measurement output pin UZP. This information can be selected by the corresponding SPI commands.

1. Voltage measurement on pin AWL2D:

Via SPI command UAWLD the voltage on pin AWL2D is measured and linked to the measurement pin UZP with a voltage ratio of 5 to 1.

Following detections are possible:

- Short to battery if driver is switched on

- Overtemperature if driver is switched on

- Short to ground if driver is switched off

- Open load if driver is switched off

2. Voltage measurement on pin AWL2S:

Via SPI command UAWLS the voltage on pin AWL2S is measured and linked to the measurement pin UZP with a voltage ratio of 5 to 1.

Following detections are possible:

- Short to ground if driver is switched on

- Overtemperature if driver is switched on

- Short to battery if driver is switched off

- Open load if driver is switched off

Current can be measured by connecting a resistor from drain pin to battery supply or source pin to ground corresponding to the application. The voltage drop across the resistor indicates the current through the load.

To protect the integrated power switch against overtemperature, a thermal shut down circuit is included. This feature prevents catastrophic failures from accidental device overheating. The attached schematic shows the principal function in case of overtemperature. If the lamp driver is on and an overtemperature signal of the AWL2 driver occurs, latch 2 is set and latch 1 is reset to switch off the driver. Activating an 'Average Chip Temperature'-measurement reports to pin UZP a reduced voltage of less than approx. 1.4V, which can be interpreted as a digital information of over temperature of lamp driver 2. Returning to the specified 'Average Chip Temperature' measurement only can be done by a SPI command SAWL2D (to switch off the lamp).

| Version B | May 05, 2001 | page 12 |

|-----------|--------------|---------|

|-----------|--------------|---------|

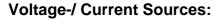

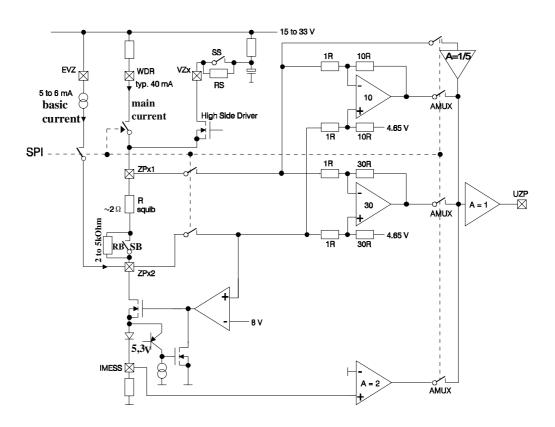

The functional block 'V/I-Sources' is provided to measure the value of four different external resistors and can be addressed by a special SPI command SELx (x=1,2,3,4) (2XXX)H. After being addressed a constant voltage source of 2.8V on pin IASGx is activated and a current flows through one addressed external resistor. The resistance dependent sensor current is reflected by a 10 to 1 current mirror to an analysis path ISENS. The voltage drop of RSENS on pin ISENS is proportional to the actual external resistive sensor value and is reported 1:1 to pin UZP. This signal is connected with an analogue port of the  $\mu$ C and stored as first measurement value. Due to the possibility of an external ground shift a second measurement occurs to use a difference measurement principle to eliminate a constant ground voltage shift. Therefor the SPI command SELx (x=1,2,3,4) AND SELV (BXXX)H has to be addressed to activate the constant voltage source to the second value of 5.0V on pin IASGx. This voltage determines a second voltage value on pin UZP.

Calculation of the external resistance value on pin IASGx (done by the  $\mu$ C):

$$R_{IASGx} = \frac{R_{SENS}}{10} \times \frac{5.0V - 2.8V}{V_{ISENS2} - V_{ISENS1}}$$

The current through pin IASGx is limited to [25]...[80] mA, if pin IASGx is shorted to ground and the voltage on pin ISENS does not reach VVCC5 due to a low resistor on pin ISENS. However the value of the IASGx current limitation can be reduced by increasing the value of the resistor on pin ISENS. Then the maximum current through pin IASGx can be calculated as:

$$I_{IASGx\,lim} = 10 x \frac{V_{VCC5}}{R_{SENS}}$$

For high accuracy the IASGx current needs to be between 1 and 20mA and the maximum ISENS voltage is less than Vvcc5-0.3V. Under clamping condition the voltage on pin ISENS is clamped to Vvcc5 + 0.3V. Calculation of the value of the resistor on pin ISENS:

$$R_{\text{SENS}} = 10 \text{ x} \frac{V_{\text{VCC5}} - 0.3V}{I_{\text{IASGmax}}}$$

| Version E | 3 |

|-----------|---|

|-----------|---|

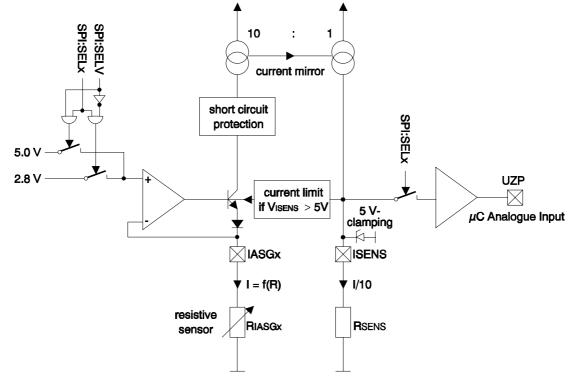

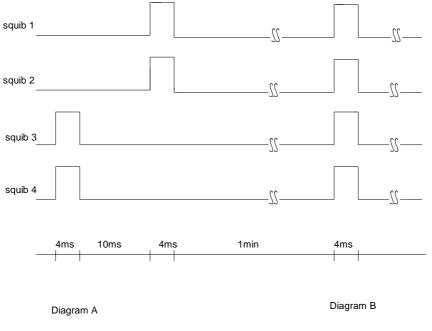

## Squib Drivers:

The TLE 6710 includes four independent driver circuits to fire one squib each. The deployment of a squib is only initiated, if two independent switches of the firing squib loop are closed. These two serial switches are realised by one highside DMOS<sup>1</sup>)-switch from squib supply pin VZx (x=1,2,3,4) to the first terminator of the squib ZPx1 (x=1,2,3,4) and one lowside DMOS-switch from the second terminator of the squib ZPx2 (x=1,2,3,4) to ground Mx (x=1,2,3,4).

| Mode  | MODE | ZKEN | ZKEN_int | HSEN_EN12 | LSEN_EN34 | Function                            |

|-------|------|------|----------|-----------|-----------|-------------------------------------|

| MODE0 | 0    | 1    | 1        | 1         | 0         | (8xxx)H: firing of HSx and / or LSx |

| MODE1 | 1    | 1    | 1        | 1         | 0         | (8xxx)H: firing of squib 1 and 2    |

| MODE1 | 1    | 1    | 1        | 0         | 1         | (8xxx)H: firing of squib 3 and 4    |

| MODE1 | 1    | 1    | 1        | 1         | 1         | (8xxx)H: firing of squibs 1 to 4    |

The squib will fire only if all following signals are present: RESQ = 1,

For MODE1 operation an initializing SPI 'Mode command' needs to be sent once after start up. If RESQ = 0 is generated, then the measurement will be interrupted and the ASIC will return to its default state of the MODE0. A soft reset (FFFF)H does not change the mode. ZKEN must be generated internally (ZKEN\_int) to high. Used as an input the ZKEN signal is not allowed to hold it to GND by an external device.

In case of activating the lowside switching transistor the firing current will be sensed (squib driver 1 and squib driver 2 only). If the current exceeds 1.75A, a digital firing current signal can be detected on pins LL and LH as described in the following table:

| Firing current of squib 1 | Firing current of squib 2 | Vll  | Vlh  |

|---------------------------|---------------------------|------|------|

| 0A                        | 0A                        | high | high |

| >1.75A                    | 0A                        | low  | high |

| 0A                        | >1.75A                    | high | low  |

| >1.75A                    | >1.75A                    | low  | low  |

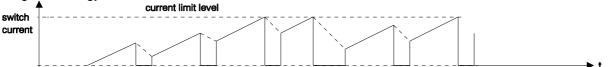

The maximum firing current of the squib loop is limited to 3.0 A by reducing the gate to source voltage of the low side DMOS transistors.

For a drain to source voltage drop less than approximately 2V of each switching transistor, no reduction of gate to source voltage of the squib transistor is demanded. So the sum of voltage drops across the high side and low side transistors does not exceed 3.0 V at 1.75 A of squib current. The gate driver of the high side transistor is supplied via pin EVZ2. A current source from EVZ to an external capacitor on pin EVZ2, de-coupled by a diode provides a sufficient gate to source voltage for the DMOS.

To protect each individual squib driver transistor in the event that the peak junction temperature of the transistor exceeds 280<sup>o</sup>C a thermal toggling circuit is provided to avoid a further increasing of the DMOS temperature. This feature prevents catastrophic failures from accidental device overheating. Due to too long switch on times and high power consumption the thermal toggling leads to a general increasing of the average chip temperature. If the average chip temperature exceeds 100°C, a driver will be deactivated under thermal toggling and stays in off-state by a latch. Repeating on-commands do not activate the affected transistor, however to resume firing it will be necessary to send a NO OP-, 0000-, driver-off- or any measurement-command to reset the latch, before sending a new firing command, once the average temperature falls below its critical level.

<sup>1)</sup>.....DMOS: Double Diffused Metal Oxide Transistor

| Version B | May 05, 2001 | page 14 |

|-----------|--------------|---------|

|           |              |         |

Truth table for the squib drivers:

| Mode  | MODE | ZKEN | ZKEN_int | HSEN_EN12 | LSEN_EN34 | SPI command / Function                |

|-------|------|------|----------|-----------|-----------|---------------------------------------|

| MODE0 | 0    | 1    | 1        | 1         | 0         | (8xxx)H: firing of HSx and / or LSx   |

| MODE0 | 0    | х    | 1        | 1         | 1         | (7xxx)H: reference + HSx main current |

| MODE0 | 0    | х    | 1        | 1         | х         | (Cxxx)H: measurement with HSx on      |

| MODE0 | 0    | х    | 1        | х         | 0         | (Cxxx)H: measurement with LSx on      |

| MODE1 | 1    | 1    | 1        | 1         | 0         | (8xxx)H: firing of squib 1 and 2      |

| MODE1 | 1    | 1    | 1        | 0         | 1         | (8xxx)H: firing of squib 3 and 4      |

| MODE1 | 1    | 1    | 1        | 1         | 1         | (8xxx)H: firing of squibs 1 to 4      |

| MODE1 | 1    | х    | 1        | 0         | 0         | (7xxx)H: reference + HSx main current |

| MODE1 | 1    | х    | 1        | 0         | 0         | (Cxxx)H: measurement with HSx on      |

| MODE1 | 1    | Х    | 1        | 0         | 0         | (Cxxx)H: measurement with LSx on      |

LSx low side switch of the squib driver (x = 1,2,3,4)

HSx high side switch of the squib driver (x = 1,2,3,4)

For MODE1 operation an initializing SPI 'Mode command' needs to be sent once after start up. If RESQ = 0 is generated, then the measurement will be interrupted and the ASIC will return to its default state of the MODE0. A soft reset (FFFF)H does not change the mode. ZKEN must be generated internally (ZKEN\_int) to high. Used as an input the ZKEN signal is not allowed to hold it to GND by an external device.

| Version B | May 05, 2001 | page 15 |

|-----------|--------------|---------|

## Squib Resistance Measurement:

The squib resistance measurement module consists of several circuit parts and can be addressed by a SPI command (4XXX)H. After being addressed a current source of approximately 5.5mA is activated and this current flows as a reference measurement current through ZPx2. The appropriate voltage drop across the squib is amplified by a precise amplifier with a fixed gain of either 10 or 30 and monitored on the external analogue output pin UZP. The measurement current is also reported by the voltage drop across the external resistor on pin IMESS. The value of this basic current through pin IMESS is determined by the external resistor on pin ROS and can be calculated by the following formula:

IIMESS = IROS x 55 x 5/12 IROS = 1.2V / RROS (IROS= $240\mu A @ 5k\Omega$ )

One of the recommended values for RROS in the application circuits is  $4.99k\Omega$ .

After the first reference measurement has been performed with the current of typ. 5.5mA, a second measurement with a programmable current source of typically 40mA is started by an additional SPI command (6XXX)H. This current is determined by an external resistor from pin EVZ to pin WDR. The voltage on pin WDR is regulated to approximately 9 V.

Squib resistance measurement: Functional schematic

Application note for calculation of the external resistor R<sub>WDR</sub>:

$$\mathsf{R}_{\mathsf{WDR}} = \frac{\mathsf{V}_{\mathsf{EVZ}} - (7.5 \text{ to } 8.5 \text{V})}{\mathsf{I}_{\mathsf{WDR}}} - (10 \text{ to } 50 \Omega) \qquad \qquad \mathsf{I}_{\mathsf{WDR}} < 60 \text{mA},$$

$$\mathsf{Rsquib} = 2\Omega \text{ approx}.$$

Also for the second measurement the voltage drop across the squib (x10 or x30) via pin UZP and the measurement current via the pin IMESS are reported to the microcontroller. This feature enables the  $\mu$ C to calculate the external squib resistance with a high accuracy by eliminating DC-offsets.

Calculation of the squib resistance R<sub>squib</sub>:

$$R_{squib} = \frac{V_{UZP1} - V_{UZP2}}{(V_{IMESS2} - V_{IMESS1})} \times R_{IMESS} / \text{ gain factor (10 or 30)} \qquad V_{UZP1} = 0.9 \times V \vee ccs \text{ typ.}$$

$$R_{IMESS} = 50\Omega \text{ approx.}$$

There is another way to measure  $R_{squib}$ , if a mechanical safing sensor (SS) with a resistor (RS) is used in parallel. Instead of activating the higher measurement current the highside switch of a squib driver can be switched on via SPI: (7XXX)H. Now a current determined by the resistor RS flows through the squib and is reported to UZP and IMESS.

For buckle switch measurement purposes an amplifier with gain 2 was provided. In applications a buckle switch (SB) with a  $2k\Omega$  to  $5k\Omega$  resistor (RB) in parallel is connected in series to the squib. For the distinction between a broken and an open seat belt switch the result of the gain 10/30 amplifier gives us no information, so the voltage drop across pin IMESS multiplied by two can be reported to pin UZP to increase the sensitivity of the current measurement through the pin IMESS. If this principle does not give information enough a squib voltage measurement with activated 'main current' can be performed to multiplex VZPx1 / 5 to pin UZP. So the SPI commands for the squib resistance measurement select between a measurement of the voltage drop across the squib (gain 10/30 amplifier), a measurement of the voltage drop across pin IMESS (gain 2 amplifier) or a measurement of the voltage on pin Zpx1 (divided by 5) reported to pin UZP each.

The measurement for each squib is activated separately, but the analogue output signals on pins UZP and IMESS are common.

<u>Note 1:</u> The high measurement current through the squib requires a force and sense measurement principle to guarantee the high resistance measurement accuracy. So the precise gain-10-amplifier sense inputs and the gain-30-amplifier sense inputs are bonded separately to the pins ZPx1 and ZPx2. (x=1,2,3,4).

Note 2: The analogue output pin UZP can be connected in parallel with other ASICs on one PCB.

<u>Note 3:</u> The current output pin IMESS can be connected in parallel with other ASICs on one PCB. So the external resistor on pin IMESS is only used once and is common for all IC's.

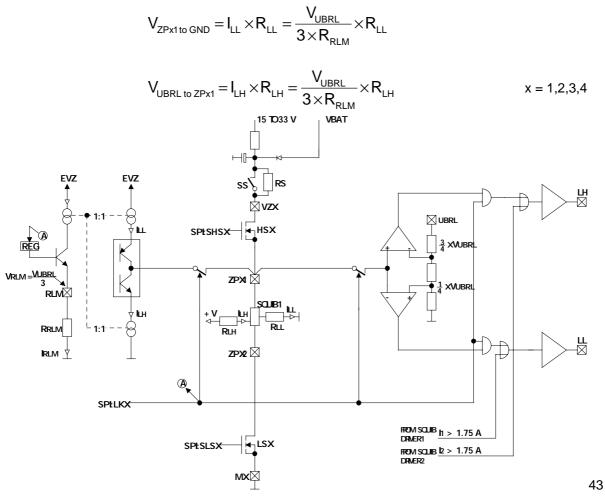

#### Squib Leakage Measurement:

The leakage resistance measurement module can be addressed only for one squib at one time by a SPI command (1XXX)H. The current for the leakage measurement  $I_{RLM}$  is determined by the reference resistor RRLM from pin RLM to ground, which is supplied by a voltage of VUBRL / 3.

$$I_{\text{RLM}} = \frac{V_{\text{UBRL}}}{3 \times R_{\text{RLM}}} = I_{\text{LL}} = I_{\text{LH}}$$

Due to a leakage the programmed leakage current  $I_{RLM}$  can flow either from the squib system via the leakage resistor  $R_{LL}$  to ground ( $I_{LL}$ ) or from a positive voltage +V via the leakage resistor  $R_{LH}$  into the squib system ( $I_{LH}$ ). See schematic.

| Version B | May 05, 2001 | page 17 |

|-----------|--------------|---------|

|           | may 00, 2001 | page    |

Across the leakage resistors R<sub>LL</sub> and R<sub>LH</sub> the following leakage voltage drops can be monitored:

Leakage resistance measurement: Functional schematic

For the TLE 6710 the leakage resistance threshold is defined by:

RLeak = RLL = RLH = RRLM x 3/4

and so the leakage voltage drops become:

VZPx1 to GNDB = VUBRL / 4

and

V+V to ZPx1 = VUBRL / 4

Two comparators, which are referenced to  $1/4 \times V_{UBRL}$  and  $3/4 \times V_{UBRL}$ , determine a leakage to  $V_{UBRL}$  or a higher voltage by setting pin LH to 'low' and a leakage to ground by setting pin LL to 'low'. If no leakage is detected the pins LL and LH report 'high'.

To prevent jitters on the output pins a hysteresis of 1/48 x V<sub>UBRL</sub> is provided in both comparators.

Leakage resistance malfunction can be simulated in a testmode by switching on only the squib driver highside transistor for a leakage to battery, as well as by switching on only the lowside transistor for a leakage to ground by SPI: (CXXX)H. (see chapter 'SPI Commands').

#### Supply Voltage Measurements:

By SPI commands (1XXX)H (see chapter J.2.8) different voltage measurements are activated and reported to the analogue output pin UZP with a defined voltage ratio. The pin names of the voltage sources which can be selected are: UBATT, UBRL, ZPx1 voltage ratio to pin UZP: 5, EVZ, EVZ2, VZ1, VZ2, VZ3, VZ4 voltage ratio to pin UZP: 8.

For test purposes the internal used reference voltage can be measured by addressing the SPI command UREF: (AA AA)H. UREF voltage ratio to pin UZP: 1 (+/-7%).

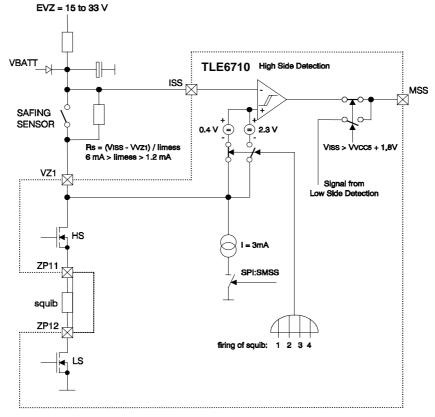

## **Detection of Safing Sensor Closure:**

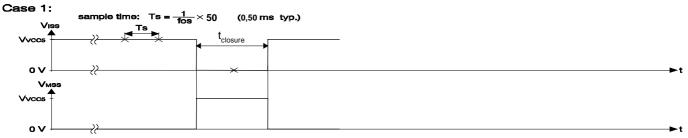

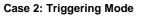

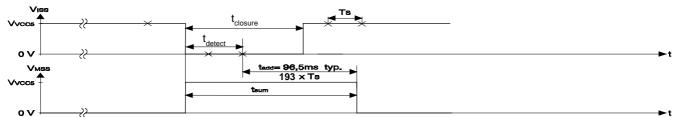

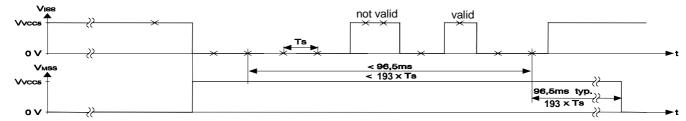

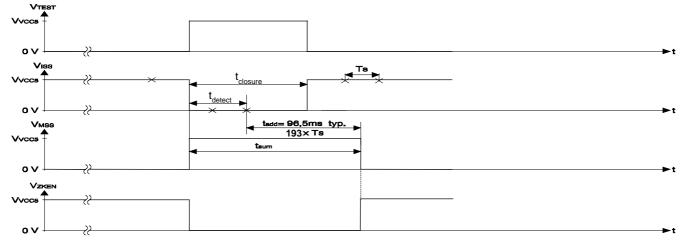

Depending on the voltage on pin ISS either the high side - or the low side detection circuit is activated.