# SPIDER - TLE7235E

8 Channel High-Side and Low-Side Relay Switch with Limp Home Mode

**Automotive Power**

### **Table of Contents**

## **Table of Contents**

|                                             | Table of Contents                                                                                                                                                                                                                                                                                  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                           | Overview                                                                                                                                                                                                                                                                                           |

| <b>2</b><br>2.1                             | Block Diagram                                                                                                                                                                                                                                                                                      |

| <b>3</b><br>3.1<br>3.2                      | Pin Configuration       8         Pin Assignment       8         Pin Definitions and Functions       8                                                                                                                                                                                             |

| <b>4</b><br>4.1<br>4.2<br>4.3               | Electrical Characteristics10Absolute Maximum Ratings10Functional Range17Thermal Resistance12                                                                                                                                                                                                       |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4        | Power Supply13Operation Modes13Limp Home Mode13Reset13Electrical Characteristics15                                                                                                                                                                                                                 |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Power Stages       16         Input Circuit       16         Channels 4 and 5       16         Inductive Output Clamp       17         Timing Diagrams       18         Electrical Characteristics       19         Command Description       20                                                   |

| 7<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | Protection Functions2Over Load Protection2Over Temperature Protection2ESD protection2Reverse Polarity Protection2Loss of $V_{\rm bb}$ 2Electrical Characteristics2                                                                                                                                 |

| <b>8</b><br>8.1<br>8.2                      | Diagnostic Features23Electrical Characteristics24Command Description25                                                                                                                                                                                                                             |

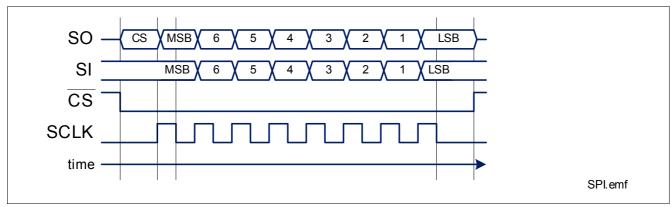

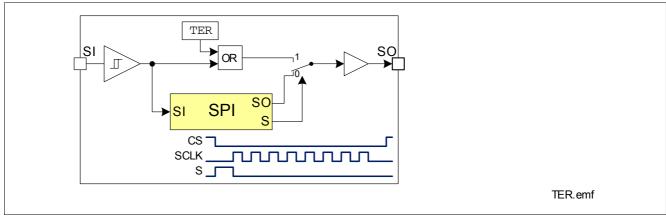

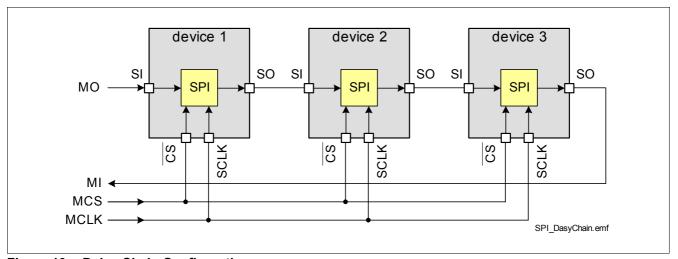

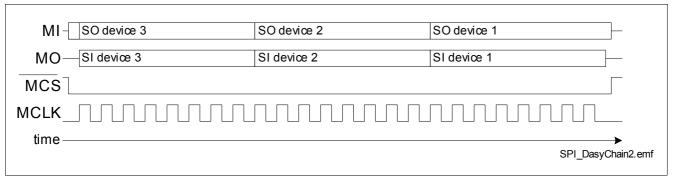

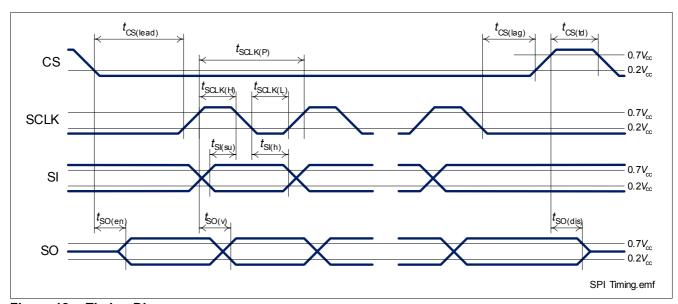

| 9<br>9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6 | Serial Peripheral Interface (SPI)         27           SPI Signal Description         27           Daisy Chain Capability         28           SPI Protocol         29           Register Overview         30           Timing Diagrams         37           Electrical Characteristics         32 |

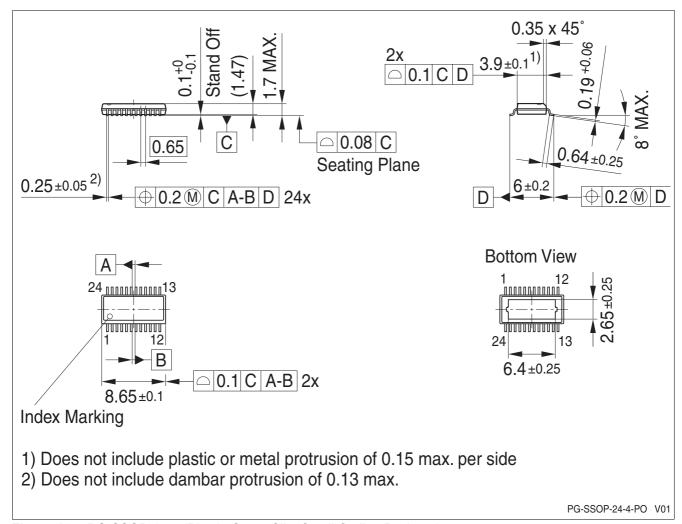

| 10                                          | Package Outlines 34                                                                                                                                                                                                                                                                                |

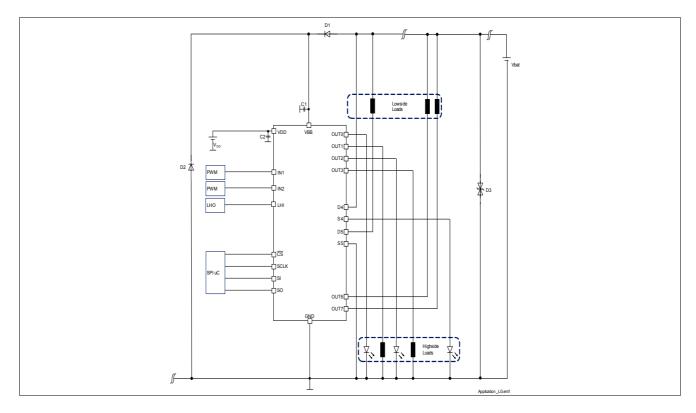

| 11                                          | Application Information                                                                                                                                                                                                                                                                            |

| 12                                          | Revision History 36                                                                                                                                                                                                                                                                                |

### **SPI Driver for Enhanced Relay Control**

**TLE7235E**

#### 1 Overview

#### **Features**

- · 8 bit SPI for diagnostics and control, providing daisy chain capability

- Very wide range for digital supply voltage

- Two configurable input pins offer complete flexibility for PWM operation

- · Stable behavior at under voltage

- Green Product (RoHS compliant)

- AEC Qualified

PG-SSOP-24-4

#### **Description**

The TLE7235E is an eight channel high-side and low-side power switch in PG-SSOP-24-4 package providing embedded protective functions. It is especially designed for standard relays and LEDs in automotive applications.

The output stages incorporate two low-side, four high-side and two auto configuring high-side or low-side switches.

A serial peripheral interface (SPI) is utilized for control and diagnosis of the device and the load. For direct control, there are two input pins available.

The TLE7235E provides a micro controller fail-safe function which is activated via a high signal at the limp home input pin. There is a power supply integrated in the device to ensure this functionality even without digital supply voltage.

The power transistors are built by N-channel power MOSFETs. The device is monolithically integrated in Smart Power Technology.

| Туре     | Package      | Marking  |

|----------|--------------|----------|

| TLE7235E | PG-SSOP-24-4 | TLE7235E |

Data Sheet 3 Rev. 1.0, 2008-10-30

Overview

### Table 1 Product Summary

| Operating range power supply voltage           | $V_{\mathrm{bb}}$   | 5.5 28 V  |

|------------------------------------------------|---------------------|-----------|

| Digital supply voltage                         | $V_{DD}$            | 3.0 5.5 V |

| Typical On-State resistance at 25 °C           | $R_{DS(ON)}$        |           |

| high-side: 2 channels (Relay)                  |                     | 0.9 Ω     |

| high-side: 2 channels (Generic, LED)           |                     | 1.6 Ω     |

| auto configuring: 2 channels (Relay, Supplies) |                     | 0.9 Ω     |

| low-side: 2 channels (Relay)                   |                     | 0.9 Ω     |

| Nominal load current (all channels active)     | $I_{L(nom,\;min)}$  |           |

| Relay                                          |                     | 350 mA    |

| LED, Generic                                   |                     | 175 mA    |

| Over load switch off threshold                 | $I_{DS(OVL,\;min)}$ | 500 mA    |

| Output leakage current per channel at 25 °C    | $I_{DS(OFF,max)}$   | 1 μΑ      |

| Drain to source clamping voltage               | $V_{DS(CL,\;min)}$  | 41 V      |

| Source to ground clamping voltage              | $V_{ m bb(CL,max)}$ | -16 V     |

| SPI clock frequency                            | $f_{\sf SCLK(max)}$ | 5 MHz     |

#### **Protective Functions**

- · Over load and short circuit protection

- Thermal shutdown

- Electrostatic discharge protection (ESD)

#### **Diagnostic Functions**

- Latched diagnostic information via SPI

- Open load detection in OFF-state

- · Over load detection in ON-state

- Over temperature

#### **Limp Home / Fail-Safe Functions**

- · Limp home activation via pin LHI

- Limp home configuration via input pins

#### **Applications**

- Especially designed for driving relays and LEDs in automotive applications

- · All types of resistive and inductive loads

- Suitable to switch 5 V power supply lines by auto configuring channels

Overview

#### **Detailed Description**

The TLE7235E is an eight channel high-side and low-side relay switch providing embedded protective functions. The output stages incorporate two low-side switches (0.9  $\Omega$  per channel), four high-side switches (two channels with 0.9  $\Omega$  and two channels with 1.6  $\Omega$ ) and two auto-configuring high-side or low-side switches (0.9  $\Omega$  per channel). The auto-configuring switches can be utilized in high-side or low-side configuration just by connecting the load accordingly. They are also suitable to switch a 5 V supply line in high-side configuration. Protective and diagnostic functions adjust automatically to the chosen configuration.

The 8 bit serial peripheral interface (SPI) is utilized for control and diagnosis of the device and the loads. The SPI interface provides daisy chain capability in order to assemble multiple devices in one SPI chain by using the same number of micro-controller pins.

Furthermore, the TLE7235E is equipped with two input pins that can be individually routed to the output control of each channel thus offering complete flexibility in design and PCB-layout. The input multiplexer is controlled via SPI.

In limp home mode (fail-safe mode), the input pins are directly routed to the configurable output channels 4 and 5. The limp home mode operates independently of digital power supply and is activated via pin LHI.

The device provides full diagnosis of the load via open load, over load and short circuit detection. SPI diagnosis flags indicate latched fault conditions that may have occurred.

Each output stage is protected against short circuit. In case of over load, the affected channel switches off. There are temperature sensors available for each channel to protect the device against over temperature.

The device protects itself with a build in reverse polarity protection which prohibits intrinsic current flow through the logic during reverse polarity. However the output stages still incorporate a reverse diode where current can flow through during reverse polarity.

The power transistors are built by N-channel power MOSFETs. The inputs are ground referenced CMOS compatible. The device is monolithically integrated in Smart Power Technology.

Data Sheet 5 Rev. 1.0, 2008-10-30

**Block Diagram**

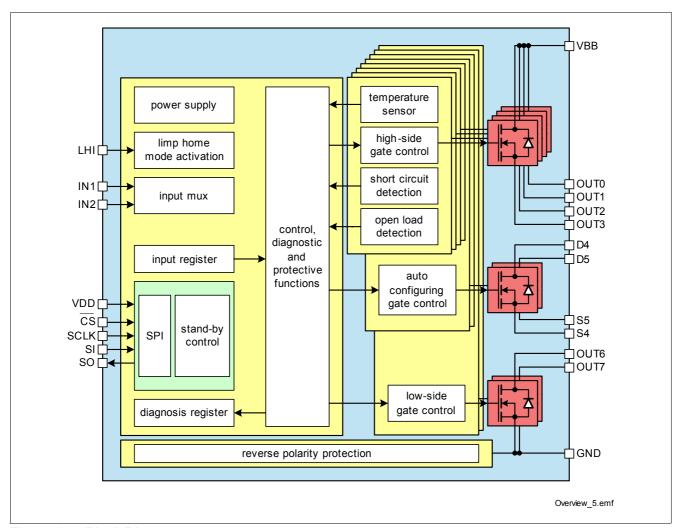

## 2 Block Diagram

Figure 1 Block Diagram

**Block Diagram**

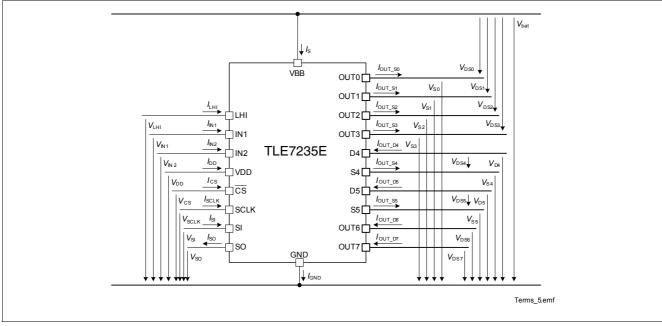

#### 2.1 Terms

Figure 2 shows all terms used in this data sheet.

Figure 2 Terms

In all tables of the electrical characteristics is valid:

Channel related symbols without channel number are valid for each channel separately (e.g.  $V_{\rm DS}$  specification is valid for  $V_{\rm DS0} \dots V_{\rm DS7}$ ). In order to make the description of output currents easier, the load current  $I_{\rm Out}$  is equivalent to the drain current  $I_{\rm OUT\_D}$  in low-side configuration and the source current  $I_{\rm OUT\_S}$  in high-side configuration.

All SPI register bits are marked as follows: ADDR. PARAMETER (e.g. ICR01.INX1). In SPI register description, the values in bold letters (e.g.  $\mathbf{0}$ ) are default values.

**Pin Configuration**

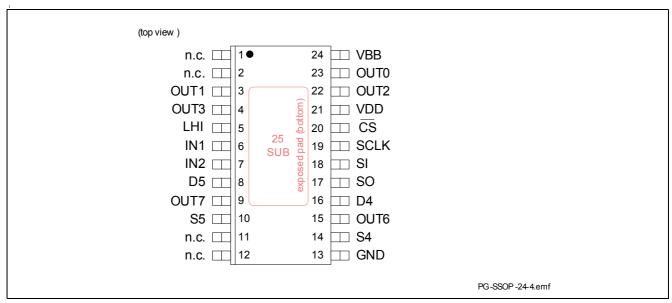

## **3** Pin Configuration

### 3.1 Pin Assignment

Figure 3 Pin Configuration PG-SSOP24-4

### 3.2 Pin Definitions and Functions

| Pin      | Symbol | I/O         | Function                                                          |

|----------|--------|-------------|-------------------------------------------------------------------|

| Power \$ | Supply | <del></del> |                                                                   |

| 21       | VDD    | -           | Digital power supply                                              |

| 24       | VBB    | -           | Power supply                                                      |

| 13       | GND    | -           | Digital, analog and power ground                                  |

| 25       | SUB    | -           | Substrate pins for thermal connection.                            |

|          |        |             | To enable reverse polarity protection these pins must be floating |

| Power 9  | Stages |             |                                                                   |

| 23       | OUT0   | 0           | Source of high side power transistor channel 0                    |

| 3        | OUT1   | 0           | Source of high side power transistor channel 1                    |

| 22       | OUT2   | 0           | Source of high side power transistor channel 2                    |

| 4        | OUT3   | 0           | Source of high side power transistor channel 3                    |

| 16       | D4     | 0           | Drain of auto configuring power transistor 4                      |

| 14       | S4     | 0           | Source of auto configuring power transistor 4                     |

| 8        | D5     | 0           | Drain of auto configuring power transistor 5                      |

| 10       | S5     | 0           | Source of auto configuring power transistor 5                     |

| 15       | OUT6   | 0           | Drain of low side power transistor channel 6                      |

| 9        | OUT7   | 0           | Drain of low side power transistor channel 7                      |

| Inputs   | 1      |             |                                                                   |

| 5        | LHI    | I           | Limp home activation input pin (pull down)                        |

| 6        | IN1    | I           | Input multiplexer input 1 pin (pull down)                         |

## **Pin Configuration**

| Pin       | Symbol | I/O | Function                                  |

|-----------|--------|-----|-------------------------------------------|

| 7         | IN2    | I   | Input multiplexer input 2 pin (pull down) |

| SPI       |        | 1   |                                           |

| 20        | CS     | I   | SPI Chip select (pull up)                 |

| 19        | SCLK   | I   | Serial clock                              |

| 18        | SI     | I   | Serial data in                            |

| 17        | SO     | 0   | Serial data out                           |

| Others    |        |     |                                           |

| 1,2,11,12 | n.c.   | I   | not connected                             |

**Electrical Characteristics**

## 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings 1)

Stresses above the ones listed here may affect device reliability or may cause permanent damage to the device. The values below are not considering combinations of different maximum conditions at one time

$T_{\rm j}$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Absolute Maximum Ratings <sup>1)</sup> |                                                                                                                                   |                   |              |      |      |                                                  |  |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|------|------|--------------------------------------------------|--|--|

| Pos.                                   | Parameter                                                                                                                         | Symbol            | Limit Values |      | Unit | <b>Test Conditions</b>                           |  |  |

|                                        |                                                                                                                                   |                   | min.         | max. |      |                                                  |  |  |

| Power                                  | Supply                                                                                                                            |                   | •            |      |      |                                                  |  |  |

| 4.1.1                                  | Power supply voltage                                                                                                              | $V_{\rm bb}$      | -16          | 40   | V    | -16V max. 2 minutes                              |  |  |

| 4.1.2                                  | Digital supply voltage                                                                                                            | $V_{DD}$          | -0.3         | 5.5  | V    | _                                                |  |  |

| 4.1.3                                  | Power supply voltage for full short circuit protection (single pulse) $(T_j = -40  ^{\circ}\text{C} \dots 150  ^{\circ}\text{C})$ | $V_{\rm bat(SC)}$ | 0            | 28   | V    | -                                                |  |  |

| Power                                  | Stages                                                                                                                            |                   |              |      |      |                                                  |  |  |

| 4.1.4                                  | Load current                                                                                                                      | $I_{L}$           |              |      | Α    | _                                                |  |  |

|                                        | channel 0, 1, 4, 5, 6, 7                                                                                                          |                   | -0.5         | 0.5  |      |                                                  |  |  |

|                                        | channel 2, 3                                                                                                                      |                   | -0.25        | 0.25 |      |                                                  |  |  |

| 4.1.5                                  | Voltage at power transistor                                                                                                       | $V_{DS}$          | _            | 41   | V    | _                                                |  |  |

| 4.1.6                                  | Power transistor's source voltage                                                                                                 | $V_{Out\_S}$      | -16          | _    | V    | _                                                |  |  |

| 4.1.7                                  | Power transistor's drain voltage                                                                                                  | $V_{Out\_D}$      | _            | 41   | ٧    | _                                                |  |  |

| 4.1.8                                  | Max. energy dissipation one channel single pulse for ch. 0, 1, 4, 5, 6, 7                                                         | $E_{AS}$          |              |      | mJ   | 2)                                               |  |  |

|                                        |                                                                                                                                   |                   | _            | 65   |      | $T_{\rm j(0)}$ = 105 °C $I_{\rm D(0)}$ = 0.35 A  |  |  |

|                                        |                                                                                                                                   |                   | _            | 50   |      | $T_{\rm j(0)}$ = 150 °C $I_{\rm D(0)}$ = 0.250 A |  |  |

| 4.1.9                                  | Maximum energy dissipation one channel repetitive pulses for ch. 0, 1, 4, 5, 6, 7                                                 | $E_{AR}$          |              |      | mJ   | 2)                                               |  |  |

|                                        | 1 · 10 <sup>4</sup> cycles                                                                                                        |                   | _            | 18   |      | $T_{\rm j(0)}$ = 105 °C $I_{\rm D(0)}$ = 0.250 A |  |  |

|                                        | 1 · 10 <sup>6</sup> cycles                                                                                                        |                   | -            | 13   |      | $T_{\rm j(0)}$ = 105 °C $I_{\rm D(0)}$ = 0.220 A |  |  |

| 4.1.10                                 | Max. energy dissipation one channel single pulse for ch. 2,3                                                                      | $E_{AS}$          |              |      | mJ   | 2)                                               |  |  |

|                                        |                                                                                                                                   |                   | _            | 50   |      | $T_{\rm j(0)}$ = 105 °C $I_{\rm D(0)}$ = 0.250 A |  |  |

|                                        |                                                                                                                                   |                   | _            | 30   |      | $T_{\rm j(0)}$ = 150 °C $I_{\rm D(0)}$ = 0.250 A |  |  |

<sup>1)</sup> not subject to production test

### **Electrical Characteristics**

$T_{\rm j}$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Abso   | lute Maximum Ratings <sup>1)</sup>                                   |            |      |                    |      |                                                     |  |

|--------|----------------------------------------------------------------------|------------|------|--------------------|------|-----------------------------------------------------|--|

| Pos.   | Parameter                                                            | Symbol     | Lim  | it Values          | Unit | Test Conditions                                     |  |

|        |                                                                      |            | min. | max.               | Ī    |                                                     |  |

| 4.1.11 | Maximum energy dissipation one channel repetitive pulses for ch. 2,3 | $E_{AR}$   |      |                    | mJ   | 2)                                                  |  |

|        | 1 · 10 <sup>4</sup> cycles                                           |            | _    | 12                 |      | $T_{\rm j(0)}$ = 105 °C<br>$I_{\rm D(0)}$ = 0.180 A |  |

|        | 1 · 10 <sup>6</sup> cycles                                           |            | _    | 11                 |      | $T_{\rm j(0)}$ = 105 °C<br>$I_{\rm D(0)}$ = 0.180 A |  |

| Logic  | Pins                                                                 |            |      | *                  |      |                                                     |  |

| 4.1.12 | Voltage at input pins                                                | $V_{IN}$   | -0.3 | $V_{\rm DD}$ + 0.3 | V    | 3)                                                  |  |

| 4.1.13 | Voltage at LHI pin                                                   | $V_{LHI}$  | -0.3 | 5.5                | V    | _                                                   |  |

| 4.1.14 | Voltage at chip select pin                                           | $V_{CS}$   | -0.3 | $V_{\rm DD}$ + 0.3 | V    | 3)                                                  |  |

| 4.1.15 | Voltage at serial clock pin                                          | $V_{SCLK}$ | -0.3 | $V_{\rm DD}$ + 0.3 | V    | 3)                                                  |  |

| 4.1.16 | Voltage at serial input pin                                          | $V_{SI}$   | -0.3 | $V_{\rm DD}$ + 0.3 | V    | 3)                                                  |  |

| 4.1.17 | Voltage at serial output pin                                         | $V_{SO}$   | -0.3 | $V_{\rm DD}$ + 0.3 | V    | 3)                                                  |  |

| Tempe  | eratures                                                             |            |      | <u> </u>           |      |                                                     |  |

| 4.1.18 | Junction Temperature                                                 | $T_{j}$    | -40  | 150                | °C   | _                                                   |  |

| 4.1.19 | Storage Temperature                                                  | $T_{stg}$  | -55  | 150                | °C   | _                                                   |  |

| ESD S  | usceptibility                                                        | •          | -    |                    |      |                                                     |  |

| 4.1.20 | ESD susceptibility on all pins                                       | $V_{ESD}$  | -2   | 2                  | kV   | HBM <sup>4)</sup>                                   |  |

<sup>1)</sup> not subject to production test

### 4.2 Functional Range

| Pos.  | Parameter                                         | Symbol                    | Lir  | nit Values | Unit | Conditions                       |  |

|-------|---------------------------------------------------|---------------------------|------|------------|------|----------------------------------|--|

|       |                                                   |                           | Min. | Max.       |      |                                  |  |

| 4.2.1 | Supply Voltage Range for Nominal Operation        | $V_{ m bb(nom)}$          | 9    | 16         | V    | -                                |  |

| 4.2.2 | upper Supply Voltage Range for Extended Operation | $V_{\mathrm{bb(ext),up}}$ | 16   | 28         | V    | Parameter Deviations possible    |  |

| 4.2.3 | lower Supply Voltage Range for Extended Operation | $V_{ m bb(ext),low}$      | 5.5  | 9          | V    | Parameter<br>Deviations possible |  |

| 4.2.4 | Junction Temperature                              | $T_{j}$                   | -40  | 150        | °C   | _                                |  |

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

<sup>2)</sup> Pulse shape represents inductive switch off:  $I_L(t) = I_L(0) * (1 - t / t_{pulse}); 0 < t < t_{pulse}$

<sup>3)</sup>  $V_{\rm DD}$  + 0.3 V < 5.5 V

<sup>4)</sup> ESD susceptibility, HBM according to EIA/JESD 22-A114

**Electrical Characteristics**

#### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                                        | Symbol                   | I    | Limit Val | ues  | Unit | Conditions |

|-------|--------------------------------------------------|--------------------------|------|-----------|------|------|------------|

|       |                                                  |                          | Min. | Тур.      | Max. |      |            |

| 4.3.1 | Junction to Case, bottom                         | $R_{\mathrm{thJC,back}}$ | _    | _         | 4    | K/W  | 2)         |

| 1.3.2 | Junction to Case, top                            | $R_{thJC,top}$           | _    | _         | 35   | K/W  | 2)         |

| 1.3.3 | Junction to Pin (6,7,18 or 19)                   | $R_{\mathrm{thJPin}}$    | _    | _         | 12   | K/W  | 2)         |

| 1.3.4 | Junction to Ambient (1s0p, min. footprint)       | $R_{thJA,min}$           | _    | 95        | _    | K/W  | 3)         |

| .3.5  | Junction to Ambient (1s0p+300mm <sup>2</sup> Cu) | $R_{thJA,300}$           | -    | 50        | _    | K/W  | 4)         |

| 1.3.6 | Junction to Ambient (1s0p+600mm <sup>2</sup> Cu) | $R_{thJA,600}$           | _    | 40        | _    | K/W  | 5)         |

| .3.7  | Junction to Ambient (2s2p)                       | $R_{\mathrm{thJA,2s2p}}$ | _    | 31        | _    | K/W  | 6)         |

- 1) Not subject to production test

- 2) Specified  $R_{\text{thJSP}}$  value is simulated at natural convection on a cold plate setup (all pins are fixed to ambient temperature).  $T_{\text{a}}$  = 85 °C. Ch1 to Ch8 are dissipating 1 W power (0.125 W each).

- 3) Specified  $R_{\rm thJA}$  value is according to Jedec JESD51-2,-3 at natural convection on FR4 1s0p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with minimal footprint copper area and 70  $\mu$ m thickness.  $T_a$  = 85 °C, Ch1 to Ch8 are dissipating 1 W power (0.125 W each).

- 4) Specified  $R_{\rm thJA}$  value is according to Jedec JESD51-2,-3 at natural convection on FR4 1s0p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with additional heatspreading copper area of 300mm² and 70  $\mu$ m thickness.  $T_{\rm a}$  = 85 °C, Ch1 to Ch8 are dissipating 1 W power (0.125 W each).

- 5) Specified  $R_{\rm thJA}$  value is according to Jedec JESD51-2,-3 at natural convection on FR4 1s0p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with additional heatspreading copper area of 600mm<sup>2</sup> and 70  $\mu$ m thickness.  $T_{\rm a}$  = 85 °C, Ch1 to Ch8 are dissipating 1 W power (0.125 W each).

- 6) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-7 at natural convection on FR4 2s2p board; The product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70  $\mu$ m Cu, 2 x 35  $\mu$ m Cu).  $T_{\rm a}$  = 85 °C, Ch1 to Ch8 are dissipating 1 W power (0.125 W each).

**Power Supply**

## 5 Power Supply

The TLE7235E is supplied by two supply voltages  $V_{\rm bb}$  and  $V_{\rm DD}$ . The  $V_{\rm bb}$  supply line is connected to a battery feed and used by the power switches and by an integrated power supply for the register banks. There is an under voltage reset function implemented for the  $V_{\rm bb}$  power supply. After start-up of the power supply, all SPI registers are reset to their default values and the device is in sleep mode (standby). The SPI command CMD.WAKE = 1 is switching the device to operation mode (ON), while a command CMD.STB = 1 send the device to sleep mode (standby) again.

The  $V_{\rm DD}$  supply line is used by the SPI shift register related circuitry and for driving the SO line. As a result, the daisy chain function is available as soon as  $V_{\rm DD}$  is provided in the specified range independent of  $V_{\rm bb}$ . A capacitor between pins  $V_{\rm DD}$  and GND is recommended (especially in case of EMI).

### 5.1 Operation Modes

There is a limp home functionality implemented in the TLE7235E, which is activated via pin LHI. Please refer to **Section 5.2** for details.

The device provides a sleep mode (stand by) to minimize current consumption, which also resets the register banks. It is entered and left by dedicated SPI commands. The sleep mode current is minimized only when limp home is inactive. After limp home, the device enters sleep mode automatically.

The following table shows the operation modes depending on  $V_{\rm bb}$ ,  $V_{\rm DD}$  and the limp home input signal LHI.

| Operation Modes      |       |       |       |      |       |      |       |

|----------------------|-------|-------|-------|------|-------|------|-------|

| VBB                  | 0 V   | 0 V   | 0 V   | 12 V | 12 V  | 12 V | 12 V  |

| VDD                  | 0 V   | 5 V   | 5 V   | 0 V  | 0 V   | 5 V  | 5 V   |

| LHI                  | X     | 0 V   | 5 V   | 0 V  | 5 V   | 0 V  | 5 V   |

| Switches operating   | -     | -     | -     | 1    | 1     | 1    | 1     |

| Limp Home            | -     | -     | -     | -    | 1     | -    | 1     |

| SPI & daisy-chain    | -     | 1     | 1     | -    | -     | 1    | 1     |

| Register Banks       | reset | reset | reset | 1    | reset | 1    | reset |

| Diagnostic functions | -     | -     | -     | 1    | -     | 1    | -     |

|                      |       |       |       |      |       |      |       |

#### 5.2 Limp Home Mode

The TLE7235E offers the capability of driving dedicated channels during fail-safe operation of the system. This limp home mode is activated by a high signal at pin LHI. In limp home mode, the SPI registers are reset and the input pins are directly routed to the auto configuring channels (channel 4 and 5). As a result, the limp home operation can be chosen for high-side and low-side driven loads.

Due to the integrated power supply, limp home operation is independent of digital power supply  $V_{\rm DD}$ . In case of stand-by, a high signal at pin LHI will wake up the device. After limp home operation, the device enters sleep mode in any case.

#### 5.3 Reset

There are several reset trigger implemented in the device. A reset switches off all channels and sets the registers to default values. After any kind of reset, the transmission error flag (TER) is set.

#### **Under Voltage Reset:**

During this device condition a read on SPI always delivers the Standard Diagnostic Frame with a TER flag. This under voltage reset is released when all the supply voltages levels are above under voltage threshold.

Data Sheet 13 Rev. 1.0, 2008-10-30

**Power Supply**

**Reset Command:** There is a reset command available to reset all register bits of the register bank and the diagnosis registers. As soon as CMD.RST = 1, a reset is triggered.

**Limp Home Mode:** In limp home mode, the SPI write-registers are reset. The SPI interface is operating normally, so the limp home bit LHI as well as the diagnosis flags can be read, but no command is accepted until the device leaves the Limp home operation.

Data Sheet 14 Rev. 1.0, 2008-10-30

**Power Supply**

### 5.4 Electrical Characteristics

Unless otherwise specified:

$V_{\rm DD}$  = 3.0 V to 5.5V,  $V_{\rm BAT}$  = 9.0 V to 16V,  $T_{\rm j}$  = -40 °C to +150 °C

| Pos.   | Parameter                                             | Symbol                   | Limit Values |      |      | Unit | Test Conditions                                                                                    |

|--------|-------------------------------------------------------|--------------------------|--------------|------|------|------|----------------------------------------------------------------------------------------------------|

|        |                                                       |                          | min.         | typ. | max. |      |                                                                                                    |

| Powe   | r Supply $V_{ m bb}$                                  | •                        | •            |      | •    |      | •                                                                                                  |

| 5.4.1  | Supply voltage for full operation                     | $V_{bb}$                 | 9            | _    | 28   | V    |                                                                                                    |

| 5.4.2  | Under voltage reset threshold voltage                 | $V_{ m bb(UV)}$          | _            | -    | 5.5  | V    |                                                                                                    |

| 5.4.3  | Operating current                                     | $I_{\mathbb{S}}$         | _            | _    | 15   | mA   | V <sub>bb</sub> = 16 V                                                                             |

|        |                                                       |                          | _            | -    | 12   | mA   | $^{1)}$ $V_{\rm bb}$ = 16 V all diagnosis off                                                      |

| 5.4.4  | Sleep mode current with disconnected loads (stand by) | $I_{\mathrm{S(Sleep)}}$  | _            | _    | 10   | μΑ   | $V_{\text{bb}}$ = 16 V<br>$V_{\text{LHI}}$ = 0 V<br>AWK= 0<br>$T_{\text{i}}$ = 25 °C <sup>1)</sup> |

|        |                                                       |                          | _            | _    | 13   |      | $T_{\rm i}$ = 85 °C <sup>1)</sup>                                                                  |

|        |                                                       |                          | _            | _    | 20   |      | $T_{\rm i}$ = 150 °C                                                                               |

| Digita | I Power Supply $V_{	extsf{DD}}$                       |                          |              |      |      |      | <u> </u>                                                                                           |

| 5.4.5  | 1                                                     | $V_{DD}$                 | 3.0          | _    | 5.5  | V    |                                                                                                    |

| 5.4.6  | Under voltage reset threshold voltage                 | $V_{\rm DD(PO)}$         | -            | -    | 3.0  | V    |                                                                                                    |

| 5.4.7  | Logic supply current                                  | $I_{DD}$                 | _            | _    | 0.2  | mA   | $f_{ m SCLK}$ = 0 Hz $V_{ m CS}$ = 0 V AWK= 1 $V_{ m CS}$ = 0V                                     |

| 5.4.8  | Logic supply sleep mode current                       | $I_{\mathrm{DD(Sleep)}}$ | _            | _    | 20   | μΑ   | $V_{\text{CS}} = V_{\text{DD}}$<br>AWK = 0<br>$T_{\text{i}} = 25 ^{\circ}\text{C}^{1)}$            |

|        |                                                       |                          | _            | _    | 20   | -    | $T_{\rm i}$ = 85 °C <sup>1)</sup>                                                                  |

|        |                                                       |                          | _            | _    | 40   | -    | $T_{\rm i}$ = 150 °C                                                                               |

| Timin  | gs                                                    |                          | 1            |      |      | 1    | J                                                                                                  |

| 5.4.9  |                                                       | $t_{\rm wu(Sleep)}$      |              | _    | 200  | μs   | 1)                                                                                                 |

| 5.4.10 | $V_{ m bb}$ under voltage reset delay time            | $t_{\rm bb(UVR)}$        | _            | _    | 1    | μs   | 1)                                                                                                 |

| 5.4.11 |                                                       |                          | _            | _    | 1    | μs   | 1)                                                                                                 |

|        | ·                                                     | . , ,                    |              | -1   | т.   | Т    | I .                                                                                                |

<sup>1)</sup> Not subject to production test, specified by design.

Note: Characteristics show the deviation of parameter at the given supply voltage and junction temperature. Typical values show the typical parameters expected at  $V_{\rm bb}$  = 13.5 V,  $V_{\rm DD}$  = 5.0 V,  $T_{\rm j}$  = 25 °C.

## 6 Power Stages

The TLE7235E is an eight channel high-side and low-side relay switch. The power stages are built by N-channel vertical power MOSFET transistors. The gates of the high-side switches are controlled by charge pumps.

### 6.1 Input Circuit

There are two input pins available at TLE7235E, which can be configured to be used for control of the output stages. The INXn parameter of the input configuration register provide following possibilities:

- · channel is switched off

- · channel is switched according to signal level at input pin IN1

- · channel is switched according to signal level at input pin IN2

- · channel is switched on

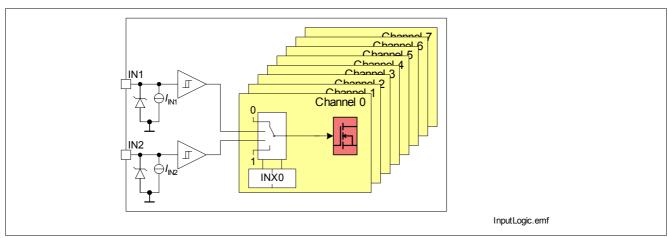

Figure 4 shows the input circuit of TLE7235E.

Figure 4 Input Multiplexer

The current sink to ground ensures that the channels switch off in case of open input pin. The zener diode protects the input circuit against ESD pulses.

#### 6.2 Channels 4 and 5

The TLE7235E provides two auto-configuring high-side or low-side switches (channels 4 and 5). They adjust the diagnostic and protective functions according their potentials at drain and source automatically.

In high-side configuration, the load is connected between ground and source of the power transistors (S4 or S5). The drain of the power transistors (D4 and D5) can be connected to any potential between GND-pin potential and VBB-pin potential. When the drain is connected to VBB, the channel behave like the other high side channels. The drain can also be connected to a 5 V power supply and the source pin will be utilized as switched 5 V supply line.

In low-side configuration, the source of the power transistors are to be connected to GND.

The configuration can be chosen for each of these channels individually, so it is feasible to connect one channel in low-side and the other in high-side configuration.

### 6.3 Inductive Output Clamp

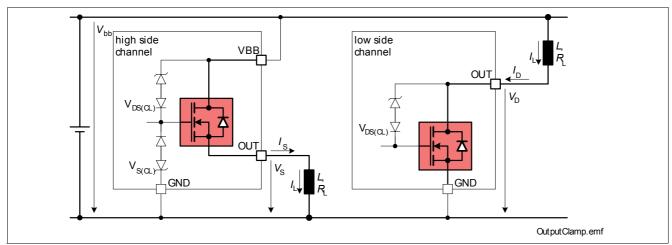

When switching off inductive loads with low-side switches, the potential at pin OUT rises to  $V_{\rm DS(CL)}$  potential, because the inductance intends to continue driving the current. For the high-side channels, the potential at pin OUT drops below ground potential to  $V_{\rm S(CL)}$ . The voltage clamping is necessary to prevent destruction of the device, see **Figure 5** for details. Nevertheless, the maximum allowed load inductance is limited by the max. clamping energy  $E_{\rm AR}$  see electrical characteristics " $E_{\rm AR}$ " on Page 10.

Figure 5 Output Clamp Implementation

#### **Maximum Load Inductance**

During demagnetization of inductive loads, energy has to be dissipated in the TLE7235E. This energy can be calculated with following equations:

$$E = V_{\text{D(CL)}} \cdot \left[ \frac{V_{\text{bb}} - V_{\text{D(CL)}}}{R_{\text{L}}} \cdot \ln \left( 1 - \frac{R_{\text{L}} \cdot I_{\text{L}}}{V_{\text{bb}} - V_{\text{D(CL)}}} \right) + I_{\text{L}} \right] \cdot \frac{L}{R_{\text{L}}}$$

Low-side (1)

$$E = (V_{\text{bb}} - V_{\text{S(CL)}}) \cdot \left[ \frac{V_{\text{S(CL)}}}{R_{\text{L}}} \cdot \ln \left( 1 - \frac{R_{\text{L}} \cdot I_{\text{L}}}{V_{\text{S(CL)}}} \right) + I_{\text{L}} \right] \cdot \frac{L}{R_{\text{L}}}$$

High-side (2)

These equations simplify under the assumption of  $R_1 = 0$ :

$$E = \frac{1}{2}LI_{L}^{2} \cdot \left(1 - \frac{V_{bb}}{V_{bb} - V_{D(CL)}}\right)$$

Low-side (3)

$$E = \frac{1}{2}LI_{L}^{2} \cdot \left(1 - \frac{V_{bb}}{V_{S(CL)}}\right)$$

High-side (4)

The maximum energy, which is converted into heat, is limited by the thermal design of the component.

## 6.4 Timing Diagrams

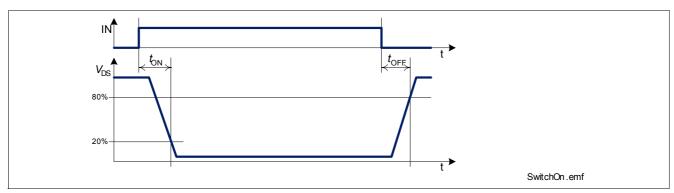

The power transistors are switched on and off with a dedicated slope via the INX bits of the serial peripheral interface (SPI). The switching times  $t_{ON}$  and  $t_{OFF}$  are designed equally.

Figure 6 Switching a Resistive Load

In input mode, a high signal at the input pin is equivalent to a SPI ON command and a low signal to SPI OFF command respectively. Please refer to **Section 9.3** for details on SPI protocol.

### 6.5 Electrical Characteristics

Unless otherwise specified:  $V_{\rm DD}$  = 3.0 V to 5.5V,  $V_{\rm BAT}$  = 9.0 V to 16V,  $T_{\rm j}$  = -40 °C to +150 °C typical values:  $V_{\rm DD}$  = 5.0 V,  $V_{\rm BAT}$  = 13.5 V,  $T_{\rm j}$  = 25 °C

| Pos.   | Parameter                                | Symbol                   | Li   | mit Val | ues  | Unit | <b>Test Conditions</b>                                                  |

|--------|------------------------------------------|--------------------------|------|---------|------|------|-------------------------------------------------------------------------|

|        |                                          |                          | min. | typ.    | max. |      |                                                                         |

| Outpu  | ut Characteristics                       | •                        |      |         |      | •    |                                                                         |

| 6.5.1  | On-State resistance                      | $R_{DS(ON)}$             |      |         |      | Ω    |                                                                         |

|        | channel 0, 1, 4, 5, 6, 7                 |                          | _    |         |      |      | $I_{\rm L}$ = 220 mA                                                    |

|        |                                          |                          |      | 0.9     | _    |      | <i>T</i> <sub>j</sub> = 25 °C                                           |

|        |                                          |                          | _    | 1.4     | 1.9  |      | <i>T</i> <sub>j</sub> = 150 °C                                          |

|        | channel 2, 3                             |                          | _    |         |      |      | $I_{\rm L}$ = 110 mA                                                    |

|        |                                          |                          |      | 1.6     | _    |      | $T_{\rm j}$ = 25 °C                                                     |

|        |                                          |                          | _    | 2.6     | 3.9  |      | $T_{\rm j}$ = 150 °C                                                    |

| 6.5.2  | Nominal load current                     | $I_{\mathrm{Out(nom)}}$  |      |         |      | mA   | all channels on                                                         |

|        |                                          |                          |      |         |      |      | $T_{\rm a}$ = 100 °C                                                    |

|        |                                          |                          |      |         |      |      | $T_{\rm j,max}$ = 150 °C based on $R_{\rm thia}$                        |

|        | channel 0, 1, 4, 5, 6, 7                 |                          | 350  | 500     |      |      | 1)                                                                      |

|        | channel 2, 3                             | _                        | 175  | 250     | _    |      | 1)                                                                      |

| 6.5.3  | Output leakage current in sleep mode     | I                        | 173  | 230     | _    | ^    | $V_{\rm DS}$ = 13.5 V                                                   |

| 0.5.5  | Output leakage current in sleep mode     | $I_{Out(Sleep)}$         | _    | _       | 1    | μΑ   | $T_{\rm DS} = 13.3 \text{ V}$<br>$T_{\rm i} = 25 ^{\circ}\text{C}^{1)}$ |

|        |                                          |                          | _    | _       | 2    |      | $T_{\rm i}$ = 85 °C <sup>1)</sup>                                       |

|        |                                          |                          | _    | _       | 5    |      | $T_{\rm i}$ = 150 °C                                                    |

| 6.5.4  | Output clamping voltage                  | $V_{OUT\_S(CL)}$         | _    | _       | -16  | V    | _                                                                       |

|        | o an part oran pring vortage             | $V_{\text{OUT\_DS(CL)}}$ | 41   | _       | _    | V    | _                                                                       |

| Input  | Characteristics                          | , 001_D8(CL)             |      |         |      | ļ -  |                                                                         |

| 6.5.5  |                                          | $V_{IN(L)}$              | 0    | _       | 0.6  | V    | _                                                                       |

| 6.5.6  | '                                        | $V_{\text{IN(H)}}$       | 1.8  | _       | 5.5  | V    | _                                                                       |

| 6.5.7  | · ·                                      | $\Delta V_{IN}$          | _    | 0.1     | _    | V    | 1)                                                                      |

| 6.5.8  | 1 0 7 1                                  | $I_{IN(L)}$              | 1.5  | _       | _    | μΑ   | $V_{\rm IN}$ = 0.6 V <sup>1)</sup>                                      |

| 6.5.9  | H-input pull-down current through pin IN | I <sub>IN(H)</sub>       | 10   | 40      | 80   | μΑ   | $V_{\text{IN}} = 5 \text{ V}$                                           |

| Timin  | , ,                                      | IN(H)                    | . •  | 1.0     |      | po t | / IN G I                                                                |

|        | Turn-on time                             | $t_{\sf ON}$             |      |         |      | μs   | $V_{\rm bb}$ = 13.5 V                                                   |

|        | $V_{\rm DS}$ = 20% $V_{\rm bat}$         | FOIN                     |      |         |      |      | resistive load                                                          |

|        | channel 0, 1,4,5                         |                          | _    | _       | 100  |      | $I_{\rm DS}$ = 250 mA                                                   |

|        | channel 2, 3                             |                          | _    | _       | 100  |      | I <sub>DS</sub> = 120 mA                                                |

|        | channel 6,7                              |                          | _    | _       | 100  |      | $I_{\rm DS}$ = 250 mA                                                   |

| 6.5.11 | ,                                        | $t_{OFF}$                |      |         |      | μs   | $V_{\rm bb}$ = 13.5 V                                                   |

|        | $V_{\rm DS}$ = 80% $V_{\rm bb}$          | OFF                      |      |         |      |      | resistive load                                                          |

|        | channel 0, 1, 4, 5                       |                          | _    | _       | 100  |      | $I_{\rm DS}$ = 250 mA                                                   |

|        | channel 2, 3 (HS)                        |                          | _    | _       | 100  | 1    | $I_{\rm DS}$ = 120 mA                                                   |

|        | channel 6, 7 (LS)                        |                          | _    | _       | 100  | 1    | $I_{\rm DS}$ = 250 mA                                                   |

<sup>1)</sup> Not subject to production test, specified by design.

## 6.6 Command Description

### **Input Configuration Registers**

| ICR01 | 000 <sub>B</sub> |    |            |

|-------|------------------|----|------------|

| 3     | 2                | 1  | 0          |

|       | INX1             | IN | KO         |

|       | rw               | rv | V          |

| ICR23 | 001 <sub>B</sub> |    |            |

| 3     | 2                | 1  | 0          |

|       | INX3             | IN | <b>(</b> 2 |

|       | rw               | rv | V          |

| ICR45 | 010 <sub>B</sub> |    |            |

| 3     | 2                | 1  | 0          |

|       | INX5             | IN | <b>K</b> 4 |

|       | rw               | rv | V          |

| ICR67 | 011 <sub>B</sub> |    |            |

| 3     | 2                | 1  | 0          |

|       | INX7             | IN | <b>K</b> 6 |

|       | rw               | rv | V          |

| Field      | Bits         | Туре | Description                                                                                |

|------------|--------------|------|--------------------------------------------------------------------------------------------|

| INXn       | [3:2], [1:0] | rw   | Input Multiplexer Configuration Channel n                                                  |

| n = 7 to 0 |              |      | <ul><li>00 Channel n is switched off</li><li>01 Channel n is switched by input 1</li></ul> |

|            |              |      | <ul><li>10 Channel n is switched by input 2</li><li>11 Channel n is switched on</li></ul>  |

**Protection Functions**

#### 7 Protection Functions

The device provides embedded protective functions. Integrated protection functions are designed to prevent IC destruction under fault conditions described in this data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 7.1 Over Load Protection

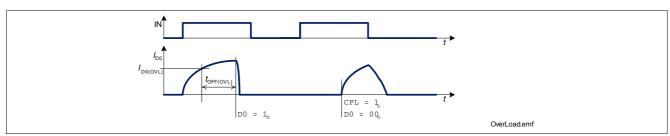

The TLE7235E is protected in case of over load or short circuit of the load. After time  $t_{\text{OFF}(\text{OVL})}$ , the over loaded channel n switches off and the according diagnosis flag Dn is set. The channel can be switched on after clearing the protection latch by command CMD.CPL = 1. The CPL command clears itself with the next valid SPI communication frame. Please refer to Figure 7 for details.

Figure 7 Shut Down at Over Load

### 7.2 Over Temperature Protection

A temperature sensor for each channel causes an overheated channel to switch off to prevent destruction. The according diagnosis flag is set. This flag is also set in OFF state, if the regarding channel temperature is too high. The channel can be only switched on after clearing the protection latch by SPI command CMD. CPL = 1. The CPL command clears itself with the next valid SPI communication frame. Please refer to "Diagnostic Features" on Page 23 for information on diagnosis features.

#### 7.3 ESD protection

There is a designed in protection against ESD disturbances up to the specified limit by using the defined model. Please see electrical characteristics "ESD susceptibility on all pins" on Page 11

#### 7.4 Reverse Polarity Protection

There is a reverse polarity protection implemented in the TLE7235E. This protection has to be divided into two parts. First the protection of the control circuits and second in the protection of the power transistors.

The control circuits are reverse polarity protected by protective measures in the ground connection. In case of reverse polarity, there is no current flow through the control circuits. The digital pins need serial resistors if the connected input stages are not floating to ground.

The power transistors contain intrinsic body diodes that cause power dissipation. The reverse current through these intrinsic body diodes has to be limited by the connected loads. The over temperature and over load protection are not active during reverse polarity.

### 7.5 Loss of $V_{\rm bh}$

In case of loss of  $V_{\rm bb}$  connection in on-state, all inductances of the loads have to be demagnetized through the ground connection or through an additional path from  $V_{\rm bb}$  to ground. Then for example, a diode (see D2 in Figure 14 "Application Diagram" on Page 35) can be placed.

**Protection Functions**

#### 7.6 **Electrical Characteristics**

Unless otherwise specified:

$V_{\rm DD}$  = 3.0 V to 5.5V,  $V_{\rm BAT}$  = 9.0 V to 16V,  $T_{\rm j}$  = -40 °C to +150 °C typical values:  $V_{\rm DD}$  = 5.0 V,  $V_{\rm BAT}$  = 13.5 V,  $T_{\rm j}$  = 25 °C

| Pos.  | Parameter                                          | Symbol                           | L    | imit Val          | ues  | Unit | <b>Test Conditions</b> |

|-------|----------------------------------------------------|----------------------------------|------|-------------------|------|------|------------------------|

|       |                                                    |                                  | min. | typ.              | max. |      |                        |

| Over  | Load Protection                                    | 1                                |      |                   |      | •    |                        |

| 7.6.1 | Over load detection current at channel 0,1,4,5,6,7 | $I_{\mathrm{Out}(\mathrm{OVL})}$ | 0.5  |                   | 1.0  | А    |                        |

| 7.6.2 | Over load detection current at channel 2,3         | $I_{\mathrm{Out}(\mathrm{OVL})}$ | 0.22 |                   | 0.5  | Α    |                        |

| 7.6.3 | Over load shut-down delay time                     | $t_{OFF(OVL)}$                   |      |                   | 60   | μs   |                        |

| Over  | Temperature Protection                             |                                  |      |                   |      |      |                        |

| 7.6.4 | Thermal shut down temperature                      | $T_{i(SC)}$                      | 150  | 170 <sup>1)</sup> |      | °C   |                        |

<sup>1)</sup> Not subject to production test, specified by design

## 8 Diagnostic Features

The SPI of TLE7235E provides diagnosis information about the device and about the load. The diagnosis information of the protective functions of channel n is latched in the diagnosis flags Dn. It is cleared by the SPI command CMD.CPL = 1. The CPL command clears itself with the next valid SPI communication frame.

The open load diagnosis of channel n is latched in the diagnosis flag OLn. This flag is cleared by reading the according diagnosis register.

Following table shows possible failure modes and the according protective and diagnostic action.

| Failure Mode                 | Comment                                                                                                                                                                                                                                                                         |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open Load                    | Diagnosis, when channel n is switched on: none Diagnosis, when channel n is switched off: according to voltage level at the output pin, flag $OLn$ is set after time $t_{d(OL)}$ . A diagnosis current can be enabled by SPI command $DCCR.DCENn = 1$ .                         |

| Over Temperature             | When over temperature occurs, the according diagnosis flag $\mathtt{Dn}$ is set. If the affected channel $\mathtt{n}$ was active it is switched off. The diagnosis flags are latched until they have been cleared by SPI command $\mathtt{CMD}.\mathtt{CPL} = 1$ .              |

| Over Load<br>(Short Circuit) | When over load is detected at channel $n$ , the affected channel is switched off after time $t_{OFF(OVL)}$ and the dedicated diagnosis flag $\mathtt{D}n$ is set. The diagnosis flags are latched until they have been cleared by SPI command $\mathtt{CMD}.\mathtt{CPL} = 1$ . |

#### 8.1 **Electrical Characteristics**

Unless otherwise specified:

$V_{\rm DD}$  = 3.0 V to 5.5V,  $V_{\rm BAT}$  = 9.0 V to 16V,  $T_{\rm j}$  = -40 °C to +150 °C typical values:  $V_{\rm BAT}$  = 13.5 V,  $V_{\rm DD}$  = 5.0 V,  $T_{\rm j}$  = 25 °C

| Parameter                                                                   | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Limit Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           | Uni | Test Conditions                                         |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------|--|

|                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | in. typ. max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                           | t   |                                                         |  |

| tate Diagnosis                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |     |                                                         |  |

| Open load diagnosis delay time                                              | $t_{\sf d(OL)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 250                                                                                                       | μs  | _                                                       |  |

| ide Channels 0,1,2,3                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |     |                                                         |  |