# **TLE94103EP**

#### Features

- Three half bridge power outputs

- Very low power consumption in sleep mode

- 3.3V / 5V compatible inputs with hysteresis

- · All outputs with overload and short circuit protection

- Independently diagnosable outputs (overcurrent, open load)

- Open load diagnostics in ON-state for all high-side and low-side

- 16-bit Standard SPI interface with daisy chain and in-frame response capability for control and diagnosis

- Fast diagnosis with the global error flag

- Overtemperature pre-warning and protection

- Over- and Undervoltage lockout

- Cross-current protection

#### **Potential applications**

- HVAC Flap DC motors

- Monostable and bistable relays

- Side mirror x-y adjustment

#### **Product validation**

Qualified for Automotive Applications. Product Validation according to AEC-Q100

### Description

The TLE94103EP is a protected triple half-bridge driver designed especially for automotive motion control applications such as side mirror x-y adjustment. It is part of a larger family offering half-bridge drivers from three outputs to twelve outputs with direct interface or SPI interface.

The half bridge drivers are designed to drive DC motor loads in sequential or parallel operation. Operation modes forward (cw), reverse (ccw), brake and high impedance are controlled from a 16-bit SPI interface. It offers diagnosis features such as short circuit, open load, power supply failure and overtemperature detection. In combination with its low quiescent current, this device is attractive among others for automotive applications. The small fine pitch exposed pad package, PG-TSDSO-14, provides good thermal performance and reduces PCB-board space and costs.

| Туре       | Package     | Marking  |

|------------|-------------|----------|

| TLE94103EP | PG-TSDSO-14 | TLE94103 |

#### Table 1Product Summary

| Operating Voltage                                        | Vs                               | 5.5 20 V    |

|----------------------------------------------------------|----------------------------------|-------------|

| Logic Supply Voltage                                     | V <sub>DD</sub>                  | 3.0 5.5 V   |

| Maximum Supply Voltage for Load Dump<br>Protection       | V <sub>S(LD)</sub>               | 40 V        |

| Minimum Overcurrent Threshold                            | I <sub>SD</sub>                  | 0.9 A       |

| Maximum On-State Path Resistance at $T_j = 150^{\circ}C$ | R <sub>DSON(total)_HSx+LSy</sub> | 1.8 + 1.8 Ω |

| Typical Quiescent Current at T <sub>j</sub> = 85°C       | I <sub>sQ</sub>                  | 0.1 μΑ      |

| Maximum SPI Access Frequency                             | f <sub>sclk</sub>                | 5 MHz       |

# **Table of Contents**

| <b>1</b><br>1.1<br>1.2                                                                                 | Pin Configuration                                                                                                                                                                                                                                                                                                                                                                            | 5                                                                    |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| <b>2</b><br>2.1                                                                                        | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

| <b>3</b><br>3.1<br>3.2<br>3.3<br>3.4                                                                   | General Product Characteristics                                                                                                                                                                                                                                                                                                                                                              | 9<br>11<br>12                                                        |

| 4                                                                                                      | Characterization results                                                                                                                                                                                                                                                                                                                                                                     | 18                                                                   |

| <b>5</b><br>5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.3<br>5.4                                                 | General Description                                                                                                                                                                                                                                                                                                                                                                          | 23<br>23<br>23<br>23<br>23<br>24                                     |

| <b>6</b><br>6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.4.1<br>6.2.4.2<br>6.2.4.3<br>6.2.5   | Half-Bridge Outputs         Functional Description         Protection & Diagnosis         Short Circuit of Output to Supply or Ground         Cross-Current         Temperature Monitoring         Overvoltage and undervoltage shutdown         V <sub>S</sub> Undervoltage         V <sub>S</sub> Overvoltage         V <sub>DD</sub> Undervoltage         Open Load                       | 25<br>26<br>28<br>30<br>32<br>33<br>33<br>33<br>33<br>33             |

| <b>7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.1.3<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.6.1<br>7.7<br>7.7.1 | Serial Peripheral Interface (SPI)<br>SPI Description<br>Global Error Flag<br>Global Status Register<br>SPI protocol error detection<br>SPI with independent slave configuration<br>Daisy chain operation<br>Status register change during SPI communication<br>SPI Bit Mapping<br>SPI Control Registers<br>Control register definition<br>SPI Status Registers<br>Status register definition | 35<br>36<br>37<br>38<br>40<br>42<br>44<br>47<br>49<br>50<br>54<br>55 |

| <b>8</b><br>8.1                                                                                        | Application Information                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| 8.2 | Thermal application information | 60 |

|-----|---------------------------------|----|

| 8.3 | EMC Enhancement                 | 61 |

|     |                                 |    |

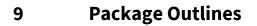

| 9   | Package Outlines                | 62 |

**Pin Configuration**

## **1** Pin Configuration

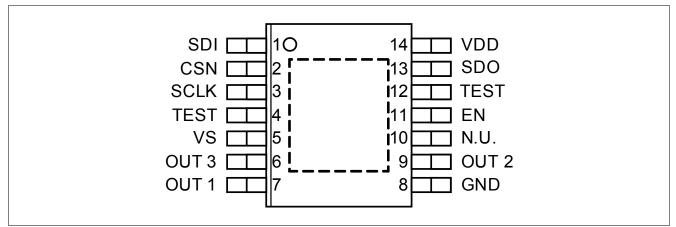

#### 1.1 Pin Assignment

Figure 1 Pin Configuration TLE94103EP with SPI interface

#### 1.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                                                                          |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SDI    | Serial data input with internal pull down                                                                                                         |

| 2   | CSN    | Chip select Not input with internal pull up                                                                                                       |

| 3   | SCLK   | Serial clock input with internal pull down                                                                                                        |

| 4   | TEST   | Test input. This pin can be left open or be terminated to ground.                                                                                 |

| 5   | VS     | Main supply voltage for power half bridges.                                                                                                       |

| 6   | OUT 3  | Power half-bridge 3                                                                                                                               |

| 7   | OUT 1  | Power half-bridge 1                                                                                                                               |

| 8   | GND    | Ground                                                                                                                                            |

| 9   | OUT 2  | Power half-bridge 2                                                                                                                               |

| 10  | N.U.   | Not used. This pin should be left open or terminated to GND.                                                                                      |

| 11  | EN     | Enable with internal pull-down; Places device in standby mode by pulling the EN line Low                                                          |

| 12  | TEST   | Test pin. This pin must be terminated to ground.                                                                                                  |

| 13  | SDO    | Serial data output                                                                                                                                |

| 14  | VDD    | Logic supply voltage                                                                                                                              |

| EDP | -      | Exposed Die Pad; For cooling and EMC purposes only - not usable as electrical ground. Electrical ground must be provided by pins 8. <sup>1)</sup> |

1) The exposed die pad at the bottom of the package allows better heat dissipation from the device via the PCB. The exposed pad (EP) must be either left open or connected to GND. It is recommended to connect EP to GND for best EMC and thermal performance.

#### **Pin Configuration**

Note: Not used (N.U.) pins and unused outputs are recommended to be left unconnected (open) on the application board. If N.U. pins or unused output pins are routed to an external connector which leaves the PCB, then these outputs should have provision for a zero ohm jumper (depopulated if unused) or ESD protection. In other words, they should be treated like used pins.

#### Block Diagram

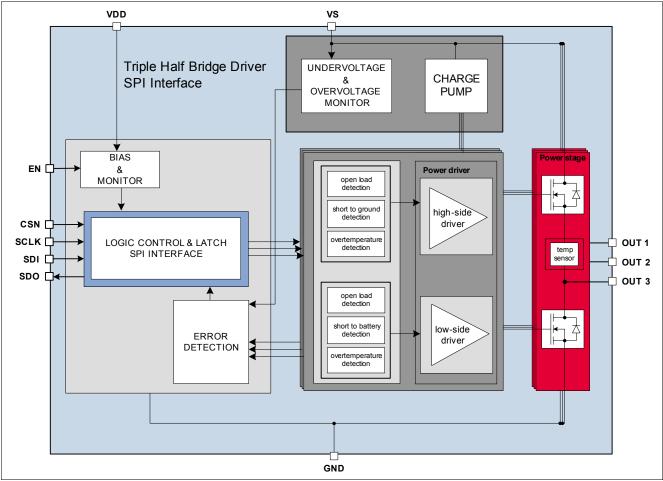

# 2 Block Diagram

Figure 2 Block Diagram TLE94103EP (SPI Interface)

#### **Block Diagram**

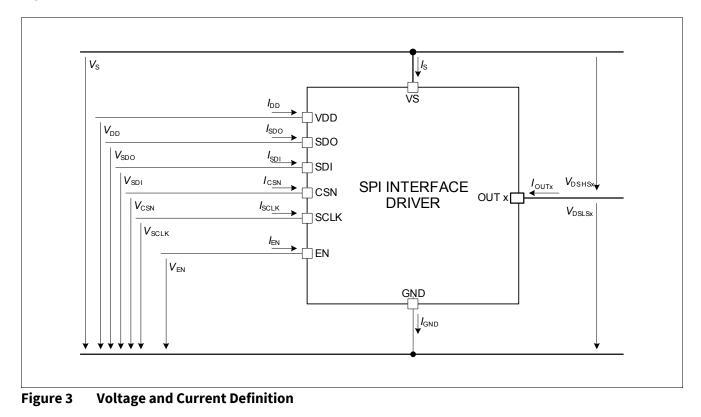

#### 2.1 Voltage and current definition

Figure 3 shows terms used in this datasheet, with associated convention for positive values.

# 3 General Product Characteristics

#### 3.1 Absolute Maximum Ratings

#### Table 2 Absolute Maximum Ratings<sup>1)</sup> $T_i = -40^{\circ}$ C to +150°C

| Parameter                                                                | Symbol                                                                          |      | Value | s    | Unit | Note or<br>Test Condition                                   | Number       |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|-------|------|------|-------------------------------------------------------------|--------------|

|                                                                          |                                                                                 | Min. | Тур.  | Max. |      |                                                             |              |

| Voltages                                                                 | 1                                                                               | -    |       |      |      |                                                             | U            |

| Supply voltage                                                           | Vs                                                                              | -0.3 | -     | 40   | V    |                                                             | P_4.1.1      |

| Supply Voltage Slew Rate                                                 | dV₅∕dt                                                                          | -    | -     | 10   | V/µs | V <sub>s</sub> increasing and decreasing <sup>1)</sup>      | P_4.2.2      |

| Power half-bridge output voltage                                         | V <sub>OUT</sub>                                                                | -0.3 | -     | 40   | V    | $0 V < V_{OUT} < V_{S}^{2}$                                 | P_4.1.2      |

| Logic supply voltage                                                     | V <sub>DD</sub>                                                                 | -0.3 | -     | 5.5  | V    | 0 V < V <sub>S</sub> < 40 V                                 | P_4.1.3      |

| Logic input voltages<br>(SDI, SCLK, CSN, EN)                             | V <sub>SDI</sub> ,<br>V <sub>SCLK</sub> ,<br>V <sub>CSN</sub> , V <sub>EN</sub> | -0.3 | -     | VDD  | V    | 0 V < V <sub>S</sub> < 40 V<br>0 V < V <sub>DD</sub> < 5.5V | P_4.1.4      |

| Logic output voltage<br>(SDO)                                            | V <sub>SDO</sub>                                                                | -0.3 | -     | VDD  | V    | $0 V < V_{S} < 40 V$<br>$0 V < V_{DD} < 5.5V$               | P_4.1.5      |

| Test pins                                                                | V <sub>TEST</sub>                                                               | -0.3 | -     | VDD  | V    | $0 V < V_{S} < 40 V$<br>$0 V < V_{DD} < 5.5V$               | P_4.1.19     |

| Currents                                                                 | 1                                                                               | ł    | 1     | 1    |      |                                                             | - <b>I</b> L |

| Continuous Supply Current for V <sub>S</sub>                             | I <sub>s</sub>                                                                  | 0    | -     | 1.5  | А    | -                                                           | P_4.1.20     |

| Current per GND pin                                                      | I <sub>GND</sub>                                                                | 0    | _     | 2.0  | А    | -                                                           | P_4.1.14     |

| Output Currents                                                          | I <sub>OUT</sub>                                                                | -2.0 | -     | 2.0  | А    | -                                                           | P_4.1.15     |

| Temperatures                                                             |                                                                                 |      |       |      |      |                                                             |              |

| Junction temperature                                                     | T <sub>j</sub>                                                                  | -40  | -     | 150  | °C   | -                                                           | P_4.1.8      |

| Storage temperature                                                      | T <sub>stg</sub>                                                                | -50  | -     | 150  | °C   | -                                                           | P_4.1.9      |

| ESD Susceptibility                                                       |                                                                                 |      |       |      |      |                                                             |              |

| ESD susceptibility OUTn and VS pins versus GND. All other pins grounded. | V <sub>ESD</sub>                                                                | -4   | -     | 4    | kV   | JEDEC HBM <sup>1)3)</sup>                                   | P_4.1.10     |

| ESD susceptibility all pins                                              | V <sub>ESD</sub>                                                                | -2   | -     | 2    | kV   | JEDEC HBM <sup>1)3)</sup>                                   | P_4.1.11     |

| ESD susceptibility all pins                                              | V <sub>ESD</sub>                                                                | -500 | _     | 500  | V    | CDM <sup>1)4)</sup>                                         | P_4.1.12     |

| ESD susceptibility corner pins                                           | V <sub>ESD</sub>                                                                | -750 | _     | 750  | V    | CDM <sup>1)4)</sup>                                         | P_4.1.13     |

1) Not subject to production test, specified by design

2) Also applicable to not used (N.U.) pins

3) ESD susceptibility, "JEDEC HBM" according to ANSI/ ESDA/ JEDEC JS001 (1.5 k $\Omega$ , 100pF)

4) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101

#### Notes

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 3.2 Functional Range

#### Table 3Functional Range

| Parameter                                       | Symbol                                                                          | Values |      |      | Unit | Note or               | Number  |

|-------------------------------------------------|---------------------------------------------------------------------------------|--------|------|------|------|-----------------------|---------|

|                                                 |                                                                                 | Min.   | Тур. | Max. |      | <b>Test Condition</b> |         |

| Supply voltage range for normal operation       | V <sub>S(nor)</sub>                                                             | 5.5    | -    | 20   | V    | -                     | P_4.2.1 |

| Logic supply voltage range for normal operation | V <sub>DD</sub>                                                                 | 3.0    | -    | 5.5  | V    | -                     | P_4.2.3 |

| Logic input voltages<br>(SDI, SCLK, CSN, EN)    | V <sub>SDI</sub> ,<br>V <sub>SCLK</sub> ,<br>V <sub>CSN</sub> , V <sub>EN</sub> | -0.3   | -    | 5.5  | V    | -                     | P_4.2.4 |

| Junction temperature                            | Tj                                                                              | -40    | -    | 150  | °C   |                       | P_4.2.5 |

*Note:* Within the normal functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

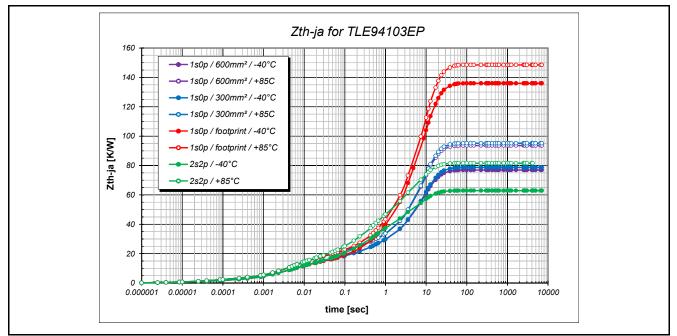

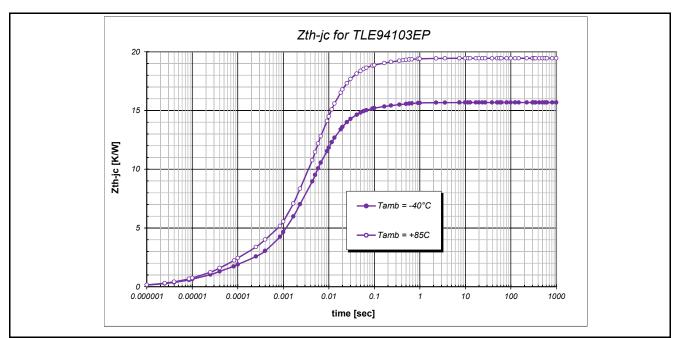

#### 3.3 Thermal Resistance

| Parameter                                                              | Symbol                   |      | Values | 5    | Unit | Note or<br>Test Condition | Number |

|------------------------------------------------------------------------|--------------------------|------|--------|------|------|---------------------------|--------|

|                                                                        |                          | Min. | Тур.   | Max. |      |                           |        |

| Junction to Case, $T_A = -40^{\circ}$ C                                | R <sub>thjC_cold</sub>   | -    | 16     | -    | K/W  | 1)                        |        |

| Junction to Case, $T_A = 85^{\circ}C$                                  | R <sub>thjC_hot</sub>    | -    | 19     | -    | K/W  | 1)                        |        |

| Junction to ambient, $T_A = -40^{\circ}C$<br>(1s0p, minimal footprint) | R <sub>thjA_cold_</sub>  | -    | 136    | -    | K/W  | 1) 2)                     |        |

| Junction to ambient, $T_A = 85^{\circ}C$ (1s0p, minimal footprint)     | R <sub>thjA_hot_m</sub>  | -    | 148    | -    | K/W  | 1) 2)                     |        |

| Junction to ambient, $T_A = -40^{\circ}C$<br>(1s0p, 300mm2 Cu)         | R <sub>thjA_cold_3</sub> | -    | 79     | -    | K/W  | 1) 3)                     |        |

| Junction to ambient, $T_A = 85^{\circ}C$<br>(1s0p, 300mm2 Cu)          | R <sub>thjA_hot_30</sub> | -    | 95     | -    | K/W  | 1) 3)                     |        |

| Junction to ambient, $T_A = -40^{\circ}C$<br>(1s0p, 600mm2 Cu)         | R <sub>thjA_cold_6</sub> | -    | 77     | -    | K/W  | 1) 4)                     |        |

| Junction to ambient, $T_A = 85^{\circ}C$<br>(1s0p, 600mm2 Cu)          | R <sub>thjA_hot_60</sub> | -    | 94     | -    | K/W  | 1) 4)                     |        |

| Junction to ambient, $T_A = -40^{\circ}C$ (2s2p)                       | R <sub>thjA_cold_2</sub> | -    | 63     | -    | K/W  | 1) 5)                     |        |

| Junction to ambient, $T_A = 85^{\circ}C$ (2s2p)                        | R <sub>thjA_hot_2s</sub> | -    | 82     | -    | K/W  | 1) 5)                     |        |

#### Table 4 Thermal Resistance TLE94103EP

1) Not subject to production test, specified by design.

Specified R<sub>thJA</sub> value is according to JEDEC JESD51-2, -3 at natural convection on FR4 1s0p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with minimal footprint copper area and 35µm thickness. Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

- 3) Specified R<sub>thJA</sub> value is according to JEDEC JESD51-2, -3 at natural convection on FR4 1s0p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with additional cooling of 300mm2 copper area and 35μm thickness. Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

- 4) Specified R<sub>thJA</sub> value is according to JEDEC JESD51-2, -3 at natural convection on FR4 1s0p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with additional cooling of 600mm2 copper area and 35μm thickness. Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

- 5) Specified R<sub>thJA</sub> value is according to JEDEC JESD51-2, -3 at natural convection on FR4 2s2p board; The product (chip + package) was simulated on a 76.2 x 114.3 x 1.5mm board with two inner copper layers (4 x 35µm Cu). Ta = -40°C, each channel dissipates 0.2W. Ta = 85°C, each channel dissipates 0.135W.

#### 3.4 Electrical Characteristics

# Table 5Electrical Characteristics, $V_s = 5.5 V$ to 20 V, $V_{DD} = 3.0V$ to 5.5V, $T_j = -40^{\circ}$ C to $+150^{\circ}$ C, EN= HIGH,<br/> $I_{OUTn} = 0 A$ ; Typical values refer to $V_{DD} = 5.0 V$ , $V_s = 13.5 V$ and $T_J = 25^{\circ}$ C unless otherwise<br/>specified; all voltages with respect to ground, positive current flowing into pin (unless<br/>otherwise specified)

| Parameter                                                | Symbol                              |          | Value   | 5    | Unit | Note or<br>Test Condition                                  | Number    |

|----------------------------------------------------------|-------------------------------------|----------|---------|------|------|------------------------------------------------------------|-----------|

|                                                          |                                     | Min.     | Тур.    | Max. | 1    |                                                            |           |

| Current Consumption, EN = GN                             | ID                                  | l        | - 1     | 4    | - I  |                                                            | 1         |

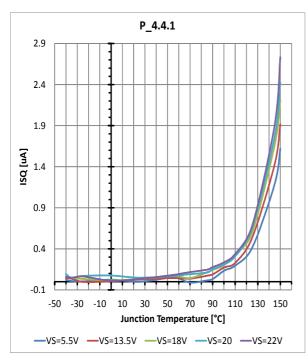

| Supply Quiescent current                                 | I <sub>SQ</sub>                     | _        | 0.1     | 2    | μA   | $-40^{\circ}\text{C} \le T_{j} \le 85^{\circ}\text{C}$     | P_4.4.1   |

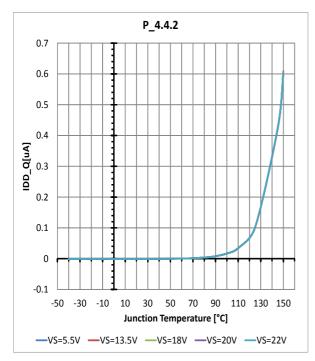

| Logic supply quiescent current                           | I <sub>DD_Q</sub>                   | -        | 0.1     | 1    | μA   | $-40^{\circ}C \le T_j \le 85^{\circ}C$                     | P_4.4.2   |

| Total quiescent current                                  | $I_{SQ} + I_{DD_Q}$                 | -        | 0.6     | 3    | μA   | $-40^{\circ}C \le T_j \le 85^{\circ}C$                     | P_4.4.3   |

| Current Consumption, EN=HIG                              | Н                                   |          |         |      |      |                                                            |           |

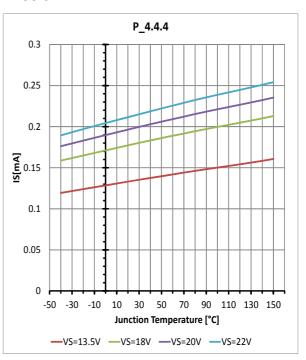

| Supply current                                           | I <sub>S</sub>                      | -        | 0.13    | 0.5  | mA   | Power drivers and<br>power stages are<br>off               | P_4.4.4   |

| Supply current                                           | I <sub>S_HSON</sub>                 | -        | 1.5     | 3    | mA   | All high-sides ON <sup>1)2)</sup>                          | P_4.4.101 |

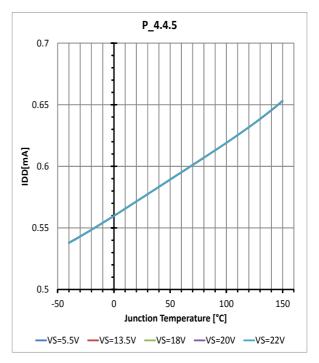

| Logic supply current                                     | I <sub>DD</sub>                     | -        | 0.6     | 2.5  | mA   | SPI not active                                             | P_4.4.5   |

| Logic supply current                                     | I <sub>DD_RUN</sub>                 | -        | 2.5     | -    | mA   | SPI 5MHz <sup>2)</sup>                                     | P_4.4.6   |

| Total supply current                                     | I <sub>S</sub> +I <sub>DD_RUN</sub> | -        | 2.7     | _    | mA   | SPI 5MHz <sup>2)</sup>                                     | P_4.4.7   |

| Over- and Undervoltage Locko                             |                                     |          |         |      |      |                                                            |           |

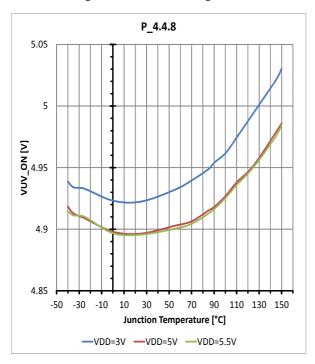

| Undervoltage Switch ON voltage threshold                 | V <sub>UV ON</sub>                  | 4.4      | 4.90    | 5.3  | V    | V <sub>s</sub> increasing                                  | P_4.4.8   |

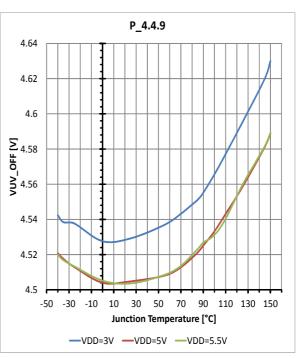

| Undervoltage Switch OFF voltage threshold                | V <sub>UV OFF</sub>                 | 4        | 4.50    | 4.9  | V    | V <sub>s</sub> decreasing                                  | P_4.4.9   |

| Undervoltage Switch ON/OFF<br>hysteresis                 | V <sub>UV HY</sub>                  | -        | 0.40    | -    | V    | $V_{\rm UVON}$ - $V_{\rm UVOFF}^{2)}$                      | P_4.4.10  |

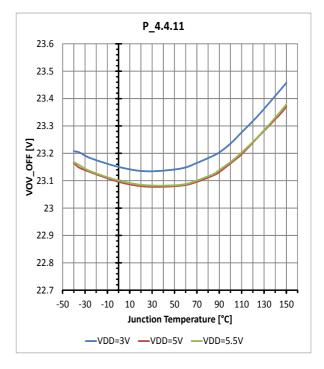

| Overvoltage Switch OFF voltage threshold                 | V <sub>OV OFF</sub>                 | 21       | 23      | 25   | V    | V <sub>s</sub> increasing                                  | P_4.4.11  |

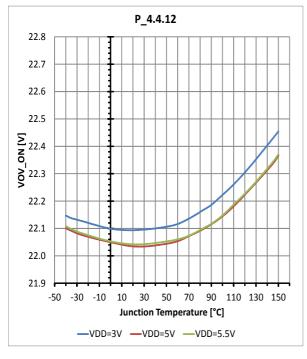

| Overvoltage Switch ON voltage threshold                  | V <sub>OV ON</sub>                  | 20       | 22      | 24   | V    | V <sub>s</sub> decreasing                                  | P_4.4.12  |

| Overvoltage Switch ON/OFF<br>hysteresis                  | V <sub>OV HY</sub>                  | -        | 1       | -    | V    | $V_{\rm OVOFF}$ - $V_{\rm OVON}^{2)}$                      | P_4.4.13  |

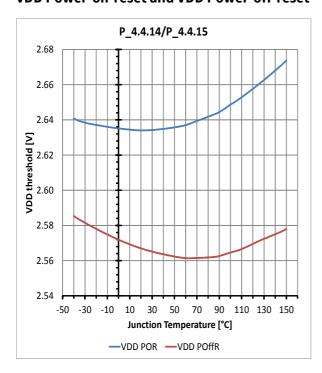

| V <sub>DD</sub> Power-On-Reset                           | V <sub>DD POR</sub>                 | 2.40     | 2.63    | 2.90 | V    | V <sub>DD</sub> increasing                                 | P_4.4.14  |

| V <sub>DD</sub> Power-Off-Reset                          | V <sub>DD POffR</sub>               | 2.35     | 2.57    | 2.85 | V    | V <sub>DD</sub> decreasing                                 | P_4.4.15  |

| V <sub>DD</sub> Power ON/OFF hysteresis                  | V <sub>DD POR HY</sub>              | -        | 0.06    | -    | V    | $V_{\rm DD POR}$ - $V_{\rm DD POffR}^{2)}$                 | P_4.4.98  |

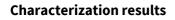

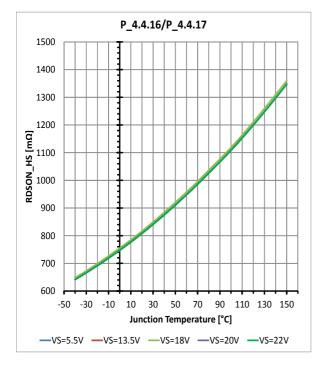

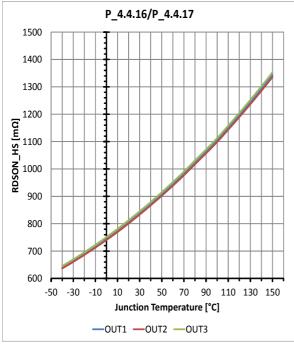

| Static Drain-source ON-Resista                           |                                     | ide or L | .ow-Sid | e)   |      |                                                            |           |

| High-Side or Low-Side R <sub>DSON</sub><br>(all outputs) | R <sub>DSON_HB_25C</sub>            | -        | 825     | 1200 | mΩ   | I <sub>OUT</sub> = ±0.5 A;<br>T <sub>i</sub> = 25 °C       | P_4.4.16  |

| High-Side or Low-Side R <sub>DSON</sub><br>(all outputs) | R <sub>DSON_HB_150</sub>            | -        | 1350    | 1800 | mΩ   | $I_{OUT} = \pm 0.5 \text{ A};$<br>$T_{i} = 150 \text{ °C}$ | P_4.4.17  |

Table 5Electrical Characteristics,  $V_s = 5.5 V \text{ to } 20 V$ ,  $V_{DD} = 3.0V \text{ to } 5.5V$ ,  $T_j = -40^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ , EN= HIGH,<br/> $I_{OUTn} = 0 \text{ A}$ ; Typical values refer to  $V_{DD} = 5.0 V$ ,  $V_s = 13.5 V$  and  $T_J = 25^{\circ}\text{C}$  unless otherwise<br/>specified; all voltages with respect to ground, positive current flowing into pin (unless<br/>otherwise specified) (cont'd)

| Parameter                                       | Symbol                                      | Values    |        |           | Unit     | Note or                                                                               | Number   |

|-------------------------------------------------|---------------------------------------------|-----------|--------|-----------|----------|---------------------------------------------------------------------------------------|----------|

|                                                 |                                             | Min.      | Тур.   | Max.      |          | <b>Test Condition</b>                                                                 |          |

| Output Protection and Diagnos                   | sis of high-s                               | ide (HS)  | chann  | els of ha | alf-brid | ge output                                                                             |          |

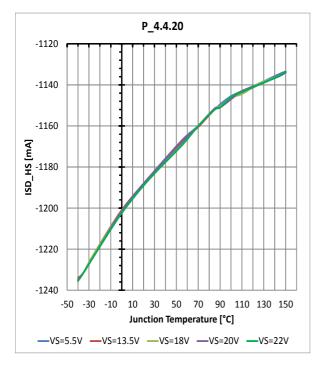

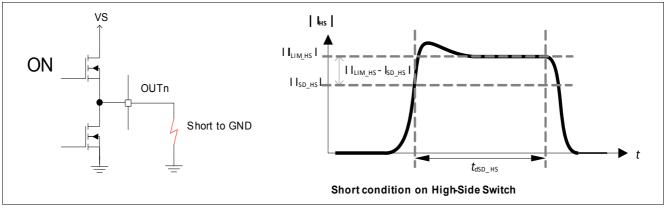

| HS Overcurrent Shutdown<br>Threshold            | I <sub>SD_HS</sub>                          | -1.5      | -1.2   | -0.9      | A        | See Figure 5                                                                          | P_4.4.20 |

| Difference between shutdown and limit current   | I <sub>LIM_HS</sub> -<br>I <sub>SD_HS</sub> | -1.2      | -0.6   | 0         | A        | $ I_{\text{LIM}_{\text{HS}}}  \ge  I_{\text{SD}_{\text{HS}}} $<br>See <b>Figure 5</b> | P_4.4.21 |

| Overcurrent Shutdown filter time                | $t_{\rm dSD_HS}$                            | 15        | 19     | 23        | μs       | 2)                                                                                    | P_4.4.22 |

| Open Load Detection Current                     | I <sub>OLD1_HS</sub>                        | -15       | -8     | -3        | mA       | -                                                                                     | P_4.4.23 |

| Open Load Detection filter time                 | t <sub>OLD1_HS</sub>                        | 2000      | 3000   | 4000      | μs       | 2)                                                                                    | P_4.4.24 |

| Output Protection and Diagnos                   |                                             | de (LS) d | channe | ls of hal | f-bridg  | e output                                                                              | 1        |

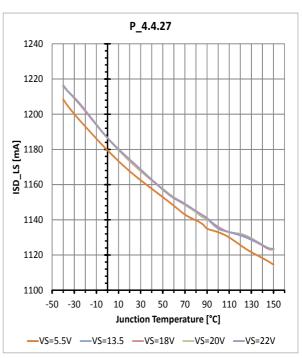

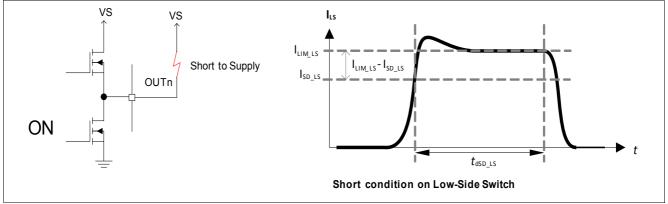

| LS Overcurrent Shutdown<br>Threshold            | I <sub>SD_LS</sub>                          | 0.9       | 1.2    | 1.5       | A        | See Figure 6                                                                          | P_4.4.27 |

| Difference between shutdown and limit current   | I <sub>LIM_LS</sub> -<br>I <sub>SD_LS</sub> | 0         | 0.6    | 1.2       | A        | <sup>2)</sup> $I_{\text{LIM}_{LS}} \ge I_{\text{SD}_{LS}}$<br>Figure 6                | P_4.4.28 |

| Overcurrent Shutdown filter time                | t <sub>dSD_LS</sub>                         | 15        | 19     | 23        | μs       | 2)                                                                                    | P_4.4.29 |

| Open Load Detection Current                     | I <sub>OLD_LS</sub>                         | 3         | 8      | 15        | mA       | -                                                                                     | P_4.4.30 |

| Open Load Detection filter time                 | t <sub>OLD_LS</sub>                         | 2000      | 3000   | 4000      | μs       | 2)                                                                                    | P_4.4.31 |

| Outputs OUT(1n) leakage cu                      |                                             | 4         | 1      | 1         | 1        |                                                                                       | 1        |

| HS leakage current in off state                 | I <sub>QLHn_NOR</sub>                       | -2        | -0.5   | -         | μA       | $V_{OUTn} = 0V$ ; EN=High                                                             | P_4.4.32 |

| HS leakage current in off state                 | I <sub>QLHn_SLE</sub>                       | -2        | -0.5   | -         | μA       | $V_{\rm OUTn}$ = 0V; EN=GND                                                           | P_4.4.33 |

| LS Leakage current in off state                 | I <sub>QLLn_NOR</sub>                       | -         | 0.5    | 2         | μΑ       | $V_{OUTn} = V_{S}$ ; EN=High                                                          | P_4.4.34 |

| LS Leakage current in off state                 | I <sub>QLLn_SLE</sub>                       | -         | 0.5    | 2         | μΑ       | $V_{\rm OUTn} = V_{\rm S}$ ; EN=GND                                                   | P_4.4.35 |

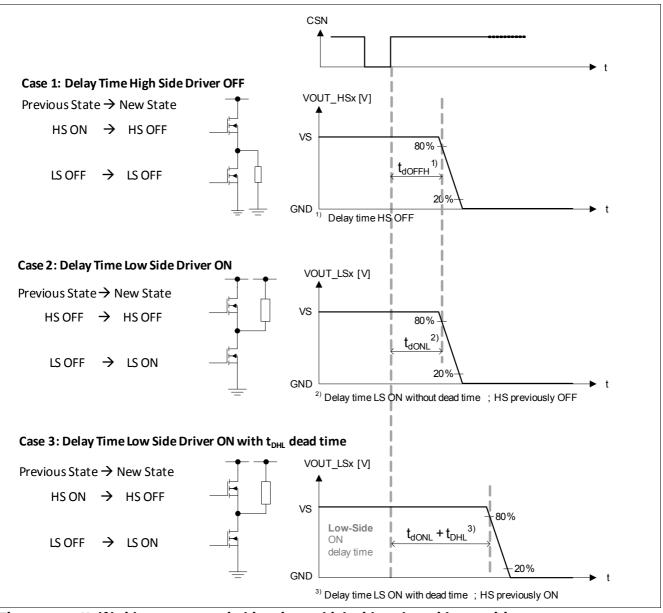

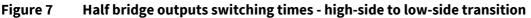

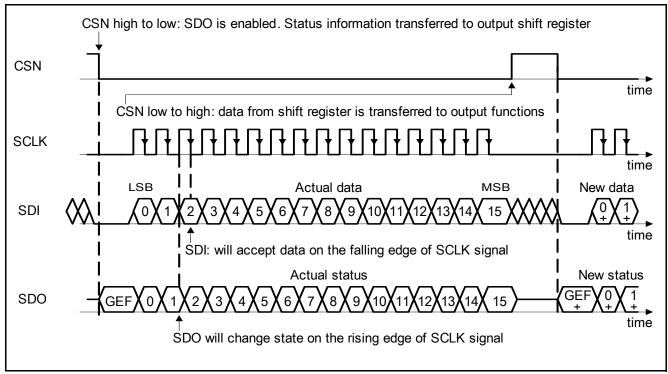

| Output Switching Times. See F                   | <mark>igure</mark> 7 and                    | Figure 8  | 3.     |           |          |                                                                                       |          |

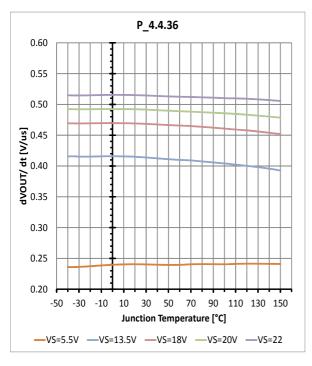

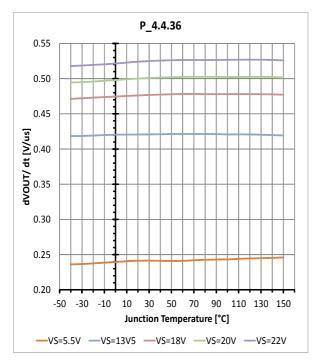

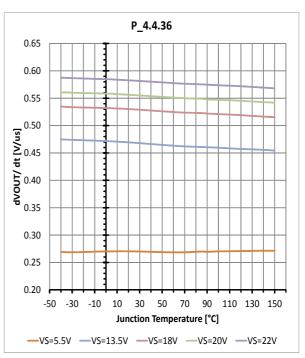

| Slew rate of high-side and low-<br>side outputs | d <sub>vout</sub> / dt                      | 0.1       | 0.45   | 0.75      | V/µs     | Resistive load = $100\Omega$ ; $V_{\rm S}$ =13.5V <sup>3)</sup>                       | P_4.4.36 |

| Output delay time high side<br>driver on        | t <sub>donh</sub>                           | 5         | 20     | 35        | μs       | Resistive load =<br>100Ω to GND                                                       | P_4.4.37 |

| Output delay time high side driver off          | t <sub>doffh</sub>                          | 15        | 45     | 75        | μs       | Resistive load =<br>100Ω to GND                                                       | P_4.4.38 |

| Output delay time low side driver on            | t <sub>donl</sub>                           | 5         | 20     | 35        | μs       | Resistive load =<br>100Ω to VS                                                        | P_4.4.39 |

| Output delay time low side driver off           | t <sub>doffl</sub>                          | 15        | 45     | 75        | μs       | Resistive load =<br>100Ω to VS                                                        | P_4.4.40 |

| Cross current protection time,<br>high to low   | t <sub>DHL</sub>                            | 100       | 130    | 160       | μs       | Resistive load = $100\Omega^{2}$                                                      | P_4.4.41 |

Table 5Electrical Characteristics,  $V_s = 5.5 V$  to 20 V,  $V_{DD} = 3.0V$  to 5.5V,  $T_j = -40^{\circ}$ C to  $+150^{\circ}$ C, EN= HIGH,<br/> $I_{OUTn} = 0$  A; Typical values refer to  $V_{DD} = 5.0 V$ ,  $V_s = 13.5 V$  and  $T_J = 25^{\circ}$ C unless otherwise<br/>specified; all voltages with respect to ground, positive current flowing into pin (unless<br/>otherwise specified) (cont'd)

| Parameter                                     | Symbol                                        | Values                      |                          | Unit                        | Note or | Number                                                           |              |

|-----------------------------------------------|-----------------------------------------------|-----------------------------|--------------------------|-----------------------------|---------|------------------------------------------------------------------|--------------|

|                                               |                                               | Min.                        | Тур.                     | Max.                        | _       | <b>Test Condition</b>                                            |              |

| Cross current protection time,<br>low to high | t <sub>DLH</sub>                              | 100                         | 130                      | 160                         | μs      | Resistive load = $100\Omega^{2}$                                 | P_4.4.42     |

| Input Interface: Logic Input El               | N                                             | ·                           | ·                        | ·                           |         |                                                                  |              |

| High-input voltage                            | V <sub>ENH</sub>                              | 0.7 *<br>V <sub>DD</sub>    | -                        | V <sub>DD</sub>             | V       | -                                                                | P_4.4.43     |

| Low-input voltage                             | V <sub>ENL</sub>                              | 0                           | -                        | 0.3 *<br>V <sub>DD</sub>    | V       | -                                                                | P_4.4.44     |

| Hysteresis of input voltage                   | V <sub>ENHY</sub>                             | _                           | 500                      | -                           | mV      | 2)                                                               | P_4.4.45     |

| Pull down resistor                            | R <sub>PD_EN</sub>                            | 20                          | 40                       | 70                          | kΩ      | $V_{\rm EN} = 0.2 \times V_{\rm DD}$                             | P_4.4.46     |

| SPI frequency                                 |                                               |                             | 1                        |                             |         |                                                                  | L            |

| Maximum SPI frequency                         | f <sub>SPI,max</sub>                          | -                           | -                        | 5.0                         | MHz     | 2) 4)                                                            | P_4.4.47     |

| SPI INTERFACE: Delay Time fr                  | om EN rising                                  | g edge to                   | first D                  | ata in                      |         |                                                                  | L            |

| Setup time                                    | t <sub>set</sub>                              | -                           | _                        | 150                         | μs      | <sup>2)</sup> See <b>Figure 12</b>                               | P_4.4.48     |

| SPI INTERFACE: Input Interfac                 |                                               | uts SDI,                    | SCLK, (                  | CSN                         | _       | 4                                                                | 1            |

| H-input voltage threshold                     | V <sub>IH</sub>                               | 0.7 *<br>V <sub>DD</sub>    | -                        | V <sub>DD</sub>             | V       | -                                                                | P_4.4.50     |

| L-input voltage threshold                     | V <sub>IL</sub>                               | 0                           | -                        | 0.3 *<br>V <sub>DD</sub>    | V       | -                                                                | P_4.4.51     |

| Hysteresis of input voltage                   | V <sub>IHY</sub>                              | _                           | 500                      | -                           | mV      | 2)                                                               | P_4.4.52     |

| Pull up resistor at pin CSN                   | R <sub>PU_CSN</sub>                           | 20                          | 40                       | 70                          | kΩ      | $V_{\rm CSN} = 0.7 \times V_{\rm DD}$                            | P_4.4.53     |

| Pull down resistor at pin SDI,<br>SCLK        | R <sub>PD_SDI</sub> ,<br>R <sub>PD_SCLK</sub> | 20                          | 40                       | 70                          | kΩ      | $V_{\text{SDI}}, V_{\text{SCLK}} = 0.2 \text{ x } V_{\text{DD}}$ | P_4.4.54     |

| Input capacitance at pin CSN,<br>SDI or SCLK  | C                                             | -                           | 10                       | 15                          | pF      | $0V < V_{DD} < 5.25V^{2}$                                        | P_4.4.55     |

| Input Interface, Logic Output                 | SDO                                           |                             |                          |                             |         |                                                                  | I            |

| H-output voltage level                        | V <sub>SDOH</sub>                             | V <sub>DD</sub> -<br>0.4    | V <sub>DD</sub> -<br>0.2 | V <sub>DD</sub>             | V       | I <sub>SDOH</sub> = -1.6 mA                                      | P_4.4.56     |

| L-output voltage level                        | V <sub>SDOL</sub>                             | 0                           | 0.2                      | 0.4                         | V       | I <sub>SDOL</sub> = 1.6 mA                                       | P_4.4.57     |

| Tri-state Leakage Current                     | I <sub>sdolk</sub>                            | -1                          | -                        | 1                           | μA      | $V_{\rm CSN} = V_{\rm DD};$<br>$0V < V_{\rm SDO} < V_{\rm DD}$   | P_4.4.58     |

| Tri-state input capacitance                   | C <sub>SDO</sub>                              | _                           | 10                       | 15                          | рF      | 2)                                                               | P_4.4.59     |

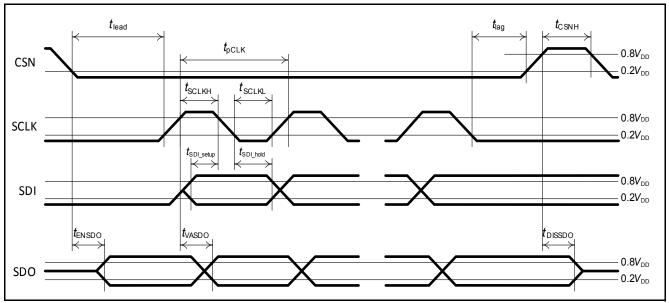

| Data Input Timing. See Figure                 |                                               | ıre 15.                     |                          |                             |         | 1                                                                | 1            |

| SCLK Period                                   | t <sub>pCLK</sub>                             | 200                         | _                        | _                           | ns      | 2)                                                               | P_4.4.60     |

| SCLK High Time                                |                                               | 0.45 *                      | -                        | 0.55 *                      | ns      | 2)                                                               | <br>P_4.4.61 |

| č                                             | JULINI                                        | t <sub>pCLK</sub>           |                          | t <sub>pCLK</sub>           |         |                                                                  |              |

| SCLK Low Time                                 | t <sub>sclkl</sub>                            | 0.45 *<br>t <sub>pCLK</sub> | -                        | 0.55 *<br>t <sub>рСLK</sub> | ns      | 2)                                                               | P_4.4.62     |

|                                               |                                               | PCLI                        |                          | POEN                        |         | 1                                                                | I            |

Table 5Electrical Characteristics,  $V_s = 5.5 V$  to 20 V,  $V_{DD} = 3.0V$  to 5.5V,  $T_j = -40^{\circ}$ C to  $+150^{\circ}$ C, EN= HIGH,<br/> $I_{OUTn} = 0 A$ ; Typical values refer to  $V_{DD} = 5.0 V$ ,  $V_s = 13.5 V$  and  $T_J = 25^{\circ}$ C unless otherwise<br/>specified; all voltages with respect to ground, positive current flowing into pin (unless<br/>otherwise specified) (cont'd)

| Parameter                                          | Symbol                 |      | Value | s    | Unit | Note or<br>Test Condition                                                                                                             | Number   |

|----------------------------------------------------|------------------------|------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                    |                        | Min. | Тур.  | Max. | _    |                                                                                                                                       |          |

| SCLK Low before CSN Low                            | t <sub>BEF</sub>       | 125  | -     | -    | ns   | 2)                                                                                                                                    | P_4.4.63 |

| CSN Setup Time                                     | t <sub>lead</sub>      | 250  | -     | -    | ns   | 2)                                                                                                                                    | P_4.4.64 |

| SCLK Setup Time                                    | t <sub>lag</sub>       | 250  | -     | -    | ns   | 2)                                                                                                                                    | P_4.4.65 |

| SCLK Low after CSN High                            | t <sub>BEH</sub>       | 125  | -     | -    | ns   | 2)                                                                                                                                    | P_4.4.66 |

| SDI Setup Time                                     | t <sub>SDI_setup</sub> | 30   | -     | -    | ns   | 2)                                                                                                                                    | P_4.4.67 |

| SDI Hold Time                                      | t <sub>SDI_hold</sub>  | 30   | -     | -    | ns   | 2)                                                                                                                                    | P_4.4.68 |

| Input Signal Rise Time at pin<br>SDI, SCLK, CSN    | t <sub>rIN</sub>       | -    | -     | 50   | ns   | 2)                                                                                                                                    | P_4.4.69 |

| Input Signal Fall Time at pin SDI,<br>SCLK, CSN    | t <sub>fIN</sub>       | -    | -     | 50   | ns   | 2)                                                                                                                                    | P_4.4.70 |

| Delay time from EN falling edge<br>to standby mode | t <sub>dmode</sub>     | -    | -     | 8    | μs   | 2)                                                                                                                                    | P_4.4.71 |

| Minimum CSN High Time                              | t <sub>csnh</sub>      | 5    | -     | -    | μs   | 2)                                                                                                                                    | P_4.4.72 |

| Data Output Timing. See Figur                      |                        |      |       | +    | -    | -                                                                                                                                     |          |

| SDO Rise Time                                      | t <sub>rSDO</sub>      | -    | 30    | 80   | ns   | $C_{load} = 40 p F^{2}$                                                                                                               | P_4.4.73 |

| SDO Fall Time                                      | t <sub>fSDO</sub>      | _    | 30    | 80   | ns   | $C_{load} = 40 p F^{2}$                                                                                                               | P_4.4.74 |

| SDO Enable Time after CSN<br>falling edge          | t <sub>ensdo</sub>     | -    | -     | 75   | ns   | Low Impedance <sup>2)</sup>                                                                                                           | P_4.4.75 |

| SDO Disable Time after CSN rising edge             | t <sub>DISSDO</sub>    | -    | -     | 75   | ns   | High Impedance <sup>2)</sup>                                                                                                          | P_4.4.76 |

| Duty cycle of incoming clock at<br>SCLK            | duty <sub>SCLK</sub>   | 45   | -     | 55   | %    | 2)                                                                                                                                    | P_4.4.77 |

| SDO Valid Time for <i>V</i> <sub>DD</sub> = 3.3V   | t <sub>VASDO3</sub>    | -    | 70    | 95   | ns   | $V_{\text{SDO}} < 0.2 \text{ x } V_{\text{DD}}$ $V_{\text{SDO}} > 0.8 \text{ x } V_{\text{DD}}$ $C_{\text{load}} = 40 \text{ pF}^{2}$ | P_4.4.78 |

| SDO Valid Time for V <sub>DD</sub> = 5V            | t <sub>VASDO5</sub>    | -    | 50    | 65   | ns   | $V_{SDO} < 0.2 \text{ x } V_{DD}$<br>$V_{SDO} > 0.8 V_{DD}$<br>$C_{load} = 40 \text{ pF}^{2}$                                         | P_4.4.79 |

| Thermal warning & Shutdown                         |                        | 1    | - I   | 1    |      |                                                                                                                                       |          |

| Thermal warning junction temperature               | T <sub>jW</sub>        | 120  | 135   | 150  | °C   | See Figure 9 <sup>2)</sup>                                                                                                            | P_4.4.80 |

| Thermal shutdown junction                          | T <sub>jSD</sub>       | 160  | 175   | 190  | °C   | See Figure 9 <sup>2)</sup>                                                                                                            | P_4.4.81 |

temperature 2) Thermal comparator hysteresis 4 °C P\_4.4.82 T<sub>iHYS</sub> \_ \_ 2) Difference between  $T_{jSD}$ - $T_{jW}$ 40 °C P\_4.4.120  $T_{\rm jSD}$  -  $T_{\rm jW}$ \_ \_

1)  $I_{S_{HSON}}$  does not include the load current

2) Not subject to production test, specified by design

- 3) Measured for 20% 80% of  $V_{\rm S}$ .

- 4) Not applicable in daisy chain configuration

#### 4 Characterization results

Performed on 5 devices, over operating temperature and nominal/extended supply range.

#### **Typical performance characteristics**

#### Supply quiescent current

#### Logic supply quiescent current

#### Supply current

#### Logic supply current

#### **HS static Drain-source ON-resistance**

#### HS static drain-source ON-resistance VS = 13.5V and VDD = 5V

# P\_4.4.16/P\_4.4.17 1600 1500 1400 1300 [Cu 1200 ST 1100 1000 900 800 700 600 $-50 \quad -30 \quad -10 \quad 10 \quad 30 \quad 50 \quad 70 \quad 90 \quad 110 \quad 130 \quad 150$ Junction Temperature [°C]

LS static Drain-source ON-resistance

#### LS static drain-source ON-resistance VS = 13.5V and VDD = 5V

#### Slew rate ON of high-side outputs

#### Slew rate OFF of high-side outputs

# P\_4.4.36

Slew rate ON of low-side outputs

#### Slew rate OFF of low-side outputs

#### HS overcurrent shutdown threshold

#### Undervoltage switch ON voltage threshold

#### LS overcurrent shutdown threshold

Undervoltage switch OFF voltage threshold

#### Overvoltage switch ON voltage threshold

# VDD Power-on-reset and VDD Power-off-reset

#### Overvoltage switch OFF voltage threshold

# infineon

#### **General Description**

# 5 General Description

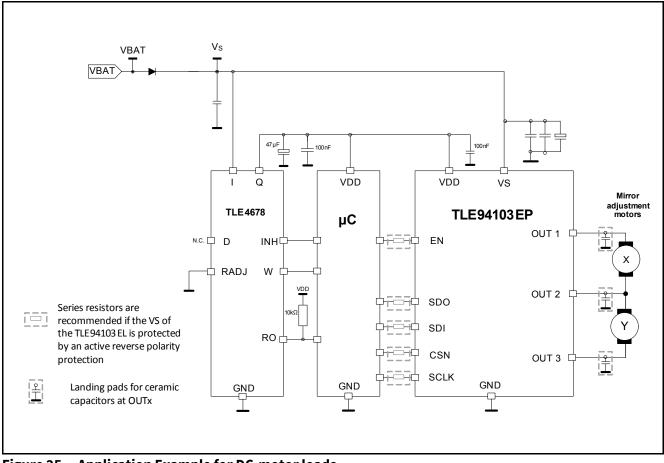

#### 5.1 Power Supply

The TLE94103EP has two power supply inputs,  $V_{\rm S}$  and  $V_{\rm DD}$ . The half bridge outputs are supplied by  $V_{\rm S}$ , which is connected to the 12V automotive supply rail.  $V_{\rm DD}$  is used to supply the I/O buffers and internal voltage regulator of the device.

$V_{\rm S}$  and  $V_{\rm DD}$  supplies are separated so that information stored in the logic block remains intact in the event of voltage drop outs or disturbances on  $V_{\rm S}$ . The system can therefore continue to operate once  $V_{\rm S}$  has recovered, without having to resend commands to the device.

A rising edge on  $V_{DD}$  crossing  $V_{DD POR}$  triggers an internal Power-On Reset (POR) to initialize the IC at power-on. All data stored internally is deleted, and the outputs are switched off (high impedance).

An electrolytic and 100nF ceramic capacitors are recommended to be placed as close as possible to the  $V_{\rm S}$  supply pin of the device for improved EMC performance in the high and low frequency band. The electrolytic capacitor must be dimensioned to prevent the VS voltage from exceeding the absolute maximum rating. In addition, decoupling capacitors are recommended on the  $V_{\rm DD}$  supply pin.

#### 5.2 Operation modes

#### 5.2.1 Normal mode

The TLE94103EP enters normal mode by setting the EN input High. In normal mode, the charge pump is active and all output transistors can be configured via SPI.

#### 5.2.2 Sleep mode

The TLE94103EP enters sleep mode by setting the EN input Low. The EN input has an internal pull-down resistor.

In sleep mode, all output transistors are turned off and the SPI register banks are reset. The current consumption is reduced to  $I_{SQ} + I_{DD_Q}$ .

#### 5.3 Reset Behaviour

The following reset triggers have been implemented in the TLE94103EP:

#### V<sub>DD</sub> Undervoltage Reset:

The SPI Interface shall not function if  $V_{DD}$  is below the undervoltage threshold,  $V_{DD POffR}$ . The digital block will be deactivated, the logic contents cleared and the output stages are switched off. The digital block is initialized once  $V_{DD}$  voltage levels is above the undervoltage threshold,  $V_{DD POR}$ . Then the NPOR bit is reset (NPOR = 0 in **SYS\_DIAG1** and Global Status Register).

#### Reset on EN pin:

If the EN pin is pulled Low, the logic content is reset and the device enters sleep mode.

The reset event is reported by the NPOR bit (NPOR = 0) once the TLE94103EP is in normal mode (EN = High;  $VDD > V_{DD POR}$ ).

#### **General Description**

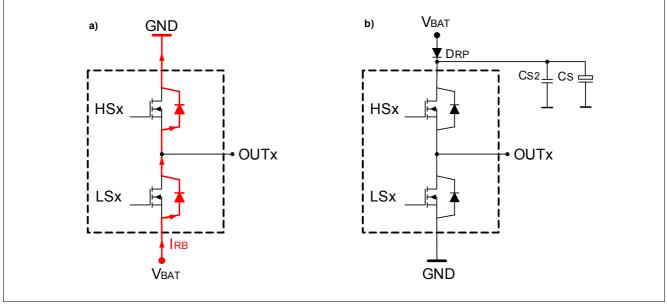

#### 5.4 Reverse Polarity Protection

The TLE94103EP requires an external reverse polarity protection. During reverse polarity, the free-wheeling diodes across the half bridge output will begin to conduct, causing an undesired current flow ( $I_{RB}$ ) from ground potential to battery and excessive power dissipation across the diodes. As such, a reverse polarity protection diode is recommended (see **Figure 4**).

Figure 4 Reverse Polarity Protection

#### 6 Half-Bridge Outputs

#### 6.1 Functional Description

The half-bridge outputs of the TLE94103EP are intended to drive motor loads.

If the outputs are driven continuously via SPI, for example HS1 and LS2 used to drive a motor, then the following suggested SPI commands shall be sent:

- Activate HS1: Bit HB1\_HS\_EN in HB\_ACT\_1\_CTRL register

- Activate LS2: Bit HB2\_LS\_EN in HB\_ACT\_1\_CTRL register

#### 6.2 Protection & Diagnosis

The TLE94103EP is equipped with an SPI interface to control and diagnose the state of the half-bridge drivers. This device has embedded protective functions which are designed to prevent IC destruction under fault conditions described in the following sections. Fault conditions are treated as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

The following table provides a summary of fault conditions, protection mechanisms and recovery states embedded in the TLE94103EP device.

| Fault<br>condition         | Error Flag<br>(EF)<br>behaviour | Error bit: Status Register                                                                                                                                                                                                                 | Output<br>Protection<br>mechanism       | Output<br>error<br>state | Output and error<br>flag (EF) recovery                                                                                                             |

|----------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Overcurrent                | Latch                           | <ol> <li>Load Error bit, LE (bit 6) in<br/>SYS_DIAG 1: Global Status 1<br/>Register</li> <li>Localized error for each HS and<br/>LS channel of half-bridge,<br/>HBn_HS_OC and HBn_LS_OC bits<br/>in SYS_DIAG_2 status register.</li> </ol> | Error output<br>shutdown<br>and latched | High-Z                   | Half-bridge control<br>bits remain set<br>despite error,<br>however the<br>output stage is<br>shutdown. Clear EF<br>to reactivate<br>output stage. |

| Open load                  | Latch                           | <ol> <li>Load Error bit, LE (bit 6) in<br/>SYS_DIAG 1: Global Status 1<br/>Register</li> <li>Localized error for each HS and<br/>LS channel of half-bridge,<br/>HBn_HS_OL and HBn_LS_OL bits in<br/>SYS_DIAG3 status register.</li> </ol>  | None                                    | No<br>state<br>change    | An open load<br>detection does not<br>change the state of<br>the output.<br>EF to be cleared.                                                      |

| Temperature<br>pre-warning | Latch                           | Global error bit 1, TPW in<br>SYS_DIAG_1: Global Status 1<br>register                                                                                                                                                                      | None                                    | No<br>state<br>change    | Not applicable                                                                                                                                     |

| Temperature<br>shutdown    | Latch                           | Global error bit 2, TSD in<br>SYS_DIAG_1: Global Status 1<br>register                                                                                                                                                                      | All outputs<br>shutdown<br>and latched. | High-Z                   | Half-bridge control<br>bits remain set<br>despite error,<br>however the<br>output stage is<br>shutdown. Clear EF<br>to reactivate<br>output stage. |

Table 6Summary of diagnosis and monitoring of outputs

| Fault<br>condition                            | Error Flag<br>(EF)<br>behaviour | Error bit: Status Register                                              | Output<br>Protection<br>mechanism                            | Output<br>error<br>state | Output and error<br>flag (EF) recovery                                                                                                                                                                          |

|-----------------------------------------------|---------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Powersupply<br>failure due to<br>undervoltage | Latch                           | Global error bit 5, VS_UV in<br>SYS_DIAG_1: Global Status 1<br>register | All outputs<br>shutdown<br>and<br>automatically<br>recovers. | High-Z                   | Half-bridge control<br>bits remain set<br>despite error,<br>however the<br>output stage is<br>shutdown. They<br>will automatically<br>be reactivated<br>once the power<br>supply recovers. EF<br>to be cleared. |

| Powersupply<br>failure due to<br>overvoltage  | Latch                           | Global error bit 4, VS_OV in<br>SYS_DIAG_1: Global Status 1<br>register | All outputs<br>shutdown<br>and<br>automatically<br>recover.  | High-Z                   | Half-bridge control<br>bits remain set<br>despite error,<br>however the<br>output stage is<br>shutdown. They<br>will automatically<br>be reactivated<br>once the power<br>supply recovers. EF<br>to be cleared. |

#### Table 6 Summary of diagnosis and monitoring of outputs (cont'd)

#### 6.2.1 Short Circuit of Output to Supply or Ground

The high-side switches are protected against short to ground whereas the low-side switches are protected against short to supply.

The high-side and low-side power switches will enter into an over-current condition if the current within the switch exceeds the overcurrent shutdown detection threshold,  $I_{SD}$ . Upon detection of the  $I_{SD}$  threshold, an overcurrent shutdown filter,  $t_{dSD}$  is begun. As the current rises beyond the threshold  $I_{SD}$ , it will be limited by the current limit threshold,  $I_{LIM}$ . Upon expiry of the overcurrent shutdown filter time, the affected power switch is latched off and the corresponding error bit, HBn\_HS\_OC or HBn\_LS\_OC is set and latched. See **Figure 5** and **Figure 6** for more detail. A global load error bit, LE, contained in the global status register, SYS\_DIAG\_1, is also set for ease of error scanning by the application software. The power switch remains deactivated as long as the error bit is set.

To resume normal functionality of the power switch (in the event the overcurrent condition disappears or to verify if the failure still exists) the microcontroller shall clear the error bit in the respective status register to reactivate the desired power switch.

Figure 5 High-Side Switch - Short Circuit and Overcurrent Protection

| activated power switch |                                |                        |                       |                       |                                                 |  |

|------------------------|--------------------------------|------------------------|-----------------------|-----------------------|-------------------------------------------------|--|

| REGISTER               | REGISTER NAME                  | Bit                    | BEFORE<br>OVERCURRENT | DURING<br>OVERCURRENT | AFTER<br>OVERCURRENT                            |  |

| ΤΥΡΕ                   |                                |                        | Bit State             | Bit State             | Bit State                                       |  |

| Control                | HB_ACT_CTRL_n                  | HBn_HS_EN<br>HBn_LS_EN | 1                     | 1                     | 1 (corresponding<br>half-bridge<br>deactivated) |  |

| Status                 | SYS_DIAG_1:<br>Global Status 1 | LE                     | 0                     | 0                     | 1                                               |  |

| Status                 | SYS_DIAG_x<br>where x=2        | HBn_HS_OC<br>HBn_LS_OC | 0                     | 0                     | 1                                               |  |

# Table 7Control and Status register bit state in the event of an overcurrent condition for an<br/>activated power switch

#### 6.2.2 Cross-Current

In bridge configurations the high-side and low-side power transistors are ensured never to be simultaneously "ON" to avoid cross currents. This is achieved by integrating delays in the driver stage of the power outputs to create a dead-time between switching off of one power transistor and switching on of the adjacent power transistor within the half-bridge. The dead times,  $t_{\text{DHL}}$  and  $t_{\text{DLH}}$ , as shown in **Figure 7** case 3 and **Figure 8** case 3, have been specified to ensure that the switching slopes do not overlap with each other. This prevents a cross conduction event.

#### **TLE94103EP**

#### **Half-Bridge Outputs**

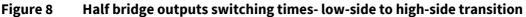

#### 6.2.3 Temperature Monitoring

Temperature sensors are integrated in the power stages. The temperature monitoring circuit compares the measured temperature to the warning and shutdown thresholds. If one or more temperature sensors reach the warning temperature, the temperature pre-warning bit, TPW is set. This bit is latched and can only be cleared via SPI. The outputs stages however remain activated.

If one or more temperature sensors reach the shut-down temperature threshold, **all outputs are latched off**. The TSD bit in SYS\_DIAG\_1: Global Status 1 is set. All outputs remain deactivated until the TSD bit is cleared. See **Figure 9**.

To resume normal functionality of the power switch (in the event the overtemperature condition disappears, or to verify if the failure still exists) the microcontroller shall clear the TSD error bit in the status register to reactivate the respective power switch.

Figure 9 Overtemperature Behavior

| activated power switch |                                |     |                                               |                                               |                                                |                                                                    |

|------------------------|--------------------------------|-----|-----------------------------------------------|-----------------------------------------------|------------------------------------------------|--------------------------------------------------------------------|

| REGISTER<br>TYPE       | REGISTER NAME                  | Bit | T <sub>j</sub> < T <sub>jw</sub><br>Bit State | T <sub>j</sub> > T <sub>jw</sub><br>Bit State | T <sub>j</sub> > T <sub>jSD</sub><br>Bit State | T <sub>j</sub> < T <sub>jSD</sub> - T <sub>jHYS</sub><br>Bit State |

|                        |                                |     |                                               |                                               |                                                |                                                                    |

| Status                 | SYS_DIAG_1: Global<br>status 1 | TPW | 0                                             | 1<br>(latched)                                | 1<br>(latched)                                 | '0' if error is<br>cleared and<br>$T_j < T_{jW}$ , else '1'        |

| Status                 | SYS_DIAG_1: Global<br>status 1 | TSD | 0                                             | 0                                             | 1<br>(latched)                                 | '0' if error is<br>cleared, else<br>'1'                            |

# Table 8Control and Status register bit state in the event of an overtemperature condition for an<br/>activated power switch

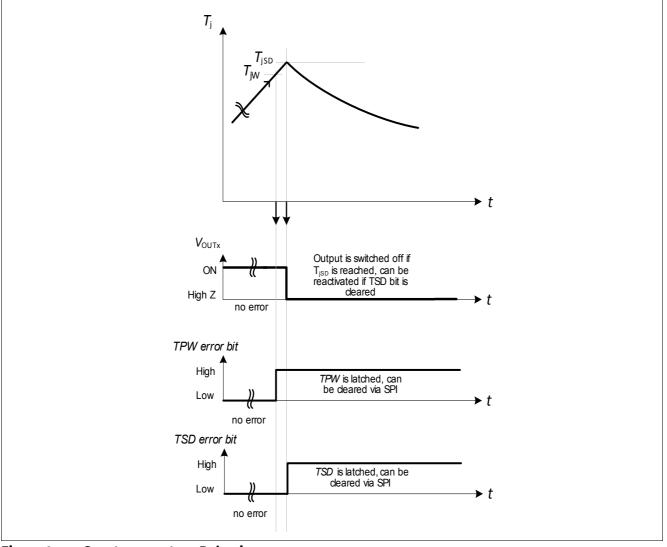

#### 6.2.4 Overvoltage and undervoltage shutdown

The power supply rails  $V_{\rm S}$  and  $V_{\rm DD}$  are monitored for supply fluctuations. The  $V_{\rm S}$  supply is monitored for underand over-voltage conditions where as the  $V_{\rm DD}$  supply is monitored for under-voltage conditions.

#### 6.2.4.1 V<sub>s</sub> Undervoltage

In the event the supply voltage  $V_S$  drops below the switch off voltage  $V_{UV OFF}$ , all output stages are switched off, however, the logic information remains intact and uncorrupted. The  $V_S$  under-voltage error bit, VS\_UV, located in SYS\_DIAG\_1: Global Status 1 status register, will be set and latched. If  $V_S$  rises again and reaches the switch on voltage  $V_{UV ON}$  threshold, the power stages will automatically be activated. The VS\_UV error bit should be cleared to verify if the supply disruption is still present. See **Figure 10**.

#### 6.2.4.2 V<sub>s</sub> Overvoltage

In the event the supply voltage  $V_S$  rises above the switch off voltage  $V_{OV OFF}$ , all output stages are switched off. The  $V_S$  over-voltage error bit, VS\_OV, located in SYS\_DIAG\_1: Global Status 1 status register, will be set and latched. If  $V_S$  falls again and reaches the switch on voltage  $V_{OV ON}$  threshold, the power stages will automatically be activated. The VS\_OV error bit should be cleared to verify if the overvoltage condition is still present. See **Figure 10**.

#### 6.2.4.3 V<sub>DD</sub> Undervoltage

In the event the VDD logic supply decreases below the undervoltage threshold,  $V_{\text{DD POffR}}$ , the SPI interface shall no longer be functional and the TLE94103EP will enter reset.

The digital block will be initialized and the output stages are switched off to High impedance. The undervoltage reset is released once  $V_{DD}$  voltage levels are above the undervoltage threshold,  $V_{DD POR}$ .

The reset event is reported in SYS\_DIAG1 by the NPOR bit (NPOR = 0) once the TLE94103EP is in normal mode (EN = High; VDD >  $V_{DD POR}$ ).

#### TLE94103EP

#### **Half-Bridge Outputs**

Figure 10 Output behavior during under- and overvoltage V<sub>s</sub> condition

#### 6.2.5 Open Load

Both high-side and low-side switches of the half-bridge power outputs are capable of detecting an open load in their activated state. If a load current lower than the open load detection threshold,  $I_{OLD}$  for at least  $t_{dOLD}$  is detected at the activated switch, the corresponding error bit, HBn\_HS\_OL or HBn\_LS\_OL is set and latched. A global load error bit, LE, in the global status register, SYS\_DIAG\_1: Global Status 1, is also set for ease of error scanning by the application software. The half-bridge output however, remains activated.

The microcontroller must clear the error bit in the respective status register to determine if the open load is still present or disappeared.

#### Serial Peripheral Interface (SPI)

# 7 Serial Peripheral Interface (SPI)

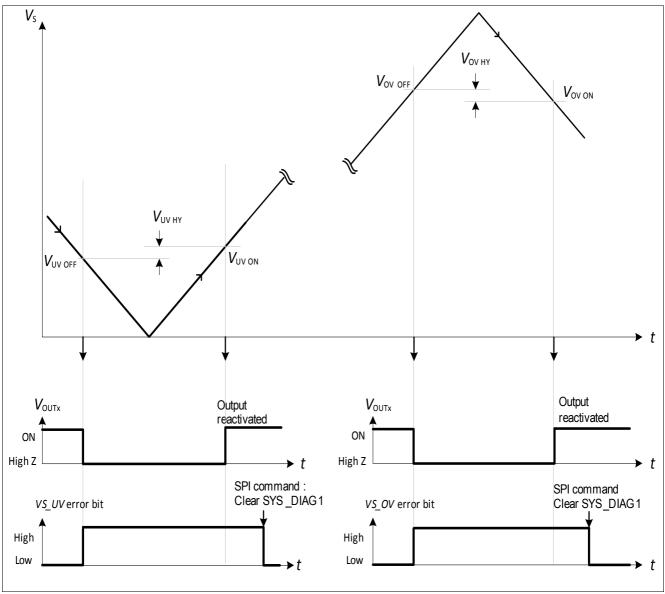

The TLE94103EP has a 16-bit SPI interface for output control and diagnostics. This section describes the SPI protocol, the control and status registers.

#### 7.1 SPI Description

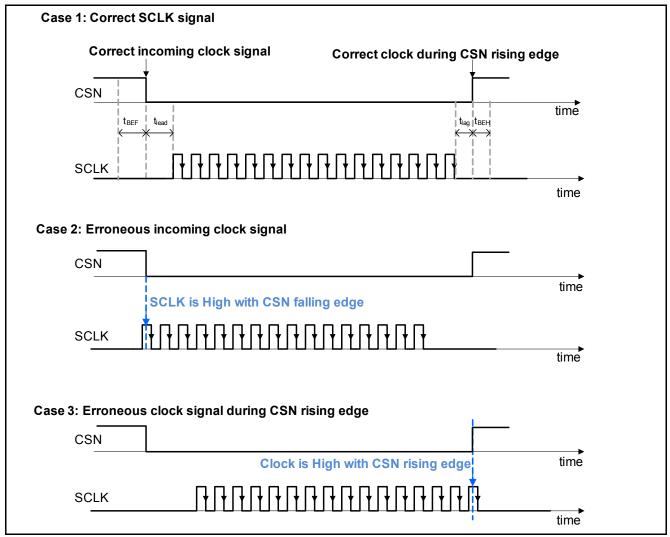

The 16-bit wide Control Input Word is read via the data input SDI, which is synchronized with the clock input SCLK provided by the microcontroller. SCLK must be Low during CSN falling edge (Clock Polarity = 0). The SPI incorporates an in-frame response: the content of the addressed register is shifted out at SDO within the same SPI frame (see **Figure 17** and **Figure 19**). The transmission cycle begins when the chip is selected by the input CSN (Chip Select Not), Low active. After the CSN input returns from Low to High, the word that has been read is interpreted according to the content. The SDO output switches to tri-state status (High impedance) at this point, thereby releasing the SDO bus for other use. The state of SDI is shifted into the input register with every falling edge on SCLK. The state of SDO is shifted out of the output register at every rising edge on SCLK (Clock Phase = 1). The SPI protocol of the TLE94103EP is compatible with independent slave configuration and with daisy chain. Daisy chaining is applicable to SPI devices with the same protocol.

Writing, clearing and reading is done byte wise. The SPI configuration and status bits are not cleared automatically by the device and therefore must be cleared by the microcontroller, e.g. if the TSD bit was set due to over temperature (refer to the respective register description for detailed information).

Figure 11 SPI Data Transfer Timing (note the reversed order of LSB and MSB as shown in this figure compared to the register description)

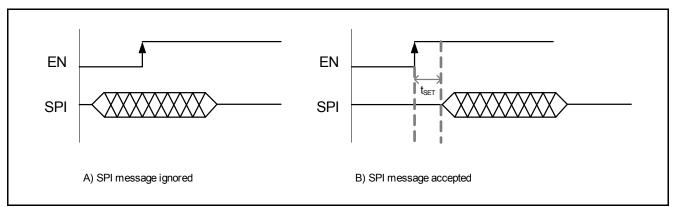

SPI messages are only recognized if a minimum set time, tSET, is observed upon rising edge of the EN pin (Figure 12).

#### Serial Peripheral Interface (SPI)

Figure 12 Setup time from EN rising edge to first SPI communication

Figure 13 SPI Data Timing

#### 7.1.1 Global Error Flag

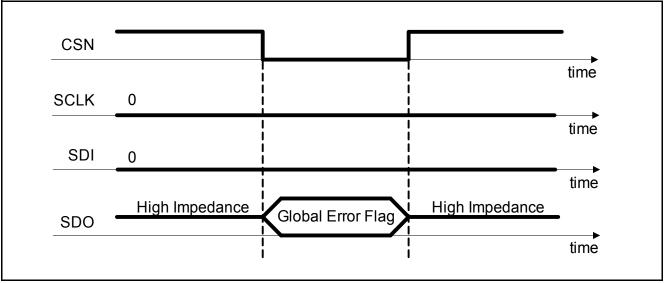

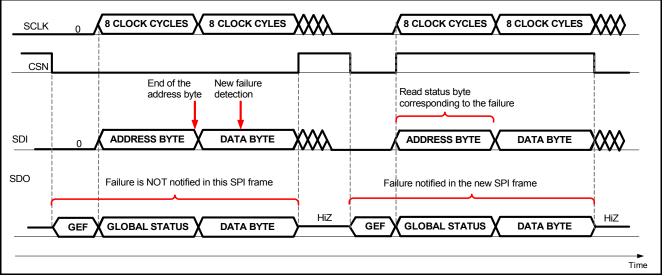

A logic OR combination between Global Error Flag (GEF) and the signal present on SDI is reported on SDO between a CSN falling edge and the first SCLK rising edge (**Figure 11**). GEF is set if a fault condition is detected or if the device comes from a Power On Reset (POR).

Note: The SDI pin of all devices in daisy chain or non daisy chain mode must be Low at the beginning of the SPI frame (between the CSN falling edge and the first SCLK rising edge).

It is possible to check if the TLE94103EP has detected a fault by reading the GEF without SPI clock pulse (Figure 14).

Figure 14 SDO behaviour with 0-clock cycle

### 7.1.2 Global Status Register

The SDO shifts out during the first eight SCLK cycles the Global Status Register. This register provides an overview of the device status. All failures conditions are reported in this byte:

- SPI protocol error (SPI\_ERR)

- Load Error (LE bit): logical OR between Open Load (OL) and Overcurrent (OC) failures

- VS Undervoltage (VS\_UV bit)

- VS Overvoltage (VS\_OV bit)

- Negated Power ON Reset (NPOR bit)

- Temperature Shutdown (TSD bit)

- Temperature Pre-Warning (TPW bit)

See **Chapter 7.7.1** for details.

Note: The Global Error Flag is a logic OR combination of every bit of the Global Status Register with the exception of NPOR: GEF = (SPI\_ERR) OR (LE) OR (VS\_UV) OR (VS\_OV) OR (NOT(NPOR)) OR (TSD) OR (TPW). It is possible to mask open load failures from the Global Error Flag by setting the OL\_BLANK bit (refer to **Chapter 7.6**).

The following table shows how failures are reported in the Global Status Register and by the Global Error Flag.

|                          | 0                                                 | 6                 |  |

|--------------------------|---------------------------------------------------|-------------------|--|

| Type of Error            | Failure reported in the Global<br>Status Register | Global Error Flag |  |

| SPI protocol error       | SPI_ERR = 1                                       | 1                 |  |

| Open load or Overcurrent | LE = 1                                            | 11)               |  |

| VS Undervoltage          | VS_UV = 1                                         | 1                 |  |

| VS Overvoltage           | VS_OV = 1                                         | 1                 |  |

| Power ON Reset           | NPOR = 0                                          | 1                 |  |

| Thermal Shutdown         | TSD = 1                                           | 1                 |  |

### Table 9 Failure reported in the Global Status Register and Global Error Flag

| Type of Error                  | Failure reported in the Global<br>Status Register                                 | Global Error Flag |

|--------------------------------|-----------------------------------------------------------------------------------|-------------------|

| Thermal Warning                | TPW = 1                                                                           | 1                 |

| No Error and no Power ON Reset | SPI_ERR = 0<br>LE = 0<br>VS_UV = 0<br>VS_OV = 0<br>NPOR = 1<br>TSD = 0<br>TPW = 0 | 0                 |

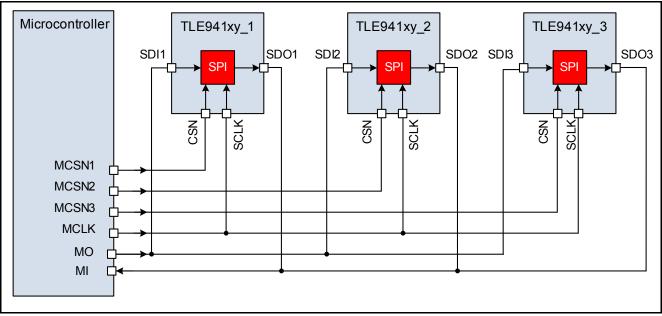

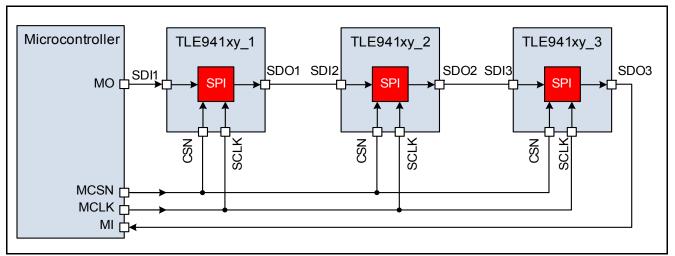

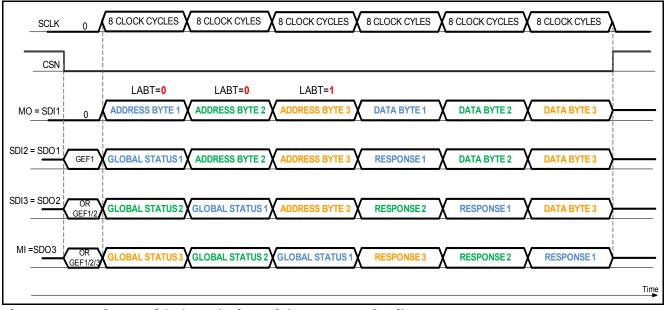

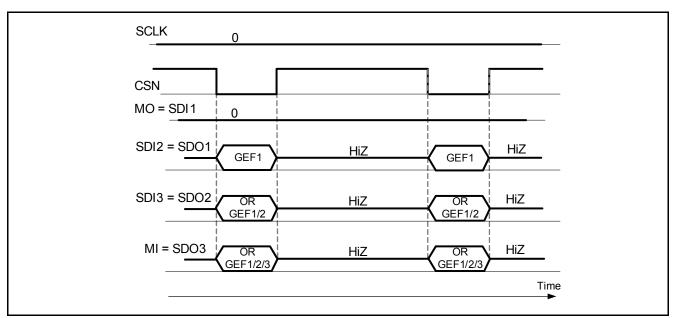

### Table 9Failure reported in the Global Status Register and Global Error Flag