# **TM52F0C63**

## DATA SHEET

## Rev 0.93

(Please read the precautions on the second page before use)

**tenx** reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. **tenx** does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. **tenx** products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses **tenx** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **tenx** and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that **tenx** was negligent regarding the design or manufacture of the part.

## PRECAUTIONS

1. The chip cannot enter Halt/Stop mode if the INTn pin is low and the INTn wake-up function is enabled. (INTn=0 and EXn=1, n=0~2)

## **AMENDMENT HISTORY**

| Version | Date      | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V0.90   | May, 2022 | New Release                                                                                                                                                                                                                                                                                                                                                                                                              |

| V0.91   | May, 2022 | Added MSOP-10 package                                                                                                                                                                                                                                                                                                                                                                                                    |

| V0.92   | Jul, 2022 | <ol> <li>Program Memory 10K erase times at least (p.8)</li> <li>Removed system clock frequency requirement before entering Halt/Stop<br/>mode (p.36)</li> <li>Added the description of pin wake-up mechanism (p.44~45)</li> <li>Corrected current value and corresponding conditions (p.10, p.115)</li> <li>Added the description about Halt mode.</li> <li>Mass production writer does not support P2.0/P2.1</li> </ol> |

| V0.93   | Nov, 2022 | <ol> <li>IAP programming voltage must be greater than 4V (p.23)</li> <li>EE programming voltage must be greater than 3V (p.118)</li> <li>Modify VBG2.5V to VBG2.54V</li> </ol>                                                                                                                                                                                                                                           |

## CONTENTS

| PRE | CAU                             | ΓΙΟΝς                                                                                                                                         | . 2            |

|-----|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| AMI | ENDN                            | IENT HISTORY                                                                                                                                  | .3             |

| TM5 | 2 F8x                           | xx FAMILY                                                                                                                                     | . 6            |

| GEN | ERA                             | L DESCRIPTION                                                                                                                                 | .7             |

| SYS | ГЕМ                             | BLOCK DIAGRAM                                                                                                                                 | .7             |

| FEA | TUR                             | ES                                                                                                                                            | . 8            |

| PIN | ASSI                            | GNMENT                                                                                                                                        | 12             |

| PIN | DES(                            | CRIPTION                                                                                                                                      | 16             |

| PIN | SUM                             | MERY                                                                                                                                          | 17             |

| FUN | СТІС                            | DNAL DESCRIPTION                                                                                                                              | 18             |

| 1.  | CPU                             | Core                                                                                                                                          | 18             |

|     | 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Accumulator (ACC)<br>B Register (B)<br>Stack Pointer (SP)<br>Dual Data Pointer (DPTRs)<br>Program Status Word (PSW)                           | 18<br>19<br>19 |

| 2.  | Mer                             | nory                                                                                                                                          | 21             |

|     | 2.1<br>2.2<br>2.3<br>2.4        | Program Memory (Support IAP)<br>EEPROM Memory<br>Data Memory<br>Special Function Register (SFR)                                               | 26<br>28       |

| 3.  | Rese                            | et                                                                                                                                            | 30             |

|     | 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Power on Reset (POR)<br>External Pin Reset (XRST)<br>Software Command Reset (SWRST)<br>Watchdog Timer Reset (WDTR)<br>Low Voltage Reset (LVR) | 30<br>30<br>30 |

| 4.  | Cloc                            | k Circuitry & Operation Mode                                                                                                                  | 34             |

|     | 4.1<br>4.2                      | System Clock<br>Operation Modes                                                                                                               | 36             |

| 5.  |                                 | rupt & Wake-up                                                                                                                                |                |

|     | 5.1<br>5.2<br>5.3<br>5.4        | Interrupt Enable and Priority Control<br>Pin Interrupt                                                                                        | 42<br>44       |

| 6.  | I/O                             | Ports                                                                                                                                         | 46             |

| 7.  | Tim                             | ers                                                                                                                                           | 59             |

| 8.  | UAI                             | RT                                                                                                                                            | 65             |

| 9.  | PW                              | Ms                                                                                                                                            | 67             |

| 10.  | Low Voltage Detection (LVD)       |

|------|-----------------------------------|

| 11.  | ADC                               |

| 12.  | S/W Controller LCD Driver         |

| 13.  | Cyclic Redundancy Check (CRC)     |

| 14.  | Multiplier and Divider            |

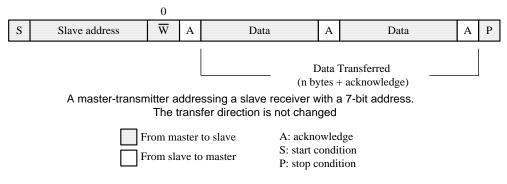

| 15.  | Master I <sup>2</sup> C Interface |

| 16.  | In Circuit Emulation (ICE) Mode   |

| SFR  | & CFGW MAP                        |

| SFR  | & CFGW DESCRIPTION                |

| INST | RUCTION SET                       |

| ELE  | CTRICAL CHARACTERISTICS           |

| 1.   | Absolute Maximum Ratings          |

| 2.   | DC Characteristics                |

| 3.   | Clock Timing                      |

| 4.   | Reset Timing Characteristics      |

| 5.   | ADC Electrical Characteristics    |

| 6.   | EEPROM Characteristics            |

| 7.   | Characteristic Graphs             |

| Pack | age and Dice Information          |

## TM52 F8xxx FAMILY

#### **Common Feature**

| CPU       | Flash Program<br>memory | RAM      | Timer0~2 | UART     |

|-----------|-------------------------|----------|----------|----------|

| Fast 8051 | 4K~32K                  | 256~2048 | 8051     | 8051     |

| (2T)      | with IAP, ISP, ICP      | bytes    | Standard | Standard |

#### **Family Members Features**

| P/N        | Program<br>Memory | Data<br>Memory                           | RAM   | IO Pin | PWM          | SAR<br>ADC      | Touch<br>Key | LCD    | LED    | Interface        |

|------------|-------------------|------------------------------------------|-------|--------|--------------|-----------------|--------------|--------|--------|------------------|

| TM52-F0C63 | Flash<br>8KB      | IAP share with main rom<br>/ EEPROM 128B | 512B  | 26     | 16-bit<br>x7 | 12-bit<br>19-ch | -            | 4com   | -      | UART*1<br>MIIC*1 |

| TM52-F8368 | Flash<br>8KB      | IAP share with main rom                  | 512B  | 26     | 16-bit<br>x7 | 12-bit<br>12-ch | _            | 4com   | _      | UART*1<br>MIIC*1 |

| TM52-F8274 | Flash             | IAP share with main rom                  | 1024B | 26     | (8+2)-bit    | 12-bit          |              | 8com   | 4Cx6S  | SPI*1<br>UART*1  |

| TM52-F8278 | 8KB               | / EEPROM 128B                            | 1024D | 20     | x3           | 14-ch           | 16-ch        | 800111 | 40,005 | UART2*1          |

| TM52-F8273 | Flash             | IAP share with main rom                  | 1024B | 26     | (8+2)-bit    | 12-bit          | _            | 8com   | 4Cx6S  | SPI*1<br>UART*1  |

| TM52-F8276 | 16KB              | / EEPROM 128B                            | 1024D | 20     | x3           | 14-ch           | 16-ch        | 800111 | 40,005 | UART2*1          |

|            | Operation  |             | Operati     | on Current  | @5V  |       | Max. System Clock |             |       | k (Hz)    |

|------------|------------|-------------|-------------|-------------|------|-------|-------------------|-------------|-------|-----------|

| P/N        | Voltage    | Fast<br>FRC | Slow<br>SRC | Idle<br>SRC | Halt | Stop  | Fast<br>FRC       | Slow<br>SRC | FXT   | FRC       |

| TM52-F0C63 | 2.2~5.5V   | 8.3mA       | 2.6mA       | 40uA        | 21uA | 0.1uA | -                 | 80K         | -     | 16.588M   |

| TM52-F8368 | 2.3~5.5V   | 9.7mA       | 2.8mA       | 24uA        |      | 0.1uA | _                 | 80K         | _     | 16.588M   |

| TM52-F8274 | 2.3~5.5V   | 5.3mA       | 1.3mA       | 20µA        | _    | 0.1µA | 32K               | 68K         | 12M   | 12.902M   |

| TM52-F8278 | 2.3~3.3 V  | 3.311A      | 1.311A      | 20μΑ        |      | 0.1μΑ | 32K               | JON         | 12111 | 12.902101 |

| TM52-F8273 | 2.3~5.5V   | 5.3mA       | 1.3mA       | 20µA        |      | 0.1µA | 32K               | 68K         | 12M   | 12.902M   |

| TM52-F8276 | 2.5.~5.5 V | J.JIIA      | 1.5111/4    | 20μΑ        |      | 0.1µA | 52K               | JOK         | 12111 | 12.702111 |

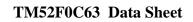

## **GENERAL DESCRIPTION**

**TM52**<sub>series</sub> **F0C63** are versions of a new, fast 8051 architecture for an 8-bit microcontroller single chip with an instruction set fully compatible with industry standard 8051, and retains most 8051 peripheral's functional block. Typically, the **TM52** executes instructions six times faster than the standard 8051 architecture.

The **TM52-F0C63** provides improved performance, lower cost and fast time-to-market by integrating features on the chip, including 8K Bytes Flash program memory, 128 Bytes EEPROM, 512 Bytes SRAM, Low Voltage Reset (LVR), Low Voltage Detector (LVD), dual clock power saving operation mode, 8051 standard UART and Timer0/1/2, real time clock Timer3, 7 set 16-bit PWMs, 19 channels 12-bit A/D Convertor, master I<sup>2</sup>C interface and Watch Dog Timer. It's a high reliability and low power consumption feature can be widely applied in consumer and home appliance products.

## SYSTEM BLOCK DIAGRAM

## **FEATURES**

#### 1. Standard 8051 Instruction set, fast machine cycle

• Executes instructions six times faster than the standard 8051.

#### 2. Flash Program Memory

- 8K Bytes

- Support "In Circuit Programming" (ICP) or "In System Programming" (ISP) for the Flash code

- Byte Write "In Application Programming" (IAP) mode is convenient as Data EEPROM access

- Code Protection Capability

- 10K erase times at least

- 10 years data retention at least

\*Each IAP address can be programmed more than 10000 times (typical value) .If the customer needs more programming times, a ROM area can be planned to disperse the address written by IAP data. Our company can provide the source code of this usage method.

#### 3. 128 Bytes EEPROM Memory

- 30K~50K erase times at least

- 10 years data retention at least

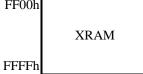

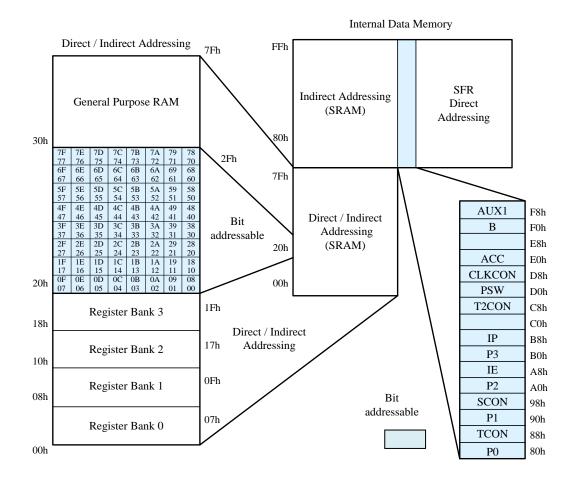

#### 4. Total 512 Bytes SRAM (IRAM + XRAM)

- 256 Bytes IRAM in the 8051 internal data memory area

- 256 Bytes XRAM in the 8051 external data memory area (accessed by MOVX Instruction)

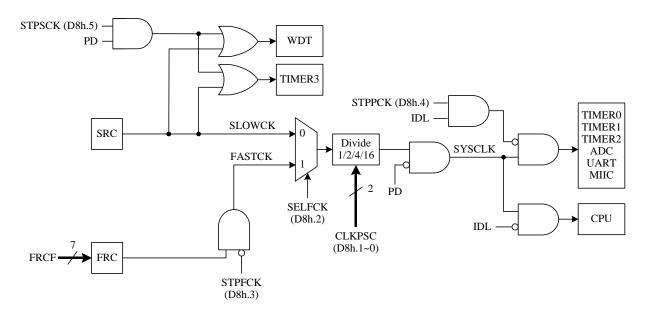

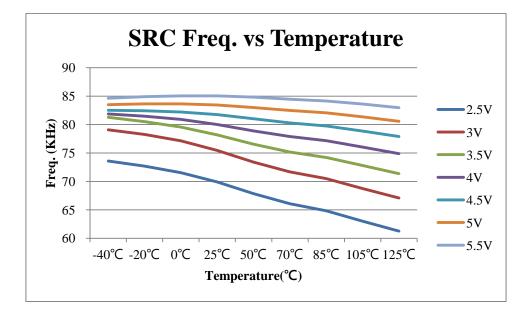

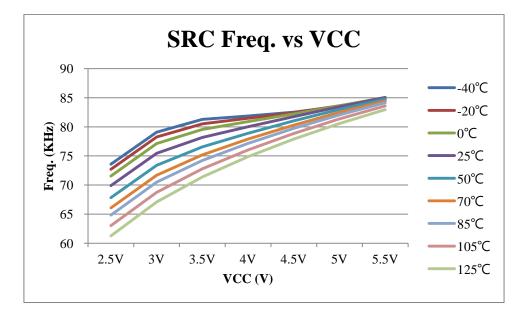

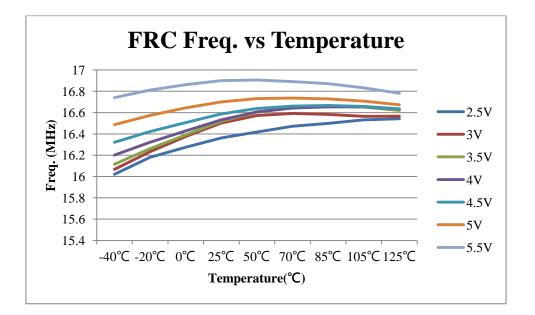

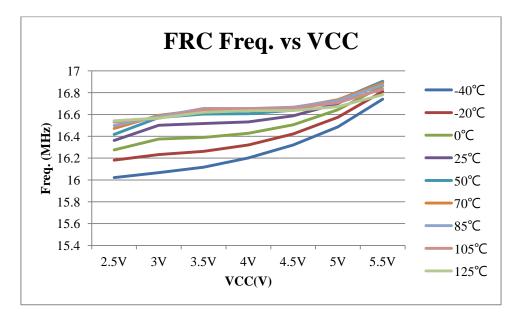

#### 5. Two System Clock type selections

- Fast clock from Internal RC (FRC, 16.588 MHz)

- Slow clock from Internal RC (SRC, 80 KHz)

- System Clock can be divided by 1/2/4/16 option

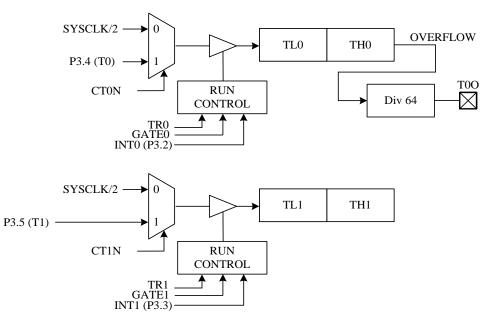

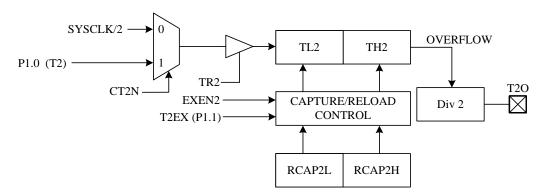

#### 6. 8051 Standard Timer – Timer0/1/2

- 16-bit Timer0, also supports T0O clock output for Buzzer application

- 16-bit Timer1, also supports T1O clock output for Buzzer application

- 16-bit Timer2, also supports T2O clock output for Buzzer application

#### 7. 15-bit Timer3

- Clock source is Slow clock

- Interrupt period can be clock divided by 32768/16384/8192/65536 option

#### 8. One UART

• 8051 standard UART, One Wire UART option can be used for ISP or other application

\*Support one UART, pin select to P30/P31 or P02/P16 by TXRXSEL (SFR 93h.7)

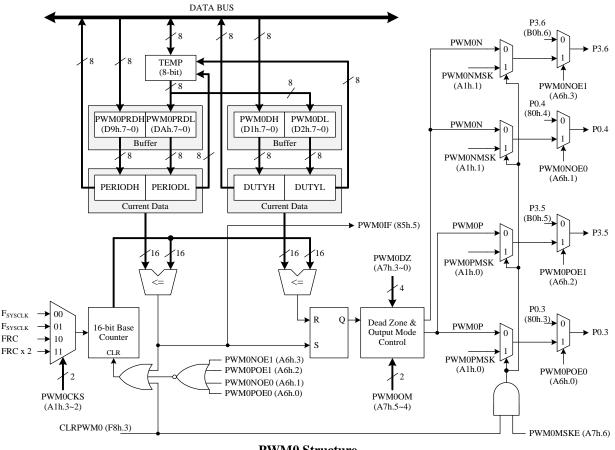

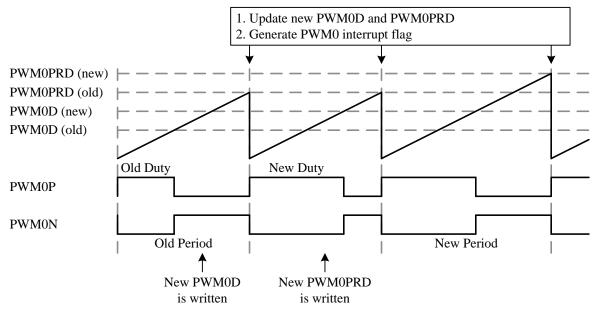

9. Seven "16" bits PWMs with prescaler/ period-adjustment

#### 10. One Master I<sup>2</sup>C interface (MIIC)

\*Support one MIIC, pin select to P35/P16 by MSDASEL (SFR B7h.7), pin select to P13/P02 by MSCLSEL (SFR B7h.6)

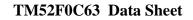

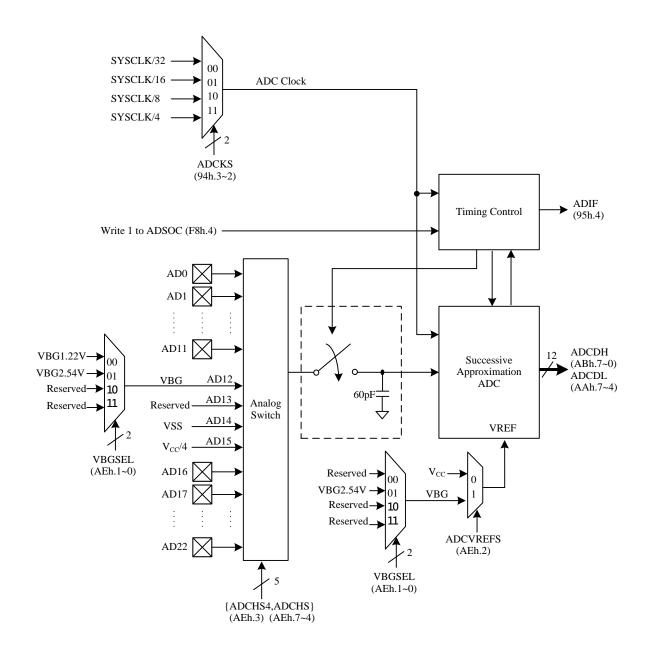

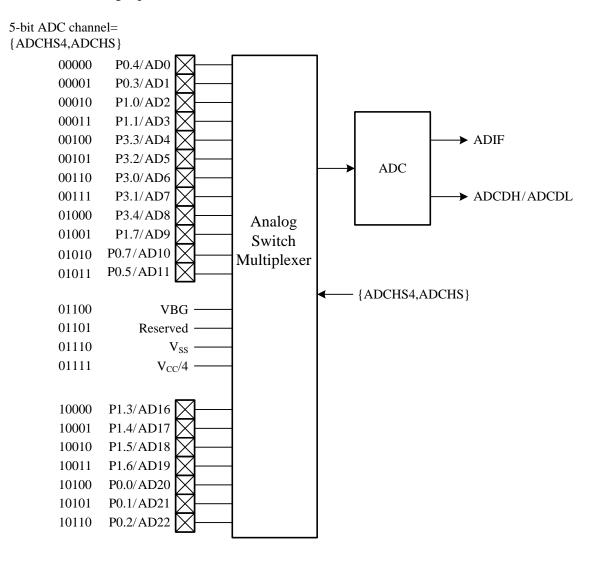

#### 11. 12-bit ADC with 19 channels External Pin Input and 3 channels Internal Reference Voltage

- Internal Reference Voltage (VBG):  $1.22V \pm 1.5\%$  @V<sub>CC</sub>= $2.5V \sim 5.5V$ ,  $25^{\circ}C$

- Internal Reference Voltage: V<sub>SS</sub> (0V)

- Internal Reference Voltage: V<sub>CC</sub>/4

- ADC reference voltage selection option:  $V_{CC}$  / 2.54V

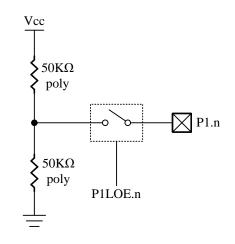

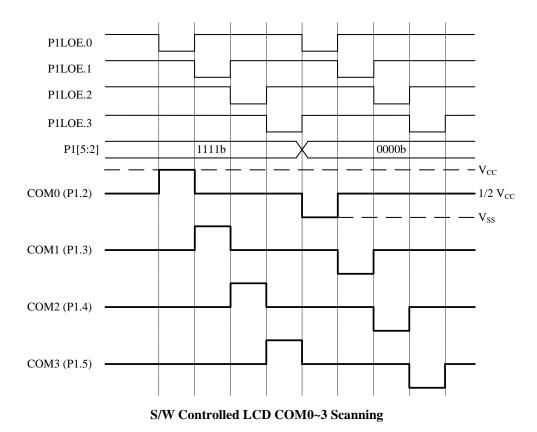

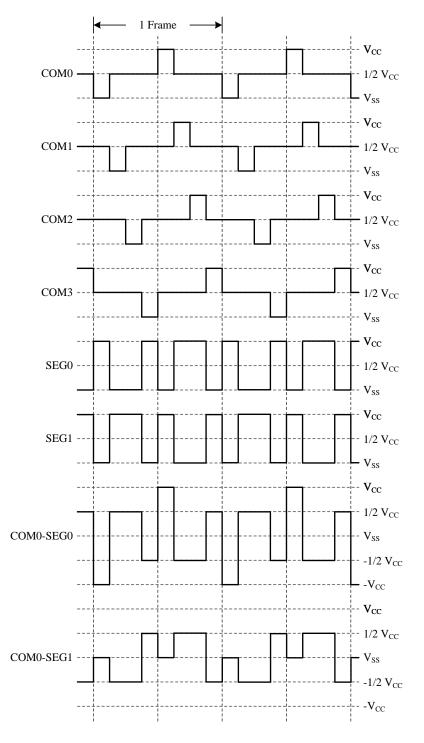

#### 12. LCD Driver

- Software controlled COM0~3

- 1/2 LCD Bias

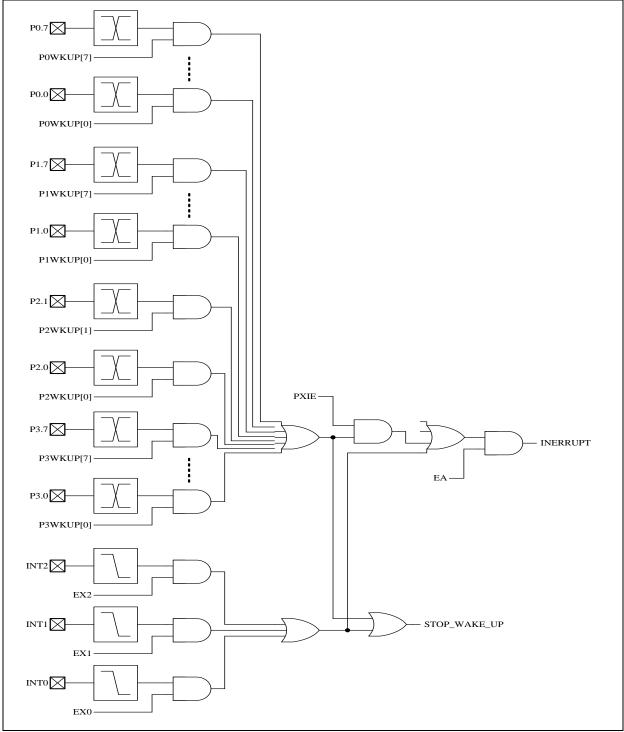

#### 13. 13 Sources, 4-level priority Interrupt

- Timer0/Timer1/Timer2/Timer3 Interrupt

- INT0/INT1 pin Falling-Edge/Low-Level Interrupt

- INT2 pin Falling-Edge Interrupt

- Port0/1/2/3 Pin Change Interrupt

- UART TX/RX Interrupt

- ADC Interrupt

- Master I<sup>2</sup>C (MIIC) interrupt

- LVD Interrupt

- PWM0/PWM1 interrupt

#### 14. Pin Interrupt can Wake up CPU from Power-Down (Halt/Stop) mode

- INT0~INT2 Interrupt & Wake-up

- Each Port0/1/2/3 pin can be defined as Interrupt & Wake-up pin (by pin change)

#### 15. Max. 26 Programmable I/O pins

- CMOS Output

- Pseudo-Open-Drain, or Open-Drain Output

- Schmitt Trigger Input

- Pin Pull-up can be Enabled or Disabled

#### 16. Independent RC Oscillating Watch Dog Timer

• 400ms/200ms/100ms/50ms selectable WDT timeout options

#### 17. Five types Reset

- Power on Reset

- Selectable External Pin Reset

- Selectable Watch Dog Reset

- Software Command Reset

- Selectable Low Voltage Reset

#### 18. 16-level Low Voltage Reset

2.25V / 2.40V / 2.55V / 2.70V / 2.80V / 2.95V / 3.10V / 3.25V / 3.40V / 3.55V / 3.70V / 3.85V / 4.0V / 4.15V / 4.30V / 4.45V

#### 19. 15-level Low Voltage Detect

2.40V / 2.55V / 2.70V / 2.80V / 2.95V / 3.10V / 3.25V / 3.40V / 3.55V / 3.70V / 3.85V / 4.0V / 4.15V / 4.30V / 4.45V

#### **20. Five Power Operation Modes**

• Fast/Slow/Idle/Halt/Stop mode

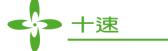

#### 21. Integrated 16-bit Cyclic Redundancy Check function

#### 22. Multiplication and division

- 8 bits Multiplier & Divider (standard 8051)

- 16 bits Multiplier & Divider

- 32 bits ÷ 16 bits Divider

#### 23. On-chip Debug/ICE interface

- Use P3.0/P3.1 pin or P2.0/P2.1 pin

- Share with ICP programming pin

- Mass production writer only supports P3.0/P3.1

#### 24. Operating Voltage and Current

- V<sub>CC</sub> =2.2V ~ 5.5V @F<sub>SYS</sub>=16.588 MHz

- $I_{CC} = 0.1 \mu A$  @Stop mode, PWRSAV=1,  $V_{CC} = 3V$

- $I_{CC} = 6\mu A$  @Halt mode, PWRSAV=1,  $V_{CC} = 3V$

- $I_{CC} = 9\mu A$  @Idle mode, PWRSAV=1, LVRPD=0x37,  $V_{CC}=3V$

#### 25. Operating Temperature Range

•  $-40^{\circ}C \sim +105^{\circ}C$

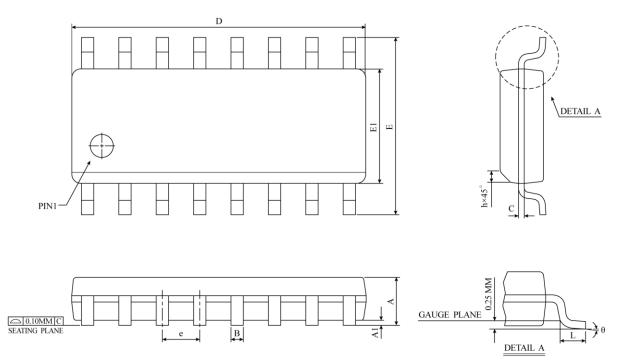

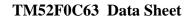

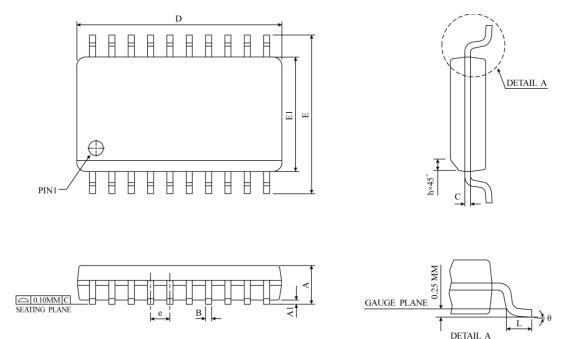

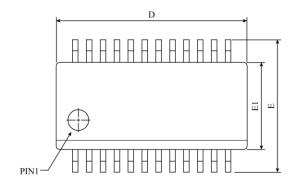

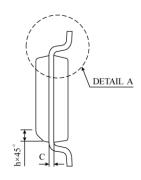

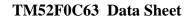

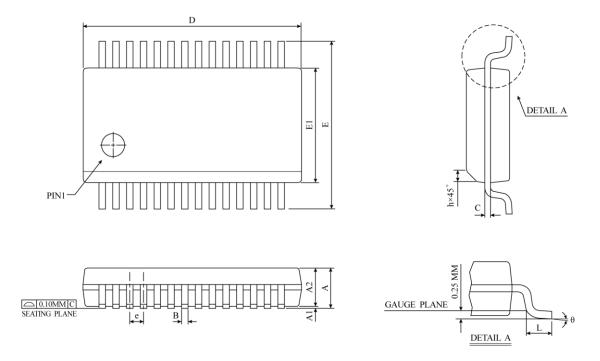

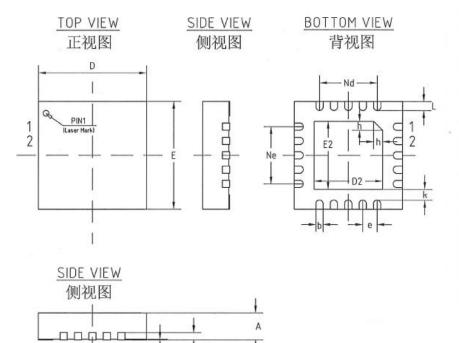

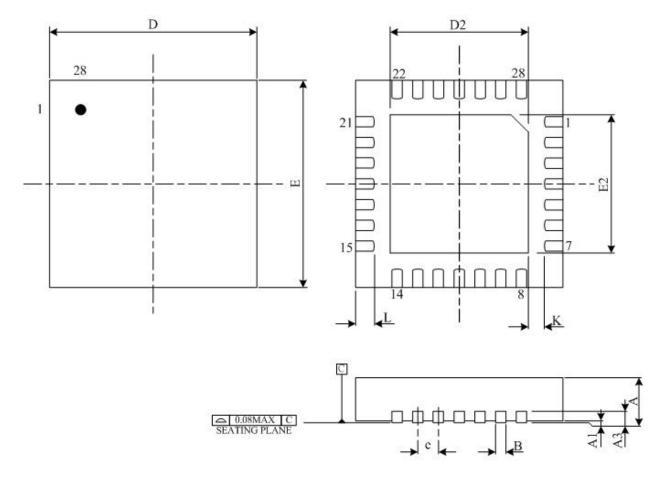

#### 26. Package Types

- 10-pin MSOP (118 mil)

- 16-pin SOP (150 mil)

- 20-pin TSSOP (173 mil)

- 20-pin SOP (300 mil)

- 20-pin QFN (3x3x0.75-0.4mm) (L=0.25mm)

- 24-pin SSOP (150 mil)

- 28-pin SOP (300 mil)

- 28-pin SSOP (150 mil)

- 28-pin QFN (4x4x0.75-0.4mm)

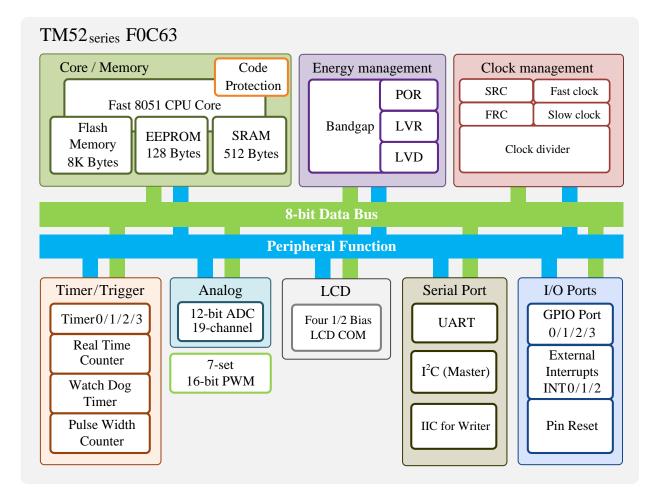

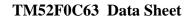

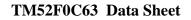

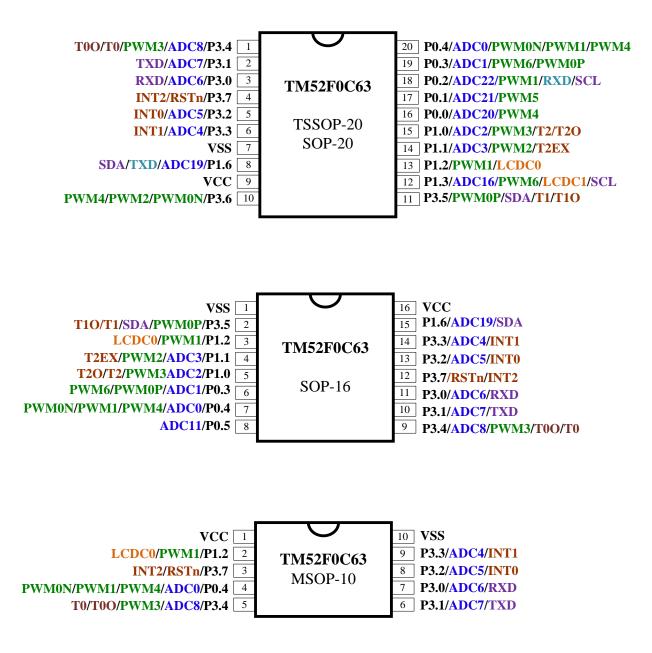

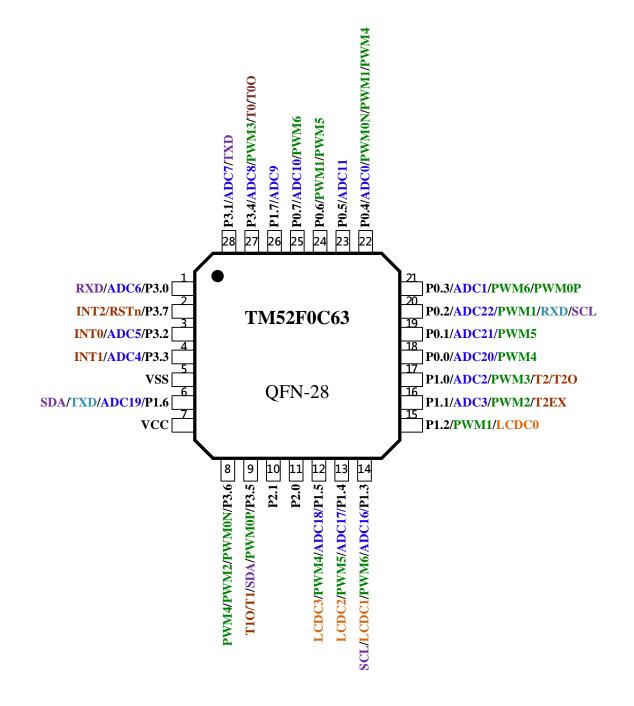

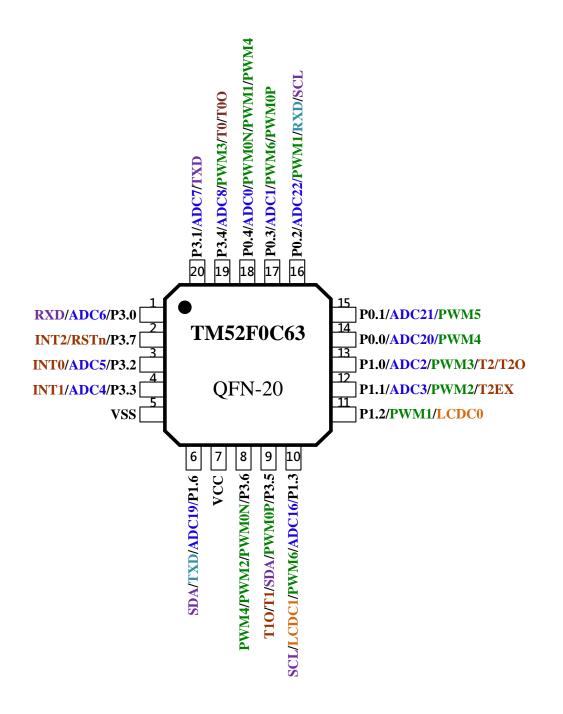

### PIN ASSIGNMENT

\*UART default pin is P30, P31, user can set P02, P16 instead by TXRXSEL (SFR 93h.7) \*Master I<sup>2</sup>C SDA default pin is P35, user can set P16 instead by MSDASEL (SFR B7h.7) \*Master I<sup>2</sup>C SCL default pin is P13, user can set P02 instead by MSCLSEL (SFR B7h.6)

For low power applications, all digital I/Os (including unbonding or unused) should avoid high-impedance settings.

## PIN DESCRIPTION

| Name                                             | In/Out | Pin Description                                                                                                                                                                                                                                  |

|--------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.0~P0.7<br>P1.0~P1.7<br>P2.0~P2.1<br>P3.3~P3.7 | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or<br>"open-drain" output. Pull-up resistors are assignable by software.<br>These pin's level change can interrupt/wake up CPU from Idle/Halt/Stop mode.              |

| P3.0~P3.2                                        | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or " <b>pseudo open drain</b> " output. Pull-up resistors are assignable by software.<br>These pin's level change can interrupt/wake up CPU from Idle/Halt/Stop mode. |

| INTO, INT1                                       | Ι      | External low level or falling edge Interrupt input, Idle/Halt/Stop mode wake up input.                                                                                                                                                           |

| INT2                                             | Ι      | External falling edge Interrupt input, Idle/Halt /Stop mode wake up input.                                                                                                                                                                       |

| RXD                                              | I/O    | UART Mode0 transmit & receive data, Mode1/2/3 receive data                                                                                                                                                                                       |

| TXD                                              | I/O    | UART Mode0 transmit clock, Mode1/2/3 transmit data. In One Wire UART mode, this pin transmits and receives serial data.                                                                                                                          |

| T0, T1, T2                                       | Ι      | Timer0, Timer1, Timer2 event count pin input.                                                                                                                                                                                                    |

| T2EX                                             | Ι      | Timer2 external trigger input.                                                                                                                                                                                                                   |

| T0O                                              | 0      | Timer0 overflow divided by 64 output                                                                                                                                                                                                             |

| T10                                              | 0      | Timer1 overflow divided by 2 output                                                                                                                                                                                                              |

| T2O                                              | 0      | Timer2 overflow divided by 2 output                                                                                                                                                                                                              |

| PWM1~PWM6<br>PWM0P/PWM0N                         | 0      | 16 bit PWM output                                                                                                                                                                                                                                |

| ADC0~ADC11,<br>ADC16~ADC22                       | Ι      | ADC input                                                                                                                                                                                                                                        |

| LCDC0~LCDC3                                      | 0      | LCD 1/2 bias output                                                                                                                                                                                                                              |

| SCL                                              | I/O    | Master I <sup>2</sup> C (MIIC) SCL                                                                                                                                                                                                               |

| SDA                                              | I/O    | Master I <sup>2</sup> C (MIIC) SDA                                                                                                                                                                                                               |

| RSTn                                             | Ι      | External active low reset input, Pull-up resistor is fixed enable.                                                                                                                                                                               |

| VCC, VSS                                         | Р      | Power input pin and ground                                                                                                                                                                                                                       |

## PIN SUMMERY

| Pin<br>Number |                           |      | I               | npu     | ıt             | C              | )utp              | ut         |     |     | lter<br>Fun |     |       | I    | MISC  |

|---------------|---------------------------|------|-----------------|---------|----------------|----------------|-------------------|------------|-----|-----|-------------|-----|-------|------|-------|

| QFN-28        | Pin Name                  | Type | Pull-up Control | Wake up | Ext. Interrupt | CMOS Push-Pull | Pseudo Open Drain | Open Drain | LCD | ADC | UART        | PWM | Timer | MIIC |       |

| 1             | RXD/ADC6/P3.0             | I/O  | 0               | •       |                | ٠              | ٠                 | •          |     | •   | ٠           |     |       |      |       |

| 2             | INT2/RSTn/P3.7            | I/O  | 0               | •       | •              | •              |                   | •          |     |     |             |     |       |      | Reset |

| 3             | INT0/ADC5/P3.2            | I/O  | 0               | •       | •              | •              | •                 | •          |     | •   |             |     |       |      |       |

| 4             | INT1/ADC4/P3.3            | I/O  | 0               | •       | ٠              | •              |                   | •          |     | •   |             |     |       |      |       |

| 5             | VSS                       | Р    |                 |         |                |                |                   |            |     |     |             |     |       |      |       |

| 6             | SDA/TXD/ADC19/P1.6        | I/O  | 0               | ٠       |                | ٠              |                   | ٠          |     | •   | ٠           |     |       | ٠    |       |

| 7             | VCC                       | Р    |                 |         |                |                |                   |            |     |     |             |     |       |      |       |

| 8             | PWM4/PWM2/PWM0N/P3.6      | I/O  | 0               | •       |                | •              |                   | ٠          |     |     |             | ٠   |       |      |       |

| 9             | T10/T1/SDA/PWM0P/P3.5     | I/O  | 0               | •       |                | •              |                   | •          |     |     |             | •   | •     | •    | T1O   |

| 10            | P2.1                      | I/O  | 0               | ٠       |                | •              |                   | ٠          |     |     |             |     |       |      |       |

| 11            | P2.0                      | I/O  | 0               | ٠       |                | •              |                   | ٠          |     |     |             |     |       |      |       |

| 12            | LCDC3/PWM4/ADC18/P1.5     | I/O  | 0               | ٠       |                | •              |                   | ٠          | •   | ٠   |             | ٠   |       |      |       |

| 13            | LCDC2/PWM5/ADC17/P1.4     | I/O  | 0               | •       |                | •              |                   | •          | •   | •   |             | ٠   |       |      |       |

| 14            | SCL/LCDC1/PWM6/ADC16/P1.3 | I/O  | 0               | •       |                | •              |                   | •          | •   | •   |             | ٠   |       | •    |       |

| 15            | LCDC0/PWM1/P1.2           | I/O  | 0               | •       |                | •              |                   | •          | •   |     |             | •   |       |      |       |

| 16            | T2EX/PWM2/ADC3/P1.1       | I/O  | 0               | ٠       |                | ٠              |                   | ٠          |     | ٠   |             | ٠   | •     |      |       |

| 17            | T2O/T2/PWM3/ADC2/P1.0     | I/O  | 0               | ۲       |                | •              |                   | ۲          |     | •   |             | •   | •     |      | T2O   |

| 18            | PWM4/ADC20/P0.0           | I/O  | ۲               | ۲       |                | ٠              |                   |            |     | ۲   |             | ٠   |       |      |       |

| 19            | PWM5/ADC21/P0.1           | I/O  | ۲               | •       |                | •              |                   |            |     | •   |             | •   |       |      |       |

| 20            | SCL/RXD/PWM1/ADC22/P0.2   | I/O  | ۲               | •       |                | ٠              |                   |            |     | ٠   | ٠           | ٠   |       | •    |       |

| 21            | PWM0P/PWM6/ADC1/P0.3      |      | ۲               | ۲       |                | •              |                   |            |     | •   |             | •   |       |      |       |

| 22            | PWM4/PWM1/PWM0N/ADC0/P0.4 | I/O  | ۲               | ٠       |                | ٠              |                   |            |     | ٠   |             | ٠   |       |      |       |

| 23            | ADC11/P0.5                | I/O  | ۲               | •       |                | •              |                   |            |     | •   |             |     |       |      |       |

| 24            | PWM5/PWM1/P0.6            | I/O  | ۲               | •       |                | ٠              |                   |            |     |     |             | ٠   |       |      |       |

| 25            | PWM6/ADC10/P0.7           | I/O  | ۲               | •       |                | •              |                   |            |     | •   |             | ٠   |       |      |       |

| 26            | ADC9/P1.7                 | I/O  | 0               | •       |                | •              |                   | ٠          |     | •   |             |     |       |      |       |

| 27            | /T00 /T0/PWM3/ADC8/P3.4   | I/O  | 0               | •       |                | •              |                   | •          |     | •   |             | •   | •     |      | TOO   |

| 28            | TXD /ADC7/P3.1            | I/O  | 0               | •       |                | •              | •                 | •          |     | •   | ٠           |     |       |      |       |

PS:

• Port1, P2.0, P2.1, Port3 these pins control Pull up resistor by operation modes

● Port0 control Pull up resistor while POOE.n=0 and P0.n=1

## FUNCTIONAL DESCRIPTION

#### 1. CPU Core

In the 8051 architecture, the C programming language is used as a development platform. The TM52 device features a fast 8051 core in a highly integrated microcontroller, allowing designers to be able to achieve improved performance compared to a classic 8051 device. TM52 series microcontrollers provide a complete binary code with standard 8051 instruction set compatibility, ensuring an easy migration path to accelerate the development speed of system products. The CPU core includes an ALU, a program status word (PSW), an accumulator (ACC), a B register, a stack point (SP), DPTRs, a program counter, an instruction decoder, and core special function registers (SFRs).

#### **1.1 Accumulator (ACC)**

This register provides one of the operands for most ALU operations. Accumulators are generally referred to as A or Acc and sometimes referred to as Register A. In this document, the accumulator is represented as "A" or "ACC" including the instruction table. The accumulator, as its name suggests, is used as a general register to accumulate the intermediate results of a large number of instructions. The accumulator is the most important and frequently used register to complete arithmetic and logical operations. It holds the intermediate results of most arithmetic and logic operations and assists in data transportation.

| SFR E0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| ACC     | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

E0h.7~0 ACC: Accumulator

#### 1.2 B Register (B)

The "B" register is very similar to the ACC and may hold a 1 Byte value. This register provides the second operand for multiply or divide instructions. Otherwise, it may be used as a scratch pad register. The B register is only used by two 8051 instructions, MUL and DIV. When A is to be multiplied or divided by another number, the other number is stored in B. For MUL and DIV instructions, it is necessary that the two operands are in A and B.

#### ex: DIV AB

When this instruction is executed, data inside A and B are divided, and the answer is stored in A.

| SFR F0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| В       | B.7   | B.6   | B.5   | B.4   | B.3   | B.2   | B.1   | B.0   |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

F0h.7~0 **B:** B register

#### 1.3 Stack Pointer (SP)

The SP register contains the Stack Pointer. The Stack Pointer is used to load the program counter into memory during LCALL and ACALL instructions and is used to retrieve the program counter from memory in RET and RETI instructions. The stack may also be saved or loaded using PUSH and POP instructions, which also increment and decrement the Stack Pointer.

| SFR 81h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| SP      |       |       |       | S     | Р     |       |       |       |

| R/W     |       |       |       | R/    | W     |       |       |       |

| Reset   | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

81h.7~0 **SP:** Stack Point

#### **1.4 Dual Data Pointer (DPTRs)**

TM52 device has two DPTRs, which share the same SFR address. Each DPTR is 16 bits in size and consists of two registers: the DPTR high byte (DPH) and the DPTR low byte (DPL). The DPTR is used for 16-bit-address external memory accesses, for offset code byte fetches, and for offset program jumps. Setting the DPSEL control bit allows the program code to switch between the two physical DPTRs.

| DPL DPL R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |   |   | PL | ום |   |   |   |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|----|----|---|---|---|-------|

| P/W P/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |   |   |    |    |   |   |   | DPL   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   | W  | R/ |   |   |   | R/W   |

| Reset         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <th>0</th> <th>0</th> <th>0</th> <th>0</th> <th>0</th> <th>0</th> <th>0</th> <th>0</th> <th>Reset</th> | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 | Reset |

82h.7~0 **DPL:** Data Point low byte

| SFR <b>83h</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| DPH            |       | DPH   |       |       |       |       |       |       |  |  |  |  |

| R/W            |       | R/W   |       |       |       |       |       |       |  |  |  |  |

| Reset          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

83h.7~0 **DPH:** Data Point high byte

| SFR F8h | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1 | Bit 0 |

|---------|--------|--------|-------|-------|---------|---------|-------|-------|

| AUX1    | CLRWDT | CLRTM3 | VBGEN | ADSOC | CLRPWM0 | CLRPWM1 | _     | DPSEL |

| R/W     | R/W    | R/W    | R/W   | R/W   | R/W     | R/W     |       | R/W   |

| Reset   | 0      | 0      | 0     | 0     | 1       | 1       |       | 0     |

F8h.0 **DPSEL:** Active DPTR Select

#### **1.5 Program Status Word (PSW)**

This register contains status information resulting from CPU and ALU operations. The instructions that affect the PSW are listed below.

| Instruction |   | Flag |    |

|-------------|---|------|----|

| Instruction | С | OV   | AC |

| ADD         | Х | Х    | Х  |

| ADDC        | Х | X    | Х  |

| SUBB        | Х | Х    | Х  |

| MUL         | 0 | X    |    |

| DIV         | 0 | Х    |    |

| DA          | Х |      |    |

| RRC         | Х |      |    |

| RLC         | Х |      |    |

| SETB C      | 1 |      |    |

| Instruction |   | Flag |    |

|-------------|---|------|----|

| mstruction  | С | OV   | AC |

| CLR C       | 0 |      |    |

| CPL C       | Х |      |    |

| ANL C, bit  | Х |      |    |

| ANL C, /bit | Х |      |    |

| ORL C, bit  | Х |      |    |

| ORL C, /bit | Х |      |    |

| MOV C, bit  | Х |      |    |

| CJNE        | Х |      |    |

|             |   |      |    |

A "0" means the flag is always cleared, a "1" means the flag is always set and an "X" means that the state of the flag depends on the result of the operation.

| SFR D0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| PSW     | CY    | AC    | F0    | RS1   | RS0   | OV    | F1    | Р     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

D0h.7 **CY:** ALU carry flag

D0h.6 AC: ALU auxiliary carry flag

D0h.5 **F0:** General purpose user-definable flag

D0h.4~3 **RS1, RS0:** The contents of (RS1, RS0) enable the working register banks as:

00: Bank 0 (00h~07h)

01: Bank 1 (08h~0Fh)

10: Bank 2 (10h~17h)

11: Bank 3 (18h~1Fh)

- D0h.2 **OV:** ALU overflow flag

- D0h.1 **F1:** General purpose user-definable flag

- D0h.0 **P:** Parity flag. Set/cleared by hardware each instruction cycle to indicate odd/even number of "one" bits in the accumulator.

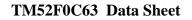

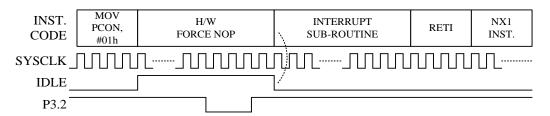

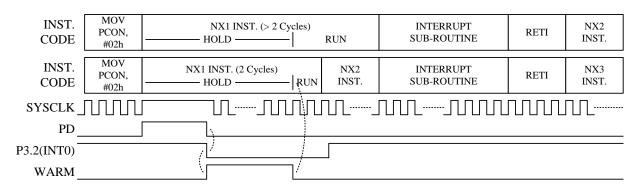

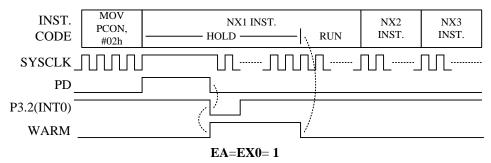

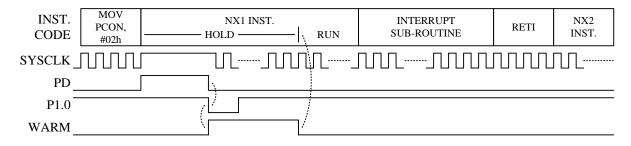

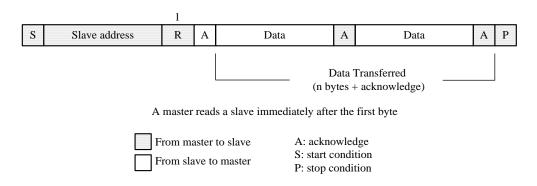

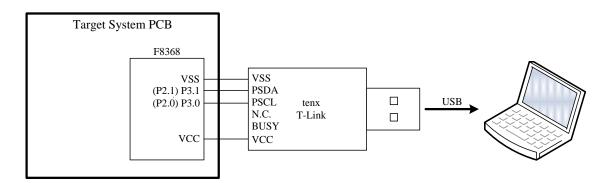

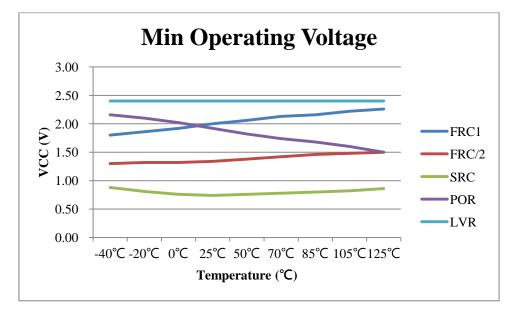

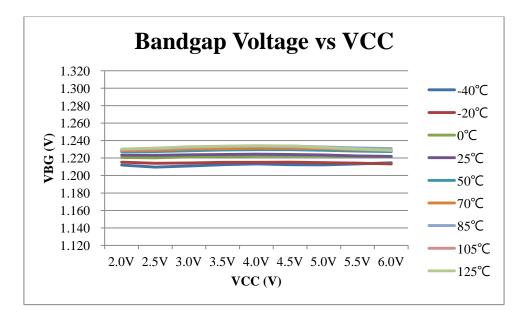

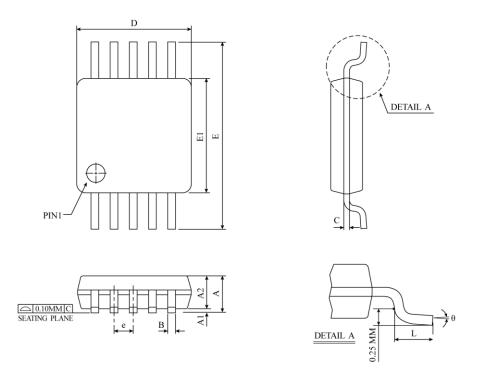

|       |       | PS               | W                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                  | ]                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |