*Rev V0.90*

**tenx** reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. **tenx** does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. **tenx** products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses tenx products for any such unintended or unauthorized application, Buyer shall indemnify and hold tenx and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that tenx was negligent regarding the design or manufacture of the part.

# **AMENDMENT HISTORY**

| Version | Date      | Description  |

|---------|-----------|--------------|

| 0.90    | Apr, 2018 | New release. |

# CONTENTS

| MENDMENT HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERAL DESCRPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PIN ASSIGNMENT DIAGRAM 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIN DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| in Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1. CPU Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.1Accumulator (ACC)141.2B Register (B)141.3Stack Pointer (SP)141.4Dual Data Pointer (DPTRs)151.5Program Status Word (PSW)16                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2. Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1       Program Memory       17         2.1.1       Program Memory Functional Partition       17         2.1.2       Flash ICP Mode       17         2.1.3       Flash IAP Mode       18         2.1.4       IAP Mode Access Routines       19         2.1.5       Flash ISP Mode       20         2.2       Data Memory       21         2.2.1       IRAM       22         2.2.2       XRAM       22         2.2.3       SFRs       22         3.       Power       24         MODE3V=0       24         MODE3V=1       24 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.1Power on Reset264.2External Pin Reset264.3Software Reset264.4Watch Dog Timer Reset (WDT)264.5Low Voltage Reset264.6USB Plug Reset26                                                                                                                                                                                                                                                                                                                                                                                        |

| 5. Clock Circuitry & Operation Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.1 System Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.2          | USB Clock                             | .28  |

|--------------|---------------------------------------|------|

| 5.3          | Operation Mode                        | . 29 |

| 6. Inte      | errupt and Wake-up                    | .30  |

| 6.1          | Interrupt Enable and Priority Control | .30  |

| 6.2          | Pin Interrupt                         |      |

| 6.3          | Idle Mode Wake up and Interrupt       | . 34 |

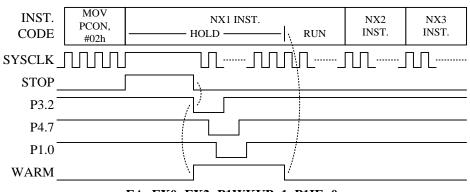

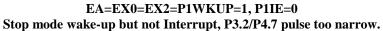

| 6.4          | Stop Mode Wake up and Interrupt       | .34  |

| 6.5          | USB interrupt                         | .36  |

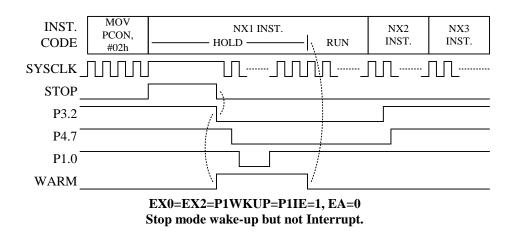

| 7. I/O       | Ports                                 | .37  |

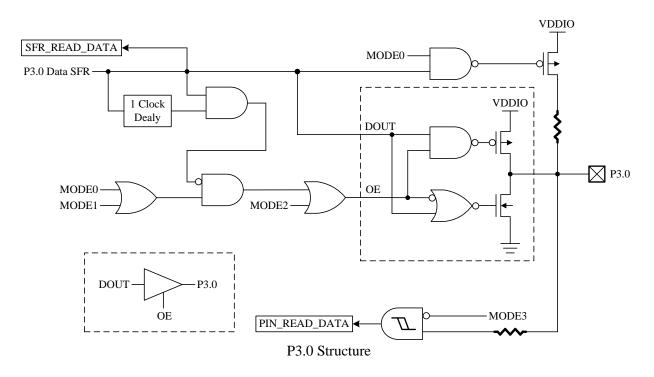

| 7.1          | Port1 & Port3 & P4                    | . 37 |

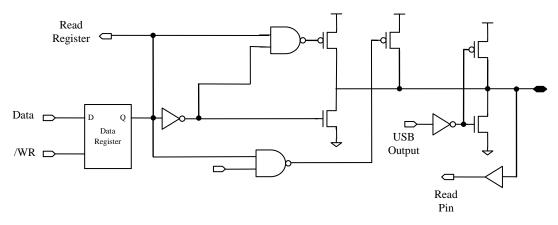

| 7.2          | P1.2 (DP) and P1.3 (DM)               | .40  |

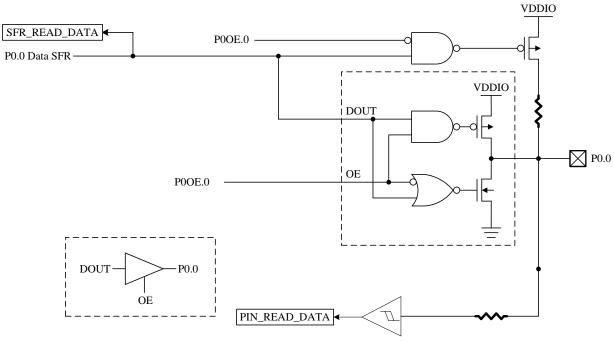

| 7.3          | Port0 & Port2 & Port5.0               | .45  |

| 8. Tin       | ners                                  | . 48 |

| 8.1          | Timer0/1                              | .48  |

| 8.2          | Timer2                                | .49  |

| 8.3          | T0O and T2O Output Control            | .51  |

| 9. UA        | RT                                    | .52  |

| 10. F        | PWMs                                  | .54  |

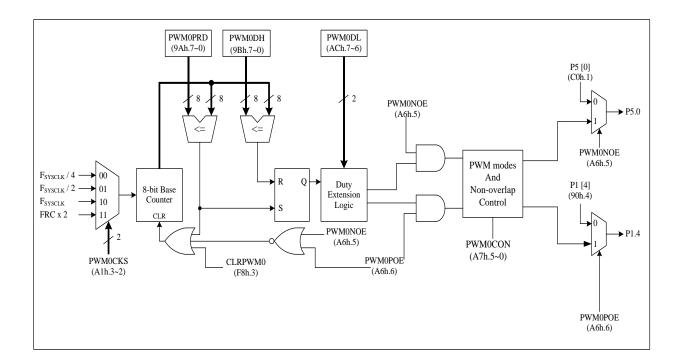

| 10.1         | PWM0                                  | .54  |

| 10.2         | PWM1                                  |      |

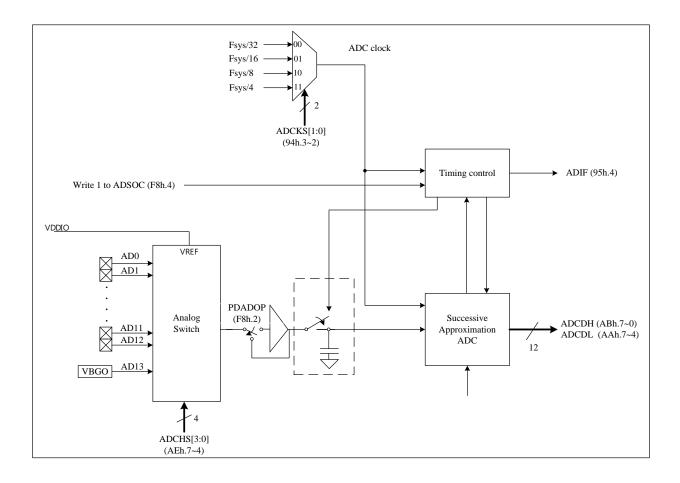

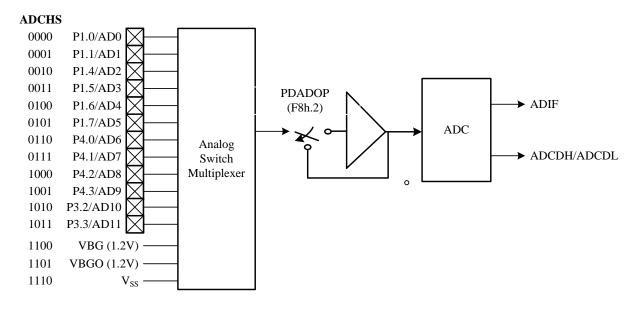

| 11. A        | \DC                                   | .61  |

| 11.1         | ADC Channels                          | . 62 |

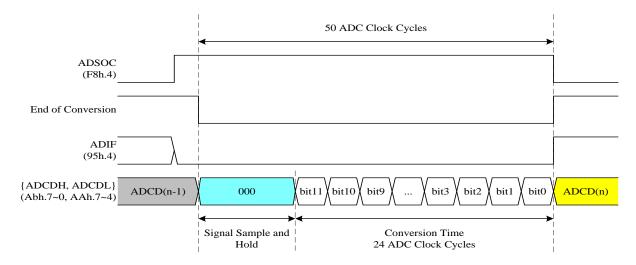

| 11.2         | ADC Conversion Time                   | . 63 |

| 12. U        | JSB Interface                         | .65  |

| 12.1         | USB Device Address                    | . 65 |

| 12.2         | Endpoint 0 Receive (SET0/OUT0)        |      |

| 12.3         | Endpoint 0 Transmit (TX0)             | .66  |

| 12.4         | Endpoint 1/2 Transmit (TX1/2)         |      |

| 12.5         | Endpoint 3 Transmit (TX3)             |      |

| 12.6         | USB Endpoint 4 Receive (RC4)          |      |

| 12.7         | USB Control and Status                |      |

| 12.8<br>12.9 | Suspend and ResumeUSB Keyboard        |      |

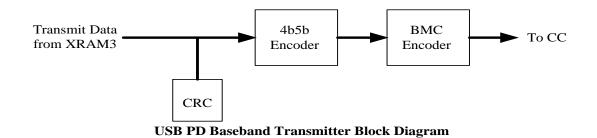

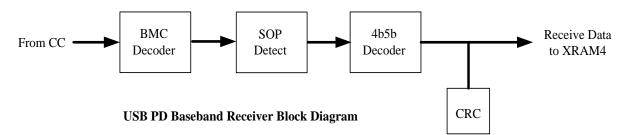

| 12.10        | USB PD                                |      |

|              | erial Peripheral Interface            |      |

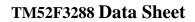

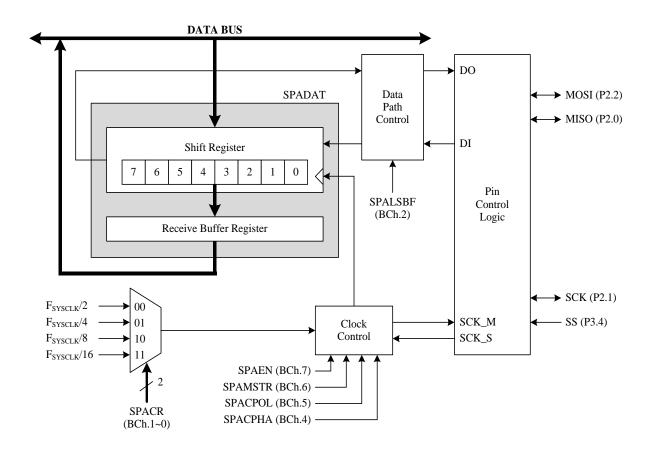

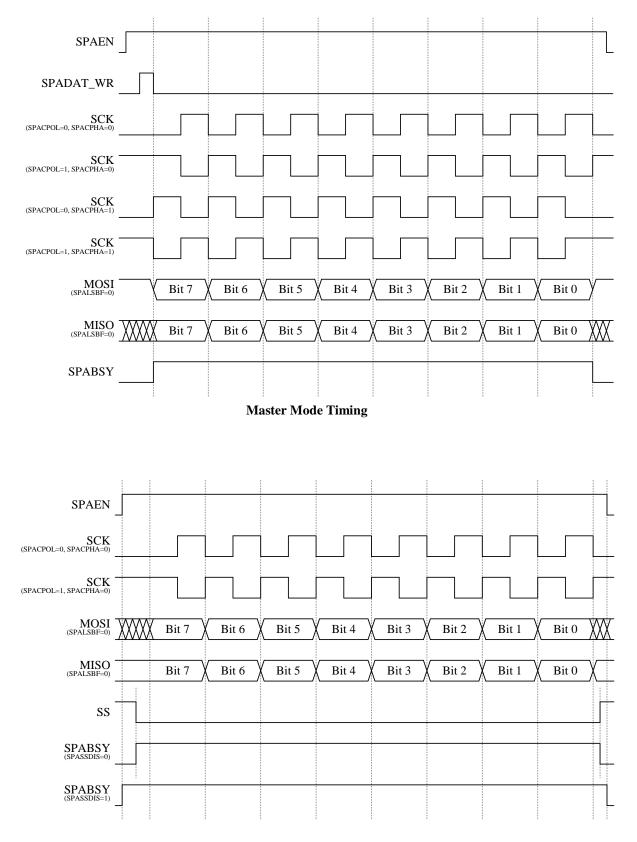

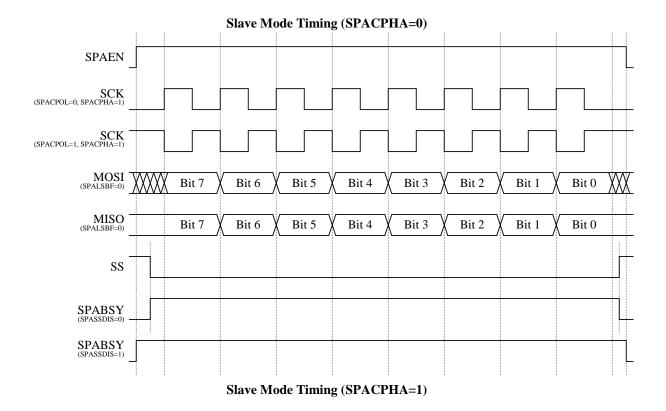

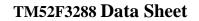

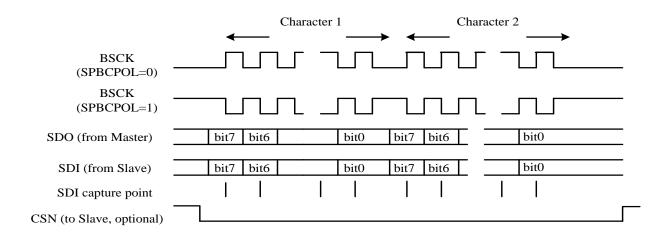

| 13.1         | Serial Peripheral Interface (SPIA)    |      |

| 13.1         |                                       |      |

| 13.          |                                       |      |

| 13.          |                                       |      |

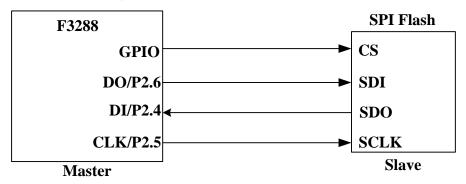

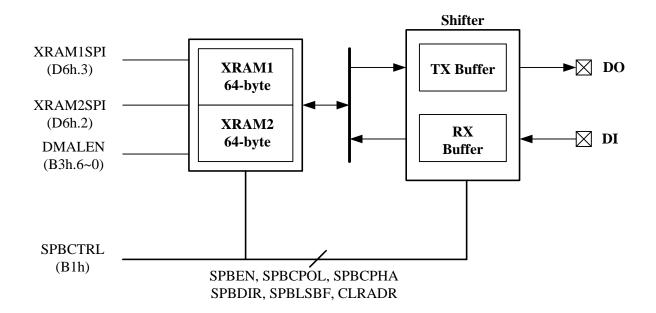

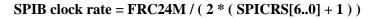

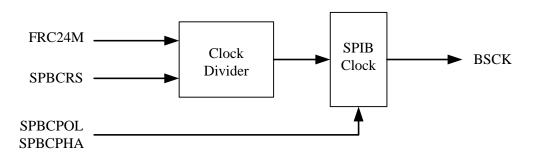

| 13.2         | Serial Peripheral Interface B (SPIB)  | . 81 |

|       | 13.2.1           | SPIB Functional Description                                                                                       | .81  |

|-------|------------------|-------------------------------------------------------------------------------------------------------------------|------|

|       | 13.2.2           | SPIB System Block diagram and Register Control                                                                    | .82  |

|       | 13.2.3           | SPIB Clock and Data Format                                                                                        |      |

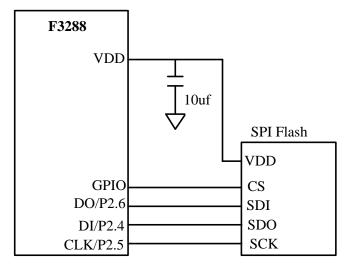

|       | 13.2.4           | SPIB Power Circuit                                                                                                | . 85 |

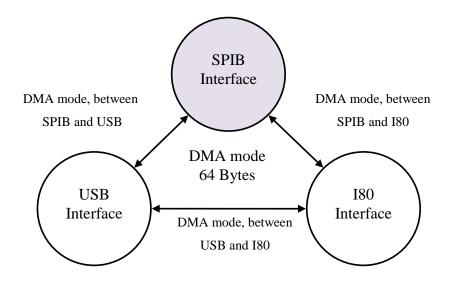

|       | 13.2.5           | SPIB DMA Transfer Mode                                                                                            | .85  |

|       | 13.2.6           | SPIB Initial Sample Code                                                                                          | . 87 |

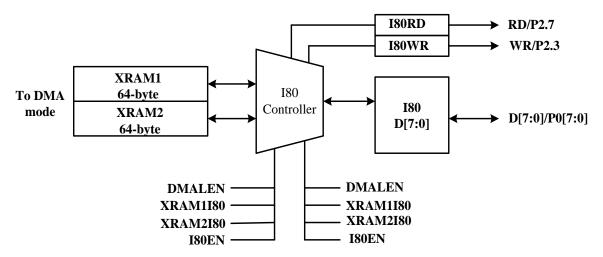

| 14.   | <b>I80 I</b>     | Peripheral Interface (I80)                                                                                        | . 88 |

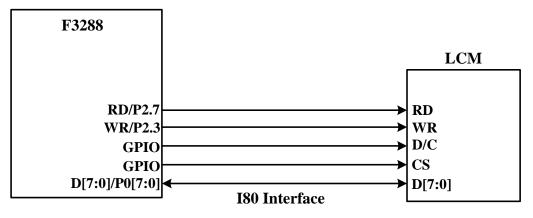

| 1     | 4.1 I8           | 0 Functional Description                                                                                          | . 88 |

| 1     | 4.2 I8           | 0 System Block Diagram and Register Control                                                                       | . 88 |

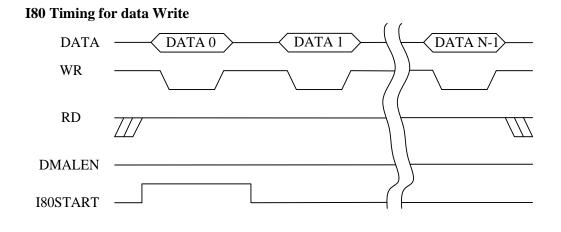

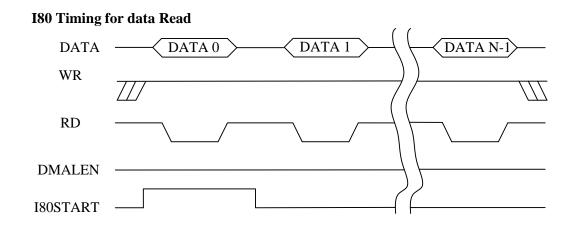

| 1     |                  | 0 Clock and Data Format                                                                                           |      |

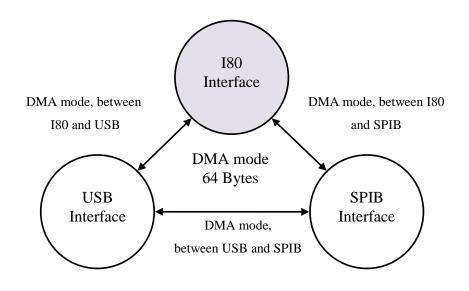

| 1     | 4.4 I8           | 0 DMA Transfer Mode                                                                                               | .90  |

| 1     | 4.5 I8           | 0 Initial Sample Code                                                                                             | .92  |

| 15.   | In C             | ircuit Emulation (ICE) Mode                                                                                       | .93  |

| SFR a | & CFGV           | V MAP                                                                                                             | .94  |

| SFR a | & CFGV           | V DESCRIPTION                                                                                                     | .97  |

| INST  | RUCTIO           | DN SET1                                                                                                           | 112  |

| ELE(  | CTRICA           | L CHARACTERISTICS1                                                                                                | 115  |

| 1.    | Absolu           | te Maximum Ratings (T <sub>A</sub> =25 <sup>°</sup> C)1                                                           | 115  |

| 2.    | DC Ch            | aracteristics (T <sub>A</sub> =25 <sup>°</sup> C, V <sub>CC</sub> =2.0V ~ 5.5V)                                   | 115  |

| 3.    | Clock '          | Fiming $(T_A = -40^{\circ}C \sim +85^{\circ}C, V_{CC} = 3.0V \sim 5.5V)$                                          | 117  |

| 4.    | Reset 7          | Timing Characteristics ( $T_A = -40^{\circ}C \sim +85^{\circ}C$ , $V_{CC} = 3.0V \sim 5.0V$ )                     | 117  |

| 5.    | ADC E            | Clectrical Characteristics (T <sub>A</sub> =25 <sup>°</sup> C, V <sub>CC</sub> =3.0V ~ 5.5V, V <sub>SS</sub> =0V) | 117  |

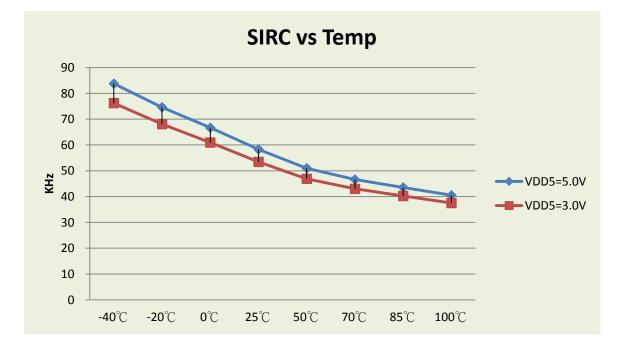

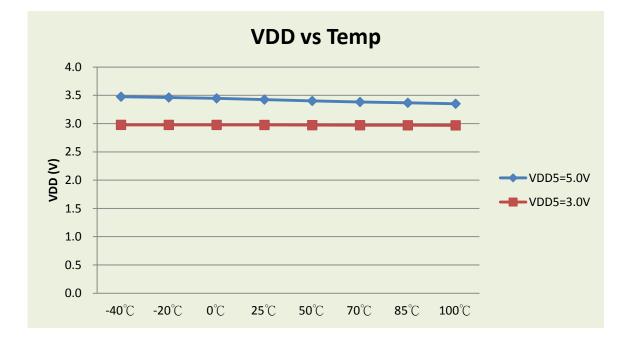

| 6.    | Charao           | cteristics Graphs1                                                                                                | 118  |

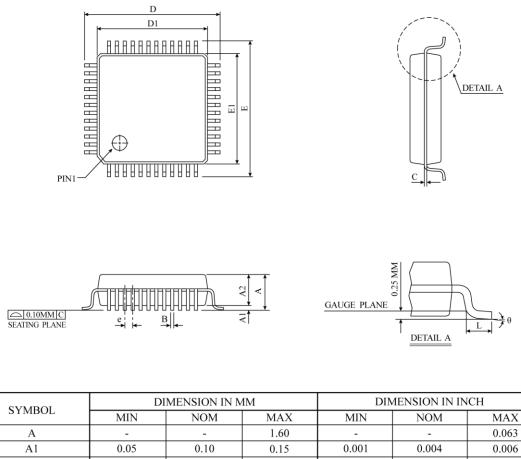

| PACI  | KAGE IN          | NFORMATION                                                                                                        | 121  |

| Packa | ige Infor        | mation1                                                                                                           | 122  |

| LQ    | <b>FP 48-p</b> i | in (7x7 mm) Package Dimensions                                                                                    | 122  |

\_\_\_\_\_

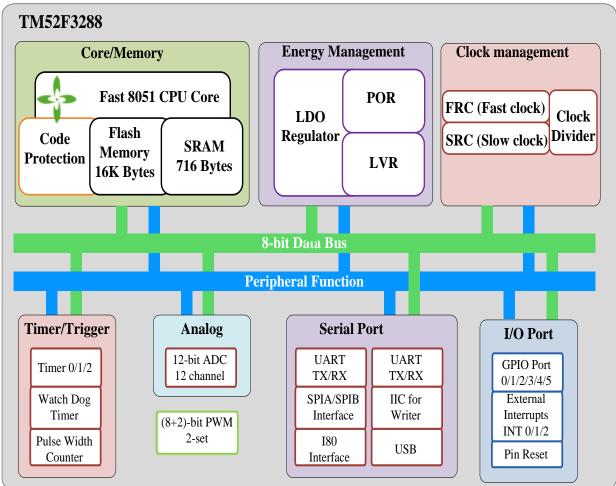

### **GENERAL DESCRPTION**

**TM52F3288** is version of a new, fast 8051 architecture for an 8-bit microcontroller single chip with an instruction set fully compatible with industry standard 8051, C language development platform, and retains most 8051 peripheral function block and contain the USB full speed general purpose application. Typically, the TM52 executes instruction six times faster than the traditional 8051 architecture.

The **TM52F3288** provides improved performance, lower cost and fast time-to-market by integrating features on the chip, including 16K Bytes Flash program memory, 716 Bytes SRAM, Low Voltage Reset (LVR), dual clock power saving operation mode, 2 set SPI Interface, 8051 standard UART and Timer0/1/2, 2 set (8+2)-bit PWMs, 12 channels 12-bit A/D Convert and Watchdog Timer. Its high reliability and lower power consummation feature can be widely applied in consummation and home appliance products. It can works in USB mode by using USB power or works in standalone mode by using battery power.

#### **BLOCK DIAGRAM**

### **FEATURES**

#### 1. Standard 8051 Instruction Set, fast machine cycle

- Execute instructions six times faster than standard 8051

#### 2. 16 K Bytes Flash Program Memory

- Support "In Circuit Programming" (ICP) or "In System Programming" (ISP) for the Flash Code

- Byte Write "In Application Programming" (IAP) mode is convenient as Data EEPROM access

- Code Protection Capability

#### 3. Total 716 Bytes SRAM (IRAM + XRAM)

- 256 Bytes IRAM in the 8051 internal data memory area

- 460 Bytes XRAM in the 8051 external data memory area (accessed by MOVX Instruction)

#### 4. Two System Clock type Selection

- Fast clock from Internal RC (FRC, 11.0592 MHz)

- Slow clock from Internal RC (SRC, 32KHz)

- System clock can be divided by 1/2/4/16 option

#### 5. 8051 Standard Timer -- Timer0/1/2

- 16-bit Timer0, also supports TOO clock output for Buzzer application

- 16-bit Timer1

- 16-bit Timer2, also supports T2O clock output for Buzzer application

#### 6. USB Interface

- Compliance with the Universal Serial Bus specification v2.0 Full Speed

- Support USB Power Delivery specification R2.0

- Built-in USB Transceiver 3.3V regulator

- Endpoint 0: Control SETUP /IN/OUT transfer (each 8 bytes)

- Endpoint 1: INTERRUPT IN transfer (8 bytes)

- Endpoint 2: INTERRUPT IN transfer (8 bytes)

- Endpoint 3: BULK IN transfer with Ping-Pong feature (2\*64 bytes)

- Endpoint 4: BULK OUT transfer with Ping-Pong feature (2\*64 bytes)

- USB PD transfer (38 bytes)

- USB PD receiver (38 bytes)

- 7. 12-bit ADC convert with 12 input channels

- 8. 8051 Standard UART

- One Wire UART option can be used for ISP or other application

#### 9. Two SPI Interface

#### SPIA:

- Master or Slave mode selectable

- Programmable transmit bit rate

- Serial clock phase and polarity options

- MSB-first or LSB-first selectable

#### SPIB:

- Support Master only

- Clock rate up to 12Mbps

- Read/Write DMA mode

- Serial clock phase and polarity options

- MSB-first or LSB-first selectable

#### 10. I80 Interface (Nand-Flash Interface)

- compatible with 8-bit parallel interface

- Read/Write DMA mode

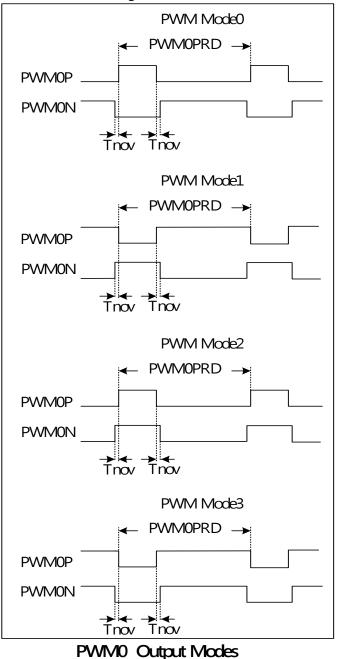

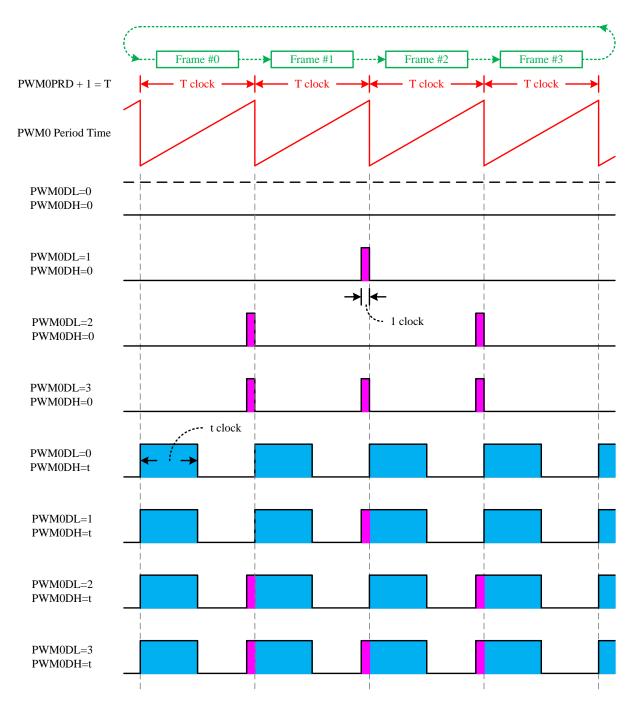

#### 11. Two independent "8+2" bits PWMs with prescaler/period-adjust

- PWM0:

- Width differential output pair

- Non-overlap durations adjustable

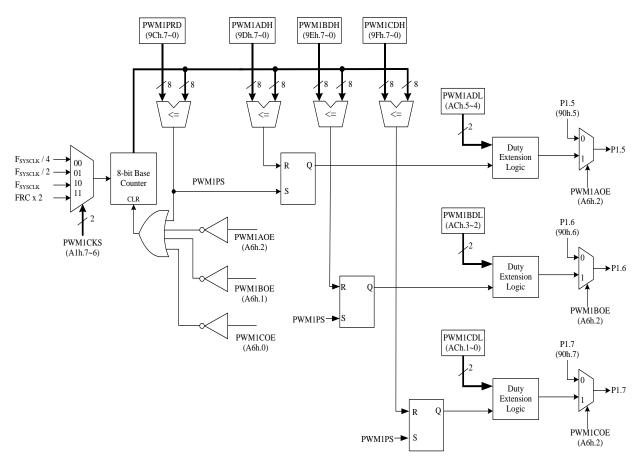

- PWM1:

3 output with different duty but share the same period

#### 12. Pin Interrupt can Wake up CPU from Power-Down (Stop) mode

- P3.2 / P3.3 (INT0 / INT1) Interrupt & Wake-up

- P4.7 (INT2) Interrupt & Wake-up

- Each Port1 pin can be defined as Interrupt & Wake-up pin (by pin change)

#### 13. 24 Sources, 4-level priority Interrupt

- Timer0/Timer1/Timer2 Interrupt

- INT0/INT1 Falling-Edge/Low-Level Interrupt

- Port1 Pin Change Interrupt

- UART TX/RX Interrupt

- P4.7 (INT2) Interrupt

- ADC End of Conversion Interrupt

- SPIA Interrupt

- USB1 Interrupt: SET0I/OUT0I/TX0I/TX1I/TX2I/SUSPI/TX3I/RC4I

- USB2 Interrupt: VDD5VRI/RSTI/RSMI/KBDI/PD\_TXI/PD\_RCI

#### 14. Max. 41 Programmable I/O pins

- CMOS Output

- Pseudo-Open-Drain, or Open-Drain Output

- Schmitt Trigger Input

- Pin Pull-up can be Enabled or Disabled

- P4.4 and P4.5 support high drive/sink current(Max. 40mA)

#### 15. Independent RC Oscillating Watchdog Timer

- 400ms/200ms/100ms/50ms Selectable WDT Timeout options

#### 16. Six type Reset

- Power on Reset

- Selectable External Pin Reset

- Selectable Watch Dog Reset

- Software Command Reset

- Selectable Battery Low Voltage Reset

- USB Plug-out Reset

#### 17. 3-level Low Voltage Reset

- 2.0V/2.3V/2.9V

#### **18. 4 Power Saving Operation Modes**

- Fast / Slow / Idle / Stop Mode

#### **19. On-chip Debug/ICE interface**

- Use P1.2/P1.3 pin or P3.6/P3.7 pin (in USB application)

- Share with ICP programming pin (P1.2/P1.3)

- 20. Operating Voltage: 4.5V~5.5V in USB application or 3.0~5.5 in non-USB application

- **21.** Operating Temperature Range

- -40C ~+85C

- **22.** 48-pin LQFP Package (7x7x1.4mm)

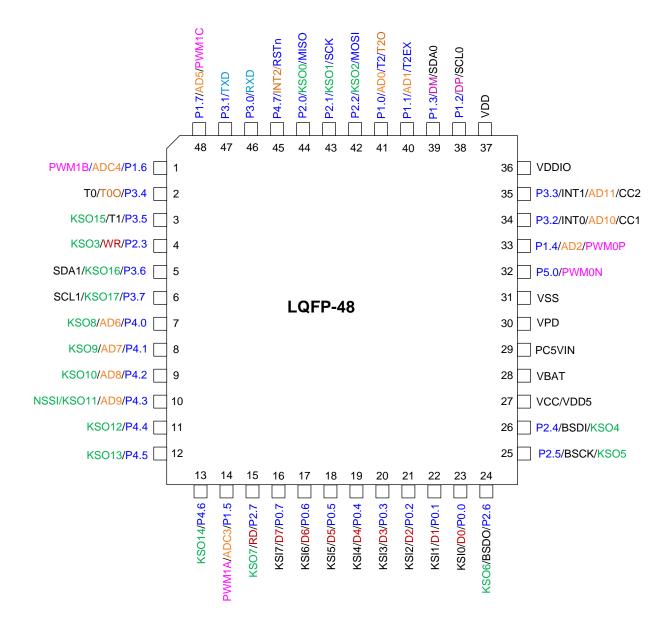

### PIN ASSIGNMENT DIAGRAM

### **PIN DESCRIPTIONS**

| Name          | In/Out | Pin Description                                                                                                                |

|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| P0.0-P0.7     | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output.                                                    |

| 10.0-10.7     | 1/0    | Pull-up resistors are assignable by software.                                                                                  |

|               |        | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or                                                  |

| P1.0~P1.7     | I/O    | "open-drain" output. Pull-up resistors are assignable by software. These pin's                                                 |

|               |        | level change can wake up CPU from Idle/Stop mode                                                                               |

| P2.0~P2.7     | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output.                                                    |

|               |        | Pull-up resistors are assignable by software.<br>Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or |

| P3.0~P3.2     | I/O    | "pseudo open drain" output. Pull-up resistors are assignable by software.                                                      |

|               |        | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or                                                  |

| P3.3~P3.7     | I/O    | "open-drain" output. Pull-up resistors are assignable by software.                                                             |

|               | 7/0    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or                                                  |

| P4.0~P4.7     | I/O    | "open-drain" output. Pull-up resistors are assignable by software.                                                             |

| D5 ()         | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output.                                                    |

| P5.0          | I/O    | Pull-up resistors are assignable by software.                                                                                  |

| INT0, INT1    | Ι      | External Low level or falling edge Interrupt input, Idle/Stop mode wake up input                                               |

| INT2          | Ι      | External falling edge Interrupt input, Idle/Stop mode wake up input                                                            |

| ADC11~ADC0    | Ι      | Analog to Digital Convert input pin                                                                                            |

| RXD           | I/O    | UART Mode0 transmit & receive data, Mode1/2/3 receive data                                                                     |

| TXD           | I/O    | UART Mode0 transmit clock, Mode1/2/3 transmit data. IN One Wire UART                                                           |

|               |        | mode, this pin transmits and receives serial data                                                                              |

| T0, T1, T2    | I      | Timer0, Timer1, Timer2 event count pin input                                                                                   |

| T00           | 0      | Timer0 overflow divided by 64 output                                                                                           |

| T2O<br>T2EX   | 0      | Timer2 overflow divided by 2 output                                                                                            |

| PWM0P/PWM0N   | Ι      | Timer2 external trigger input                                                                                                  |

| PWM1A/PWM1B/  | 0      | 8+2 bit PWM output                                                                                                             |

| PWM1C         | 0      | 0+2 off 1 wiw output                                                                                                           |

| MISO          | I/O    | SPIA data input for master mode, data output for slave mode                                                                    |

| MOSI          | I/O    | SPIA data output for master mode, data input for slave mode                                                                    |

| SCK           | I/O    | SPIA clock output for master or clock input for slave mode                                                                     |

| BSDI          | Ι      | SPIB data input                                                                                                                |

| BSDO          | 0      | SPIB data output                                                                                                               |

| BSCK          | 0      | SPIB clock out                                                                                                                 |

| D0~D7         | I/O    | I80 Data                                                                                                                       |

| RD            | 0      | I80 Read signal output                                                                                                         |

| WR            | 0      | I80 Write signal output                                                                                                        |

| KSI0~KSI7     | Ι      | Keyboard matrix input                                                                                                          |

| KSO0~KSO17    | 0      | Keyboard matrix output                                                                                                         |

| PC5VIN        | Ι      | USB Power input pin                                                                                                            |

| RSTn          | Ι      | External active low reset                                                                                                      |

| VDD           | Р      | 3.3V output power generate by internal regulator; need connect 1uF to Ground                                                   |

| VDDIO         | Р      | 3.3V/5V input power for I/O port; need connect 1uF to Ground                                                                   |

| VPD           | Р      | 1.1V output power generated by internal regulator; used for USB PD;                                                            |

|               |        | need connect 1uF to Ground                                                                                                     |

| VBAT          | P      | VBAT input power                                                                                                               |

| VCC/VDD5, VSS | Р      | Power input pin and Ground                                                                                                     |

# **Pin Summary**

|            |                     |      | I                      | npu     | ıt             | 0    | utp   | ut         | A   | lter | nat  | te I | Tun | ctio | n     | MISC |

|------------|---------------------|------|------------------------|---------|----------------|------|-------|------------|-----|------|------|------|-----|------|-------|------|

| Pin number | Pin Name            | Type | <b>Pull-up Control</b> | Wake up | Ext. Interrupt | P.P. | P.O.D | <b>O.D</b> | PWM | ADC  | UART | IdS  | I80 | KBD  | Timer |      |

| 1          | PWM1B/ADC4/P1.6     | I/O  | $\odot$                | •       |                | •    |       | •          | •   | •    |      |      |     |      |       |      |

| 2          | T0/T00/P3.4         | I/O  | $\odot$                |         |                | •    |       | •          |     |      |      |      |     |      | •     |      |

| 3          | KSO15/T1/P3.5       | I/O  | $\odot$                |         |                | •    |       | •          |     |      |      |      |     | •    | •     |      |

| 4          | KSO3/WR/P2.3        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 5          | SDA1/KDO16/P3.6     | I/O  | $\odot$                |         |                | •    |       | •          |     |      |      |      |     | •    |       |      |

| 6          | SCL1/KSO17/P3.7     | I/O  | $\odot$                |         |                | •    |       | •          |     |      |      |      |     | •    |       |      |

| 7          | KSO8/AD6/P4.0       | I/O  | $\odot$                |         |                | •    |       | •          |     | •    |      |      |     | •    |       |      |

| 8          | KSO9/AD7/P4.1       | I/O  | $\odot$                |         |                | •    |       | •          |     | •    |      |      |     | •    |       |      |

| 9          | KSO10/AD8/P4.2      | I/O  | $\odot$                |         |                | •    |       | •          |     | •    |      |      |     | •    |       |      |

| 10         | NSSI/KSO11/AD9/P4.3 | I/O  | $\odot$                |         |                | •    |       | •          |     | •    |      | •    |     | •    |       |      |

| 11         | KSO12/ P4.4         | I/O  | $\odot$                |         |                | •    |       | •          |     |      |      |      |     | •    |       |      |

| 12         | KSO13/ P4.5         | I/O  | $\odot$                |         |                | •    |       | •          |     |      |      |      |     | •    |       |      |

| 13         | KSO14/ P4.6         | I/O  | $\odot$                |         |                | •    |       | •          |     |      |      |      |     | •    |       |      |

| 14         | PWM1A/AD3/ P2.7     | I/O  | 0                      |         |                | •    |       |            | •   | •    |      |      |     |      |       |      |

| 15         | KSO7/RD/P2.7        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 16         | KSI7/D7/P0.7        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 17         | KSI6/D6/P0.6        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 18         | KSI5/D5/P0.5        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 19         | KSI4/D4/P0.4        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 20         | KSI3/D3/P0.3        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 21         | KSI2/D2/P0.2        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 22         | KSI1/D1/P0.1        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 23         | KSI0/D0/P0.0        | I/O  | 0                      |         |                | •    |       |            |     |      |      |      | •   | •    |       |      |

| 24         | KSO6/ BSDO /P2.6    | I/O  | 0                      |         |                | •    |       |            |     |      |      | •    |     | •    |       |      |

| 25         | KSO5/BSCK/P2.5      | I/O  | 0                      |         |                | •    |       |            |     |      |      | •    |     | •    |       |      |

| 26         | KSO4/BSDI/P2.4      | I/O  | 0                      |         |                | •    |       |            |     |      |      | •    |     | ٠    |       |      |

| 27         | VCC                 | Р    |                        |         |                |      |       |            |     |      |      |      |     |      |       |      |

| 28         | VBAT                | Р    |                        |         |                |      |       |            |     |      |      |      |     |      |       |      |

| 29         | PC5VIN              | Ι    |                        |         |                |      |       |            |     |      |      |      |     |      |       |      |

| 30         | VPD                 | Р    |                        |         |                |      |       |            |     |      |      |      |     |      |       |      |

| 31 | VSS                | Р   |         |           |   |   |   |   |   |   |   |   |   |   |  |

|----|--------------------|-----|---------|-----------|---|---|---|---|---|---|---|---|---|---|--|

| 32 | PWM0N/P5.0         | I/O | 0       |           |   | • |   |   | • |   |   |   |   |   |  |

| 33 | PWM0P/AD2/P1.4     | I/O | $\odot$ | •         |   | • |   | • | • | • |   |   |   |   |  |

| 34 | CC1/AD10/INT0/P3.2 | I/O | $\odot$ | •         | • | ۲ | • |   |   | • |   |   |   |   |  |

| 35 | CC2/AD11/INT1/P3.3 | I/O | $\odot$ | $\bullet$ | • | ۲ |   | • |   | • |   |   |   |   |  |

| 36 | VDDIO              | Р   |         |           |   |   |   |   |   |   |   |   |   |   |  |

| 37 | VDD                | Р   |         |           |   |   |   |   |   |   |   |   |   |   |  |

| 38 | SCL0/DP/P1.2       | I/O | $\odot$ | ullet     |   | ۲ |   | • |   |   |   |   |   |   |  |

| 39 | SDA0/DM/P1.3       | I/O | $\odot$ | •         |   | ● |   | • |   |   |   |   |   |   |  |

| 40 | T2EX/AD1/P1.1      | I/O | $\odot$ | ullet     |   | ● |   | • |   | • |   |   |   | • |  |

| 41 | T2/T2O/AD0/P1.0    | I/O | $\odot$ | $\bullet$ |   | ۲ |   | • |   | • |   |   |   | • |  |

| 42 | AMOSI/KSO2/P2.2    | I/O | 0       |           |   | ۲ |   |   |   |   |   | • | • |   |  |

| 43 | ASCK/KSO1/P2.1     | I/O | 0       |           |   | ۲ |   |   |   |   |   | • | • |   |  |

| 44 | AMISO/KSO0/P2.0    | I/O | 0       |           |   | ۲ |   |   |   |   |   | • | • |   |  |

| 45 | RSTn/INT2/P4.7     | I/O | $\odot$ | $\bullet$ | • | ۲ |   | • |   |   |   |   |   |   |  |

| 46 | RXD/P3.0           | I/O | $\odot$ |           |   | • | • |   |   |   | • |   |   |   |  |

| 47 | TXD/P3.1           | I/O | $\odot$ |           |   | ۲ | • |   |   |   | ۲ |   |   |   |  |

| 48 | PWM1C/AD5/P1.7     | I/O | $\odot$ | •         |   | • |   | • | • | • |   |   |   |   |  |

Symbol:

P.P. = Push-Pull Output

O.D. = Open Drain

P.O.D. = Pseudo Open Drain

PS:

- 1.  $\odot$  Port1, Port3, Port4 theses pins control Pull up resistor by operation modes

- 2. Port0, Port2, Port5 these pins control Pull up resistor while PxOE.n=0 and Px.n=1

### **Functional Description**

#### 1. CPU Core

In the 8051 architecture, the C programming language is used as a development platform. The **TM52F3288** features a fast 8051 core in a highly integrated microcontroller, allowing designers to be able to achieve improved performance compared to a classic 8051 device. TM52 series microcontrollers provide a complete binary code with standard 8051 instruction set compatibility, ensuring an easy migration path to accelerate the development speed of system products. The CPU core includes an ALU, a program status word (PSW), an accumulator (ACC), a B register, a stack point (SP), DPTRs, a programming counter, an instruction decoder, and core special function registers (SFRs).

#### **1.1 Accumulator (ACC)**

This register provides one of the operands for most ALU operations. Accumulators are generally referred to as A or Acc and sometimes referred to as Register A. In this document, the accumulator is represented as "A" or "ACC," including the instruction table. The accumulator, as its name suggests, is used as a general register to accumulate the intermediate results of a large number of instructions. The accumulator is the most important and frequently used register to complete arithmetic and logical operations. It holds the intermediate results of most arithmetic and logic operations and assists in data transportation.

| SFR E0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| ACC     | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

E0h.7~0 **ACC:** Accumulator

#### 1.2 B Register (B)

The "B" register is very similar to the ACC and may hold a 1 Byte value. This register provides the second operand for multiply or divide instructions. Otherwise, it may be used as a scratch pad register. The B register is only used by two 8051 instructions, MUL and DIV. When A is to be multiplied or divided by another number, the other number is stored in B. For MUL and DIV instructions, it is necessary that the two operands be in A and B.

#### ex: DIV A,B

When this instruction is executed, data inside A and B are divided, and the answer is stored in A.

| SFR F0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| В       | B.7   | B.6   | B.5   | B.4   | B.3   | B.2   | B.1   | B.0   |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

F0h.7~0 **B:** B register

#### 1.3 Stack Pointer (SP)

The SP register contains the Stack Pointer. The Stack Pointer is used to load the program counter into memory during LCALL and ACALL instructions and is used to retrieve the program counter from

```

DS-TM52F3288_E

```

memory in RET and RETI instructions. The stack may also be saved or loaded using PUSH and POP instructions, which also increment and decrement the Stack Pointer. The Stack Pointer points to the top location of the stack.

| SFR 81h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| SP      | SP    |       |       |       |       |       |       |       |  |  |  |  |

| R/W     | R/W   |       |       |       |       |       |       |       |  |  |  |  |

| Reset   | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1     |  |  |  |  |

81h.7~0 **SP:** Stack Point

#### **1.4 Dual Data Pointer (DPTRs)**

F2261/64 has two DPTRs, which share the same SFR address. Each DPTR is 16 bits in size and consists of two registers: the DPTR high byte (DPH) and the DPTR low byte (DPL). The DPTR is used for 16bit-address external memory accesses, for offset code byte fetches, and for offset program jumps. Setting the DPSEL control bit allows the program code to switch between the two physical DPTRs.

| SFR 82h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| DPL     | DPL   |       |       |       |       |       |       |       |  |  |  |  |

| R/W     |       | R/W   |       |       |       |       |       |       |  |  |  |  |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

82h.7~0 **DPL:** Data Point low byte

| SFR <b>83h</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| DPH            | DPH   |       |       |       |       |       |       |       |  |  |  |  |

| R/W            |       | R/W   |       |       |       |       |       |       |  |  |  |  |

| Reset          | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |

83h.7~0 **DPH:** Data Point high byte

| SFR F8h | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|---------|--------|-------|-------|-------|---------|-------|-------|-------|

| AUX1    | CLRWDT | WI    | DTE   | ADSOC | CLRPWM0 | PDDP  | BOOTV | DPSEL |

| R/W     | R/W    | R/    | W     | R/W   | R/W     | R/W   | R/W   | R/W   |

| Reset   | 0      | 0     | 0     | 0     | 0       | 0     | u     | 0     |

F8h.0 **DPSEL:** Active DPTR Select

#### 1.5 Program Status Word (PSW)

This register contains status information resulting from CPU and ALU operations. The PSW affected by instructions is listed below.

| Instruction |   | Flag |    |   |

|-------------|---|------|----|---|

| Instruction | С | OV   | AC |   |

| ADD         | Х | X    | Х  |   |

| ADDC        | Х | Х    | Х  |   |

| SUBB        | Х | X    | Х  |   |

| MUL         | 0 | Х    |    |   |

| DIV         | 0 | Х    |    |   |

| DA          | Х |      |    |   |

| RRC         | Х |      |    | ] |

| RLC         | Х |      |    |   |

| SETB C      | 1 |      |    |   |

| Instruction |   | Flag |    |

|-------------|---|------|----|

| Instruction | С | OV   | AC |

| CLR C       | 0 |      |    |

| CPL C       | Х |      |    |

| ANL C, bit  | Х |      |    |

| ANL C. /bit | Х |      |    |

| ORL C, bit  | Х |      |    |

| ORL C, /bit | Х |      |    |

| MOV C, bit  | Х |      |    |

| CJNE        | Х |      |    |

|             |   |      |    |

A "0" means the flag is always cleared, a "1" means the flag is always set and an "X" means that the state of the flag depends on the result of the operation.

| SFR D0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| PSW     | CY    | AC    | F0    | RS1   | RS0   | OV    | F1    | Р     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

D0h.7 **CY:** ALU carry flag

D0h.6 **AC:** ALU auxiliary carry flag

D0h.5 **F0:** General purpose user-definable flag

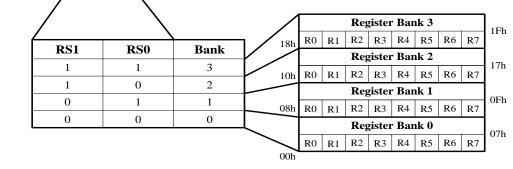

- D0h.4~3 **RS1, RS0:** The contents of (RS1, RS0) enable the working register banks as:

- 00: Bank 0 (00h-07h)

- 01: Bank 1 (08h-0Fh)

- 10: Bank 2 (10h-17h)

- 11: Bank 3 (18h-1Fh)

- D0h.2 **OV:** ALU overflow flag

- D0h.1 **F1:** General purpose user-definable flag

- D0h.0 **P:** Parity flag. Set/cleared by hardware each instruction cycle to indicate odd/even number of "one" bits in the accumulator.

|       | PSW   |       |       |       |       |       |       |  |  |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| R/W   |  |  |  |

| CY    | AC    | FO    | RS1   | RS0   | OV    | F1    | Р     |  |  |  |

#### 2. Memory

#### 2.1 Program Memory

The **F3288** has a 16K Bytes Flash program memory, which can support In Circuit Programming (ICP), In Application Programming (IAP) and In System Programming (ISP) function modes. The Flash write endurance is at least 50K cycle. The Flash program memory address continuous space (0000h–3FFFh) is partitioned to several sectors for device operation.

#### 2.1.1 Program Memory Functional Partition

The last 4 bytes (3FFCh-3FFFh) of program memory is defined as chip Configuration Word (CFGW), which is loaded into the device control registers upon power on reset (POR). The address space 3F00h–3FFBh is the IAP free area, while the 0000h–005Fh is occupied by Reset/Interrupt vectors as standard 8051 definition. In the in-circuit emulation (ICE) mode, user also needs to reserve the address space 1D00h~1FFFh for ICE System communication.

| 0000h<br>Reset/Interrupt Vector<br>005Fh<br>0060h |

|---------------------------------------------------|

| 005Fh                                             |

|                                                   |

| 0060h                                             |

| 00000                                             |

| User Code area                                    |

| 1CFFh                                             |

| 1D00h                                             |

| ICE mode reserved area                            |

| 1FFFh                                             |

| 2000h                                             |

| User Code area                                    |

| 3EFFh                                             |

| 3F00h                                             |

| IAP-Free area                                     |

|                                                   |

| 3FFBh                                             |

| 3FFCh                                             |

| CFGW                                              |

| 3FFFh                                             |

#### 2.1.2 Flash ICP Mode

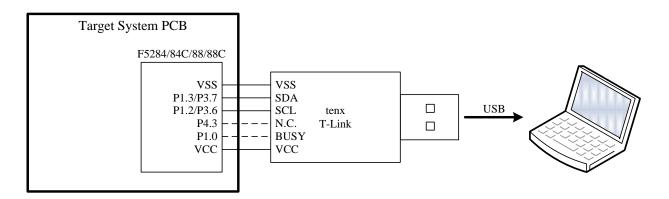

The Flash memory can be programmed by the tenx proprietary writer (**TWR98/TWR99**), which needs at least four wires VCC, VSS, SCL and SDA pins to connect to this chip. If the user wants to program the Flash memory on the target circuit board (In Circuit Program, ICP), these pins must be reserved sufficient freedom to be connected to the Writer. More pins connected to Writer ensure more writing efficiency and speed. SCL and SDA can be P1.2 and P1.3 or can be P3.6 and P3.7.

| Writer wire number | Pin connection                       |

|--------------------|--------------------------------------|

| 4-Wire             | VCC, VSS, SCL, SDA                   |

| 5-Wire             | VCC, VSS, SCL, SDA, P1.0             |

| 7-Wire             | VCC, VSS, SCL, SDA, P1.0, P1.1, P4.3 |

4-wire: Minimum program pin 5-Wire: add P1.0 (BUSY) 7-Wire: add P4.3 (TRIM), P1.1 (CKO)

#### 2.1.3 Flash IAP Mode

The **F3288** has "In Application Program" (IAP) capability, which allows software to read/write data from/to the Flash memory during CPU run time as conveniently as data EEPROM access. The IAP function is byte writable, meaning that the **F3288** does not need to erase one Flash page before write. The available IAP data space is 254 Bytes after chip reset, and can be re-defined by the "MVCLOCK" and "IAPALL" control register as shown below.

|       | 16K Bytes Flash<br>Program memory | Flash memory  | MVCLOCK | IAPALL | MOVC<br>Accessible | MOVX (IAP)<br>Accessible |

|-------|-----------------------------------|---------------|---------|--------|--------------------|--------------------------|

| 0000h |                                   |               | 1       | Х      | No                 | No                       |

|       | MOVC-Lock area                    | 0000h~01FFh   | 0       | 0      | Yes                | No                       |

| 01FFh |                                   |               | 0       | 1      | Yes                | Yes                      |

| 0200h | IAP-All area                      | 0200h~3EFFh   | X       | 0      | Yes                | No                       |

| 3EFFh |                                   | 020011~3EFF11 | X       | 1      | Yes                | Yes                      |

| 3F00h | IAP-Free area                     | 3F00h~3FFBh   | X       | Х      | Yes                | Yes                      |

| 3FFCh |                                   | 3FFC~3FFEh    | X       | 0      | Yes                | No                       |

|       | CFGW area                         | JELC~JEL      | Х       | 1      | Yes                | Yes                      |

| 3FFFh |                                   | 3FFFh         | Х       | Х      | Yes                | No                       |

In IAP mode, the program Flash memory is separated into four sectors: MOVC-Lock area, IAP-All area, IAP-Free area, and CFGW area. These four sectors are regulated differently.

In the **MOVC-Lock area**, IAP read/write is limited by MVCLOCK bit, which can be set to control the accessibility of the MOVC and MOVX instructions to this area. The size of this area is 512 Bytes. The lock function is made to protect the main program code against unconsciously writing Flash memory in IAP mode. Locking or unlocking the function should be performed by the tenx TWR98/99 writing to the CFGW in Flash memory.

The **IAP-All area** is protected by the IAPALL register to prevent IAP mode from writing application data to the program area, resulting in a program code error that cannot be repaired. The size of this area is 15,616 Bytes. Enabling IAPALL requires writing 65h to SFR SWCMD 97h to set the IAPALL control flag. Then, software can use MOVX instructions to write application data to flash memory from 0200h to 3EFFh. If user wants to disable IAPALL function, user can write other values to SFR SWCMD 97h to clear the IAPALL control flag. User must be careful not to overwrite program code which is already resided on the same Flash memory area.

The **IAP-Free area** has no control bit to protect. It can be used to reliably store system application data that needs to be programmed once or periodically during system operation. Other areas of Flash memory can be used to store data, but this area is usually the best. The size of this area is 252 Bytes, equivalent to an EEPROM, and Flash memory can provide byte access to read and write commands. In the past, storage of configuration data required an additional EEPROM or the other storage device. However, this functionality can now be provided by on-chip Flash, reducing the chip count of embedded applications. An external EEPROM or SRAM may not be needed.

The **CFGW area** has 4 data bytes (CFGWH1, CFGWH2, CFGWL1 and CFGWL2), which is located at the last 4 addresses of Flash memory. The CFGWH2 is not accessible to IAP, while the others can be read or written by IAP in case the IAPALL flag is set. CFGWH1(FRC Trimming value) is copied to the

SFR F7h after power on reset, software then take over CFGWH1's control capability by modifying the SFR F7h. CFGWL1(VBG Trimming value) is copied to the SFR F6h after power on reset, software then take over CFGWL1's control capability by modifying the SFR F6h. The CFGWL2 is reserved. BOOTV (CFGWH2[0]) bit is also copied to the SFR F8h[1].

#### 2.1.4 IAP Mode Access Routines

Flash IAP write is simply achieved by a "MOVX @DPTR, A" instruction while the DPTR contains the target Flash address (0–3FFEH), and the ACC contains the data being written. The F3288 accepts IAP Write command only when the IAPWE SFR is enabled. Flash IAP writing requires approximately 500uS. Meanwhile, the CPU stays in a waiting state, but all peripheral modules (Timers and others) continue running during the writing time. The software must handle the pending interrupts after an IAP write. Flash IAP writing needs higher VCC voltage, VCC>2.8V.

Because the Program memory and the IAP data space share the same entity, a Flash IAP read can be performed by the "MOVX A, @DPTR" or "MOVC" instruction as long as the target address points to the 0~3FFFh area. A Flash IAP read does not require extra CPU wait time.

| ; IAP e  | example code |                                           |

|----------|--------------|-------------------------------------------|

| ; need V | VCC > 2.8V   |                                           |

| mov      | dptr, #3f00h | ; dptr = 3f00h = target IAP address       |

| mov      | a, #5ah      | ; $a = 5ah = target IAP$ write data       |

| mov      | IAPWE, #47h  | ; IAPWE SFR write 47h to enable IAPWE     |

| movx     | @dptr, a     | ; $Flash[3f00h] = 5ah$ , after IAP write  |

|          |              | ; 200us~500us H/W writing time, CPU wait  |

|          |              | ;                                         |

| mov      | IAPWE, #00h  | ; IAPWE = $0$ immediately after IAP write |

| clr      | a            | ; a= 0                                    |

| movx     | a, @dptr     | ; a= 5ah                                  |

| clr      | а,           | ; a= 0                                    |

| movc     | a, @a+dptr   | ; a= 5ah                                  |

|          |              |                                           |

| Flash 3FFFh | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1   | Bit 0 |

|-------------|-------|-------|-------|-------|-------|--------|---------|-------|

| CFGWH2      | PROT  | XRSTE | LV    | RE    | -     | PWRSAV | MVCLOCK | BOOTV |

3FFFh.1 MVCLOCK: If 1, the MOVC & MOVX instruction's accessibility to MOVC-Lock area is limited.

3FFFh.0 BOOT vector select

0: Boot from ROM address 0000h

1: Boot from ROM address 3000h

| SFR <b>97h</b> | Bit 7                                                                                      | Bit 6          | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|----------------|--------------------------------------------------------------------------------------------|----------------|-------|-------|-------|-------|-------|-------|--|--|

| SWCMD          |                                                                                            | IAPALL / SWRST |       |       |       |       |       |       |  |  |

| R/W            |                                                                                            | W              |       |       |       |       |       |       |  |  |

| Reset          |                                                                                            | _              |       |       |       |       |       |       |  |  |

| 07h 7_0        | 0 IADALL (W): Write 65h to get IADALL control flag: Write other value to clear IADALL flag |                |       |       |       |       |       |       |  |  |

97h.7~0 **IAPALL (W):** Write 65h to set IAPALL control flag; Write other value to clear IAPALL flag.

97h.0 **IAPALL (R):** Flag indicates Flash memory sectors can be accessed by IAP or not. This bit combines with MVCLOCK to define the accessible IAP area.

| SFR C9h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| IAPWE   | IAPWE | IAPTO |       |       |       | -     |       |       |

| R/W     | W/R   | R     |       |       |       | -     |       |       |

| Reset   | 0     | 0     |       |       |       | -     |       |       |

C9h.7 IAPWE (W): Write 47h to set IAPWE control flag; Write other value to clear IAPWE flag.

C9h.7 IAPWE (R): IAPWE flag

#### 2.1.5 Flash ISP Mode

The "In System Program" (ISP) usage is similar to IAP, except the purpose is to refresh the Program code. User can use UART/SPI or other method to get new Program code from external host, then writes code as the same way as IAP. ISP operation is complicated; basically it needs to assign a Boot code area to the Flash which does not change during the ISP process. When BOOTV is set to high, the Boot address is changed to 3000h after chip reset. If BOOTV = 0, the Boot address is 0000h after chip reset.

#### 2.2 Data Memory

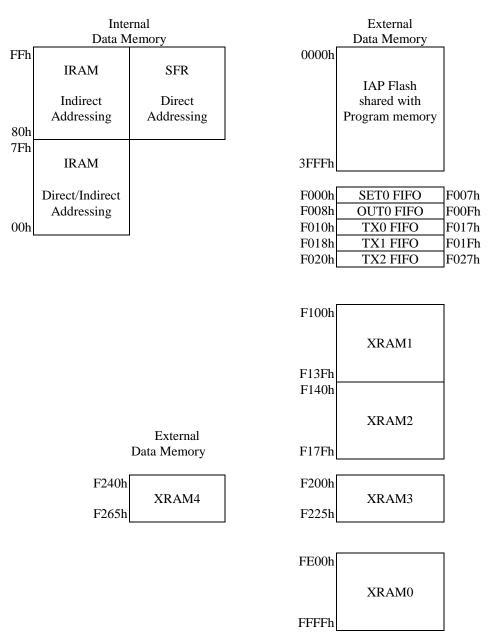

As the standard 8051, the **F3288** has both Internal and External Data Memory space. The Internal Data Memory space consists of 256 Bytes IRAM and 63 SFRs, which are accessible through a rich instruction set. The External Data Memory space consists of 460 Bytes XRAM and IAP Flash, which can be only accessed by MOVX instruction.

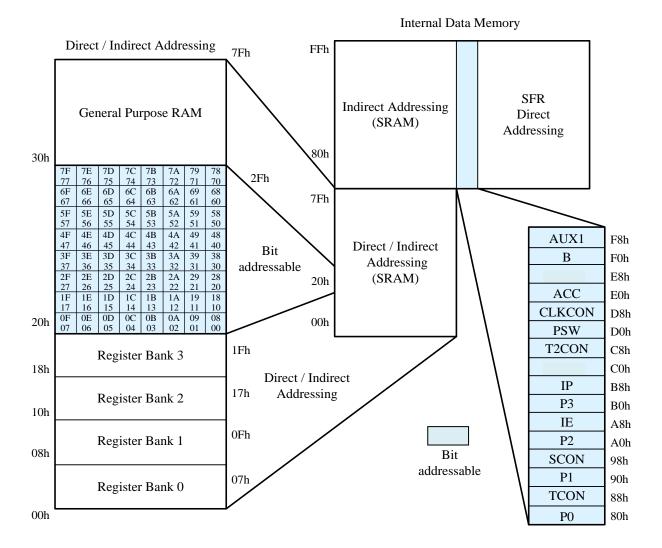

#### 2.2.1 IRAM

IRAM is located in the 8051 internal data memory space. The whole 256 Bytes IRAM are accessible using indirect addressing but only the lower 128 Bytes are accessible using direct addressing. There are four directly addressable register banks (switching by PSW), which occupy IRAM space from 0x00 to 0x1F. The address 0x20 to 0x2F 16 Bytes IRAM space is bit-addressable. IRAM can be used as scratch pad registers or program stack.

#### 2.2.2 XRAM

XRAM0 is located in the 8051 external data memory space (address from FF00h to FFFFh). The 256 Bytes XRAM can be only accessed by "MOVX" instruction. XRAM1/2 is located in the 8051 external data memory space (address from F100h to F17Fh). The two 64 Bytes XRAM can be accessed by "MOVX" instruction and can be accessed by USB, SPI and I80 hardware DMA module. XRAM3/4 is located in the 8051 external data memory space (address from F200h to F225 and F240h to F265h). The two 38 Bytes XRAM can be accessed by "MOVX" instruction and can be accessed by USB PD module.

#### 2.2.3 SFRs

All peripheral functional modules such as I/O ports, Timers and UART operations for the chip are accessed via Special Function Registers (SFRs). These registers occupy upper 128 Bytes of direct Data Memory space locations in the range 0x80 to 0xFF. There are 14 bit addressable SFRs (which means that eight individual bits inside a single byte are addressable), such as ACC, B register, PSW, TCON, SCON, and others. The remaining SFRs are only byte addressable. SFRs provide control and data exchange with the resources and peripherals of the **F3288**. The TM52 series of microcontrollers provides complete binary code with standard 8051 instruction set compatibility. Beside the standard 8051 SFRs, the **F3288** implements additional SFRs used to configure and access subsystems such as the USB/SPI, which are unique to the **F3288**.

|     | 8/0    | 9/1     | A/2     | B/3      | C/4     | D/5       | E/6       | F/7       |

|-----|--------|---------|---------|----------|---------|-----------|-----------|-----------|

| F8h | AUX1   |         |         |          |         |           |           |           |

| F0h | В      |         |         |          |         | AUX2      | CFGWL1    | CFGWH1    |

| E8h | P4     |         |         |          |         |           |           | ANAT      |

| E0h | ACC    |         |         |          |         |           |           |           |

| D8h | CLKCON |         | USB1IE  | USB2IE   | USBRSTM |           |           | PDCTRL    |

| D0h | PSW    | TX3CNT  | RC4CNT  | RCOREG   | I80CTRL |           | XRAMCTRL  |           |

| C8h | T2CON  | IAPWE   | RCP2L   | RCP2H    | TL2     | TH2       | TX3CTRL   | RC4CTRL   |

| C0h | P5     | USBADR  | USB1I   | USB2I    | USBCTRL | TX0CTRL   | TX1CTRL   | TX2CTRL   |

| B8h | IP     | IPH     | IP1     | IP1H     | SPACON  | SPASTA    | SPADAT    |           |

| B0h | P3     | SPBCTRL | SPBCRS  | DMALEN   | P4MODL  | P4MODH    | KBMASK    |           |

| A8h | IE     | INTE1   | ADCDL   | ADCDH    | PWMDTYL |           | CHSEL     |           |

| A0h | P2     | PWMCON  | P1MODL  | P1MODH   | P3MODL  | P3MODH    | PINMOD    | PWM0MODT  |

| 98h | SCON   | SBUF    | PWM0PRD | PWM0DTYH | PWM1PRD | PWM1ADTYH | PWM1BDTYH | PWM1CDTYH |

| 90h | P1     | POOE    |         | P2OE     | OPTION  | INTFLG    | P1WKUP    | SWCMD     |

| 88h | TCON   | TMOD    | TL0     | TL1      | TH0     | TH1       |           |           |

| 80h | P0     | SP      | DPL     | DPH      |         |           |           | PCON      |

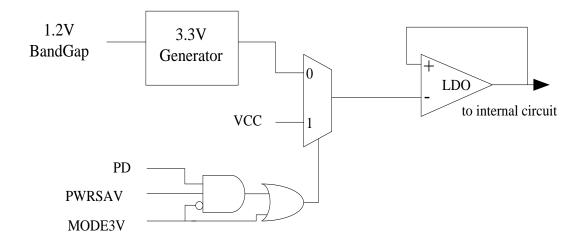

#### 3. Power

VCC pin is the main power supply for this chip. When MODE3V=0, the voltage regulator output 3.3V (VDD) power to the internal chip circuit. When MODE3V=1, the LDO is turned off, and the internal circuit receives a power supply directly from the VCC pin. Because the LDO consumes 150uA for operation, turning off LDO by setting MODE3V=1 can reduce the chip current consumption. However, setting MODE3V=1 is only valid for an operation of VCC < 3.6V. The PWRSAV also control the LDO. When MODE3V=0 and PWRSAV=1, the LDO is turned off in STOP mode for saving power consumption. In addition, set PWRSAV will affect the LVR setting. When **F3288** is used for USB application, the LDO output must keep at 3.3V; the LDO cannot be turned off in STOP mode for saving power consumption.

| Operation    | CFGV   | VH2  |     | Function      |

|--------------|--------|------|-----|---------------|

| Mode         | PWRSAV | LVRE | LDO | Function      |

|              | Х      | 00   | ON  | LV Reset 2.9V |

| Fast         | Х      | 01   | ON  | LV Reset 2.3V |

| Slow<br>Idle | Х      | 10   | ON  | LV Reset 2.3V |

| Idic         | Х      | 11   | ON  | LV Reset 2.1V |

|              | 0      | 00   | ON  | LV Reset 2.9V |

|              | 0      | 01   | ON  | LV Reset 2.3V |

|              | 0      | 10   | ON  | LV Reset 2.3V |

| STOD         | 0      | 11   | ON  | LV Reset 2.1V |

| STOP         | 1      | 00   | OFF | LV Reset 2.9V |

|              | 1      | 01   | OFF | LV Reset 2.3V |

|              | 1      | 10   | OFF | LV Reset 2.3V |

|              | 1      | 11   | OFF | LV Reset 2.1V |

#### MODE3V=0

#### MODE3V=1

| Operation    | CFGW   | /H2  |     | Function      |

|--------------|--------|------|-----|---------------|

| Mode         | PWRSAV | LVRE | LDO | Function      |

| East         | 0      | 00   | OFF | LV Reset 2.9V |

| Fast<br>Slow | 0      | 01   | OFF | LV Reset 2.3V |

| Idle         | 0      | 10   | OFF | LV Reset 2.3V |

| Iule         | 0      | 11   | OFF | LV Reset 2.1V |

|              | 1      | 00   | OFF | LV Reset 2.1V |

|              | 1      | 01   | OFF | LV Reset 2.1V |

|              | 1      | 10   | OFF | LV Reset 2.1V |

|              | 1      | 11   | OFF | LV Reset 2.1V |

|              | 0      | 00   | OFF | LV Reset 2.9V |

|              | 0      | 01   | OFF | LV Reset 2.3V |

|              | 0      | 10   | OFF | LV Reset 2.3V |

| STOD         | 0      | 11   | OFF | LV Reset 2.1V |

| STOP         | 1      | 00   | OFF | LV Reset 2.1V |

|              | 1      | 01   | OFF | LV Reset 2.1V |

|              | 1      | 10   | OFF | LV Reset 2.1V |

|              | 1      | 11   | OFF | LV Reset 2.1V |

| Flash <b>3FFFh</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1   | Bit 0 |

|--------------------|-------|-------|-------|-------|-------|--------|---------|-------|

| CFGWH2             | PROT  | XRSTE | LV    | RE    | -     | PWRSAV | MVCLOCK | BOOTV |

3FFFh.2 **PWRSAV:** Power saving function control bit

1: Enable Power saving function

| SFR <b>94h</b> | Bit 7  | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|--------|--------|--------|-------|-------|-------|-------|-------|

| OPTION         | UART1W | MODE3V | WDTPSC |       | ADCKS |       | -     |       |

| R/W            | R/W    | R/W    | R/     | R/W   |       | R/W   |       | -     |

| Reset          | 0      | 0      | 0      | 0     | 0     | 0     | -     | -     |

94h.6 MODE3V:3V mode selection control bit

If this bit is set, the chip can be only operated in the condition of VCC < 3.6V, and LDO is turned off to save current

<sup>0:</sup> Disable Power saving function

#### 4. Reset

The **F3288** has six types of reset method. Resets can caused by Power on Reset (POR), External Pin Reset (XRST), Software Command Reset (SWRST), Watchdog Timer Reset (WDTR), Low Voltage Reset (LVR), or USB power plug-out/plug-in reset. The CFGW controls the Reset functionality. The SFRs are returned to their default value after Reset.

#### 4.1 Power on Reset

After Power on Reset, the device stays on Reset state for 24 ms as chip warm up time, then downloads the CFGW register from ROM's last byte (Other Reset will not reload the CFGW). The Power on Reset needs VCC pin's voltage first discharge to near VSS level, then rise beyond 2.1V.

#### 4.2 External Pin Reset

Pin Reset is active low. It needs to keep at least 2 SRC clock cycle long to be seen by the chip. Pin Reset can be disabled or enabled by CFGWH2.

#### 4.3 Software Reset

Software Reset is activated by writing the SFR 97h with data 56h.

#### 4.4 Watch Dog Timer Reset (WDT)

WDT overflow Reset is disabled or enable by SFR F8h. The WDT uses SRC as its counting time base. It runs in Fast / Slow mode and runs or stops in Idle/ Stop mode. WDT overflow speed can be defined by WDTPSC SFR. WDT is cleared by device Reset or CLRWDT SFR bit.

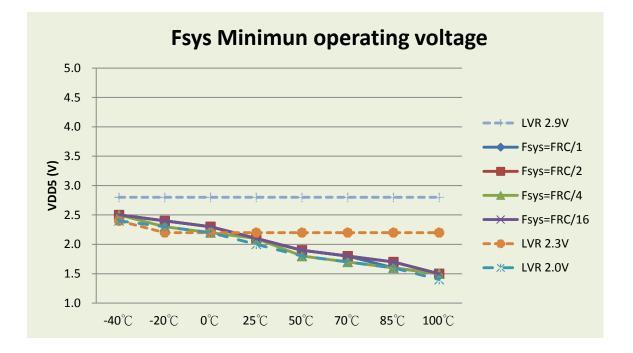

#### 4.5 Low Voltage Reset

The **F3288** offers three options for LVR function. The user can make a selection by CFGWH2, let LVR voltage of 2.9V, 2.3V and 1.9V be selected separately. The LVR can be disabled or enabled by CFGWH2.

#### 4.6 USB Plug Reset

The **F3288** support USB application. USB cable plugs in or out can cause chip reset. By checking the register VDD5VFLG status, the F/W can determine **F3288** is working in USB or non-USB application. When VDD5VFLG is high, which means USB cable plugs in PC5V power supply to the chip, **F3288** can work in USB application. IF VDD5VFLG is low, **F3288** can work in non-USB application.

| System Clock Frequency | 12 MHz   | 6 MHz    | 3MHz     | 0.75MHz  |

|------------------------|----------|----------|----------|----------|

| Minimum LVR level      | LVR=2.9V | LVR=2.9V | LVR=2.3V | LVR=2.1V |

| SFR F8h | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2  | Bit 1 | Bit 0 |

|---------|--------|-------|-------|-------|---------|--------|-------|-------|

| AUX1    | CLRWDT | WI    | WDTE  |       | CLRPWM0 | PDADOP | BOOTV | DPSEL |

| R/W     | R/W    | R/    | R/W   |       | R/W     | R/W    | R/W   | R/W   |

| Reset   | 0      | 0     | 0     | 0     | 0       | 0      | 0     | 0     |

F8h.7 **CLRWDT**: Set to clear WDT, H/W auto clear it at next clock cycle

F8h.6~5 **WDTE:** Watchdog Timer Reset control

0x: Watchdog Timer Reset disable

10: Watchdog Timer Reset enable in Fast/Slow mode, disable in Idle/Stop mode

11: Watchdog Timer Reset always enable

| Flash <b>3FFFh</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1   | Bit 0 |

|--------------------|-------|-------|-------|-------|-------|--------|---------|-------|

| CFGWH2             | PROT  | XRSTE | LVRE  |       | -     | PWRSAV | MVCLOCK | BOOTV |

3FFFh.6 **XRSTE:** External Pin Reset control

0: Disable External Pin Reset

1: Enable External Pin Reset

3FFFh.5~4 LVRE: Low Voltage Reset function select

00: Set LVR at 2.9V

01: Set LVR at 2.3V

10: Reserved

11: Set LVR at 1.9V

| SFR <b>94h</b> | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|--------|--------|-------|-------|-------|-------|-------|-------|

| OPTION         | UART1W | MODE3V | WD    | ГРSC  | ADCKS |       | -     |       |

| R/W            | R/W    | R/W    | R/    | R/W   |       | W     |       | -     |

| Reset          | 0      | 0      | 0     | 0     | 0     | 0     |       | _     |

94h.5~4 **WDTPSC:** Watchdog Timer pre-scaler time select

00: 400ms WDT overflow rate

01: 200ms WDT overflow rate

10: 100ms WDT overflow rate

11: 50ms WDT overflow rate

| SFR <b>97h</b> | Bit 7 | Bit 6          | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|----------------|-------|----------------|-------|-------|-------|-------|-------|-------|--|--|--|

| SWCMD          |       | IAPALL / SWRST |       |       |       |       |       |       |  |  |  |

| R/W            |       | W              |       |       |       |       |       |       |  |  |  |

| Reset          |       | _              |       |       |       |       |       |       |  |  |  |

97h.7~0 **SWRST:** Write 56h to generate S/W Reset.

| SFR F5h | Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|---------|----------|----------|-------|-------|-------|-------|--------|-------|

| AUX2    | VDD5VFLG | VDD5FALL | _     |       |       | IAI   | VCCFLT |       |

| R/W     | R        | R/W      | _     |       |       | R/    | W      | R/W   |

| Reset   | 0        | 0        | _     |       |       | (     | )      | 0     |

|         |          |          |       |       |       |       |        |       |

F5h.7 VDD5VFLG: PC5V status 0: PC5V Low

1: PC5V High (USB plug in)

F5h.6 **VDD5FALL:** USB Plug out flag write 0 or power on reset to clear flag

#### 5. Clock Circuitry & Operation Mode

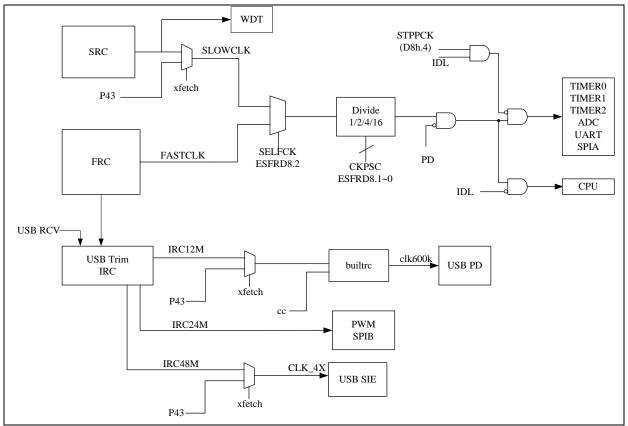

#### 5.1 System Clock

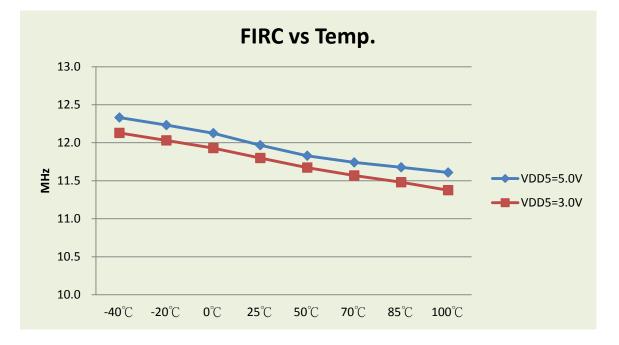

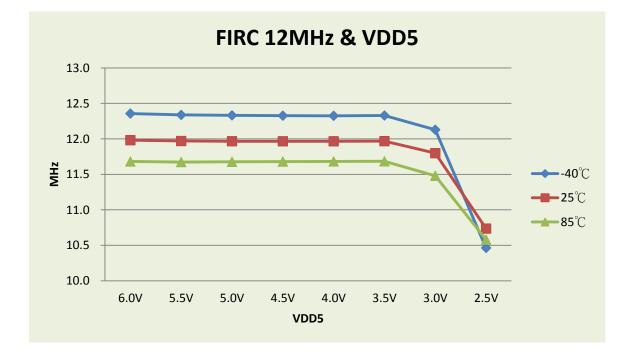

The **F3288** is designed with dual-clock system. During runtime, user can directly switch the System clock from Fast to Slow or from slow to fast. It also can directly select a clock divider of 1, 2, 4 or 16. The Fast clock is fixed to FRC (Fast Internal RC, 11.0592 MHz at VCC=5V). The Slow clock is SRC (Slow Internal RC, 32KHz). Fast mode and Slow mode are defined as the CPU running at Fast and Slow clock speeds.

After Reset, the device is running at Slow mode with 32KHz SRC. The user should select the proper clock rate for chip operation safety. The higher VCC allows the chip to run at a higher System clock frequency.

The **CLKCON** SFR controls the System clock operating. H/W automatically blocks the S/W abnormally setting for this register. Never to write both STPFCK=1 and SELFCK=1. It is recommended to write this SFR bit by bit.

#### 5.2 USB Clock

The F3288 incorporates flexible internal oscillator and clock generators, including a 24 MHz accurate to 3% over temperature and voltage. The 24 MHz can also be doubled to 48 MHz for USB application, and the Internal RC clock generators will self-tune to  $\pm 0.25\%$  accuracy when USB communication.

Clock Structure

#### **5.3 Operation Mode**

There are four operation modes for this device. Fast Mode is defined as the CPU running at Fast clock speed. Slow Mode is defined as the CPU running at Slow clock speed. When the System clock speed is lower, the power consumption is lower.

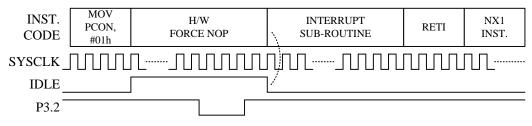

Idle Mode is entered by setting the IDL bit in PCON SFR. Both Fast and Slow clock can be set as the System clock source in Idle Mode, but Slow clock is better for power saving. In Idle mode, the CPU puts itself to sleep while the on-chip peripherals stay active. The STPPCK bit in CLKCON SFR can be set to furthermore reduce Idle mode current. If STPPCK=1, Timer0/1/2, ADC and UART are stopped in Idle mode. The slower System clock rate also helps current saving. It can be achieved by setup the CLKPSC SFR to divide System clock frequency. Idle mode is terminated by Reset or enabled Interrupts wake up.

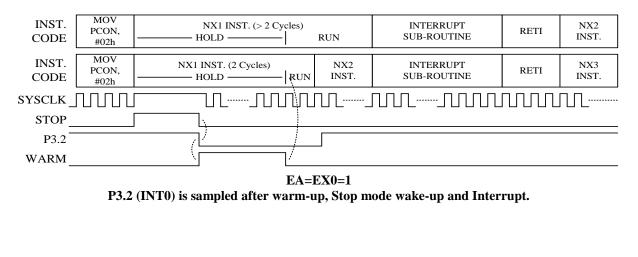

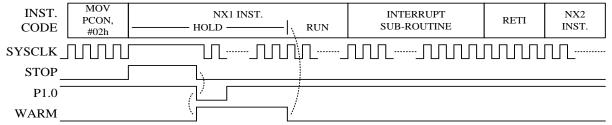

Stop Mode is entered by setting the PD bit in PCON SFR. This mode is the so-called "Power Down" mode in standard 8051. In Stop mode, all clocks stop except the WDT is alive if it is enabled. Stop mode can be terminated by Reset or pin wake up.

*Note:* Chip cannot enter Stop Mode if INTn pin is low and wakeup is enable. (INTn=0 and EXn=1, n=0,1,2)

| SFR 87h | Bit 7                                           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|---------|-------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| PCON    | SMOD                                            | —     | —     | —     | GF1   | GF0   | PD    | IDL   |  |  |

| R/W     | R/W                                             | —     | —     | —     | R/W   | R/W   | R/W   | R/W   |  |  |

| Reset   | 0                                               | —     | —     | —     | 0     | 0     | 0     | 0     |  |  |

| 87h.1   | <b>PD:</b> Stop bit. If 1 Stop mode is entered. |       |       |       |       |       |       |       |  |  |

87h.0

**PD:** Stop bit. If 1 Stop mode is entered. IDL: Idle bit. If 1, Idle mode is entered.

| SFR D8h | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|---------|-------|-------|--------|--------|--------|--------|-------|-------|

| CLKCON  | -     | -     | STPSCK | STPPCK | STPFCK | SELFCK | CLK   | PSC   |

| R/W     | -     | -     | R/W    | R/W    | R/W    | R/W    | R/    | W     |

| Reset   | -     | -     | 0      | 0      | 0      | 0      | 1     | 1     |

D8h.5 **STPSCK:** Set 1 to stop Slow clock

D8h.4 STPPCK: Set 1 to stop UART/Timer0/Timer1/Timer2/ADC clock in Idle mode

D8h.3 STPFCK: Set 1 to stop Fast clock for power saving in Slow/Idle mode. This bit can be changed only in Slow mode.

D8h.2 SELFCK: System clock source selection. This bit can be changed only when STPFCK=0. 0: Slow clock

1: Fast clock

D8h.1~0 CLKPSC: System clock prescaler.

00: System clock is Fast/Slow clock divided by 16

01: System clock is Fast/Slow clock divided by 4

10: System clock is Fast/Slow clock divided by 2

11: System clock is Fast/Slow clock divided by 1

#### 6. Interrupt and Wake-up

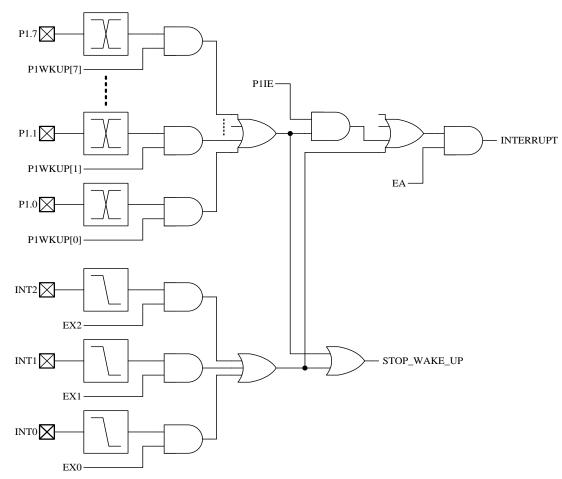

This **F3288** has a 25-source four-level priority interrupt structure. All enabled Interrupts can wake up CPU from Idle mode, but only the Pin Interrupts can wake up CPU from Stop mode. Each interrupt source has its own enable control bit. An interrupt event will set its individual Interrupt Flag, no matter whether its interrupt enable control bit is 0 or 1. The Interrupt vectors and flags are list below.

| Vector | Flag     | Description                                                 |

|--------|----------|-------------------------------------------------------------|

| 0003   | IE0      | INT0 external pin Interrupt (can wake up Stop mode)         |

| 000B   | TF0      | Timer0 Interrupt                                            |

| 0013   | IE1      | INT1 external pin Interrupt (can wake up Stop mode)         |

| 001B   | TF1      | Timer1 Interrupt                                            |

| 0023   | RI+TI    | Serial Port (UART) Interrupt                                |

| 002B   | TF2+EXF2 | Timer2 Interrupt                                            |

| 0033   | NMI      | Reserved for ICE mode use                                   |

| 003B   | SPAI     | SPIA Interrupt                                              |

| 0043   | P1IF     | Port1 external pin change Interrupt (can wake up Stop mode) |

| 004B   | IE2      | INT2 external pin Interrupt (can wake up Stop mode)         |

| 0053   | ADIF     | ADC Interrupt                                               |

| 005B   | USB1I    | USB1 Interrupt Vector (8 sources)                           |

| 0063   | USB2I    | USB2 Interrupt Vector (6 sources)                           |

Interrupt Vector & Flag

#### 6.1 Interrupt Enable and Priority Control

The IE and INTE1 SFRs decide whether the pending interrupt is serviced by CPU. The IP, IPH, IP1 and IP1H SFRs decide the interrupt priority. An interrupt will be serviced as long as an interrupt of equal or higher priority is not already being serviced. If an interrupt of equal or higher level priority is being serviced, the new interrupt will wait until it is finished before being serviced. If a lower priority level interrupt is being serviced, it will be stopped and the new interrupt serviced. When the new interrupt is finished, the lower priority level interrupt that was stopped will be completed.

| SFR <b>96h</b> | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

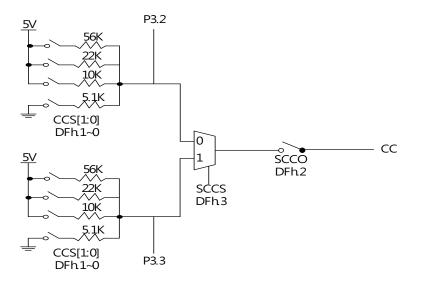

|----------------|-------|--------|-------|-------|-------|-------|-------|-------|--|