# Special for Humidifier

(Please read the precautions on the second page before use)

**tenx** reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. **tenx** does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. **tenx** products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses **tenx** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **tenx** and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that **tenx** was negligent regarding the design or manufacture of the part.

## PRECAUTIONS

- Chip cannot enter Stop Mode if INTn pin is low and wakeup is enabled. (INTn=0 and EXn=1, n=0~2)

- 2. Use MOVC to read flash, MOVX read flash is forbidden.

## AMENDMENT HISTORY

| Version | Date      | Description                    |

|---------|-----------|--------------------------------|

| V0.90   | Apr, 2021 | New release                    |

| V0.91   | Jul, 2022 | 1. Modify system Block Diagram |

## CONTENTS

| PRE | CAU                 | TIONS                                                  | 2  |

|-----|---------------------|--------------------------------------------------------|----|

| AMI | END                 | MENT HISTORY                                           | 3  |

| TM5 | 52 <sub>Serie</sub> | s F85xx FAMILY                                         | 7  |

| GEN | IERA                | L DESCRPTION                                           | 8  |

| BLO | CK I                | DIAGRAM                                                | 8  |

| FEA | TUR                 | ES                                                     | 9  |

| PIN | ASSI                | GNMENT                                                 | 12 |

| PIN | DES                 | CRIPTION                                               | 13 |

| PIN | SUM                 | [MARY                                                  | 14 |

| FUN | CTI                 | ONAL DESCRIPTION                                       | 15 |

| 1.  | CPU                 | J Core                                                 | 15 |

|     | 1.1                 | Accumulator (ACC)                                      | 15 |

|     | 1.2                 | B Register (B)                                         |    |

|     | 1.3                 | Stack Pointer (SP)                                     |    |

|     | 1.4<br>1.5          | Dual Data Pointer (DPTRs)<br>Program Status Word (PSW) |    |

| 2   |                     | nory                                                   |    |

| 2.  |                     |                                                        |    |

|     | 2.1<br>2.2          | Program Memory EEPROM Memory                           |    |

|     | 2.2                 | Data Memory                                            |    |

| 3.  | Pow                 | 'er                                                    | 23 |

|     |                     | et                                                     |    |

|     | 4.1                 | Power on Reset                                         |    |

|     | 4.2                 | External Pin Reset                                     |    |

|     | 4.3                 | Software Command Reset                                 |    |

|     | 4.4                 | Watchdog Timer Reset                                   | 24 |

|     | 4.5                 | Low Voltage Reset                                      | 24 |

| 5.  | Clo                 | ck Circuitry and Operation Mode                        | 26 |

|     | 5.1                 | System Clock                                           |    |

|     | 5.2                 | Operation Mode                                         | 28 |

| 6.  | Inte                | rrupt and Wake-up                                      | 29 |

|     | 6.1                 | Interrupt Enable and Priority Control                  |    |

|     | 6.2                 | Pin Interrupt                                          |    |

|     | 6.3                 | Idle Mode Wake up and Interrupt                        |    |

| -   | 6.4                 | Stop Mode Wake up and Interrupt                        |    |

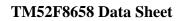

| 7.  | I/O .               | Ports                                                  | 35 |

|      | 7.1 Port1 & P2.2 & Port3                                           | 25          |

|------|--------------------------------------------------------------------|-------------|

| 0    |                                                                    |             |

| 8.   | Timers                                                             |             |

|      | 8.1 Timer0/1                                                       |             |

|      | 8.3 Timer3                                                         |             |

|      | 8.4 T0O, T1O and T2O Output Control                                |             |

| 9.   | UART                                                               | 17          |

| 10.  | PWMs                                                               | 19          |

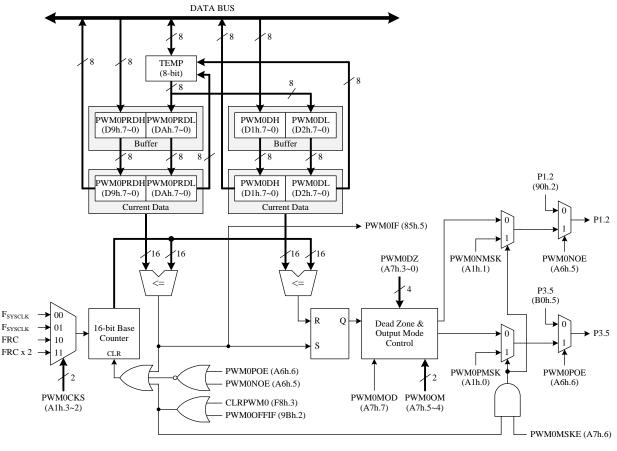

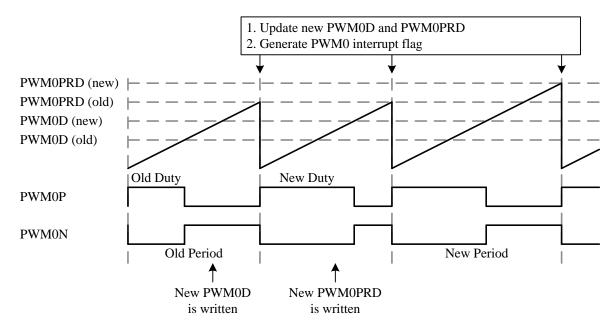

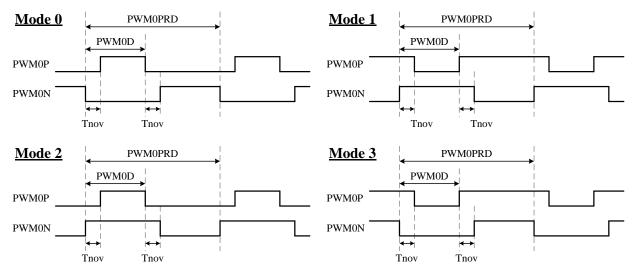

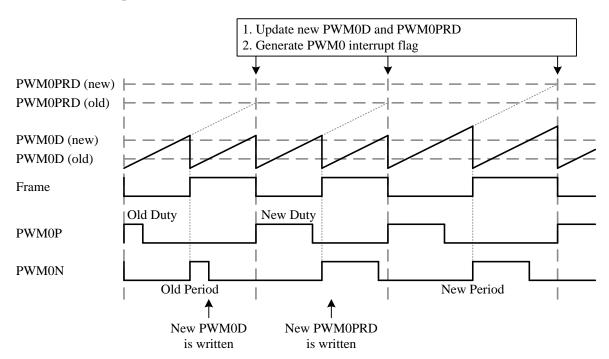

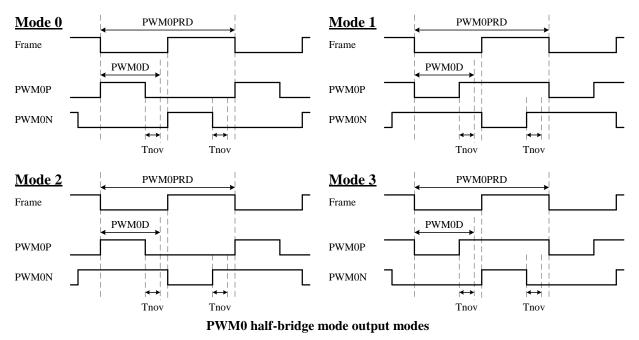

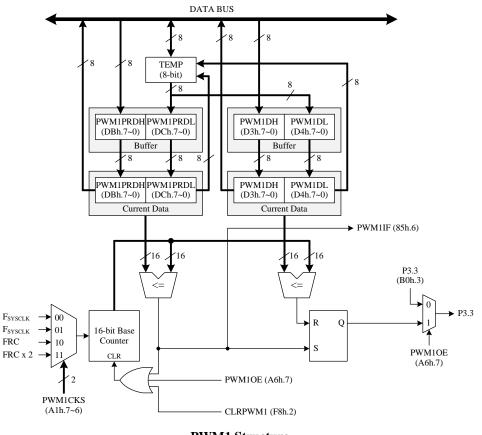

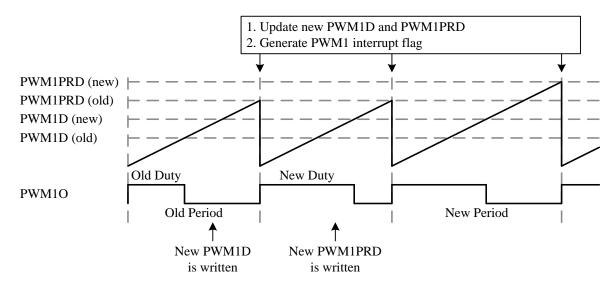

|      | 10.1 PWM0                                                          |             |

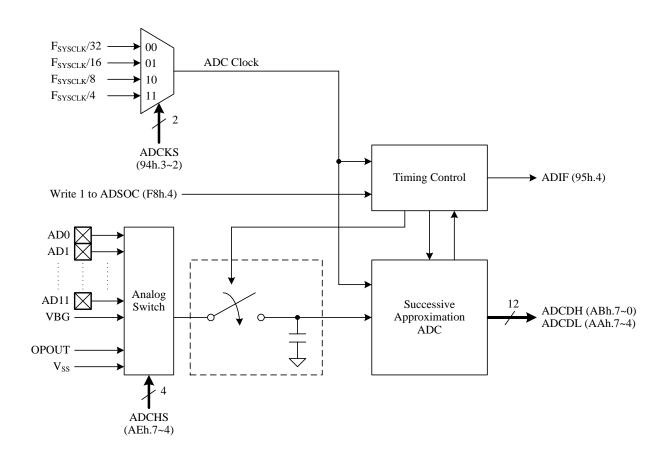

| 11.  | ADC                                                                | 56          |

|      | 11.1 ADC Channels       4         11.2 ADC Conversion Time       4 |             |

| 12.  | Multiplier and divider                                             | 50          |

| 13.  | Operational Amplifier                                              | 52          |

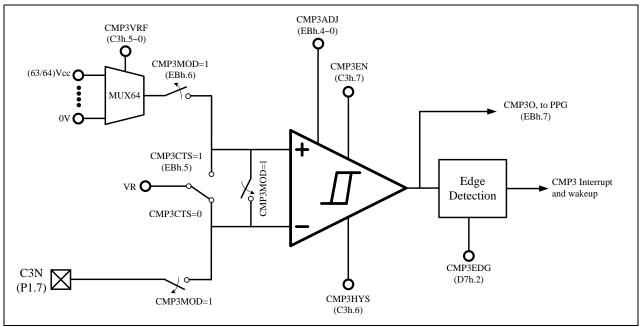

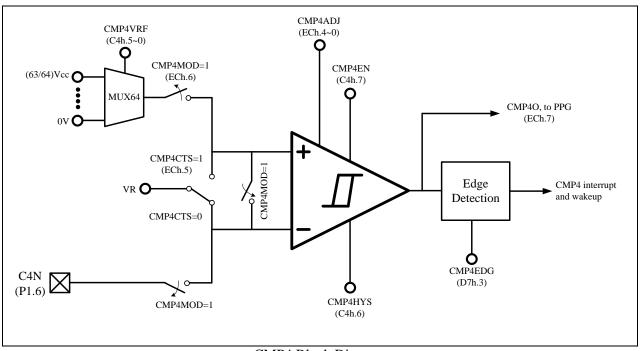

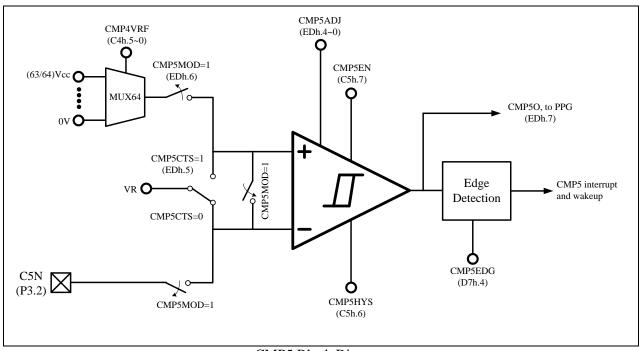

| 14.  | Analog Comparators                                                 | 55          |

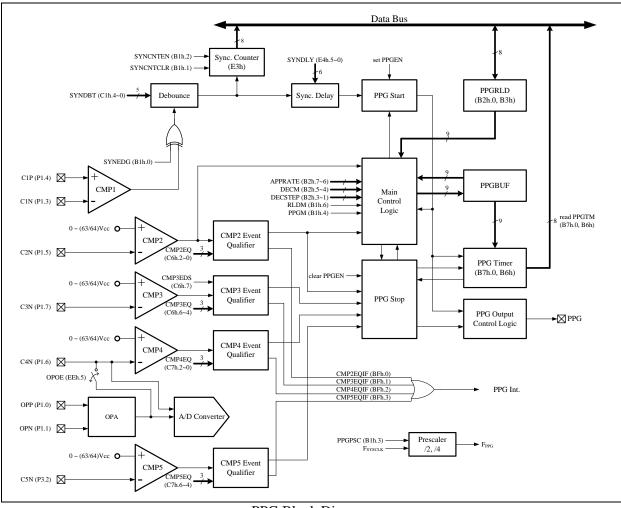

| 15.  | Programmable Pulse Generator (PPG)                                 | 73          |

|      | 15.1 Single Pulse Mode                                             |             |

|      | 15.2 Synchronous Mode                                              |             |

| 16   | Phase Protect Detector (PPD)                                       |             |

|      | 16.1 Phase Detector                                                |             |

|      | 16.2 CMP                                                           | 83          |

|      | 16.3 PWM0 Force OFF                                                | 34          |

|      | Master I <sup>2</sup> C Interface                                  |             |

|      | In Circuit Emulation (ICE) Mode                                    |             |

| SFR  | & CFGW MAP                                                         | <b>)</b> () |

| SFR  | & CFGW DESCRIPTION                                                 | <b>)</b> 3  |

| INST | TRUCTION SET   11                                                  | 10          |

| ELE  | CTRICAL CHARACTERISTICS11                                          | 13          |

| 1.   | Absolute Maximum Ratings                                           | 13          |

| 2.   | DC Characteristics                                                 | 13          |

| 3.   | Clock Timing                                                       | 14          |

| 4.   | Reset Timing Characteristics                                       | 14          |

| 5.   | ADC Electrical Characteristics                                     | 15          |

| 6.   | OPA Characteristics                                                | 15          |

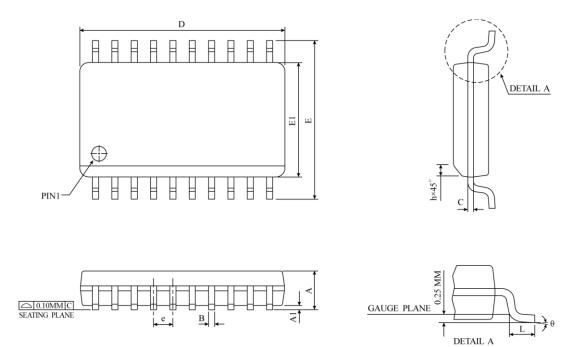

| PAC | KAGE INFORMATION                  | 120 |

|-----|-----------------------------------|-----|

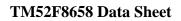

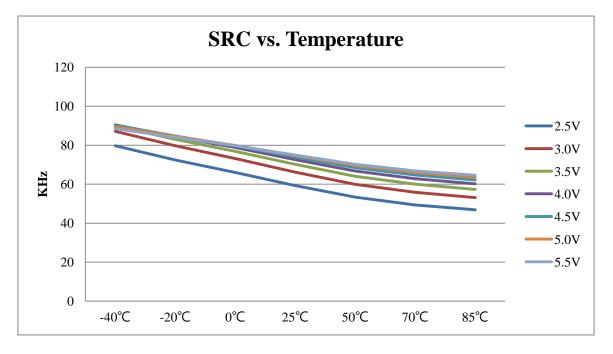

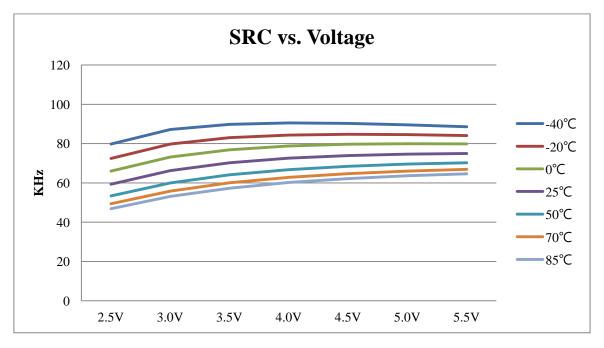

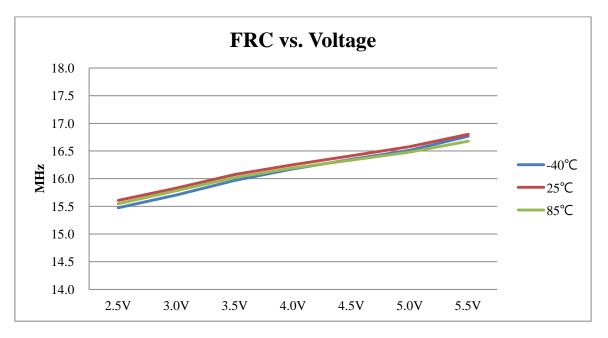

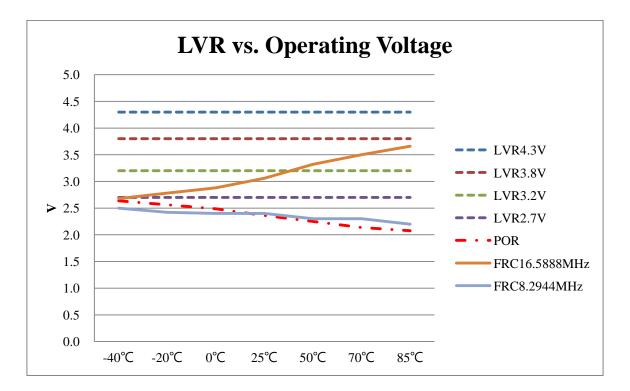

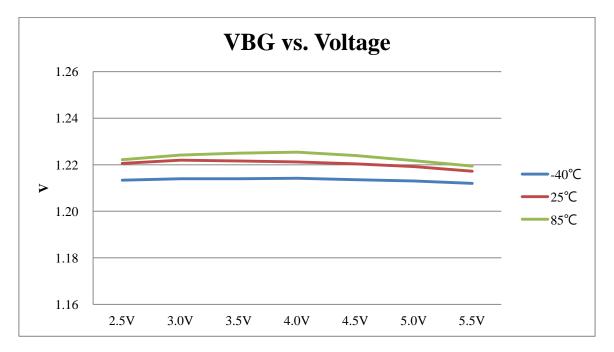

| 8.  | Characteristics Graphs            | 117 |

| 7.  | Analog Comparator Characteristics | 116 |

## TM52<sub>Series</sub> F85xx FAMILY

#### **Common Features**

| CPU               | MTP/Flash<br>Program<br>Memory | RAM<br>Bytes    | Dual<br>Clock            | Operation<br>Mode            | Timer0<br>Timer1<br>Timer2 | UART   | Real-time<br>Timer3 | LVR                          |

|-------------------|--------------------------------|-----------------|--------------------------|------------------------------|----------------------------|--------|---------------------|------------------------------|

| Fast 8051<br>(2T) | 4K~16K<br>With ICP             | 256<br>~<br>512 | SXT<br>SRC<br>FXT<br>FRC | Fast<br>Slow<br>Idle<br>Stop | 8051 St                    | andard | 15-bit              | 2.7V<br>3.2V<br>3.8V<br>4.3V |

#### **Family Members Features**

| P/N        | Program<br>Memory | Data<br>Memory      | RAM<br>Bytes | IO Pin | PWM       | SAR<br>ADC      | OPA   | CMP   | Serial<br>Interface    |

|------------|-------------------|---------------------|--------------|--------|-----------|-----------------|-------|-------|------------------------|

| TM52-F8558 | Flash<br>8K Bytes | EEPROM<br>128 Bytes | 512          | 17     | 16-bit x2 | 12-bit<br>12-ch | 1 set | 5 set | Master I2C*1<br>UART*1 |

| TM52-F8658 | Flash<br>8K Bytes | EEPROM<br>128 Bytes | 512          | 17     | 16-bit x2 | 12-bit<br>12-ch | 1 set | 5 set | Master I2C*1<br>UART*1 |

| P/N        | Operation | OĮ          | peration Cur<br>PWRS |             | Max. System Clock (Hz) |     |     |     |         |

|------------|-----------|-------------|----------------------|-------------|------------------------|-----|-----|-----|---------|

|            | Voltage   | Fast<br>FRC | Slow<br>SRC          | Idle<br>SRC | Stop                   | SXT | SRC | FXT | FRC     |

| TM52-F8558 | 2.7~5.5V  | 8.9mA       | 2.6mA                | 424µA       | $< 0.1 \mu A$          | _   | 80K | _   | 16.588M |

| TM52-F8658 | 2.7~5.5V  | 8.9mA       | 2.6mA                | 424µA       | < 0.1µA                | _   | 80K | _   | 16.588M |

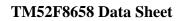

## **GENERAL DESCRPTION**

**TM52**<sub>Series</sub> **F8658** are versions of a new, fast 8051 architecture for an 8-bit microcontroller single chip with an instruction set fully compatible with industry standard 8051, and retains most 8051 peripheral's function block. Typically, the **TM52-F8658** executes instructions six times faster than standard 8051.

The **TM52-F8658** provides improved performance, lower cost and fast time-to-market by integrating features on the chip, including 8K Bytes Flash program memory, 128 Bytes EEPROM, 512 Bytes SRAM, Low Voltage Reset (LVR), dual clock power saving operation mode, 8051 standard UART and Timer0/1/2, real time clock Timer3, Master IIC Interface, Operational Amplifier, 5 Voltage Comparators, 2 set 16-bit PWMs, 12 channels 12-bit A/D Convertor, 9-bit Programmable Pulse Generator (PPG) and Watchdog Timer. Its high reliability and low power consumption feature can be widely applied in consumer and home appliance products.

## **BLOCK DIAGRAM**

## FEATURES

#### 1. Standard 8051 Instruction set, fast machine cycle

• Executes instructions six times faster than standard 8051

#### 2. 8K Bytes Flash Program Memory

- Support "In Circuit Programming" (ICP) for the Flash code

- Code Protection Capability

- 10K erase times at least

- 10 years data retention at least

#### 3. 128 Bytes EEPROM Memory

- 50K erase times at least

- 10 years data retention at least

#### 4. Total 512 Bytes SRAM (IRAM+XRAM)

- 256 Bytes IRAM in the 8051 internal data memory area

- 256 Bytes XRAM in the 8051 external data memory area (accessed by MOVX Instruction)

#### 5. Two System Clock type Selections

- Fast clock from Internal RC (FRC, 16.5888 MHz)

- Slow clock from Internal RC (SRC, 80 KHz)

- System clock can be divided by 1/2/4/16 option

#### 6. 8051 Standard Timer – Timer0/1/2

- 16-bit Timer0, also supports T0O clock output for Buzzer application

- 16-bit Timer1, also supports T1O clock output for Buzzer application

- 16-bit Timer2, also supports T2O clock output for Buzzer application

#### 7. 15-bit Time3

- Clock source is Slow clock or FRC/512

- Interrupt period can be clock divided by 32768/16384/8192/128 option

#### 8. 8051 Standard UART

• One Wire UART option

#### 9. Two independent 16 bits PWMs with period-adjustment/buffer-reload/clear and hold function

#### **10. One Master I<sup>2</sup>C Interface**

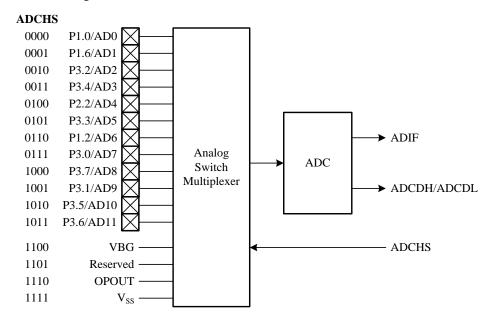

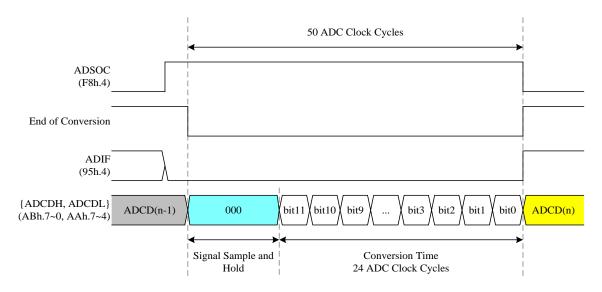

11. 12-bit ADC with 12 Channels External Pin Input, 2 Channels Internal Reference Voltage and 1 OPA Output Voltage

#### **12.** Build-In OP Amp x 1 for the IGBT Current Sensing

DS-TM52F8658\_E

- Low Power Rail-to-Rail Input / Output

- Vos < |2mV| by calibration

- High Gain-Bandwidth 2.1MHz

- High Open Loop Gain 90dB

- CMRR 80dB, PSRR 80dB

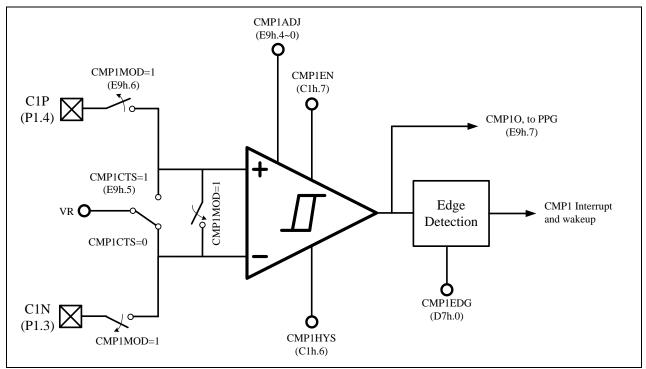

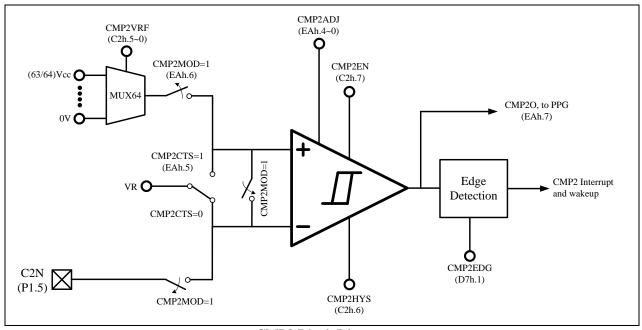

#### 13. Build-In Voltage Comparator x 5

- Vos < |2mV| by calibration

- |40mV| Hysteresis Option (Disable / Enable)

- Phase Protect Detector (PPD)

#### 14. One 9-Bit Programmable Pulse Generator (PPG) Output Channel

- Sing Pulse Mode / Synchronous Mode

- Direct / Approach Reload Mode

- Programmable Output Delay Time (Synchronous Mode only)

- Auto-Decrement Pulse Width Control

- Over-Voltage / Over-Current Protection

#### 15. Multiplication and division

- 8 bits Multiplier & Divider (standard 8051)

- 16 bits Multiplier & Divider

- 32 bits ÷ 16 bits hardware Divider

#### 16. Integrated 16-bit Cyclic Redundancy Check function

#### 17. 20 Sources, 4-level Priority Interrupt

- Timer0/Timer1/Timer2/Timer3 Interrupt

- INT0/INT1 Falling-Edge/Low-Level Interrupt

- Port1 Pin Change Interrupt

- UART TX/RX Interrupt

- P3.7 (INT2) Interrupt

- ADC Interrupt

- I2C Interrupt

- PPG/PPD Interrupt

- CMP1~5 Interrupt

- PWM0/PWM1 Interrupt

#### 18. Pin Interrupt can Wake up CPU from Power-Down (Stop) mode

- P3.2/P3.3 (INT0/INT1) Interrupt & Wake-up

- P3.7 (INT2) Interrupt & Wake-up

- Each Port1 pin can be defined as Interrupt & Wake-up pin (by pin change)

#### 19. Max. 17 Programmable I/O pins

- CMOS Output

- Pseudo-Open-Drain, or Open-Drain Output

- Schmitt Trigger Input

- Pin Pull-up can be Enable or Disable

#### 20. Independent RC Oscillating Watchdog Timer

• 400ms/200ms/100ms/50ms Selectable WDT Timeout options

#### 21. Five types Reset

- Power on Reset

- Selectable External Pin Reset

- Software Command Reset

- Selectable Watchdog Timer Reset

- Selectable Low Voltage Reset

#### 22. 4-level Low Voltage Reset

• 2.7V/3.2V/3.8V/4.3V

#### 23. Four Power Saving Operation Modes

• Fast/Slow/Idle/Stop Mode

#### 24. On-chip Debug/ICE interface

- Use P3.0/P3.1 pin

- Share with ICP programming pin

#### 25. Operating Voltage and Current

- $V_{CC}=3.7V \sim 5.5V @F_{SYSCLK}=16.5888 MHz$

- $V_{CC}=2.5V \sim 5.5V @F_{SYSCLK}=8.2944 MHz$

- $I_{CC}$ =52µA @Stop mode, LVR enable, PWRSAV=0,  $V_{CC}$ =5V

- $I_{CC}$ =47µA @Stop mode, LVR enable, PWRSAV=0,  $V_{CC}$ =3V

- $I_{CC}$ <0.1µA @Stop mode, LVR disable, PWRSAV=1,  $V_{CC}$ =5V

#### 26. Operating Temperature Range

● -40°C ~ +85°C

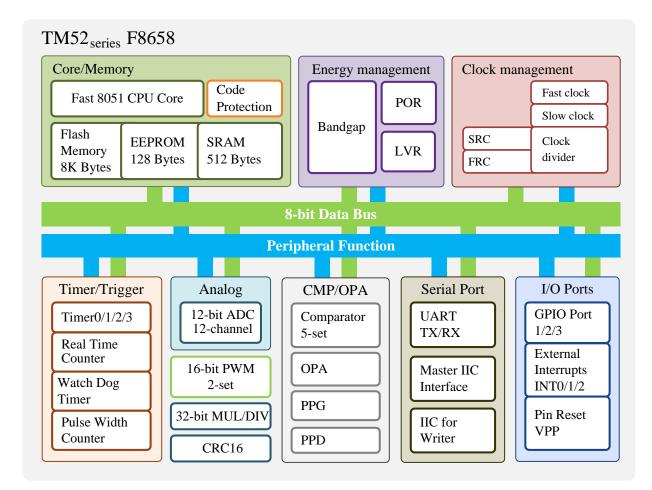

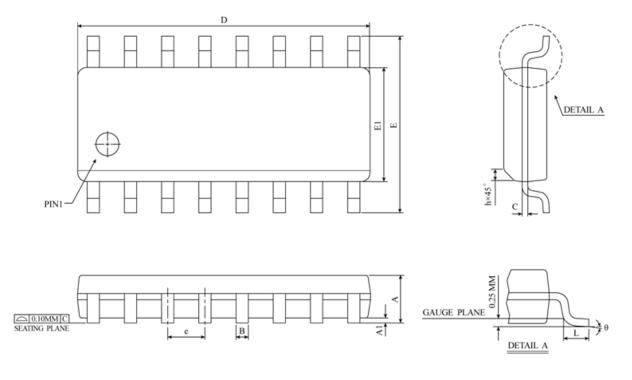

#### 27. Package Types

- SOP 20-pin (300 mil)

- SOP 16-pin (150 mil)

## PIN ASSIGNMENT

## **PIN DESCRIPTION**

| Name                   | In/Out | Pin Description                                                                                                                                                                                                |

|------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

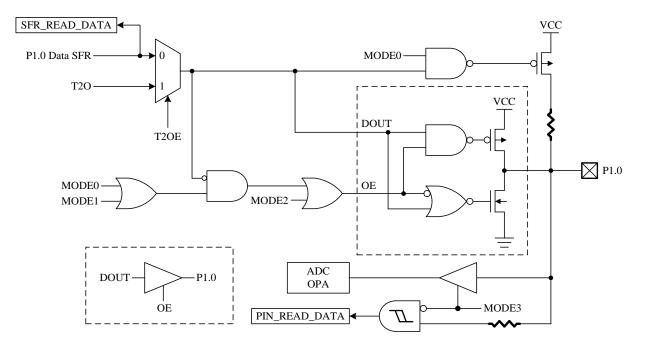

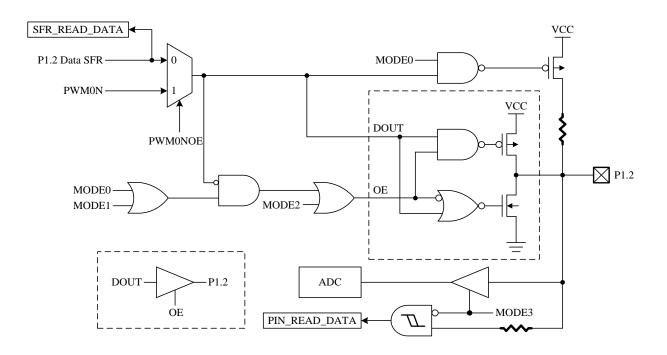

| P1.0~P1.7              | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "open-drain" output. Pull-up resistors are assignable by software. These pin's level change can wake up CPU from Idle/Stop mode. |

| P2.2                   | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "open-drain" output. Pull-up resistors are assignable by software.                                                               |

| P3.0~P3.2              | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "pseudo open drain" output. Pull-up resistors are assignable by software.                                                        |

| P3.3~P3.7              | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "open-drain" output. Pull-up resistors are assignable by software.                                                               |

| INT0, INT1             | Ι      | External low level or falling edge Interrupt input, Idle/Stop mode wake up input.                                                                                                                              |

| INT2                   | Ι      | External falling edge Interrupt input, Idle/Stop mode wake up input.                                                                                                                                           |

| RXD                    | I/O    | UART Mode0 transmit & receive data, Mode1/2/3 receive data.                                                                                                                                                    |

| TXD                    | I/O    | UART Mode0 transmit clock, Mode1/2/3 transmit data. In One Wire UART mode, this pin transmits and receives serial data.                                                                                        |

| T0, T1, T2             | Ι      | Timer0, Timer1, Timer2 event count pin input                                                                                                                                                                   |

| TOO                    | 0      | Timer0 overflow divided by 64 output                                                                                                                                                                           |

| T10                    | 0      | Timer1 overflow divided by 2 output                                                                                                                                                                            |

| T2O                    | 0      | Timer2 overflow divided by 2 output                                                                                                                                                                            |

| T2EX                   | Ι      | Timer2 external trigger input                                                                                                                                                                                  |

| VBGO                   | 0      | Bandgap voltage output                                                                                                                                                                                         |

| PWM0P<br>PWM0N<br>PWM1 | 0      | 16 bits PWM output                                                                                                                                                                                             |

| AD0~AD11               | Ι      | ADC input                                                                                                                                                                                                      |

| OPP                    | Ι      | OPA positive input                                                                                                                                                                                             |

| OPN                    | Ι      | OPA negative input                                                                                                                                                                                             |

| OPO                    | 0      | OPA output                                                                                                                                                                                                     |

| C1P                    | Ι      | Comparator 1 positive input                                                                                                                                                                                    |

| C1N                    | Ι      | Comparator 1 negative input                                                                                                                                                                                    |

| C2N                    | Ι      | Comparator 2 negative input                                                                                                                                                                                    |

| C3N                    | Ι      | Comparator 3 negative input                                                                                                                                                                                    |

| C4N                    | Ι      | Comparator 4 negative input                                                                                                                                                                                    |

| C5N                    | Ι      | Comparator 5 negative input                                                                                                                                                                                    |

| SCL                    | 0      | Master IIC clock output                                                                                                                                                                                        |

| SDA                    | I/O    | Master IIC data input or output                                                                                                                                                                                |

| PPG                    | 0      | PPG output                                                                                                                                                                                                     |

| RSTn                   | Ι      | External active low reset input, Pull-up resistor is fixed enable                                                                                                                                              |

| VCC, VSS               | Р      | Power input pin and ground                                                                                                                                                                                     |

## PIN SUMMARY

#### TM52F8658

| Pin Nu | umber  |                        |      | I               | npu        | t              | C    | )utp   | ut        |     | Alte | erna | te F | unc  | tion | l     |       |

|--------|--------|------------------------|------|-----------------|------------|----------------|------|--------|-----------|-----|------|------|------|------|------|-------|-------|

| SOP-20 | SOP-16 | Pin Name               | Type | Pull-up Control | Wake up    | Ext. Interrupt | P.P. | P.O.D. | 0.D.      | OPA | ADC  | COMP | IIC  | UART | PWM  | Timer | Misc  |

| 1      | 1      | C3N/P1.7               | I/O  | 0               |            |                | •    |        | •         |     |      | •    |      |      |      |       |       |

| 2      | 2      | AD11/P3.6              | I/O  | 0               |            |                | •    |        | $\bullet$ |     | •    |      |      |      |      |       |       |

| 3      |        | PPG                    | 0    |                 |            |                |      |        | •         |     |      |      |      |      |      |       |       |

| 4      | 3      | PWM0P/T1/T1O/AD10/P3.5 | I/O  | 0               |            |                | •    |        | $\bullet$ |     | •    |      |      |      | •    | •     |       |

| 5      | 4      | SCL/TXD/AD9/P3.1       | I/O  | 0               |            |                | •    | •      |           |     | •    |      | •    | •    |      |       |       |

| 6      |        | RSTn/INT2/AD8/P3.7     | I/O  | 0               | •          | •              | •    |        | •         |     | •    |      |      |      |      |       | Reset |

| 7      | 5      | VSS                    | Р    |                 |            |                |      |        |           |     |      |      |      |      |      |       |       |

| 8      | 6      | SDA/RXD/AD7/P3.0       | I/O  | 0               |            |                | •    | •      |           |     | •    |      | •    | •    |      |       |       |

| 9      | 7      | PWM0N/AD6/P1.2         | I/O  | 0               | •          |                | •    |        | •         |     | •    |      |      |      | •    |       |       |

| 10     | 8      | PWM1/INT1/AD5/P3.3     | I/O  | 0               | •          | •              | •    |        | •         |     | •    |      |      |      | •    |       |       |

| 11     | 9      | AD4/P2.2               | I/O  | 0               |            |                | •    |        | •         |     | •    |      |      |      |      |       |       |

| 12     |        | T0/T00/AD3/P3.4        | I/O  | 0               |            |                | •    |        | •         |     | •    |      |      |      |      | •     |       |

| 13     | 10     | VCC                    | Р    |                 |            |                |      |        | •         |     |      |      |      |      |      |       |       |

| 14     | 11     | VBGO/INT0/AD2/C5N/P3.2 | I/O  | 0               | •          | •              | •    | •      |           |     | •    | •    |      |      |      |       | VBGO  |

| 15     | 12     | AD1/OPO/C4N/P1.6       | I/O  | 0               | •          |                | •    |        | •         | •   | •    | •    |      |      |      |       |       |

| 16     | 13     | T2/T2O/AD0/OPP/P1.0    | I/O  | 0               | •          |                | •    |        | •         | •   | •    |      |      |      |      | •     |       |

| 17     |        | T2EX/OPN/P1.1          | I/O  | 0               | •          |                | •    |        | •         | •   |      |      |      |      |      |       |       |

| 18     | 14     | C2N/P1.5               | I/O  | 0               | •          |                | •    |        | •         |     |      | •    |      |      |      |       |       |

| 19     | 15     | C1P/P1.4               | I/O  | 0               | lacksquare |                | •    |        | •         |     |      | ●    |      |      |      |       |       |

| 20     | 16     | C1N/P1.3               | I/O  | 0               | •          |                | •    |        | •         |     |      | •    |      |      |      |       |       |

Symbol:

P.P. = Push-Pull Output

O.D. = Open Drain

P.O.D. = Pseudo Open Drain

PS:

1. • Port1, Port3, P2.2 these pins control Pull up resistor by operation modes

## FUNCTIONAL DESCRIPTION

#### 1. CPU Core

In the 8051 architecture, the C programming language is used as a development platform. The TM52 device features a fast 8051 core in a highly integrated microcontroller, allowing designers to be able to achieve improved performance compared to a classic 8051 device. TM52 series microcontrollers provide a complete binary code with standard 8051 instruction set compatibility, ensuring an easy migration path to accelerate the development speed of system products. The CPU core includes an ALU, a program status word (PSW), an accumulator (ACC), a B register, a stack point (SP), DPTRs, a program counter, an instruction decoder, and core special function registers (SFRs).

#### **1.1 Accumulator (ACC)**

This register provides one of the operands for most ALU operations. Accumulators are generally referred to as A or Acc and sometimes referred to as Register A. In this document, the accumulator is represented as "A" or "ACC" including the instruction table. The accumulator, as its name suggests, is used as a general register to accumulate the intermediate results of a large number of instructions. The accumulator is the most important and frequently used register to complete arithmetic and logical operations. It holds the intermediate results of most arithmetic and logic operations and assists in data transportation.

| SFR E0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| ACC     | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

E0h.7~0 ACC: Accumulator

#### **1.2 B Register (B)**

The "B" register is very similar to the ACC and may hold a 1 Byte value. This register provides the second operand for multiply or divide instructions. Otherwise, it may be used as a scratch pad register. The B register is only used by two 8051 instructions, MUL and DIV. When A is to be multiplied or divided by another number, the other number is stored in B. For MUL and DIV instructions, it is necessary that the two operands are in A and B.

#### ex: DIV AB

When this instruction is executed, data inside A and B are divided, and the answer is stored in A.

| SFR F0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| В       | B.7   | B.6   | B.5   | B.4   | B.3   | B.2   | B.1   | B.0   |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

F0h.7~0 **B:** B register

#### 1.3 Stack Pointer (SP)

The SP register contains the Stack Pointer. The Stack Pointer is used to load the program counter into memory during LCALL and ACALL instructions and is used to retrieve the program counter from memory in RET and RETI instructions. The stack may also be saved or loaded using PUSH and POP instructions, which also increment and decrement the Stack Pointer. The Stack Pointer points to the top location of the stack.

| SFR 81h | Bit 7 | Bit 6 | Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bi |   |   |   |   |   |  |  |  |  |  |  |

|---------|-------|-------|----------------------------------------------------------------------------------------|---|---|---|---|---|--|--|--|--|--|--|

| SP      |       | SP    |                                                                                        |   |   |   |   |   |  |  |  |  |  |  |

| R/W     |       | R/W   |                                                                                        |   |   |   |   |   |  |  |  |  |  |  |

| Reset   | 0     | 0     | 0                                                                                      | 0 | 0 | 1 | 1 | 1 |  |  |  |  |  |  |

81h.7~0 **SP:** Stack Point

#### 1.4 Dual Data Pointer (DPTRs)

TM52 device has two DPTRs, which share the same SFR address. Each DPTR is 16 bits in size and consists of two registers: the DPTR high byte (DPH) and the DPTR low byte (DPL). The DPTR is used for 16-bit-address external memory accesses, for offset code byte fetches, and for offset program jumps. Setting the DPSEL control bit allows the program code to switch between the two physical DPTRs.

| SFR 82h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| DPL     |       | DPL   |       |       |       |       |       |       |

| R/W     |       |       |       | R/    | W     |       |       |       |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

82h.7~0 **DPL:** Data Point low byte

| SFR <b>83h</b> | Bit 7       | Bit 6         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------------|---------------|-------|-------|-------|-------|-------|-------|

| DPH            |             | DPH           |       |       |       |       |       |       |

| R/W            |             |               |       | R/    | W     |       |       |       |

| Reset          | 0           | 0             | 0     | 0     | 0     | 0     | 0     | 0     |

| 83h.7~0        | DPH: Data H | Point high by | te    |       |       |       |       |       |

| SFR F8h | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1 | Bit 0 |

|---------|--------|--------|-------|-------|---------|---------|-------|-------|

| AUX1    | CLRWDT | CLRTM3 |       | ADSOC | CLRPWM0 | CLRPWM1 | _     | DPSEL |

| R/W     | R/W    | R/W    |       | R/W   | R/W     | R/W     | _     | R/W   |

| Reset   | 0      | 0      |       | 0     | 0       | 0       | _     | 0     |

F8h.0 **DPSEL:** Active DPTR Select

#### **1.5 Program Status Word (PSW)**

This register contains status information resulting from CPU and ALU operations. The instructions that affect the PSW are listed below.

| Instruction |   | Flag |    |

|-------------|---|------|----|

| instruction | С | OV   | AC |

| ADD         | Х | Х    | Х  |

| ADDC        | Х | Х    | Х  |

| SUBB        | Х | Х    | Х  |

| MUL         | 0 | Х    |    |

| DIV         | 0 | Х    |    |

| DA          | Х |      |    |

| RRC         | Х |      |    |

| RLC         | Х |      |    |

| SETB C      | 1 |      |    |

| Instruction |   | Flag |    |

|-------------|---|------|----|

| Instruction | С | OV   | AC |

| CLR C       | 0 |      |    |

| CPL C       | Х |      |    |

| ANL C, bit  | Х |      |    |

| ANL C, /bit | Х |      |    |

| ORL C, bit  | Х |      |    |

| ORL C, /bit | Х |      |    |

| MOV C, bit  | Х |      |    |

| CJNE        | Х |      |    |

|             |   |      |    |

A "0" means the flag is always cleared, a "1" means the flag is always set and an "X" means that the state of the flag depends on the result of the operation.

| SFR D0h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| PSW     | CY    | AC    | F0    | RS1   | RS0   | OV    | F1    | Р     |

| R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

D0h.7 **CY:** ALU carry flag

D0h.6 AC: ALU auxiliary carry flag

D0h.5 **F0:** General purpose user-definable flag

D0h.4~3 **RS1, RS0:** The contents of (RS1, RS0) enable the working register banks as:

- 00: Bank 0 (00h~07h)

- 01: Bank 1 (08h~0Fh)

- 10: Bank 2 (10h~17h)

- 11: Bank 3 (18h~1Fh)

- D0h.2 **OV:** ALU overflow flag

- D0h.1 **F1:** General purpose user-definable flag

- D0h.0 **P:** Parity flag. Set/cleared by hardware each instruction cycle to indicate odd/even number of "one" bits in the accumulator.

|       | PSW   |       |       |       |       |       |       |  |  |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| R/W   |  |  |  |

| CY    | AC    | FO    | RS1   | RS0   | OV    | F1    | Р     |  |  |  |

| _ |    |    |      |       |        |     |    |    |        |      |     |     |

|---|----|----|------|-------|--------|-----|----|----|--------|------|-----|-----|

|   |    |    | ık 3 | Bar   | gister | Reg |    |    |        |      |     | /   |

|   | R7 | R6 | R5   | R4    | R3     | R2  | R1 | R0 | 18h    | Bank | RS0 | RS1 |

| l |    |    | ık 2 | · Bar | gister | Reg |    |    | ¥ /    |      | KSU | KOI |

| I | R7 | R6 | R5   | R4    | R3     | R2  | R1 | R0 | 10h    | 3    | 1   | 1   |

| İ |    |    |      | · Bar | gister | Reg |    | -  |        | 2    | 0   | 1   |

| l | R7 | R6 | R5   | R4    | R3     | R2  | R1 | R0 | 08h    | 1    | 1   | 0   |

| l |    |    |      |       | gister |     |    |    |        | 0    | 0   | 0   |

|   | R7 | R6 | R5   | R4    | R3     | R2  | R1 | R0 | $\sim$ |      |     |     |

| 1 |    | ·  |      |       |        |     |    |    | 00h    |      |     |     |

#### 2. Memory

#### 2.1 Program Memory

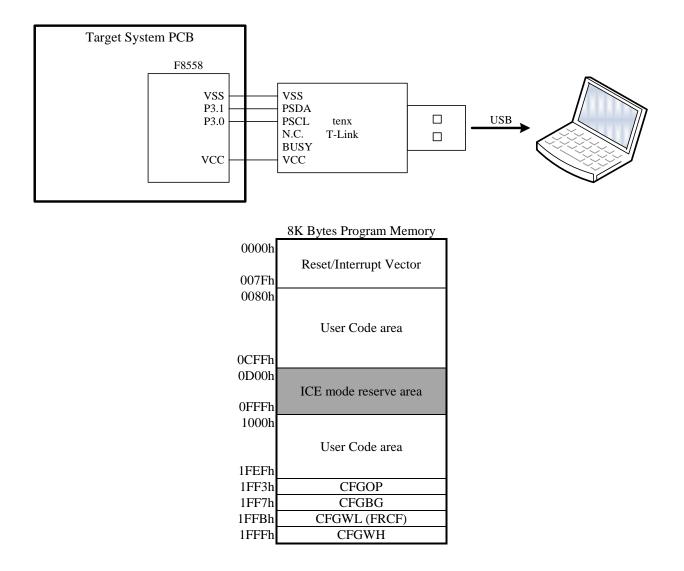

The Chip has an 8K Bytes Flash program memory, which can support In Circuit Programming (ICP) function mode. The Flash write endurance is at least 10K cycles. The Flash program memory address continuous space (0000h~1FFFh) is partitioned to several sectors for device operation.

#### 2.1.1 Program Memory Functional Partition

The last 16 bytes (1FF0h~1FFFh) of program memory is defined as chip Configuration Word (CFGW), which is loaded into the device control registers upon power on reset (POR). The address space 0000h~007Fh is occupied by Reset/Interrupt vectors as standard 8051 definition. In the in-circuit emulation (ICE) mode, user also needs to reserve the address space 0D00h~0FFFh for ICE System communication. CRC16H/L is the reserved area of the checksum. Tenx can provide a CRC verification subroutine. The user can calculate the checksum by the CRC verification subroutine to compare with CRC16H/L and check the validity of the ROM code.

|       | 8K Bytes Program Memory |

|-------|-------------------------|

| 0000h |                         |

|       | Reset/Interrupt Vector  |

| 007Fh |                         |

| 0080h |                         |

|       |                         |

|       | User Code area          |

|       |                         |

| 0CFFh |                         |

| 0D00h |                         |

|       | ICE mode reserve area   |

| 0FFFh |                         |

| 1000h |                         |

|       | User Code area          |

| 1FEFh |                         |

| 1FF3h | CFGOP                   |

| 1FF7h | CFGBG                   |

| 1FFBh | CFGWL (FRC)             |

| 1FFFh | CFGWH                   |

#### 2.1.2 Flash ICP Mode

The Flash memory can be programmed by the tenx proprietary writer (**TWR98/TWR99**), which needs at least four wires (VCC, VSS, P3.0, and P3.1 pins) to connect to this chip. If the user wants to program the Flash memory on the target circuit board (In Circuit Programming, ICP), these pins must be reserved sufficient freedom to be connected to the Writer.

| Writer wire number | Pin connection       |

|--------------------|----------------------|

| 4-Wire             | VCC, VSS, P3.0, P3.1 |

#### 2.2 EEPROM Memory

The **F8658** contains 128 bytes of data EEPROM memory. It is organized as a separate data space, in which single bytes can be read and written. The EEPROM has an endurance of at least 50K write/erase cycles.

|       | <b>EEPROM Memory</b> |

|-------|----------------------|

| EE00h | EEPROM[0]            |

| EE04h | EEPROM[1]            |

| EE08h |                      |

|       |                      |

|       |                      |

|       |                      |

| EFF8h | EEPROM[126]          |

| EFFCh | EEPROM[127]          |

**The EEPROM Write** usage is simply achieved by a "MOVX @DPTR, A" instruction while the DPTR contains the target EEPROM address (EE00h~EFFCh, ADDR=ADDR+4), and the ACC contains the data being written. EEPROM writing requires approximately  $2ms@V_{CC}=3V$ ,  $1ms@V_{CC}=5V$ . Meanwhile, the CPU stays in a waiting state, but all peripheral modules (Timers, PWM, and others) continue running during the writing time. The software must handle the pending interrupts after an EEPROM write. The **F8658** has a build-in EEPROM Time-out function for escaping write fail state. EEPROM writing needs  $V_{CC}$ =3.0V.

**The EEPROM Read** can be performed by the "MOVX A, @DPTR" instruction as long as the target address points the EE00h~EFFCh area. The EEPROM read does require approximately 300ns.

| ; EEPROM 6                | example code |                                                        |

|---------------------------|--------------|--------------------------------------------------------|

| ; need V <sub>CC</sub> >3 | 3.0V         |                                                        |

| MOV                       | DPTR, #EE00h | ; DPTR=EE00h=target EEPROM[0] address                  |

| MOV                       | A, #5Ah      | ; A=5Ah=target EEPROM[0] write data                    |

| MOV                       | EEPWE, #E2h  | ; EEPROM write enable                                  |

| MOV                       | AUX2, #02h   | ; EEPROM Time-Out function enable                      |

| MOVX                      | @DPTR, A     | ; EEPROM[0] =5Ah, after EEPROM write                   |

|                           |              | ; 1ms~2ms H/W writing time, CPU wait                   |

| MOV                       | EEPWE, #00h  | ; EEPROM write disable, immediately after EEPROM write |

| CLR                       | А            | ; A=0                                                  |

| MOVX                      | A, @DPTR     | ; A=5Ah                                                |

|                           |              |                                                        |

| SFR C9h  | Bit 7                                                                                               | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2           | Bit 1 | Bit 0     |  |  |

|----------|-----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-----------------|-------|-----------|--|--|

| EEPWE    |                                                                                                     |       |       | EEP   | PWE   |                 |       |           |  |  |

|          | —                                                                                                   | EEPTO | EEPWE | -     |       |                 |       |           |  |  |

| R/W      | W                                                                                                   | R/W   | R/W   | W     |       |                 |       |           |  |  |

| Reset    | —                                                                                                   | 0     | 0     | -     |       |                 |       |           |  |  |

| C9h.7~0  | <b>EEPWE</b> (W): Write E2h to set EEPWE control flag; Write other value to clear EEPWE flag. It is |       |       |       |       |                 |       |           |  |  |

| C)II.740 |                                                                                                     | ,     |       |       | 0     | viller value it |       | vL mag. n |  |  |

recommended to clear it immediately after EEPROM write.

C9h.6 EEPTO (R): EEPROM write Time-Out flag, set by H/W when EEPROM write Time-out occurs. Cleared by H/W when EEPWE=0.

C9h.5 **EEPWE** (**R**): Flag indicates EEPROM memory can be written or not, 1=EEPROM write enable.

| SFR F7h | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0    |

|---------|-------|-------|--------|--------|-------|-------|-------|----------|

| AUX2    | WI    | DTE   | PWRSAV | VBGOUT | DIV32 | EEI   | PTE   | MULDIV16 |

| R/W     | R/W   | R/W   | R/W    | R/W    | R/W   | R/W   | R/W   | R/W      |

| Reset   | 0     | 0     | 0      | 0      | 0     | 1     | 1     | 0        |

F7h.2~1 **EEPTE:** EEPROM write watchdog timer enable

00: Disable

01: wait 0.8mS trigger watchdog time-out flag, and escape the write fail state

10: wait 3.1mS trigger watchdog time-out flag, and escape the write fail state

11: wait 6.2mS trigger watchdog time-out flag, and escape the write fail state

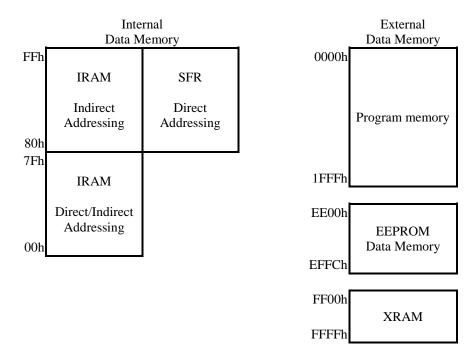

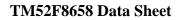

#### 2.3 Data Memory

As the standard 8051, the Chip has both Internal and External Data Memory space. The Internal Data Memory space consists of 256 Bytes IRAM and 97 SFRs, which are accessible through a rich instruction set. The External Data Memory space consists of 256 Bytes XRAM and 128 Bytes EEPROM, which can be only accessed by MOVX instruction.

#### 2.3.1 IRAM

IRAM is located in the 8051 internal data memory space. The whole 256 Bytes IRAM are accessible using indirect addressing but only the lower 128 Bytes are accessible using direct addressing. There are four directly addressable register banks (switching by PSW), which occupy IRAM space from 00h to 1Fh. The address 20h to 2Fh 16 Bytes IRAM space is bit-addressable. IRAM can be used as scratch pad registers or program stack.

#### 2.3.2 XRAM

XRAM is located in the 8051 external data memory space (address from FF00h to FFFFh). The 256 Bytes XRAM can be only accessed by "MOVX" instruction.

#### 2.3.3 SFRs

All peripheral functional modules such as I/O ports, Timers and UART operations for the chip are accessed via Special Function Registers (SFRs). These registers occupy upper 128 Bytes of direct Data Memory space locations in the range 80h to FFh. There are 14 bit-addressable SFRs (which means that eight individual bits inside a single byte are addressable), such as ACC, B register, PSW, TCON, SCON, and others. The remaining SFRs are only byte addressable. SFRs provide control and data exchange with the resources and peripherals of the Chip. The TM52 series of microcontrollers provides complete binary code with standard 8051 instruction set compatibility. Beside the standard 8051 SFRs, the Chip implements additional SFRs used to configure and access subsystems such as the ADC/PPG, which are unique to the Chip.

| _   | 8/0    | 9/1      | A/2      | B/3      | C/4      | D/5     | E/6     | F/7     |

|-----|--------|----------|----------|----------|----------|---------|---------|---------|

| F8h | AUX1   |          |          |          |          |         |         |         |

| F0h | В      | CRCDL    | CRCDH    | CRCIN    |          | CFGBG   | CFGWL   | AUX2    |

| E8h |        | CMP1CAL  | CMP2CAL  | CMP3CAL  | CMP4CAL  | CMP5CAL | OPCON   | OPCAL   |

| E0h | ACC    | MICON    | MIDAT    | SYNCNT   | SYNDLY   | LVRPD   | EXA     | EXB     |

| D8h | CLKCON | PWM0PRDH | PWM0PRDL | PWM1PRDH | PWM1PRDL |         |         |         |

| D0h | PSW    | PWM0DH   | PWM0DL   | PWM1DH   | PWM1DL   |         |         | CMPIEDG |

| C8h | T2CON  | EEPWE    | RCP2L    | RCP2H    | TL2      | TH2     | EXA2    | EXA3    |

| C0h |        | CMP1CON  | CMP2CON  | CMP3CON  | CMP4CON  | CMP5CON | CMP23EQ | CMP45EQ |

| B8h | IP     | IPH      | IP1      | IP1H     |          |         |         | CMPEQI  |

| B0h | P3     | PPGCON0  | PPGCON1  | PPGRLDL  |          |         | PPGTML  | PPGTMH  |

| A8h | IE     | INTE1    | ADCDL    | ADCDH    |          |         | CHSEL   |         |

| A0h | P2     | PWMCON   | P1MODL   | P1MODH   | P3MODL   | P3MODH  | PINMOD  | PWMCON2 |

| 98h | SCON   | SBUF     | PPDCON   | PPDSTA   | PPDTH    | PPDIE   |         |         |

| 90h | P1     |          |          |          | OPTION   | INTFLG  | P1WKUP  | SWCMD   |

| 88h | TCON   | TMOD     | TL0      | TL1      | TH0      | TH1     |         |         |

| 80h | P0     | SP       | DPL      | DPH      | INTE2    | INTFLG2 |         | PCON    |

#### 3. Power

The Chip provides Low Voltage Reset (LVR) function. There are 4-level LVR can be selected by CFGWH. It can be disabled at Fast by LVRPD (E5h) SFR. In addition, set PWRSAV will affect the LVR setting at Idle and Stop Mode.

| SFR E5h | Bit 7                                | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|---------|--------------------------------------|-----------------|-------|-------|-------|-------|-------|-------|--|--|--|

| LVRPD   |                                      | LVRPD           |       |       |       |       |       |       |  |  |  |

| R/W     |                                      | W               |       |       |       |       |       |       |  |  |  |

| Reset   | 0                                    | 0 0 0 0 0 0 0 0 |       |       |       |       |       |       |  |  |  |

| E5h     | LVRPD: LVR and POR power down option |                 |       |       |       |       |       |       |  |  |  |

**LVRPD:** LVR and POR power down option Write 0x37 to force LVR disable, POR disable Write 0x38 to force LVR disable, POR enable

| SFR F7h | Bit 7   | Bit 6 | Bit 5 | Bit 4  | Bit 3                                 | Bit 2 | Bit 1      | Bit 0    |

|---------|---------|-------|-------|--------|---------------------------------------|-------|------------|----------|

| AUX2    | WI      | WDTE  |       | VBGOUT | DIV32                                 | EEI   | PTE        | MULDIV16 |

| R/W     | R       | R/W   |       | R/W    | R/W                                   | R/    | W          | R/W      |

| Reset   | 0       | 0     | 0     | 0      | 0                                     | 1     | 1          | 0        |

| D71 5   | DIVDCAT | 0.1.1 | .1 1  |        | · · · · · · · · · · · · · · · · · · · | 10.1  | <b>7</b> 1 |          |

F7h.5 **PWRSAV:** Set 1 to reduce the chip's power consumption at Idle and Stop Mode

| Flash 1FFFh | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0  |

|-------------|-------|-------|-------|-------|-------|-------|---------|--------|

| CFGWH       | PROT  | XRSTE | LV    | LVRE  |       | _     | MVCLOCK | FRCPSC |

1FFFh.5~4 LVRE: Low Voltage Reset function select

00: Set LVR at 4.3V

01: Set LVR at 3.8V

10: Set LVR at 3.2V

11: Set LVR at 2.7V

#### 4. Reset

The Chip has five types of reset methods. Resets can be caused by Power on Reset (POR), External Pin Reset (XRST), Software Command Reset (SWRST), Watchdog Timer Reset (WDTR), or Low Voltage Reset (LVR). The CFGW controls the Reset functionality. The SFRs are returned to their default value after Reset.

#### 4.1 Power on Reset

After Power on Reset, the device stays on Reset state for 25 ms as chip warm up time, then downloads the CFGW register from Flash's last 16 bytes. The Power on Reset needs VCC pin's voltage first discharge to near VSS level, then rise beyond 2.7V.

#### 4.2 External Pin Reset

External Pin Reset is active low. It needs to keep at least 2 SRC clock cycle long to be seen by the chip. External Pin Reset can be disabled or enabled by CFGWH.

#### 4.3 Software Command Reset

Software Reset is activated by writing the SFR 97h with data 56h.

#### 4.4 Watchdog Timer Reset

WDT overflow Reset is disabled or enabled by SFR F7h. The WDT uses SRC as its counting time base. It runs in Fast/Slow mode and runs or stops in Idle/Stop mode. WDT overflow speed can be defined by WDTPSC SFR. WDT is cleared by device Reset or CLRWDT SFR bit.

#### 4.5 Low Voltage Reset

The Chip offers four options for LVR function. The user can make a selection by CFGWH, let LVR voltages of 4.3V, 3.8V, 3.2V, and 2.7V be selected separately. It can be disabled at Fast by LVRPD (E5h) SFR.

| System Clock frequency | 16 MHz   | 8 MHz    | 4 MHz    | 2 MHz    |

|------------------------|----------|----------|----------|----------|

| Minimum LVR level      | LVR=4.3V | LVR=2.7V | LVR=2.7V | LVR=2.7V |

#### LVR setting table

*Note:* LVR must be enable, also refer to AP-TM52XXXXX\_02S for LVR setting information.

| Flash 1FFFh                  | Bit 7                         | Bit 6         | Bit 5          | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0  |  |  |  |

|------------------------------|-------------------------------|---------------|----------------|-------|-------|-------|---------|--------|--|--|--|

| CFGWH                        | PROT                          | XRSTE         | LV             | RE    | _     |       | MVCLOCK | FRCPSC |  |  |  |

| 1FFFh.6                      | XRSTE: Ex                     | ternal Pin Re | set control    |       |       |       |         |        |  |  |  |

|                              | 0: Disable External Pin Reset |               |                |       |       |       |         |        |  |  |  |

| 1: Enable External Pin Reset |                               |               |                |       |       |       |         |        |  |  |  |

| 1FFFh.5~4                    | LVRE: Low                     | Voltage Res   | set function s | elect |       |       |         |        |  |  |  |

|                              | 00: Set LV                    | R at 4.3V     |                |       |       |       |         |        |  |  |  |

|                              | 01: Set LV                    | R at 3.8V     |                |       |       |       |         |        |  |  |  |

|                              | 10: Set LVR at 3.2V           |               |                |       |       |       |         |        |  |  |  |

|                              | 11: Set LVR at 2.7V           |               |                |       |       |       |         |        |  |  |  |

| SFR <b>94h</b> | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0 |

|----------------|--------|--------|-------|-------|-------|-------|--------|-------|

| OPTION         | UART1W | TM3CKS | WDT   | ГРSC  | ADCKS |       | TM3PSC |       |

| R/W            | R/W    | R/W    | R/    | W     | R/    | W     | R/     | W     |

| Reset          | 0      | 0      | 0     | 0     | 0     | 0     | 0      | 0     |

94h.5~4 WDTPSC: Watchdog Timer pre-scalar time select

00: 400ms WDT overflow rate

01: 200ms WDT overflow rate

10: 100ms WDT overflow rate

11: 50ms WDT overflow rate

| SFR <b>97h</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| SWCMD          |       |       |       |       |       |       |       |       |

| SWCMD          |       |       | -     | _     |       |       | WDTO  | _     |

| R/W            |       |       | V     | V     |       |       | R/W   | W     |

| Reset          |       |       | -     | _     |       |       | 0     | —     |

97h.7~0 **SWRST:** Write 56h to generate S/W Reset

| SFR E5h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| LVRPD   |       | LVRPD |       |       |       |       |       |       |  |  |  |

| R/W     |       | W     |       |       |       |       |       |       |  |  |  |

| Reset   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

E5h **LVRPD:** LVR and POR power down option Write 0x37 to force LVR disable, POR disable Write 0x38 to force LVR disable, POR enable

| SFR F7h | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0    |

|---------|-------|-------|-------|--------|-------|-------|-------|----------|

| AUX2    | WI    | WDTE  |       | VBGOUT | DIV32 | EEI   | PTE   | MULDIV16 |

| R/W     | R/    | R/W   |       | R/W    | R/W   | R/    | W     | R/W      |

| Reset   | 0     | 0     | 0     | 0      | 0     | 1     | 1     | 0        |

F7h.7~6 **WDTE:** Watchdog Timer Reset control

0x: Watchdog Timer Reset disable

10: Watchdog Timer Reset enable in Fast/Slow mode, disable in Idle/Stop mode

11: Watchdog Timer Reset always enable

F7h.5 **PWRSAV:** Set 1 to reduce the chip's power consumption at Idle and Stop Mode

| SFR F8h | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1 | Bit 0 |

|---------|--------|--------|-------|-------|---------|---------|-------|-------|

| AUX1    | CLRWDT | CLRTM3 | _     | ADSOC | CLRPWM0 | CLRPWM1 | _     | DPSEL |

| R/W     | R/W    | R/W    | _     | R/W   | R/W     | R/W     | _     | R/W   |

| Reset   | 0      | 0      | _     | 0     | 0       | 0       | _     | 0     |

F8h.7 **CLRWDT:** Set to clear WDT, H/W auto clear it at next clock cycle

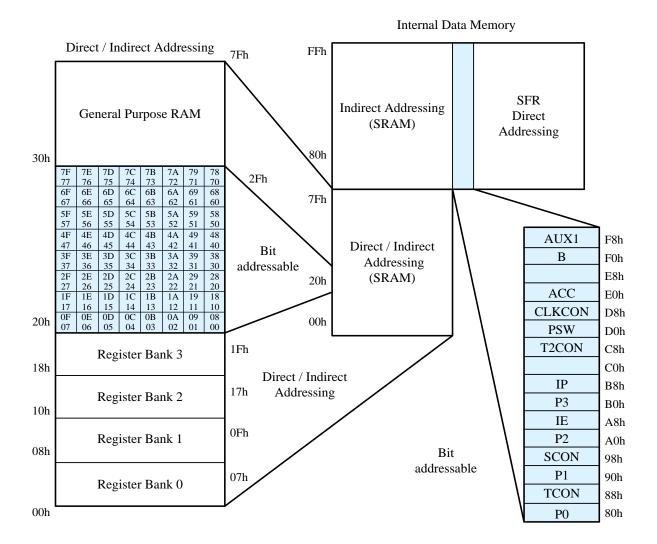

#### 5. Clock Circuitry and Operation Mode

#### 5.1 System Clock

The Chip is designed with dual-clock system. During runtime, user can directly switch the System clock from fast to slow or from slow to fast. It also can directly select a clock divider of 1, 2, 4 or 16. The Fast clock is FRC (Fast Internal RC, 16.5888 MHz or 8.2944MHz). The Slow clock is SRC (Slow Internal RC, 80 KHz). Fast mode and Slow mode are defined as the CPU running at Fast and Slow clock speeds.

After Reset, the device is running at Slow mode with 80KHz SRC. S/W should select the proper clock rate for chip operation safety. The higher  $V_{CC}$  allows the chip to run at a higher System clock frequency. In a typical condition, an 8 MHz System clock rate requires  $V_{CC}$ >2.0V.

The **CLKCON** SFR controls the System clock operating. H/W automatically blocks the S/W abnormally setting for this register. S/W can only change the Slow clock type in Fast mode and change the Fast clock type in Slow mode. Never to write both STPFCK=1 & SELFCK=1. It is recommended to write this SFR bit by bit.

| Flash <b>1FFBh</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| CFGWL              | _     |       |       |       | FRCF  |       |       |       |

1FFFh.6~0 **FRCF:** FRC frequency adjustment

FRC is trimmed to 16.5888 MHz in chip manufacturing. FRCF records the adjustment data.

| SFR F6h | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| CFGWL   | _     |       | FRCF  |       |       |       |       |       |

| R/W     | _     |       | R/W   |       |       |       |       |       |

| Reset   |       | -     |       |       | —     | -     |       | —     |

F6h.6~0 **FRCF:** FRC frequency adjustment

00=lowest frequency, 7Fh=highest frequency

The frequency range is about 13MHz (FRCF=00h) to 22MHz (FRCF=7Fh) with approaching linearity. Due to the chip process issue, the frequency range is different between each chip.

| SFR D8h | Bit 7                                                                                                 | Bit 6                                            | Bit 5         | Bit 4         | Bit 3        | Bit 2        | Bit 1      | Bit 0 |

|---------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|---------------|--------------|--------------|------------|-------|

| CLKCON  | —                                                                                                     | _                                                | _             | STPPCK        | STPFCK       | SELFCK       | CLK        | PSC   |

| R/W     | —                                                                                                     |                                                  |               | R/W           | R/W          | R/W          | R/         | W     |

| Reset   | _                                                                                                     |                                                  |               | 0             | 0            | 0            | 1          | 1     |

| D8h.4   | 4 <b>STPPCK:</b> Set 1 to stop UART/Timer0/Timer1/Timer2/ADC clock in Idle mode for current reducing. |                                                  |               |               |              |              |            |       |

|         | If set, only Timer3 and pin interrupts are alive in Idle Mode.                                        |                                                  |               |               |              |              |            |       |

| D8h.3   | STPFCK: Set 1 to stop Fast clock for power saving in Slow/Idle mode. This bit can be changed only     |                                                  |               |               |              |              |            |       |

|         | in Slow mode.                                                                                         |                                                  |               |               |              |              |            |       |

| D8h.2   | SELFCK: S                                                                                             | ystem clock                                      | source select | ion. This bit | can be chang | ed only when | n STPFCK=0 | ).    |

|         | 0: Slow clo                                                                                           | ck                                               |               |               |              |              |            |       |

|         | 1: Fast cloc                                                                                          | k                                                |               |               |              |              |            |       |

| D8h.1~0 | CLKPSC: S                                                                                             | •                                                | 1             |               | •            | es (Max.) de | lay.       |       |

|         | 00: System clock is Fast/Slow clock divided by 16                                                     |                                                  |               |               |              |              |            |       |

|         | •                                                                                                     |                                                  | /Slow clock   | •             |              |              |            |       |

|         | 10: System                                                                                            | 10: System clock is Fast/Slow clock divided by 2 |               |               |              |              |            |       |

11: System clock is Fast/Slow clock divided by 1

|               | CLKCO             | N (D8h)           |

|---------------|-------------------|-------------------|

| SYSCLK        | Bit3              | Bit2              |

|               | STPFCK            | SELFCK            |

| Fast FRC      | 0                 | 1                 |

| Slow SRC      | 0/1               | 0                 |

| Stop FRC      | $0 \rightarrow 1$ | 0                 |

| Switch to FRC | 0                 | $0 \rightarrow 1$ |

| Switch to SRC | 0                 | $1 \rightarrow 0$ |

*Note:* Because of the CLKPSC delay, it needs to wait for 16 clock cycles (max.) before switching Slow clock to Fast clock. Also refer to AP-TM52XXXXX\_01S and AP-TM52XXXXX\_02S about System Clock Application Note.

#### 5.2 Operation Mode

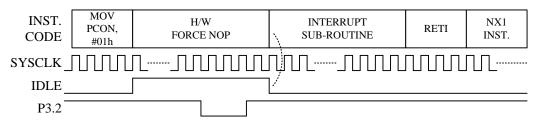

There are four operation modes for this device. **Fast Mode** is defined as the CPU running at Fast clock speed. **Slow Mode** is defined as the CPU running at Slow clock speed. When the System clock speed is lower, the power consumption is lower.

**Idle Mode** is entered by setting the IDL bit in PCON SFR. Both Fast and Slow clock can be set as the System clock source in Idle Mode, but Slow clock is better for power saving. In Idle mode, the CPU puts itself to sleep while the on-chip peripherals stay active. The "STPPCK" bit in CLKCON SFR can be set to furthermore reduce Idle mode current. If STPPCK is set, only Timer3 and pin interrupts are alive in Idle Mode, others peripherals such as Timer0/1/2, UART and ADC are stop. The slower System clock rate also helps current saving. It can be achieved by setup the CLKPSC SFR to divide System clock frequency. Idle mode is terminated by Reset or enabled Interrupts wake up.

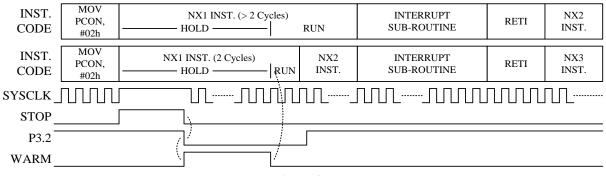

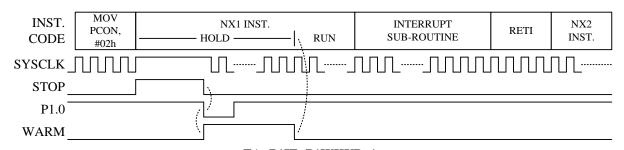

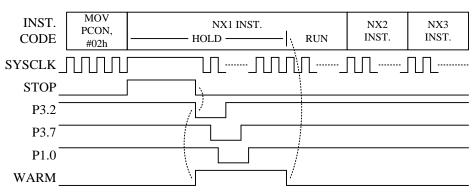

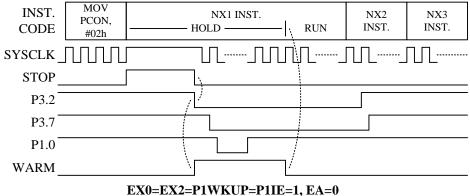

**Stop Mode** is entered by setting the PD bit in PCON SFR. This mode is the so-called "Power Down" mode in standard 8051. In Stop mode, all clocks stop except the WDT is alive if it is enabled. Stop mode is terminated by Reset or pin wake up.

*Note:* Chip cannot enter Stop Mode if INTn pin is low and wakeup is enabled. (INTn=0 and EXn=1, n=0,1,2) *Note:* FW must turn off Bandgap to obtain Tiny Current (PWRSAV=1, Disable OPA and CMP)

| SFR <b>87h</b> | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PCON           | SMOD  | _     | _     | —     | GF1   | GF0   | PD    | IDL   |

| R/W            | R/W   |       |       | —     | R/W   | R/W   | R/W   | R/W   |

| Reset          | 0     |       |       | _     | 0     | 0     | 0     | 0     |

| 0.51 4         |       |       |       | ~     |       |       |       |       |

87h.1 **PD:** Power down control bit, set 1 to enter Stop mode.

87h.0 **IDL:** Idle mode control bit, set 1 to enter Idle mode.

| SFR D8h                                                                                                   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 |

|-----------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|--------|--------|--------|-------|

| CLKCON                                                                                                    | —     | —     | —     | STPPCK | STPFCK | SELFCK | CLKPSC |       |

| R/W                                                                                                       | —     | _     | _     | R/W    | R/W    | R/W    | R/W    |       |

| Reset                                                                                                     | —     | _     | _     | 0      | 0      | 0      | 1      | 1     |

| D8h.4 <b>STPPCK:</b> Set 1 to stop UART/Timer0/Timer1/Timer2/ADC clock in Idle mode for current reducing. |       |       |       |        |        |        |        |       |

| If set, only Timer3 and pin interrupts are alive in Idle Mode.                                            |       |       |       |        |        |        |        |       |

D8h.3 **STPFCK:** Set 1 to stop Fast clock for power saving in Slow/Idle mode. This bit can be changed only in Slow mode.

D8h.2 **SELFCK:** System clock source selection. This bit can be changed only when STPFCK=0. 0: Slow clock

1: Fast clock

D8h.1~0 CLKPSC: System clock prescaler. Effective after 16 clock cycles (Max.) delay.

00: System clock is Fast/Slow clock divided by 16

01: System clock is Fast/Slow clock divided by 4

10: System clock is Fast/Slow clock divided by 2

11: System clock is Fast/Slow clock divided by 1

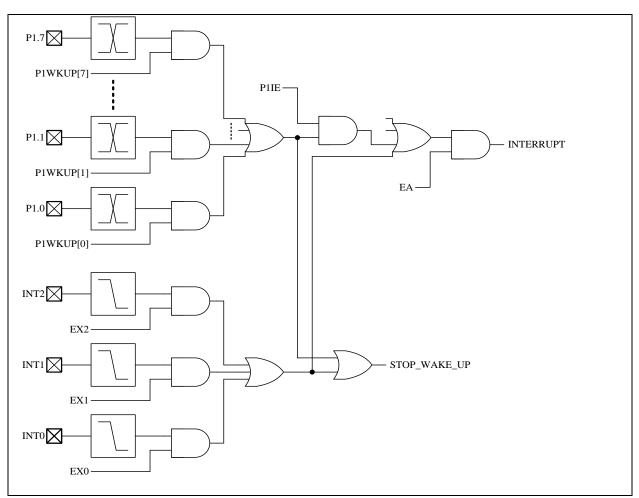

#### 6. Interrupt and Wake-up

This Chip has a 20-source four-level priority interrupt structure. All enabled Interrupts can wake up CPU from Idle mode, but only the Pin Interrupts can wake up CPU from Stop mode. Each interrupt source has its own enable control bit. An interrupt event will set its individual Interrupt Flag, no matter whether its interrupt enable control bit is 0 or 1. The Interrupt vectors and flags are list below.

| Vector | Flag        | Description                                                 |

|--------|-------------|-------------------------------------------------------------|

| 0003   | IE0         | INT0 external pin Interrupt (can wake up Stop mode)         |

| 000B   | TF0         | Timer0 Interrupt                                            |

| 0013   | IE1         | INT1 external pin Interrupt (can wake up Stop mode)         |

| 001B   | TF1         | Timer1 Interrupt                                            |

| 0023   | RI+TI       | Serial Port (UART) Interrupt                                |

| 002B   | TF2+EXF2    | Timer2 Interrupt                                            |

| 0033   | -           | Reserved for ICE mode use                                   |

| 003B   | TF3         | Timer3 Interrupt                                            |

| 0043   | P1IF        | Port1 external pin change Interrupt (can wake up Stop mode) |

| 004B   | IE2         | INT2 external pin Interrupt (can wake up Stop mode)         |

| 0053   | ADIF        | ADC Interrupt                                               |

| 005B   | MIICIF      | MIIC Interrupt                                              |

| 0063   | PPGIF+PPDIF | PPG/PPD Interrupt                                           |

| 006B   | CMPIF       | Comparator1~5 Interrupt                                     |

| 0073   | PWMIF       | PWM0~1 Interrupt                                            |

**Interrupt Vector & Flag**

#### 6.1 Interrupt Enable and Priority Control

The IE and INTE1 SFRs decide whether the pending interrupt is serviced by CPU. The IP, IPH, IP1 and IP1H SFRs decide the interrupt priority. An interrupt will be serviced as long as an interrupt of equal or higher priority is not already being serviced. If an interrupt of equal or higher level priority is being serviced, the new interrupt will wait until it is finished before being serviced. If a lower priority level interrupt is being serviced, it will be stopped and the new interrupt serviced. When the new interrupt is finished, the lower priority level interrupt that was stopped will be completed.

| SFR <b>96h</b> | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------------|-------|--------|-------|-------|-------|-------|-------|-------|

| P1WKUP         |       | P1WKUP |       |       |       |       |       |       |

| R/W            |       |        |       | R/    | W     |       |       |       |

| Reset          | 0     | 0      | 0     | 0     | 0     | 0     | 0     | 0     |

96h.7~0 **P1WKUP:** P1.7~P1.0 pin individual Wake up/Interrupt enable control

0: Disable

1: Enable

| SFR A8h | Bit 7                                                                                     | Bit 6                                                                            | Bit 5                                 | Bit 4        | Bit 3         | Bit 2      | Bit 1        | Bit 0  |  |

|---------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|--------------|---------------|------------|--------------|--------|--|

| IE      | EA                                                                                        | _                                                                                | ET2                                   | ES           | ET1           | EX1        | ET0          | EX0    |  |

| R/W     | R/W                                                                                       | —                                                                                | R/W                                   | R/W          | R/W           | R/W        | R/W          | R/W    |  |

| Reset   | 0                                                                                         | —                                                                                | 0                                     | 0            | 0             | 0          | 0            | 0      |  |

| A8h.7   | EA: Global                                                                                | interrupt enal                                                                   | ole                                   |              |               |            |              |        |  |

|         |                                                                                           | all interrupts                                                                   |                                       |              |               |            |              |        |  |

|         |                                                                                           | 1: Each interrupt is enabled or disabled by its individual interrupt control bit |                                       |              |               |            |              |        |  |

| A8h.5   | ET2: Timer2 interrupt enable                                                              |                                                                                  |                                       |              |               |            |              |        |  |

|         |                                                                                           | 0: Disable Timer2 interrupt                                                      |                                       |              |               |            |              |        |  |

| A 01. 4 |                                                                                           | Timer2 interru                                                                   |                                       | 1.           |               |            |              |        |  |

| A8h.4   | ES: Serial Port (UART) interrupt enable                                                   |                                                                                  |                                       |              |               |            |              |        |  |

|         | 0: Disable Serial Port (UART) interrupt<br>1: Enable Serial Port (UART) interrupt         |                                                                                  |                                       |              |               |            |              |        |  |

| A8h.3   | ET1: Timer                                                                                | ,                                                                                | · · · · · · · · · · · · · · · · · · · | րւ           |               |            |              |        |  |

| Aon.5   |                                                                                           | Timer1 interr                                                                    |                                       |              |               |            |              |        |  |

|         |                                                                                           | imer1 interr                                                                     |                                       |              |               |            |              |        |  |

| A8h.2   | EX1: INT1                                                                                 |                                                                                  |                                       | top mode wal | ke up enable  |            |              |        |  |

|         |                                                                                           |                                                                                  |                                       | op mode wak  |               |            |              |        |  |

|         | 1: Enable I                                                                               | NT1 pin Inte                                                                     | rrupt and Sto                         | p mode wake  | up, it can wa | ake up CPU | from Stop me | ode no |  |

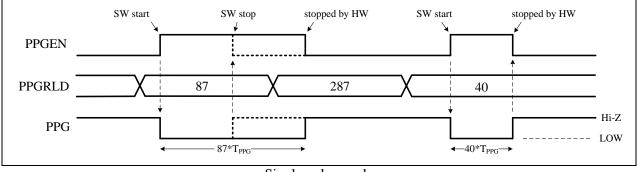

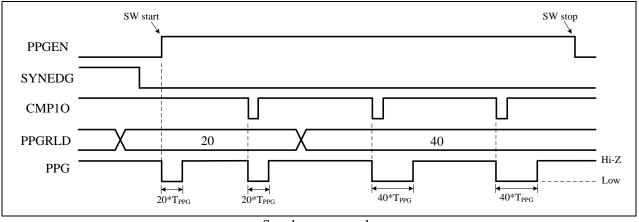

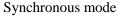

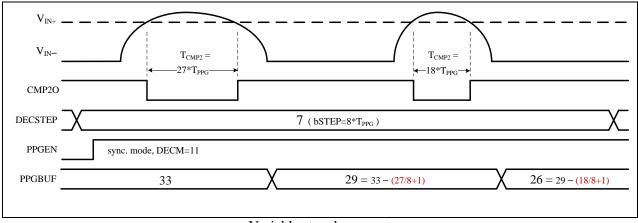

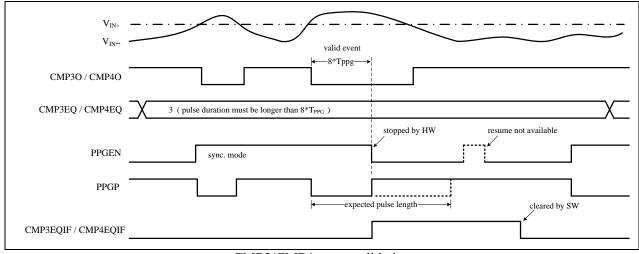

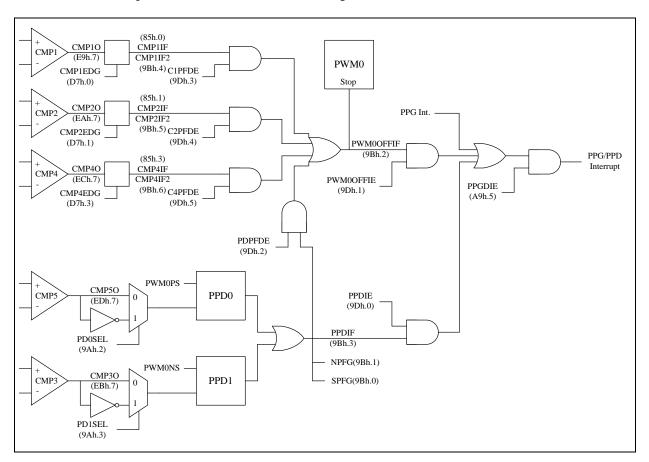

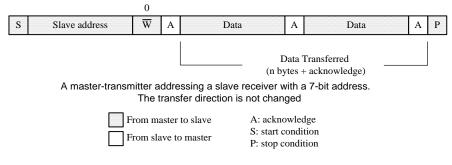

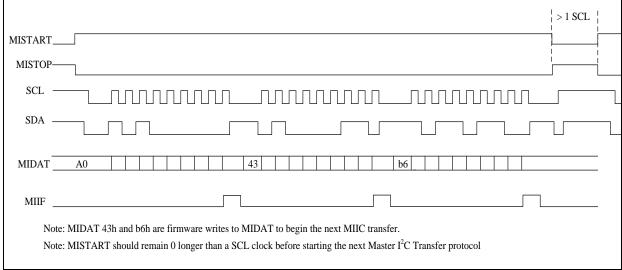

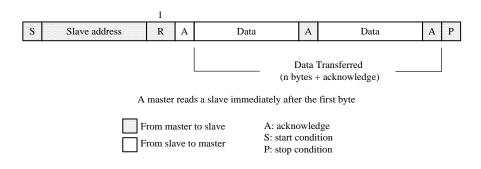

|         |                                                                                           | A is 0 or 1.                                                                     |                                       |              |               |            |              |        |  |