tenx reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. Tenx does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Tenx products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses tenx products for any such unintended or unauthorized application, Buyer shall indemnify and hold tenx and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that tenx was negligent regarding the design or manufacture of the part.

## AMENDMENT HISTORY

| Version | Date      | Description                                                          |  |  |  |

|---------|-----------|----------------------------------------------------------------------|--|--|--|

| V1.0    | Aug, 2010 | New release                                                          |  |  |  |

| V1.1    | Dec, 2010 | 1. Add more description about /Borrow and /Digit Borrow in ALU       |  |  |  |

|         |           | and Working (W) Register section.                                    |  |  |  |

|         |           | 2. Add Internal RC mode description and figure in System Clock       |  |  |  |

|         |           | Oscillator section.                                                  |  |  |  |

|         |           | 3. Modify the status affected of the NOP instruction.                |  |  |  |

| V1.2    | Feb, 2011 | 1. Modify IVCPD description in System Configuration Register         |  |  |  |

|         |           | (SYSCFG) section.                                                    |  |  |  |

| V1.3    | May, 2011 | Add operating voltage selection in System Configuration              |  |  |  |

|         |           | Register (SYSCFG) section.                                           |  |  |  |

|         |           | 2. Add 32 KHz operating current in Electrical Characteristics        |  |  |  |

|         | 0 0011    | section.                                                             |  |  |  |

| V1.4    | Oct, 2011 | Modify the package type data.                                        |  |  |  |

| V1.5    | Dec, 2011 | Add Ordering Information table in the Packaging Information          |  |  |  |

|         |           | section.                                                             |  |  |  |

|         |           | 1. Add the Electrical Characteristics specs in the Features section. |  |  |  |

| V1.6    | Jan, 2012 | 2. Add description in Reset section.                                 |  |  |  |

|         |           | 3. Merge the information about LVR Circuit Characteristics into      |  |  |  |

|         | T 1 2012  | DC Characteristics table.                                            |  |  |  |

| V1.7    | Jul, 2012 | Modify document format.                                              |  |  |  |

| V1.8    | Apr, 2013 | 1. Modify Block Diagram.                                             |  |  |  |

|         | 1 /       | 2. Modify Packaging Information.                                     |  |  |  |

| T.11.0  | T 1 2012  | 1. Add supported EV board on ICE.                                    |  |  |  |

| V1.9    | Jul, 2013 | 2. Modify pin assignment name.                                       |  |  |  |

|         |           | 3. Add pin summary.                                                  |  |  |  |

| N/2 0   | . 2012    | 1. Modify 32-DIP/SOP pin assignment.                                 |  |  |  |

| V2.0    | Aug, 2013 | 2. Modify Interrupt description.                                     |  |  |  |

|         |           | 3. Modify Ordering Information                                       |  |  |  |

DS-TM57ME20\_E 2 Rev 2.0, 2013/09/03

# **CONTENTS**

| AMENDMENT HISTORY                                    | 2  |

|------------------------------------------------------|----|

| CONTENTS                                             | 3  |

| FEATURES                                             | 5  |

| BLOCK DIAGRAM                                        | 8  |

| PIN ASSIGNMENT                                       | 9  |

| PIN DESCRIPTION                                      |    |

| PIN SUMMARY                                          |    |

| FUNCTIONAL DESCRIPTION                               |    |

|                                                      |    |

| 1. CPU Core                                          |    |

| 1.1 Clock Scheme and Instruction Cycle               |    |

| 1.2 Addressing Mode                                  |    |

| 1.3 Programming Counter (PC) and Stack               |    |

| 1.4 ALU and Working (W) Register                     |    |

| 1.5 STATUS Register                                  |    |

| 1.6 Interrupt                                        |    |

| 2. Chip Operation Mode                               | 16 |

| 2.1 Reset                                            | 16 |

| 2.2 System Configuration Register (SYSCFG)           | 17 |

| 2.3 MTP Program ROM                                  | 18 |

| 2.4 Power-Down Mode                                  |    |

| 2.5 Dual System Clock                                |    |

| 2.6 Dual System Clock Modes Transition               |    |

| 3. Peripheral Functional Block                       | 23 |

| 3.1 Watchdog (WDT) / Wakeup (WKT) Timer              | 23 |

| 3.2 Timer0: 8-bit Timer/Counter with Pre-scale (PSC) |    |

| 3.3 Timer1: 16-bit Timer with Pre-scale (PSC)        |    |

| 3.4 Timer2: 15-bit Timer with Pre-scale (PSC)        |    |

| 3.5 8+2 bits PWM                                     |    |

| 3.6 Analog Comparator                                |    |

| 3.7 System Clock Oscillator                          | 31 |

| 4. I/O Port                                          | 32 |

| 4.1 PA0-2                                            |    |

| 4.2 PA3-6, PB0-7, PC0-7, PD0-4                       |    |

| 4.3 PA7                                              | 34 |

| MEMORY MAP                                           | 35 |

| F-Plane                                              | 35 |

| R-Plane                             | 37 |

|-------------------------------------|----|

| INSTRUCTION SET                     | 39 |

| ELECTRICAL CHARACTERISTICS          | 51 |

| 1. Absolute Maximum Ratings         | 51 |

| 2. DC Characteristics               | 52 |

| 3. Clock Timing                     | 53 |

| 4. Reset Timing Characteristics     | 53 |

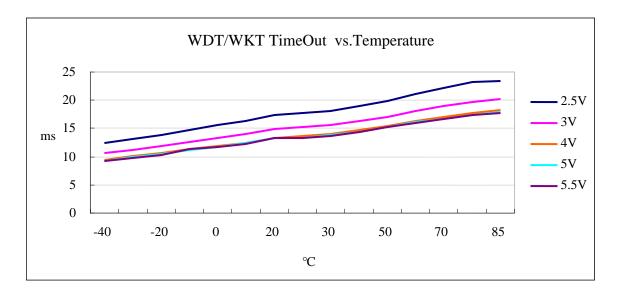

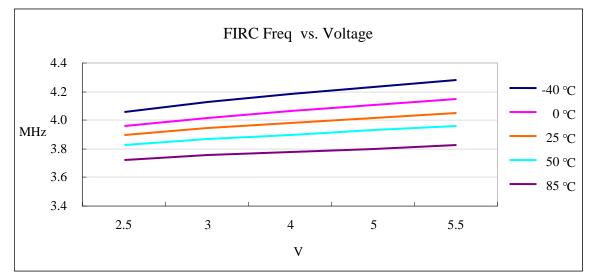

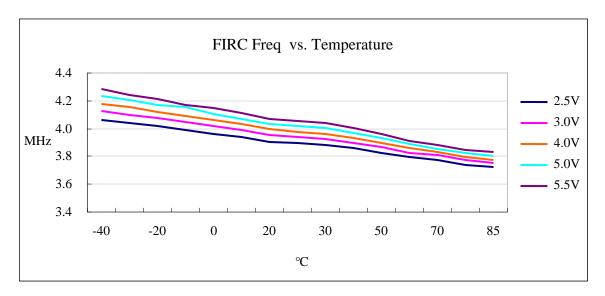

| 5. Characteristic Graphs            | 54 |

| PACKAGING INFORMATION               | 56 |

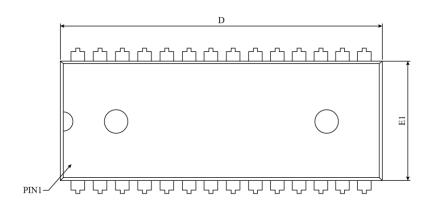

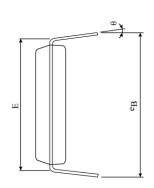

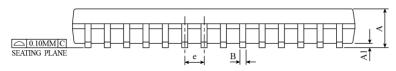

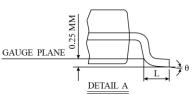

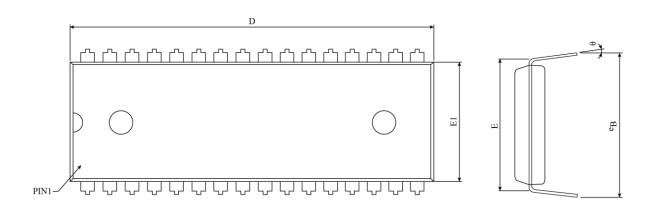

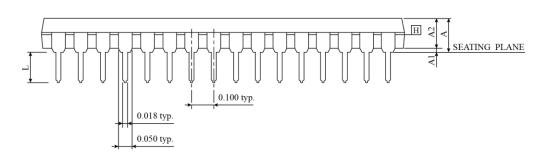

| 28-DIP ( 600mil ) Package Dimension | 57 |

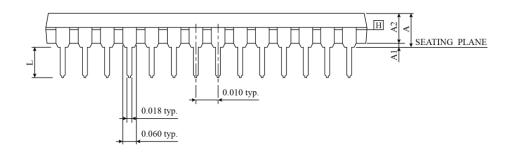

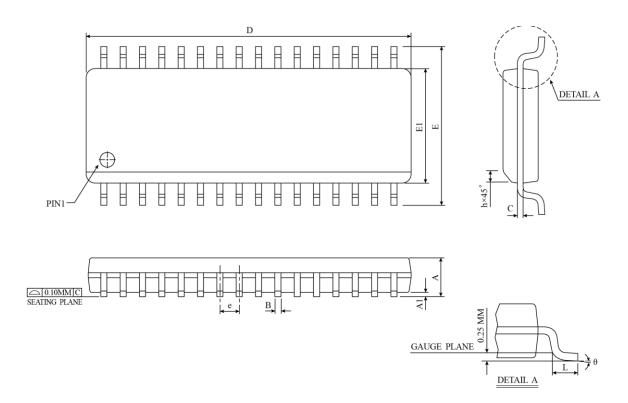

| 28-SOP Package Dimension            | 58 |

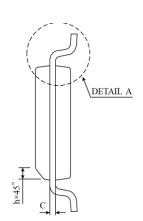

| 32-DIP ( 600mil ) Package Dimension | 59 |

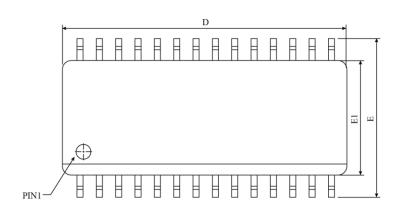

| 32-SOP ( 300mil ) Package Dimension | 60 |

## **FEATURES**

- 1. MTP: 2K x 14 bits MTP ROM (Support ISP uses 5 wires)

- 2. RAM: 96 x 8 bits

- 3. STACK: 8 Levels

- **4.** I/O ports: Four Bit programmable I/O ports (Max. 29 pins)

- 5. Timer0/Counter: 8-bit timer/counter with divided by 1~256 pre-scale option, stop counting

- 6. Timer1: 16-bit auto-reloadable timer with divided by 1~256 pre-scale option

- **7.** Timer2:

- 15-bit Timer2 with divided by 2-bit pre-scale option

- 15-bit Timer2 with 4 interrupt interval option

Timer2 is used to idle mode wake-up timer or one simple 15-bit time base

- 8. Two 8+2 bits PWM channels capable of 1024 duty resolution and 256 period resolution

- **9.** Two analog voltage comparators

- 10. PB0~PB7 individual pin low level wake up

- 11. Oscillation Sources

- Fast Clock:

- FXT (Fast Crystal): 1 MHz~12 MHz

- FIRC (Fast Internal RC): 4 MHz

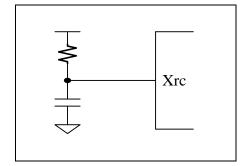

- XRC (External R, External C): 10 KHz~3 MHz

- Slow Clock:

- SXT (Slow Crystal): 32768 Hz

- XRC (External R, External C): 10 KHz~3 MHz

- SIRC (Slow Internal RC): 138 KHz/35 KHz/8.5 KHz/2.1 KHz, @5V; 119 KHz/30 KHz/7.5 KHz/1.9 KHz, @3V

- 12. Power Saving Operation Mode

- Fast Mode: Slow clock can be disabled or enabled

- Slow Mode: Fast clock stops, CPU is running

- Idle Mode: Slow clock is running, CPU stops, Timer2 is running

- Stop Mode: All clocks stop, Wake-up Timer is disabled or enabled

DS-TM57ME20\_E 5 Rev 2.0, 2013/09/03

- 13. Dual system clock

- FIRC + SIRC

- FIRC + SXT

- FIRC + XRC

- FXT + SIRC

- XRC + SIRC

- **14.** Reset

- Power On Reset

- Watchdog Reset

- Low Voltage Reset

- External Pin Reset

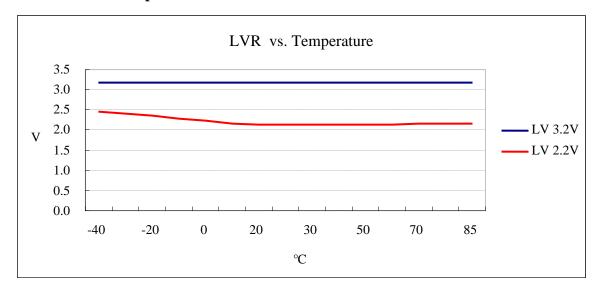

- **15.** 2-Level Low Voltage Reset: 2.2V/3.2V (Can be disabled)

- 16. Operation Voltage: Low Voltage Reset Level to 5.5V

- $fosc = 4 \text{ MHz}, 2.2 \text{V} \sim 5.5 \text{V}$

- $fosc = 8 \text{ MHz}, 2.3\text{V} \sim 5.5\text{V}$

- $fosc = 12 \text{ MHz}, 2.6\text{V} \sim 5.5\text{V}$

- $fosc = 16 \text{ MHz}, 3.3\text{V} \sim 5.5\text{V}$

#### **17.** Interrupts

- Two External Interrupt pins:

- One pin is falling edge triggered

- One pin is rising or falling edge triggered

- Timer0, Timer1, Timer2, Wake-up Timer Interrupt

- CP0, CP1 Interrupt

- 18. Watchdog Timer

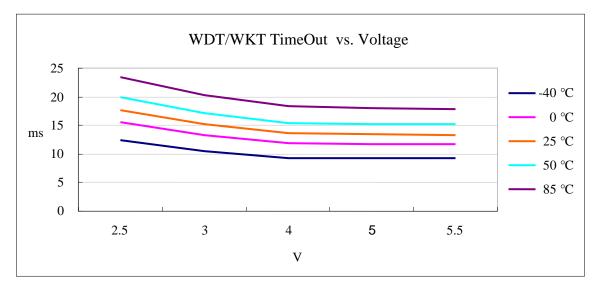

- Clocked by built-in RC oscillator with 4 adjustable reset/interrupt time durations (111 ms/57 ms/28 ms/14 ms, @5V; 121 ms/61 ms/30 ms/15 ms, @3V)

- Watchdog timer can be disabled/enabled in stop mode

- 19. Support auto store/restore STATUS and W before/after interrupt routine

- **20.** I/O Ports

- CMOS Output

- Pseudo-Open-Drain or Open-Drain Output

- Schmitt Trigger Input with/without pull-up resistor

- 21. Instruction Set: 36 Instructions

- 22. Package Types: 28-DIP/SOP, 32-DIP/SOP

23. Supported EV board on ICE

EV board: EV2788

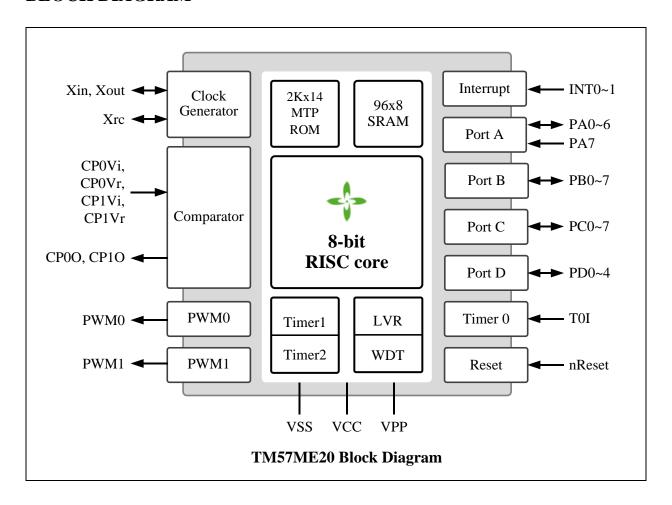

## **BLOCK DIAGRAM**

DS-TM57ME20\_E 8 Rev 2.0, 2013/09/03

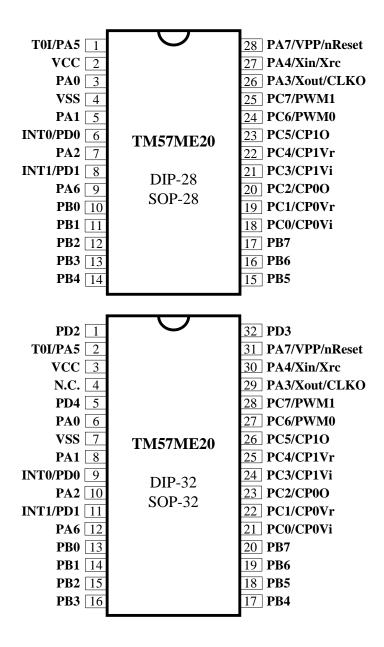

## PIN ASSIGNMENT

DS-TM57ME20\_E 9 Rev 2.0, 2013/09/03

## PIN DESCRIPTION

| Name         | In/Out | Pin Description                                                                                                                                         |  |  |

|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PA0-PA2      | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or "pseudo-open-drain" output. Pull-up resistors are assignable by software. |  |  |

| PA3-PA6      | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or open-drain output. Pull-up resistors are assignable by software.          |  |  |

| PA7          | I      | Schmitt-trigger input                                                                                                                                   |  |  |

| PB0–PB7      | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or open-drain output. Pull-up resistors are assignable by software.          |  |  |

| PC0-PC7      | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output or open-drain output. Pull-up resistors are assignable by software.          |  |  |

| PD0-PD4      | I/O    | Bit-programmable I/O port for Schmitt-trigger input, CMOS push-pull output open-drain output. Pull-up resistors are assignable by software.             |  |  |

| nRESET       | I      | External active low reset                                                                                                                               |  |  |

| Xin, Xout    | _      | Crystal/Resonator oscillator connection for system clock                                                                                                |  |  |

| Xrc          | _      | External RC oscillator connection for system clock                                                                                                      |  |  |

| CLKO         | О      | CPU Instruction clock output for external/internal RC mode                                                                                              |  |  |

| VCC, VSS     | P      | Power Voltage input pin and ground                                                                                                                      |  |  |

| VPP          | I      | PROM programming high voltage input                                                                                                                     |  |  |

| INT0-INT1    | I      | External interrupt input                                                                                                                                |  |  |

| CP0Vi, CP1Vi | I      | Comparator voltage input                                                                                                                                |  |  |

| CP0Vr, CP1Vr | I      | Comparator reference voltage input                                                                                                                      |  |  |

| CP0O, CP1O   | О      | Comparator output                                                                                                                                       |  |  |

| PWM0-PWM1    | О      | PWM output                                                                                                                                              |  |  |

| TOI          | I      | Clock input to Timer0                                                                                                                                   |  |  |

## **PIN SUMMARY**

| Pi<br>Nun  |            |                |      |              |                | GPIO |       |     | #                    | A   | Altern    | ate Fu | nction |

|------------|------------|----------------|------|--------------|----------------|------|-------|-----|----------------------|-----|-----------|--------|--------|

|            |            |                |      | Inj          | put            | (    | Outpu | t   | <b>Ses</b>           |     |           |        |        |

| 32-SOP/DIP | 28-SOP/DIP | Pin Name       | Туре | Weak Pull-up | Ext. Interrupt | 0.D  | P.O.D | P.P | Function After Reset | PWM | Touch Key | ADC    | MISC   |

| 1          | -          | PD2            | I/O  | 0            |                | 0    |       | 0   | PD2                  |     |           |        |        |

| 2          | 1          | PA5/T0I        | I/O  | 0            |                | 0    |       | 0   | PA5                  |     |           |        | TOI    |

| 3          | 2          | VCC            | P    |              |                |      |       |     |                      |     |           |        |        |

| 4          | -          | NC             | -    |              |                |      |       |     |                      |     |           |        |        |

| 5          | -          | PD4            | I/O  | 0            |                | 0    |       | 0   | PD4                  |     |           |        |        |

| 6          | 3          | PA0            | I/O  | 0            |                |      | 0     | 0   | PA0                  |     |           |        |        |

| 7          | 4          | VSS            | P    |              |                |      |       |     |                      |     |           |        |        |

| 8          | 5          | PA1            | I/O  | 0            |                |      | 0     | 0   | PA1                  |     |           |        |        |

| 9          | 6          | PD0/INT0       | I/O  | 0            | 0              | 0    |       | 0   | PD0                  |     |           |        |        |

| 10         | 7          | PA2            | I/O  | 0            |                |      | 0     | 0   | PA2                  |     |           |        |        |

| 11         | 8          | PD1/INT1       | I/O  | 0            | 0              | 0    |       | 0   | PD1                  |     |           |        |        |

| 12         | 9          | PA6            | I/O  | 0            |                | 0    |       | 0   | PA6                  |     |           |        |        |

| 13         | 10         | PB0            | I/O  | 0            |                | 0    |       | 0   | PB0                  |     |           |        |        |

| 14         | 11         | PB1            | I/O  | 0            |                | 0    |       | 0   | PB1                  |     |           |        |        |

| 15         | 12         | PB2            | I/O  | 0            |                | 0    |       | 0   | PB2                  |     |           |        |        |

| 16         | 13         | PB3            | I/O  | 0            |                | 0    |       | 0   | PB3                  |     |           |        |        |

| 17         | 14         | PB4            | I/O  | 0            |                | 0    |       | 0   | PB4                  |     |           |        |        |

| 18         | 15         | PB5            | I/O  | 0            |                | 0    |       | 0   | PB5                  |     |           |        |        |

| 19         | 16         | PB6            | I/O  | 0            |                | 0    |       | 0   | PB6                  |     |           |        |        |

| 20         | 17         | PB7            | I/O  | 0            |                | 0    |       | 0   | PB7                  |     |           |        |        |

| 21         | 18         | PC0/CP0Vi      | I/O  | 0            |                | 0    |       | 0   | PC0                  |     |           |        | CP0Vi  |

| 22         | 19         | PC1/CP0Vr      | I/O  | 0            |                | 0    |       | 0   | PC1                  |     |           |        | CP0Vr  |

| 23         | 20         | PC2/CP0O       | I/O  | 0            |                | 0    |       | 0   | PC2                  |     |           |        | CP0O   |

| 24         | 21         | PC3/CP1Vi      | I/O  | 0            |                | 0    |       | 0   | PC3                  |     |           |        | CP0Vi  |

| 25         | 22         | PC4/CP1Vr      | I/O  | 0            |                | 0    |       | 0   | PC4                  |     |           |        | CP1Vr  |

| 26         | 23         | PC5/CP1O       | I/O  | 0            |                | 0    |       | 0   | PC5                  |     |           |        | CP1O   |

| 27         | 24         | PC6/PWM0       | I/O  | 0            |                | 0    |       | 0   | PC6                  | 0   |           |        |        |

| 28         | 25         | PC7/PWM1       | I/O  | 0            |                | 0    |       | 0   | PC7                  | 0   |           |        |        |

| 29         | 26         | PA3/Xout/CLKO  | I/O  | 0            |                | 0    |       | 0   | PA3                  |     |           |        | CLKO   |

| 30         | 27         | PA4/Xin/Xrc    | I/O  | 0            |                | 0    |       | 0   | PA4                  |     |           |        |        |

| 31         | 28         | PA7/VPP/nReset | I    | 0            |                |      |       |     | PA7                  |     |           |        | nReset |

| 32         | -          | PD3            | I/O  | 0            |                | 0    |       | 0   | PD3                  |     |           |        |        |

Symbol: P.P. = Push-Pull Output P.O.D. = Pseudo Open Drain

O.D. = Open Drain

## **FUNCTIONAL DESCRIPTION**

#### 1. CPU Core

## 1.1 Clock Scheme and Instruction Cycle

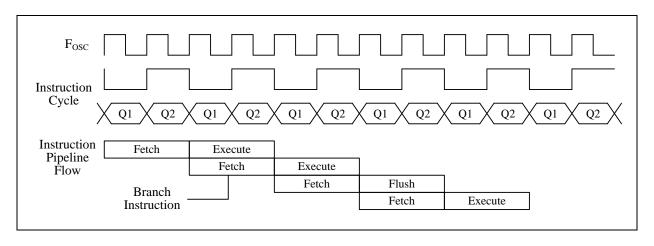

The system clock is internally divided by two to generate Q1 state and Q2 state for each instruction cycle. The Programming Counter (PC) is updated at Q1 and the instruction is fetched from program ROM and latched into the instruction register in Q2. It is then decoded and executed during the following Q1-Q2 cycle. Branch instructions take two cycles since the fetch instruction is 'flushed' from the pipeline, while the new instruction is being fetched and then executed.

DS-TM57ME20\_E 12 Rev 2.0, 2013/09/03

#### 1.2 Addressing Mode

There are two Data Memory Planes in CPU, R-Plane and F-Plane. The registers in R-Plane are write-only. The "MOVWR" instruction copy the W-register's content to R-Plane registers by direct addressing mode.

The lower locations of F-Plane are reserved for the SFR. Above the SFR is General Purpose Data Memory, implemented as static RAM. F-Plane can be addressed directly or indirectly. Indirect Addressing is made by INDF register. The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer). The first half of F-Plane is bit-addressable, while the second half of F-Plane is not bit-addressable.

| ,         | R-Plane                         |

|-----------|---------------------------------|

| 00        | MOVWR Instruction<br>Write Only |

| <b>3F</b> |                                 |

|          | F-Plane                 |

|----------|-------------------------|

| 00       | SFR<br>Bit Addressable  |

| 1F       |                         |

| 20       | SRAM<br>Bit Addressable |

| 3F       |                         |

| 40<br>7F | SRAM                    |

#### 1.3 Programming Counter (PC) and Stack

The Programming Counter is 11-bit wide capable of addressing a 2K x 14 MTP ROM. As a program instruction is executed, the PC will contain the address of the next program instruction to be executed. The PC value is normally increased by one except the followings. The Reset Vector (000h) and the Interrupt Vector (001h) are provided for PC initialization and Interrupt. For CALL/GOTO instructions, PC loads 11 bits address from instruction word. For RET/RETI/RETLW instructions, PC retrieves its content from the top level STACK. For the other instructions updating PC [7:0], the PC [10:8] keeps unchanged. The STACK is 11-bit wide and 8-level in depth. The CALL instruction and hardware interrupt will push STACK level in order. While the RET/RETI/RETLW instruction pops the STACK level in order.

DS-TM57ME20\_E 13 Rev 2.0, 2013/09/03

#### 1.4 ALU and Working (W) Register

The ALU is 8-bit wide and capable of addition, subtraction, shift and logical operations. In two-operand instructions, typically one operand is the W register, which is an 8-bit non-addressable register used for ALU operations. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either W register or a file register. Depending on the instruction executed, the ALU may affect the values of Carry (C), Digit Carry (DC), and Zero (Z) Flags in the STATUS register. The C and DC flags operate as a /Borrow and /Digit Borrow, respectively, in subtraction.

Note: /Borrow represents inverted of Borrow register.

/Digit Borrow represents inverted of Digit Borrow register.

#### 1.5 STATUS Register

This register contains the arithmetic status of ALU and the reset status. The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. It is recommended, therefore, that only BCF, BSF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect those bits.

| STATUS                                       | Bit 7                                          | Bit 6                                                                                                  | Bit 5     | Bit 4 | Bit 3           | Bit 2 | Bit 1           | Bit 0 |  |

|----------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------|-------|-----------------|-------|-----------------|-------|--|

| Reset Value                                  | _                                              | _                                                                                                      | _         | 0     | 0               | 0     | 0               | 0     |  |

| R/W                                          | _                                              | _                                                                                                      | _         | R     | R               | R/W   | R/W             | R/W   |  |

| Bit                                          |                                                | Description                                                                                            |           |       |                 |       |                 |       |  |

| 7-5                                          | Not Used                                       | Not Used                                                                                               |           |       |                 |       |                 |       |  |

| 4                                            | 0: after Pov                                   | TO: Time Out  D: after Power On Reset, LVR Reset, or CLRWDT/SLEEP instruction  1: WDT time out occurs  |           |       |                 |       |                 |       |  |

| 3                                            | 0: after Pov                                   | PD: Power Down 0: after Power On Reset, LVR Reset, or CLRWDT instruction 1: after SLEEP instruction    |           |       |                 |       |                 |       |  |

| 2                                            | 0: the resul                                   | Z: Zero Flag 0: the result of a logic operation is not zero 1: the result of a logic operation is zero |           |       |                 |       |                 |       |  |

|                                              | DC: Decimal Carry Flag or Decimal /Borrow Flag |                                                                                                        |           |       |                 |       |                 |       |  |

|                                              |                                                | ADD in                                                                                                 | struction |       | SUB instruction |       |                 |       |  |

| 1 1: a carry from the low occurs 0: no carry |                                                | e low nibble bits of the result 0: a borrow from the low nibble bits of the recovers                   |           |       |                 |       | s of the result |       |  |

|                                              |                                                | lag or /Borr                                                                                           | ow Flag   |       |                 |       |                 |       |  |

| 0                                            |                                                |                                                                                                        | struction |       | SUB instruction |       |                 |       |  |

| U                                            | -                                              | occurs from                                                                                            | the MSB   |       | 1: no borrow    |       |                 |       |  |

|                                              | 0: no carry 0: a borrow occurs from the MSB    |                                                                                                        |           |       |                 |       |                 |       |  |

DS-TM57ME20\_E 14 Rev 2.0, 2013/09/03

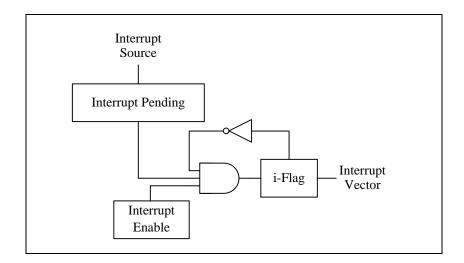

## 1.6 Interrupt

The TM57ME20 has 1 level, 1 vector and 8 interrupt sources. Each interrupt source has its own enable control bit. An interrupt event will set its individual pending flag; no matter its interrupt enable control bit is 0 or 1. Because TM57ME20 has only 1 vector, there is not an interrupt priority register. The interrupt priority is determined by F/W.

If the corresponding interrupt enable bit has been set (F-Plane 08h), it would trigger CPU to service the interrupt. CPU accepts interrupt in the end of current executed instruction cycle. In the mean while, A "CALL 001" instruction is inserted to CPU, and i-flag is set to prevent recursive interrupt nesting.

The i-flag is cleared in the instruction after the "RETI" instruction. That is, at least one instruction in main program is executed before service the pending interrupt. The interrupt event is level triggered. F/W must clear the interrupt event register while serving the interrupt routine.

The STATUS and W register can be automatically stored into the internal memory when interrupt and be restored when exit from interrupt. This functionality is optional and can be enabled or disabled via HWAUTO which in R-Plane 0BH Bit7.

DS-TM57ME20\_E 15 Rev 2.0, 2013/09/03

## 2. Chip Operation Mode

#### 2.1 Reset

The TM57ME20 can be RESET in four ways.

- Power On Reset

- Low Voltage Reset (LVR)

- External Pin Reset (PA7)

- Watchdog Reset (WDT)

After Power On Reset, all system and peripheral control registers are then set to their default hardware reset values. The clock source, LVR level and chip operation mode are selected by the SYSCFG register value. The Low Voltage Reset features static reset when supply voltage is below a threshold level. There are two threshold levels can be selected. The LVR's operation mode is defined by the SYSCFG register.

There are two voltage selections for the LVR threshold level, one is higher level which is suitable for application with  $V_{CC}$  is more than 3.3V, while another one is suitable for application with  $V_{CC}$  is less than 3.3V. See the following LVR Selection Table; user must also consider the lowest operating voltage of operating frequency.

#### LVR Selection Table:

| LVR Threshold Level | Consider the operating voltage to choose LVR                  |  |  |  |

|---------------------|---------------------------------------------------------------|--|--|--|

| LVR3.2              | $5.5V > V_{CC} > 3.3V$                                        |  |  |  |

| LVR2.2              | V <sub>CC</sub> is wide voltage range, more or less than 3.3V |  |  |  |

The External Pin Reset and Watchdog Reset can be disabled or enabled by the SYSCFG register. These two resets also set all the control registers to their default reset values. The TO/PD flag is not affected by these resets.

DS-TM57ME20\_E 16 Rev 2.0, 2013/09/03

## 2.2 System Configuration Register (SYSCFG)

The System Configuration Register (SYSCFG) is located at MTP INFO area. The SYSCFG determines the option for initial condition of MCU. It is written by MTP Writer only. User can select clock source, LVR threshold voltage and chip operation mode by SYSCFG register. The 13th bit of SYSCFG is code protection selection bit. If this bit is 1, the data in MTP will be protected, when user reads MTP.

| Bit           | 13~0                                         |                                                   |  |  |  |  |

|---------------|----------------------------------------------|---------------------------------------------------|--|--|--|--|

| Default Value | 00_0000_0000_0000                            |                                                   |  |  |  |  |

| Bit           | Description                                  |                                                   |  |  |  |  |

| 13            | PROTECT: Code Protection Selection           |                                                   |  |  |  |  |

|               | 1                                            | Code Protection                                   |  |  |  |  |

|               | 0                                            | No Protect                                        |  |  |  |  |

| 12            | ICVPD: I                                     | VC*/LVR Mode Selection                            |  |  |  |  |

|               | 1                                            | IVC/LVR Auto OFF in Idle/Stop Mode                |  |  |  |  |

|               | 0                                            | IVC/LVR Always ON                                 |  |  |  |  |

|               | LVR: I                                       | VR Threshold                                      |  |  |  |  |

| 11            | 1                                            | LVR threshold is 2.2V, always enable              |  |  |  |  |

|               | 0                                            | LVR threshold is 3.2V, always enable              |  |  |  |  |

|               | LVRE: I                                      | VR Enable                                         |  |  |  |  |

| 10            | 1                                            | Enable LVR                                        |  |  |  |  |

|               | 0                                            | Disable LVR                                       |  |  |  |  |

| 9-8           | CLKS: Clock Source Selection                 |                                                   |  |  |  |  |

|               | 11                                           | Fast Crystal (1 MHz~12 MHz)                       |  |  |  |  |

|               | 10                                           | Slow Crystal (32 KHz~1 MHz)                       |  |  |  |  |

|               | 01                                           | Fast Internal RC (4 MHz)                          |  |  |  |  |

|               | 00                                           | External RC                                       |  |  |  |  |

| 7             | XRESETE: External Pin Reset Enable           |                                                   |  |  |  |  |

|               | 1                                            | Enable External Pin Reset                         |  |  |  |  |

|               | 0                                            | Disable External Pin Reset                        |  |  |  |  |

| 6             | WDTE: V                                      | VDT Reset Enable                                  |  |  |  |  |

|               | 1                                            | Enable WDT Reset, Disable WKT Timer               |  |  |  |  |

|               | 0                                            | Disable WDT Reset, Enable WKT Timer               |  |  |  |  |

| 5             | 3V/5V Selection: Operating Voltage Selection |                                                   |  |  |  |  |

|               | 1                                            | V <sub>CC</sub> maximum operating voltage at 3.3V |  |  |  |  |

|               | 0                                            | V <sub>CC</sub> maximum operating voltage at 5.5V |  |  |  |  |

| 4-0           | FIRCF: F                                     | ast Internal RC Frequency Adjustment Control      |  |  |  |  |

st IVC is the chip built-in 3.3V regulator for internal circuit.

DS-TM57ME20\_E 17 Rev 2.0, 2013/09/03

## 2.3 MTP Program ROM

The MTP ROM of this device is 2K words, with an extra INFO area to store the SYSCFG. The MTP ROM can be written multi-times and can be read as long as the PROTECT bit of SYSCFG is not set. The SYSCFG can be read no matter PROTECT is set or cleared, but can be written only when PROTECT is not set or MTP ROM is erased. That is, un-protect the PROTECT bit needs the erased MTP ROM.

|     | Program Memory   |  |  |  |  |

|-----|------------------|--|--|--|--|

| 000 | Reset Vector     |  |  |  |  |

| 001 | Interrupt Vector |  |  |  |  |

| 002 |                  |  |  |  |  |

|     |                  |  |  |  |  |

|     |                  |  |  |  |  |

|     |                  |  |  |  |  |

|     | User             |  |  |  |  |

|     | Code             |  |  |  |  |

|     |                  |  |  |  |  |

|     |                  |  |  |  |  |

|     |                  |  |  |  |  |

| 7FF |                  |  |  |  |  |

|    | Config Memory |

|----|---------------|

| 00 | SYSCFG        |

| 01 |               |

|    | Manufacturer  |

|    | Reserved Area |

| 0F |               |

#### 2.4 Power-Down Mode

The Power-down mode is activated by SLEEP instruction. During the Power-down mode, the system clock and peripherals stop to minimize power consumption, while the WDT/WKT Timer is working or not depends on F/W setting. The Power-down mode can be terminated by reset, or enabled interrupts (external pins and WKT interrupt) or PB0-7 pins low level wakeup. In the Power-down mode, user can enable or disable IVC according to the standby current requirement. Enabled IVC can provide the chip internal circuit more stable 3.3V power.

DS-TM57ME20\_E 18 Rev 2.0, 2013/09/03

## 2.5 Dual System Clock

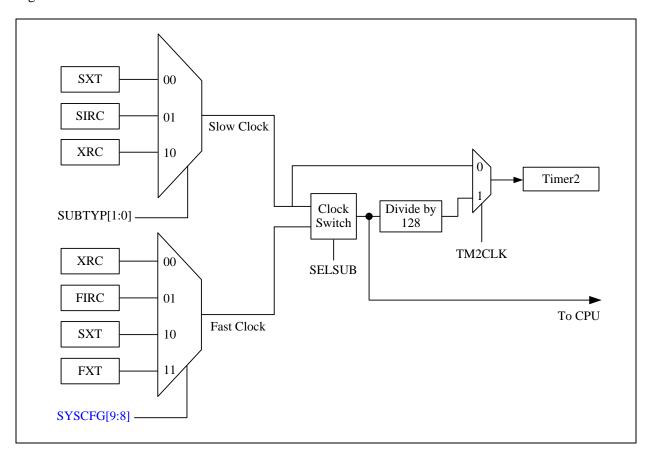

TM57ME20 is designed with dual-clock system. There are five kinds of clock source, FXT (Fast Crystal) Clock, SXT (Slow Crystal) Clock, XRC (External RC) Clock, SIRC (Slow Internal RC) Clock and FIRC (Fast Internal RC). Each clock source can be applied to CPU kernel as system clock. When in idle mode, only slow clock can be configured to keep oscillating to provide clock source to Timer2. Refer to the Figure as below.

DS-TM57ME20\_E 19 Rev 2.0, 2013/09/03

#### **Fast Mode:**

After power on or reset, TM57ME20 enters fast mode. In fast mode, TM57ME20 can select FXT, XRC or FIRC as its CPU clock by SYSCFG bit9 and bit8 setting. Besides, firmware can also enable or disable the slow clock for the Timer2 system operating. In this mode, the program is executed using fast clock as CPU clock. The Timer0, PWM0, PWM1 blocks are also driven by fast clock. Timer2 can also be driven by fast clock by setting TM2CLK to "1".

#### **Slow Mode:**

In slow mode, TM57ME20 can select SXT, XRC or SIRC as its CPU clock by R-Plane control register (SUBTYP). In this mode, the fast clock is stopped and slow clock is enabled for power saving. All peripheral blocks clock sources are slow clock in the slow mode.

#### **Idle Mode:**

If slow clock is enabled and TM2CLK=0 before executing the SLEEP instruction, the TM57ME20 enters the "Idle Mode". In this mode, the slow clock will continue running to provide clock to Timer2 block. CPU stop fetching code and all blocks are stop except Timer2 related circuits.

#### **Stop Mode:**

If slow clock is disabled before executing the SLEEP instruction, every block is turned off and the TM57ME20 enters the "Stop Mode". Stop mode is similar to idle mode. The difference is all clock oscillators either fast or slow is powered-down and no clock is generated.

DS-TM57ME20\_E 20 Rev 2.0, 2013/09/03

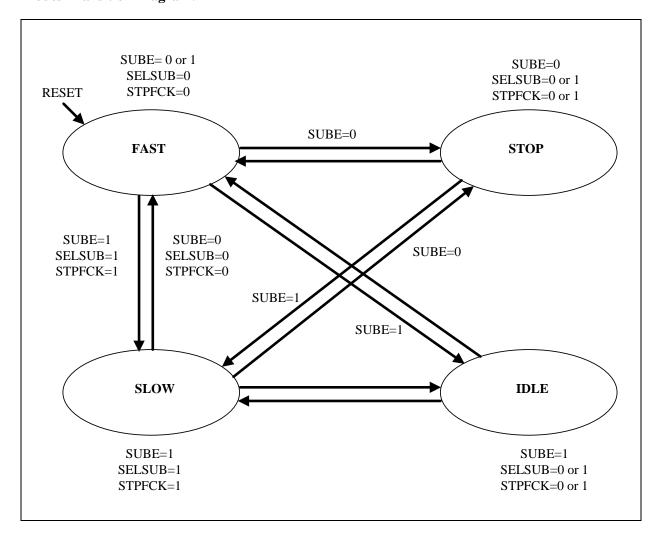

## 2.6 Dual System Clock Modes Transition

TM57ME20 is operated in one of four modes: Fast Mode, Slow Mode, Idle Mode, and Stop Mode.

### **Modes Transition Diagram:**

#### **Fast Mode transits to Slow Mode:**

Fast mode can be chosen by SYSCFG [9:8] when equals to 11 (Fast Crystal), 00 (External RC), or 01 (Fast Internal RC). The following steps are suggested to be executed by order when fast mode transits to slow mode:

- (1) Enable slow clock (SUBE=1)

- (2) Switch to slow clock (SELSUB=1)

- (3) Stop fast clock (STPFCK=1)

DS-TM57ME20\_E 21 Rev 2.0, 2013/09/03

#### **Slow Mode transits to Fast Mode:**

Slow mode can be enabled by SUBE bit and SELSUB bit in CLKCTRL register. The following steps are suggested to be executed by order when slow mode transits to fast mode:

- (1) Enable fast clock (STPFCK=0)

- (2) Switch to fast clock (SELSUB=0)

- (3) Stop slow clock (SUBE=0)

Note: Stop slow clock (SUBE=0) is optional. Slow clock can keep oscillating to provide Timer2 counter block in fast mode.

## **Idle Mode Setting:**

The idle mode can be configured by following setting in order:

- (1) Enable slow clock (SUBE=1)

- (2) Switch Timer2 clock source to slow clock (TM2CLK=0)

- (3) Execute SLEEP instruction

Idle mode can be woken up by XINT, PBWAKP, Wake-up Timer, and Timer2 interrupt.

### **Stop Mode Setting:**

The stop mode can be configured by following setting in order:

- (1) Stop slow clock (SUBE=0)

- (2) Execute SLEEP instruction

Stop mode can be woken up by XINT, PBWAKP, and Wake-up Timer.

#### IO setting note in dual clock mode:

Note: In slow clock modes, PA3 and PA4 must be set as input pull-up mode when slow clock selects SXT or XRC mode. PA3 and PA4 IO setting list is as shown bellow.

|   | Fast Clock | Slow Clock | PAD3 | PAE3 | nPAPU3 | PAD4 | PAE4 | nPAPU4 |

|---|------------|------------|------|------|--------|------|------|--------|

| 1 | FIRC       | SIRC       | *    | *    | *      | *    | *    | *      |

| 2 | FIRC       | SXT        | 1    | 0    | 0      | 1    | 0    | 0      |

| 3 | FIRC       | XRC        | *    | *    | *      | 1    | 0    | 0      |

| 4 | FXT        | SIRC       | *    | *    | *      | *    | *    | *      |

| 5 | XRC        | SIRC       | *    | *    | *      | *    | *    | *      |

## 3. Peripheral Functional Block

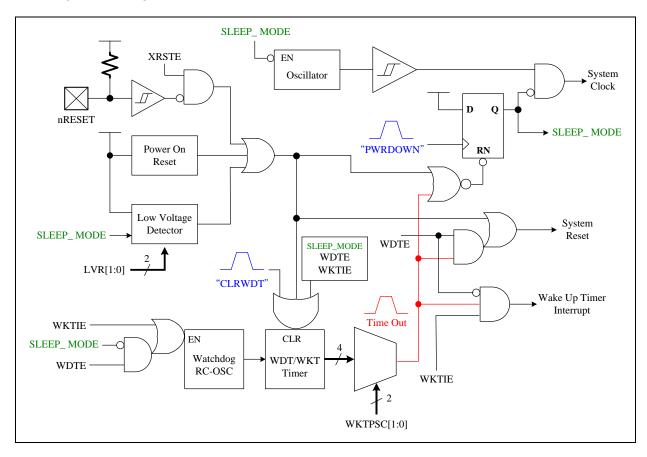

### 3.1 Watchdog (WDT) / Wakeup (WKT) Timer

The WDT and WKT share the same internal RC Timer. The overflow period of WDT/WKT can be selected from 14 ms to 121 ms. The WDT/WKT is cleared by the CLRWDT instruction. If the Watchdog Reset is enabled (WDTE=1), the WDT generates the chip reset signal, otherwise, the WKT only generates overflow time out interrupt. The WDT/WKT works in both normal mode and sleep mode. During sleep mode, user can further choose to enable or disable the WDT/WKT by "WKTIE". If WKTIE=0 in sleep mode (no matter WDTE is 1 or 0), the internal RC Timer stops for power saving. In other words, user keeps the WDT/WKT alive in sleep mode by setting WKTIE=1. If the WDTE=1 and WKTIE=0, WDT/WKT timer will be cleared and stopped to power saving in sleep mode. If the WDTE=1 and WKTIE=1, WDT/WKT timer keeps counting in sleep/normal mode. Refer to the following table and figure.

DS-TM57ME20\_E 23 Rev 2.0, 2013/09/03

If the user program needs the MCU totally shuts down for power conservation in sleep mode, the following setting of control bits should be followed.

| Mode         | WDTE | WKTIE | Watchdog RC Oscillator |  |

|--------------|------|-------|------------------------|--|

|              | 0    | 0     | Stop                   |  |

| Normal Mode  | 0    | 1     |                        |  |

| Normai Wiode | 1    | 0     | Run                    |  |

|              | 1    | 1     |                        |  |

|              | 0    | 0     | Stop                   |  |

| Slaan Mada   | 0    | 1     | Run                    |  |

| Sleep Mode   | 1    | 0     | Stop                   |  |

|              | 1    | 1     | Run                    |  |

DS-TM57ME20\_E 24 Rev 2.0, 2013/09/03

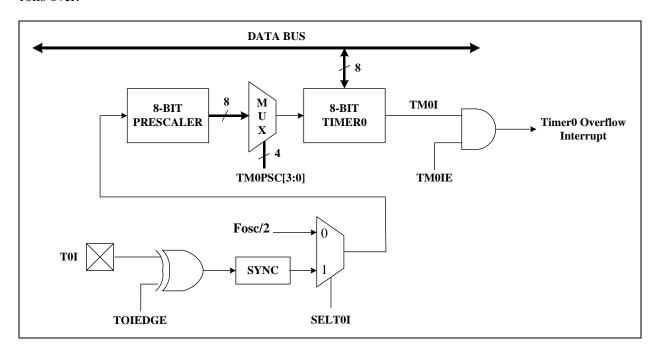

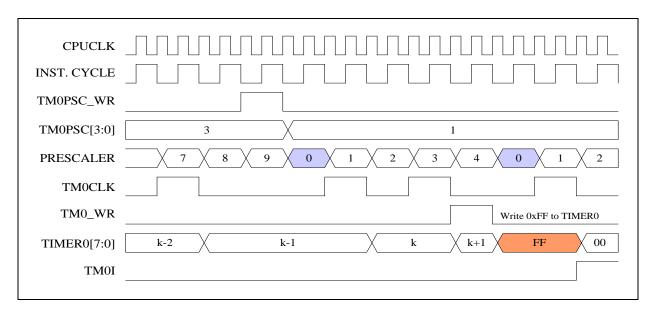

## 3.2 Timer0: 8-bit Timer/Counter with Pre-scale (PSC)

The Timer0 is an 8-bit wide register of F-Plane. It can be read or written as any other register of F-Plane. Besides, Timer0 increases itself periodically and automatically rolls over based on the pre-scaled clock source, which can be the instruction cycle or T0I input. The Timer0 increase rate is determined by "Timer0 Pre-Scale" (TM0PSC) register in R-Plane. The Timer0 can generate interrupt (TM0I) when it rolls over.

DS-TM57ME20\_E 25 Rev 2.0, 2013/09/03

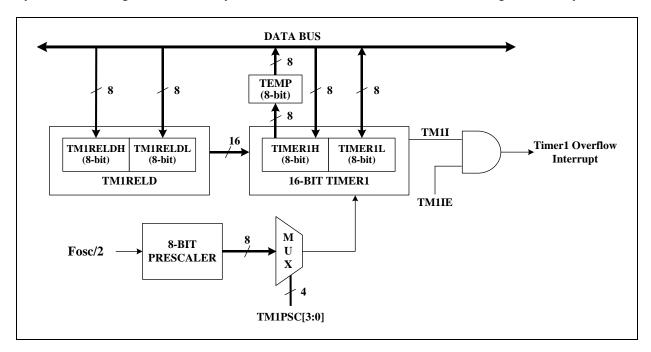

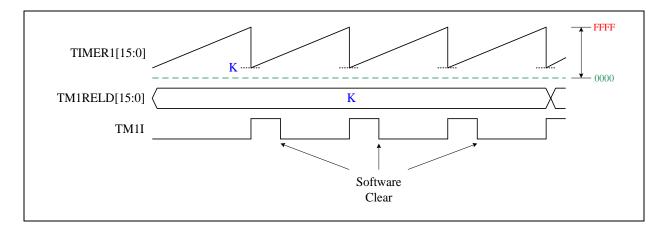

#### 3.3 Timer1: 16-bit Timer with Pre-scale (PSC)

The Timer1 is a 16-bit wide register of F-Plane. It can be read or written as any other register of F-Plane. Besides, Timer1 increases itself periodically and automatically reloads a new "offset value" (TM1RELD) while it rolls over based on the pre-scaled instruction clock. The Timer1 increase rate is determined by "Timer1 Pre-Scale" (TM1PSC) register in R-Plane. The Timer1 can generate interrupt (TM1I) when it rolls over.

The Timer1 and TM1RELD are 16-bit registers that can be accessed via 8-bit data bus. The 16-bit register must be byte accessed using two read or write operations. There is a single 8-bit register for temporary storing of the high byte of Timer1 read. When the low byte of Timer1 register is read by the CPU, the high byte of Timer1 register is copied into the temporary register in the same clock cycle as the low byte is read. For Timer1 read, the low byte must be read before the high byte. Whatever high or low byte of a 16-bit register is written by the CPU, the value will be written into the register directly.

DS-TM57ME20\_E 26 Rev 2.0, 2013/09/03

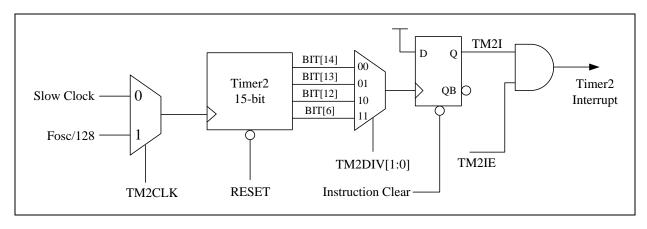

## 3.4 Timer2: 15-bit Timer with Pre-scale (PSC)

The Timer2 is a 15-bit counter and the clock sources are from either Fosc/128 or slow clock. It is used to generate time base interrupt and Timer2 counter block clock. The Timer2 content cannot be read by instructions. It generates interrupt flag (TM2I) with the clock divided by 32768, 16384, 8192, and 128, depends on TM2DIV register bits. Figure shows the block diagram of Timer2.

DS-TM57ME20\_E 27 Rev 2.0, 2013/09/03

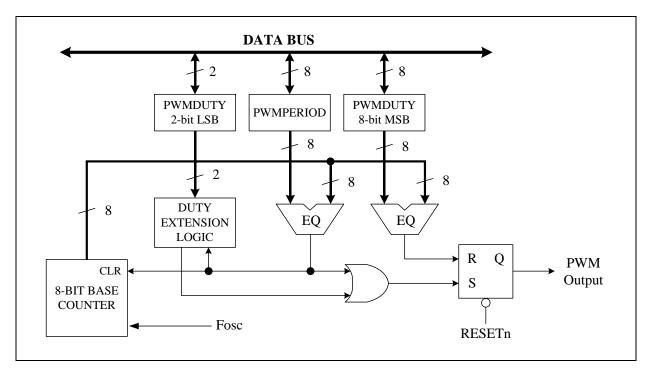

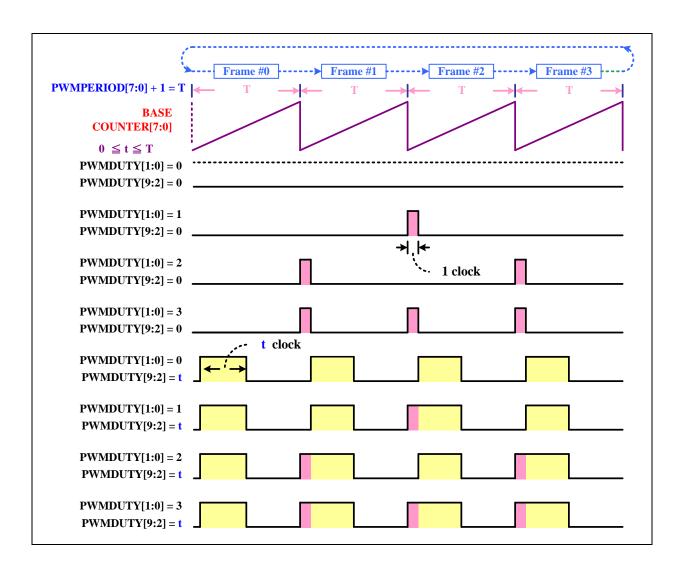

#### 3.5 8+2 bits PWM

PWM0 and PWM1 have the same structure. The PWM supports period time and duty time adjustable. It also can generate fix frequency waveform with 1024 duty resolution based on system clock. A spread LSB technique allows PWM to run its frequency at "System Clock divided by 256" instead of "System Clock divided by 1024", which means the PWM is 4 times faster than normal. The advantage of higher PWM frequency is that the post RC filter can transform the PWM signal to more stable DC voltage level. The PWM output signal reset to low level whenever the 8-bit base counter matches the 8-bit MSB of PWM duty register (PWMDUTY). When the base counter rolls over, the 2-bit LSB of PWM duty register decides whether to set the PWM output signal high immediately or set it high after one clock cycle delay.

DS-TM57ME20\_E 28 Rev 2.0, 2013/09/03

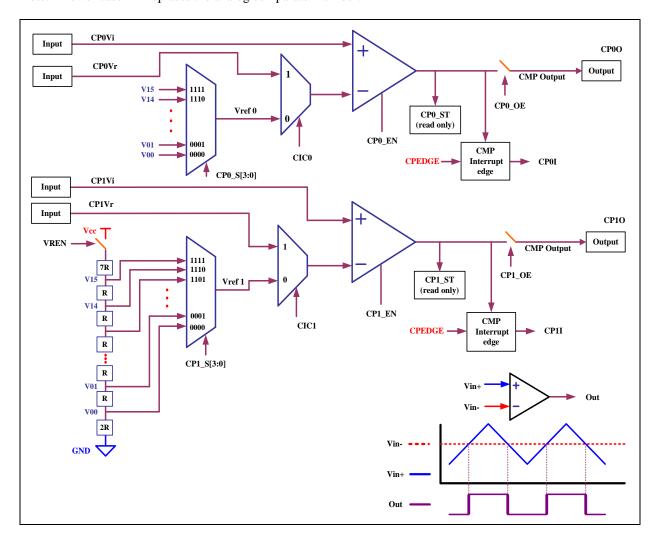

#### 3.6 Analog Comparator

TM57ME20 has two analog comparators CMP0 and CMP1. They can be enabled by CPx\_EN which is in F-Plane 12H Bit4~5. The analog comparators compare the input values on the positive pin CPxVi and negative pin CPxVr. When the voltage on positive pin is higher than the voltage on the negative pin, the analog comparators output CPxO is set. The output status CPx\_ST can be read from F-Plane 14H Bit0~1, or output to pin by setting CPx\_OE which is in F-Plane 12H Bit2~3. The analog comparator can generate interrupt (CPxI) when the output status changes. The user can select interrupt triggering on comparator output rise or fall. The analog comparators support internal reference voltage. To use internal reference voltage, enable VREN and clear CICx (default). The internal reference voltage provides the range of output voltage with 16 distinct levels. The range can be selected by CPx\_S. A block diagram of the analog comparators is shown in below.

Note: A lower case "x" replaces the analog comparator number.

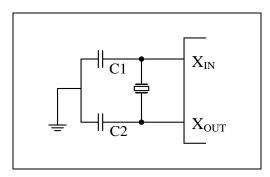

## 3.7 System Clock Oscillator

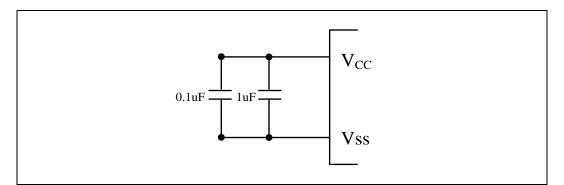

System clock can be operated in four different oscillation modes, which is selected by setting the CLKS in the SYSCFG register. In Slow/Fast Crystal mode, a crystal or ceramic resonator is connected to the Xin and Xout pins to establish oscillation. In external RC mode, the external resistor and capacitor determine the oscillation frequency. In the fast internal RC mode, the on-chip oscillator generates 4 MHz system clock. In this mode, PCB Layout may have strong effect on the stability of Internal Clock Oscillator. Since power noise degrades the performance of Internal Clock Oscillator, placing power supply bypass capacitors 1 uF and 0.1 uF very close to  $V_{\rm CC}/V_{\rm SS}$  pins improves the stability of clock and the overall system.

External Oscillator Circuit (Crystal or Ceramic)

External RC Oscillator

Internal RC Mode

DS-TM57ME20\_E 31 Rev 2.0, 2013/09/03

#### 4. I/O Port

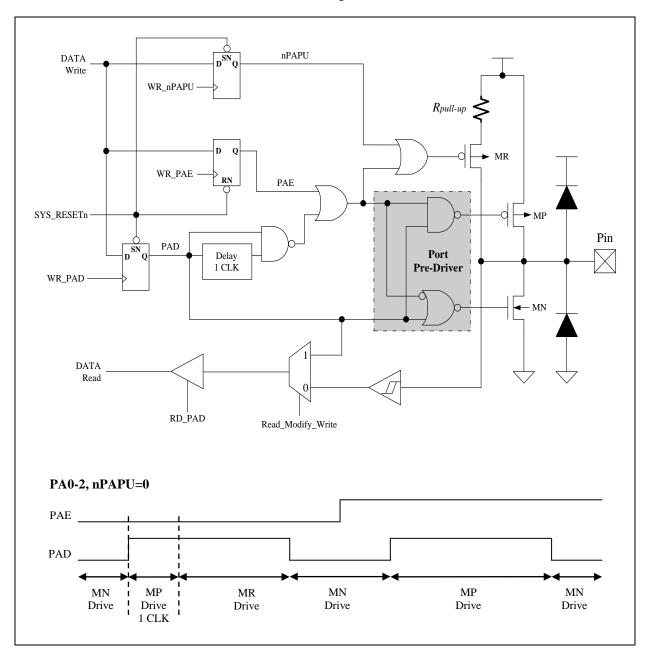

#### 4.1 PA0-2

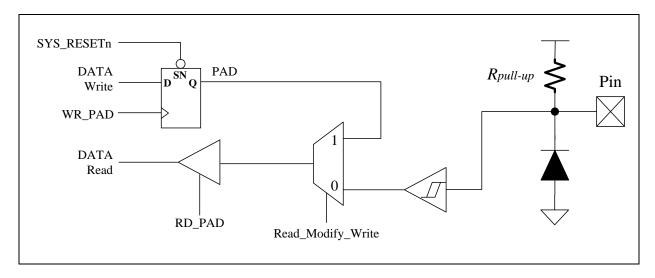

These pins can be used as Schmitt-trigger input, CMOS push-pull output or "pseudo-open-drain" output. The pull-up resistor is assignable to each pin by S/W setting. To use the pin in Schmitt-trigger input mode, S/W needs to set the PAE=0 and PAD=1. To use the pin in pseudo-open-drain mode, S/W sets the PAE=0. The benefit of pseudo-open-drain structure is that the output rise time can be much faster than pure open-drain structure. S/W sets PAE=1 to use the pin in CMOS push-pull output mode. Reading the pin data (PAD) has different meaning. In "Read-Modify-Write" instruction, CPU actually reads the output data register. In the other instructions, CPU reads the pin state. The so-called "Read-Modify-Write" instruction includes BSF, BCF and all instructions using F-Plane as destination.

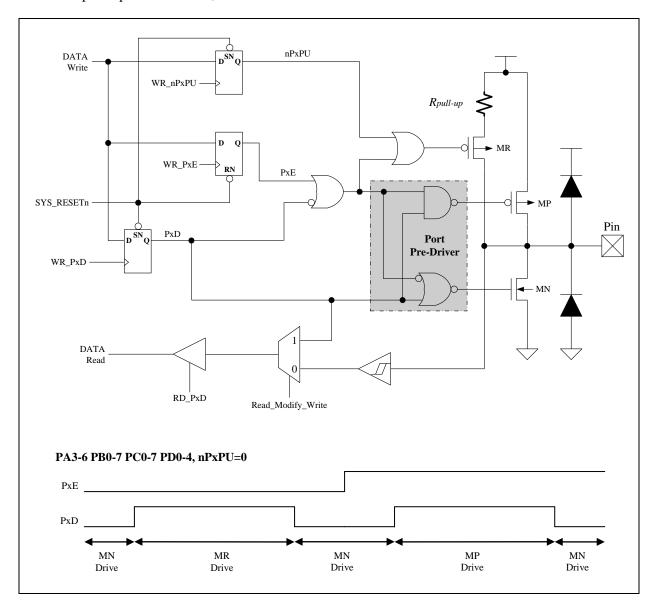

## 4.2 PA3-6, PB0-7, PC0-7, PD0-4

These pins are almost the same as PA0-2, except they do not support pseudo-open-drain mode. They can be used in pure open-drain mode, instead.

DS-TM57ME20\_E 33 Rev 2.0, 2013/09/03

## 4.3 PA7

PA7 can be only used in Schmitt-trigger input mode. The pull-up resistor is always connected to this pin.

DS-TM57ME20\_E 34 Rev 2.0, 2013/09/03

## **MEMORY MAP**

## F-Plane

| Name    | Address | R/W | Rst | Description                                                              |  |

|---------|---------|-----|-----|--------------------------------------------------------------------------|--|

| INDF    | 00.7~0  | R/W | _   | Not a physical register, addressing INDF actually point to the register  |  |

|         |         |     |     | whose address is contained in the FSR register                           |  |

|         | 01.7~0  | R/W | 0   | Timer0 content                                                           |  |

|         | 02.7~0  | R/W | 0   | Programming Counter [7~0]                                                |  |

|         | 03.4    | R   | 0   | WDT time out flag                                                        |  |

|         | 03.3    | R   | 0   | Sleep mode flag                                                          |  |

| -       | 03.2    | R/W | 0   | Zero flag                                                                |  |

|         | 03.1    | R/W | 0   | Decimal Carry flag                                                       |  |

| CFLAG   | 03.0    | R/W | 0   | Carry flag                                                               |  |

| GBIT1   | 04.7    | R/W | 0   | General purpose bit                                                      |  |

| FSR     | 04.6~0  | R/W | -   | File Select Register, indirect address mode pointer                      |  |

| PAD7    | 05.7    | R   | -   | PA7 pin state                                                            |  |

| PAD     | 05.6~0  | R   | -   | Port A pin or "data register" state                                      |  |

| FAD     | 03.0~0  | W   | 7F  | Port A output data register                                              |  |

| DDD     | 067.0   | R   | -   | Port B pin or "data register" state                                      |  |

| PBD     | 06.7~0  | W   | FF  | Port B output data register                                              |  |

| DCD     | 07.7~0  | R   | -   | Port C pin or "data register" state                                      |  |

| PCD     |         | W   | FF  | Port C output data register                                              |  |

| CP1IE   | 08.7    | R/W | 0   | Comparator1 interrupt enable, 1=enable, 0=disable                        |  |

| CP0IE   | 08.6    | R/W | 0   | Comparator0 interrupt enable, 1=enable, 0=disable                        |  |

| TM1IE   | 08.5    | R/W | 0   | Timer1 interrupt enable, 1=enable, 0=disable                             |  |

| TM0IE   | 08.4    | R/W | 0   | Timer0 interrupt enable, 1=enable, 0=disable                             |  |

| WKTIE   | 08.3    | R/W | 0   | Wakeup Timer interrupt enable, 1=enable, 0=disable                       |  |

| TM2IE   | 08.2    | R/W | 0   | Timer2 Interrupt enable, 1=enable, 0=disable                             |  |

| XINT1E  | 08.1    | R/W | 0   | INT1 pin interrupt enable, 1=enable, 0=disable                           |  |

| XINT0E  | 08.0    | R/W | 0   | INTO pin interrupt enable, 1=enable, 0=disable                           |  |

| CD1I    | 09.7    | R   | -   | Comparator1 interrupt event pending flag                                 |  |

| CP1I    |         | W   | 0   | write 0: clear this flag; write 1: no action                             |  |

| CDOL    | 00.6    | R   | -   | Comparator0 interrupt event pending flag                                 |  |

| CP0I    | 09.6    | W   | 0   | write 0: clear this flag; write 1: no action                             |  |

| (D) (1) | 09.5    | R   | -   | Timer1 interrupt event pending flag, set by H/W while Timer1 overflows   |  |

| TM1I    |         | W   | 0   | write 0: clear this flag; write 1: no action                             |  |

| TON FOX | 09.4    | R   | -   | Timer0 interrupt event pending flag, set by H/W while Timer0 overflows   |  |

| TM0I    |         | W   | 0   | write 0: clear this flag; write 1: no action                             |  |

| *****   | 09.3    | R   | -   | WKT interrupt event pending flag, set by H/W while WKT time out          |  |

| WKTI    |         | W   | 0   | write 0: clear this flag; write 1: no action                             |  |

| FD 507  | 00.2    | R   | -   | Timer2 interrupt event pending flag, set by H/W while Timer2 overflows   |  |

| TM2I    | 09.2    | W   | 0   | write 0: clear this flag; write 1: no action                             |  |

|         | 09.1    | R   | -   | INT1 interrupt event pending flag, set by H/W at INT1 pin's falling edge |  |

| XINT1   |         | W   | 0   | write 0: clear this flag; write 1: no action                             |  |

| Name                                      | Address                                                        | R/W          | Rst                  | Description                                                                                                               |  |  |

|-------------------------------------------|----------------------------------------------------------------|--------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| XINT0                                     | 09.0                                                           | R            | -                    | INT0 interrupt event pending flag, set by H/W at INT0 pin's f/r edge                                                      |  |  |

|                                           |                                                                | W            | 0                    | write 0: clear this flag; write 1: no action                                                                              |  |  |

| TIMER1                                    | 0a.7~0                                                         | R/W          | 0                    | Timer1 content 8-bit MSB                                                                                                  |  |  |

|                                           | 0b.7~0                                                         | R/W          | 0                    | Timer1 content 8-bit LSB                                                                                                  |  |  |

| PWM0DUTY                                  | 0c.7~0                                                         | R/W          | 0                    | PWM0 duty 8-bit MSB                                                                                                       |  |  |

|                                           | 0d.7~6                                                         | R/W          | 0                    | PWM0 duty 2-bit LSB                                                                                                       |  |  |

| PWM1DUTY                                  | 0e.7~0                                                         | R/W          | 0                    | PWM1 duty 8-bit MSB                                                                                                       |  |  |

|                                           | 0f.7~6                                                         | R/W          | 0                    | PWM1 duty 2-bit LSB                                                                                                       |  |  |

| PWMPERIOD                                 | 10.7~0                                                         | R/W          | FF                   | PWM period                                                                                                                |  |  |

| PDD                                       | 11.4~0                                                         | R            | -                    | Port D pin or "data register" state                                                                                       |  |  |

| 1 00                                      | 11.4~0                                                         | W            | 1F                   | Port D output data register                                                                                               |  |  |

| CPEDGE                                    | 12.7                                                           | R/W          | 0                    | 0: Comparator0/1 falling edge to trigger interrupt event 1: Comparator0/1 rising edge to trigger interrupt event          |  |  |

| VREN                                      | 12.6                                                           | R/W          | 0                    | Internal reference voltage enable, 1: enable, 0: disable                                                                  |  |  |

| CP1_EN                                    | 12.5                                                           | R/W          | 0                    | Comparator1 enable, 1: enable, 0: disable                                                                                 |  |  |

| CP0_EN                                    | 12.4                                                           | R/W          | 0                    | Comparator0 enable, 1: enable, 0: disable                                                                                 |  |  |

| CP1_OE                                    | 12.3                                                           | R/W          | 0                    | Comparator1 output enable, 1: enable, 0: disable                                                                          |  |  |

| CP0_OE                                    | 12.2                                                           | R/W          | 0                    | Comparator0 output enable, 1: enable, 0: disable                                                                          |  |  |

| CIC1                                      | 12.1                                                           | R/W          | 0                    | Comparator1 reference in selection  1: External reference voltage  0: Internal reference voltage                          |  |  |

| CIC0                                      | 12.0                                                           | R/W          | 0                    | Comparator 0 reference in selection  1: External reference voltage  0: Internal reference voltage                         |  |  |

| CP1_S 13.7~4                              |                                                                | R/W          | 0                    | Comparator1 internal reference voltage select 0000: $V_{CC}$ * 2/24 0001: $V_{CC}$ C * 3/24 $\sim$ 1111: $V_{CC}$ * 17/24 |  |  |

| CP0_S                                     | 13.3~0                                                         | R/W          | 0                    | Comparator0 internal reference voltage select 0000: $V_{CC}$ * 2/24 0001: $V_{CC}$ C * 3/24 $\sim$ 1111: $V_{CC}$ * 17/24 |  |  |

| CP1ST                                     | 14.1                                                           | R            |                      | Comparator1 output status                                                                                                 |  |  |

| CPOST 14.0 R - Comparator 0 output status |                                                                | *            |                      |                                                                                                                           |  |  |

| SELSUB                                    |                                                                |              |                      |                                                                                                                           |  |  |

| STPFCK                                    |                                                                |              |                      |                                                                                                                           |  |  |

| SUBE                                      | 15.5                                                           | R/W          |                      |                                                                                                                           |  |  |

| -                                         | - 15.4~3 Reserved                                              |              |                      |                                                                                                                           |  |  |

|                                           | CLRTM2 15.2 R/W 0 Write 1 to clear Timer2, auto cleared by H/W |              | -                    |                                                                                                                           |  |  |

| STOPTM0                                   | TOPTM0 15.1 R/W 0 Stop Timer0 counting                         |              | Stop Timer0 counting |                                                                                                                           |  |  |

| -                                         | 15.0 - Reserved                                                |              |                      |                                                                                                                           |  |  |

| SRAM 20~7F R/W - Internal RAM             |                                                                | Internal RAM |                      |                                                                                                                           |  |  |

## R-Plane

| Name        | Address | R/W   | Rst | Description                                                                                            |

|-------------|---------|-------|-----|--------------------------------------------------------------------------------------------------------|

| T0IEDGE     | 02.5    | W     | 0   | 0: T0I rising edge to increase Timer0/PSC count                                                        |

| TVIEDGE     | 02.0    | . ' ' | 0   | 1: TOI falling edge to increase Timer0/PSC count                                                       |

| SELT0I      | 02.4    | W     | 0   | 0: Timer0/PSC clock source is "Instruction Cycle" 1: Timer0/PSC clock source is T0I pin                |

|             |         |       |     | 0000: Timer0 input clock divided by 1                                                                  |

|             |         |       |     | 0001: Timer0 input clock divided by 2                                                                  |

| TM0PSC      | 02.3~0  | W     | 0   | ~                                                                                                      |

|             |         |       |     | 0111: Timer0 input clock divided by 128                                                                |

| DIVIDE OVIE | 0.2     | ***   |     | 1000: Timer0 input clock divided by 256                                                                |

| PWRDOWN     | 03      | W     | -   | Write this register to enter Power-Down Mode                                                           |

| CLRWDT      | 04      | W     | -   | Write this register to clear WDT/WKT                                                                   |

|             | 05.6~3  | W     | 0   | 0: the pin is open-drain output or Schmitt-trigger input                                               |

| PAE         |         |       |     | 1: the pin is CMOS push-pull output 0: the pin is pseudo-open-drain output or Schmitt-trigger input    |

|             | 05.2~0  | W     | 0   | 1: the pin is CMOS push-pull output                                                                    |

| DDE         | 067.0   | ***   | 0   | 0: the pin is open-drain output or Schmitt-trigger input                                               |

| PBE         | 06.7~0  | W     | 0   | 1: the pin is CMOS push-pull output                                                                    |

| PCE         | 07.7~0  | W     | 0   | 0: the pin is open-drain output or Schmitt-trigger input                                               |

| - 102       | 07.7    | . ' ' | 0   | 1: the pin is CMOS push-pull output                                                                    |

| nPAPU       | 08.6~0  | W     | 7F  | 0: the pin pull up resistor is enabled, except a. the pin's output data register (PAD) is 0            |

|             |         |       |     | b. the pin's CMOS push-pull mode is chosen (PAE=1)                                                     |

|             |         |       |     | c. the pin is working for Crystal or external RC oscillation                                           |

|             |         |       |     | 1: the pin pull up resistor is disabled                                                                |

| nPBPU       | 09.7~0  | W     | FF  | 0: the pin pull up resistor is enabled                                                                 |

|             |         |       |     | 1: the pin pull up resistor is disabled 0: the pin pull up resistor is enabled                         |

| nPCPU       | 0a.7~0  | W     | FF  | 1: the pin pull up resistor is disabled                                                                |

| HWAUTO      | 0b.7    | W     | 0   | Auto store/restore STATUS and W before/after interrupt routine                                         |

| PWM0E       | Oh 6    | W     | 0   | 0: disable PWM0 output to pin                                                                          |

| PWMUE       | 0b.6    | W     | U   | 1: enable PWM0 output to pin                                                                           |

| PWM1E       | 0b.5    | W     | 0   | 0: disable PWM1 output to pin                                                                          |

|             |         |       |     | 1: enable PWM1 output to pin                                                                           |

| INT0EDGE    | 0b.4    | W     | 0   | 0: INT0 pin falling edge to trigger interrupt event 1: INT0 pin rising edge to trigger interrupt event |

|             | 01.0    |       |     | 0: No Instruction Clock output to PA3 pin                                                              |

| CLK2PIN     | 0b.3    | W     | 0   | 1: Instruction Clock output to PA3 pin for external/internal RC mode                                   |

| -           | 0b.2    | -     | -   | Reserved                                                                                               |

| Name    | Address | R/W | Rst | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|---------|---------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| WKTPSC  | 0b.1~0  | w   | 11  | WDT/WKT pre-scale option or SIRC frequency select WDT/WKT pre-scale option 00: WDT/WKT period is 14 ms, @5V; 15 ms, @3V 01: WDT/WKT period is 28 ms, @5V; 30 ms, @3V 10: WDT/WKT period is 57 ms, @5V; 61 ms, @3V 11: WDT/WKT period is 111 ms, @5V; 121 ms, @3V SIRC frequency select 00: SIRC Frequency is 138 KHz, @5V; 119 KHz, @3V 01: SIRC Frequency is 35 KHz, @5V; 30 KHz, @3V 10: SIRC Frequency is 8.5 KHz, @5V; 7.5 KHz, @3V 11: SIRC Frequency is 2.1 KHz, @5V; 1.9 KHz, @3V |  |

| TM1PSC  | 0c.3~0  | W   | 0   | 0000: Timer1 input clock divided by 1 0001: Timer1 input clock divided by 2 0111: Timer1 input clock divided by 128 1000: Timer1 input clock divided by 256                                                                                                                                                                                                                                                                                                                              |  |

| TM1RELD | 0d.7~0  | W   | 0   | Timer1 reloads offset value 8-bit MSB while it rolls over                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| IMIKELD | 0e.7~0  | W   | 0   | Timer1 reloads offset value 8-bit LSB while it rolls over                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PDE     | 10.4~0  | W   | 0   | 0: the pin is open-drain output or Schmitt-trigger input 1: the pin is CMOS push-pull output                                                                                                                                                                                                                                                                                                                                                                                             |  |

| nPDPU   | 11.4~0  | W   | 1F  | 0: the pin pull up resistor is enabled 1: the pin pull up resistor is disabled                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|         | 12.3    | W   | 1   | PC4/CP1vr input type, 0: analog input, 1: digital input                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PIE     | 12.2    | W   | 1   | PC3/CP1vi input type, 0: analog input, 1: digital input                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PIE     | 12.1    | W   | 1   | PC1/CP0vr input type, 0: analog input, 1: digital input                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|         | 12.0    | W   | 1   | PC0/CP0vi input type, 0: analog input, 1: digital input                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| IVCTRL  | 13.1~0  | W   | 0   | Built-in regulator control in stop mode<br>$00: V_{CC} > 4.5V$<br>$01: 4.5V > V_{CC} > 3.6V$<br>$10: 3.6V > V_{CC}$                                                                                                                                                                                                                                                                                                                                                                      |  |

| PBWKUP  | 14.7~0  | W   | 0   | Enable PB7~PB0 pin low level wake up                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| TM2CLK  | 15.4    | W   | 0   | Timer2 clock source 0: slow clock 1: CPUCLK/128                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| TM2DIV  | 15.3~2  | W   | 0   | Timer2 interrupt is Timer2 divide by – 0: 32768, 1: 16384, 2: 8192, 3: 128                                                                                                                                                                                                                                                                                                                                                                                                               |  |