#### I. Overview

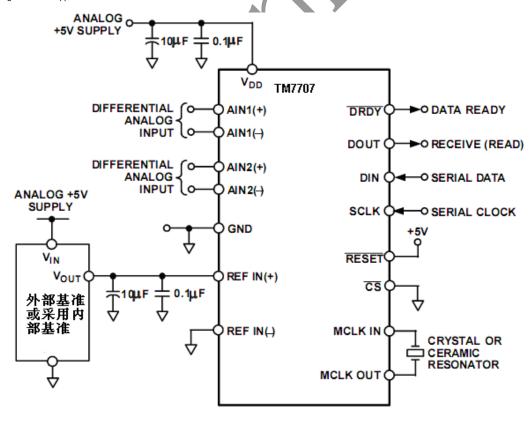

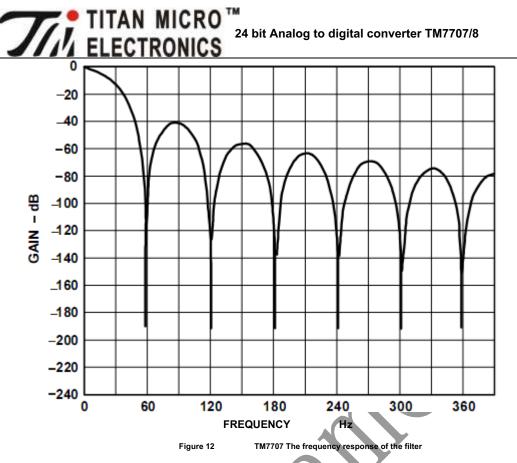

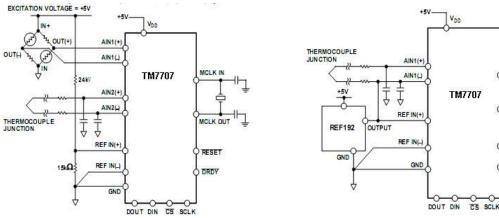

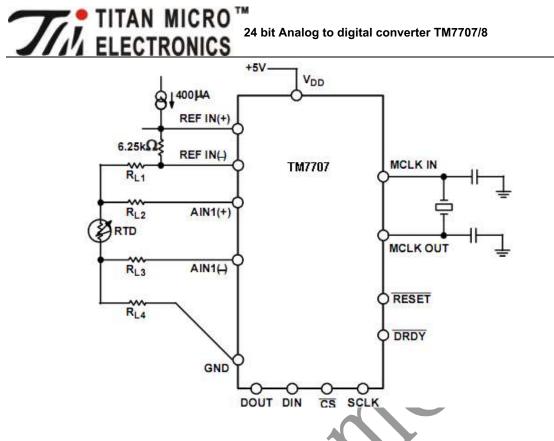

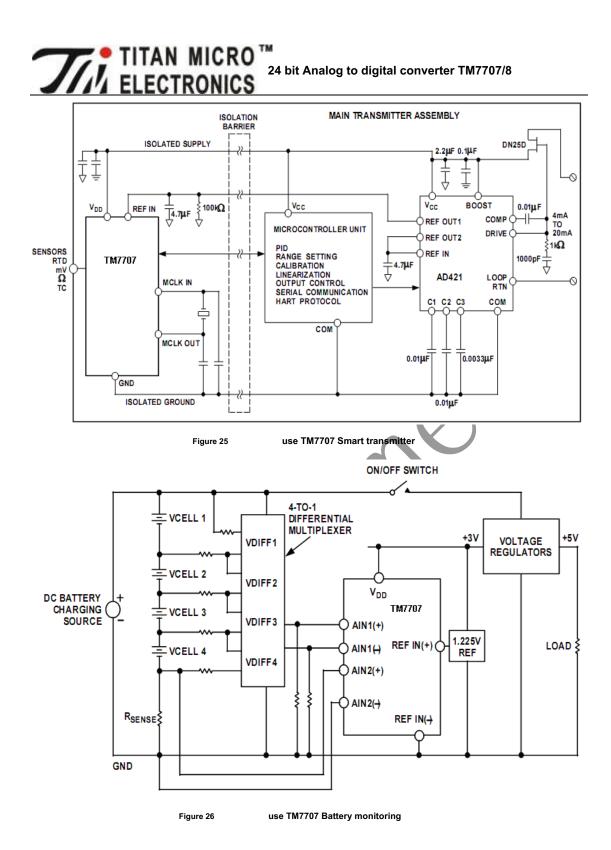

TM7707/8 Is used for low frequency measurement 2/3 The analog front end of the channel. The device can accept low-level input signals directly from the sensor, and then generate a serial digital output. use  $\Sigma$ - $\Delta$  Conversion technology Technique achieved twenty four No missing code performance. The selected input signal is sent to an analog modulator based Dedicated front end with programmable gain. The on-chip digital filter processes the output signal of the modulator. Send via on-chip control The register can adjust the cut-off point of the filter and the output update rate, thereby entering the first notch of the digital filter Line programming.

TM7707/8 Just 2.7~3.3V or 4.75~5.25V Single power supply. TM7707 Is dual channel fully differential Analog input, while TM7708 Yes 3 Channel pseudo differential analog input, both have a differential reference input. When the power supply voltage is 5V, The reference voltage is 2.5V When these two devices can change the input signal range from 0~+20mV To 0~+2.5V The signal is processed. Can also handle ±20mV~±2.5V Bipolar input signal, for TM7707 So AIN (-) The input terminal is the reference point, and TM7708 Yes COMMON

Input terminal. When the power supply voltage is 3V, The reference voltage is 1.225V Can be processed 0~+10mV To 0~+1.225V Unipolar input signal, its bipolar input signal range is  $\pm 10mV$  To  $\pm 1.225V$ . therefore, TM7707/8 can be realised 2/3 The conditioning and conversion of all signals in the channel system.

TM7707/7708 Is used in intelligent systems, microcontroller systems and based on DSP The ideal product of the system. The serial interface can be configured as a three-wire interface. The selection of gain value, signal polarity and update rate can be serial The input port is configured by software. The device also includes self-calibration and system calibration options to eliminate the device itself or The gain and offset error of the system.

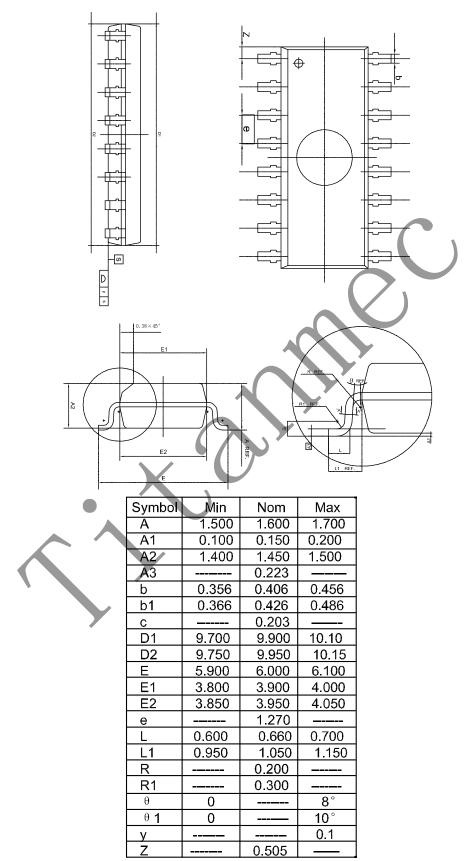

CMOS The structure ensures that the device has extremely low power consumption, and the power-down mode reduces the power consumption during (Typical value). TM7707/8 use 16 foot SOPL Package.

## 2. Features

- TM7707 : 2 Fully differential input channels ADC

- TM7708 : 3 Pseudo-differential input channels ADC twenty four No missing code

0.003% Non-linear

- Programmable gain front end Gain: 1 ~ 128

- Three-wire serial interface

- Ability to buffer analog input

- 2.7 ~ 3.3V or 4.75 ~ 5.25V Operating Voltage

- 3V At voltage, the maximum power consumption is 1mW

- The maximum waiting current is 8µA

- 16 foot SOP16L Package

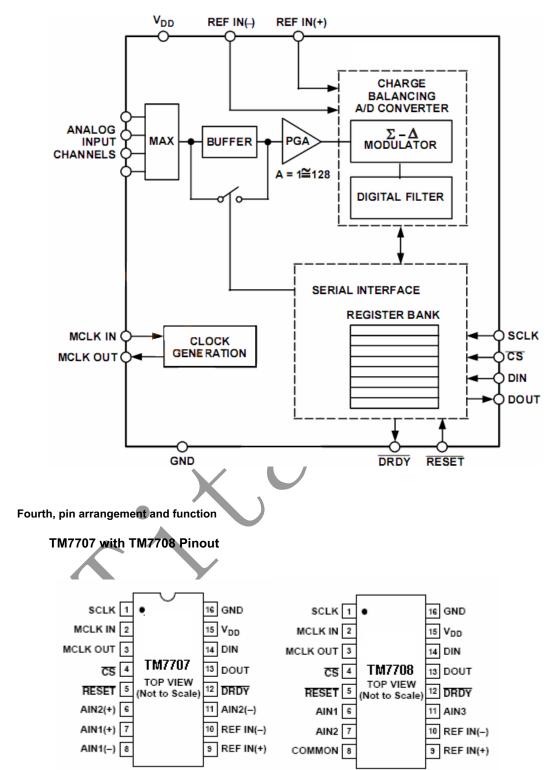

Three, functional block diagram

TITAN MICRO<sup>™</sup> ELECTRONICS

## Five, pin function

| Numberi | ng name Weigh            | Work can                                                                                                     |

|---------|--------------------------|--------------------------------------------------------------------------------------------------------------|

|         |                          | Serial clock, Schmitt logic input. Add an external serial clock to this                                      |

|         |                          | Enter the port to access TM7707/TM7708 Serial data. The serial clock                                         |

| 1       | SCLK                     | It can be a continuous clock that transmits all data in continuous bursts. Conversely, it also               |

|         |                          | It can be a non-continuous clock, and the information is sent to                                             |

|         |                          | TM7707/TM7708                                                                                                |

|         |                          | Provide the master clock signal for the converter. Can be in the form of crystal/resonator or external clock |

| 2       | MCLK IN                  | provide. The crystal/resonator can be connected to MCLK IN with MCLK OUT Between two pins. In                |

| 2       |                          | addition, MCLK IN Also available CMOS Compatible clock driver,                                               |

|         |                          | and MCLK OUT Not connected. The range of clock frequency is 500kHz~5MHz                                      |

|         |                          | When the main clock is a crystal/resonator, the crystal/resonator is connected to MCLK IN with               |

|         |                          | MCLK OUT between. If in MCLK IN An external clock is connected to the pin,                                   |

|         |                          | MCLK OUT An inverted clock signal will be provided. This clock can be used for external                      |

| 3       | MCLK OUT                 | The circuit provides a clock source and can drive one CMOS load. If the user                                 |

|         |                          | No need, MCLK OUT Can be passed in the clock register CLK DIS Bit off. In this way, the device will not      |

|         |                          | be MCLK OUT Drive capacitive load on the pin and consume                                                     |

|         |                          | Unnecessary power                                                                                            |

|         |                          | Chip select, active low logic input, select TM7707/TM7708 . Put                                              |

|         |                          | The pin is connected to low level, TM7707/8 Can operate in three-wire interface mode (in                     |

| 4       | CS                       | Unnecessary power<br>Chip select, active low logic input, select TM7707/TM7708 . Put                         |

|         |                          |                                                                                                              |

|         |                          | —                                                                                                            |

|         | RESET                    | Reset input. The low-level input is effective to combine the control logic, interface logic,                 |

| 5       |                          | Calibration coefficients, digital filters and analog modulators are reset to the power-on state              |

|         | $\wedge \wedge$          | for TM7707, Differential analog input channel 2 The positive input terminal. for TM7708,                     |

| 6       | AIN2(+)[AIN1]            | Analog input channel 1 Input                                                                                 |

|         |                          | for TM7707, Differential analog input channel 1 The positive input terminal. for TM7708,                     |

| 7       | AIN1(+)[AIN2]            | Analog input channel 2 Input                                                                                 |

|         | 7                        | for TM7707 , Differential analog input channel 1 Negative input terminal; for TM7708 ,                       |

| 8       | AIN1(-)[COMMON] COMMON I | nput terminal, analog channel 1 , 2 , 3 The input is based on this input                                     |

|         |                          | quasi-                                                                                                       |

|         |                          | Reference input. TM7707/TM7708 The positive input terminal of the differential reference input. base         |

| 9       | REF IN (+)               | Quasi-input is differential and stipulates REF IN (+) Must be greater than REF IN (-).                       |

|         | . ,                      | REF IN (+) Can take V $_{10}$ with GND Any value between the reference input. TM7707/TM7708 The negative     |

|         |                          | input terminal of the differential reference input. REF                                                      |

| 10      | REF IN (-)               | IN (-) can take V DD with GND Any value between and satisfy REF IN (+)                                       |

|         |                          | more than the REF IN (-)                                                                                     |

|         |                          | for TM7707, Differential analog input channel 2 The negative input terminal. for TM7708,                     |

| 11      | AIN2 (-)[ AIN3]          | Analog input channel 3 Input                                                                                 |

| 12      |                          |                                                                                                              |

| 12      |                          | Logic output. A logic low level on this output indicates that TM7707 with                                    |

| 7  | TITAN MICRO <sup>™</sup><br>24 bit Analog to digital converter TM7707/8<br>ELECTRONICS                         |                                                                                                                      |  |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|    |                                                                                                                | TM7708 Get the new output word in the data register. Complete to a complete loss                                     |  |  |  |  |

|    |                                                                                                                | After reading the word, DRDY The pin immediately returns to high level. If you lose twice                            |  |  |  |  |

|    |                                                                                                                | No data reading occurs between updates, DRDY Will be before the next output update                                   |  |  |  |  |

|    | DRDY                                                                                                           | 500 X t CLKIN The time returns to high level. when DRDY When in the high level, the read operation cannot be         |  |  |  |  |

|    |                                                                                                                | performed, so as to avoid the read operation when the data in the data register is being updated                     |  |  |  |  |

|    |                                                                                                                | Made. When the data is updated, DRDY It will return to low again. DRDY Also use                                      |  |  |  |  |

|    |                                                                                                                | To indicate when TM7707/ TM7708 The on-chip calibration sequence serial data output terminal has been                |  |  |  |  |

|    |                                                                                                                | completed. The serial data read from the on-chip output shift register is                                            |  |  |  |  |

| 13 | DOUT                                                                                                           | This end is output. According to the register selection bit in the communication register, the shift register can be |  |  |  |  |

|    |                                                                                                                | Contains information from communication registers, clock registers or data registers                                 |  |  |  |  |

|    |                                                                                                                | Serial data input terminal. The serial data written to the on-chip input shift register is determined by             |  |  |  |  |

| 14 | DIN This input. Enter the shift register according to the register selection bit in the communication register |                                                                                                                      |  |  |  |  |

|    |                                                                                                                | The data in is transferred to the setting register, clock register or communication register                         |  |  |  |  |

| 15 | V DD                                                                                                           | Power supply voltage, + 2.7V~+5.25V                                                                                  |  |  |  |  |

| 16 | GND                                                                                                            | Ground potential reference point of internal circuit                                                                 |  |  |  |  |

Six, limit parameters (TA = +25 °C, unless otherwise specified)

| V DD Correct GND                                  | -0.3V ~+ 7V         |

|---------------------------------------------------|---------------------|

| Analog input voltage pair GND                     | -0.3V ~ V DD + 0.3V |

| Reference input voltage pair GND                  | -0.3V ~ V DD + 0.3V |

| Digital input voltage pair GND                    | -0.3V ~ V DD + 0.3V |

| Digital output voltage pair GND                   | -0.3V ~ V DD + 0.3V |

| Operating temperature range (commercial grade, B) | -40 ℃ ~ + 85 ℃      |

| Storage temperature range                         | -65 ℃ ~ + 150 ℃     |

| Junction temperature                              | + 150 °C            |

| Power consumption (plastic DIP Package)           | 450mW               |

| $\theta$ JA Thermal resistance                    | 105 °C/ W           |

| Pin temperature (soldering, 10 second)            | + 260 °C            |

| Power consumption (plastic SOIC Package)          | 450mW               |

| $\theta$ JA Thermal resistance                    | 75 ℃/ W             |

| Pin temperature (soldering)                       |                     |

| Vapor phase ( 60 second)                          | + 215 °C            |

| infrared( 15 second)                              | + 220 °C            |

| Power consumption (SSOP Package)                  | 450mW               |

| θ JA Thermal resistance                           | 139 °C/ W           |

| Pin temperature (soldering)                       |                     |

| Vapor phase ( 60 second)                          | + 215 °C            |

| infrared( 15 second)                              | + 220 °C            |

| anti- ESD                                         | > 4000V             |

| Vapor phase ( 60 second)<br>infrared( 15 second)  | + 220 °C            |

Note: Strength exceeding the listed limit parameters may cause permanent damage to the device. These are just limit parameters,

It does not mean that the device is under extreme conditions or in any other conditions that exceed the parameters shown in the recommended operating conditions

Pieces can work effectively. Extending the working time under extreme parameter conditions will affect the reliability of the device.

)

-4-

## Seven, electrical characteristics

## ( V $_{\text{DD}=+}$ 3V Or + 5V , REF IN (+)=+ 1.225V $\ ; \ \text{REF IN}$ (-)= GND , MCLK IN

=2.4576MHz , T\_A= T MIN ~ T MAX , unless Otherwise stated ).

| Parameter                                          | B Version 1          | Units Co                | nditions/Comments                                |

|----------------------------------------------------|----------------------|-------------------------|--------------------------------------------------|

| STATIC PERFORMANCE                                 |                      |                         |                                                  |

| No Missing Codes                                   | 16                   | Bits min                | Guaranteed by Design. Filter Notch <60<br>Hz     |

| Output Noise                                       | See Tables I and III |                         | Dependson Filter Cutoffs and Selected<br>Gain    |

| Integral Nonlinearity 2±                           | 0.003                | %of FSR Filte           | r Notch <60 Hz. Typically max<br>0.0003%         |

| Unipolar Offset Error                              | See Note3            |                         |                                                  |

| Unipolar Offset Drift₄                             | 0.5                  | µV/ °C typ              |                                                  |

| Bipolar Zero Error                                 | See Note 3           |                         |                                                  |

| Bipolar Zero Drift₄                                | 0.5                  | μV/ °C typ Fo           | Gains1,2and4 μV/ °C typ For                      |

|                                                    | 0.1                  | Gains8,16,32,           | 64and128                                         |

| Positive Full-Scale<br>Error <sup>5</sup>          | See Note3            |                         |                                                  |

| Full-Scale Drift 4.6                               | 0.5                  | μV/ °C typ              |                                                  |

| Gain Error 7                                       | See Note3            |                         |                                                  |

| Gain Drift 4.8                                     | 0.5                  | ppm of<br>FSR/°C<br>typ |                                                  |

| Bipolar Negative Full<br>-Scale Error <sup>2</sup> | ±0.003               | %of<br>FSR/ °C<br>typ   | Typically±0.001%                                 |

| Bipolar Negative Full<br>-Scale Drift <sup>4</sup> | 1                    | μV/ °C typ              | For Gains of 1 to 4                              |

|                                                    | 0.6                  | μV/ °C typ Fo           | Gains of 8 to 128                                |

| ANALOG INPUTS/REFERENC                             | E INPUTS             |                         | Specifications for AIN and REF IN<br>UnlessNoted |

| Input Common-Mode Rejection                        | on(CMR) 2            |                         |                                                  |

| V DD= 5V                                           |                      |                         |                                                  |

| Gain=1                                             | 96                   | dB typ                  |                                                  |

| Gain=2                                             | 105                  | dB typ                  |                                                  |

| Gain=4                                             | 110                  | dB typ                  |                                                  |

| Gain=8 → 128                                       | 130                  | dB typ                  |                                                  |

| V DD= 3V                                           |                      |                         |                                                  |

| Gain=1                                             | 105                  | dB typ                  |                                                  |

| Gain=2                                             | 110                  | dB typ                  |                                                  |

| Gain=4                                             | 120                  | dB typ                  |                                                  |

|                               | MICRO™                                         |                |                                       |

|-------------------------------|------------------------------------------------|----------------|---------------------------------------|

| THE ELECT                     | MICRO <sup>™</sup><br>RONICS <sup>24 bit</sup> | Analog to digi | ital converter TM7707/8               |

| $Gain=8 \rightarrow 128$      | 130                                            | dB typ         |                                       |

| Normal-Mode50Hz               |                                                |                | For Filter Notches of                 |

| Rejection 2                   | 98                                             | dB typ         | 25Hz, 50Hz, ±0.02×f Nотсн             |

| Normal-Mode60Hz               |                                                |                | For Filter Notches of                 |

| <b>Rejection</b> <sub>2</sub> | 98                                             | dB typ         | 20Hz, 60Hz, ±0.02×f NOTCH             |

| Common-Mode 50Hz              | 450                                            | dD to us       | For Filter Notches of                 |

| Rejection 2                   | 150                                            | dB typ         | 25Hz, 50Hz, ±0.02×f Nотсн             |

| Common-Mode 60Hz              | 150                                            | dB typ         | For Filter Notches of                 |

| Rejection 2                   | 150                                            | ав тур         | 20Hz, 60Hz, ±0.02×f Nотсн             |

| Absolute/Common-M GND to      | V DD                                           | Vmin to        |                                       |

| ode REF IN Voltage 2          |                                                | V mas          |                                       |

| Absolute/Common-M GND-3       | 30mV                                           | Vmin           | BUF Bit of Setup Register=0           |

| ode AIN Voltage 2.9           |                                                |                |                                       |

|                               | V DD+ 30mV                                     | Vmax           |                                       |

| Absolute/Common-M GND+5       | 0mV                                            | Vmin           | BUF Bit of Setup Register=1           |

| ode AIN Voltage 2.9           |                                                |                |                                       |

|                               | V DD -1.5V                                     | Vmax           |                                       |

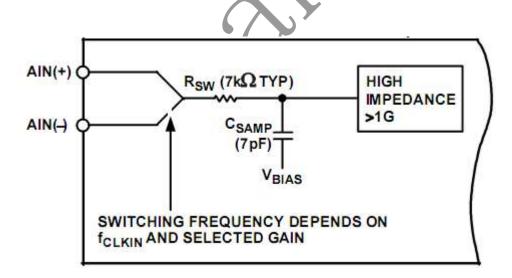

| AIN DC Input                  | 1                                              | nAmax          |                                       |

| Current 2                     |                                                |                |                                       |

| AIN                           | 10                                             | pF max         |                                       |

| SamplingCapacitanc            | 4                                              | $\sim$ $>$     |                                       |

| <b>e</b> 2                    |                                                |                |                                       |

| AIN Differential              | 0to+V REP/ GAIN 11                             | nom            | Unipolar Input Range(B/U Bit of Setup |

| Voltage Range 10              |                                                | nom            | Register=1)                           |

|                               | ±V REP/ GAIN                                   | nom            | Bipolar Input Range(B/U Bit of Setup  |

|                               |                                                |                | Register=0)                           |

| AIN Input Sampling            | GAIN×f clkin/ 64                               |                | For Gains of 1 to 4                   |

| Rate,fs                       |                                                |                |                                       |

|                               | fclkin/8                                       |                | For Gains of 8 to 128                 |

| ReferenceInput                | *                                              |                |                                       |

| Range                         |                                                |                |                                       |

| REFIN(+)—REFIN( -)            | 4/4 75                                         | Vmin/ma V =2   | .7V\$03.3V.V REF= 1.225±1             |

| Voltage                       | 1/1.75                                         | x              | % for Specifled Performance           |

| REFIN(+)—REFIN( -)            | 1/3.5                                          | Vmin/ma V =4   | .75¥to5.25V.V REF= 2.5±1              |

| Voltage                       | 1/3.3                                          | x              | % for Specifled Performance           |

| REF IN Input                  | f                                              |                |                                       |

| SamplingRate, fs              | fclkin/ 64                                     |                |                                       |

| LOGIC INPUTS                  |                                                |                |                                       |

| Input Current                 |                                                |                |                                       |

| All Inputs Except             | ±1                                             | µAmax          | Typically±20nA                        |

| MCLK IN                       |                                                |                |                                       |

| MCLK                          | ±10                                            | µAmax          | Typically±20µA                        |

| All Inputs Except             |                                                |                |                                       |

|                  | MICRO <sup>™</sup><br>24 bit.<br>RONICS | Analog to dig | ital converter TM7707/8 |

|------------------|-----------------------------------------|---------------|-------------------------|

| SCLK and MCLK IN |                                         |               |                         |

| VINL, Input Low  | 0.8                                     | Vmax          | V DD= 5V                |

| Voltage          |                                         |               |                         |

|                  |                                         |               |                         |

| Voltage                                      |           |         |                             |

|----------------------------------------------|-----------|---------|-----------------------------|

|                                              | 0.4       | Vmax    | V dd= 3V                    |

| V <sub>INL</sub> , Input High<br>Voltage     | 2.0       | Vmin    | V <sub>DD=</sub> 3V and 5V  |

| SCLK Only(Schmitt                            |           |         | V DD= 5V NOMINAL            |

| Triggered Input)                             |           |         |                             |

| V <sub>T+</sub>                              | 1.4/3     | Vmin/V  |                             |

|                                              |           | max     |                             |

| V <sub>T_</sub>                              | 0.8/1.4   | Vmin/V  |                             |

|                                              |           | max     |                             |

| V T+ -V T_                                   | 0.4/0.8   | Vmin/V  | C                           |

| -                                            |           | max     |                             |

| SCLK Only(Schmitt                            |           |         |                             |

| Triggered Input)                             |           |         |                             |

| V <sub>T+</sub>                              | 1/2.5     | Vmin/Vm |                             |

|                                              |           | ax      |                             |

| V <sub>T_</sub>                              | 0.4/1.1   | Vmin/Vm |                             |

|                                              |           | ax      |                             |

| <b>V</b> <sub>T+</sub> <b>V</b> <sub>T</sub> | 0.375/0.8 | Vmin/Vm |                             |

|                                              |           | ax      | r                           |

| MCLK IN Only                                 | (         |         |                             |

| VINL, Input Low                              | 0.8       | V max   |                             |

| Voltage                                      |           |         |                             |

| VINL, Input High                             | 3.5       | V min   |                             |

| Voltage                                      |           |         |                             |

| MCLK IN Only                                 |           |         |                             |

| VINL, Input Low                              | 0.4       | V max   |                             |

| Voltage                                      |           | -       |                             |

| V <sub>INL</sub> , Input High                | 2.5       | V min   |                             |

| Voltage                                      |           |         |                             |

| LOGIC OUTPUTS(Including N                    | ICLK OUT) |         |                             |

| VoL, Output Low                              | ,<br>0.4  | V max   | Isink₌ 800µA Exceptfor MCLK |

| Voltage                                      |           |         | OUT. 12 V DD= 5V.           |

| VoL, Output Low                              | 0.4       | V max   | Isink= 100µA Exceptfor MCLK |

| Voltage                                      |           |         | OUT. 12 V DD= 3V.           |

| V он, Output High                            | 4         | V min   | Isource= 200µA Exceptfor    |

| Voltage                                      |           |         | MCLK OUT. 12 V DD= 5V.      |

| V он, Output High                            | V DD0.6   | V min   | Isource= 100µA Exceptfor    |

| Voltage                                      | ~         |         | MCLK OUT. 12 V DD= 3V.      |

| Floating                                     | ± 10      | μAmax   |                             |

| StateLeakage                                 |           |         |                             |

|                                              |           |         |                             |

| JI'I ELEU              | KUNICS                    |         |                                           |

|------------------------|---------------------------|---------|-------------------------------------------|

| Current                |                           |         |                                           |

| Floating StateOutput 9 |                           | pF typ  |                                           |

| Capacitance 13         |                           |         |                                           |

| Data Output Coding     | Binary                    |         | Unipolar Mode                             |

|                        | OffsetBinary              |         | Bipolar Mode                              |

| SYSTEM CALIBRATION     |                           |         |                                           |

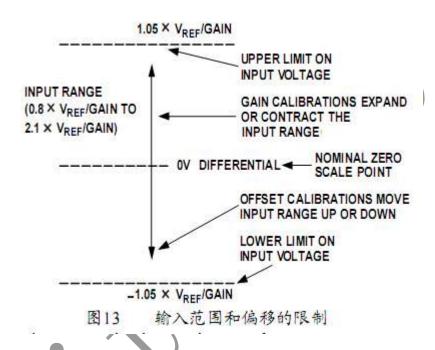

| Positive Full—Scale    | (1.0 5× V REF)            | V max   | GAIN Is the Selected PGA Gain(1           |

| Calibration Limit 14   | GAIN                      |         | to 128)                                   |

| Negative Full—Scale    | — (1.0 5× V REF)          | V max   | GAIN Is the Selected PGA Gain(1           |

| Calibration Limit 14   | GAIN                      |         | to 128)                                   |

| Offset Calibration     | — (1.0 5× V REF)          | V max   | GAIN Is the Selected PGA Gain(1           |

| Limit 14               | GAIN                      |         | to 128)                                   |

| Input Span 15          | (0. 8× V REF)/ GAIN V min |         | GAIN Is the Selected PGA Gain(1           |

|                        |                           |         | to 128)                                   |

|                        | (2.1 X V REF)/ GAIN V max |         | GAIN Is the Selected PGA Gain(1           |

|                        |                           |         | to 128)                                   |

| POWER REQUIREMENTS     |                           |         |                                           |

| V DD Voltage           | + 2.7 to +3.3             | Vmin to | For Specified Performance                 |

|                        |                           | Vmax    |                                           |

|                        |                           |         | Digital I/Ps=0V or V DD. External MCLK IN |

|                        |                           | $\sim$  | and CLK DIS=1                             |

|                        | 0.32                      | mAmax   | BUF Bit=O. f CLKIN= 1MHz.Gains            |

|                        |                           |         | of 1 to 128                               |

|                        | 0.6                       | mAmax   | BUF Bit=1. fclkin= 1MHz.Gains             |

| Power Supply           |                           |         | of 1 to 128                               |

| Currents 16            | 0.4                       | mAmax   | BUF Bit=Of CLKIN= 2.4576MHz.              |

|                        |                           |         | Gains of 1 to 4                           |

|                        | 0.6                       | mAmax   | BUF Bit=O. f clkin= 2.4576MHz.            |

|                        |                           |         | Gains of 8 to 128                         |

|                        | 0.7                       | mAmax   | BUF Bit=O. f clkin= 2.4576MHz.            |

|                        |                           |         | Gains of 1 to 4                           |

|                        | 1.1                       | mAmax   | BUF Bit=1. f ськіл= 2.4576МНz.            |

|                        |                           |         | Gains of 8 to 128                         |

| Variation              | + 4.75 to +5.25           | Vmin    | For Specified Performance                 |

| V DD Voltage           |                           | toVmax  |                                           |

|                        |                           |         | Digital I/Ps=0V or V DD. External MCLK IN |

|                        |                           |         | and CLK DIS=1.                            |

| Power Supply 0.4       | 45                        | mAmax   | BUF Bit=0. fcLKIN= 1MHz.Gains             |

| Currents 16            |                           |         | of 1 to 128                               |

|                        | 0.7                       | mAmax   | BUF Bit=1. fcLKIN= 1MHz.Gains             |

|                        |                           |         | of 1 to 128                               |

|                        |                           |         |                                           |

|                        | 0.6                       | mAmax   | BUF Bit=0. f clkin= 2.4576MHz.            |

|                   | 0.85        | mAmax  | BUF Bit=0. f CLKIN= 2.4576MHz.   |

|-------------------|-------------|--------|----------------------------------|

|                   |             |        | Gains of 8 to 128                |

|                   | 0.9         | mAmax  | BUF Bit=1. f CLKIN= 2.4576MHz.   |

|                   |             |        | Gains of 1 to 4                  |

|                   | 1.3         | mAmax  | BUF Bit=1. f CLKIN= 2.4576MHz.   |

|                   |             |        | Gains of 8 to 128                |

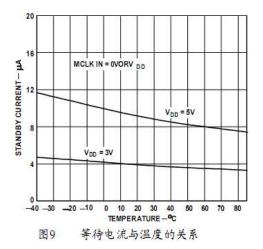

|                   | 16          | μAmax  | External MCLK IN=0V or V DD.     |

| Standby(Power-Dow |             |        | V <sub>DD=</sub> 5V.See Figure 9 |

| n)Current 17      | 8           | μAmax  | External MCLK IN=0V or V DD.     |

|                   |             |        | V DD= 3V                         |

| Power Supply      | See Note 19 | dB typ |                                  |

| Rejection 18      |             |        |                                  |

## Notes:

1. B Grade temperature range is- 40 °C~+ 85 °C.

- 2. These data are released according to the originally designed product.

- 3. A calibration is actually a conversion, so these errors are the table 1 And table 3 The order of the switching noise shown. This applies after calibration at the desired temperature.

- 4. Recalibration under any temperature conditions will remove these drift errors.

- 5. Positive full-scale error includes zero-scale error (Zero-Scale Error) (Unipolar offset error or bipolar zero error), and it is suitable for both unipolar input range and bipolar input range.

- Full-scale drift includes zero-scale drift (unipolar offset drift or bipolar zero drift) and is suitable for unipolar and Bipolar input range.

- Gain error does not include zero-scale error, it is calculated as full-scale error-unipolar offset for unipolar range Error, and for bipolar range is full-scale error-bipolar zero error.

- 8. Gain error drift does not include unipolar offset drift and unipolar zero drift. When only the zero-scale calibration is completed, add The gain error is actually the amount of drift of the device.

- 9. Common mode voltage range: analog input voltage does not exceed V DD+ 30mV, not lower than GND-30mV. Voltage is lower than GND-200mV When the device function is effective, the leakage current will increase at high temperature.

- 10. Given here AIN (+) terminal analog input voltage range, right TM7707 In terms of AIN (-) Terminal voltage Correct TM7708 In terms of COMMON Input terminal. The input analog voltage should not exceed V DD+ 30mV,

- Should not be lower than GND-30mV . GND-200mV The input voltage can also be used, but the leakage current will increase at high temperatures. 11. VREF=REF IN (+)- REF IN (-).

- 12. Only when loading one CMOS Load, these logic output levels are only suitable for MCLK OUT .

- 13. +25 Test samples at °C to ensure consistency.

- 14. After calibration, if the analog input exceeds the positive full scale, the converter will output full 1, If the analog input is below the negative full scale, Will output all 0.

- 15. The limit of the calibration voltage applied to the analog input terminal should not exceed V  $_{DD}$  + 30mV Or less than GND 30mV .

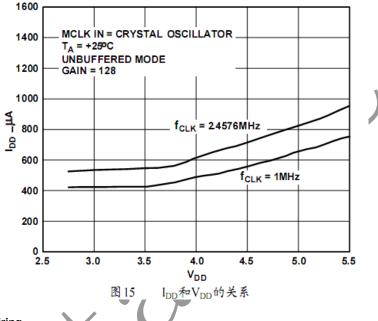

- 16. When using a crystal or ceramic resonator as the clock source of the device (by MCLK Pin), V DD Current and power consumption

Varies with the type of crystal and resonator (see the "Clock and Oscillator Circuit" section).

17. In wait mode, the external main clock continues to run, 5V Wait for the current to increase to 150  $\mu$  A , 3V Electricity

Increase to 75 µ A . When a crystal or ceramic resonator is used as the clock source of the device, the internal oscillator continues to run in the wait

mode, and the power consumption of the power supply varies with the type of crystal and resonator (see "Wait Mode"

one period)

18. Measured in the DC state, applicable to the selected passband. 50Hz Time, PSRR exceed 120dB (Filter notch

© Titan Micro Electronics

V1.1

www.titanmec.com

- 9-

for 25Hz or 50Hz ). 60Hz Time, PSRR exceed 120dB (The filter notch is 20Hz or 60Hz ).

19. PSRR By gain and V DD Decide as follows:

| Gain                   | 1  | 2  | 4  | 8~128 |

|------------------------|----|----|----|-------|

| V DD= 3V               | 86 | 78 | 85 | 93    |

| <b>V</b> DD= <b>5V</b> | 90 | 78 | 84 | 91    |

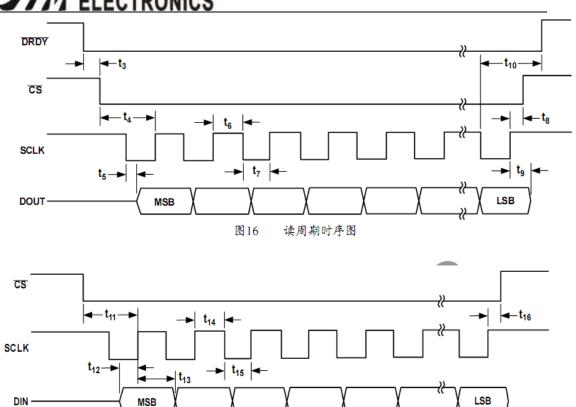

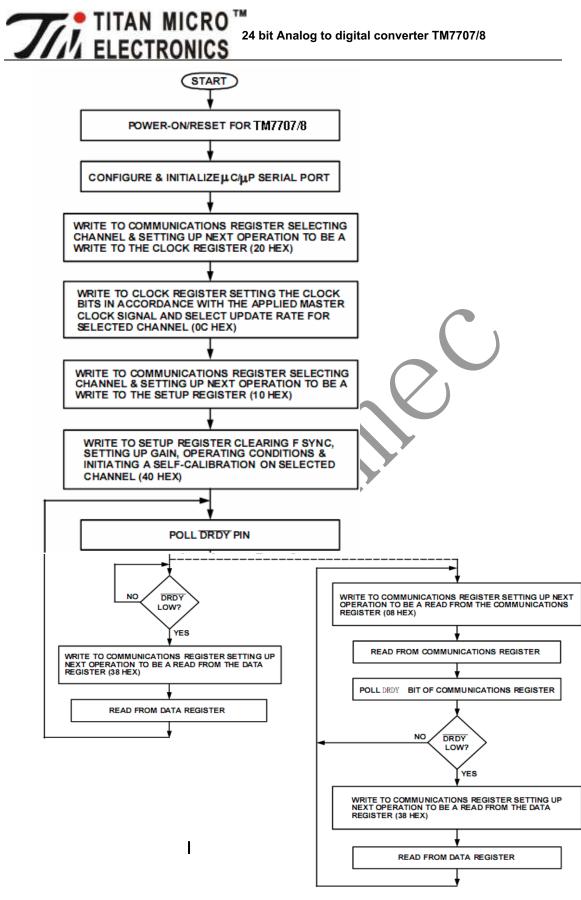

## 8. Timing parameters

(V DD = + 2.7V~+5.2V ; GND=0V ; f CLKIN = 2.4567MHz ; Input Logic 0=0 V,

Logic 1 = <u>V DD</u> Unless otherwise Description)

|                       | Limit at     |           |                                                   |

|-----------------------|--------------|-----------|---------------------------------------------------|

| Parameter             | T MIN, T MAX | Units     | Conditions/Comments                               |

|                       | (B Version)  |           |                                                   |

| fclkin <sup>3,4</sup> | 400          | kHzmin    | Master Clock Frequency: Crystal Oscillator        |

|                       | 400          | KEIZIIIII | or Externally Supplied for Specified              |

|                       | 2.5          | MHz max   | Performance                                       |

| t clkin lo            | 0.4×t clkin  | ns min    | Master Clock Input Low Time.<br>tclkin= 1/ fclkin |

| t clkin Hi            | 0.4×t clkin  | ns min    | Master Clock Input High Time. DRDY                |

| <b>t</b> 1            | 500×t CLKIN  | ns mon    | High Time                                         |

| t 2                   | 100          | ns min    | RESETPulsewidth                                   |

| Read Operation        | on           |           |                                                   |

| t 3                   | 0            | ns min    | DRDY to CS Setup Time                             |

| <b>t</b> 4            | 120          | ns min    | CS Falling Edge to SCLK Rising Edge               |

|                       |              |           | Setup Time                                        |

| tg                    | 0            | ns min    | SCLK Falling Edge to Data Valid Delay             |

|                       | 80           | ns max    | V DD=+ 5V                                         |

|                       | 100          | ns max    | V DD=+ 3.0V                                       |

| t6                    | 100          | ns min    | SCLK High Pulsewidth                              |

| t7                    | 100          | ns min    | SCLK Low Pulsewidth                               |

|                       | 0            | ns min    | CS Rising Edge to SCLK Rising Edge Hold           |

| ts                    | U            | ns min    | Time                                              |

| tg                    | 10           | ns min    | Bus RelinguishTimeafter SCLK                      |

|                       |              |           | Rising Edge                                       |

|                       | 60           | ns max    | V DD=+ 5V                                         |

|                       | 100          | ns max    | V DD=+ 3.0V                                       |

| <b>t</b> 10           | 100          | ns max    | SCLK Falling Edge to DRDY High 7                  |

| Write Operation       | on           |           |                                                   |

| <b>t</b> 11           | 120          | ns min    | CS Falling Edge to SCLK Rising Edge               |

|                       |              |           | Setup Time                                        |

| <b>t</b> 12           | 30           | ns min    | Data Valid to SCLK Rising Edge                    |

|             |     |        | Setup Time                          |

|-------------|-----|--------|-------------------------------------|

| <b>t</b> 13 | 20  | ns min | Data Valid to SCLK Rising Edge Hold |

|             |     |        | Time                                |

| t 14        | 100 | ns min | SCLK High Pulsewidth                |

| t 15        | 100 | ns min | SCLK High Pulsewidth                |

| <b>t</b> 16 | 0   | ns min | CS Rising Edge to SCLK Rising Edge  |

|             |     |        | Hold Time                           |

## Notes:

1. The sample test temperature is + 25 °C to ensure consistency. All input signals meet: t  $_{\rm f}$  = t  $_{\rm f}$  = 5ns ( V  $_{\rm DD}$

of 10%~90% ), and from 1.6V Level timing.

2. See picture 16 And figure 17 .

3. fcLKIN The duty cycle is 45%~55% . as long as TM7707/8 Not in wait mode, must provide fcLKIN. At this In this case, if there is no clock, the device will draw more current than specified and may become uncalibrated.

4. f CLKIN = 2.4567MHz Carry out production test from time to time to ensure the device works 400kHz .

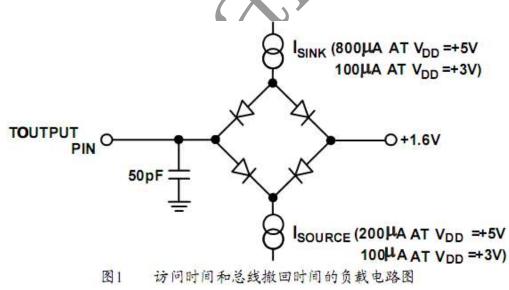

- 5. These numbers are in the figure 1 Measured under the load circuit. They are defined as output through V or or Vor

- 6. The value is in the data output as 0.5V Measured at the time (the load situation is shown in the figure 1 Shown) Then the measured value is pushed Play back to eliminate 50pF The effect of capacitor charging or discharging. This means that all mentioned in the timing parameter table The time values are the real bus withdrawal time (relinquish time), and therefore there is no connection with the external bus load capacitance turn off.

- 7. After the output is updated, DRDY Return to high level after reading from the device for the first time. when DRDY When it is high, if If necessary, the same data can be read again. But it must be noted that after the next output update, random randomness will not happen soon. After reading.

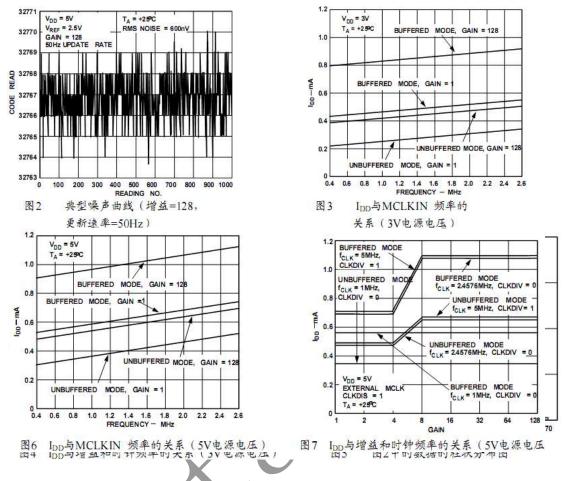

#### Nine, typical characteristic curve

### 10. Output noise

## 10.1TM7707/8 5V Output noise

table 1a Means when f CLKIN= 2.4576MH Z When, for some typical notches and- 3dB frequency, TM7707/8 The output rms noise and effective resolution; table 1b Gives f CLKIN= 1MHZ Time data. The data given applies to V REF

As + 2.5V And BUFFER=0 The bipolar input range. These data are typical values and the analog input voltage is 0V Under the circumstances. The data in

parentheses in each table is the effective resolution of the period (rounded to the nearest 0.5 LSB)

The effective resolution of the device is defined as the output rms noise and the input full scale (ie, 2 X V REF/ GAIN )Ratio. should

Note that it is not calculated using peak-to-peak output noise data. Peak-to-peak noise data can be as high as the root mean square data 6.6 Times,

At the same time, the effective resolution data based on peak-to-peak noise can be compared with the effective resolution based on rms noise shown in the slogan in the table.

The output noise of the device comes from two sources. The first source is the electrical noise of the semiconductor devices used in the implementation of the modulator.

Piece noise) . Second, when the analog input signal is converted to the digital domain, quantization noise is added. Device noise is low level

And basically has nothing to do with frequency. The quantization noise starts at a fairly low level, but rises rapidly as the frequency increases to become

The main noise source. Therefore, the lower filter notch setting (for  $f_{\mbox{ CLKIN= }2.4576\mbox{MH}\,\mbox{Z}}$  , About below 100MHZ ,

for f CLKIN= 1MH z , About below 40H z ) Is controlled by the device noise, and the setting of the higher notch is controlled by the quantization noise

system. As table I As shown, the change of the filter notch and cutoff frequency in the quantization noise control domain will be greater than that in the device noise control domain

The change in is independent of the gain in noise performance. At the same time, device noise is added to PGA Medium, therefore, high frequency at lower notches

In the case of gain, the effective resolution will decrease. In addition, in the device noise control area, the output noise (with µ V meter)

Basically it has nothing to do with the reference voltage; in the quantization noise control area, the noise ratio is based on the value of the reference. Adopted on the device

Post-filtering may improve the output data rate for a given -3dB frequency, and further reduce the output

Out of noise.

Set at the lower filter notch ( f CLKIN= 2.4576MH z Time below 60Hz , f CLKIN= 1MH z ) Case,

The error-free performance of the device is at twenty four Bit level. In the case of a higher setting, more errors will be generated until the

f CLKIN= 2.4576MH z When the notch is set to 1kHz (f CLKIN= 1MH z Set as 400Hz )until. Only for 12 Bits guarantee error-free performance.

## table 1a fCLKIN=2.4576MHZ , BUFFER=0 Time

TM7707/8 Output noise/resolution and gain 1 The relationship of a notch (5V Voltage)

| Filter           | Туріс         | al Output R     | MS Noise in     | μ V(Effecti     | ve Resoluti     | on in bits)     |                 |                 |

|------------------|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| First            |               |                 |                 |                 |                 | -               |                 |                 |

| Notch and        | Gain of       | Gain of         | Gain of         | Gain of         | Gain of         | Gain of         | Gain of         | Gain of         |

| O/P — 3 dB       | Gain Or       | Gain Or         | Gain Or         | Gain Or         | Gain Or         | Gain of         | Gain of         | Gain Or         |

| Data Rate        |               | •               |                 | 0               | 40              | 20              | <b>C</b> 4      | 400             |

| <b>Frequency</b> | 1             | 2               | 4               | 8               | 16              | 32              | 64              | 128             |

| 5Hz              | 0.87          | 0.48            | 0.24            | 0.2             | 0.18            | 0.17            | 0.17            | 0.17            |

| 1.31Hz           | <u>(22.5)</u> | <u>( 22.5 )</u> | <u>(22.5)</u>   | <u>( 21.5 )</u> | <u>( 20.5 )</u> | <u>( 20 )</u>   | <u>(19)</u>     | <u>(18)</u>     |

| 10Hz             | 1.0           | 0.78            | 0.48            | 0.33            | 0.25            | 0.25            | 0.25            | 0.25            |

| 2.62Hz           | <u>(22.5)</u> | <u>(21.5)</u>   | <u>( 21.5 )</u> | ( twenty one )  | <u>( 20.5 )</u> | <u>( 19.5 )</u> | <u>( 18.5 )</u> | <u>( 17.5 )</u> |

| 25Hz             | 1.8           | 1.1             | 0.63            | 0.5             | 0.44            | 0.41            | 0.38            | 0.38            |

| 6.55Hz           | <u>(21.5)</u> | ( twenty one )  | (twenty one)    | (20)            | (19.5)          | (18.5)          | (17.5)          | (16.5)          |

| 30Hz             | 2.5           | 1.31            | 0.84            | 0.57            | 0.46            | 0.43            | 0.4             | 0.4             |

| 7.86Hz           | (twenty one)  | (twenty one)    | (20.5)          | (20)            | (19.5)          | (18.5)          | (17.5)          | (16.5)          |

| 50Hz             | 4.33          | 2.06            | 1.2             | 0.64            | 0.54            | 0.46            | 0.46            | 0.46            |

| 13.1Hz           | (20)          | <u>(20)</u>     | <u>(20)</u>     | <u>(20)</u>     | <u>(19)</u>     | <u>( 18.5 )</u> | <u>( 17.5 )</u> | (16.5)          |

| 60Hz             | 5.28          | 2.36            | 1.33            | 0.87            | 0.63            | 0.62            | 0.6             | 0.56            |

| 15.72Hz          | (20)          | <u>(20)</u>     | <u>(20)</u>     | <u>(19.5)</u>   | <u>(19)</u>     | <u>(18)</u>     | <u>(17)</u>     | (16)            |

| 100 Hz           | 12.1          | 5.9             | 2.86            | 1.91            | 1.06            | 0.83            | 0.82            | 0.76            |

| 26.2 Hz          | (18.5)        | <u>( 18.5 )</u> | <u>(19)</u>     | <u>( 18.5 )</u> | <u>(18)</u>     | <u>( 17.5 )</u> | <u>( 16.5 )</u> | (15.5)          |

| 250Hz            | 127           | 58              | 29              | 15.9            | 6.7             | 3.72            | 1.96            | 1.5             |

| 65.5Hz           | <u>(15.5)</u> | <u>( 15.5 )</u> | (14.5)          |

| 500Hz            | 533           | 267             | 137             | 66              | 38              | 20              | 8.6             | 4.4             |

| 131Hz            | <u>(13)</u>   | <u>(13)</u>     | <u>(13)</u>     | <u>(13)</u>     | <u>(13)</u>     | <u>(13)</u>     | <u>(13)</u>     | (13)            |

© Titan Micro Electronics

-13-

| 1Hz   | 2850 | 1258 | 680  | 297  | 131  | 99     | 53     | 28     |  |  |  |

|-------|------|------|------|------|------|--------|--------|--------|--|--|--|

| 262Hz | (11) | (11) | (11) | (11) | (11) | (10.5) | (10.5) | (10.5) |  |  |  |

table 1b fCLKIN=1MHZ , BUFFER=0 Time

TM7707/8 Output noise/resolution and gain 1 The relationship of a notch ( 5V Voltage)

| Filter<br>First               | Typical Output RMS Noise in μ V(Effective Resolution in bits) |                |                |                      |                |                |                    |                |  |  |

|-------------------------------|---------------------------------------------------------------|----------------|----------------|----------------------|----------------|----------------|--------------------|----------------|--|--|

| Notch and<br>O/P — 3 dB       | Gain of                                                       | Gain of        | Gain of        | Gain of              | Gain of        | Gain of        | Gain of            | Gain of        |  |  |

| Data Rate<br><u>Frequency</u> | 1                                                             | 2              | 4              | 8                    | 16             | 32             | 64                 | 128            |  |  |

| 2Hz                           | 0.75                                                          | 0.56           | 0.31           | 0.19                 | 0.17           | 0.14           | 0.14               | 0.14           |  |  |

| 0.52Hz                        | (22.5)                                                        | (twenty two)   | (twenty two)   | (21.5)               | (twenty one)   | (20)           | (19)               | (18)           |  |  |

| 4Hz<br>1.05Hz                 | 1.04<br>(twenty two)                                          | 0.88<br>(21.5) | 0.45<br>(21.5) | 0.28<br>(twenty one) | 0.21<br>(20.5) | 0.21<br>(19.5) | 0.21<br>(18.5<br>) | 0.21<br>(17.5) |  |  |

| 10Hz                          | 1.66                                                          | 1.01           | 0.77           | 0.41                 | 0.27           | 0.35           | 0.35               | 0.35           |  |  |

| 2.62Hz                        | (21.5)                                                        | (21.5)         | (20.5)         | (20.5)               | (19.5)         | (1 9)          | (18)               | (17)           |  |  |

| 25Hz                          | 5.2                                                           | 2.06           | 1.4            | 0.86                 | 0.63           | 0.61           | 0.59               | 0.59           |  |  |

| 6.55Hz                        | (20)                                                          | (20)           | (20)           | (19.5)               | (19)           | (18)           | (17)               | (16)           |  |  |

| 30Hz                          | 7.1                                                           | 3.28           | 1.42           | 1.07                 | 0.78           | 0.64           | 0.61               | 0.61           |  |  |

| 7.86Hz                        | (19.5)                                                        | (19.5)         | (19.5)         | (19)                 | (18.5)         | (18)           | (17)               | (16)           |  |  |

| 50Hz                          | 19.4                                                          | 9.11           | 4.2            | 2.45                 | 1.56           | 1.1            | 0.82               | 0.8            |  |  |

| 13.1Hz                        | (18)                                                          | (18)           | (18)           | (18)                 | (17.5)         | (17)           | (16.5)             | (15.5)         |  |  |

| 60Hz                          | 25                                                            | 16             | 6.5            | 2.9                  | 1.93           | 1.4            | 1.1                | 0.98           |  |  |

| 15.72Hz                       | (17.5)                                                        | (17.5)         | (17.5)         | (17.5)               | (17.5)         | (17)           | (16)               | (15.5)         |  |  |

| 100Hz                         | 102                                                           | 58             | 25             | 13.5                 | 5.7            | 3.9            | 2.1                | 1.3            |  |  |

| 26.2Hz                        | (15.5)                                                        | (15.5)         | (15.5)         | (15.5)               | (15.5)         | (15.5)         | (15)               | (15)           |  |  |

| 200Hz                         | 637                                                           | 259            | 130            | 76                   | 33             | 16             | 11                 | 6              |  |  |

| 52.4Hz                        | (13)                                                          | (13)           | (13)           | (13)                 | (13)           | (13)           | (13)               | (12.5)         |  |  |

| 400Hz                         | 2830                                                          | 1430           | 720            | 334                  | 220            | 94             | 54                 | 25             |  |  |

| 104.8Hz                       | (11)                                                          | (11)           | (11)           | (11)                 | (10.5)         | (10.5)         | (10.5)             | (10.5)         |  |  |

## 10.2 TM7707/8 3V Output noise

table 2a Means when  $f_{CLKIN= 2.4576MH Z}$  When, for some typical notches and - 3dB frequency, TM7707/8 The output rms noise and effective resolution; table 2b Gives  $f_{CLKIN= 1MHZ}$  Time data. The data given applies to V REF

As + 1.25V And BUFFER=0 The bipolar input range. These data are typical values and the analog input voltage is 0V Under the circumstances. The data in

parentheses in each table is the effective resolution of the device (rounded to the nearest 0.5LSB )

The effective resolution of the device is defined as the output rms noise and the input full scale (ie, 2 X V REF/ GAIN )Ratio. should

Note that it is not calculated using peak-to-peak output noise data. Peak-to-peak noise data can be as high as the root mean square data 6.6 Times,

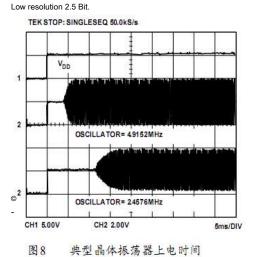

At the same time, the effective resolution data based on peak-to-peak noise can be compared with the effective resolution based on rms noise shown in the slogan in the table. Low resolution 2.5 Bit.

The output noise of the device comes from two sources. The first source is the electrical noise of the semiconductor devices used in the implementation of the modulator.

© Titan Micro Electronics V1.1 www.titanmec.com

-14-

Piece noise) . Second, when the analog input signal is converted to the digital domain, quantization noise is added. Device noise is low level

And basically has nothing to do with frequency. The quantization noise starts at a fairly low level, but rises rapidly as the frequency increases to become

The main noise source. Therefore, the lower filter notch setting (for f CLKIN= 2.4576MH Z , About below 100HZ ,

for f CLKIN= 1MH z, About below 40H z) Is controlled by the device noise, and the setting of the higher notch is controlled by the quantization noise

system. As table I As shown, the change of the filter notch and cutoff frequency in the quantization noise control domain will be greater than that in the device noise control domain

The change in is independent of the gain in noise performance. At the same time, device noise is added to PGA Medium, therefore, high frequency at lower notches

In the case of gain, the effective resolution will decrease. In addition, in the device noise control area, the output noise (with µ V meter)

Basically it has nothing to do with the reference voltage; in the quantization noise control area, the noise ratio is based on the value of the reference. Adopted on the device

Post-filtering may improve the output data rate for a given -3dB frequency, and further reduce the output

Out of noise.

Set at the lower filter notch (  $f_{\mbox{CLKIN}=\mbox{2.4576MH}\mbox{ z}}$  Time below 60Hz ,  $f_{\mbox{CLKIN}=\mbox{1MH}\mbox{ z}}$  ) Case,

The error-free performance of the device is at twenty four Bit level. In the case of a higher setting, more errors will be generated until the

f CLKIN= 2.4576MH z When the notch is set to 1kHz (f CLKIN= 1MH z Set as 400Hz )until. Only for 12 Bits guarantee error-free performance.

#### table 2a fCLKIN=2.4576MHZ , BUFFER=0 Time

TM7707/8 Output noise/resolution and gain 1 Notch relationship ( 3V Voltage)

| Filter           | Туріса          | Typical Output RMS Noise in μ V(Effective Resolution in bits) |                 |                 |                 |                 |                 |               |  |  |  |  |

|------------------|-----------------|---------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------|--|--|--|--|

| First            |                 | Gain                                                          |                 |                 |                 |                 |                 |               |  |  |  |  |

| Notch and        | Gain of         | Gain of                                                       | Gain of         | Gain of         | Gain of         | Gain of         | Gain of         |               |  |  |  |  |

| O/P — 3 dB       |                 |                                                               |                 |                 |                 |                 |                 | of            |  |  |  |  |

| Data Rate        | 1               | 2                                                             | 4               | 8               | 16              | 32              | 64              | 128           |  |  |  |  |

| <b>Frequency</b> | •               | -                                                             |                 |                 |                 |                 | ••              |               |  |  |  |  |

| 5Hz              | 1.07            | 0.68                                                          | 0.29            | 0.24            | 0.22            | 0.17            | 0.17            | 0.17          |  |  |  |  |

| 1.31Hz           | ( twenty one )  | ( twenty one )                                                | ( twenty one )  | <u>(20)</u>     | <u>( 19.5 )</u> | <u>(20)</u>     | <u>(19)</u>     | <u>( 18 )</u> |  |  |  |  |

| 10Hz             | 1.69            | 1.1                                                           | 0.56            | 0.35            | 0.33            | 0.33            | 0.33            | 0.33          |  |  |  |  |

| 2.62Hz           | <u>( 20.5 )</u> | (20)                                                          | <u>(20)</u>     | <u>( 19.5 )</u> | <u>(19)</u>     | <u>(18)</u>     | <u>(17)</u>     | <u>(16)</u>   |  |  |  |  |

| 25Hz             | 3.03            | 1.7                                                           | 0.89            | 0.55            | 0.49            | 0.46            | 0.46            | 0.45          |  |  |  |  |

| 6.55Hz           | <u>(19.5)</u>   | <u>(19.5)</u>                                                 | (19.5)          | (19)            | (18.5)          | (17.5)          | (16.5)          | <u>(15.5)</u> |  |  |  |  |

| 30Hz             | 3.55            | 2.1                                                           | 1.1             | 0.61            | 0.58            | 0.57            | 0.55            | 0.55          |  |  |  |  |

| 7.86Hz           | (19.5)          | (19)                                                          | (19)            | (18.5)          | (18)            | (17)            | (16)            | (15)          |  |  |  |  |

| 50Hz             | 4.72            | 2.3                                                           | 1.5             | 0.84            | 0.7             | 0.68            | 0.67            | 0.66          |  |  |  |  |

| 13.1Hz           | (19)            | <u>(19)</u>                                                   | <u>( 18.5 )</u> | <u>( 18.5 )</u> | <u>(18)</u>     | <u>(17)</u>     | <u>(16)</u>     | (15)          |  |  |  |  |

| 60Hz             | 5.12            | 3.1                                                           | 1.6             | 0.98            | 0.9             | 0.7             | 0.69            | 0.68          |  |  |  |  |

| 15.72Hz          | (19)            | <u>( 18.5 )</u>                                               | <u>(18)</u>     | <u>(18)</u>     | <u>( 17.5 )</u> | <u>(17)</u>     | <u>(16)</u>     | (18)          |  |  |  |  |

| 100 Hz           | 9.68            | 5.6                                                           | 2.4             | 1.3             | 1.1             | 0.95            | 0.88            | 0.9           |  |  |  |  |

| 26.2 Hz          | (18)            | <u>(18)</u>                                                   | <u>(18)</u>     | <u>(18)</u>     | <u>(17)</u>     | <u>( 16.5 )</u> | <u>( 15.5 )</u> | <u>(14.5)</u> |  |  |  |  |

| 250Hz            | 44              | 31                                                            | 15              | 5.8             | 3.7             | 2.4             | 1.8             | 1.5           |  |  |  |  |

| 65.5Hz           | <u>(16)</u>     | <u>( 15.5 )</u>                                               | <u>( 15.5 )</u> | <u>( 15.5 )</u> | <u>( 15.5 )</u> | <u>(15)</u>     | <u>( 14.5 )</u> | <u>(14.5)</u> |  |  |  |  |

| 500Hz            | 304             | 129                                                           | 76              | 33              | 20              | 11              | 6.3             | 3             |  |  |  |  |

| 131Hz            | <u>(13)</u>     | <u>(13)</u>                                                   | <u>(13)</u>     | <u>(13)</u>     | <u>(13)</u>     | <u>(13)</u>     | <u>( 12.5 )</u> | <u>(12.5)</u> |  |  |  |  |

| 1Hz              | 1410            | 715                                                           | 350             | 177             | 101             | 51              | 31              | 12            |  |  |  |  |

| 262Hz            | (11)            | (11)                                                          | (11)            | (11)            | (10.5)          | (10.5)          | (10.5)          | <u>(10.5)</u> |  |  |  |  |

© Titan Micro Electronics -15-

TITAN MICRO <sup>14</sup> 24 bit Analog to digital converter TM7707/8

table 2b fCLKIN=1MHZ , BUFFER=0 Time

TM7707/8 Output noise/resolution and gain 1 Notch relationship ( 3V Voltage)

| Filter<br>First               | Typica       | I Output RM  | IS Noise in  | μ V(Effectiv | e Resolutio | n in bits) |         |               |

|-------------------------------|--------------|--------------|--------------|--------------|-------------|------------|---------|---------------|

| Notch and<br>O/P — 3 dB       | Gain of      | Gain of      | Gain of      | Gain of      | Gain of     | Gain of    | Gain of | Gain<br>of    |

| Data Rate<br><u>Frequency</u> | 1            | 2            | 4            | 8            | 16          | 32         | 64      | 128           |

| 2Hz                           | 0.86         | 0.58         | 0.32         | 0.21         | 0.2         | 0.2        | 0.2     | 0.2           |

| 0.52Hz                        | (21.5)       | (twenty one) | (twenty one) | (20.5)       | (19.5)      | (18.5)     | (17.5)  | <u>(16.5)</u> |

| 4Hz                           | 1.26         | 0.74         | 0.44         | 0.35         | 0.3         | 0.3        | 0.3     | 0.3           |

| 1.05Hz                        | (twenty one) | (20.5)       | (20.5)       | (20)         | (19)        | (18)       | (17)    | (16)          |

| 10Hz                          | 1.68         | 1.33         | 0.73         | 0.5          | 0.49        | 0.49       | 0.48    | 0.47          |

| 2.62Hz                        | (20.5)       | (20)         | (20)         | (19)         | (18.5)      | (17.5)     | (16.5)  | <u>(15.5)</u> |

| 25Hz                          | 3.82         | 2.0          | 1.2          | 0.88         | 0.66        | 0.57       | 0.55    | 0.55          |

| 6.55Hz                        | (19.5)       | (19.5)       | (19)         | (18.5)       | (18)        | (17)       | (16)    | (15)          |

| 30Hz                          | 4.88         | 2.1          | 1.3          | 0.93         | 0.82        | 0.69       | 0.68    | 0.66          |

| 7.86Hz                        | (19)         | (19)         | (19)         | (18.5)       | (17.5)      | (17)       | (16)    | (15)          |

| 50Hz                          | 61           | 30           | 12           | 6.1          | 2.9         | 2.4        | 1.8     | 1.8           |

| 13.1Hz                        | (15.5)       | (15.5)       | (15.5)       | (15.5)       | (15.5)      | (15)       | (14.5)  | <u>(13.5)</u> |

| 60Hz                          | 25           | 16           | 6.5          | 2.9          | 1.93        | 1.4        | 1.1     | 0.98          |

| 15.72Hz                       | (17.5)       | (17.5)       | (17.5)       | (17.5)       | (17.5)      | (17)       | (16)    | <u>(15.5)</u> |

| 100Hz                         | 102          | 58           | 25           | 13.5         | 5.7         | 3.9        | 2.1     | 1.3           |

| 26.2Hz                        | (15.5)       | (15.5)       | (15.5)       | (15.5)       | (15.5)      | (15.5)     | (15)    | (15)          |

| 200Hz                         | 275          | 130          | 65           | 33           | 17          | 11         | 6.3     | 3             |

| 52.4Hz                        | (13)         | <b>(</b> 13) | (13)         | (13)         | (13)        | (13)       | (12.5)  | <u>(12.5)</u> |

| 400Hz                         | 1435         | 720          | 362          | 175          | 110         | 51         | 31      | 12            |

| 104.8Hz                       | (11)         | (11)         | (11)         | (11)         | (10.5)      | (10.5)     | (10.5)  | <u>(10.5)</u> |

#### 10.3 Buffer mode output noise

table 3 Means when f CLKINF 2.4576MH z with BUFFER=+5V When, for some typical notches and- 3dB frequency, TM7707/8 The output rms noise and effective resolution; table 4 Gives f CLKIN= 2.4576MHz with BUFFER=+5V Time TM7707/8 The data. The data given applies to the bipolar input range and has 0V Differential analog input voltage generation. for TM7707/8, VDD=5V Time V REF Voltage is + 2.5V; for TM7707/8, VDD=3V Time V REF Voltage As + 1.25V. The effective resolution of the data device in the brackets in each table (rounded to the nearest 0.5LSB). Device The effective resolution of the device is defined as the output rms noise and the input full scale (ie, 2 X V REF/ GAIN )Ratio. It should be noted It is not calculated using peak-to-peak output noise data. Peak-to-peak noise data can be as high as the root mean square data 6.6 Times, the same The effective resolution data based on peak-to-peak noise can be compared with the effective resolution based on root mean square noise shown in the slogan in the table. Low rate 2.5 Bit.

table 3 fCLKIN=2.4576MHZ Time TM7707/8 Output noise in buffer mode/resolution (5V Voltage)

| Filter     |                | al Output R     |                        | u V(Effecti      | ve Resoluti     | on in hits)     |                 |                 |

|------------|----------------|-----------------|------------------------|------------------|-----------------|-----------------|-----------------|-----------------|

|            | i ypic         | aroutputr       |                        | iµ v(⊏necu       | ve nesoluti     | on in bits)     |                 |                 |

| First      |                |                 |                        |                  |                 |                 |                 |                 |

| Notch and  | Gain of        | Gain of         | Gain of                | Gain of          | Gain of         | Gain of         | Gain of         | Gain of         |

| O/P — 3 dB |                |                 |                        |                  |                 |                 |                 |                 |

| Data Rate  | 1              | 2               | 4                      | 8                | 16              | 32              | 64              | 128             |

| Frequency  |                | <b>L</b>        | -                      |                  | 10              | 52              |                 | 120             |

| 5Hz        | 0.99           | 0.68            | 0.46                   | 0.26             | 0.26            | 0.26            | 0.26            | 0.260           |

| 1.31Hz     | <u>(22.5)</u>  | ( twenty two )  | <u>( 21.5 )</u>        | ( twenty one )   | <u>(20)</u>     | <u>(19)</u>     | <u>(18)</u>     | <u>(17)</u>     |

| 10Hz       | 1.5            | 0.95            | 0.63                   | 0.41             | 0.39            | 0.36            | 0.36            | 0.36            |

| 2.62Hz     | <u>(21.5)</u>  | <u>( 21.5 )</u> | ( twenty one )         | <u>( 20.5 )</u>  | <u>( 19.5 )</u> | <u>( 18.5 )</u> | <u>( 17.5 )</u> | <u>( 16.5 )</u> |

| 25Hz       | 2.5            | 1.7             | 0.88                   | 0.75             | 0.57            | 0.57            | 0.57            | 0.56            |

| 6.55Hz     | ( twenty one ) | <u>(20.5)</u>   | (20.5)                 | (19.5)           | (19)            | (18)            | (17)            | (16)            |

| 30Hz       | 2.9            | 1.8             | 1                      | 0.87             | 0.75            | 0.72            | 0.72            | 0.71            |

| 7.86Hz     | (20.5)         | (20.5)          | (20)                   | (19.5)           | (18.5)          | (17.5)          | (16.5)          | (15.5)          |

| 50Hz       | 4.2            | 2.5             | 1.5                    | 1.1              | 0.94            | 0.94            | 0.94            | 0.87            |

| 13.1Hz     | (20)           | <u>(20)</u>     | <u>( 19.5 )</u>        | <u>(19)</u>      | <u>(18.5)</u>   | <u>(17.5)</u>   | <u>(17.5)</u>   | (15.5)          |

| 60Hz       | 6.1            | 2.9             | 2                      | 1.2              |                 | 0.97            | 0.95            | 0.94            |

| 15.72Hz    | (19.5)         | <u>(19.5)</u>   | <u>( 19.5 )</u>        | <u>(19)</u>      | <u>(18.5)</u>   | <u>(17.5)</u>   | <u>(16.5)</u>   | (15.5)          |

| 100 Hz     | 13.8           | 6.5             | 3.5                    | 2.2              | 1.3             | 1.2             | 1.3             | 1.1             |

| 26.2 Hz    | (18.5)         | <u>(18.5)</u>   | <u>( 18.5 )</u>        | <u>(18)</u>      | <u>(18)</u>     | <u>(17)</u>     | <u>(16)</u>     | (15)            |