#### **TMC9660**

#### **General Description**

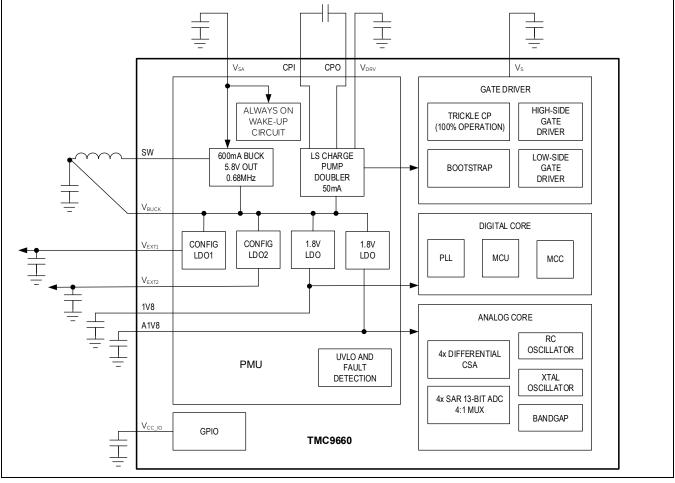

The TMC9660 is a highly integrated monolithic gate driver and motor controller IC with buck converter.

It includes a smart gate driver, a high-performance motion controller with hardware-based field-oriented control (FOC) and servo controller (velocity, position, ramp generator), motor position feedback interfaces (A/B/N encoder, hall), an analog signal processing block for bottom shunt current measurement (programmable current-sense amplifiers [CSAs] and analog-to-digital converters [ADCs]). It also includes a powerful and flexible power management unit (PMU) along with a buck converter and programmable low-dropout (LDO) regulators. For overall control and communication with an external processor through SPI or UART, a preprogrammed 32-bit microcontroller is embedded. The processor system supports either low-level direct register access to all motor control peripherals or higherlevel parameter mode access for extended functionality and ease of use. For initial configuration of system hardware connections and software selection, a bootloader is available also supporting permanent storage of this configuration in the one-timeprogrammable (OTP) memory.

#### **Applications**

- Robotics

- Power Tools

- Gardening

- Automated Guided Vehicles (AGV)/Warehouse Automation

- Pump (e.g., Peristaltic)

- Industrial 3D Printing

- Factory Automation

- Desktop Manufacturing

- E-Bike/Light Electric Vehicles or LEV

#### **Benefits and Features**

- Three-Phase Permanent Magnet Synchronous Motors (PMSM)/Brushless DC (BLDC), Two-Phase Stepper Motor, and Brushed DC Motor Support

- 7.7V to 70V Single-Supply Operating Voltage Range

- Smart Gate Driver with Adjustable Strength up to 1A/2A Source/Sink

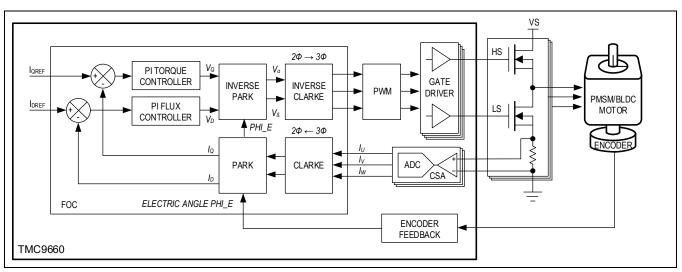

- Field-Oriented Controller/FOC in Hardware for Wide Bandwidth Current Control Loop

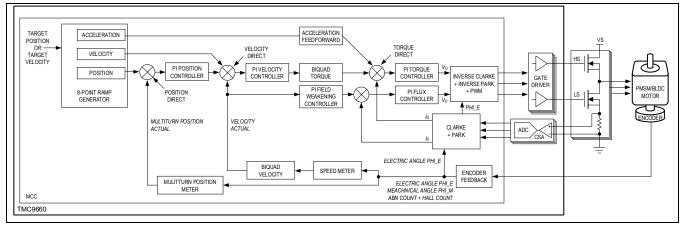

- Position, Velocity, and Torque Controller in Hardware for Fast and Precise Control

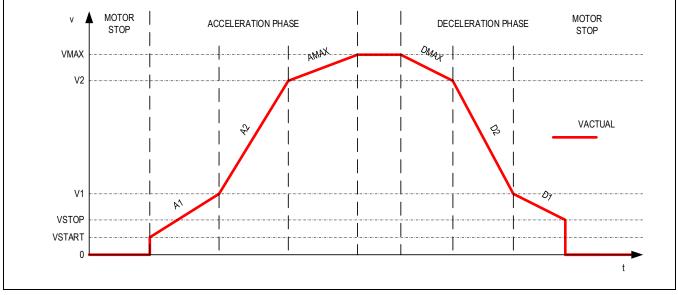

- 8-Point Ramp Generator with Ramp Calculation in Real Time in Hardware

- Fast Space Vector Pulse Width Modulation (SVPWM) Engine (2kHz ...100kHz) with 120MHz Clock

- Feedback Position Sensor Support (Hall, A/B/N, SPI)

- Bottom Shunt Current Measurement (Programmable CSA and ADCs)

- 5.8V/600mA Buck Converter

- 2x Configurable LDOs (2.5V, 3.3V, or 5V) for Supply of External Circuits with each having 150mA current

- Charge Pump with Voltage Doubler

- Trickle Charge Pump for 100% PWM Duty Cycle

- Integrated Preprogrammed 32-Bit/40MHz Microcontroller Supporting Initial Configuration (OTP) of the Device and Direct Hardware/Register or Parameter Mode Access

- SPI, UART Interfaces for Communication with Main/Application Controller

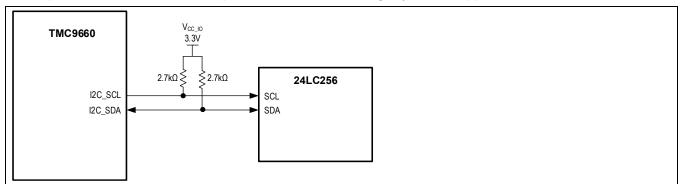

- Parameter Storage (Optional) in SPI flash memory or I2C EEPROM

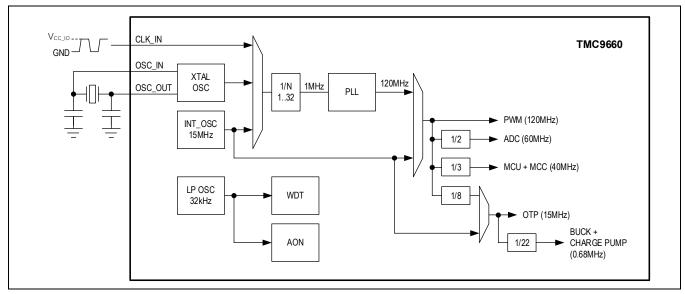

- Internal Oscillator with Phase Locked Loop (PLL) and Optional External Crystal or Clock Support

- Watchdog with Separate Internal Oscillator

- Low-Power Hibernation Mode with Wake-Up Button and Timer Support

- Compact Monolithic Solution, 64-Pin, 9mm x 9mm TQFN Package

Ordering Information appears at end of data sheet.

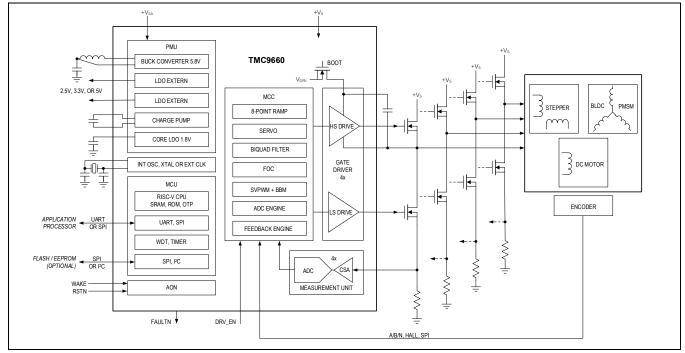

# Simplified Block Diagram

Figure 1. TMC9660 Simplified Block Diagram

# 70V Smart Gate Driver with Servo (FOC) Controller in HW and Buck Converter

# TABLE OF CONTENTS

| General Description                       | 1  |

|-------------------------------------------|----|

| Applications                              | 1  |

| Benefits and Features                     | 1  |

| Simplified Block Diagram                  | 2  |

| Absolute Maximum Ratings                  | 9  |

| Package Information                       | 10 |

| Pin Configurations                        | 11 |

| Pin Descriptions                          | 12 |

| Functional Diagrams                       | 15 |

| Application Modes                         | 16 |

| Power-Saving Modes                        | 16 |

| Power Supply—Electrical Characteristics   | 17 |

| General-Purpose Input/Output Description  | 19 |

| GPIO Electrical Characteristics           | 22 |

| Microcontroller Unit Description          | 23 |

| Timer                                     | 23 |

| System Timer                              | 23 |

| Basic Timer                               | 23 |

| Advanced Timer                            | 23 |

| Watchdog Timer                            | 23 |

| UART                                      | 23 |

| SPI                                       | 25 |

| I <sup>2</sup> C                          | 27 |

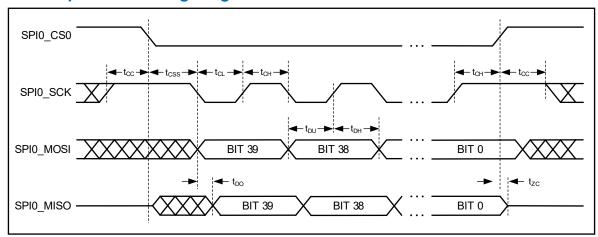

| SPI Peripheral—Timing Diagram             | 27 |

| SPI Peripheral—Electrical Characteristics | 27 |

| Motor Control Core Description            |    |

| Field-Oriented Control                    |    |

| Servo Controller                          |    |

| Ramp Generator                            | 31 |

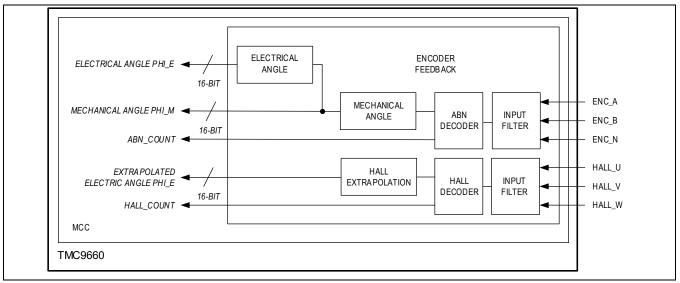

| Encoder Feedback                          |    |

| Motor Types                               |    |

| Power Management Unit Description         |    |

| PMU List of Features                      |    |

| PMU Diagram TMC9660                       | 35 |

| Power Management Unit                     | 35 |

| Power Management Unit Electrical Characteristics      |    |

|-------------------------------------------------------|----|

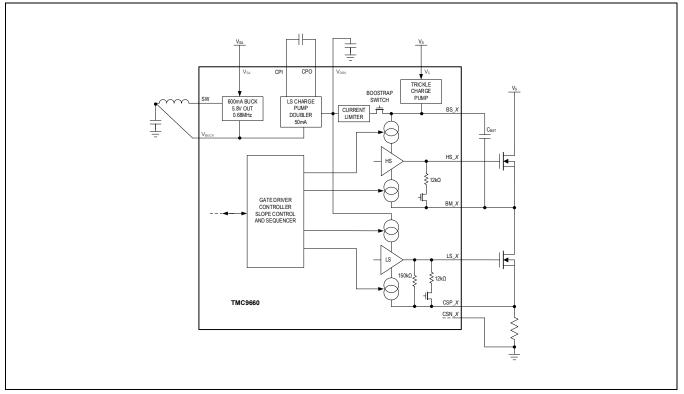

| Gate Driver Unit Description                          | 41 |

| Introduction                                          | 41 |

| GDU List of Features                                  | 41 |

| Detailed Description                                  | 41 |

| Gate Driver Unit Electrical Characteristics           |    |

| Measurement Unit Description                          | 50 |

| MU List of Features                                   | 50 |

| Programmable Current-Sense Amplifiers                 | 50 |

| Measurement Unit Block Diagram                        |    |

| Analog Input Measurement                              |    |

| Analog-to-Digital Converter                           | 53 |

| IC Temperature Measurement                            | 53 |

| Supply Voltage Measurement                            | 53 |

| Measurement Unit Electrical Characteristics           | 54 |

| Protections Description                               |    |

| Introduction                                          |    |

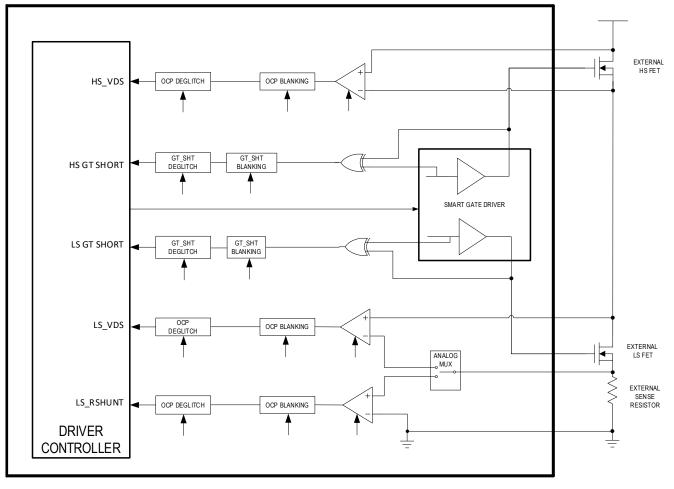

| Driver Protection Diagram                             | 57 |

| Output Stage Overcurrent and Short-Circuit Protection | 57 |

| Gate Protection—VGS Protection                        | 59 |

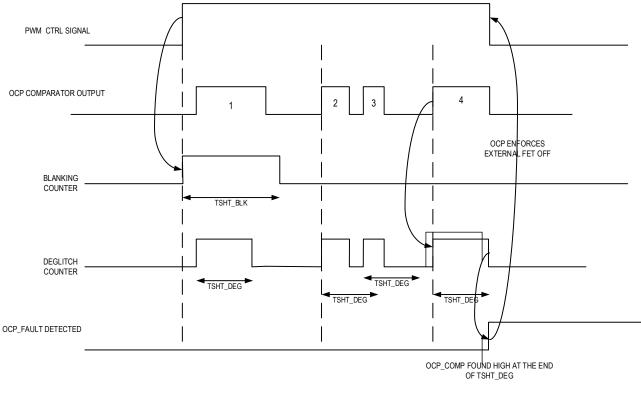

| Blanking and Deglitch                                 | 59 |

| Thermal Protections                                   | 61 |

| Undervoltage Lockout                                  | 61 |

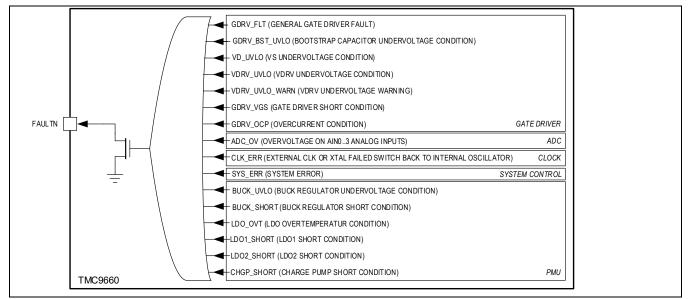

| Fault Pin (FAULTN)                                    | 61 |

| Protections—Electrical Characteristics                | 61 |

| Clock and Control Description                         | 63 |

| Clock                                                 | 63 |

| Crystal Oscillator                                    | 63 |

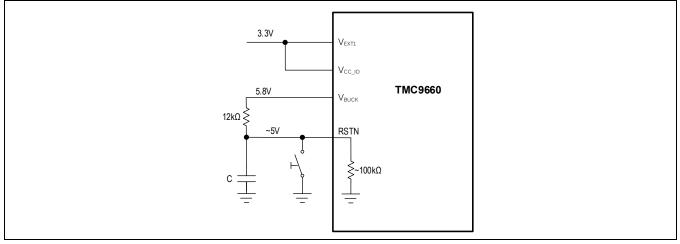

| Reset (RSTN)                                          | 64 |

| Driver Enable (DRV_EN)                                | 64 |

| Wake-Up (WAKE)                                        | 65 |

| FAULT Output (FAULTN)                                 | 65 |

| Clock and Control—Electrical Characteristics          | 65 |

| Bootloader                                            |    |

| Chip Bootstrapping Overview                           |    |

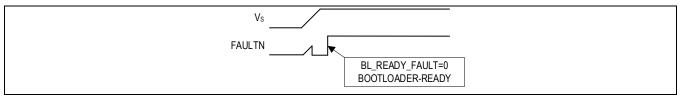

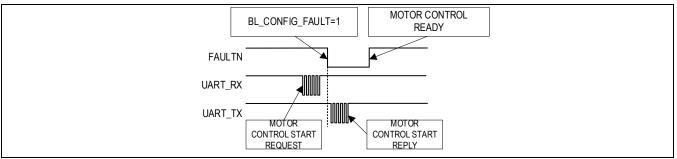

| Bootloader FAULTN Signaling                           |    |

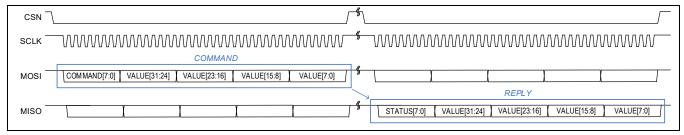

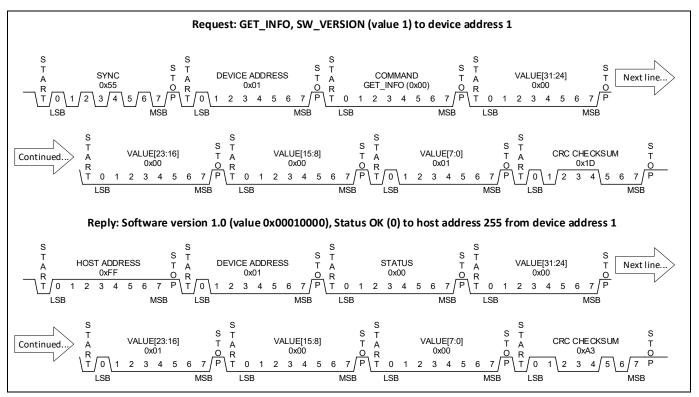

| Communication Protocol                                | 70 |

| UART Communication         |    |

|----------------------------|----|

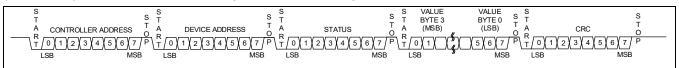

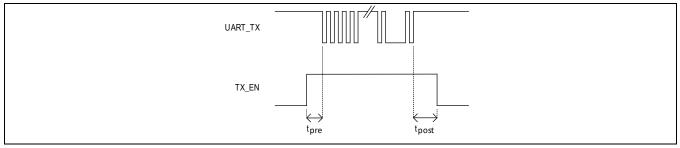

| RS485 Communication        | 71 |

| Bootstrapping RS485        | 71 |

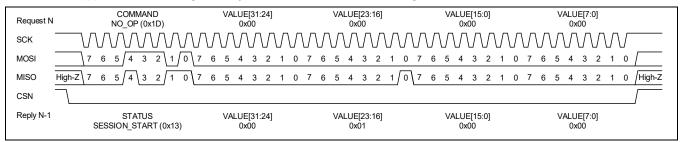

| SPI Communication          |    |

| Memory Access              |    |

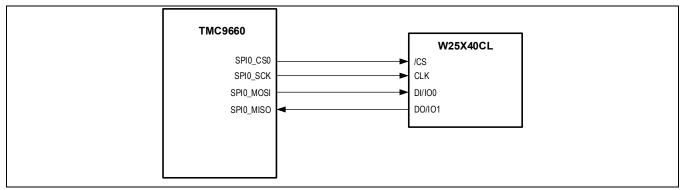

| External Memory            |    |

| External Memory Partitions |    |

| SPI Flash                  |    |

| I <sup>2</sup> C EEPROM    |    |

| OTP Memory                 |    |

| Applications               |    |

| Launching Applications     |    |

| Commands                   |    |

| Command Overview           |    |

| Reply Status Codes         |    |

| GET_INFO                   |    |

| GET_BANK                   |    |

| SET_BANK                   |    |

| GET_ADDRESS                |    |

| SET_ADDRESS                |    |

| READ_32                    |    |

| READ_32_INC                |    |

| READ_16                    |    |

| READ_16_INC                |    |

| READ_8                     |    |

| READ_8_INC                 |    |

| WRITE_32                   |    |

| WRITE_32_INC               |    |

| WRITE_16                   |    |

| WRITE_16_INC               |    |

| WRITE_8                    |    |

| WRITE_8_INC                | 81 |

| NO_OP                      | 81 |

| OTP_LOAD                   |    |

| OTP_BURN                   |    |

| MEM_IS_CONFIGURED          |    |

| MEM_IS_CONNECTED           |    |

| FLASH_SEND_CMD                                | 82 |

|-----------------------------------------------|----|

| FLASH_ERASE_SECTOR                            | 82 |

| MEM_IS_BUSY                                   | 82 |

| BOOTSTRAP_RS485                               | 83 |

| Configuration                                 | 83 |

| Runtime Reconfiguration                       | 83 |

| Configuration Storage                         | 84 |

| Configuration List                            | 84 |

| LDO Configuration                             | 84 |

| Bootstrap Configuration                       | 84 |

| UART Configuration                            | 85 |

| RS485 Configuration                           | 85 |

| SPI Communication Configuration               |    |

| SPI Flash Configuration                       |    |

| I <sup>2</sup> C EEPROM Configuration         | 87 |

| Clock Configuration                           | 87 |

| GPIO Configuration                            | 88 |

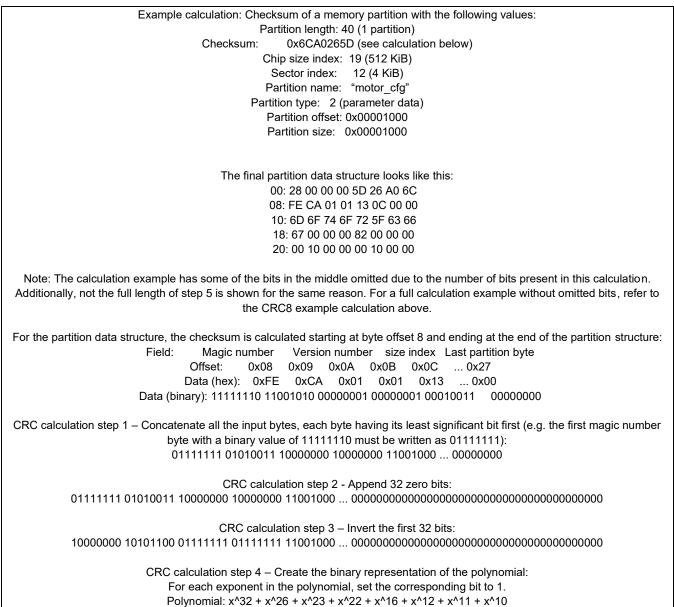

| Checksum Calculations                         |    |

| CRC8 Calculation                              |    |

| CRC32 Calculation Example                     | 91 |

| Applications Information                      |    |

| Bootstrap Capacitor Selection                 | 92 |

| BUCK Recommended Inductor and Capacitor       |    |

| Charge Pump Recommended External Capacitors   | 93 |

| Shunt Resistor Signal Routing                 |    |

| Gate Driver Unit Gate-Signal Routing          | 93 |

| Gate Driver Unit Protection Signal Routing    | 93 |

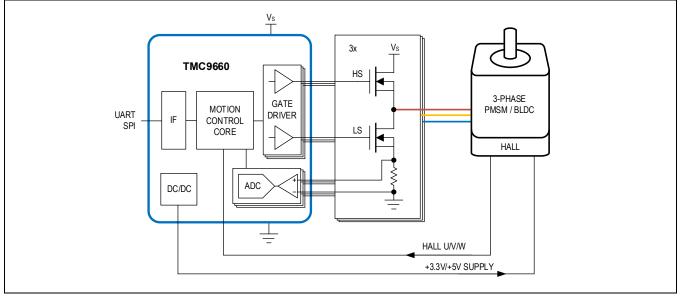

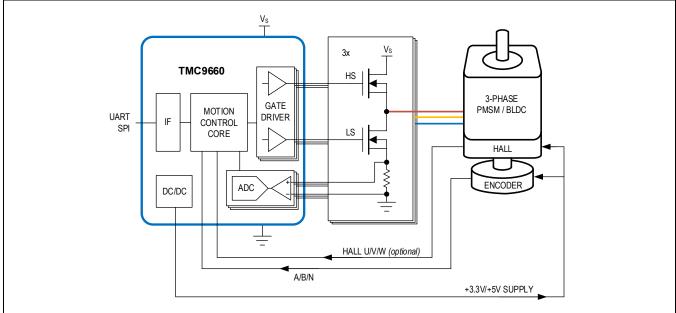

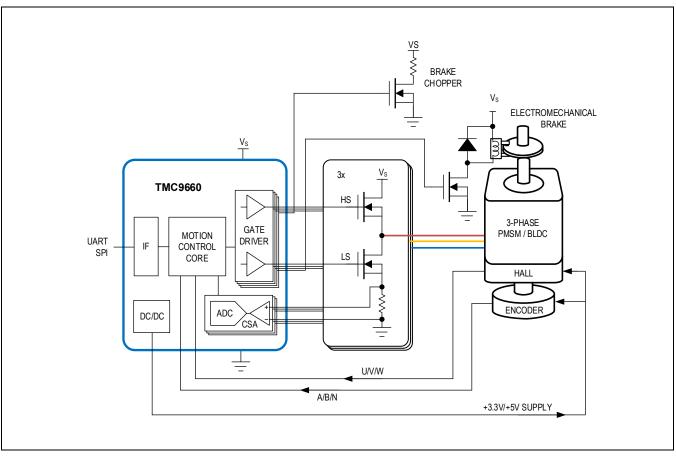

| Typical Application Circuits                  | 94 |

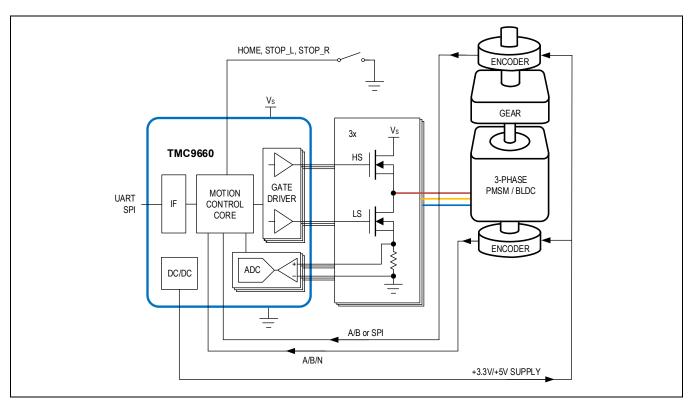

| BLDC/PMSM with Hall Sensor                    | 94 |

| BLDC/PMSM with Encoder                        | 94 |

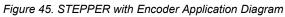

| BLDC/PMSM with Encoder + 2nd Absolute Encoder |    |

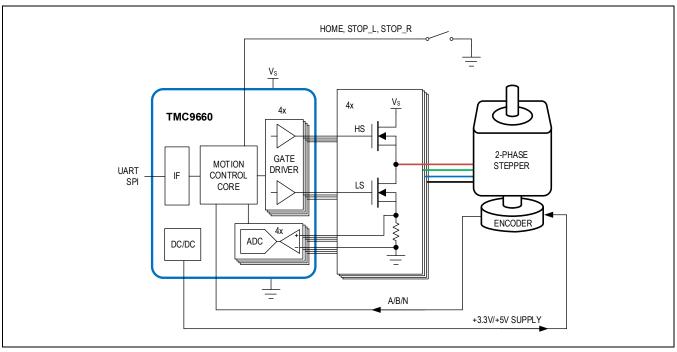

| STEPPER with Encoder                          | 97 |

| Ordering Information                          |    |

| Errata                                        |    |

| Erratum 1: Bootloader OTP_BURN Command        |    |

| Erratum 2: SPI slave MISO operation           |    |

### 70V Smart Gate Driver with Servo (FOC) Controller in HW and Buck Converter

#### LIST OF FIGURES Figure 2. TMC9660 Pinout......11 Figure 3. Detailed Block Diagram ......15 Figure 10. TMC9660 Connected as SPI Peripheral to Application Processor and SPI Communication in Bootloader Figure 21. Gate Driver Sequencer Diagram—Adaptive......45 Figure 28. TMC9660 Clock Options and Clock Tree ......63 Figure 36. UART Example Request and Reply Pair ......71 Figure 37. UART Timing Diagram......71 Figure 38. SPI Datagram Example of the Very First Datagram ......72 Figure 42. BLDC/PMSM with Encoder Application Diagram ......95 Figure 46. SPI Slave Operation, Workaround with External Component ......100

# 70V Smart Gate Driver with Servo (FOC) Controller in HW and Buck Converter

## LIST OF TABLES

| Table 1.  | Recommended Operating Conditions                  | 9  |

|-----------|---------------------------------------------------|----|

| Table 2.  | TMC9660 Supported Features per Application Mode   |    |

| Table 3.  | Alternate Function Mapping                        |    |

| Table 4.  | Peripheral Pin Description                        |    |

| Table 5.  | UART Baud Rates                                   |    |

| Table 6.  | Motor Connection Mapping                          |    |

| Table 7.  | PMU Regulators                                    |    |

| Table 8.  | Isource Table                                     | 43 |

| Table 9.  | I <sub>SINK</sub> Table                           |    |

| Table 10. | RMS Noise vs. Settling Time                       |    |

| Table 11. | Overcurrent Protection Thresholds                 | 58 |

| Table 12. | Overcurrent Protection                            |    |

| Table 13. | Gate Driver Output Protection                     | 59 |

| Table 14. | Blanking and Deglitch Possible Values             | 60 |

| Table 15. | XTAL Output Current vs. Crystal Frequency         |    |

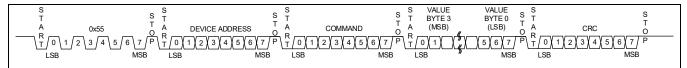

| Table 16. | Bootloader UART Request Communication Byte Format | 70 |

| Table 17. | Bootloader UART Reply Communication Byte Format   | 70 |

| Table 18. | Bootloader SPI Request Communication Byte Format  |    |

| Table 19. | Bootloader SPI Reply Communication Byte Format    | 72 |

| Table 20. | Bootloader Memory Bank Decode                     | 72 |

| Table 21. | External Memory Partition Header Addresses        | 73 |

| Table 22. | External Memory Partition Entry Addresses         | 74 |

| Table 23. | Bootloader Command Overview and Decode            | 76 |

| Table 24. | Bootloader Command GET_INFO Decode                |    |

|           |                                                   |    |

# 70V Smart Gate Driver with Servo (FOC) Controller in HW and Buck Converter

### **Absolute Maximum Ratings**

| $V_{\mbox{S}},V_{\mbox{SA}}$ to GND0.3V to +87.0V                  |

|--------------------------------------------------------------------|

| SW to GND0.3V to $V_{\mbox{VSA}}$ + 0.3V                           |

| $V_{\mbox{\scriptsize BUCK}}$ to GND0.3V to +6.5V                  |

| CPI to GND0.3 V to $V_{\mbox{VBUCK}}$ + 0.3V                       |

| CPO to GNDV_VBUCK - 0.3V to min(V_VDRV + 0.3, V_VBUCK + 6.5)V      |

| $V_{DRV}$ to GND $V_{CPO}$ - 0.3V to min(+13.0, $V_{CPO}$ + 6.5)V  |

| $V_{EXT1},V_{EXT2}$ to GND0.3V to min(+6.0, $V_{VBUCK}$ + 0.3)V    |

| 1V8, A1V8 to GND0.3V to min(+2.2, $V_{\ensuremath{VBUCK}}$ + 0.3)V |

| $V_{\mbox{CC\_IO}}$ to GND0.3V to +6.0V                            |

| GPIO_ to GND0.3V to $~V_{CC\_IO}$ + 0.3V                           |

| AIN_ to GND0.3V to V_CC_IO + 0.3V                                  |

| DRV_EN to GND0.3V to V_CC_IO + 0.3V                                |

| FAULTN, RSTN to GND0.3V to 6V                                      |

| WAKE to GND0.3V to $V_{\mbox{SA}}$ + 0.3V                                                                         |

|-------------------------------------------------------------------------------------------------------------------|

| GNDA, GNDP, EP to GND0.3V to 0.3V                                                                                 |

| BM_ to GND max((BS16) , (V_S - 87)) V to min(V_S + 6, 87)V                                                        |

| BS_ to GND0.3V to min(BM_ + 16, 87)V                                                                              |

| HS_ to GND BM - 0.3V to BS_ + 0.3V                                                                                |

| HS_ to BM0.3V to BS_ + 0.3V                                                                                       |

| LS_ to GND2.7V to V_DRV + 0.3V                                                                                    |

| CSP_ to GND2.7V to 2.7V                                                                                           |

| CSN_ to GND2.7V to 2.7V                                                                                           |

| Gate Driver Source Current (HS_/LS_) Internally limited                                                           |

| Gate Driver Sink Current (HS_/LS_) Internally limited                                                             |

| Continuous Power Dissipation (Multilayer Board) (T <sub>A</sub> = +70°C,<br>derate 43.9 mW/°C above +70°C.)2412mW |

| Operating Temperature Range ( <u>Note 1</u> )40°C to 125°C                                                        |

| Junction Temperature+150°C                                                                                        |

Note 1: Junction temperature greater than +125°C degrades operating lifetimes.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Table 1. Recommended Operating Conditions

| PARAMETER                                                       | SYMBOL             | CONDITION                   | TYPICAL RANGE | UNIT |

|-----------------------------------------------------------------|--------------------|-----------------------------|---------------|------|

| Motor Supply Voltage (V <sub>S</sub> )                          | V <sub>S</sub>     |                             | 7.7 to 70     | V    |

| Core Supply Voltage (V <sub>SA</sub> )                          | V <sub>VSA</sub>   | DCR <sub>LBUCK</sub> <300mΩ | 7.7V to 80.0  | V    |

| Logic Input Supply<br>Voltage                                   | V <sub>CC_IO</sub> |                             | 2.5 to 5      | V    |

| High-Side Gate Drive<br>Current                                 | IGATE_HS           |                             | 0 to 25       | mA   |

| Low-Side Gate Drive<br>Current                                  | IGATE_LS           |                             | 0 to 25       | mA   |

| External Load Current on V <sub>EXT1</sub>                      | IEXT1              |                             | 0 to 150      | mA   |

| External Load Current on V <sub>EXT2</sub>                      | IEXT2              |                             | 0 to 150      | mA   |

| PWM Drive<br>Frequency                                          | FPWM               |                             | 1.83 to 100   | kHz  |

| Trickle Charge Pump<br>Maximum External<br>Load Current per Pin | ITKCHP             |                             | 2             | μΑ   |

| Ambient Temperature<br>Range | ТА |  |  | -40 to 125 | °C |

|------------------------------|----|--|--|------------|----|

|------------------------------|----|--|--|------------|----|

### **Package Information**

| TQFN 64 – 9mm x 9mm                                   |                  |  |  |

|-------------------------------------------------------|------------------|--|--|

| Package Code                                          | T6499+2C         |  |  |

| Outline Number                                        | <u>21-100060</u> |  |  |

| Land Pattern Number                                   | <u>90-100053</u> |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                  |                  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 22.8°C/W         |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 0.69°C/W         |  |  |

For the latest package outline information and land patterns (footprints), go to <u>https://www.analog.com/en/resources/packaging-quality-symbols-footprints/package-index.html</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>https://www.analog.com/en/resources/technical-articles/thermal-characterization-of-ic-packages.html</u>.

# 70V Smart Gate Driver with Servo (FOC) Controller in HW and Buck Converter

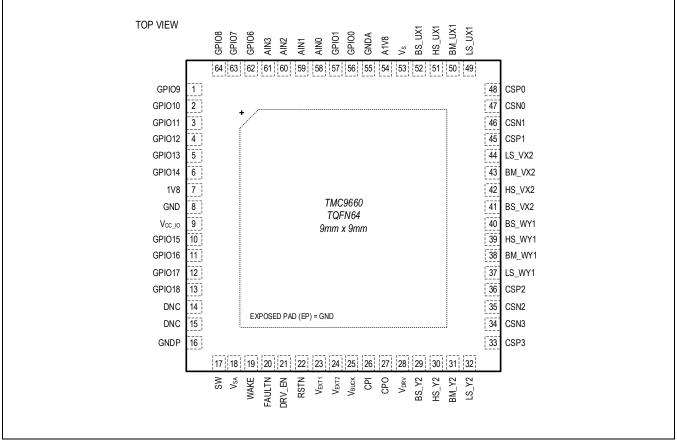

### **Pin Configurations**

The package is a TQFN 64-pin, 0.5mm pitch 9mm x 9mm, and the pins are positioned as follows:

Figure 2. TMC9660 Pinout

# 70V Smart Gate Driver with Servo (FOC) Controller in HW and Buck Converter

# **Pin Descriptions**

| PIN      | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                               | REF<br>SUPPLY | Туре  |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|

| PMU      |                    |                                                                                                                                                                                                                                                                                                                        |               |       |

| 53       | VS                 | Gate Driver Supply Voltage Input. Connect at least a $1\mu$ F V <sub>VS_RNG</sub> rated ceramic capacitor from V <sub>S</sub> to GND as close to the IC as possible.                                                                                                                                                   | VS            | POWER |

| 18       | V <sub>SA</sub>    | Core Circuit and Buck Supply Voltage Input. Connect at least a $0.5\mu$ F V <sub>VSA_RNG</sub> rated low ESL ceramic capacitor from V <sub>SA</sub> to GNDP as close to the IC as possible. Also, place a large $10\mu$ F V <sub>VSA_RNG</sub> rated bypass capacitor close to the IC to limit V <sub>SA</sub> ripple. |               | POWER |

| 17       | SW                 | Buck Switching Output. Connect an inductor $L_{BUCK}$ from SW to $V_{BUCK}$ according to what is recommended in the <u>Applications Information</u> section.                                                                                                                                                           |               |       |

| 25       | VBUCK              | Buck Output Voltage, Charge-Pump and LV LDOs Supply Voltage Input.<br>Connect a ceramic capacitor $C_{VBUCK}$ from $V_{BUCK}$ to GND as close to the IC as possible and according to what is recommended in the <u>Applications</u><br>Information section.                                                            | VBUCK         | POWER |

| 28       | V <sub>DRV</sub>   | Charge-Pump Output Voltage, Gate Driver Supply Voltage Input. OTP programming voltage input. Connect a ceramic capacitor C <sub>VDRV</sub> from V <sub>DRV</sub> to GND as close to the IC as possible and according to what is recommended in the <i>Applications Information</i> section.                            | VDRV          | POWER |

| 26       | CPI                | Charge-Pump Fly Capacitor Low-Voltage Side. Connect a ceramic capacitor $C_{FLY}$ from CPI to CPO as close to the IC as possible and according to what is                                                                                                                                                              |               |       |

| 27       | СРО                | recommended in the Applications Information section.Charge-Pump Fly Capacitor High-Voltage Side. Connect a ceramic capacitorC <sub>FLY</sub> from CPI to CPO as close to the IC as possible and according to what isrecommended in the Applications Information section.                                               |               |       |

| 23       | V <sub>EXT1</sub>  | $5.0V/3.3V/2.5V$ output for supply of external circuits including encoder, sensor, switches, microcontroller, etc. Connect at least $1.6\mu$ F 6V rated ceramic capacitor from V <sub>EXT1</sub> to GND as close to the IC as possible.                                                                                |               |       |

| 24       | V <sub>EXT2</sub>  | $5.0V/3.3V/2.5V$ output for supply of external circuits including encoder, sensor, switches, microcontroller, etc. Connect at least $1.6\mu$ F 6V rated ceramic capacitor from V <sub>EXT2</sub> to GND as close to the IC as possible.                                                                                |               |       |

| 54       | A1V8               | Analog Core Supply Voltage Input. Connect a 10µF 2V rated ceramic capacitor from A1V8 to GND as close to the IC as possible.                                                                                                                                                                                           | A1V8          | POWER |

| 7        | 1V8                | Digital Core Supply Voltage Input. Connect a 10µF 2V rated ceramic capacitor from 1V8 to GND as close to the IC as possible.                                                                                                                                                                                           | 1V8           | POWER |

| 55       | GNDA               | Analog Ground                                                                                                                                                                                                                                                                                                          |               | GND   |

| 16       | GNDP               | Buck Power Ground                                                                                                                                                                                                                                                                                                      |               | GND   |

| 8        | GND                | Ground                                                                                                                                                                                                                                                                                                                 |               | GND   |

| 9        | V <sub>CC_IO</sub> | Logic Supply Voltage Input. Connect a 1 $\mu$ F, at least V <sub>VCCIO_RNG</sub> rated, ceramic capacitor from V <sub>CC_IO</sub> to GND as close to the IC as possible.                                                                                                                                               | VCCIO         | POWER |

| GATE DRI | VER                |                                                                                                                                                                                                                                                                                                                        |               |       |

| 52       | BS_UX1             | Boost Flying Capacitor Connection. Connect a V <sub>DRV</sub> rated ceramic capacitor from BS_UX1 to BM_UX1 as close to the IC as possible for the high-side MOSFET driver supply.                                                                                                                                     |               |       |

| 51       | HS_UX1             | High-Side Gate Driver Output. Driver output for the high-side MOSFET gate.                                                                                                                                                                                                                                             |               |       |

| 50       | BM_UX1             | Source Connection for High-Side MOSFET. Also serves as the return for the high-side driver.                                                                                                                                                                                                                            |               |       |

| 49       | LS_UX1             | Low-Side Gate Driver Output. Driver output for the low-side MOSFET gate.                                                                                                                                                                                                                                               |               |       |

| r          | 1          |                                                                                                                                                                                                                                                                     |       | 1 1      |

|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|

| 41         | BS_VX2     | Boost Flying Capacitor Connection. Connect a $V_{DRV}$ rated ceramic capacitor from BS_VX2 to BM_VX2 as close to the IC as possible for the high-side MOSFET driver supply.                                                                                         |       |          |

| 42         | HS_VX2     | High-Side Gate Driver Output. Driver output for the high-side MOSFET gate.                                                                                                                                                                                          |       |          |

| 43         | BM_VX2     | Source Connection for High-Side MOSFET. Also serves as the return for the high-side driver.                                                                                                                                                                         |       |          |

| 44         | LS_VX2     | Low-Side Gate Driver Output. Driver output for the low-side MOSFET gate.                                                                                                                                                                                            |       |          |

|            |            | Boost Flying Capacitor Connection. Connect a V <sub>DRV</sub> rated ceramic                                                                                                                                                                                         |       |          |

| 40         | BS_WY1     | capacitor from BS_WY1 to BM_WY1 as close to the IC as possible for the high-side MOSFET driver supply.                                                                                                                                                              |       |          |

| 39         | HS_WY1     | High-Side Gate Driver Output. Driver output for the high-side MOSFET gate.                                                                                                                                                                                          |       |          |

| 38         | BM_WY1     | Source Connection for High-Side MOSFET. Also serves as the return for the high-side driver.                                                                                                                                                                         |       |          |

| 37         | LS_WY1     | Low-Side Gate Driver Output. Driver output for the low-side MOSFET gate.                                                                                                                                                                                            |       |          |

| 29         | BS_Y2      | Boost Flying Capacitor Connection. Connect a $V_{DRV}$ rated ceramic capacitor from BS_Y2 to BM_Y2 as close to the IC as possible for the high-side MOSFET driver supply.<br>Note: Tie this pin to $V_{DRV}$ in case HS_Y2 is used to drive a low-side MOSFET gate. |       |          |

| 30         | HS_Y2      | High-Side Gate Driver Output. Driver output for the high-side MOSFET gate.                                                                                                                                                                                          |       |          |

| 31         | BM_Y2      | Source Connection for High-Side MOSFET. Also serves as the return for the high-side driver.<br>Note: Tie this pin to GND in case HS_Y2 is used to drive a low-side MOSFET gate.                                                                                     |       |          |

| 32         | LS_Y2      | Low-Side Gate Driver Output. Driver output for the low-side MOSFET gate.                                                                                                                                                                                            |       |          |

| GATE DRIV  | /ER        |                                                                                                                                                                                                                                                                     |       | 1        |

| CSA        |            |                                                                                                                                                                                                                                                                     |       |          |

| 48         | CSP0       | Channel 0 current-sense amplifier positive analog input. Also serves as the return for the low-side driver.                                                                                                                                                         |       |          |

| 47         | CSN0       | Channel 0 current-sense amplifier negative analog input.                                                                                                                                                                                                            |       |          |

| 45         | CSP1       | Channel 1 current-sense amplifier positive analog input. Also serves as the return for the low-side driver.                                                                                                                                                         |       |          |

| 46         | CSN1       | Channel 1 current-sense amplifier negative analog input.                                                                                                                                                                                                            |       |          |

| 36         | CSP2       | Channel 2 current-sense amplifier positive analog input. Also serves as the return for the low-side driver.                                                                                                                                                         |       |          |

| 35         | CSN2       | Channel 2 current-sense amplifier negative analog input.                                                                                                                                                                                                            |       |          |

| 33         | CSP3       | Channel 3 current-sense amplifier positive analog input. Also serves as the return for the low-side driver.                                                                                                                                                         |       |          |

| 34         | CSN3       | Channel 3 current-sense amplifier negative analog input.                                                                                                                                                                                                            |       |          |

| Other Anal | og         |                                                                                                                                                                                                                                                                     |       |          |

| 56         | GPIO0      | GPIO0 (input with pull-down at power-up)                                                                                                                                                                                                                            | VCCIO | AIDIOpud |

| 57         | GPIO1      | GPIO1 (input with pull-down at power-up)                                                                                                                                                                                                                            | VCCIO | AODIOpud |

| 58         | AIN0       | Analog input 0 (high-Z at power-up)                                                                                                                                                                                                                                 | VCCIO | AIDIOpud |

| 59         | AIN1       | Analog input 1 (high-Z at power-up)                                                                                                                                                                                                                                 | VCCIO | AIDIOpud |

| 60         | AIN2       | Analog input 2 (high-Z at power-up)                                                                                                                                                                                                                                 | VCCIO | AIDIOpud |

| 61         | AIN3       | Analog input 3 (high-Z at power-up)                                                                                                                                                                                                                                 | VCCIO | AIDIOpud |

| GPIO and O | CONTROL SI | GNALS                                                                                                                                                                                                                                                               |       |          |

|            |            |                                                                                                                                                                                                                                                                     |       |          |

| 22 | RSTN                                              | External System Reset Input (active low). The device remains in reset while this pin is in its active state. This pin has an internal pull-down resistor.                                                |        | Dlpd   |

|----|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|

| 14 | DNC                                               | Do not connect – internally connected                                                                                                                                                                    | VICCIO |        |

| 15 | Do not connect—internally connected—or tie to GND |                                                                                                                                                                                                          | VCCIO  |        |

| 21 | DRV_EN                                            | Driver enable input (active high). This pin has an internal pull-down resistor.                                                                                                                          | VCCIO  | Dlpd   |

| 62 | GPIO6                                             | GPIO6 (input with pull-up at power-up)                                                                                                                                                                   | VCCIO  | DIOpud |

| 63 | GPIO7                                             | GPIO7 (input with pull-up at power-up)                                                                                                                                                                   | VCCIO  | DIOpud |

| 64 | GPIO8                                             | GPIO8 (input with pull-up at power-up)                                                                                                                                                                   | VCCIO  | DIOpud |

| 1  | GPIO9                                             | GPIO9 (input with pull-up at power-up)                                                                                                                                                                   | VCCIO  | DIOpud |

| 2  | GPIO10                                            | GPIO10 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 3  | GPIO11                                            | GPIO11 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 4  | GPIO12                                            | GPIO12 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 5  | GPIO13                                            | GPIO13 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 6  | GPIO14                                            | GPIO14 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 10 | GPIO15                                            | GPIO15 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 11 | GPIO16                                            | GPIO16 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 12 | GPIO17                                            | GPIO17 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpud |

| 13 | GPIO18                                            | GPIO18 (input with pull-up at power-up)                                                                                                                                                                  | VCCIO  | DIOpu  |

| 20 | FAULTN                                            | FAULT output signal (open drain). Indicates busy state during bootstrapping<br>or severe error (e.g., 1V8 UVLO) when the integrated processor is not able to<br>communicate error/error details anymore. |        | DOod   |

| 19 | WAKE                                              | Drive this pin high in order to enable power-up and exit from hibernation mode. When WAKE pin is not shorted to $V_{SA}$ , an external pull-down resistor is recommended.                                | VSA    | DI     |

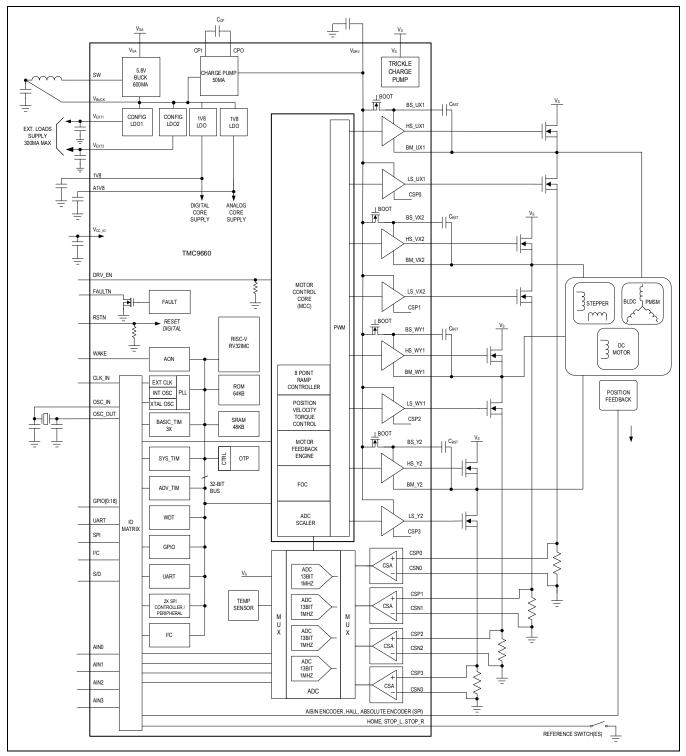

# **Functional Diagrams**

TMC9660

Figure 3. Detailed Block Diagram

### **Application Modes**

The TMC9660 offers two different application modes through its integrated microcontroller – a higher-level parameter mode and a lower-level register mode. Selection of the application mode is part of the chip <u>Chip Bootstrapping</u> sequence.

The register mode offers direct access to the hardware registers without any extra features. The parameter mode offers managed access to the hardware with additional software-backed features extending the system capabilities.

#### Table 2. TMC9660 Supported Features per Application Mode

| FEATURE                                | PARAMETER<br>MODE | REGISTER<br>MODE |

|----------------------------------------|-------------------|------------------|

| FOC motor control in hardware          | Y                 | Y                |

| Hall and ABN feedback                  | Y                 | Υ                |

| Secondary AB feedback                  | Y                 | Ν                |

| SPI encoder feedback                   | Y                 | Ν                |

| BrakeChopper support                   | Y                 | Ν                |

| Mechanical brake support               | Y                 | Ν                |

| StepDir                                | Y                 | Ν                |

| Extended gate driver fault handling    | Y                 | Ν                |

| Communication heartbeat monitoring     | Y                 | Ν                |

| Motor parameter storage                | Y                 | Ν                |

| Script execution from external memory  | Y                 | Ν                |

| Automated GDRV bootstrapping           | Y                 | Ν                |

| Automated ADC calibration              | Y                 | Ν                |

| Configurable supply voltage monitoring | Y                 | N                |

| ABN encoder initialization             | Y                 | N                |

| Basic reference switch support         | Y                 | Y                |

| Automated reference switch homing      | Y                 | Ν                |

#### **Power-Saving Modes**

The TMC9660 offers several options for reducing power consumption by switching off unused blocks. In addition, a hibernation mode is available. Upon entering this mode everything inside the TMC9660 is switched off and put into reset, including the driver stage, the buck regulator, all voltages available externally, the microcontroller part with memory and peripherals, and the analog blocks apart from the always-on (AON) block. The AON block contains its own regulator and internal 32.768kHz oscillator in addition to 16 registers for preserving status information. AON registers content and settings are reset when  $V_{SA}$  is removed. The AON block supports "push button" and timer-based power on. The dedicated WAKE input pin connected to the AON block has to be pulled high in order to enable start up of the device or exit hibernation mode. This pin can withstand voltages up to main supply voltage ( $V_{SA}$ ). In case timer wake-up has been configured, the device automatically powers up again after the predefined amount of time.

The typical power-down/wake-up procedure is as follows:

- Processor configures wake-up method—through external WAKE pin or wake-up timer.

- Processor powers down all components including itself, and the digital part is put into reset/hibernation mode in order to reduce power consumption to minimum.

- Depending on the selection, either a rising edge on the WAKE pin or an overflow of the wake-up timer puts the device out of reset and hibernation mode and powers it up again.

## **Power Supply—Electrical Characteristics**

$(V_{SA} = \text{from 7.7V to 80V}, V_S = \text{from 7.7V to 70V}, V_{CC_IO} = \text{from 2.2V to 5.5V}, L_{BUCK} = 27\mu\text{H DCR}<300\text{m}\Omega$ ,  $C_{BUCK} = 8\mu\text{F}$ , CPP1 = 220nF, CVDRVE = 4.7 $\mu$ F, Junction Temperature = from -40°C to 125°C, Unless otherwise noted, Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                                    | SYMBOL                      | CONDITIONS                                                                                 |                                                 | MIN | TYP  | MAX | UNITS | GL |

|--------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------|-----|------|-----|-------|----|

| OPERATING VOLTAGE                                            | RANGE                       |                                                                                            |                                                 |     | •    |     |       |    |

| Core Supply Voltage<br>Range (V <sub>SA</sub> )              | V <sub>VSA_RNG</sub>        |                                                                                            |                                                 | 7.7 |      | 80  | V     | II |

| Driver Operating<br>Voltage Range (V <sub>S</sub> )          | V <sub>VS_RNG</sub>         | 12V gate drive – B                                                                         | uck = 5.8V                                      | 7.7 |      | 70  | V     | II |

| GPIO Supply Voltage<br>Range (V <sub>CC_IO</sub> )           | V <sub>VCC_IO_RN</sub><br>G |                                                                                            |                                                 | 2.2 |      | 5.5 | V     | II |

| CURRENT CONSUMPT                                             | ION                         |                                                                                            |                                                 |     |      |     |       |    |

|                                                              |                             | PMU, GDU, MU                                                                               | V <sub>VSA</sub> = 24V                          |     | 13   |     |       | VI |

| V <sub>SA</sub> Quiescent Current<br>Consumption             | Ivsa_q                      | and digital core<br>enabled.<br>Quiescent<br>operation (not<br>switching).                 | V <sub>VSA</sub> = 48V                          |     | 10   |     | mA    | VI |

| V <sub>S</sub> Quiescent Current<br>Consumption              | I <sub>VS_Q</sub>           | GDU enabled.<br>Quiescent<br>operation (not<br>switching).                                 | V <sub>VS</sub> = 24V<br>Entire Chip<br>Enabled |     | 2.1  | 3   | mA    | II |

| V <sub>BUCK</sub> Quiescent<br>Current Consumption           | IVBUCK_Q                    | PMU, GDU, MU<br>and digital core<br>enabled.<br>Quiescent<br>operation (not<br>switching). | Entire Chip<br>Enabled                          |     | 36   | 47  | mA    | II |

| V <sub>DRV</sub> Quiescent<br>Current Consumption            | I <sub>VDRV_Q</sub>         | GDU enabled.<br>Quiescent<br>operation (not<br>switching).                                 | V <sub>DRV</sub> = 11.6V                        |     | 1.4  | 2   | mA    | II |

| Quiescent Current<br>Consumption $V_{CC IO}$                 | Ivcc_io                     | GPIOx stable<br>PU disabled                                                                |                                                 |     | 3.8  | 15  | μA    | II |

| V <sub>SA</sub> Current<br>Consumption -<br>Hibernate Mode   | I <sub>VSA_HIB</sub>        | Hard hibernate<br>mode                                                                     | Buck and Driver<br>and Logic shut<br>down.      |     | 12.7 | 40  | μΑ    | 11 |

| V <sub>S</sub> Supply Leakage<br>Current - Hibernate<br>Mode | I <sub>VS_HIB</sub>         | Hard hibernate<br>mode                                                                     | Buck and Driver<br>and Logic shut<br>down.      |     |      | 6   | μΑ    | II |

| GUARANTEE LEVEL | DESCRIPTION                                                                     |

|-----------------|---------------------------------------------------------------------------------|

| I               | Production Tested @ Multiple Temps                                              |

| II              | Production Tested @ Room Temp, Characterized @ Multiple Temps                   |

| llsc            | Production Tested via Scan @ Room Temp, Characterized via Scan @ Multiple Temps |

| 111             | Sample Tested                                                                   |

| IV   | Not Production Tested, Characterized by ATE             |

|------|---------------------------------------------------------|

| V    | Not Production Tested, Characterized by Bench (GBDC)    |

| VI   | Internal Design Target                                  |

| VII  | Production Tested, Internal Only                        |

| VIII | Production Tested @ Hot, Characterized @ Multiple Temps |

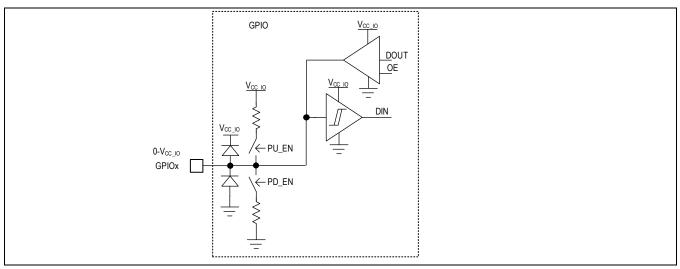

### **General-Purpose Input/Output Description**

The TMC9660 offers 19 general-purpose digital inputs and outputs (GPIO). Each GPIO pin can be configured individually as digital input or as output (push-pull). Inputs can be configured individually with internal pull-up resistors to  $V_{CC\_IO}$  or pull-down resistors to GND. GPIO pins are shared with alternate digital inputs or outputs from peripheral blocks and analog inputs which can be selected per pin.

At power-up, all four analog inputs AIN0-3 are selected as default for pin 58-61 and GPIO configured as inputs for the others. For GPIO0 and GPIO1, internal pull-down resistors are enabled, while for all other GPIO6-18 pull-ups are enabled. Note that the analog inputs do not have pull-up or pull-down enabled. In case these pins are not used, they should be connected to defined voltage levels externally, e.g., GND.

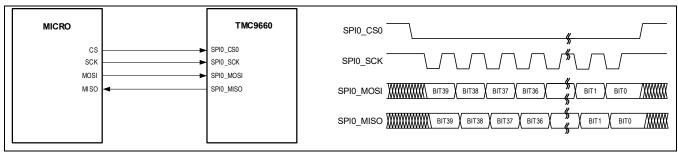

At first-time power-up, the integrated bootloader configures the UART and the SPI peripheral interfaces and accepts commands on either interface. For UART communication, serial data in signal UART\_RX is selected instead of GPIO7 for Pin 63 and serial data out signal UART\_TX instead of GPIO6 for Pin 62. The bootloader listens for any incoming command through UART\_RX. In case a valid command is received, a reply message is sent out through UART\_TX.

For SPI communication, the SPI peripheral block is initialized and listens on SPI0\_MOSI, SPI0\_SCK, and SPI0\_CS0 for incoming data, clock, and chip select signals and switches SPI0\_MISO to output and sends out data as soon as SPI0\_CS0 is pulled down externally. The SPI0\_MISO is selected instead of GPI09 for Pin 1, SPI0\_MOSI instead of GPI010 for Pin 2, SPI0\_SCK instead of GPI011 for Pin 3, and SPI0\_CS0 instead of GPI012 for Pin 4.

The bootloader supports selection of alternate pin functionality according to application circuit requirements. The configuration may be written to internal OTP memory for permanent storage. This configuration is then used as default for all future power-ups.

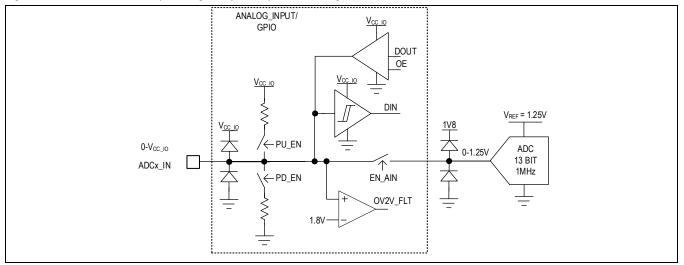

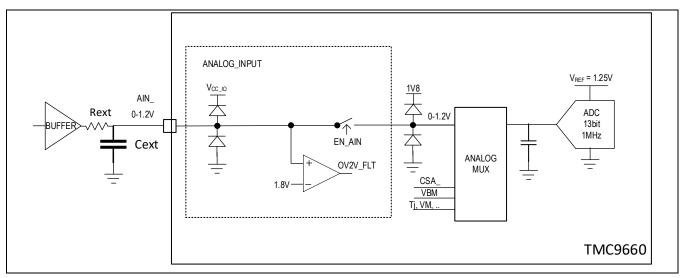

*Figure 4* and *Figure 5* show the equivalent input diagram for a GPIO and an analog input GPIO. When the pin is configured as analog input, its range is limited to 0V to 1.2V and if more than 1.8V is applied to the analog pin, the analog switch is open to avoid damages at the ADC and a fault is triggered.

| PIN | AF0 (DEFAULT*)               | AF1         | AF2          | AF3         | AF4    |

|-----|------------------------------|-------------|--------------|-------------|--------|

| 56  | GPIO0 (input with pull-down) | OSC_IN      | CLK_IN       | UART_TX     |        |

| 57  | GPIO1 (input with pull-down) | OSC_OUT     | UART_RX      |             | ENC_B  |

| 58  | AIN0                         | GPIO2       | UART_TXEN    | STOP_L      | HALL_U |

| 59  | AIN1                         | GPIO3       | TIM_ADV_OUT1 | STOP_R      | HALL_V |

| 60  | AIN2                         | GPIO4       | I2C_SCL      | HOME        | HALL_W |

| 61  | AIN3                         | GPIO5       | I2C_SDA      | ENC_A       |        |

| 62  | GPIO6 (input with pull-up)   | UART_TX*    | TIM_ADV_IN0  | SPI0_SCK    |        |

| 63  | GPIO7 (input with pull-up)   | UART_RX*    | TIM_ADV_IN1  | HOME        | HALL_U |

| 64  | GPIO8 (input with pull-up)   | UART_TXEN   | SPI0_CS1     | ENC_A       | HALL_W |

| 1   | GPIO9 (input with pull-up)   | SPI0_MISO*  | TIM_ADV_IN2  |             | HALL_U |

| 2   | GPIO10 (input with pull-up)  | SPI0_MOSI*  | TIM_ADV_OUT0 |             | HALL_W |

| 3   | GPIO11 (input with pull-up)  | SPI0_SCK*   | I2C_SDA      | TIM_ADV_IN1 |        |

| 4   | GPIO12 (input with pull-up)  | SPI0_CS0*   | I2C_SCL      | STOP_L      |        |

| 5   | GPIO13 (input with pull-up)  | SPI0_CS1    | I2C_SCL      | ENC_B       |        |

| 6   | GPIO14 (input with pull-up)  | I2C_SDA     | SPI1_SCK     | ENC_N       |        |

| 10  | GPIO15 (input with pull-up)  | TIM_ADV_IN0 | SPI1_CS0     | HOME        | HALL_V |

| 11  | GPIO16 (input with pull-up)  | TIM_ADV_IN1 | SPI0_CS2     | STOP_L      | ENC_N  |

### Table 3. Alternate Function Mapping

| 13 GPIO18 (input with pull-up) TIM0 BASIC PWM SPI1 MOSI STOP R ENC B | 12 | GPIO17 (input with pull-up) | TIM_ADV_IN2    | SPI1_MISO | ENC_A | HOME  |

|----------------------------------------------------------------------|----|-----------------------------|----------------|-----------|-------|-------|

|                                                                      | 13 | GPIO18 (input with pull-up) | TIM0_BASIC_PWM | SPI1_MOSI |       | ENC_B |

\*Defaults in hardware are overridden by the bootloader on power-up.

## Table 4. Peripheral Pin Description

| PIN GROUP                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO018                                                                       | General Purpose Digital Inputs and Outputs. These signals can be set to input with optional pull-up or pull-down resistor or digital output (push-pull).<br>In parameter mode, the two-point hysteresis-based control signal for an external brake chopper circuit for limiting the supply voltage can be configured for any available GPIO output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AIN03                                                                         | Analog inputs connected to the ADC inputs of the measurement unit (MU). It is sampled with current motor pulse-width modulation (PWM) frequency. Values are available through the motor control core (MCC).<br>The parameter mode supports external temperature sensor needs to be connected to AIN3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OSC_IN, OSC_OUT                                                               | Connect a crystal between these two pins when using an external crystal oscillator instead of the internal oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLK_IN                                                                        | External clock input when using an external clock instead of the internal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UART_TX, UART_RX,<br>UART_TXEN                                                | UART serial transmit data out (Tx) and receive data in (Rx). For half-duplex operation, the transmitter enable signal (TxEN) may be connected to an external transceiver (e.g., RS485). The UART interface may be used for communication with the application processor (bootloader configuration).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I2C_SCL, I2C_SDA                                                              | I <sup>2</sup> C interface, controller mode with clock output only. An I <sup>2</sup> C EEPROM may be connected externally for program and parameter storage (bootloader configuration).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| STOP_L, STOP_R,<br>HOME                                                       | Stop left/right and Home switch inputs connected to the internal 8-point ramp generator of the MCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ENC_A, ENC_B,<br>ENC_N                                                        | Incremental encoder A/B/N input channels connected directly to the feedback engine of the internal MCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| HALL_U, HALL_V,<br>HALL_W                                                     | Hall sensor U/V/W input channels connected directly to the feedback engine of the internal MCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TIM_ADV_IN0,<br>TIM_ADV_IN1,<br>TIM_ADV_IN2,<br>TIM_ADV_OUT0,<br>TIM_ADV_OUT1 | Inputs and Outputs of the advanced timer peripheral block. In parameter mode,<br>TIM_ADV_IN0/TIM_ADV_IN1 can be configured as Step/Direction inputs or<br>TIM_ADV_IN0/TIM_ADV_IN1 as second incremental encoder A/B channel inputs with<br>processor/software support (parameter mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TIM0_BASIC_PWM,<br>TIM_ADV_OUT0,<br>TIM_ADV_OUT1                              | In parameter mode, the PWM control signal for an external electromagnetic brake driver can be configured for one of the timer outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SPI0_MISO,<br>SPI0_MOSI,<br>SPI0_SCK, SPI0_CS0,<br>SPI0_CS1, SPI0_CS2         | SPI block 0 supporting controller mode (SPI0_MISO: serial data in, SPI0_MOSI: serial data out,<br>SPI0_SCK: clock output, SPI0_CSx: chip select outputs/low active). An SPI flash memory may be<br>connected externally for program and parameter storage (bootloader configuration). In parameter mode,<br>this interface may be used for connecting an external absolute encoder with SPI with processor/software<br>support (parameter mode).<br>Note: SPI block 0 may be replaced with SPI peripheral block. In this case, signals change direction<br>(SPI0_MISO: serial data output, SPI0_MOSI: serial data input, SPI0_SCK: clock input and SPI0_CS0:<br>chip select input). This interface may be used for communication with the application processor as fast<br>alternative to UART communication (bootloader configuration).<br>For an SPI-Flash connection, chip select signal generation is done in software for more flexibility. Any<br>available GPIO pin may be configured as chip select signal and not just the dedicated signals supported<br>by the SPI peripheral block 0 in hardware (SPI0_CSx). |

| SPI1_MISO,<br>SPI1_MOSI,<br>SPI1_SCK, SPI1_CS0                                | SPI block 1 supporting controller mode (SPI1_MISO: serial data in, SPI1_MOSI: serial data out,<br>SPI1_SCK: clock output, SPI1_CS0: chip select output/low active). An SPI flash memory may be<br>connected externally for program and parameter storage (bootloader configuration). In parameter mode,<br>this interface may be used for connecting an external absolute encoder with SPI with processor/software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| support (parameter mode).<br>Note: SPI block 1 may be replaced with SPI peripheral block. In this case, signals change direction<br>(SPI1_MISO: serial data output, SPI1_MOSI: serial data input, SPI1_SCK: clock input and SPI1_CS0:<br>chip select input). This interface may be used for communication with the application processor as fast<br>alternative to UART communication (bootloader configuration). |

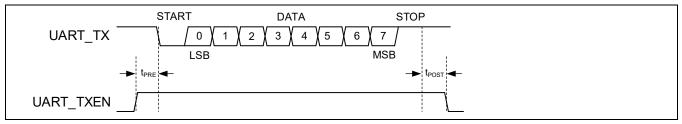

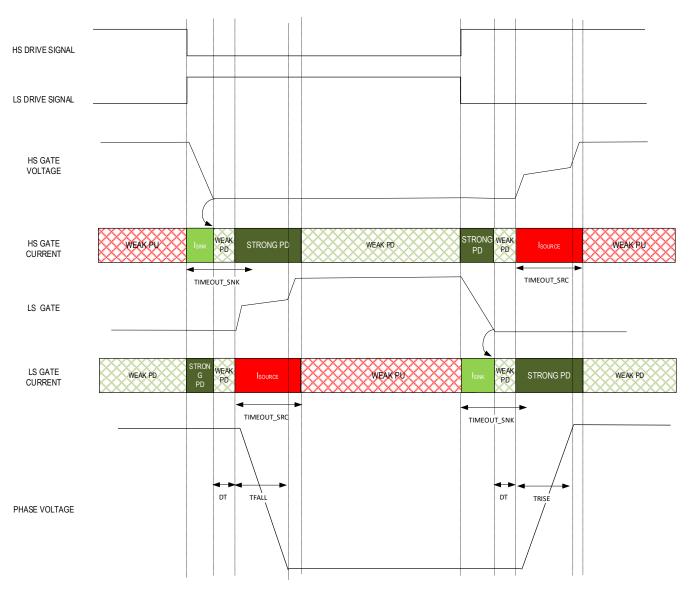

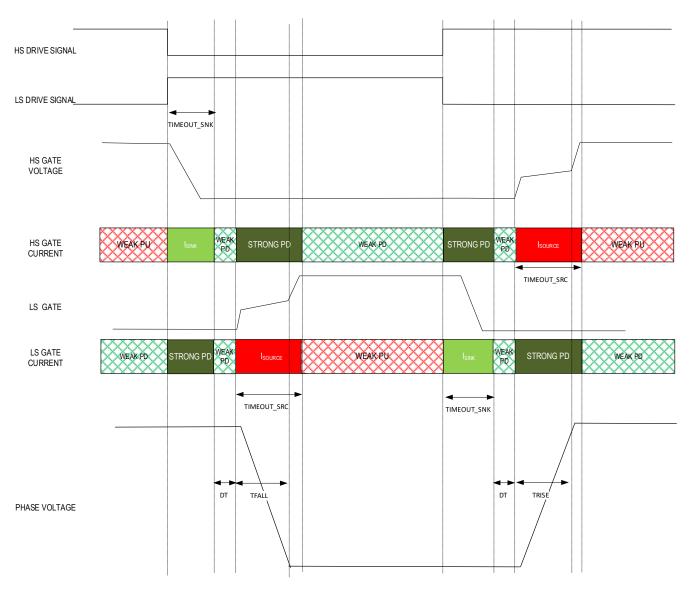

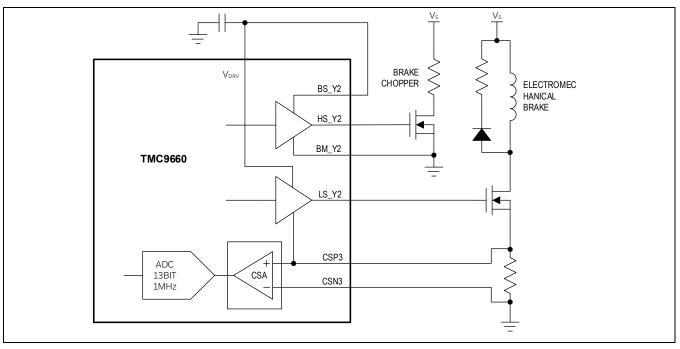

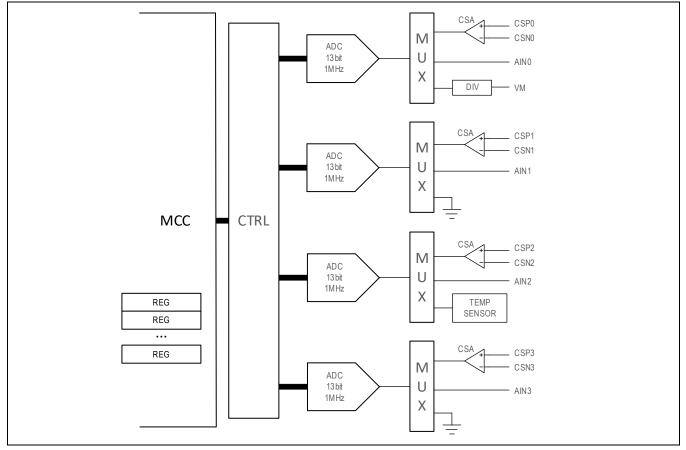

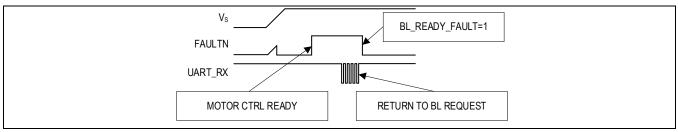

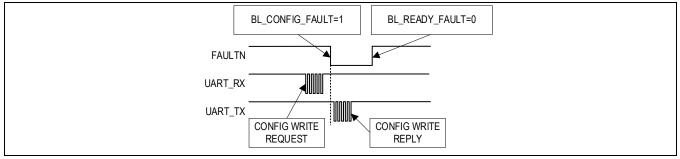

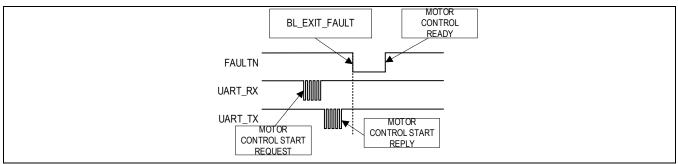

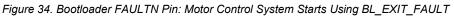

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|