# Wide Input Range Buck Converter

# With Integrated Synchronous 2-Switchs

#### 1. Features

- Wide Input Voltage Range from 4V to 32V

- Programmable Vout Range from 0.8V to 30V

- Peak Current Mode Control

- Integrated Two low Rdson N-MOSFETs

- Adjustable Cycle-by-Cycle Current Limit by ILIM

- Adjustable Frequency: 100kHz~1MHz

- External Soft-Start Limits the Input Inrush Current

- Selectable FCCM or DCM with Pulse Skipping

- Cable Impedance Compensation

- Low Dropout Operation with Maximum Duty Cycle at 99.5%

- Input Under-Voltage Lockout

- Output OCP, SCP, OVP

- Thermal Shutdown

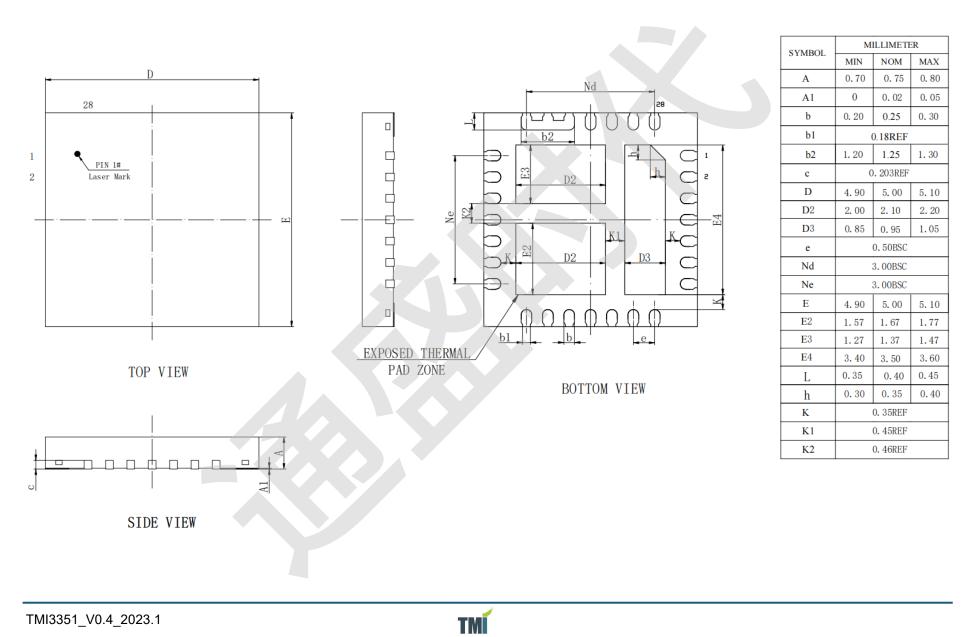

- QFN-28 Package, 5mm×5mm×0.75mm

#### 2. Applications

- USB Power Delivery Supply

- Car Charger

- USB Dedicated Charging Port

- Type-C Docks/Adapters

- Computer Peripherals

#### 3. Description

The TMI3351 is an integrates 2-switchs synchronous buck converter mainly for widely varying input step-down regulator applications. The control method is based upon current mode control that enables maximum performance under transient conditions. The output voltage can be programmed by the FB pin. It operates as a Buck mode while the input voltage is sufficiently greater than the regulated output voltage and transitions to the low dropout operation mode with maximum duty cycle at 99.5% as the input voltage very approaches the output voltage.

It also features an adjustable soft-start function and cable impedance compensation function and offers protection features including input UVLO, cycle-by-cycle current limit, over power protection (OPP), output short protection (SCP) or OVP and thermal shutdown. In addition, it features selectable Forced Continuous Conduction Mode (FCCM) or Discontinuous Conduction Mode (DCM) operation for light load condition.

The TMI3351 is available in compact QFN5x5-28.

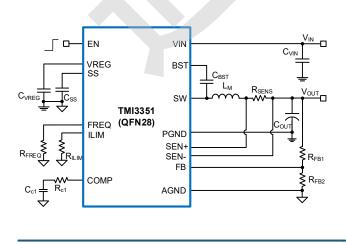

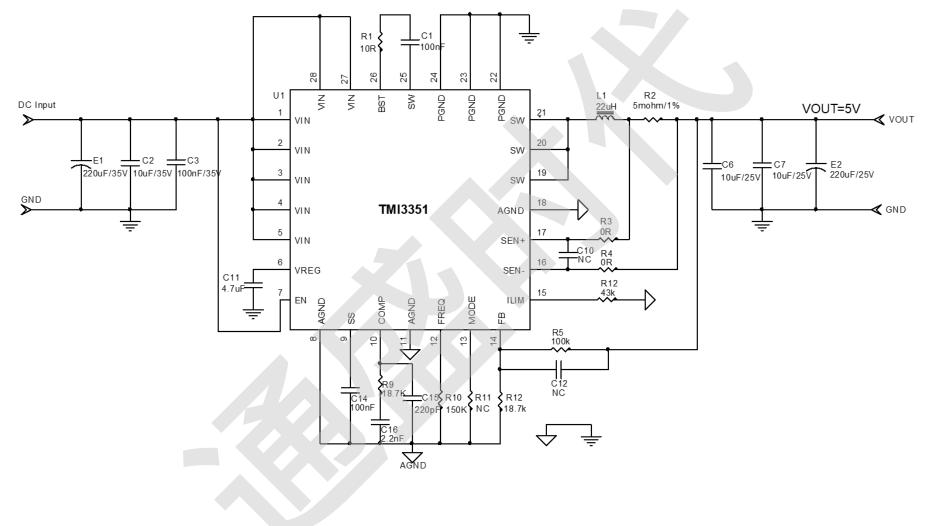

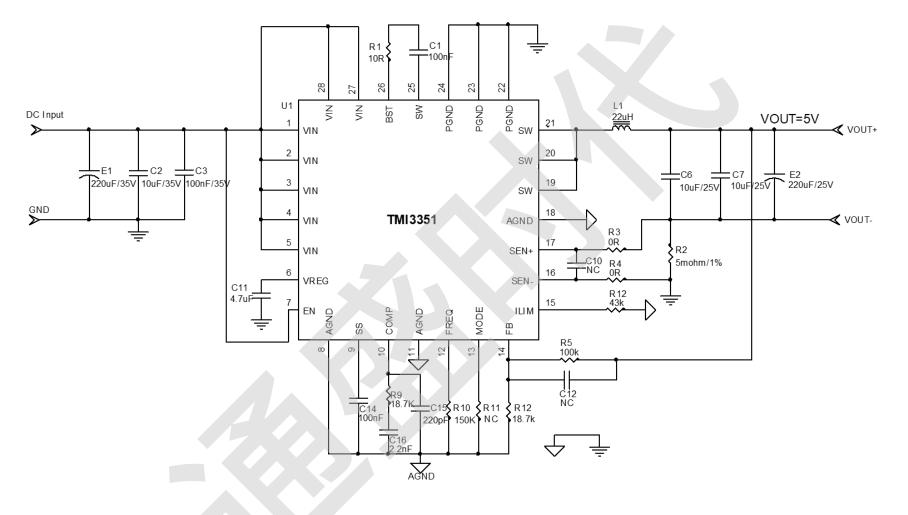

#### 4. Typical Application Circuit

#### TMI3351\_V0.4\_2023.1

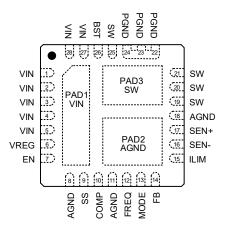

#### 5. Pin Configuration

TM

# 6. Ordering Information

| Part Number | Package                       | Top Marking <sup>1</sup> | Quantity / Reel |

|-------------|-------------------------------|--------------------------|-----------------|

|             |                               | T3351                    | 2000            |

| TMI3351     | 3351 QFN-28 (5mm x 5mm) XXXXX | XXXXX                    | 3000            |

Note: 1. T3351: Device Code, 2. XXXXX: Inside Code

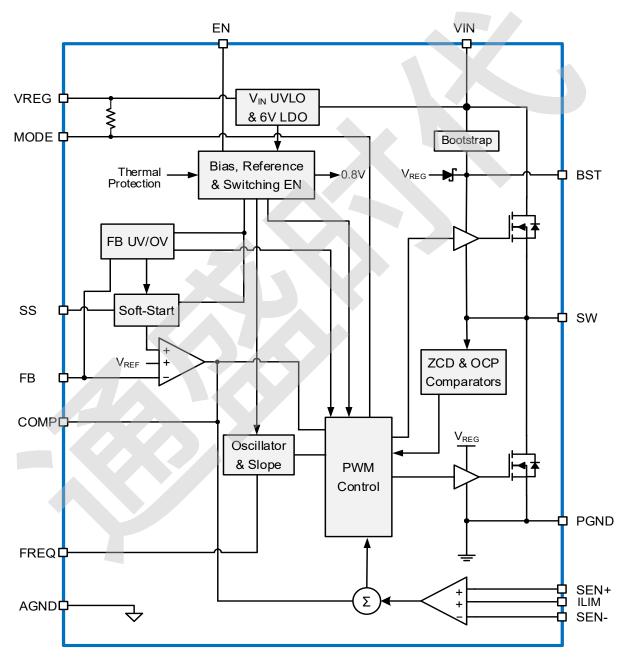

# 7. Block Diagram

Figure 1. TMI3351 Block Diagram

# 8. Pin Description

| Pin NO.                      | Pin<br>Name | Description                                                                                                                                                                                                                                                                                                    |  |

|------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1,2,3,4,5,<br>27,28,<br>PAD1 | VIN         | Power supply input pin. Must bypass with a low ESR ceramic capacitor. Place cap as close to the IC as possible.                                                                                                                                                                                                |  |

| 6                            | VREG        | Output pin of the internal 6V bias regulator. Locally decouple to PGND using a low ESR/ESL capacitor located as close to the IC as possible.                                                                                                                                                                   |  |

| 7                            | EN          | Enable control pin, logic high enable. This pin has an internal $1M\Omega$ resistor to ground.                                                                                                                                                                                                                 |  |

| 8,11,18,<br>PAD2             | AGND        | Analog ground pin. It is internally connected to the sensitive analog ground circuitry. The exposed pad must be soldered to the PCB ground plane. It serves as a means of conducting heat way from the IC.                                                                                                     |  |

| 9                            | SS          | Soft-Start control pin. This pin is used to program soft-start period with an external connect a capacitor. A 100nF is recommended from this pin to ground.                                                                                                                                                    |  |

| 10                           | COMP        | Output of the error amplifier, input to the PWM comparator. A RC network is connected from this pin to AGND to compensate the overall loop.                                                                                                                                                                    |  |

| 22,23,24                     | PGND        | Power ground pin. The power ground copper needs to be connected to these pins.                                                                                                                                                                                                                                 |  |

| 12                           | FREQ        | Switching frequency program pin. A resistor to ground sets the frequency from 100kHz to 1MHz.                                                                                                                                                                                                                  |  |

| 13                           | MODE        | Mode selection pin for light load. When this pin voltage is higher than 2.5V, the converter is set<br>as PFM mode. This pin is internal resistor pulled up to VREG and can be left floating default<br>for PFM operation. When the MODE pin is pulled to low, the forced continuous current mode<br>is active. |  |

| 14                           | FB          | The Buck output feedback pin. Connect this pin to output through a resistor divider.                                                                                                                                                                                                                           |  |

| 15                           | ILIM        | Current program pin. A resistor to ground sets the peak current limit and average current limit.                                                                                                                                                                                                               |  |

| 16                           | SEN-        | Negative input for the current sense. The sensed inductor current limit threshold is determined by voltage of ILIM pin.                                                                                                                                                                                        |  |

| 17                           | SEN+        | Positive input for the current sense. The sensed inductor current limit threshold is determined by voltage of ILIM pin.                                                                                                                                                                                        |  |

| 19,20,21,<br>25, PAD3        | SW          | The Buck switching node pin.                                                                                                                                                                                                                                                                                   |  |

| 26                           | BST         | Buck high-side MOSFET $M_T$ driver supply pin. Connect a 100nF capacitor (C <sub>BST</sub> ) and a 10 $\Omega$ resistor between this pin and the SW pin.                                                                                                                                                       |  |

## 9. Absolute Maximum Ratings<sup>1</sup>

|                                                              | Parameters                      | Symbol                         | Value                       |  |

|--------------------------------------------------------------|---------------------------------|--------------------------------|-----------------------------|--|

| Maximur                                                      | n Input voltage                 | VIN, EN                        | 32V                         |  |

| Voltage on pins with respect to ground                       |                                 | SW                             | -0.3V (-4V for <20ns) ~ 32V |  |

|                                                              |                                 | VREG                           | -0.3V to 6.5V               |  |

|                                                              |                                 | BST                            | (Vsw-0.3V) to (Vsw+6.5V)    |  |

|                                                              |                                 | SEN+, SEN-                     | -0.3V to 25V                |  |

|                                                              |                                 | SS, COMP, ILIM, FREQ, MODE, FB | -0.3V to 6.5V               |  |

| Maximum operating junction temperature <sup>2</sup>          |                                 | +150°C                         |                             |  |

| Storage temperature                                          |                                 | -55°C to +150°C                |                             |  |

| Thermal resistance of junction to case, $\theta_{JC}^3$      |                                 | 15 °C/W                        |                             |  |

| Thermal resistance of junction to ambient, $\theta_{JA}{}^3$ |                                 | 40 °C/W                        |                             |  |

| ESD <sup>4</sup>                                             | All pads, according to human-bo | 2kV                            |                             |  |

|                                                              |                                 | del, JEDEC STD 22, method C101 | 500V                        |  |

- **Note:** 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Not to exceed the maximum junction temperature of the IC, which relate to the power consumption of the IC and the thermal resistance of the IC package. For a typical application (refer to the Block Diagram, Page 2), the power consumption of the IC comprises the operation power of the IC. The operation power of the IC can be calculated by  $P_D=V_{IN}\times I_{IN}$ , where  $V_{IN}$  represents the voltage at the VIN pin and  $I_{IN}$  represents the IC operation current of internal control and driver circuitry.

- 3. Measured on JESD51-7, 4-layer PCB

- 4. CAUTION: ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

#### **10. Recommended Operating Conditions**

| Parameter                                           | Value           |

|-----------------------------------------------------|-----------------|

| Input supply voltage                                | 4V to 30V       |

| Output voltage                                      | 0.8V to 30V     |

| Operating ambient temperature range, T <sub>A</sub> | -40°C to +85°C  |

| Operating junction temperature range, TJ            | -40°C to +125°C |

# **11. Electrical Characteristics**

| Symbol              | Parameter                                | Test Conditions                                                                | Min   | Тур  | Max    | Unit |

|---------------------|------------------------------------------|--------------------------------------------------------------------------------|-------|------|--------|------|

| Supply Vo           | Itage (VIN Pin)                          |                                                                                |       |      |        | •    |

| VINON               | Turn-on threshold voltage                | V <sub>IN</sub> rising                                                         | 3.6   | 4.0  | 4.25   |      |

| VINOFF              | Turn-off threshold voltage               | V <sub>IN</sub> falling                                                        | 3.3   | 3.5  | 3.75   | V    |

| I <sub>SHDN</sub>   | VIN shutdown current                     | $V_{IN}$ rising, $V_{IN}$ =24V, $V_{EN}$ =0V                                   | _     | -    | 5      | φμA  |

| la                  | VIN standby current                      | V <sub>IN</sub> =24V, V <sub>FB</sub> =2.0V, No switching                      | _     | -    | 1.3    | mA   |

| 6V Interna          | I Regulator (VREG Pin)                   |                                                                                |       |      |        | •    |

|                     | 6V internal regulator output             | I <sub>VREG</sub> =1mA, V <sub>IN</sub> ≥7V,                                   | 5.7   | 6    | 6.3    | V    |

| Vreg                | voltage                                  | I <sub>VREG</sub> =1mA, V <sub>IN</sub> =4.0V                                  | -     | 3.95 | -      | V    |

| CVREG               | Output capacitor range                   |                                                                                | -     | 4.7  |        | μF   |

| Enable Lo           | gic Control (EN pins)                    |                                                                                |       |      |        | •    |

| $V_{ENH}$           | Enable pins logic high (enabled)         | When V <sub>ENH</sub> ≥1.2V, it is enabled;                                    | 1.2   | -    | _      |      |

| VENL                | Enable pins logic low (disabled)         | When V <sub>ENH</sub> ≤0.4V, it is disabled.                                   | -     | -    | 0.4    | V    |

| Internal O          | scillator (FREQ pin)                     |                                                                                |       |      |        |      |

| f <sub>SW_LOW</sub> | Lowest switching frequency               |                                                                                | _     | _    | 100    | kHz  |

| fsw_ніgн            | Highest switching frequency              |                                                                                | 1000  | -    | _      | kHz  |

| fsw                 | Operating frequency                      | R <sub>FREQ</sub> =107kΩ                                                       | 170   | 200  | 230    | kHz  |

| D <sub>MAX</sub>    | Maximum duty cycle                       |                                                                                | _     | 99.5 | _      | %    |

| Error Amp           | blifier                                  |                                                                                |       |      |        |      |

|                     |                                          | TJ=25°C                                                                        | 0.784 | 0.80 | 0.816  |      |

| Vref_fb             | Feedback reference voltage               | T <sub>J</sub> = -40°C to 125°C                                                | 0.776 | 0.80 | 0.824  | V    |

| Soft-Start          |                                          |                                                                                |       |      |        |      |

| Iss                 | Soft-start source current                | SS = 0.8V                                                                      | 2     | 4    | 6      | μA   |

| Output Vo           | Itage Monitor                            |                                                                                |       |      |        |      |

| Vfb_ovp             | FB OVP rising threshold                  | FB pin, measured with respect to $V_{\text{REF}}$                              | 115%  | 118% | 122.5% | VREF |

| Vfb_rovp            | OVP fault return threshold               | FB pin, measured with respect to $V_{\text{REF}}$                              | _     | 102% | -      | VREF |

| Over-Curr           | ent Limit (OCL)                          | 1                                                                              | 1     | 1    | 1      | 1    |

| I <sub>OCL</sub>    | Cycle-by-cycle of inductor current limit | R <sub>ILIM</sub> = 40kΩ, R <sub>FREQ</sub> =87.6kΩ<br>R <sub>SENSE</sub> =7mΩ | _     | 10   | _      | А    |

All specifications below are at ambient 25°C, VIN= 5V to 30V, unless otherwise noted.

# 11. Electrical Characteristics (Continued)

All specifications below are at ambient 25°C,  $V_{IN}$ = 5V to 30V, unless otherwise noted.

| Symbol            | Parameter                                             | Test Conditions | Min | Тур | Max | Unit |

|-------------------|-------------------------------------------------------|-----------------|-----|-----|-----|------|

| Power MO          | Power MOSFET                                          |                 |     |     |     |      |

| Rмт               | High-side MOSFET static<br>drain-source on-resistance |                 | _   | 10  | _   | mΩ   |

| R <sub>мв</sub>   | Low-side MOSFET static drain-source on-resistance     |                 | -   | 8   | -   | mΩ   |

| Thermal Shutdown  |                                                       |                 |     |     |     |      |

| TSHDN             | Thermal shutdown trip threshold                       |                 | _   | 160 | _   |      |

| $\Delta T_{SHDN}$ | Thermal shutdown hysteresis                           |                 | -   | 20  | _   | °C   |

#### 12. Operational Description

The TMI3351 is an integrates two low Rdson N-MOSFETs synchronous buck converter. The buck converter utilizes peak current mode control for instant transient response and easier compensation over the 4 to 30V supply range. There is an external soft-start, and a MODE pin to select between DCM mode and FCCM mode for light load condition. The TMI3351 also features include UVLO, OCP, OPP, OVP, SCP, TSDN. Refer to Block Diagram for the following discussions. All parameters mentioned below are typical values.

### 12.1 Under-voltage Lockout

When VIN pin voltage is below the turn-on threshold, the device is held in a low power shutdown mode, drawing less than  $5\mu$ A from the VIN pin. Once VIN is above the turn-on threshold, the internal bias rails and the VREG regulator are enabled. The PWM controller commences operation when the output of internal M<sub>T</sub> bootstrap is established. A minimum hysteresis of 500mV on VIN pin provides hysteresis that prevents abnormal shutdown due to line voltage transient drop during power on period.

#### **12.2 VREG Internal Regulator**

The TMI3351 devices provide an internal 6V LDO using input from VIN. When  $V_{IN}$  exceeds 4.0V, the internal LDO regulator is enabled. The  $V_{REG}$  voltage provides bias voltage for the internal analog circuitry and also provides supply voltage for the gate drives.

For  $V_{IN}$  less than 6V, the  $V_{REG}$  tracks  $V_{IN}$  with a small voltage drop. The dropout voltage of VREG with 20mA load current is maximum 300mV when  $V_{IN}$ =4V.

### 12.3 Peak Current Mode Control with Slope Compensation

The TMI3351 implement peak current mode control. It provides fast transient response, cycle-by-cycle current limiting, and ease of loop compensation. The controller provides internal slope compensation to ensure stable operation with a duty cycle greater than 50%.

#### 12.4 Operating Mode

TMI3351 works in forced PWM mode at connect MODE pin to GND. In FCCM condition, buck on-time is determined by internal circuit to get a constant switching frequency based on  $V_{IN}/V_{OUT}$  ratio. This forces inductor current works in continuous mode with constant frequency, can produce lower output voltage ripple, but the efficiency is low at light load condition because of the high switching loss.

It works in DCM mode at connect MODE pin to high than 2.5V. In DCM mode, the efficiency can be improved under light load condition, but the output voltage ripple will be larger than FCCM, it also works with constant switching frequency under heavy load condition, when the load is light or no-load, the controller will enter pulse skipping mode.

# 12.5 Synchronous MOSFET

The TMI3351 contains two internal NMOS switch. The gate driver circuit of high side MOSFET works in conjunction with an internal diode and an external bootstrap capacitor. A 100nF or larger ceramic capacitor, connected with short traces between the BST pin and SW pin is recommended. During the off-time of top-side MOSFET, the SW pin voltage is approximately 0V and the bootstrap capacitor charges from V<sub>REG</sub> through the internal bootstrap diode. When operating with a high PWM duty cycle, the top-side switch will be forced off if it turns on time above maximum on time, to ensure that the bootstrap capacitor is recharged.

When TMI3351 commences operation from cold-start or wakes up from pulse-skipping mode, it will firstly turn on the bottom-side MOSFETs  $M_{B^{+}}$  and last till both of the (BST-SW) voltage above 2.5V. This ensures that the

TTM 拓尔微电子 TOLL Microelectronic

top-side MOSFETs M<sub>T</sub>, gate driver power supply rail is sufficiently.

#### 12.6 Soft-Start

The controller features a programable soft-start function, which reduces inrush current and overshoot of the output voltage. When the power on, the internal circuitry generates a soft-start voltage ramping up from 0V to VREG. When it is lower than the reference voltage, SS voltage overrides FB, so the error amplifier uses SS voltage as the reference. When SS voltage is higher than reference voltage, the reference regains control and enters close loop.

An external capacitor connected from SS to AGND is charged from an internal 4µA (typical) current source, producing a ramped voltage.

#### 12.7 Maximum on duty improves dropout

When input voltage approaches the output voltage, the TMI3351 is designed to operate at top-side MOSFETs  $M_T$  maximum duty on mode to satisfy the duty cycle requirement to regulate the output voltage. If the input further drops to equal the output voltage, the TMI3351 forces the top-side MOSFETs  $M_T$  to remain on for more than one cycle, eventually reaching 99.5% duty cycle. In this low dropout mode, the controller turns on top-side MOSFETs  $M_T$  for multiple switching cycles until it turns off top-MOS switch momentarily and turns on bottom-MOS switch to refresh the BST supply voltage when the voltage of (BST-SW) is drops below 2.5V. In order to avoid the switching frequency entering the audio range, the minimum switching frequency is limited at 25kHz in low dropout mode.

#### **12.8 Current Limit**

The controller provides cycle-by-cycle current limit to protect against over-current conditions. The over-current limit (OCL) scheme senses the R<sub>SENSE</sub> current. If the sensed current is larger than the locL, an over current condition occurs. The present switching cycle is terminated (cycle-by-cycle current limit), and the MOSFETs  $M_T$  is turned off immediately. the MOSFETs  $M_T$  cannot be turned on again until the inductor current drops to the valley current limit.

If the Soft-start is completed and the FB is less than 54% V<sub>REF</sub>, an V<sub>OUT</sub> short condition occurs. the MOSFETs  $M_T$  and  $M_B$  are turned off immediately. Then the IC enter the hiccup mode to periodically restart the part. Meanwhile, the frequency would be lowered when FB < 350mV, maximum frequency conversion ratio is 1/2. This protection mode is especially useful when the output is dead-shorted to ground. The average short-circuit current is greatly reduced to alleviate the thermal issues. The TMI3351 exits the hiccup mode once the over-current condition is removed.

#### 12.9 VOUT cable impedance compensation

$V_{OUT}$  has a cable drop compensation. The slope is a default value that can be set by the factory. If external feedback resistor is applied,  $R_{FB1}$  must be 100k $\Omega$  and  $R_{SENSE}$  must be 7m $\Omega$  to have the designed slope.

$$V_{CAB\_COMP} = \frac{R_{FB1}(\Omega) \times R_{sense}(\Omega) \times I_{OUT}}{700} \times CABLE\_COMP$$

Where  $R_{FB1}$  is the upper resistor of the feedback divider network.  $R_{SENSE}$  is current sense resistor value to sense output current. CABLE\_COMP is  $0m\Omega$ (default),  $20m\Omega$ ,  $40m\Omega$ ,  $60m\Omega$  four gears can be selected and set by the factory.

The typical values of the  $R_{SENSE}$  is  $7m\Omega$ .

For example,  $R_{FB1} = 100k\Omega$ ,  $R_{SENSE} = 7m\Omega$ ,  $I_{OUT} = 1A$ , set CABLE\_COMP =  $20m\Omega$ ,  $V_{OUT}$  cable impedance compensation voltage is:

$V_{CAB_COMP} = \frac{100 \times 10^3 \times 7 \times 10^{-3} \times 1A}{700} \times 20m\Omega = 20mV$

# 12.10 Over-Voltage Protection (OVP)

When the voltage at the FB pin ( $V_{FB}$ ) is 18% above the feedback reference voltage  $V_{REF}$ , an output OVP fault is set. All of the switches will be turned off, and discharge circuit starts to discharge output through SW pin. Switching resumes once the output falls down to 102% of  $V_{REF}$ .

# 12.11 Thermal Shutdown (TSDN)

The TMI3351 also has a built-in thermal shutdown circuit that prevents heat damage to the IC. Normal operation should always be within the IC's power dissipation rating. If the rating is exceeded for a continued period, the junction temperature  $T_J$  will rise above 160°C and will activate the TSDN circuit. It will turn off the  $M_T$  &  $M_B$  switch. The device automatically restarts once the junction temperature drops by the thermal shutdown hysteresis of 20°C below the thermal shutdown threshold.

#### **13. Application Information**

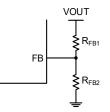

#### 13.1 Setting the Output Voltage

Output voltage can be set by feeding the output back to the FB pin with a resistor divider network.

Figure 2. VOUT Setting Resistor

As shown in Figure 2, the resistor divider network includes  $R_{FB1}$  and  $R_{FB2}$ . Usually, first is picking a fixed  $R_{FB1}$  value (such as  $100k\Omega$ ) then using the equation below to calculate the  $R_{FB2}$  value:

$$R_{FB2} = \frac{0.8 \times R_{FB1}}{V_{OUT} - 0.8}$$

Some of the normally used output voltages and corresponding  $R_{FB1}$  and  $R_{FB2}$  values are listed in the table below:

| R <sub>FB1</sub> (kΩ) | $R_{FB2}(k\Omega)$ | Vout(V) |

|-----------------------|--------------------|---------|

| 100                   | 18.7               | 5.0     |

| 113                   | 11                 | 9.0     |

| 113                   | 8.06               | 12      |

| 113                   | 6.34               | 15      |

| 113                   | 4.7                | 20      |

Table 1. Resistor Selection for Common Output Voltage

#### **13.2 Setting the Frequency**

The selection of switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger inductance and/or capacitance to maintain low output ripple voltage. The switching frequency of the TMI3351's controllers can be selected using the FREQ pin. The FREQ pin can be used to adjust the controller's operating frequency from 100kHz to 1MHz. The value of R<sub>FREQ</sub> for a given operating frequency can be calculated by:

$$R_{FREQ}(k\Omega) = \frac{21800}{f_s(kHz)} - 4$$

To get  $f_s = 500 \text{ kHz}$ , set  $R_{FREQ}$  to  $39 \text{ k}\Omega$ .

Some recommended values of RFREQ for most commonly used switching frequency are listed in Table 2.

| Table 2. Frequency VS. RFREQ |                 |  |  |

|------------------------------|-----------------|--|--|

| R <sub>FREQ</sub> (kΩ)       | Frequency (kHz) |  |  |

| 150                          | 150             |  |  |

| 68                           | 300             |  |  |

| 39                           | 500             |  |  |

| 18                           | 1000            |  |  |

Table 2. Frequency vs. R<sub>FREQ</sub>

The PWM switching frequency is programmable, while the duty cycle is fixed limited to 99.5%, allowing the bootstrap capacitor to charge during when the voltage is low. The TMI3351 allows a high ratio of input to output voltage conversion.

#### 13.3 Setting the Peak Current Limit

The peak current limit can be set with below formula.

$$I_{PEAK}(A) = \frac{R_{ILIM}(k\Omega)}{6.5 * R_{EREO}(k\Omega) * R_{SENSE}(\Omega)}$$

Where R<sub>SENSE</sub> is current sense resistor value to sense output current, R<sub>ILIM</sub> is resistor at ILIM pin, R<sub>FREQ</sub> is resistor at FREQ pin.

The typical values of the  $R_{\text{SENSE}}$  is  $7m\Omega$ .

#### 13.4 Setting the Average Current Limit

The value of average current limit can be calculated by following formula.

$$I_{AVG} = 60\% \times I_{PEAK}$$

The threshold calculated by the above formula is the value when internal average current limit signal is pulled low, the actual value will be higher.

#### **13.5 Input Capacitor Selection**

The input current of a buck convertor is discontinuous, therefore an input capacitor must be connected between the Vin pin and GND pin to keep the input voltage stable and filter out the pulsing input current.

The voltage rating of input capacitor must be greater than maximum input voltage plus ripple voltage. The input ripple voltage can be approximated by equation below:

$$\Delta V_{IN} = \frac{I_{OUT}}{f_S \times C_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \frac{V_{OUT}}{V_{IN}}$$

As mentioned above, the input current is discontinuous in a buck converter, the current stress on the input capacitor is necessary to concern when selecting the capacitor. For a buck circuit, the RMS value of input capacitor current can be calculated by:

$$I_{CIN\_RMS} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

According to the formula, it can be concluded that the  $I_{CIN_RMS} = 0.5 \times I_{OUT}$  when  $V_{OUT} = 0.5 \times V_{IN}$ , which is the worst case. To obtain the best performance and reliability, the input capacitors must have current rating higher than  $I_{CIN_RMS}$  at worst operating conditions. It should be noted that the ripple current rating from capacitor manufactures is based on certain amount of life time, so further de-rating needs to be considered for long term reliability.

Ceramic capacitor is the optimal choice for an input capacitor due to its low ESR and high ripple current rating. The X5R or X7R type dielectric ceramic capacitors are recommended for their better temperature and voltage characteristics. Depending on the application condition, other low ESR tantalum capacitor or aluminum electrolytic capacitor may also be suitable.

#### **13.6 Inductor Selection**

When a switching voltage is applied on an inductor, the inductor can provide the output with a constant current. The inductance can be calculated as follows:

$$L = \frac{V_{OUT}}{f_S \times \Delta I_L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Higher inductance gives lower inductor ripple current and lower ripple voltage on the load, but leads to larger size of the inductor to avoid saturation. Low ripple current reduces inductor core losses. It also reduces RMS current through inductor and switches, which results in less conduction loss. Usually, the ripple current is recommended to be set to 30% of the maximum load current.

When selecting the inductor, make sure it is able to handle the peak current without saturation even at the highest operating temperature. The peak inductor current can be calculated as follows:

$$I_{LPEAK} = I_{OUT} + \frac{V_{OUT}}{2 \times f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

The inductor takes the highest current in a buck regulation circuit. The conduction loss on the inductor should be taken in to account for thermal and efficiency requirements.

Shielded inductors are small and radiate less EMI noise, but at the cost of higher price than unshielded inductors. So, the selection of inductor depends on the trade-offs among EMI requirement, price and size.

#### **13.7 Output Capacitor Selection**

The output capacitor is used to provide the load with constant and stable voltage. The output capacitor is selected based on the DC output voltage rating, output ripple voltage specification and ripple current rating.

The selected output capacitor must have a higher rated voltage specification than the maximum desired output voltage including ripple. De-rating needs to be considered for long term reliability.

In a buck converter circuit, output ripple voltage is determined by inductor value, switching frequency, output capacitor value and ESR. It can be calculated by the equation below:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \left(R_{ESR} + \frac{1}{8 \times f_S \times C_{OUT}}\right)$$

Where, COUT is output capacitor value and RESR is the Equivalent Series Resistor of output capacitor.

When low ESR ceramic capacitor is adopted for output capacitor, the output ripple voltage is determined by the output capacitor value and the inductor ripple current, and it can be calculated by using the equation below:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f_s^2 \times L \times C_{OUT}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

When tantalum capacitor or aluminum electrolytic capacitor is adopted for output capacitor, the impedance of ESR at switching frequency dominates, and it can be calculated by using the equation below:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_S \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times R_{ESR}$$

The X5R and X7R dielectric type of ceramic or other low ESR tantalum or aluminum electrolytic capacitors is suitable for low output ripple voltage requirement over the entire operational temperature range.

In a buck converter, output capacitor current is continuous. The RMS current of output capacitor is decided by the peak to peak inductor ripple current. It can be calculated by:

$$I_{Co\_RMS} = \frac{\Delta I_L}{\sqrt{12}}$$

Usually, the ripple current rating of the output capacitor is a less important issue than that of the input capacitor, due to its comparatively smaller current stress. It should be noted that the output capacitor could be overstressed when the inductor value is selected to be very small.

The output capacitor has some effects on the loop stability, the TMI3351 is optimized for wide range of output capacitor values and ESR ratings.

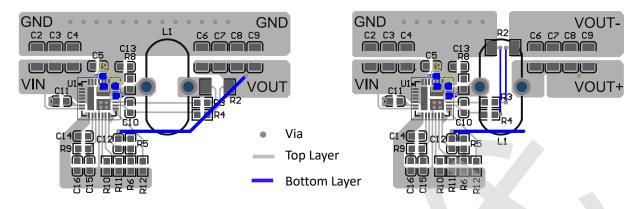

#### **13.8 PCB Layout Considerations**

All switching power supplies, especially for those with high switching frequency and high load currents, good PCB is crucial. A badly PCB layout might cause instability and noise issue. To maximize efficiency, switch rise and fall time are very fast. To prevent radiation of high frequency noise (for example, EMI), proper layout of the high-frequency switching path is essential.

In the TMI3351 buck regulator circuit, high pulsing current flows through two circuit loops. The first loop starts from the input capacitors, to Vin pin, to the filter inductor, to the output capacitor and load, and then return to the input capacitor through ground. Current flows in the first loop when the high side switch is on. The second loop starts from inductor, to the output capacitors and load, to the PGND pin, to SW pin. Current flows in the second loop when the low side switch is on.

In PCB layout, minimizing the two loops area reduces the noise of this circuit and improves efficiency. A ground plane is recommended to connect input capacitor, output capacitor, and PGND pin of the low-side switch.

Some layout tips for optimal electrical and thermal performance:

- 1. The input capacitor should be connected to the VIN pin (1~5, 27, 28) and the PGND pin (22~24) as close as possible.

- The 22-24 pin is the power ground, and the power ground copper needs to be connected to these pins. The GND of PAD2 can drill several more vias on the power ground of the bottom layer. The GND of pins 8, 11 and 18 can be directly connected with GND of PAD2.

- 3. C<sub>BST</sub> capacitor should be placed near the chip, and be connected to the BST pin and SW pin with short and thick wire.

- 4. Make the current trace from SW pin to L to C<sub>OUT</sub> to the PGND pin as short as possible. Meanwhile, the current trace from in input capacitor to VIN pin, then to the PGND pin should be kept as short as possible to reduce the EM radiation.

- 5. Place the feedback resistors as close to the FB pin as possible, the trace from FB pin to AGND as short as possible.

- 6. Keep sensitive signal trace such as trace connected with FB pin, COMP pin, FREQ pin, ILIM pin far away from the SW trace.

- 7. Route the sensing traces (SEN+, SEN-) in paired way with smallest closed area. Avoid crossing noisy areas such as SW. Place the RC filter for the current sense signal as close to the IC pins as possible. At the same time, a short and wide type resistor is recommended for current sense. When the output voltage is greater than or equal to 24V, the current sense resistor needs to be placed on the low side. When the output voltage is less than 24V, the current sense resistor can be placed on the high side in order to lay the ground wire more conveniently.

- 8. VREG capacitor should be placed as close as possible to VREG pin. The capacitor ground needs to be connected to the GND of PAD2 as short as possible.

- 9. The ground return of input/output capacitor should be tied close with large PGND copper area.

- 10. For heavy load, suggest layout large copper, more layers and more vias for heat sink to enhance the thermal performance.

Figure 4. Layout Recommendation

## 14. Typical Application Schematic:

Figure 5. Typical Application Schematic with High Side Current Sense (V<sub>OUT</sub><24V)

Figure 6. Typical Application Schematic with Low Side Current Sense (Vour≥24V)

#### 15. Package Information: QFN-28, 5mm×5mm×0.75mm

# **Important Notification**

This document only provides product information. Toll Microelectronic Co., Ltd. (TMI) reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and to discontinue any product without notice at any time.

Toll Microelectronic Co., Ltd. (TMI) cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a TMI product. No circuit patent licenses are implied.

All rights are reserved by Toll Microelectronic Co., Ltd.