# 32-Bit RISC Microprocessor TX19 Family TMP1962C10BXBG

### Features

The TX19 is a family of high-performance 32-bit microprocessors that offers the speed of a 32-bit RISC solution with the added advantage of a significantly reduced code size of a 16-bit architecture. The instruction set of the TX19 includes as a subset the 32-bit instructions of the TX39, which is based on the MIPS R3000A<sup>TM</sup> architecture. Additionally, the TX19 supports the MIPS16<sup>TM</sup> Application-Specific Extensions (ASE) for improved code density.

DataSheet4U.com

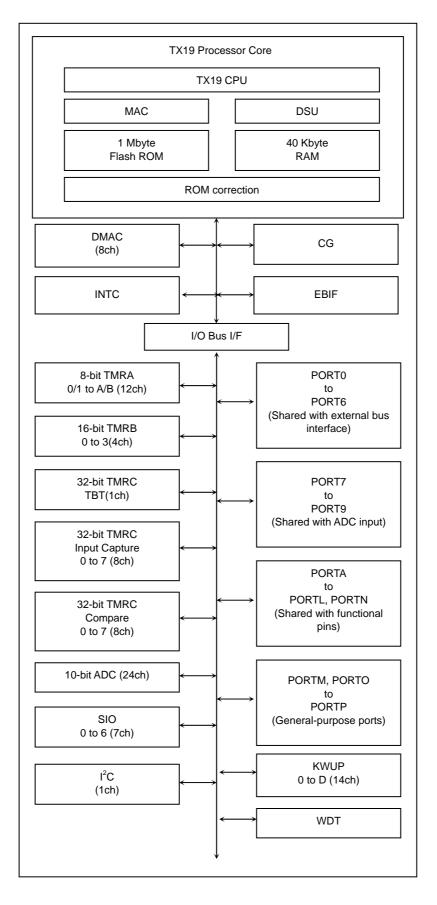

The TMP1962 is built on a TX19 core processor and a selection of intelligent peripherals. The TMP1962 is suitable for low-voltage, low-power applications.

Features of the TMP1962 include the following:

- (1) TX19 core processor

- 1) Two instruction set architecture (ISA) modes: 16-bit ISA for code density and 32-bit ISA for speed

- The 16-bit ISA is object-code compatible with the code-efficient MIPS16<sup>TM</sup> ASE.

- The 32-bit ISA is object-code compatible with the high-performance TX39 family.

- 2) Combines high performance with low power consumption.

- High performance

- Single clock cycle execution for most instructions

- 3-operand computational instructions for high instruction throughput

- 5-stage pipeline

030619EBP

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in

general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of

the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system,

and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or

damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

- On-chip high-speed memory

- DSP function: Executes 32-bit x 32-bit multiplier operations with a 64-bit accumulation in a single clock cycle.

- Low power consumption

- Optimized design using a low-power cell library

- Programmable standby modes in which processor clocks are stopped

- 3) Fast interrupt response suitable for real-time control

- Distinct starting locations for each interrupt service routine

- Automatically generated vectors for each interrupt source

- Automatic updates of the interrupt mask level

- (2) On-chip program memory and data memory

| Product       | On-Chip ROM     | On-Chip RAM |

|---------------|-----------------|-------------|

| TMP1962C10AXB | 1 Mbyte         | 40 Kbyte    |

| TMP1962F10AXB | 1 Mbyte (Flash) | 40 Kbyte    |

- ROM correction logic (8 words x 8 blocks)

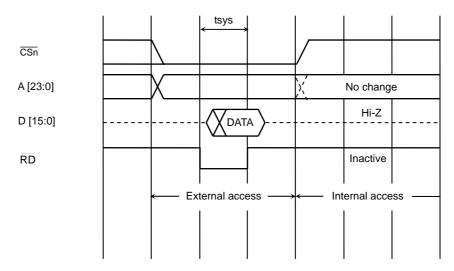

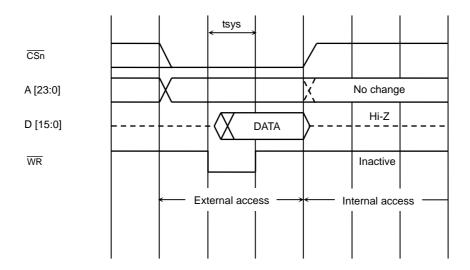

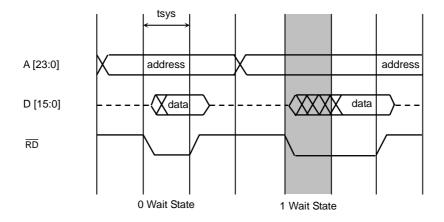

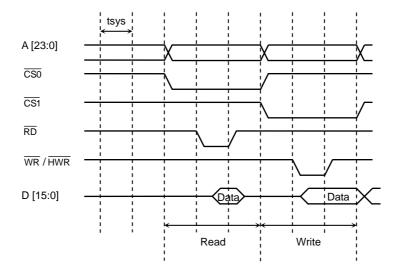

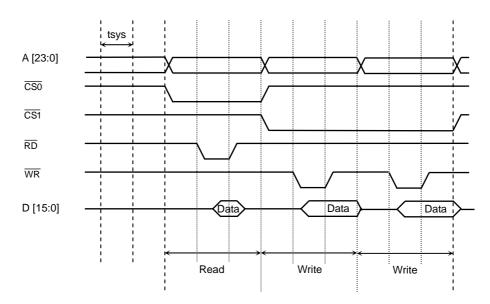

- (3) External memory expansion

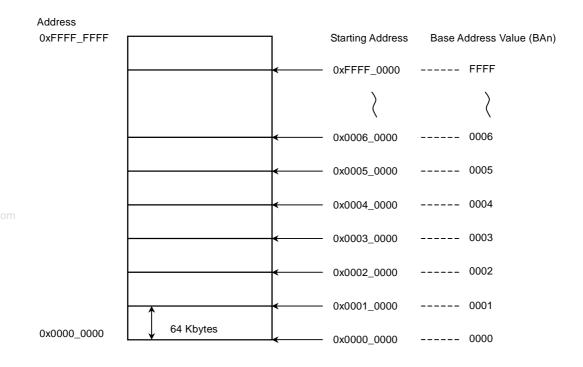

- 16-Mbyte off-chip address space for code and data

- External data bus

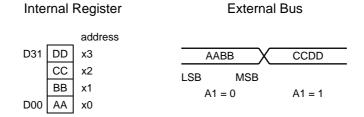

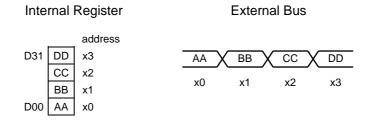

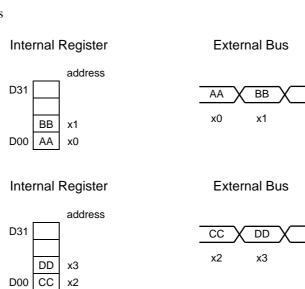

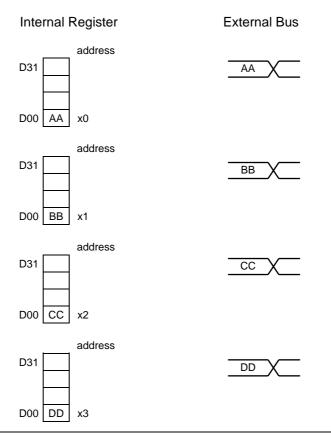

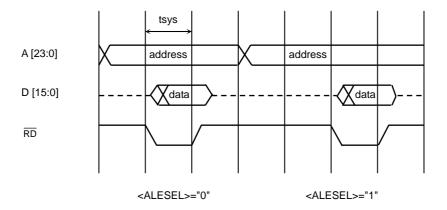

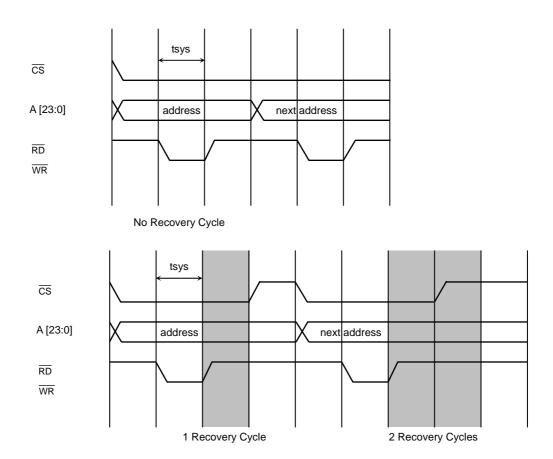

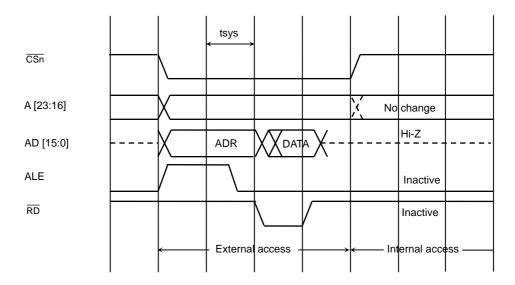

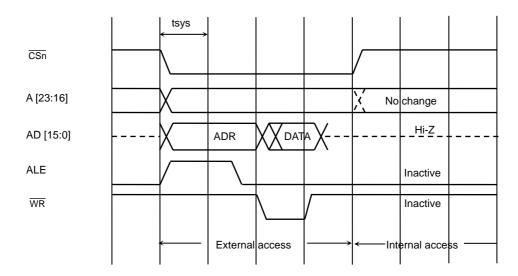

Separate bus/multiplexed bus: Dynamic bus sizing for 8-bit and 16-bit data ports

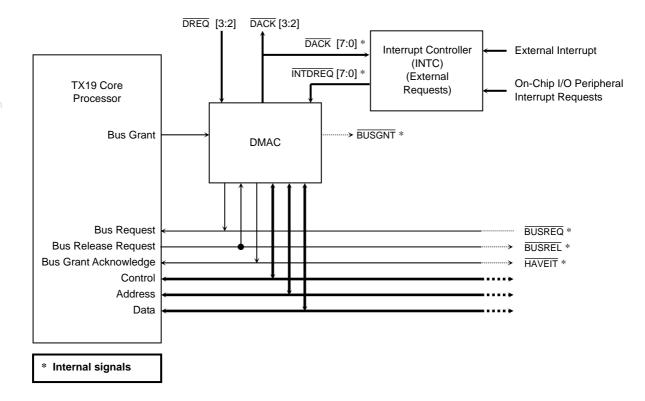

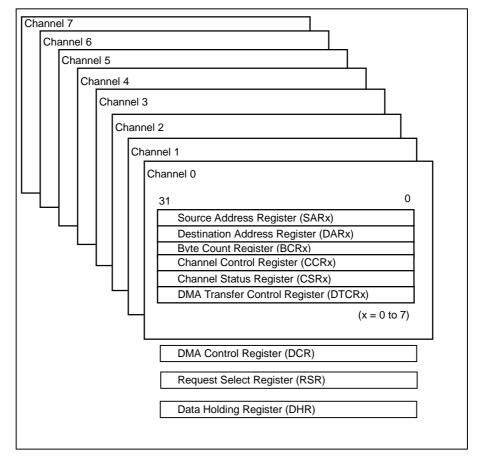

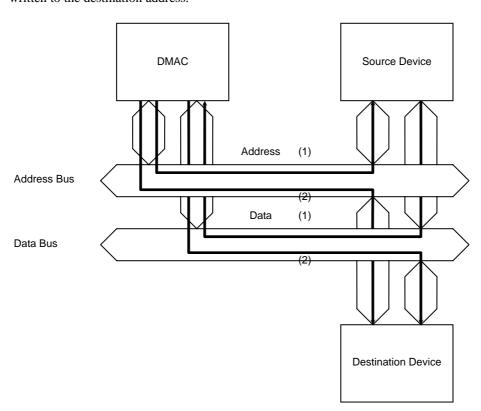

- (4) 8-channel DMA controller

- Interrupt- or software-triggered

- Transfer destination: On-chip memory, on-chip peripherals, external memory, external peripherals

- (5) 12-channel 8-bit timer

- 8/16/24/32-Bit Interval Timer mode

- 8-Bit PWM mode

- 8-Bit PPG mode

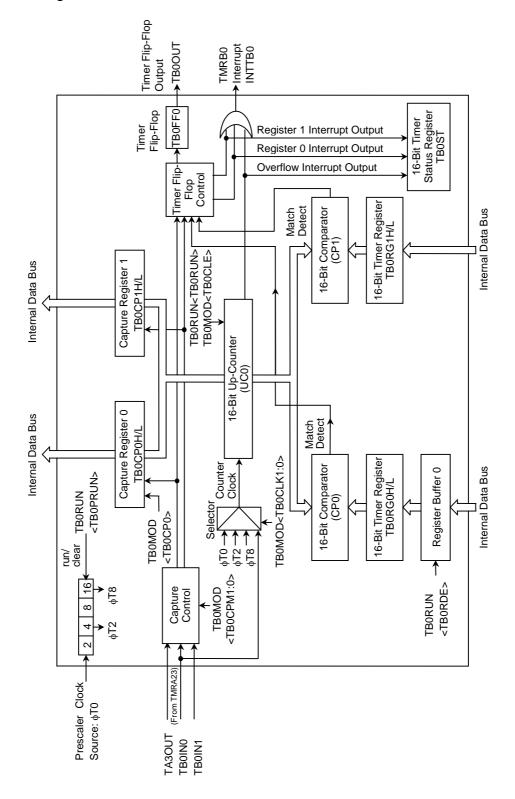

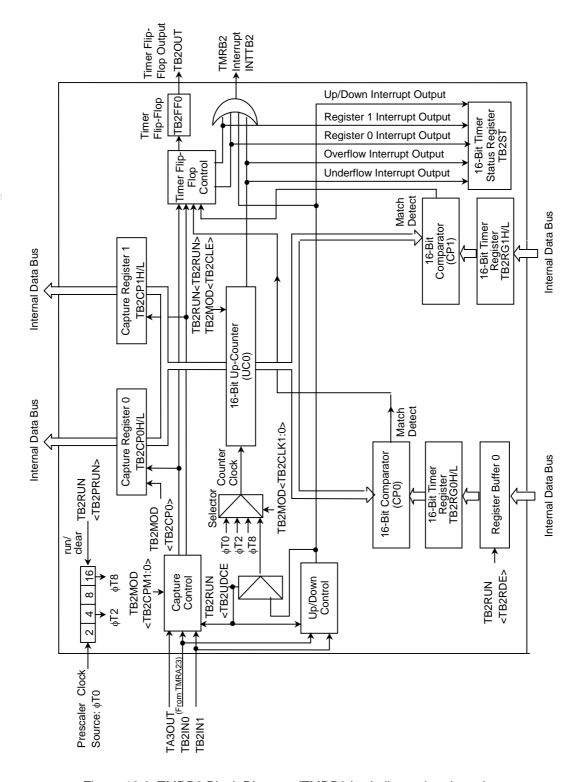

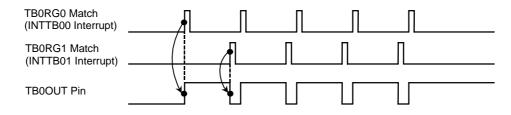

- (6) 4-channel 16-bit timer

- 16-Bit Interval Timer mode

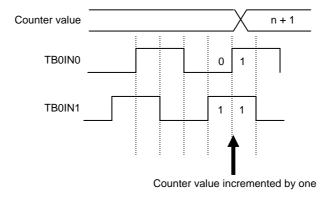

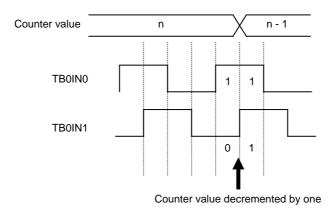

- 16-Bit Event Counter mode

- 16-bit PPG output

- Input capture

- 2-phase pulse input counter (2 channels)

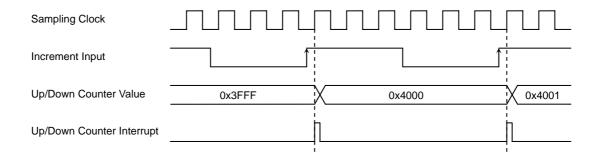

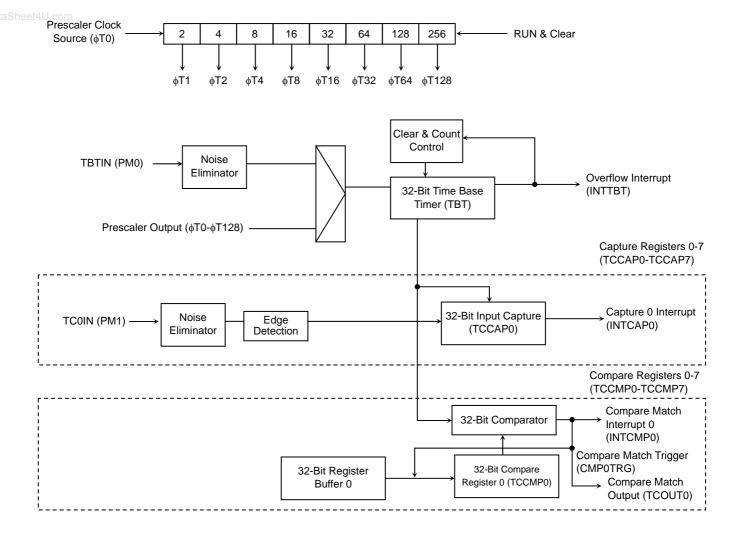

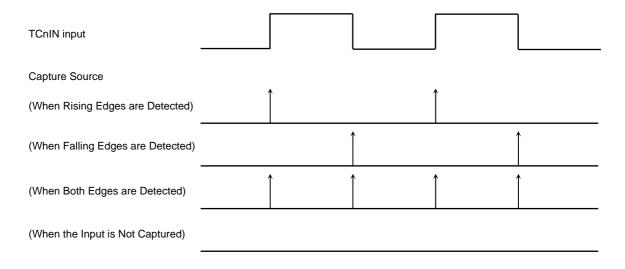

- (7) 32-bit input capture

- 32-bit input capture registers (8 channels)

- 32-bit compare registers (8 channels)

- 32-bit time base timer (1 channel)

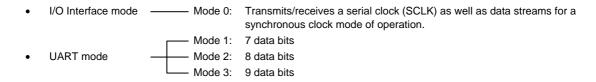

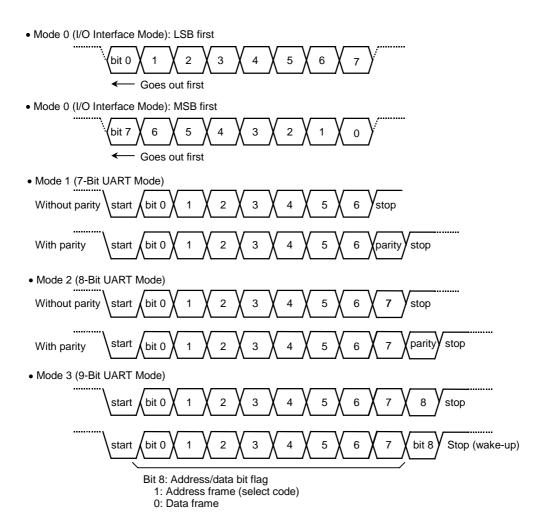

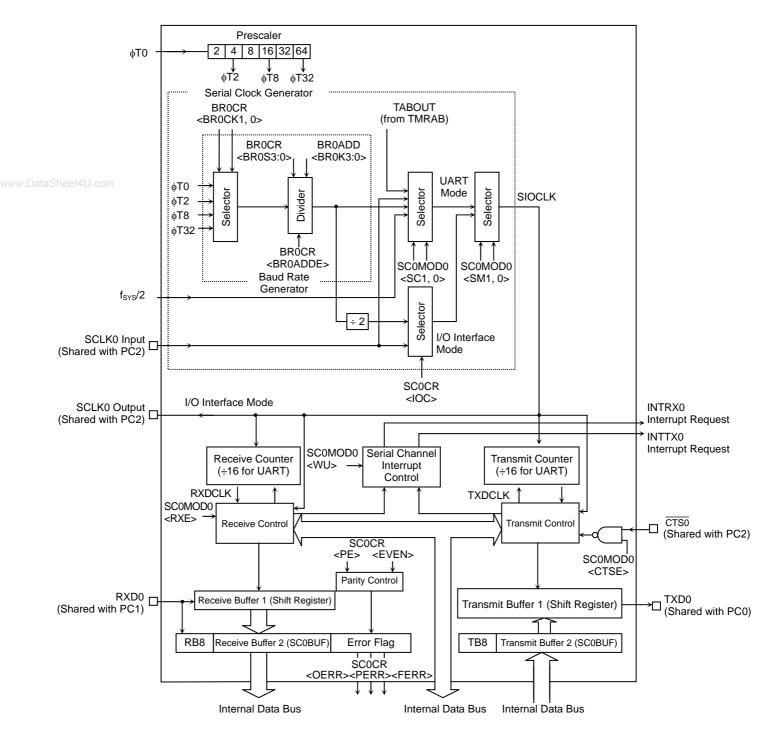

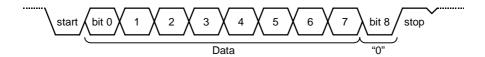

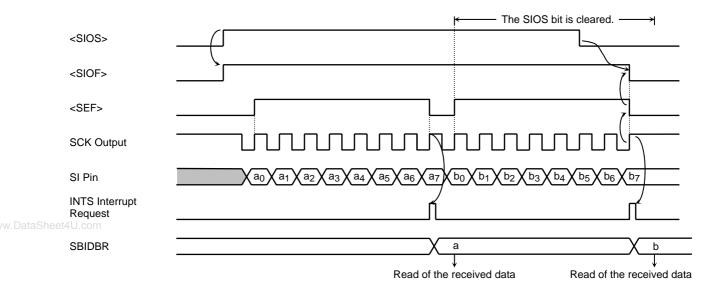

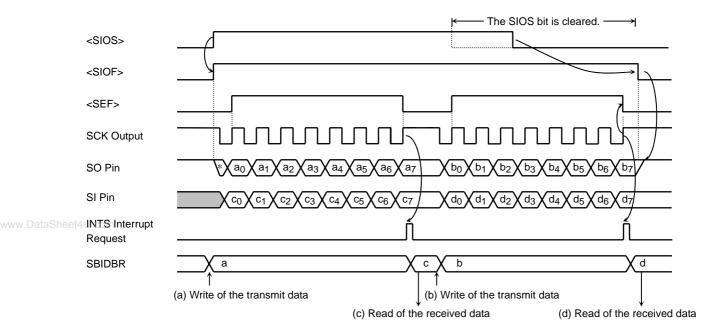

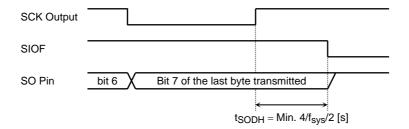

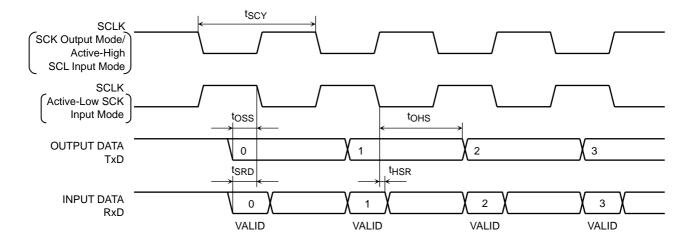

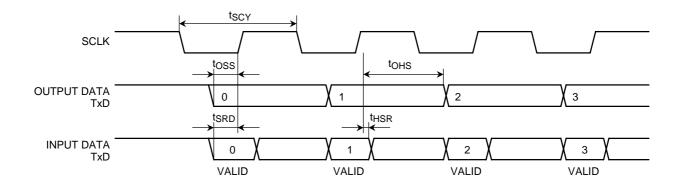

- (8) 7-channel general-purpose serial interface

- Either UART mode or Synchronous mode can be selected.

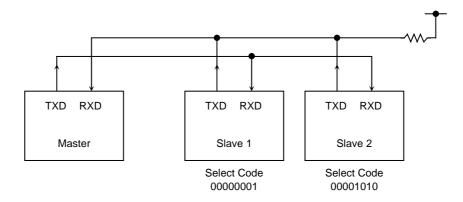

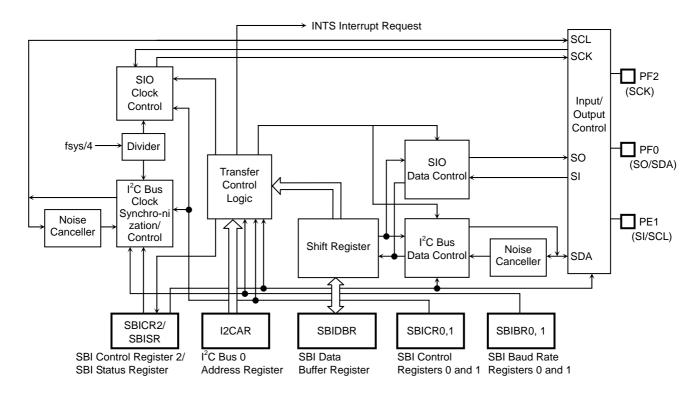

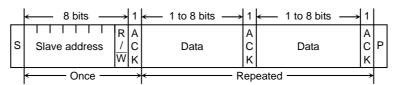

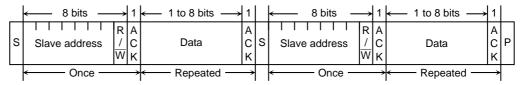

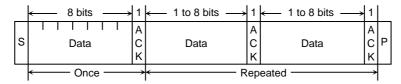

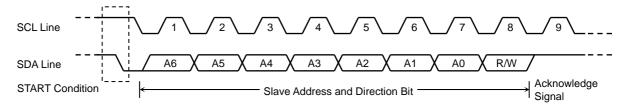

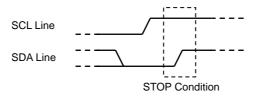

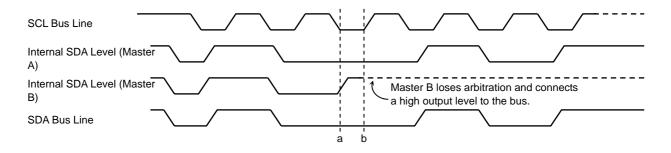

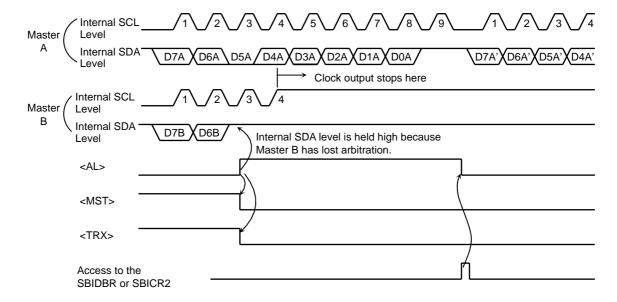

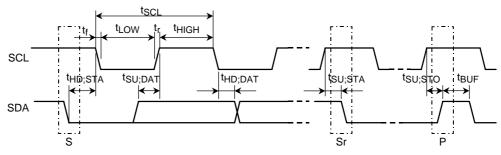

- (9) 1-channel serial bus interface

- Either I<sup>2</sup>C Bus mode or Clock-Synchronous mode can be selected.

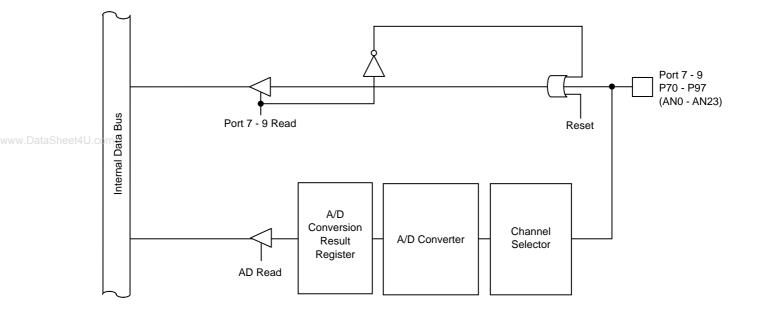

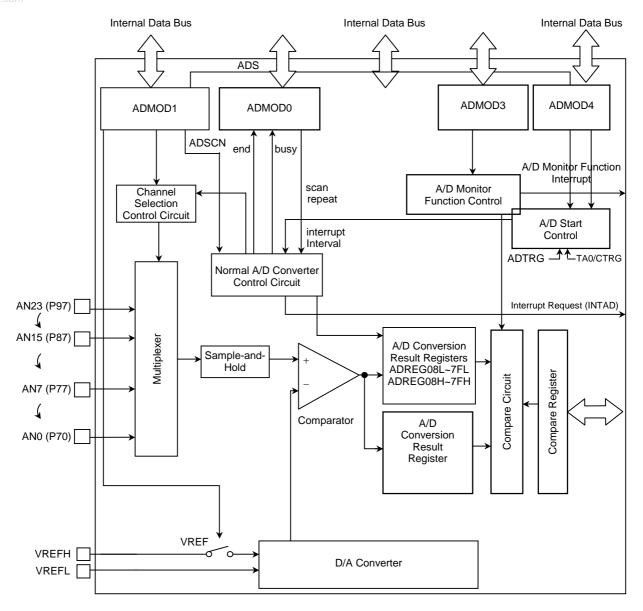

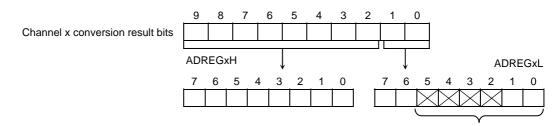

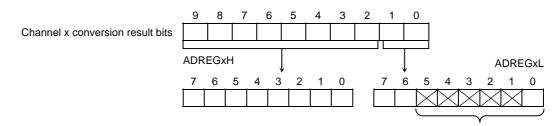

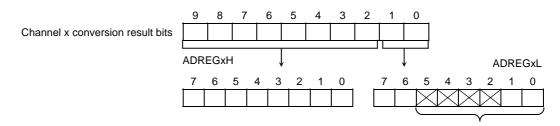

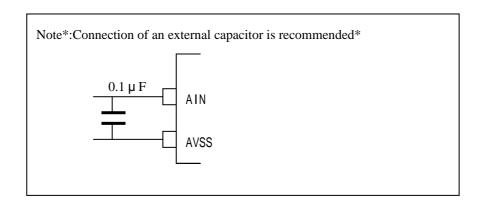

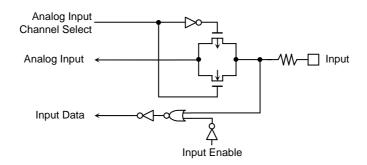

- (10) 24-channel 10-bit A/D converter (with internal sample/hold)

- External trigger supported

- Fixed-Channel or Channel Scan mode

- Single Conversion or Continuous Conversion mode

- Timer monitoring

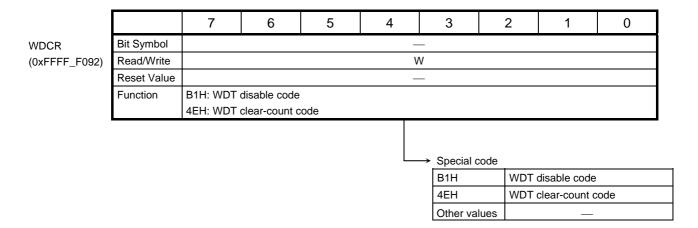

- (11) 1-channel watchdog timer

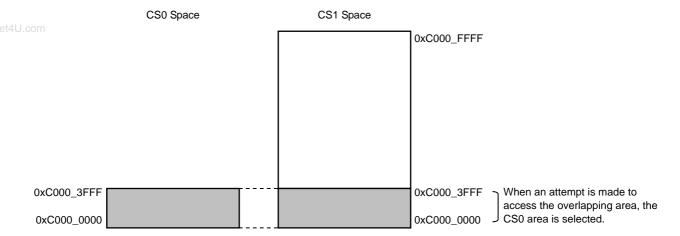

- (12) 4-channel chip select/wait controller

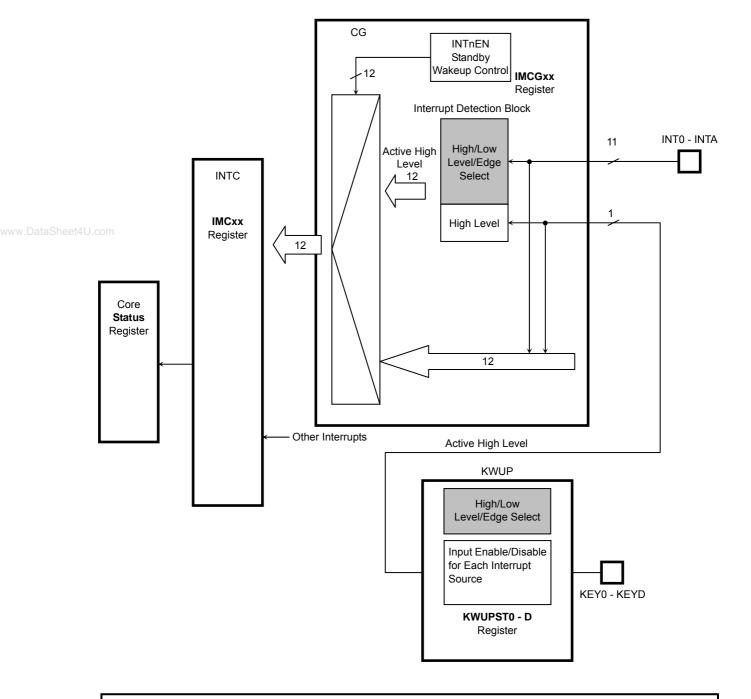

- (13) Interrupt sources

- 4 CPU interrupts: Software interrupt instruction

- 55 internal interrupts: 7 priority levels, with the exception of the watchdog timer interrupt

- 25 external interrupts: 7 priority levels, with the exception of the NMI interrupt

The external sources include 14 KWUP sources, which are all assigned to a single interrupt vector.

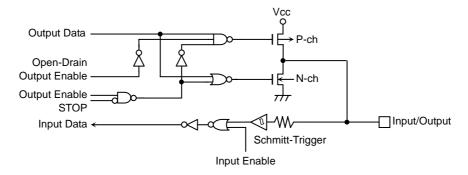

- (14) 202-pin input/output ports

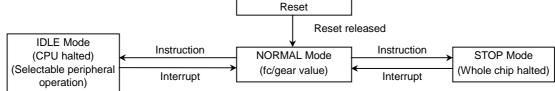

- (15) Standby modes

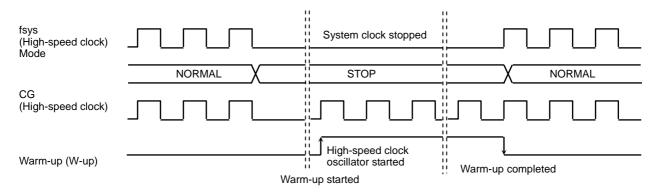

- Two standby modes: IDLE, STOP

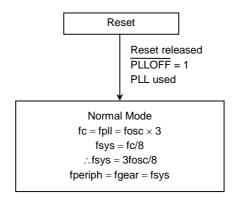

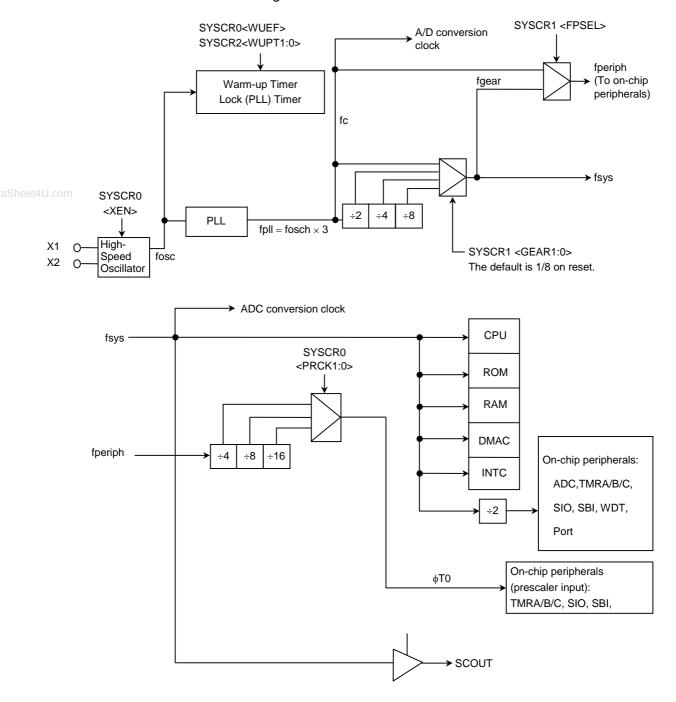

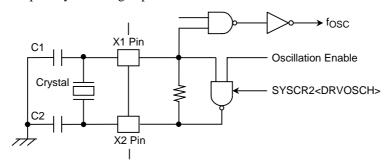

- (16) Clock generator

- On-chip PLL (x3)

- Clock gear: Divides the high-speed clock by 1/2, 1/4 or 1/8.

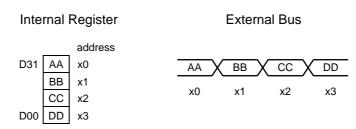

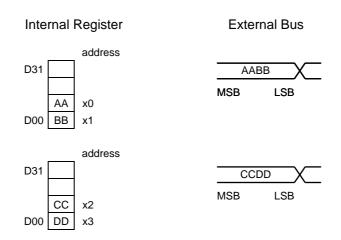

### (17) Optional big-endian alignment

### Big-endian

| Higher address | 31 24 | 23 16 | 15 8 | 7 0 | Word address |

|----------------|-------|-------|------|-----|--------------|

| <b>↑</b>       | 8     | 9     | 10   | 11  | 8            |

|                | 4     | 5     | 6    | 7   | 4            |

|                | 0     | 1     | 2    | 3   | 0            |

Lower address

- Byte 0 is the highest-order byte (bits 31-24).

- The address of a word data item is the address of its highest-order byte (byte 0).

Little-endian

Higher address 0 Word address 24 23 16 15 11 10 9 8 8 7 6 5 4 4 3 2 1 0 0

Lower address

- Byte 0 is the lowest-order byte (bits 7-0).

- The address of a word data item is the address of its lowest-order byte (byte 0).

### (18) Operating frequency

• 40.5 MHz (Vcc = 1.35 V to 1.65 V)

### (19) Package

• P-FBGA281 (13 mm x 13 mm, 0.65-mm pitch)

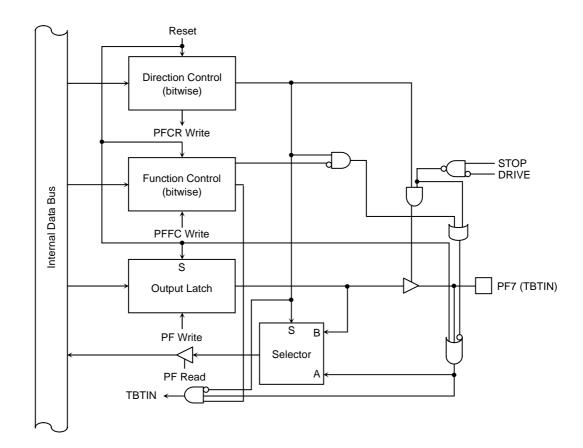

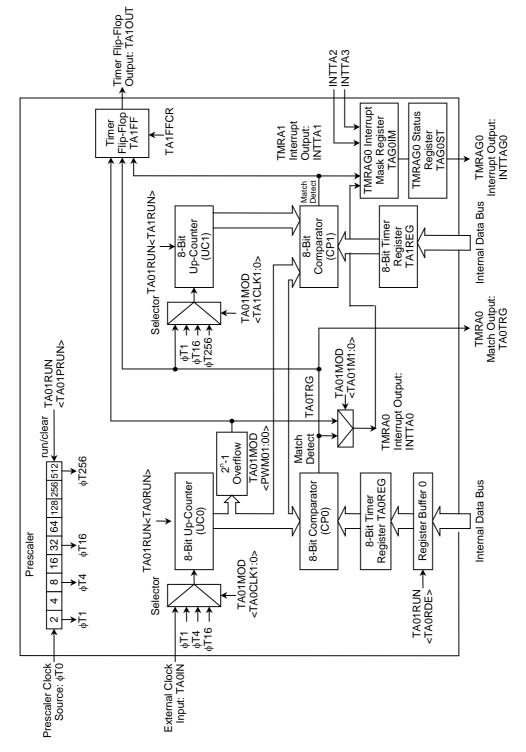

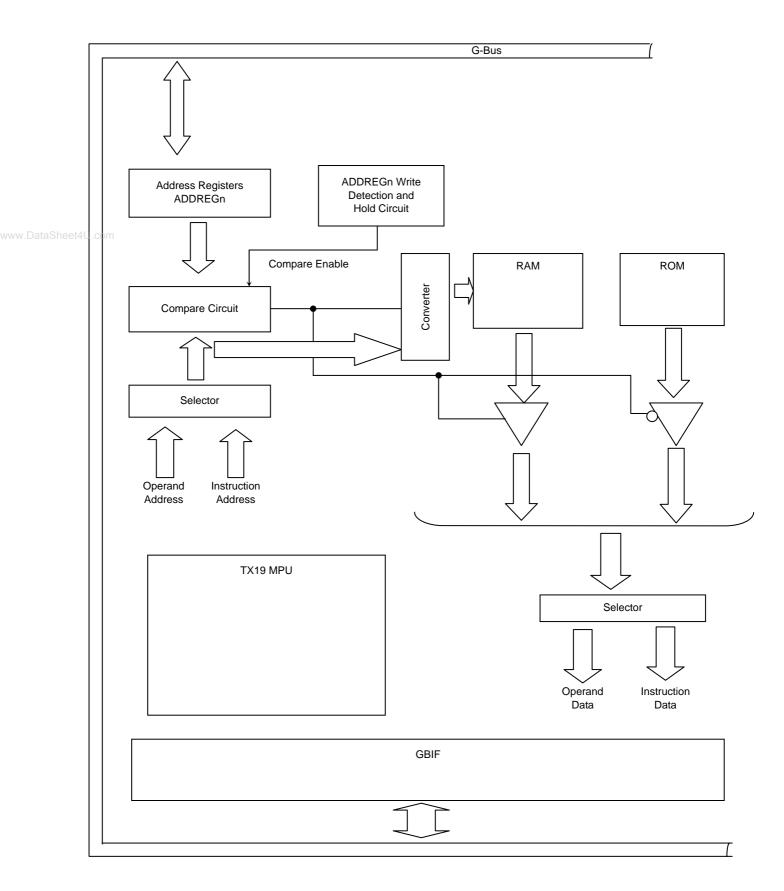

Figure 1.1 TMP1962 Block Diagram

#### Signal Descriptions 2.

This section contains pin assignments for the TMP1962 as well as brief descriptions of the TMP1962 input and output signals.

#### 2.1 Pin Assignment (TOP View)

The following illustrates the TMP1962 pin assignment.

|    | A1 | A2 | А3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 | A13 | A14 | A15 | A16 | A17 |     |

|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|    | B1 | B2 | В3 | B4 | B5 | В6 | B7 | B8 | В9 | B10 | B11 | B12 | B13 | B14 | B15 | B16 | B17 | B18 |

| .c | C1 | C2 | СЗ | C4 | C5 | C6 | C7 | C8 | C9 | C10 | C11 | C12 | C13 | C14 | C15 | C16 | C17 | C18 |

|    | D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 | D16 | D17 | D18 |

|    | E1 | E2 | E3 | E4 | E5 | E6 | E7 | E8 | E9 | E10 | E11 | E12 | E13 | E14 | E15 | E16 | E17 | E18 |

|    | F1 | F2 | F3 | F4 | F5 |    | F7 | F8 | F9 | F10 | F11 | F12 |     | F14 | F15 | F16 | F17 | F18 |

|    | G1 | G2 | G3 | G4 | G5 | G6 |    |    |    |     |     |     | G13 | G14 | G15 | G16 | G17 | G18 |

|    | H1 | H2 | НЗ | H4 | H5 | H6 |    |    |    |     |     |     | H13 | H14 | H15 | H16 | H17 | H18 |

|    | J1 | J2 | J3 | J4 | J5 | J6 |    |    |    |     |     |     | J13 | J14 | J15 | J16 | J17 | J18 |

|    | K1 | K2 | K3 | K4 | K5 | K6 |    |    |    |     |     |     | K13 | K14 | K15 | K16 | K17 | K18 |

|    | L1 | L2 | L3 | L4 | L5 | L6 |    |    |    |     |     |     | L13 | L14 | L15 | L16 | L17 | L18 |

|    | M1 | M2 | М3 | M4 | M5 | M6 |    |    |    |     |     |     | M13 | M14 | M15 | M16 | M17 | M18 |

|    | N1 | N2 | N3 | N4 | N5 |    | N7 | N8 | N9 | N10 | N11 | N12 |     | N14 | N15 | N16 | N17 | N18 |

|    | P1 | P2 | P3 | P4 | P5 | P6 | P7 | P8 | P9 | P10 | P11 | P12 | P13 | P14 | P15 | P16 | P17 | P18 |

|    | R1 | R2 | R3 | R4 | R5 | R6 | R7 | R8 | R9 | R10 | R11 | R12 | R13 | R14 | R15 | R16 | R17 | R18 |

|    | T1 | T2 | Т3 | T4 | T5 | T6 | T7 | T8 | T9 | T10 | T11 | T12 | T13 | T14 | T15 | T16 | T17 | T18 |

|    | U1 | U2 | U3 | U4 | U5 | U6 | U7 | U8 | U9 | U10 | U11 | U12 | U13 | U14 | U15 | U16 | U17 | U18 |

| _  |    | V2 | V3 | V4 | V5 | V6 | V7 | V8 | V9 | V10 | V11 | V12 | V13 | V14 | V15 | V16 | V17 |     |

Figure 2.1 P-FBGA281 Pin Assignment

Table 2.1 shows the correspondence between the numbers and names of the TMP1962 pins.

Pin Pin Pin Pin Pin Pin Name Pin Name Pin Name Pin Name Pin Name No. No. No. No. No. P75/AIN5 C14 PK6/KEY6 Α1 NC A13 PK1/KEY1 В8 C2 PCST3 (DSU) **VREFL** A14 PI1/INT1 **B9** PL0/TA4IN P92/AIN18 C15 PI5/INT9 A2 C3 P90/AIN16 PI3/INT3 PL3/TAAIN TCK (JTAG) A15 B10 C4 P95/AIN21 C16 P93/AIN19 PI6/INTA CVCC15 (CVCC2) A4 A16 B11 PM1 C5 P82/AIN10 C17 P80/AIN8 A17 X2 PM4 P85/AIN13 C18 NC (XT2) Α5 B12 C6 P83/AIN11 AVCC31 PK2/KEY2 P72/AIN2 SDAO/TPC (DSU) A6 B1 **B13** C7 D1 Α7 P70/AIN0 B2 VREFH B14 PI2/INT2 C8 **AVSS** D2 PCST2 (DSU) P74/AIN4 PI4/INT4 SDI/DINT (DSU) ВЗ P91/AIN17 B15 C9 PL1/TA6IN D3 **A8** Α9 B4 P94/AIN20 B16 PI7 C10 PL4/TB0IN0 DVCC15 (DVCC22) PL2/TA8IN B5 P81/AIN9 B17 **CVSS** C11 PM2 P96/AIN22 A10 D5 A11 PM0 P84/AIN12 B18 X1 C12 PM5 D6 P86/AIN14 P73/AIN3 A12 PK0/KEY0 B7 P71/AIN1 C1 PCST0 (DSU) C13 PK3/KEY3 D7

Table 2.1 Pin Numbers and Names (1/2)

Table 2.1 Pin Numbers and Names (2/2)

|              |            |                                         |            |                 |            |                 | ,          | /               |            |                 |

|--------------|------------|-----------------------------------------|------------|-----------------|------------|-----------------|------------|-----------------|------------|-----------------|

|              | Pin<br>No. | Pin Name                                | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        | Pin<br>No. | Pin Name        |

|              | D8         | DVCC15 (DVCC22)                         | F18        | P44/SCOUT       | K14        | P12/D10/AD10    | N18        | DVSS            | T8         | PD4/TXD4        |

|              | D9         | DVSS                                    | G1         | RESET           | K15        | P13/D11/AD11    | P1         | PP0             | Т9         | PC0/TXD0        |

|              | D10        | PL5/TB0IN1                              | G2         | TEST5           | K16        | P14/D12/AD12    | P2         | PB2/TB2IN0/INT5 | T10        | PC3/TXD1        |

|              | D11        | PM3                                     | G3         | DVCC2 (FVCC2)   | K17        | DVCC33          | P3         | PB3/TB2IN1/INT6 | T11        | PH4/TCOUT4      |

|              | D12        | PM6                                     | G4         | NC (FVSS)       | K18        | P15/D13/AD13    | P4         | PB4/TB2OUT      | T12        | PE2/SCLK5/ CTS5 |

|              | D13        | PK4/KEY4                                | G5         | PJ0/INT0        | L1         | NC (FVCC3)      | P5         | PB5/TB3IN0/INT7 | T13        | PE5/KEYB        |

|              | D14        | PK7/KEY7                                | G6         | BW0             | L2         | PO1             | P6         | PG5/TC5IN       | T14        | P53/A3          |

|              | D15        | DVCC34                                  | G13        | TRST            | L3         | PO2             | P7         | PG7/TC7IN       | T15        | P56/A6          |

|              | D16        | TDI (JTAG)                              | G14        | NC (CAP1)       | L4         | PO3             | P8         | PD6/SCLK4/CTS4  | T16        | P62/A10         |

| www.DataShee | D17        | TDO (JTAG)                              | G15        | P41/ CS1        | L5         | PO4             | P9         | PC2/SCLK0/CTS0  | T17        | P65/A13         |

|              | D18        | NC (XT1)                                | G16        | P37/ALE         | L6         | PO7             | P10        | PC5/SCLK1/CTS1  | T18        | P20/A16/A0      |

|              | E1         | DCLK (DSU)                              | G17        | P35/BUSAK       | L13        | NC (TEST3)      | P11        | PH6/TCOUT6      | U1         | PA0/TA0IN       |

|              | E2         | PCST1 (DSU)                             | G18        | NC (FVCC2)      | L14        | P06/D6/AD6      | P12        | NC              | U2         | PA3/TA3OUT      |

|              | E3         | DBGE                                    | H1         | NMI             | L15        | NC (FVCC2)      | P13        | P50/A0          | U3         | PA6/TA9OUT      |

|              | E4         | PJ3/INTLV                               | H2         | DVCC31          | L16        | P07/D7/AD7      | P14        | P51/A1          | U4         | PF1/SI/SCL      |

|              | E5         | PJ4/ENDIAN                              | H3         | PN7             | L17        | P10/D8/AD8      | P15        | P54/A4          | U5         | PF5/ DREQ3      |

|              | E6         | P97/AIN23                               | H4         | BW1             | L18        | P11/D9/AD9      | P16        | P23/A19/A3      | U6         | PG2/TC2IN       |

|              | E7         | P87/AIN15                               | H5         | PLLOFF          | M1         | PO0             | P17        | P24/A20/A4      | U7         | PD2/RXD3        |

|              | E8         | P76/AIN6                                | H6         | NC (TEST1)      | M2         | PP5             | P18        | P25/A21/A5      | U8         | DVCC32          |

|              | E9         | P77/AIN7                                | H13        | NC (TEST2)      | M3         | PP6             | R1         | PB0/TB0OUT      | U9         | PC7/RXD2        |

|              | E10        | PL6/TB1IN0                              | H14        | P31/ WR         | M4         | PP7             | R2         | PB1/TB1OUT      | U10        | PH1/TCOUT1      |

|              | E11        | PL7/TB1IN1                              | H15        | P32/ HWR        | M5         | PB7/TB3OUT      | R3         | PF3/ DREQ2      | U11        | PH3/TCOUT3      |

|              | E12        | PM7                                     | H16        | P33/WAIT/RDY    | M6         | DVCC32          | R4         | PF4/ DACK2      | U12        | PE1/RXD5        |

|              | E13        | PK5/KEY5                                | H17        | P30/RD          | M13        | NC (TEST4)      | R5         | PF7/TBTIN       | U13        | PE4/KEYA        |

|              | E14        | NC                                      | H18        | P40/ CS0        | M14        | P02/D2/AD2      | R6         | PG4/TC4IN       | U14        | DVCC32          |

|              | E15        | TMS (JTAG)                              | J1         | PN2/SCLK6/ CTS6 | M15        | NC (FVSS)       | R7         | PG6/TC6IN       | U15        | P57/A7          |

|              | E16        | NC (CVCCH)                              | J2         | PN3             | M16        | P03/D3/AD3      | R8         | PD5/RXD4        | U16        | P63/A11         |

|              | E17        | NC                                      | J3         | PN4             | M17        | P04/D4/AD4      | R9         | PC1/RXD0        | U17        | P66/A14         |

|              | E18        | DVCC15 (DVCC22)                         | J4         | PN5             | M18        | P05/D5/AD5      | R10        | PC4/RXD1        | U18        | DVCC33          |

|              | F1         | DVSS                                    | J5         | PN6             | N1         | PP1             | R11        | PH5/TCOUT5      | V2         | PA2/TA2IN       |

|              | F2         | DRESET                                  | J6         | DVCC15 (DVCC22) | N2         | PP2             | R12        | PH7/TCOUT7      | V3         | PA5/TA7OUT      |

|              | F3         | SYSRDY                                  | J13        | NC (FVSS)       | N3         | PP3             | R13        |                 | V4         | PF0/SO/SDA      |

|              | F4         | PJ1/BUSMD                               | J14        | P16/D14/AD14    | N4         | PP4             |            | P52/A2          | V5         | PG0/TC0IN       |

|              | F5         | PJ2/BOOT                                |            | DVSS            | N5         | PB6/TB3IN1/INT8 |            | P55/A5          | V6         | PG1/TC1IN       |

|              | F7         | AVSS                                    | J16        | P17/D15/AD15    | N7         | DVSS            | R16        | P61/A9          | V7         | PD1/TXD3        |

|              | F8         | AVSS                                    | J17        | P36/R/W         | N8         | PD7/KEY8        | R17        | P21/A17/A1      | V8         | PD0/SCLK2/CTS2  |

|              | F9         | AVCC32                                  | J18        | P34/BUSRQ       | N9         | DVCC15 (DVCC22) | R18        |                 | V9         | PC6/TXD2        |

|              | F10        | DVCC34                                  | K1         | PN0/TXD6        | N10        | DVSS (DVCC22)   | T1         | PA1/TA1OUT      | V10        | PH0/TCOUT0      |

|              | F11        | PI0/ ADTRG                              | K2         | PN1/RXD6        | N11        | RSTPUP          | T2         | PA4/TA5OUT      | V10        | PH2/TCOUT2      |

|              | F12        | DVSS                                    | K3         | PO5             | N12        | DVSS            | T3         | PA7/TABOUT      | V11        | PE0/TXD5        |

|              | F14        | NC (CAP2)                               | K4         | PO6             | N14        | P26/A22/A6      | T4         | PF2/SCK         | V12        | PE3/KEY9        |

|              | F15        | P42/ CS2                                | K5         | NC (FVSS)       | N15        | P27/A23/A7      | T5         | PF6/DACK3       | V13        | PE7/KEYD        |

|              | F16        | P43/ CS3                                | K6         | DVSS            | N16        | P00/D0/AD0      | T6         | PG3/TC3IN       | V14        | P60/A8          |

|              | F17        | DVCC33                                  |            | NC (TEST0)      | N17        | P01/D1/AD1      | T7         | PD3/SCLK3/CTS3  | V15        | P64/A12         |

|              | Е17        | D 1 C C C C C C C C C C C C C C C C C C | KIS        | NO (TESTO)      | IN I /     | וטאווטוואטו     | 17         | 1 D3/30LN3/0133 |            |                 |

|              |            |                                         |            |                 |            |                 |            |                 | V17        | P67/A15         |

Note: Parentheses indicate the pin name on TMP1962F10AXBG with on-chip flash memory. (Except "DSU" and "JTAG". The same pin names are used for the on-chip mask ROM type and on-chip flash memory type.)

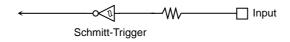

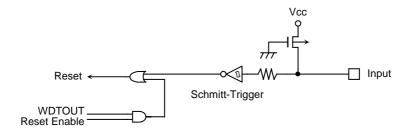

### 2.2 Pin Usage Information

Table 2.2 lists the input and output pins of the TMP1962, including alternate pin names and functions for multi-function pins.

Table 2.2 Pin Names and Functions (1/6)

| Pin Name        | Number of Pins | Туре         | Function                                                                              |

|-----------------|----------------|--------------|---------------------------------------------------------------------------------------|

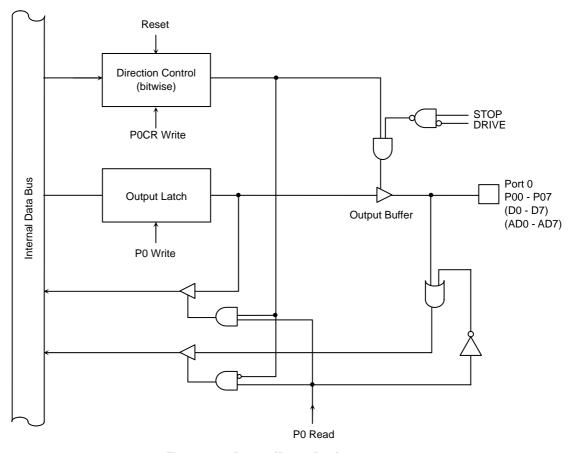

| P00 - P07       | 8              | Input/Output | Port 0: Individually programmable as input or output                                  |

| D0 - D7         |                | Input/Output | Data (Lower): Bits 0 to 7 of the data bus (Separate Bus mode)                         |

| AD0 - D7        |                | Input/Output | Address/Data (Lower): Bits 0 to 7 of the address/data bus (Multiplexed Bus mode)      |

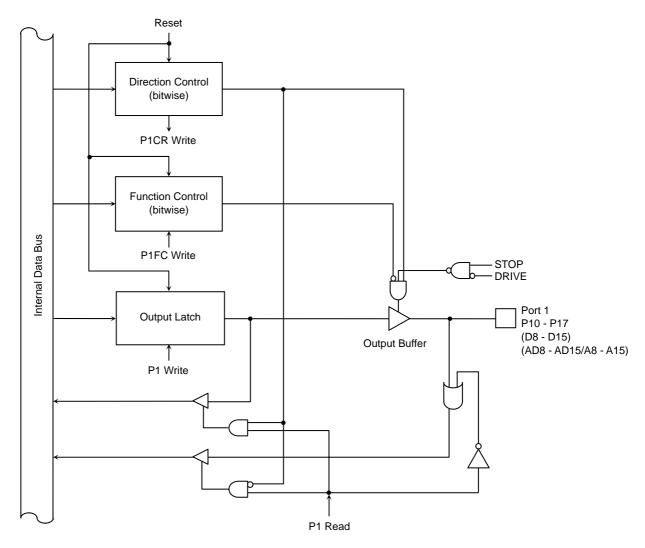

| 4P10+P17        | 8              | Input/Output | Port 1: Individually programmable as input or output                                  |

| D8 - D15        |                | Input/Output | Data (Upper): Bits 8 to 15 of the data bus (Separate Bus mode)                        |

| AD8 - AD15      |                | Input/Output | Address/Data (Upper): Bits 8 to 15 of the address/data bus (Multiplexed Bus mode)     |

| A8 - A15        |                | Output       | Address: Bits 8 to 15 of the address bus (Multiplexed Bus mode)                       |

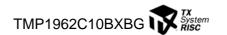

| P20 - P27       | 8              | Input/Output | Port 2: Individually programmable as input or output                                  |

| A16 - A23       |                | Output       | Address: Bits 16 to 23 of the address bus (Separate Bus mode)                         |

| A0 - A7         |                | Output       | Address: Bits 0 to 7 of the address bus (Multiplexed Bus mode)                        |

| A16 - A23       |                | Output       | Address: Bits 16 to 23 of the address bus (Multiplexed Bus mode)                      |

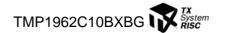

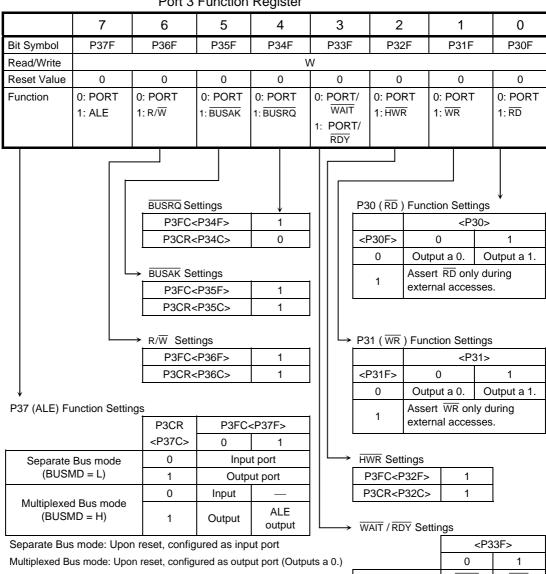

| P30             | 1              | Output       | Port 30: Output-only                                                                  |

| RD              |                | Output       | Read Strobe: Asserted during a read operation from an external memory device          |

| P31             | 1              | Output       | Port 31: Output-only                                                                  |

| $\overline{WR}$ |                | Output       | Write Strobe: Asserted during a write operation on D0 to D7                           |

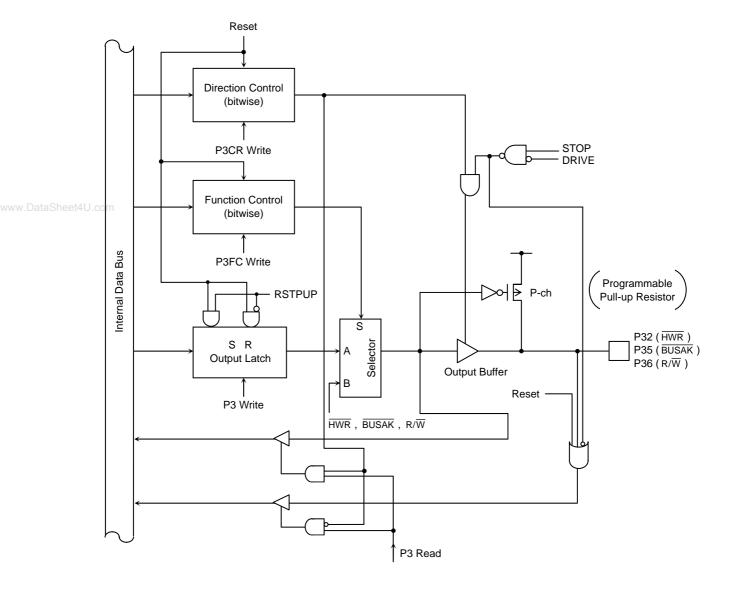

| P32             | 1              | Input/Output | Port 32: Programmable as input or output (with internal pull-up resistor)             |

| HWR             |                | Output       | Higher Write Strobe: Asserted during a write operation on D8 to D15                   |

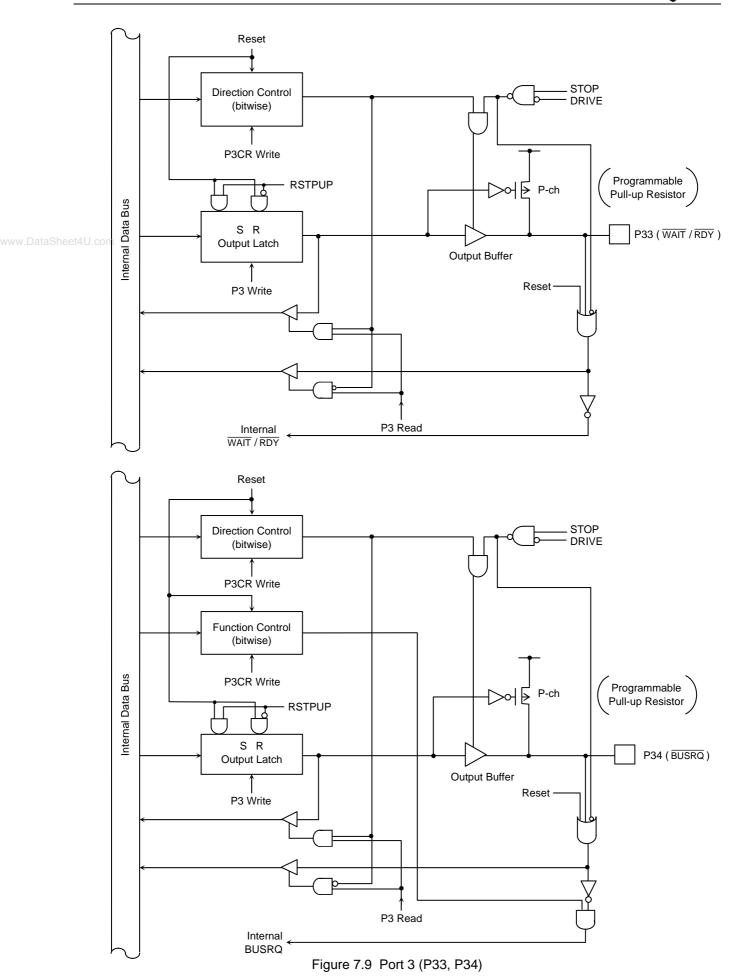

| P33             | 1              | Input/Output | Port 33: Programmable as input or output (with internal pull-up resistor)             |

| WAIT            | ·              | Input        | Wait: Causes the CPU to suspend external bus activity                                 |

| RDY             |                | Input        | Ready: Notifies the CPU that the bus is ready                                         |

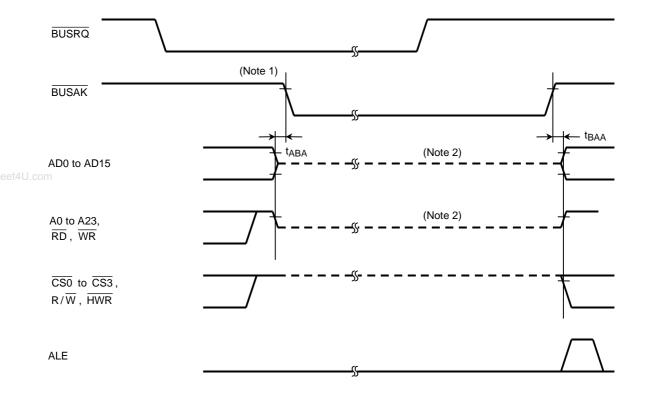

| P34             | 1              | Input/Output | Port 34: Programmable as input or output (with internal pull-up resistor)             |

| BUSRQ           |                | Input        | Bus Request: Asserted by an external bus master to request bus mastership             |

| P35             | 1              | Input/Output | Port 35: Programmable as input or output (with internal pull-up resistor)             |

| BUSAK           |                | Output       | Bus Acknowledge: Indicates that the CPU has relinquished the bus in response to BUSRQ |

| P36             | 1              | Input/Output | Port 36: Programmable as input or output (with internal pull-up resistor)             |

| R/W             | ·              | Output       | Read/Write: Indicates the direction of data transfer on the bus: 1 = read or dummy    |

|                 |                | Саграг       | cycle, 0 = write cycle                                                                |

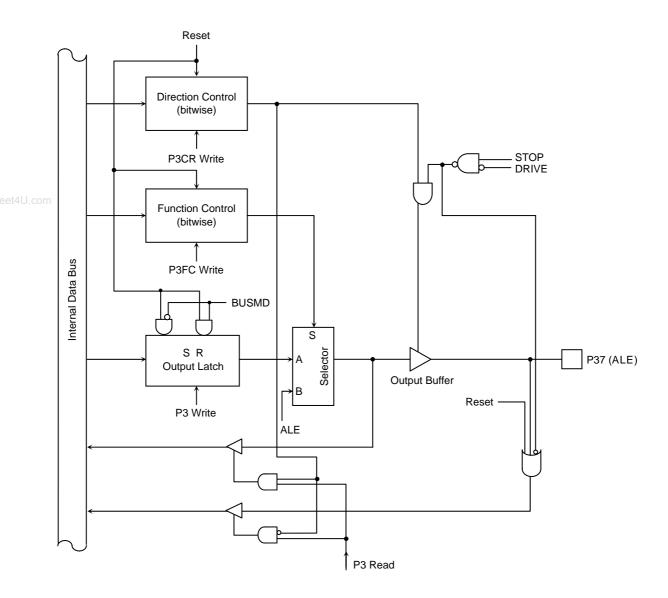

| P37             | 1              | Input/Output | Port 37: Programmable as input or output                                              |

| ALE             |                | Output       | Address Latch Enable (enabled only when an external memory device is accessed)        |

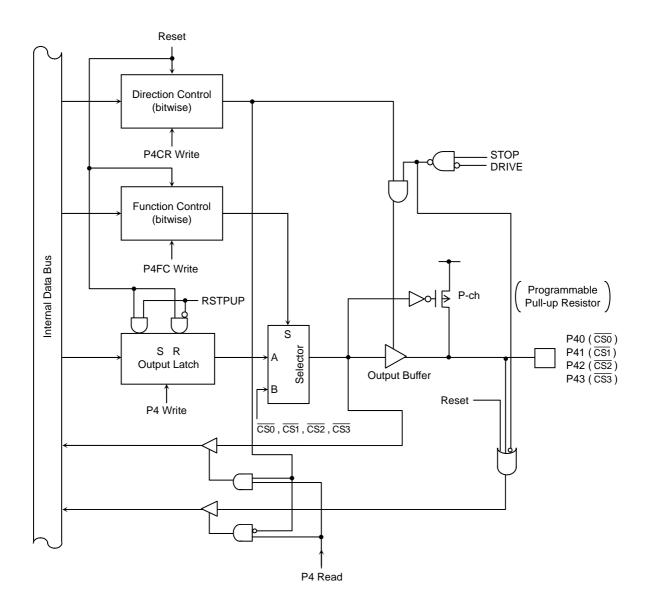

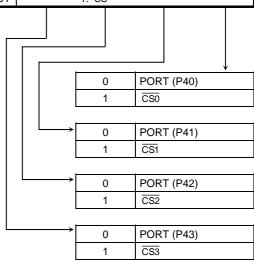

| P40             | 1              | Input/Output | Port 40: Programmable as input or output (with internal pull-up resistor)             |

| CS0             |                | Output       | Chip Select 0: Asserted low to enable external devices at programmed addresses        |

| P41             | 1              | Input/Output | Port 41: Programmable as input or output (with internal pull-up resistor)             |

| CS1             |                | Output       | Chip Select 1: Asserted low to enable external devices at programmed addresses        |

| P42             | 1              | Input/Output | Port 42: Programmable as input or output (with internal pull-up resistor)             |

| CS2             |                | Output       | Chip Select 2: Asserted low to enable external devices at programmed addresses        |

| P43             | 1              | Input/Output | Port 43: Programmable as input or output (with internal pull-up resistor)             |

| CS3             |                | Output       | Chip Select 3: Asserted low to enable external devices at programmed addresses        |

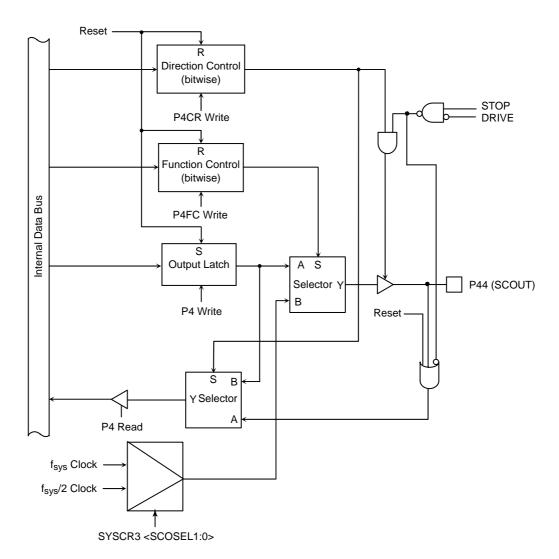

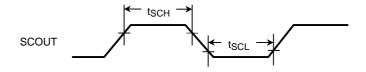

| P44             | 1              | Input/Output | Port 44: Programmable as input or output                                              |

| SCOUT           |                | Output       | System Clock Output: Drives out a clock signal at the same frequency as the CPU clock |

|                 |                |              | (high-speed or low-speed) or half the high-speed clock frequency                      |

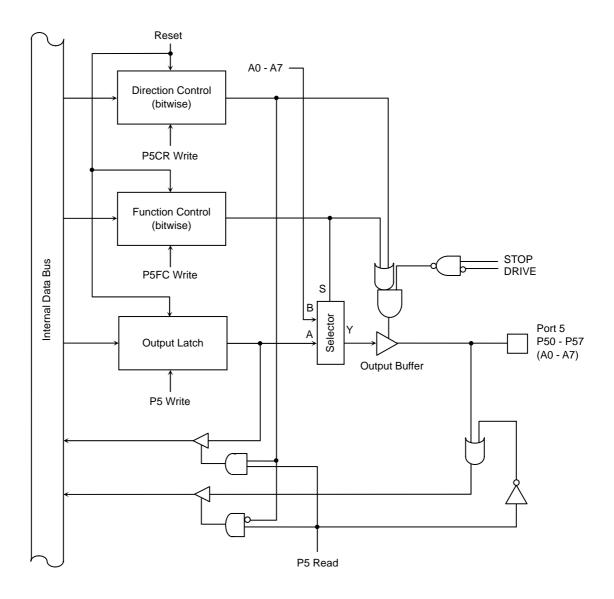

| P50 - P57       | 8              | Input/Output | Port 5: Individually programmable as input or output                                  |

| A0 - A7         |                | Output       | Address: Bits 0 to 7 of the address bus (Separate Bus mode)                           |

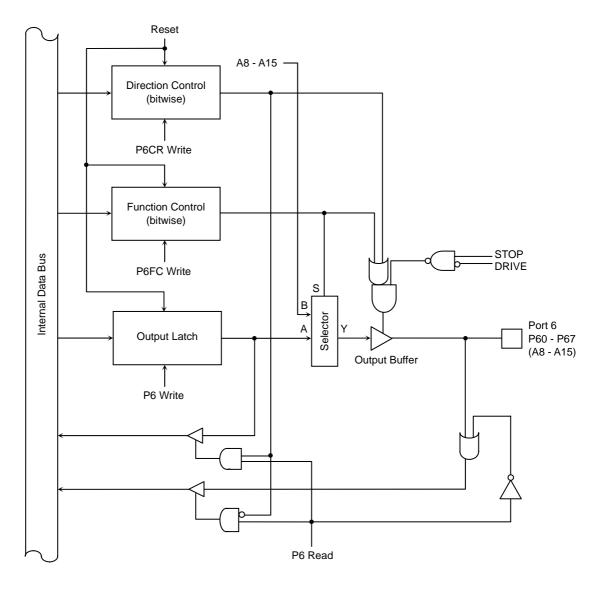

| P60 - P67       | 8              | Input/Output | Port 6: Individually programmable as input or output                                  |

| A8 - A15        |                | Output       | Address: Bits 8 to 15 of the address bus (Separate Bus mode)                          |

Table 2.2 Pin Names and Functions (2/6)

|   | Pin Name      | Number of Pins | Туре                   | Function                                                                                               |

|---|---------------|----------------|------------------------|--------------------------------------------------------------------------------------------------------|

| I | P70 - P77     | 8              | Input                  | Port 7: Input-only                                                                                     |

|   | AN0 - AN7     |                | Input                  | Analog Input: Input to the on-chip A/D converter                                                       |

|   | P80 - P87     | 8              | Input                  | Port 8: Input-only                                                                                     |

| L | AN8 - AN15    |                | Input                  | Analog Input: Input to the on-chip A/D converter                                                       |

|   | P90 - P97     | 8              | Input                  | Port 9: Input-only                                                                                     |

| L | AN16 - AN23   |                | Input                  | Analog Input: Input to the on-chip A/D converter                                                       |

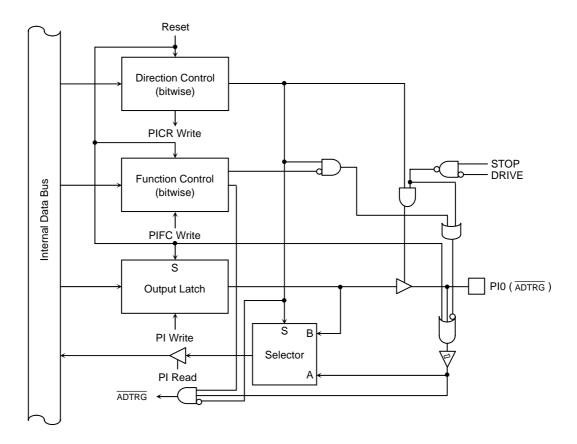

|   | PI0           | 1              | Input/Output           | Port I0: Programmable as input or output                                                               |

|   | ADTRG         |                | Input                  | A/D Trigger: Starts an A/D conversion                                                                  |

|   | L-L           |                |                        | Schmitt-triggered input                                                                                |

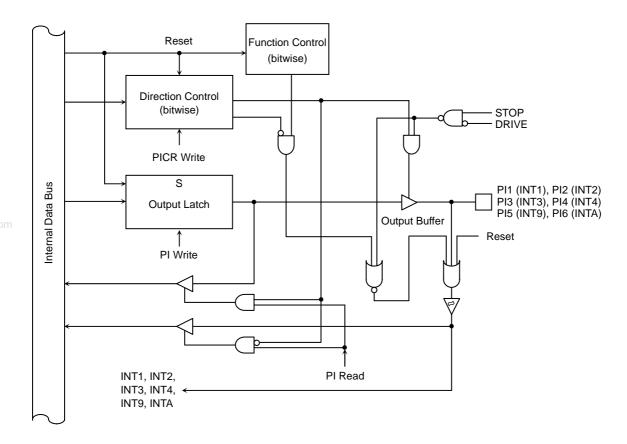

|   | PI1           | 1              | Input/Output           | Port I1: Programmable as input or output                                                               |

|   | INT1          |                | Input                  | Interrupt Request 1: Programmable to be high-level, low-level, rising-edge or                          |

|   |               |                |                        | falling-edge sensitive                                                                                 |

| ŀ | Bio           |                |                        | Schmitt-triggered input                                                                                |

|   | PI2           | 1              | Input/Output           | Port I2: Programmable as input or output                                                               |

|   | INT2          |                | Input                  | Interrupt Request 2: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive   |

|   |               |                |                        | Schmitt-triggered input                                                                                |

| ŀ | PI3           | 1              | Input/Output           | Port I3: Programmable as input or output                                                               |

|   | INT3          | ,              | Input                  | Interrupt Request 3: Programmable to be high-level, low-level, rising-edge or                          |

|   |               |                |                        | falling-edge sensitive                                                                                 |

|   |               |                |                        | Schmitt-triggered input                                                                                |

| ı | PI4           | 1              | Input/Output           | Port I4: Programmable as input or output                                                               |

|   | INT4          |                | Input                  | Interrupt Request 4: Programmable to be high-level, low-level, rising-edge or                          |

|   |               |                |                        | falling-edge sensitive                                                                                 |

|   |               |                |                        | Schmitt-triggered input                                                                                |

|   | PI5           | 1              | Input/Output           | Port I5: Programmable as input or output                                                               |

|   | INT9          |                | Input                  | Interrupt Request 9: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive   |

| L |               |                |                        | Schmitt-triggered input                                                                                |

|   | PI6           | 1              | Input/Output           | Port I6: Programmable as input or output                                                               |

|   | INTA          |                | Input                  | Interrupt Request A: Programmable to be high-level, low-level, rising-edge or                          |

|   |               |                |                        | falling-edge sensitive                                                                                 |

| ŀ | PI7           | 4              | Innert/Output          | Schmitt-triggered input                                                                                |

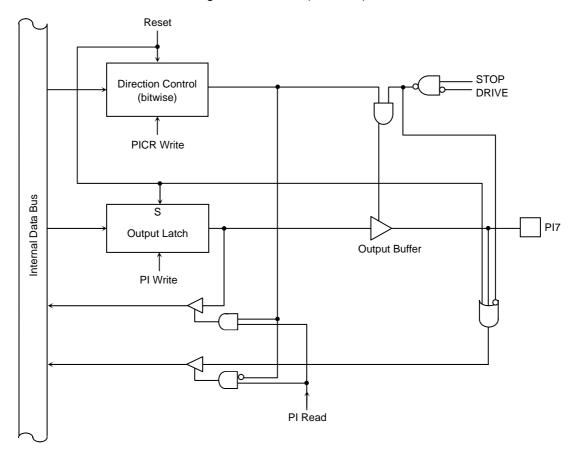

| ŀ |               | 1              | Input/Output           | Port I7: Programmable as input or output                                                               |

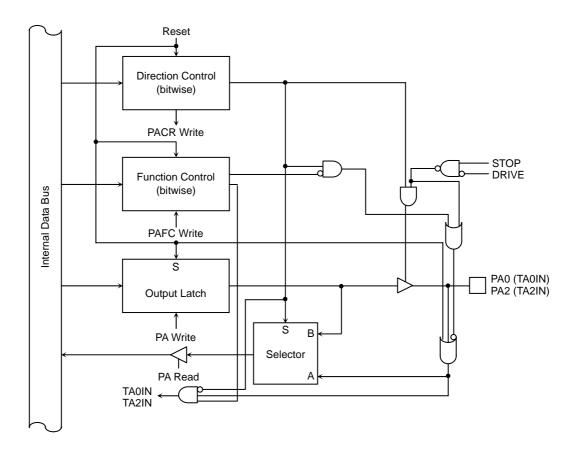

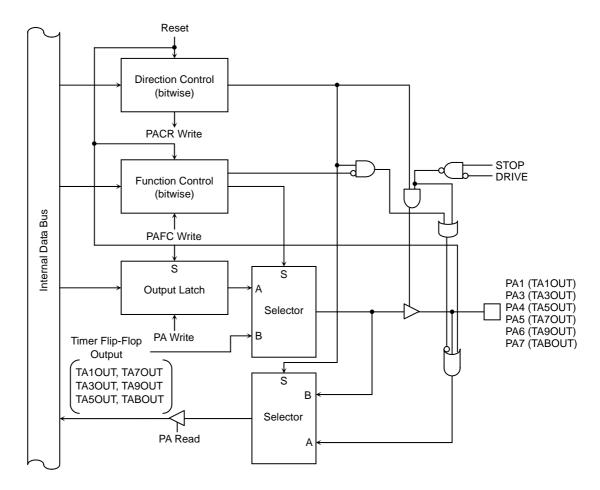

| ĺ | PA0<br>TA0IN  | 1              | Input/Output           | Port A0: Programmable as input or output                                                               |

| ŀ |               | 4              | Input/Output           | 8-Bit Timer 0 Input: Input to 8-bit timer 0                                                            |

| ĺ | PA1<br>TA1OUT | 1              | Input/Output<br>Output | Port A1: Programmable as input or output  8-Bit Timer 01 Output: Output from either 8-bit timer 0 or 1 |

| ŀ | PA2           | 1              | Input/Output           | Port A2: Programmable as input or output                                                               |

| Į | TA2IN         | '              | Input                  | 8-Bit Timer 2 Input: Input to 8-bit timer 2                                                            |

| ŀ | PA3           | 1              | Input/Output           | Port A3: Programmable as input to o-bit timer 2                                                        |

| Į | TA3OUT        | !              | Output                 | 8-Bit Timer 23 Output: Output from either 8-bit timer 2 or 3                                           |

| ŀ | PA4           | 1              | Input/Output           | Port A4: Programmable as input or output                                                               |

|   | TA5OUT        | '              | Output                 | 8-Bit Timer 45 Output: Output from either 8-bit timer 4 or 5                                           |

| ŀ | PA5           | 1              | Input/Output           | Port A5: Programmable as input or output                                                               |

| ĺ | TA7OUT        | '              | Output                 | 8-Bit Timer 67 Output: Output from either 8-bit timer 6 or 7                                           |

| ŀ | PA6           | 1              | Input/Output           | Port A6: Programmable as input or output                                                               |

|   | TA9OUT        | i i            | Input                  | 8-Bit Timer 89 Output: Output from either 8-bit timer 8 or 9                                           |

| ŀ | PA7           | 1              | Input/Output           | Port A7: Programmable as input or output                                                               |

|   | TABOUT        | ·              | Output                 | 8-Bit Timer AB Output: Output from either 8-bit timer A or B                                           |

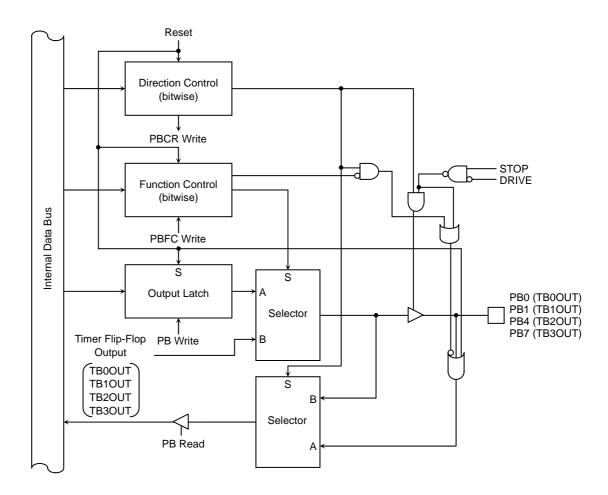

| f | PB0           | 1              | Input/Output           | Port B0: Programmable as input or output                                                               |

|   | TB0OUT        |                | Output                 | 16-Bit Timer 0 Output: Output from 16-bit timer 0                                                      |

| ľ | PB1           | 1              | Input/Output           | Port B1: Programmable as input or output                                                               |

| ı | TB1OUT        |                | Output                 | 16-Bit Timer 1 Output: Output from 16-bit timer 1                                                      |

| L |               | l .            | •                      | · ·                                                                                                    |

Table 2.2 Pin Names and Functions (3/6)

|   | Pin Name    | Number of Pins | Туре         | Function                                                                      |

|---|-------------|----------------|--------------|-------------------------------------------------------------------------------|

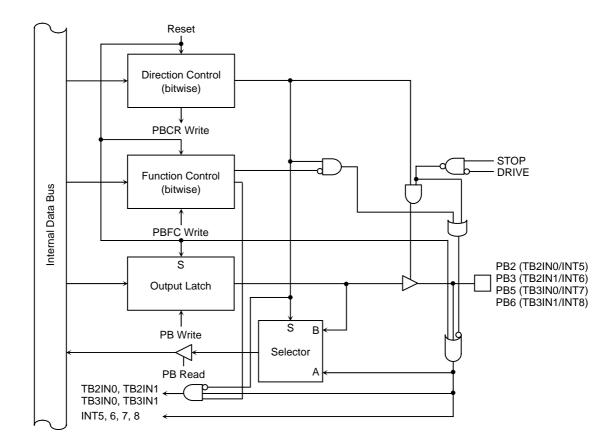

| ľ | PB2         | 1              | Input/Output | Port B2: Programmable as input or output                                      |

|   | TB2IN0      |                | Input        | 16-Bit Timer 2 Input 0: Count/capture trigger input to 16-bit timer 2         |

|   | INT5        |                | Input        | Interrupt Request 5: Programmable to be high-level, low-level, rising-edge or |

|   |             |                |              | falling-edge sensitive                                                        |

| ĺ | PB3         | 1              | Input/Output | Port B3: Programmable as input or output                                      |

|   | TB2IN1      |                | Input        | 16-Bit Timer 2 Input 1: Capture trigger input to 16-bit timer 2               |

|   | INT6        |                | Input        | Interrupt Request 6: Programmable to be high-level, low-level, rising-edge or |

|   |             |                |              | falling-edge sensitive                                                        |

|   | PB4         | 1              | Output       | Port B4: Programmable as input or output                                      |

|   | TB2OUT      |                | Output       | 16-Bit Timer 2 Output: Output from 16-bit timer 2                             |

| e | PB5         | 1              | Output       | Port B5: Programmable as input or output                                      |

|   | TB3IN0      |                | Input        | 16-Bit Timer 3 Input 0: Count/capture trigger input to 16-bit timer 3         |

|   | INT7        |                | Input        | Interrupt Request 7: Programmable to be high-level, low-level, rising-edge or |

|   |             |                |              | falling-edge sensitive                                                        |

|   | PB6         | 1              | Output       | Port B6: Programmable as input or output                                      |

|   | TB3IN1      |                | Input        | 16-Bit Timer 3 Input 1: Capture trigger input to 16-bit timer 3               |

|   | INT8        |                | Input        | Interrupt Request 8: Programmable to be high-level, low-level, rising-edge or |

|   |             |                |              | falling-edge sensitive                                                        |

| ĺ | PB7         | 1              | Output       | Port B7: Programmable as input or output                                      |

|   | TB3OUT      |                | Output       | 16-Bit Timer 3 Output: Output from 16-bit timer 3                             |

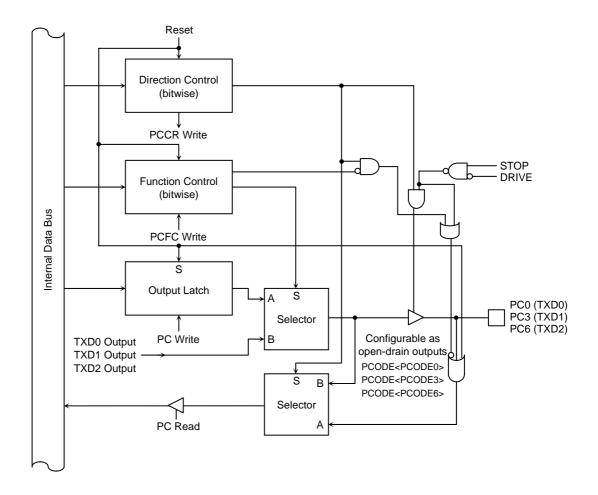

| Í | PC0         | 1              | Input/Output | Port C0: Programmable as input or output                                      |

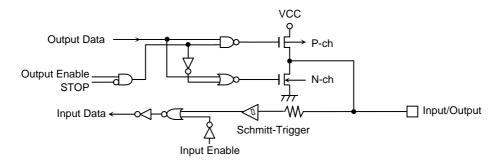

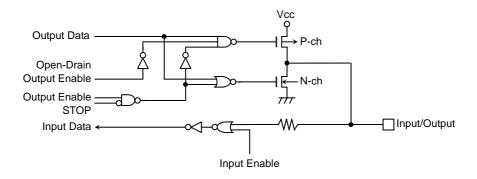

|   | TXD0        |                | Output       | Serial Transmit Data 0: Programmable as a push-pull or open-drain output      |

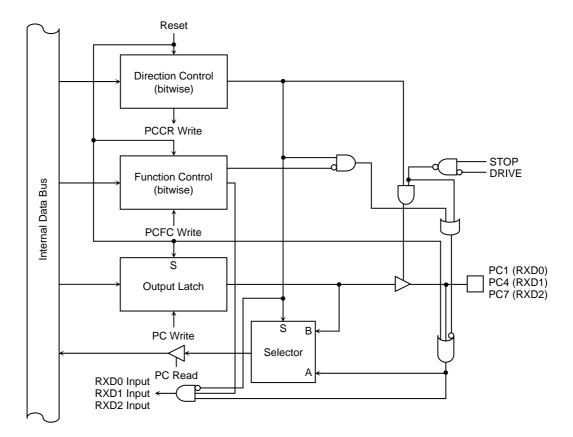

|   | PC1         | 1              | Input/Output | Port C1: Programmable as input or output                                      |

|   | RXD0        |                | Input        | Serial Receive Data 0                                                         |

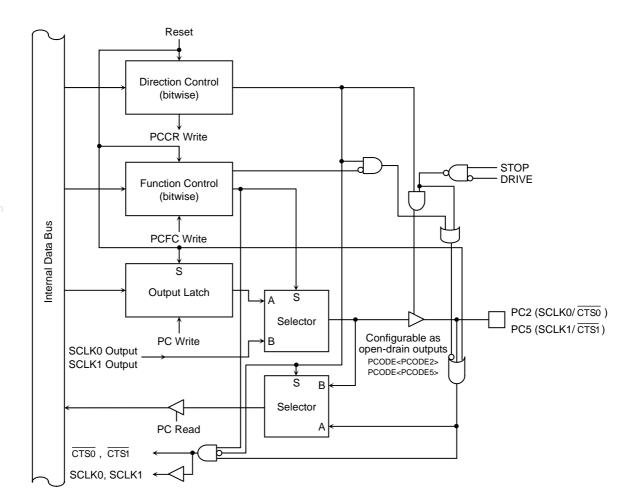

| ĺ | PC2         | 1              | Input/Output | Port C2: Programmable as input or output                                      |

|   | SCLK0       |                | Input        | Serial Clock Input/Output 0                                                   |

|   | CTS0        |                | Input        | Serial Clear-to-Send 0: Programmable as a push-pull or open-drain output      |

| Ī | PC3         | 1              | Input/Output | Port C3: Programmable as input or output                                      |

|   | TXD1        |                | Output       | Serial Transmit Data 1: Programmable as a push-pull or open-drain output      |

| İ | PC4         | 1              | Input/Output | Port C4: Programmable as input or output                                      |

|   | RXD1        |                | Input        | Serial Receive Data 1                                                         |

| İ | PC5         | 1              | Input/Output | Port C5: Programmable as input or output                                      |

|   | SCLK1       |                | Input        | Serial Clock Input/Output 1                                                   |

|   | CTS1        |                | Input        | Serial Clear-to-Send 1: Programmable as a push-pull or open-drain output      |

| ĺ | PC6         | 1              | Input/Output | Port C6: Programmable as input or output                                      |

|   | TXD2        |                | Output       | Serial Transmit Data 2: Programmable as a push-pull or open-drain output      |

| İ | PC7         | 1              | Input/Output | Port C7: Programmable as input or output                                      |

|   | RXD2        |                | Input        | Serial Receive Data 2                                                         |

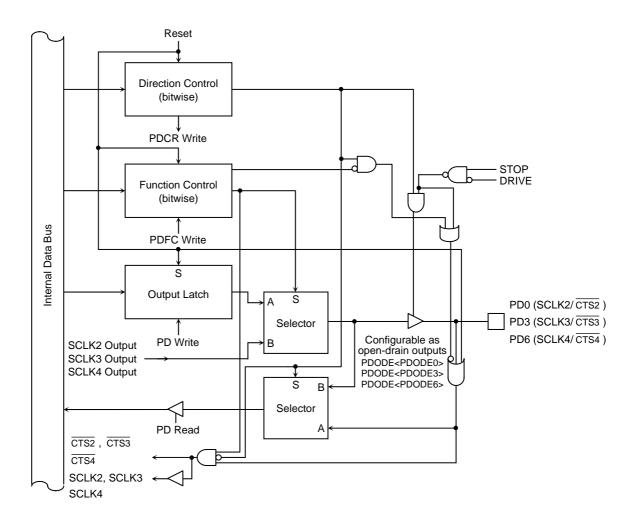

| j | PD0         | 1              | Input/Output | Port D0: Programmable as input or output                                      |

|   | SCLK2       |                | Input        | Serial Clock Input/Output 2                                                   |

| ı | CTS2        |                | Input        | Serial Clear-to-Send 2: Programmable as a push-pull or open-drain output      |

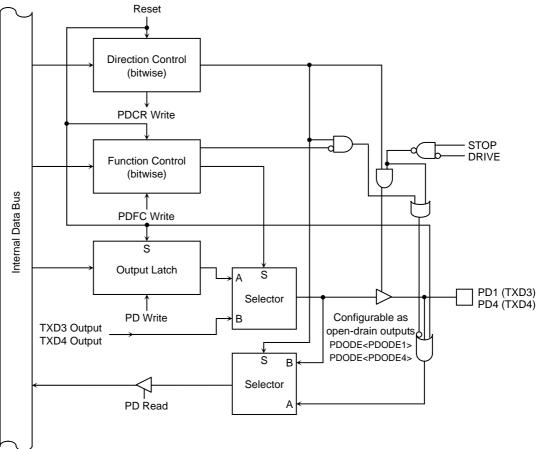

| ı | PD1         | 1              | Input/Output | Port D1: Programmable as input or output                                      |

| ı | TXD3        |                | Output       | Serial Transmit Data 3: Programmable as a push-pull or open-drain output      |

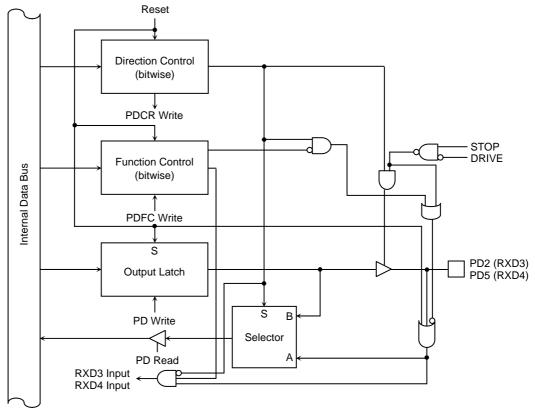

| j | PD2         | 1              | Input/Output | Port D2: Programmable as input or output                                      |

| Į | RXD3        |                | Input        | Serial Receive Data 3                                                         |

| j | PD3         | 1              | Input/Output | Port D3: Programmable as input or output                                      |

| ı | SCLK3       |                | Input        | Serial Clock Input/Output 3                                                   |

| ı | CTS3        |                | Input        | Serial Clear-to-Send 3: Programmable as a push-pull or open-drain output      |

| ı | PD4         | 1              | Input/Output | Port D4: Programmable as input or output                                      |

| ١ | TXD4        |                | Output       | Serial Transmit Data 4: Programmable as a push-pull or open-drain output      |

| ı | PD5         | 1              | Input/Output | Port D5: Programmable as input or output                                      |

| Į | RXD4        |                | Input        | Serial Receive Data 4                                                         |

| j | PD6         | 1              | Input/Output | Port D6: Programmable as input or output                                      |

| ı | SCLK4       |                | Input        | Serial Clock Input/Output 4                                                   |

| ı | CTS4        |                | Input        | Serial Clear-to-Send 4: Programmable as a push-pull or open-drain output      |

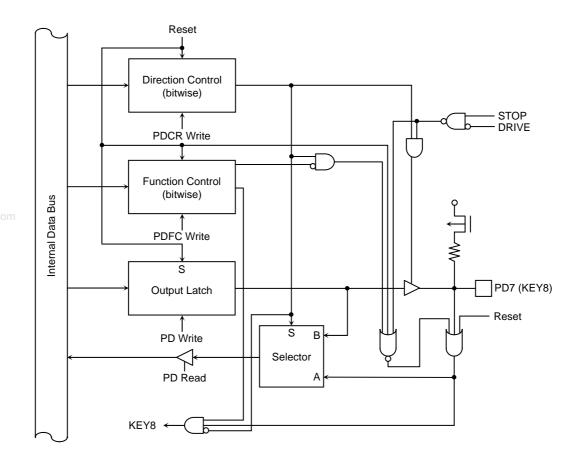

| ı | PD7         | 1              | Input/Output | Port D7: Programmable as input or output                                      |

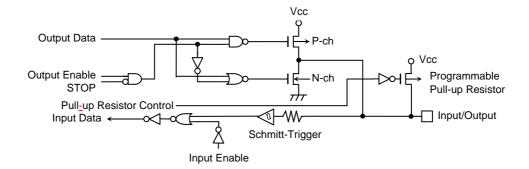

| ١ | KEY8        | '              | Input        | Key-Pressed Wake-up Input 8 (with internal pull-up resistor): Dynamic pull-up |

|   | <del></del> |                | 1p           | selectable                                                                    |

| Į |             |                |              | Schmitt-triggered input                                                       |

| 1 |             |                |              |                                                                               |

Table 2.2 Pin Names and Functions (4/6)

| Pin Name                     | Number of Pins | Туре                                   | Function                                                                                                                                                                                                                                                |

|------------------------------|----------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

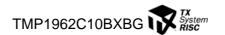

| PE0<br>TXD5                  | 1              | Input/Output<br>Output                 | Port E0: Programmable as input or output<br>Serial Transmit Data 5: Programmable as a push-pull or open-drain output                                                                                                                                    |

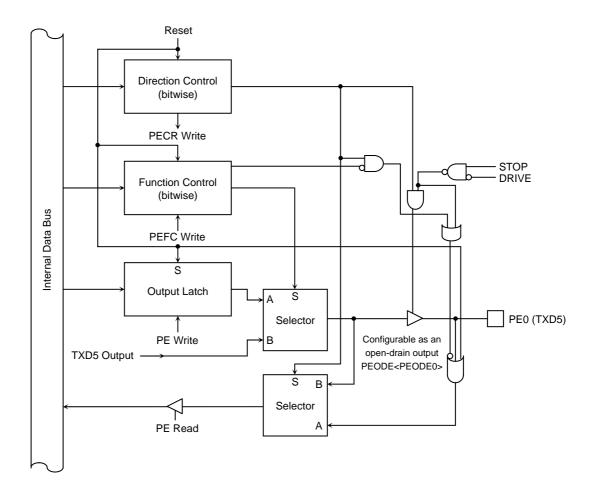

| PE1<br>RXD5                  | 1              | Input/Output<br>Input                  | Port E1: Programmable as input or output<br>Serial Receive Data 5                                                                                                                                                                                       |

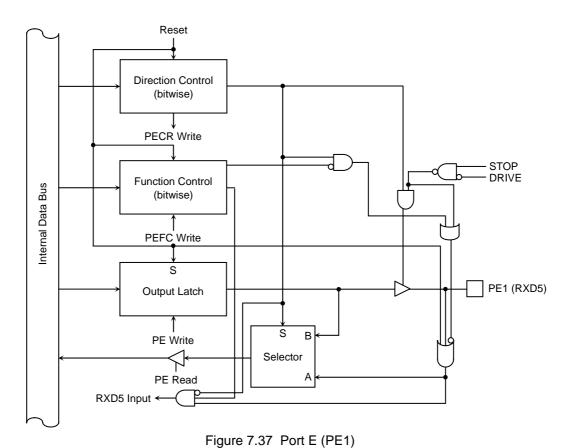

| PE2<br>SCLK5<br>CTS5         | 1              | Input/Output<br>Input<br>Input         | Port E2: Programmable as input or output<br>Serial Clock Input/Output 5<br>Serial Clear-to-Send 5: Programmable as a push-pull or open-drain output                                                                                                     |

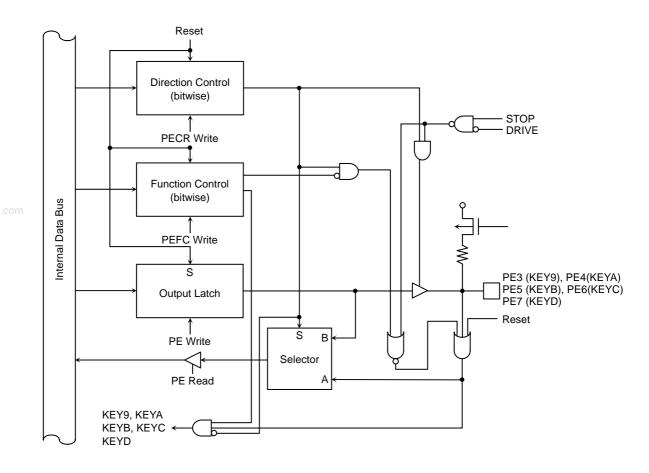

| PE3<br>KEY9                  | 1              | Input/Output<br>Input                  | Port E3: Programmable as input or output Key-Pressed Wake-up Input 9 (with internal pull-up resistor): Dynamic pull-up selectable                                                                                                                       |

| PE4<br>KEYA                  | 1              | Input/Output<br>Input                  | Schmitt-triggered input  Port E4: Programmable as input or output Key-Pressed Wake-up Input A (with internal pull-up resistor): Dynamic pull-up selectable Schmitt-triggered input                                                                      |

| PE5<br>KEYB                  | 1              | Input/Output<br>Input                  | Port E5: Programmable as input or output Key-Pressed Wake-up Input B (with internal pull-up resistor): Dynamic pull-up selectable Schmitt-triggered input                                                                                               |

| PE6<br>KEYC                  | 1              | Input/Output<br>Input                  | Port E6: Programmable as input or output Key-Pressed Wake-up Input C (with internal pull-up resistor): Dynamic pull-up selectable Schmitt-triggered input                                                                                               |

| PE7<br>KEYD                  | 1              | Input/Output<br>Input                  | Port E7: Programmable as input or output Key-Pressed Wake-up Input D (with internal pull-up resistor): Dynamic pull-up selectable Schmitt-triggered input                                                                                               |

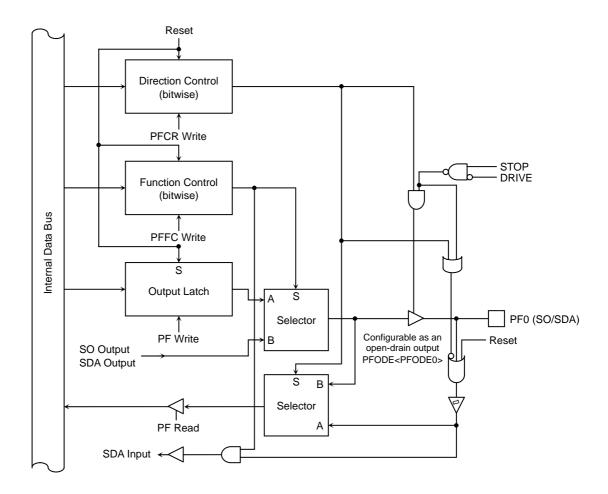

| PF0<br>SO<br>SDA             | 1              | Input/Output<br>Output<br>Input/Output | Port F0: Programmable as input or output Data transmit pin when the Serial Bus Interface is in SIO mode Data transmit/receive pin when the Serial Bus Interface is in I2C mode Programmable as a push-pull or open-drain output Schmitt-triggered input |

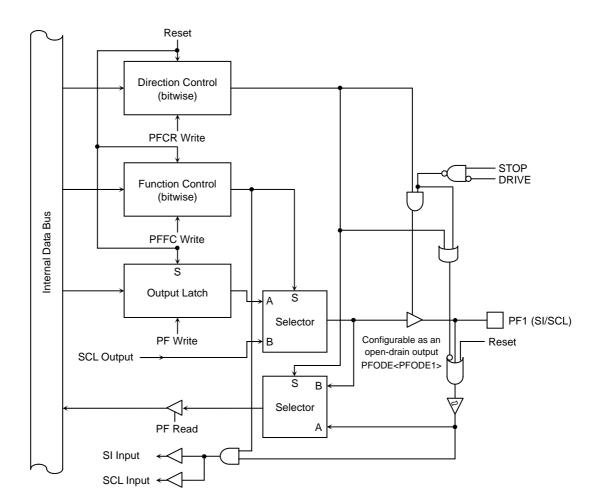

| PF1<br>SI<br>SCL             | 1              | Input/Output<br>Input<br>Input/Output  | Port F1: Programmable as input or output Data receive pin when the Serial Bus Interface is in SIO mode Clock input/output pin when the Serial Bus Interface is in I2C mode Programmable as a push-pull or open-drain output Schmitt-triggered input     |

| PF2<br>SCK                   | 1              | Input/Output<br>Input/Output           | Port F2: Programmable as input or output Clock input/output pin when the Serial Bus Interface is in SIO mode                                                                                                                                            |

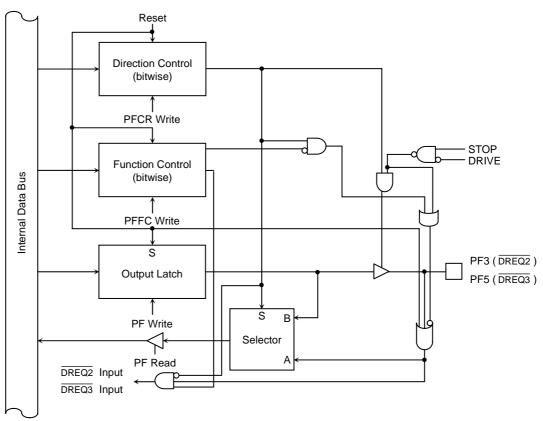

| PF3<br>DREQ2                 | 1              | Input/Output<br>Input                  | Port F3: Programmable as input or output  DMA Request 2: Asserted by an external input/output device to request DMA transfer with DMAC2                                                                                                                 |

| PF4<br>DACK2                 | 1              | Input/Output<br>Output                 | Port F4: Programmable as input or output  DMA Acknowledge 2: Indicates acknowledgement for a DMA transfer request made with DREQ2                                                                                                                       |

| PF5<br>DREQ3                 | 1              | Input/Output<br>Input                  | Port F5: Programmable as input or output  DMA Request 3: Asserted by an external input/output device to request DMA transfer with DMAC3                                                                                                                 |

| PF6<br>DACK3                 | 1              | Input/Output<br>Output                 | Port F6: Programmable as input or output  DMA Acknowledge 3: Indicates acknowledgement for a DMA transfer request made with DREQ3                                                                                                                       |

| PF7<br>TBTIN                 | 1              | Input/Output<br>Input                  | Port F7: Programmable as input or output 32-Bit Time Base Timer Input: Count input to the 32-bit time base timer                                                                                                                                        |

| PG0 - PG7<br>TC0IN - TC7IN   | 8              | Input/Output<br>Input                  | Port G: Individually programmable as input or output 32-Bit Timer Capture Trigger Input                                                                                                                                                                 |

| PH0 - PH7<br>TCOUT0 - TCOUT7 | 8              | Input/Output<br>Output                 | Port H: Individually programmable as input or output 32-Bit Timer Compare Match Output                                                                                                                                                                  |

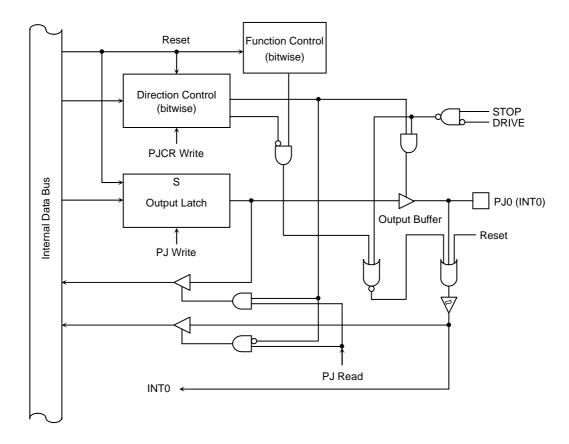

| PJ0<br>INT0                  | 1              | Input/Output<br>Input                  | Port J0: Programmable as input or output Interrupt Request 0: Programmable to be high-level, low-level, rising-edge or falling-edge sensitive Schmitt-triggered input                                                                                   |

Table 2.2 Pin Names and Functions (5/6)

| Pin Name                 | Number of Pins | Туре                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------------------------|----------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PJ1<br>BUSMD             | 1              | Input/Output<br>Input | Port J1: Programmable as input or output  External Bus Mode: Multiplexed Bus mode is selected if this signal is sampled high on the rising edge of the reset signal. Separate Bus mode is selected if this signal is sampled low on the rising edge of the reset signal. The BUSMD pin should be pulled up or down upon a reset according to the bus mode to be used.                                                             |  |  |

| PJ2                      | 1              | Input/Output<br>Input | Port J2: Programmable as input or output Single Boot Mode: Single Boot mode is selected if this signal is sampled low on the rising edge of the reset signal. Single Boot mode is used to rewrite the contents of on-chip flash memory. Normal operation is selected if the signal is sampled high on the rising edge of the reset signal. When performing normal operation, the BOOT pin should not be pulled down upon a reset. |  |  |

| PJ3                      | 1              | Input/Output<br>Input | Port J3: Programmable as input or output Interleave Mode: Interleave mode is selected if this signal is sampled high on the rising edge of the reset signal. The INTLV pin should be pulled up when using Interleave mode. Otherwise, it should be pulled down.                                                                                                                                                                   |  |  |

| PJ4<br>ENDIAN            | 1              | Input/Output<br>Input | Port J4: Programmable as input or output Endian Mode: Big-Endian mode is selected if this signal is sampled high on the rising edge of the reset signal. Little-Endian mode is selected if this signal is sampled low on the rising edge of the reset signal.                                                                                                                                                                     |  |  |

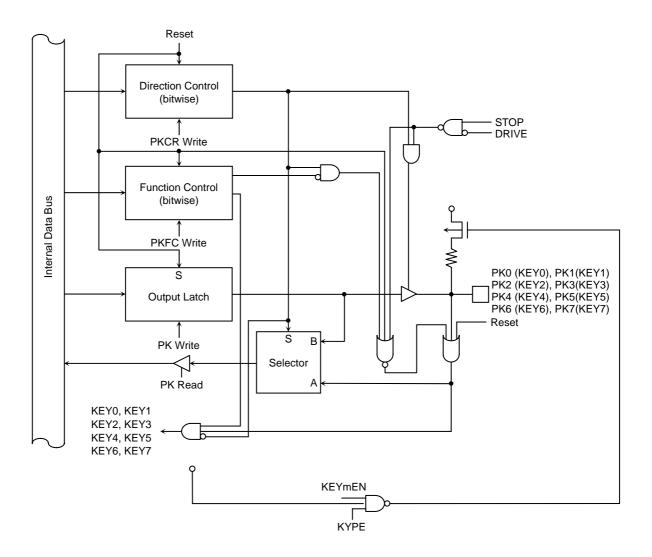

| PK0 - PK7<br>KEY0 - KEY7 | 8              | Input/Output<br>Input | Port K: Individually programmable as input or output Key-Pressed Wake-up Input 0 to 7 (with internal pull-up resistor): Dynamic pull-up selectable Schmitt-triggered input                                                                                                                                                                                                                                                        |  |  |

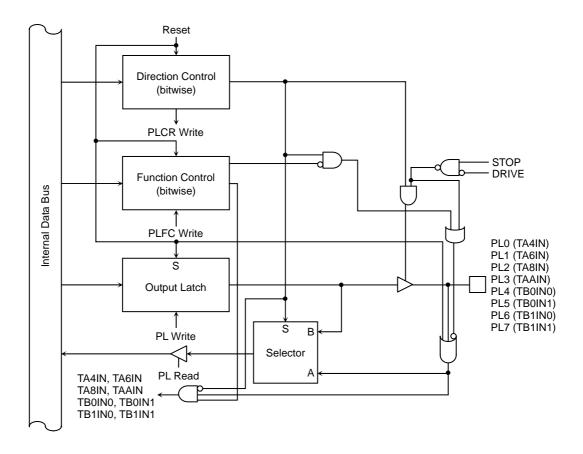

| PL0<br>TA4IN             | 1              | Input/Output<br>Input | Port L0: Programmable as input or output<br>8-Bit Timer 4 Input: Input to 8-bit timer 4                                                                                                                                                                                                                                                                                                                                           |  |  |

| PL1<br>TA6IN             | 1              | Input/Output<br>Input | Port L1: Programmable as input or output  8-Bit Timer 6 Input: Input to 8-bit timer 6                                                                                                                                                                                                                                                                                                                                             |  |  |

| PL2<br>TA8IN             | 1              | Input/Output<br>Input | Port L2: Programmable as input or output  8-Bit Timer 8 Input: Input to 8-bit timer 8                                                                                                                                                                                                                                                                                                                                             |  |  |

| PL3<br>TAAIN             | 1              | Input/Output<br>Input | Port L3: Programmable as input or output  8-Bit Timer A Input: Input to 8-bit timer A                                                                                                                                                                                                                                                                                                                                             |  |  |

| PL4<br>TB0IN0            | 1              | Input/Output<br>Input | Port L4: Programmable as input or output 16-Bit Timer 0 Input 0: Count/capture trigger input to 16-bit timer 0                                                                                                                                                                                                                                                                                                                    |  |  |

| PL5<br>TB0IN1            | 1              | Input/Output<br>Input | Port L5: Programmable as input or output 16-Bit Timer 0 Input 1: Capture trigger input to 16-bit timer 0                                                                                                                                                                                                                                                                                                                          |  |  |

| PL6<br>TB1IN0            | 1              | Input/Output<br>Input | Port L6: Programmable as input or output  16-Bit Timer 1 Input 0: Count/capture trigger input to 16-bit timer 1                                                                                                                                                                                                                                                                                                                   |  |  |

| PL7<br>TB1IN1            | 1              | Input/Output<br>Input | Port L7: Programmable as input or output  16-Bit Timer 1 Input 1: Capture trigger input to 16-bit timer 1                                                                                                                                                                                                                                                                                                                         |  |  |

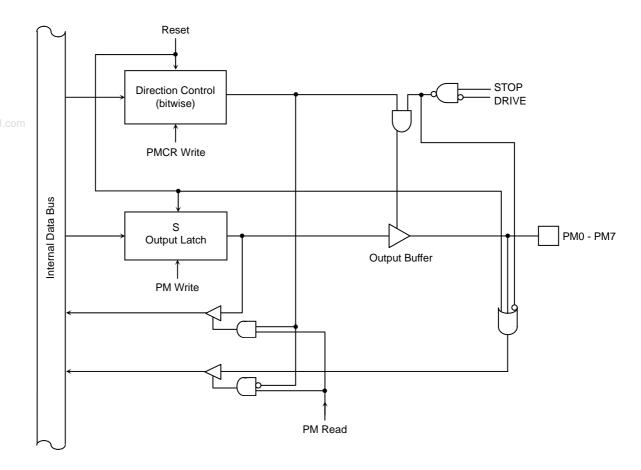

| PM0 - PM7                | 8              | Input/Output          | Port M: Individually programmable as input or output                                                                                                                                                                                                                                                                                                                                                                              |  |  |

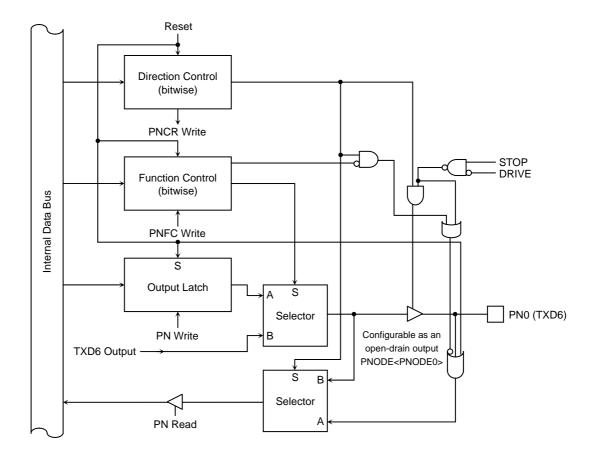

| PN0<br>TXD6              | 1              | Input/Output Output   | Port N0: Programmable as input or output Serial Transmit Data 6: Programmable as a push-pull or open-drain output                                                                                                                                                                                                                                                                                                                 |  |  |

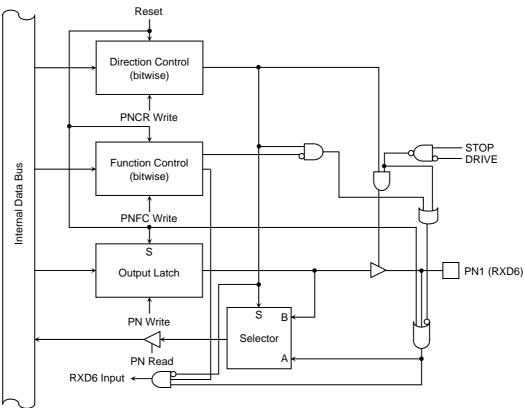

| PN1                      | 1              | Input/Output          | Port N1: Programmable as input or output                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| RXD6                     |                | Input                 | Serial Receive Data 6                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

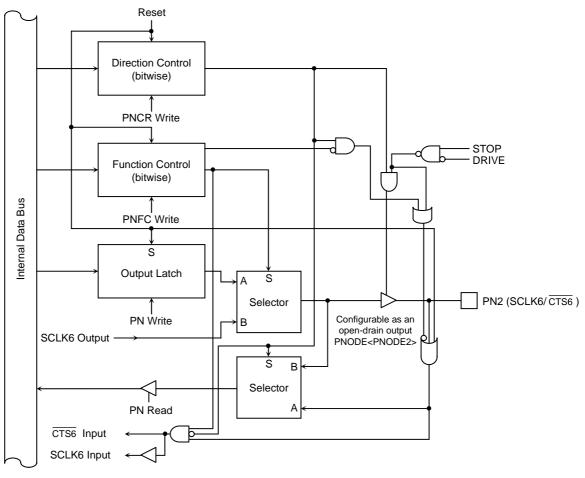

| PN2                      | 1              | Input/Output          | Port N2: Programmable as input or output                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| SCLK6                    |                | Input                 | Serial Clock Input/Output 6                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| CTS6                     |                | Input                 | Serial Clear-to-Send 6: Programmable as a push-pull or open-drain output                                                                                                                                                                                                                                                                                                                                                          |  |  |

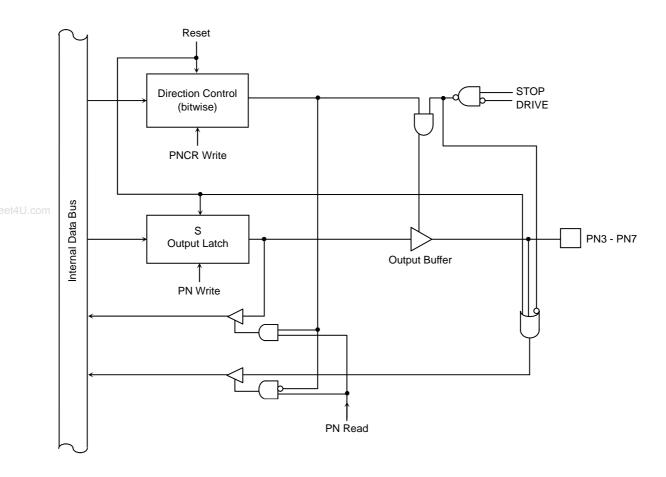

| PN3 - PN7                | 5              | Input/Output          | Port N3 to N7: Individually programmable as input or output                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| P00 - P07                | 8              | Input/Output          | Port O: Individually programmable as input or output                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PP0 - PP7                | 8              | Input/Output          | Port P: Individually programmable as input or output                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Table 2.2 Pin Names and Functions (6/6)

| Pin Name    | Number of Pins | Туре         | Function                                                                                                                                                             |

|-------------|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

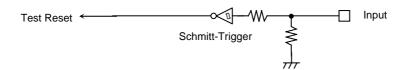

| NMI         | 1              | Input        | Nonmaskable Interrupt Request: Causes an NMI interrupt on the falling edge<br>Schmitt-triggered input                                                                |

| PLLOFF      | 1              | Input        | This pin should be tied to logic 1 when the frequency multiplied clock from the PLL is used; otherwise, it should be tied to logic 0 (Schmitt-triggered input).      |

| RSTPUP      | 1              | Input        | Pull-up resistors for Ports 3 and 4 are enabled if this signal is sampled high upon a reset; otherwise, the pull-up resistors are disabled.  Schmitt-triggered input |

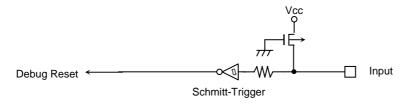

| RESET       | 1              | Input        | Reset (with internal pull-up resistor): Initializes the whole TMP1962. Schmitt-triggered input                                                                       |

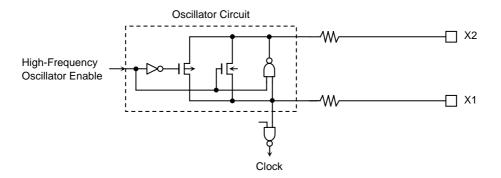

| X1/X2       | 2              | Input/Output | Connection pins for a high-speed resonator                                                                                                                           |

| DRESET      | 1              | Input        | Debug Reset: Signal for a DSU-ICE (Schmitt-triggered input with internal pull-up resistor)                                                                           |

| DCLK        | 1              | Output       | Debug Clock: Signal for a DSU-ICE                                                                                                                                    |

| DBGE        | 1              | Input        | Debug Enable: Signal for a DSU-ICE (Schmitt-triggered input with internal pull-up resistor)                                                                          |

| PCST3 - 0   | 4              | Output       | PC Trace Status: Signals for a DSU-ICE                                                                                                                               |

| SDI/ DINT   | 1              | Input        | Serial Data Input/Debug Interrupt: Signal for a DSU-ICE (Schmitt-triggered input with internal pull-up resistor)                                                     |

| SDAO/TPC    | 1              | Output       | Serial Data Address Output/Target PC: Signal for a DSU-ICE                                                                                                           |

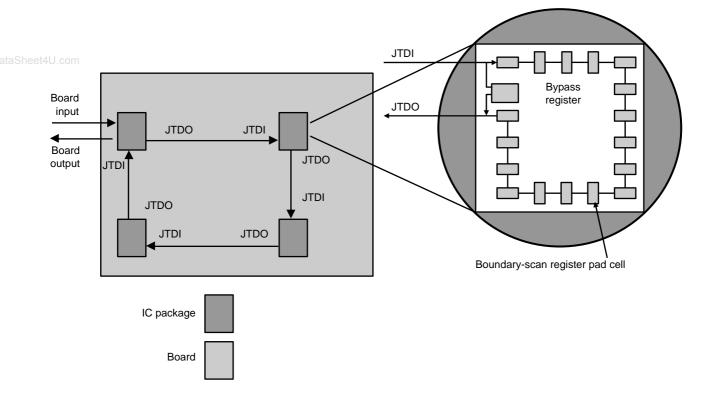

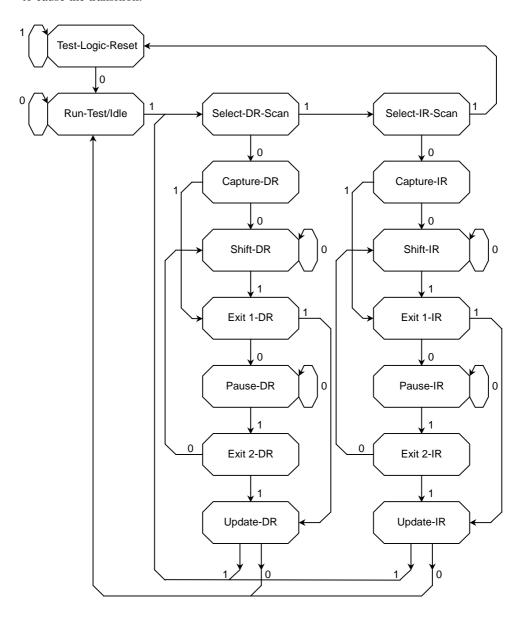

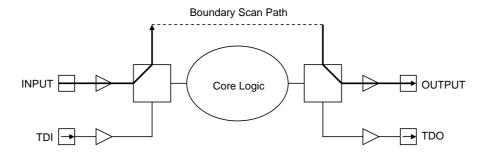

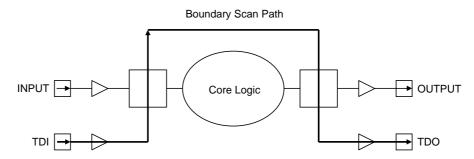

| TCK         | 1              | Input        | Test Clock Input: JTAG test signal (Schmitt-triggered input with internal pull-up resistor)                                                                          |

| TMS         | 1              | Input        | Test Mode Select Input: JTAG test signal (Schmitt-triggered input with internal pull-up resistor)                                                                    |

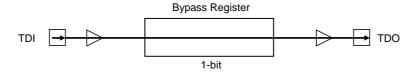

| TDI         | 1              | Input        | Test Data Input: JTAG test signal (Schmitt-triggered input with internal pull-up resistor)                                                                           |

| TDO         | 1              | Output       | Test Data Output: JTAG test signal                                                                                                                                   |

| TRST        | 1              | Input        | Test Reset Input: JTAG test signal (Schmitt-triggered input with internal pull-down resistor)                                                                        |

| BW0 - 1     | 2              | Input        | Both BW0 and BW1 should be tied to logic 1 (Schmitt-triggered input).                                                                                                |

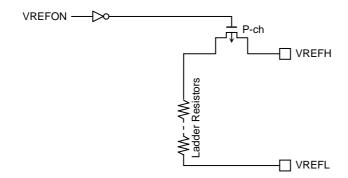

| VREFH       | 1              | Input        | Input pin for high reference voltage for the A/D Converter. This pin should be connected to the AVCC pin when the A/D Converter is not used.                         |

| VREFL       | 1              | Input        | Input pin for low reference voltage for the A/D Converter. This pin should be connected to the AVSS pin when the A/D Converter is not used.                          |

| AVCC31 - 32 | 2              |              | Power supply pins for the A/D Converter. These pins should always be connected to power supply even when the A/D Converter is not used.                              |

| AVSS        | 3              | _            | Ground pin for the A/D Converter. This pin should always be connected to ground even when the A/D Converter is not used.                                             |

| TEST5       | 1              | Input        | Test pin: This pin should be tied to ground.                                                                                                                         |

| SYSRDY      | 1              | Output       | Flash memory access enable                                                                                                                                           |

| CVCC15      | 1              | _            | 1.5-V power supply pin for the oscillator                                                                                                                            |

| CVSS        | 1              | _            | Ground pin (0 V) for the oscillator                                                                                                                                  |

| DVCC15      | 1              | _            | 1.5-V power supply pin                                                                                                                                               |

| DVCC2       | 5              |              | 2-V power supply pin                                                                                                                                                 |

| DVCC31 - 34 | 9              | _            | 3-V power supply pins                                                                                                                                                |

| DVSS        | 9              |              | Ground pin (0 V)                                                                                                                                                     |

Note: PJ1, PJ2, PJ3 and PJ4 should be held at the prescribed logic states for one system clock cycle before and after the rising edge of RESET, with the RESET signal being stable in either logic state.

Table 2.3 shows the correspondence between pins and power supply pins.

Table 2.3 Pins and Corresponding Power Supply Pins

| Pin  | Power     | Supply     | Pin       | Power Supply |            |  |

|------|-----------|------------|-----------|--------------|------------|--|

| FIII | Mask Type | Flash Type | FIII      | Mask Type    | Flash Type |  |

| P0   | DVCC33    | DVCC33     | PP        | DVCC31       | DVCC31     |  |

| P1   | DVCC33    | DVCC33     | X1        | CVCC15       | CVCC2      |  |

| P2   | DVCC33    | DVCC33     | X2        | CVCC15       | CVCC2      |  |

| P3   | DVCC33    | DVCC33     | RESET     | DVCC2        | DVCC21     |  |

| P4   | DVCC33    | DVCC33     | NMI       | DVCC2        | DVCC21     |  |

| P5   | DVCC33    | DVCC33     | PLLOFF    | DVCC2        | DVCC21     |  |

| P6   | DVCC33    | DVCC33     | DRESET    | DVCC2        | DVCC21     |  |

| P7   | AVCC32    | AVCC32     | DCLK      | DVCC2        | DVCC21     |  |

| P8   | AVCC32    | AVCC32     | DBGE      | DVCC2        | DVCC21     |  |

| P9   | AVCC31    | AVCC31     | PCST3 - 0 | DVCC2        | DVCC21     |  |

| PA   | DVCC32    | DVCC32     | SDI/ DINT | DVCC2        | DVCC21     |  |

| PB   | DVCC32    | DVCC32     | SDAO/TPC  | DVCC2        | DVCC21     |  |

| PC   | DVCC32    | DVCC32     | TCK       | DVCC34       | DVCC34     |  |

| PD   | DVCC32    | DVCC32     | TMS       | DVCC34       | DVCC34     |  |

| PE   | DVCC32    | DVCC32     | TDI       | DVCC34       | DVCC34     |  |

| PF   | DVCC32    | DVCC32     | TDO       | DVCC34       | DVCC34     |  |

| PG   | DVCC32    | DVCC32     | TRST      | DVCC34       | DVCC34     |  |

| PH   | DVCC32    | DVCC32     | BW1 - 0   | DVCC2        | DVCC21     |  |

| PI   | DVCC34    | DVCC34     | RSTPUP    | DVCC32       | DVCC32     |  |

| PJ   | DVCC2     | DVCC21     | G3        | DVCC2        | FVCC2      |  |

| PK   | DVCC34    | DVCC34     | G18       | NC           | FVCC2      |  |

| PL   | DVCC34    | DVCC34     | K5        | NC           | FVSS       |  |

| PM   | DVCC34    | DVCC34     | L1        | NC           | FVCC       |  |

| PN   | DVCC31    | DVCC31     | L15       | NC           | FVCC2      |  |

| PO   | DVCC31    | DVCC31     | M15       | NC           | FVSS       |  |

www.DataSheet4U.com

Table 2.4 shows the supply voltage for power supply pins.

Table 2.4 Supply Voltage for Power Supply Pins

| Power Supply Pin | Supply Voltage  | Applied for         |  |  |

|------------------|-----------------|---------------------|--|--|

| DVCC15           | 1.35 V - 1.65 V |                     |  |  |

| CVCC15           | 1.35 V - 1.65 V | Mask Type           |  |  |

| DVCC2            | 2.3 V - 3.3 V   |                     |  |  |

| DVCC21           | 2.2 V - 2.7 V   |                     |  |  |

| DVCC22           | 2.2 V - 2.7 V   |                     |  |  |

| CVCC2            | 2.2 V - 2.7 V   | Flash Type          |  |  |

| FVCC2            | 2.2 V - 2.7 V   |                     |  |  |

| FVCC3            | 2.9 V - 3.6 V   |                     |  |  |

| DVCC31 - 34      | 1.65 V - 3.3 V  | Mask/Flash Type     |  |  |

| AVCC31 - 32      | 2.7 V - 3.3 V   | iviasivi iasii Type |  |  |

w.DataSheet4U.com

#### Note 1: AVCC32 ≤ AVCC31

. When P7 to P9 are used as A/D converter inputs:

2.7 V < AVCC3\*

When P9 (powered by AVCC31) is used as an A/D converter input while P7 and P8 (powered by AVCC32) are used as ports:

$2.7 \text{ V} \le \text{AVCC31} \le 3.3 \text{ V}$  $1.65 \text{ V} \le \text{AVCC32} \le \text{AVCC31}$

When P7 (powered by AVCC32) is used as an A/D converter input while P8 (powered by AVCC32) and P9 (powered by AVCC31) are used as ports:

$2.7 \text{ V} \leq \text{AVCC32} \leq \text{AVCC31} \leq 3.3 \text{ V}$

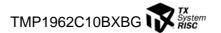

Note 2: With power supplies for CPU and internal logic (mask type: DVCC15/DVCC2/CVCC15, and flash type: DVCC21/DVCC22/CVCC2/FVCC2/FVCC3) being applied, power supplies for other I/O ports can be interrupted on TMP1962. However, when AVCC31 for analog power supply is interrupted, overlap current is generated on the TMP1962F10AXBG with on-chip flash memory during the transition to be stable in 0 V. Overlap current can be suppressed by AD conversion of the conversion result 0 V before interrupting AVCC31 power supply, but please suppress it on devices.

### Core Processor

The TMP1962 contains a high-performance 32-bit core processor called the TX19. For a detailed description of the core processor, refer to the TX19 Family Architecture manual.

Functions unique to the TMP1962, which are not covered in the architecture manual, are described below.

### 3.1 Reset Operation

To reset the TMP1962, RESET must be asserted for at least 12 system clock periods after the power supply voltage and the internal high-frequency oscillator have stabilized. This time is typically  $2.37~\mu s$  at 40.5~MHz when the on-chip PLL is utilized.

After a reset, either the PLL-multiplied clock or an external clock is selected, depending on the logic state of the PLLOFF pin. By default, the selected clock is geared down to 1/8 for internal operation.

The following occurs as a result of a reset:

- The System Control Coprocessor (CP0) registers within the TX19 core processor are initialized. For details, refer to the architecture manual.

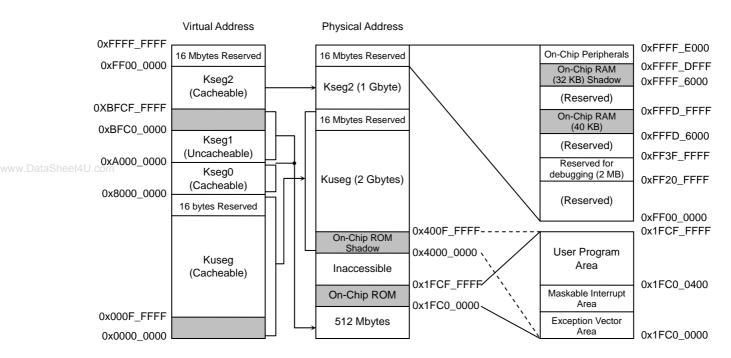

- The Reset exception is taken. Program control is transferred to the exception handler at a predefined address. This predefined location is called an exception vector, which directly indicates the start of the actual exception handler routine. The Reset exception is always vectored to virtual address 0xBFC0\_0000 (which is the same as for the Nonmaskable Interrupt exception).

- All on-chip I/O peripheral registers are initialized.

- All port pins, including those multiplexed with on-chip peripheral functions, are configured as either general-purpose inputs or general-purpose outputs.

Note 1: The TMP1962 must be powered up with RESET asserted. The reset state should not be terminated until after the power supply voltage stabilizes within the valid operating range.