## TMP 4321AP

TOSHIBA MOS Digital Integrated Circuit

Silicon Monolithic

N-channel Silicon Gate Depression Load

#### GENERAL DESCRIPTION

TMP4321AP is one version of single-chip microcomputer TLCS43 series processed with NMOS.

Since TMP4321AP can make periodic interrupt gained by dividing the CPU clock to 512 or 1024 using the built-in prescaler, it is most appropriate for computer control, such as sequence control.

Refer to the technical data of TLCS43 when using or considering TMP4321AP.

#### **FEATURES**

- o Software compatible with TLCS43 series

- o ROM capacity: 2048W x 8 Bits

- o RAM capacity: 128W x 4 Bits

- o Instruction executing rate: 4 μs

- o Input ports: 3 x 4 Bits

- o Input/output ports: 2 x 4 Bits

- Output ports: 3 x 4 Bits

1 x 3 Bits

- o Interrupt level: 1 level (Interrupt by timer)

- o Subroutine nesting: 4 levels (including interrupt

- o ROM data readout instructions

- o I/O level: TTL compatible

- o Ports available for large current output: 2 x 4 Bits

- o +5V single power operating (operating voltage margin: 5V  $\pm$  10%)

- o Operating temperature range: -10 ~ 70°C

TEST 1 D V DD INOO 2 41 | IN10 40 | IN11 INO, IS INO2 4 39 IN12 38 IN13 INO3 5 IN20 ото₀ 🛛 6 ото1 🛮 7 36 NIN21 35 | IN22 0T02 8 OTO3 09 34 | IN23 OT10 10 33 11010 от ј д 🗖 11 1011 OT12 12 33 1012 от 1 3 🗖 13 30 1013 0T20 4 1000 29 OT21 15 28 1001 ОТ22 □16 27 1000 OT23 **1**17 26 🛛 100<sub>5</sub> отзо □18 25 DX OUT OT3 1 19 24 **P**XIN OT32 20 23 DRST GND 21 22 INT

PIN CONNECTIONS

#### TIMER INTERRUPT

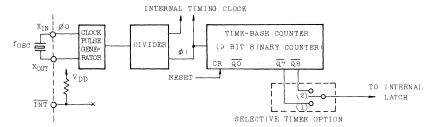

The following figure shows the configuration of timer interrupt circuit of TMP4321AP.

As shown in the above figure, interrupt is not caused by external source via  $\overline{\text{INT}}$  pin, but it is only caused by the output divided by the built-in prescaler. The  $\overline{\text{INT}}$  pin is usually set to "H" level (open) by the pull-up resistor, but it is not connected with the internal circuit.

Assignment of selective timer option is as follows:

- (1) Option INTDV7 is interrupted at  $\frac{1}{\text{fosc}}$  x 512(S) cycle ( $\overline{\text{Q7}}$ ).

- (2) Option INTDV8 is interrupted at  $\frac{1}{\text{fosc}}$  x 1024(S) cycle ( $\overline{\text{Q8}}$ ).

(Refer to "Mask Option Assignment" in the technical data of TLCS43 for further details.)

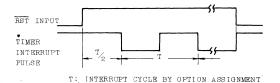

The relation between timer interrupt and reset is shown in the following figure.

Initial interrupt occurs at T/2 interval after the  $\overline{RST}$  input is released, and then repeatedly occurs by every T cycle.

## MASK ROM DATA TAPE FORMAT

#### BASIC CLOCK

The following are four methods to generate and supply the basic clock pulse in the TMP4321AP.

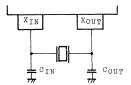

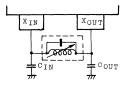

(1) Direct connection of crystal oscillator

When a crystal oscillator has been connected to TMP4321AP as shown in the left figure, the basic clock pulse is generated at the frequency inherent in the crystal oscillator. Recommendations for CIN and COUT  $C_{TN}=C_{OUT}=60 pF \ (f_{OSC} \approx 500 \text{KHz})$

(2) Direct connection of ceramic oscillator

When a ceramic oscillator has been connected to TMP4321AP as shown in the left figure, the basic clock pulse is generated at the frequency inherent in the ceramic oscillator. Recommendations for  $C_{\rm IN}$  and  $C_{\rm OUT}$   $C_{\rm IN}=C_{\rm OUT}=100 {\rm pF}~(f_{\rm OSC}\approx500 {\rm KHz})$

(3) Direct connection of IFT

When a IFT has been connected to TMP4321AP as shown in the left figure, the basic clock pulse is determined according to the circuit constant.

Recommendations for  $C_{\rm IN}$  and  $C_{\rm OUT}$   $C_{\rm IN}$ = $C_{\rm OUT}$ =100pF (f<sub>OSC</sub>  $\approx$  500KHz)

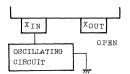

(4) Supply of external clock

The basic clock pulse of TMP4321AP can be supplied by an external oscillating circuit as shown in the left figure.

# TMP 4321AP

MAXIMUM RATINGS

| SYMBOL | ITEM                                        | RATING        | UNIT |

|--------|---------------------------------------------|---------------|------|

| VDD    | Supply Voltage                              | -0.5 ∿ 7      | V    |

| VIN    | Input Voltage                               | -0.5 ∿ 7      | ٧    |

| VOUT1  | Output Voltage (except open drain terminal) | -0.5 ∿ 7      | ٧    |

| Vout2  | Output Voltage (open drain terminal)        | -0.5 ~ 10     | ٧    |

| IOUT1  | Output Current (except OT1, OT2)            | 4             | mA   |

| IOUT2  | Output Current (OT1, OT2)                   | 30            | mA   |

| Tstg   | Storage Temperature                         | -55 ∿ 125     | °C   |

| Topr   | Operating Temperature                       | -10 ∿ 70      | °C   |

| Ts1d   | Solder Temperature                          | 260 (10 sec.) | °C   |

| PW     | Power Dissipation (Ta = 70°C)               | 850           | mW   |

D.C. ELECTRICAL CHARACTERISTICS ( $^{V}DD = 5V \pm 10\%$ , Topr =  $-10 \sim 70$ °C)

| D.C. LLLC          | C. ELECTRICAL CHARACTERISTICS (*DD = 5V=10%, 10pl = -10 070 C) |            |                            |      |      |                   |      |

|--------------------|----------------------------------------------------------------|------------|----------------------------|------|------|-------------------|------|

| SYMBOL             | PARAMETER                                                      |            | TEST CONDITION             | MIN. | TYP. | MAX.              | UNIT |

| VIH1               | Input High Voltage (INO,IN1,IN2,IOO,IO1,RST)                   |            | -                          | 2.2  | _    | $v_{\mathrm{DD}}$ | V    |

| $v_{\mathrm{IH2}}$ | Input High Voltage (INT)                                       |            | _                          | 3.5  | -    | $V_{\mathrm{DD}}$ | V    |

| VIL                | Input Low Voltage                                              |            | -                          | 0    | -    | 0.6               | V    |

| VCH                | Input High Clock Voltage (XIN)                                 |            | -                          | 3.8  | -    | $V_{\mathrm{DD}}$ | V    |

| $v_{\mathrm{CL}}$  | Input Low Clock Voltage (XIN)                                  |            | -                          | 0    | -    | 0.6               | V    |

| IIN1               | Input Current (INo, IN1, IN2)                                  |            | $\Lambda I N = \Lambda DD$ | -    | -    | 20                | μΑ   |

| I <sub>IN2</sub>   | Input Current (IOO, IO1)                                       | Open Drain | VIN = VDD                  | _    | _    | 20                | μA   |

|                    |                                                                | Pull Up    | -                          | -    | -    | -                 | -    |

| IIL1               | Input Low Current (IOO, IO1)                                   | Open Drain | _                          | -    | -    | _                 | _    |

|                    |                                                                | Pull Up    | VIN = 0.6V                 | -    | -    | -1.6              | mA   |

| IIL2               | Input Low Current (RST, INT)                                   |            | VIN = 0.6V                 | -    | _    | -0.1              | mA   |

| ILO                | Output Leak Current (OTO,OT1)                                  | Open Drain | VOUT = VDD                 | _    | _    | 20                | μΑ   |

|                    | OT2,OT3                                                        | Pull Up    | -                          | -    | -    | -                 | -    |

| VOH                | Output High Voltage                                            | Open Drain | -                          | _    | _    | _                 | _    |

|                    | (except XOUT)                                                  | Pull Up    | IOH =-100μA                | 2.4  | _    | -                 | V    |

| VOL                | Output Low Voltage (except XOUT)                               |            | IOL = 1.6 mA               | _    | -    | 0.4               | v    |

| $I_{\mathrm{DD}}$  | Supply Current                                                 |            | _                          | -    | 40   | 80                | mA   |

|                    |                                                                |            |                            |      |      |                   |      |

Output Low Voltage: Output large current IOL TYP.=20mA (VOL=2V) is made possible by output ports OT1, OT2. When output large current sinks, output low voltage becomes VOL MAX.≈0.5V(IOL=1.6mA).

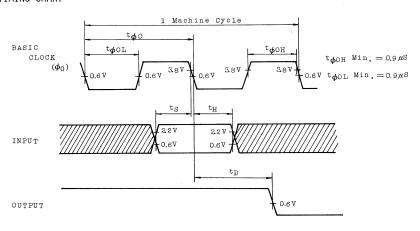

A.C. ELECTRICAL CHARACTERISTICS ( $^{V}DD$  =  $5V\pm10\%$ , Topr = -10  $^{\circ}$  70  $^{\circ}$  C) Refer to Timing Chart.

| SYMBOL | PARAMETER             | TEST CONDITION                   | MIN. | TYP. | MAX. | UNIT  |

|--------|-----------------------|----------------------------------|------|------|------|-------|

| tø0    | Clock Cycle Time      | _                                | 2    | -    | 5    | μS    |

| ts     | Input Setup Time      | _                                | 0.9  | -    | -    | μS    |

| tH     | Input Hold Time       | _                                | 0.9  | -    | -    | μS    |

| tp     | Output Delay Time     | CL=50pF, R(Pull<br>Up)=50kΩ,1TTL | -    | -    | 1.8  | μS    |

| tINT   | INT (Low Level Width) | -                                | 4    | -    | -    | Cycle |

| tRST   | RST (Low Level Width) | -                                | 4    | -    | -    | Cycle |

## TIMING CHART

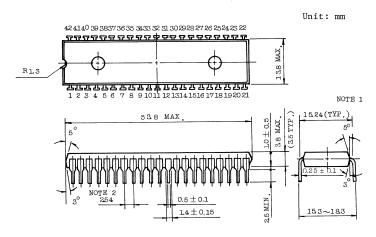

### EXTERNAL VIEW OF PACKAGE (Plastic Package)

Note 1. The dimension of this external view indicates the lead bending center.

Note 2. Lead pitch is 2.54mm and tolerance is  $\pm$  0.25mm against theoretical center of each lead that is obtained on the basis of No.1 and No.42 leads.