TOSHIBA MOS TYPE DIGITAL INTEGRATED CIRCUIT TMP47C40P, TMP47C41P TMP47C20P, TMP47C21P SILICON MONOLITHIC SILICON GATE CMOS

# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER (TLCS-47C) TMP47C40P, TMP47C20P, TMP47C41P, TMP47C21P

#### GENERAL DESCRIPTION

The TLCS-47 is the high speed and high performance, 4-bit single chip microcomputer series designed for the general purpose use.

The TLCS-47 has variously powerful functions in order to meet with advanced and complicated applications, which will be made in near future. In addition, software compatible NMOS family (TLCS-47N) and CMOS family (TLCS-47C) are also provided.

The TMP47C4OP and TMP47C2OP are the standard chips for the TLCS-47C. These chips are similar to each other, except memory capacity. And in the case of high breakdown voltage output type, production part's number is TMP47C41P or TMP47C21P. The TMP4700C (NMOS) is an evaluator chip used for the system development.

| Part No.     | ROM (Bit)                          | RAM (Bit) |

|--------------|------------------------------------|-----------|

| TMP47C40/41P | 4,096 × 8                          | 256 × 4   |

| TMP47C20/21P | 2,048 × 8                          | 128 × 4   |

| TMP4700C     | Externally provided<br>(4,096 × 8) | 256 × 4   |

TMP47C40P, TMP47C41P

TMP47C20P, TMP47C21P

TECHNICAL DATA

### FEATURES

| • | 4-bit single chip microcomputer with built-in<br>ROM, RAM, input/output port, divider, timer/counter, and serial port.                                                                                                                                                                                                      |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Instruction execution time: $4\mu s$ (at 4 MHz clock)                                                                                                                                                                                                                                                                       |

| • | Effective instruction set<br>90 instructions, software compatible in the series                                                                                                                                                                                                                                             |

| • | Subroutine nesting: Maximum 15 levels                                                                                                                                                                                                                                                                                       |

| • | 6 interrupts (External: 2, Internal: 4)<br>Independently latched control and multiple interrupt control                                                                                                                                                                                                                     |

| • | Input/output port (35 pins)                                                                                                                                                                                                                                                                                                 |

|   | Input1 port4 pinsOutput (corresponding to PLA)2 ports8 pinsI/04 ports16 pinsI/0 (Note)2 ports7 pins                                                                                                                                                                                                                         |

|   | Note: These $I/0$ ports are also used for the interrupt input, timer/                                                                                                                                                                                                                                                       |

|   | counter input, and serial port; therefore, it is programmably                                                                                                                                                                                                                                                               |

|   | selectable for each application.                                                                                                                                                                                                                                                                                            |

| • | PLA data converting function (Instruction)<br>Output of data to output port (8-bit)                                                                                                                                                                                                                                         |

| • | Table look-up and table search function (Instruction)<br>Table can be set up in the whole ROM area.                                                                                                                                                                                                                         |

| • | <pre>12-bit timer/counter (2 channels)<br/>Event counter, timer, and pulse width measurement mode is programmably<br/>selectable.<br/>Serial port with 4-bit buffer<br/>Receive/transfer mode is programmably selectable.<br/>External/internal clock and leading/trailing edge mode are programmably<br/>selectable.</pre> |

| • | 18-stage divider (with 4-stage prescaler)<br>Frequency applied for timer interrupt of divider is programmably selectable.                                                                                                                                                                                                   |

| • | High breakdown voltage output (20 pins)<br>Maximum rating 42V, FL tube direct drive is available.                                                                                                                                                                                                                           |

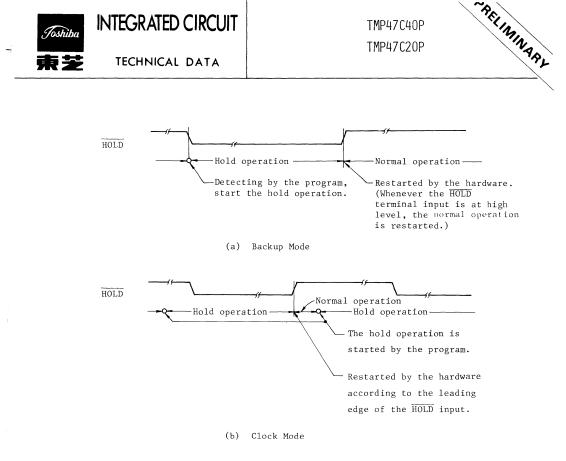

| • | Hold function<br>Battery operation/condenser backup is available.                                                                                                                                                                                                                                                           |

| • | On chip oscillator                                                                                                                                                                                                                                                                                                          |

| • | TTL/CMOS compatible                                                                                                                                                                                                                                                                                                         |

| • | +5V single power supply                                                                                                                                                                                                                                                                                                     |

| • | 42-pin DIL plastic package                                                                                                                                                                                                                                                                                                  |

| , | Si-gate CMOS LSI                                                                                                                                                                                                                                                                                                            |

TMP47C40P, TMP47C41P

Toshiba **R Z**

TECHNICAL DATA

TMP47C20P, TMP47C21P

PIN CONNECTIONS (Top View)

| R40 1                        | 42 <b>0</b> V <sub>DD</sub>        |

|------------------------------|------------------------------------|

| R41 2                        | 41 R92 (SCK)                       |

| R <sub>42</sub> <b>C</b> 3   | 40 <b>0</b> R <sub>91</sub> (SO)   |

| R <sub>43</sub> ¢ 4          | 39 <b>P</b> R <sub>90</sub> (SI)   |

| R <sub>50</sub> <b>C</b> 5   | 38 R <sub>83</sub> (T1)            |

| R <sub>51</sub> <b>q</b> 6   | 37 R <sub>82</sub> (INT1)          |

| R52 7                        | 36 R <sub>81</sub> (T2)            |

| R53 4 8                      | 35 <b>P</b> R <sub>80</sub> (INT2) |

| R <sub>60</sub> <b>9</b> 9   | 34 HOLD                            |

| R <sub>61</sub> <b>q</b> 10  | 33 RESET                           |

| R <sub>62</sub> <b>4</b> 11  | 32 <b>2</b> X <sub>OUT</sub>       |

| R <sub>63</sub> <b>4</b> 12  | 31 <b>0</b> X <sub>IN</sub>        |

| R70 <b>4</b> 13              | 30 D TEST                          |

| R71 <b>4</b>                 | 29 <b>9</b> K <sub>O3</sub>        |

| R <sub>72</sub> <b>C</b> 15  | 28 D Koo                           |

| R73 <b>4</b> 16              | 27 <b>P</b> Kol                    |

| P <sub>10</sub> <b>4</b> 17  | 26µ K <sub>00</sub>                |

| P <sub>11</sub> <b>4</b> 18  | 25 <b>P</b> P <sub>23</sub>        |

| P <sub>12</sub> <b>[</b> 19  | 24 ] P22                           |

| P <sub>13</sub> <b>0</b> 20  | 23 <b>p</b> P <sub>21</sub>        |

| v <sub>DD</sub> <b>q</b> 2 1 | 22 <b>9</b> P <sub>20</sub>        |

|                              |                                    |

## PIN NAMES AND PIN DESCRIPTION

| Pin Name                           | No. of<br>pins           | Input/Output | Function                                |  |  |

|------------------------------------|--------------------------|--------------|-----------------------------------------|--|--|

| $K_{o 3} \sim K_{o o}$             | 4                        | Input        | Input port                              |  |  |

| $P_{13} \sim P_{10}$               | 4                        | Output       | Output port (Corresponding to PLA)      |  |  |

| $P_{23} \sim P_{20}$               | 4                        | Output       | " ( " )                                 |  |  |

| $R_{43} \sim R_{40}$               | 4                        | I/0          | I/O port                                |  |  |

| $R_{53} \sim R_{50}$               | 4                        | I/0          | 11                                      |  |  |

| $R_{63} \sim R_{60}$               | 4                        | 1/0          | 11                                      |  |  |

| $R_{73} \circ R_{70}$              | 4                        | I/0          | TI                                      |  |  |

| R <sub>83</sub> (T1)               | R <sub>83</sub> (T1) 1 1 |              | I/O port or timer/counter input         |  |  |

| R <sub>82</sub> (INT1)             | 1                        | I/0          | I/O port or interrupt input             |  |  |

| R <sub>81</sub> (T2)               | 1                        | I/O          | I/O port or timer/counter input         |  |  |

| R <sub>so</sub> (INT2)             | 1                        | 1/0          | I/O port or interrupt input             |  |  |

| R <sub>92</sub> (SCK)              | 1                        | I/0          | I/O port or shift clock for serial port |  |  |

| R <sub>91</sub> (SO)               | 1                        | I/0          | I/O port or serial output               |  |  |

| R <sub>90</sub> (SI)               | 1                        | I/O          | I/O port or serial input                |  |  |

| X <sub>IN</sub> , X <sub>OUT</sub> | 2                        | Input,Output | Resonator connection terminals          |  |  |

| RESET 1                            |                          | Input        | Initialize signal input                 |  |  |

| HOLD 1 Input                       |                          | Input        | Hold signal input                       |  |  |

| TEST                               | 1                        | Input        | (Low level is input.)                   |  |  |

| VDD                                | 1                        | Power Supply |                                         |  |  |

| VSS                                | 1                        | Power Supply | ov                                      |  |  |

TMP47C40P, TMP47C41P TMP47C20P, TMP47C21P PREI MINARY

# TECHNICAL DATA

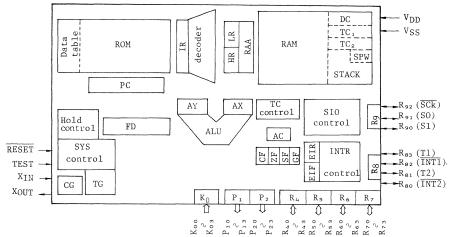

BLOCK NAMES AND DESCRIPTION

| Block Name             | Function                                                                                                |

|------------------------|---------------------------------------------------------------------------------------------------------|

| PC                     | Program counter (12 bits)                                                                               |

| ROM                    | Program memory (including fixed data)                                                                   |

| IR, decoder            | Instruction register, Decoder                                                                           |

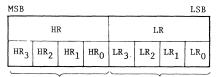

| HR, LR                 | H register (page assignment of RAM), L register (address assignment in RAM page), (each 4-bit register) |

| RAA                    | RAM address buffer register (8 bits)                                                                    |

| RAM                    | Data memory                                                                                             |

| STACK                  | Save area of program counter and flags (RAM area)                                                       |

| SPW                    | Stack pointer word (RAM area)                                                                           |

| DC, data table         | Data counter (12 bits, RAM area), Data table (ROM area).                                                |

| AX, AY                 | Temporary register of ALU input                                                                         |

| ALU                    | Arighmetic and logic unit                                                                               |

| AC                     | Accumulator                                                                                             |

| FLAG (CF,ZF,SF,<br>GF) | Flags                                                                                                   |

| K, P, R                | Ports                                                                                                   |

| INTR control           | Interrupt control                                                                                       |

|                        | (EIF: Enable interrupt master F/F, EIR: Enable interrupt                                                |

|                        | register)                                                                                               |

| FD                     | Frequency divider (4-stage prescaler + 18 stages)                                                       |

| $TC_1$ , $TC_2$        | 12-bit timer/counter 2 channels (RAM area)                                                              |

| TC control             | Timer/counter control                                                                                   |

| SIO control            | Serial port control                                                                                     |

| HOLD control           | Control for hold function                                                                               |

| SYS control            | Generation of various internal control signals                                                          |

| CG, TG                 | Clock generator, Timing generator                                                                       |

```

FUNCTIONAL DESCRIPTION

1. System Configuration

1. Program Counter (PC)

2. Program Memory (ROM)

3. H Register (HR), L Register (LR), RAM Address Buffer Register (RAA)

4. Data Memory (RAM)

(1) Stack (STACK)

(2) Stack Pointer Word (SPW)

(3) Data Counter (DC)

5. ALU, Accumulator (AC)

6. Flags (FLAG)

7. Ports (PORT)

8. Interrupt Control Circuit (INTR)

9. Frequency Divider (FD)

10. Timer/Counter (TC1, TC2)

11. Serial Port (SIO)

12. Hold Control Circuit (HOLDC)

Concerning the above component parts, the configuration and functions of

hardwares are described :

Hexadecimal notation is used for the description, charts, and tables in order

to indicate the address and the like, without assigning identification symbols

as far as it does not give rise to confusion.

The following names and symbols are used unconsciously.

```

| (a) | CPU | Control Processing Unit except for the built-in peripheral   |

|-----|-----|--------------------------------------------------------------|

|     |     | circuitry, such as interrupt control circuit, timer/counter, |

|     |     | and serial port.                                             |

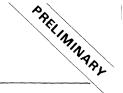

- (b) CP Clock pulse generated in the clock oscillator. It is called the "basic clock" or merely "clock".

- (c) fc Indicates the frequency of the clock oscillator, namely, the frequency of the basic clock.

- (d) MSB/LSB Indicates Most/Least Significant Bit.

- (e) F/F Indicates Flip/Flop.

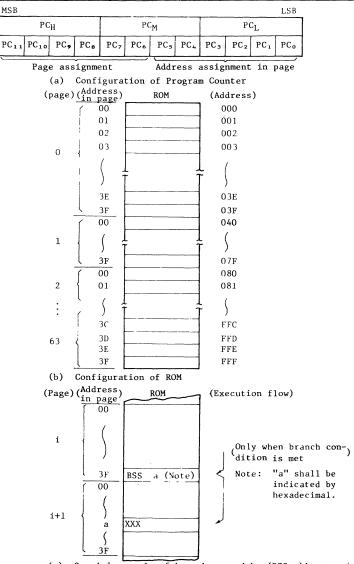

# 1.1 Program Counter (PC)

It is a 12-bit binary counter, and the contents of the program counter indicate the address of program memory in which the next instruction to be executed is stored.

The program counter generally gains increment at every instruction fetch by the number of bytes assigned to the instruction. However, when executing the branch and subroutine instructions or receiving the interrupt, the values specified by these instructions and operation are set. Value "0" is specified by initializing the program counter.

The page structure of program memory is made with 64 words per page. The TMP47C40P has 64 pages and the TMP47C20P 32 pages.

At the execution of (BSS a) instruction, the value assigned by the instruction is set in the lower 6 bits of the program counter when the branch condition is met. That is, the (BSS a) instruction is used as a branch or jump instruction within a page. If the (BSS a) instruction is stored in the last address of the page, the value in the higher 6 bits of the program counter indicates that the branch or jump instruction to the next page is executed.

At the execution of (CALL a) instruction, the value specified by the instruction is set in the program counter after the previous contents of the program counter has been saved in the stack. Since 11 bits are of the address bit length which can be assigned by the instruction, the call address of subroutine should be in the range of addresses 000 - 7FF.

# TECHNICAL DATA

MSB

# 1.2 Program Memory (ROM)

Processing programs and fixed data are stored in the program memory. The next instruction to be executed is read out from the address indicated by the contents of the program counter.

The fixed data stored in the program memory can be read by using the ROM data referring instruction or the PLA referring instruction. The ROM data referring instruction reads out the higher or lower 4-bit data of the fixed data stored in the address decided by the data counter [(LDH A, @DC+) and (LDL A, @DC) instruction respectively], and stores the data in the accululator. The PLA referring instruction (OUTB @HL) reads out the fixed data (8-bit) stored in the address decided by the contents of the data memory indicated by the contents of H and L registers as well as contents of the carry flag, and outputs the data to output ports (P2 · P1).

Addresses are individually assignged to the program memory and data memory, so that the fixed data in the ROM area cannot be directly read out by the address of the data memory.

#### Specific Addresses of Program Memory

The following addresses of the program memory are used for specific purposes. When not used for these purposes, the specific addresses can be used to store the processing programs and fixed data.

TECHNICAL DATA

TMP47C40P TMP47C20P

| Specific Address               | Specific Purposes                     |

|--------------------------------|---------------------------------------|

| 000<br>(001)                   | Start address by initialization       |

| 002<br>(003)                   | INT1 Interrupt vector address         |

| 004<br>(005)                   | ISIO Interrupt vector address         |

| 006<br>(007)                   | IOVF1 Interrupt vector address        |

| 008<br>(009)                   | IOVF2 Interrupt vector address        |

| 00A<br>(00B)                   | ITMR Interrupt vector address         |

| 00C<br>(00D)                   | INT2 Interrupt vector address         |

| 8n+6<br>(n=1~15)<br>086 (Note) | Call address by instruction (CALLS a) |

| FEO<br>2<br>FFF                | PLA data conversion table             |

Note : 086 (hexadecimal) = 134 (decimal)

Table 1.2.1 Specific Address of Program Memory

TECHNICAL DATA

TMP47C40P TMP47C20P PREIMINARY

ROM CAPACITY

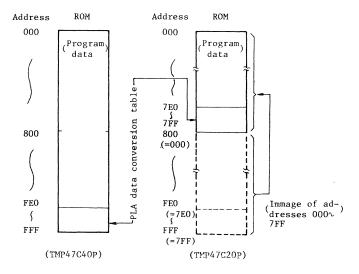

The TMP47C40P and TMP47C20P contain a program memory with 4,096  $\times$  8-bit (addresses 000 - FFF) capacity and 2,048 x 8-bit (addresses 000 - 7FF) capacity, respectively. But the TMP47C20P contains a program counter with 12-bit length. Therefore, when one of addresses 800 - FFF is accessed in a program, the ROM data corresponding to addresses 000 - 7FF read out. It is because there is no physical ROM in addresses 800-FFF, but the MSB in the program counter is not decoded. For example, when the data located in address FF3 is output to a port by the PLA referring instruction on a program, the data located in addresses 7F3 is read out. In the TMP47C20P, the PLA data conversion table (addresses FE0 - FFF) is, therefore, located in addresses 7E0 - 7FF.

"0" [(NOP) instruction] is read out for the ROM data within the range of the built-in ROM capacity, if it is not specified by the user.

Fig. 1.2.1 ROM Capacity and Address

1.3 H Register (HR), L Register (LR), and RAM Address Buffer Register (RAA)

The H and L registers are 4-bit registers used as the data memory address pointers or general purpose registers.

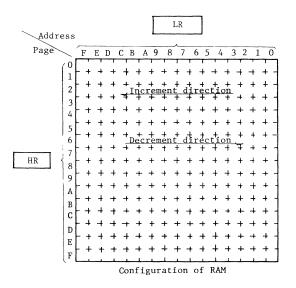

The page structure of the data memory is based on 16 words per page. Pages are specified by H register, and addresses in page are done by L register, respectively. TMP47C40P has 16 pages and TMP47C20P 8 pages.

The L register is also used to specify the bits corresponding to pins  $R_{73} \sim R_{40}$  of the I/O port when instructions (SET @L), (CLR @L), and (TEST @L), are executed.

The RAM address buffer register is a temporary register used to specify the address in the data memory, and serves as an input of the RAM address decoder. Normally, the data specified by the contents of the H and L registers or immediate data of an instruction is fed into the RAM address buffer register.

TMP47C40P TMP47C20P

TECHNICAL DATA

Page specification Address specification in page

Fig. 1.3.1 H Register, L Register and Data Memory (RAM)

#### 1.4 Data Memory (RAM)

The processing data of user are stored in the data memory. The data is read out or written in according to the address indicated by the contents of the RAM address buffer register.

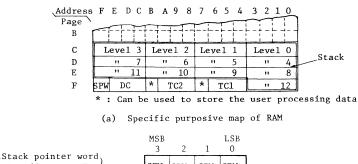

#### Specific addresses of data memory

The data memory is also used for the following specific purposes. When it is not used for the respective purposes, the RAM of the corresponding address can be used to store the user processing data.

- (1) Stack (STACK)

- (2) Stack pointer word (SPW)

- (3) Data counter (DC)

- (4) Timer/Counter (TC1, TC2)

- (1) Stack (STACK)

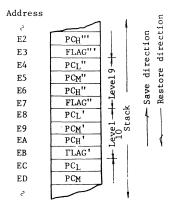

The stack, which is contained in the data memory (one level of the stack consists of 4-word RAM), is area to save the contents of the program counter (return address) and flag prior to jumping to the processing program at time of subroutine call or interrupt acceptance. To return from the processing program, (RET) instruction is used to restore the contents saved in the stack to the program counter, and (RETI) instruction is used to restore the contents saved in the stack to the program counter and flags.

The location of the stack to save/restore the contents is determined by the stack pointer word, which is automatically decremented after the saving operation, and incremented prior to the restoring operation.

#### (2) Stack Pointer Word (SPW)

The address FF in the data memory is called a stack pointer word and decides the stack pointer. The stack is contained in the RAM, and accessed by the stack pointer.

The stack pointer is decided with the format shown in Fig. 1.4.1, but this address indicates the lower RAM address in each level of the stack.

Values "E" - "0" can be assigned for the stack pointer word, so that the maximum of 15 nesting levels are available for the stack. However, when the timer/counter mentioned following is used, the level containing the RAM address corresponding to the timer/counter cannot be used for the stack (value "F" is not assigned to the stack pointer word, because the stack contains the RAM address corresponding to the stack pointer word). The stack pointer word is automatically updated by the subroutine call or interrupt acceptance; however, it cannot exceed the allowable size of the stack for the system configuration.

Since the stack pointer word is never initialized in terms of hardware, it is necessary to set it to the highest possible level of the stack in the user's initialization prpgram. For instance, it is set to "C" level when the two channels of timer/counter are used.

Note: The "level" indicates the depth of the nesting in the stack as well as the location of the next available stack. That is, it represents the contents of the stack pointer word.

TMP47C40P TMP47C20P

TECHNICAL DATA

| (RAM address : FF | )   |   | SPW₃ | SPW2  | SPW1 | SP₩₀ |   |     |  |

|-------------------|-----|---|------|-------|------|------|---|-----|--|

|                   | MSB |   |      | ·     |      |      |   | LSB |  |

|                   | 7   | 6 | 5    | 4     | 3    | 2    | 1 | 0   |  |

| (Stack pointer)   | 1   | 1 | SPW₃ | SPW 2 | SPW1 | SPW₀ | 0 | 0   |  |

(b) Stack pointer and stack pointer word

(c) Structure of stack

Fig. 1.4.1 Specific Address and Stack of Data Memory

#### (3) Data Counter (DC)

Data counter is a 12-bit binary counter used to specify the address when the data table in the ROM area is referred (ROM data referring instruction).

The RAM address with 4-bit unit is allocated to the data counter, so that the initial value setting and the content reading of the data counter can be executed by the RAM manipulative instructions.

|                | MSB  |      |     | LSB |

|----------------|------|------|-----|-----|

|                |      | D    | С   |     |

| (Data Counter) | DCH  | DCM  | DCL |     |

| (RAM Address)  | (FE) | (FD) | (FC | )   |

Fig. 1.4.2 Data Counter and RAM Address

#### (4) Timer/Counter (TC1, TC2)

The two channels of 12-bit timer/counter are built-in, and the RAM address with 4-bit unit is allocated to the timer/counter, so that the initial value setting and the content reading of the timer/counter can be executed by the RAM manipulative instructions.

When the timer/counter l is not used, the stack lower from level 13 can be used. When both of the timer/counter l and 2 are not used, the stack lower from level 14 can be used.

|                   | MSB              |      | LSB  |

|-------------------|------------------|------|------|

| (Timer/Counter 1) |                  | TC1  |      |

| (IImer/Counter I) | tc1 <sub>H</sub> | TCIM | TC1L |

| (RAM Address)     | (F6)             | (F5) | (F4) |

|                    | MSB              |                  | LSB  |

|--------------------|------------------|------------------|------|

| (Timer/Counter 2)  |                  | TC2              |      |

| (Timer, counter 2) | TC2 <sub>H</sub> | TC2 <sub>M</sub> | TC2L |

| (RAM Address)      | (FA)             | (F9)             | (F8) |

Fig. 1.4.3 Timer/Counter and RAM Address

(5) Page 0 in Data Memory

Page 0 in the data memory (addresses 00 - OF) is effectively used as a flag or pointer in a user's program.

ТМР47С40Р ТМР47С20Р РЯСТИМИЛАРУ

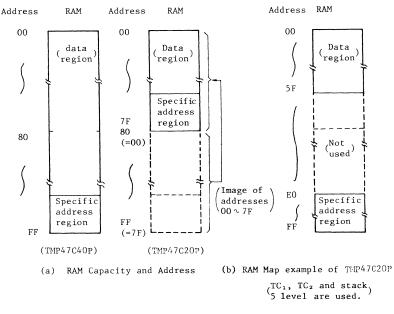

#### RAM Capacity

Data memory contained in TMP47C46P has a  $256 \times 4$ -bit (addresses 00 - FF) capacity, and that contained in TMP47C20P has a  $120 \times 4$ -bit (addresses 00 - 7F) capacity.

Since the TMP47C2OP also has the RAM address buffer register of 8-bit length, there is no physical RAM in addresses 80 - FF in the TMP47C2OP. However, the RAM equivalent to addresses 00 - 7F are referred when addresses 80 - FF are accessed in a program, because the MSB of RAM address buffer register is not decoded. That is, the specific RAM address is distributed to C0 - FF in a program, but the RAM equivalent to addresses 40 - 7F are assigned in the T4P47C2OP.

Fig. 1.4.4 RAM Capacity and Address

TMP47C40P TMP47C20P PRELIMINARY

TECHNICAL DATA

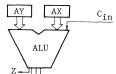

1.5 ALU, Accumulator (AC)

The ALU is a circuit used for various arithmetic and logical operation for 4-bit binary data. It performs the operation designated by the instruction, and outputs the 4-bit result, carry (C), and zero detection signal (Z).

The accumulator is a 4-bit register to use a source operand for the arithmetic operation, and in which the result is stored.

$C \longrightarrow (AX and AY are temporary registers.)$

Output of result

MSB LSB 2 0 (Accumulator)

Fig. 1.5.1 ALU, Accumulator

#### Detection of operating condition

Output C from the ALU indicates the carry output from the most significant position in the addition operation. However, the subtraction is executed with the addition of the 2's complement, so that output C in the subtraction operation indicates the "non-borrow" from the most significant position (i.e., in case of non-borrow, C = "1"). Accordingly, borrow (B) can be represented with " $\overline{C}$ ".

Output Z indicates the zero detection signal to which "1" is applied when all of the 4-bit data transferred to accumulator or output of the ALU are cleared to zero.

TECHNICAL DATA

Example (4-bit operation)

| (a) | 4 + 5 = 9       | (C = 0, Z = 0) |

|-----|-----------------|----------------|

| (b) | 7 + 9 = 0       | (C = 1, Z = 1) |

| (c) | 3 - 1 = 2       | (B = 0, Z = 0) |

| (d) | 2 - 2 = 0       | (B = 0, Z = 1) |

| (e) | 6 - 8 = -2 or E | (B = 1, Z = 0) |

Note :  $B = \overline{C}$  is indicated.

1.6 Flag (FLAG)

Flag is a 4-bit register used to store the condition of arithmetic operation, and of which the set/reset conditions are specified by the instruction. The flag consisting of CF, ZF, SF, and GF is saved in the stack when the interrupt is accepted. By executing the (RETI) instruction, it is restored from the stack to the conditions immediately before the interrupt is accepted.

| <br>3 | 2  | 1  | 0  |

|-------|----|----|----|

| CF    | ZF | SF | GF |

Fig. 1.6.1 Flag

(1) Carry Flag (CF)

This flag is used to hold the carry in the addition operation as an input to the ALU by the (ADDC A, @HL) instruction as well as to hold the non-borrow in the subtraction operation (the carry in the addition of the 2's complement) as an input to the ALU by the (SUBRC A, @HL) instruction. The rotate instruction makes the flag hold the data shifted out of the accumulator.

#### (2) Zero Flag (ZF)

This flag is stored the zero detection signal (Z) when the instruction designate to change. "1" is set if all 4 bits are cleared to zero by an arithmetic operation or data processing.

#### (3) Status Flag (SF)

This flag is set or reset according to the condition specified by the instruction. With the exception of particular cases, it is usually presented at every execution of an instruction, and holds the contents of the result during execution of the next instruction. It is normally set to "1", but is reset to "0" for a time under the certain condition (it varies according to the instruction, for examples, when the result is zero, when carry occurs in the addition, or when borrow occurs in the subtraction, the flag is reset).

The status flag is referred to as branch condition in a branch instruction. The memory location is branched when this flag is set to "1"; therefore, normally the branch instruction can be required as "unconditional jump instruction". On the contrary, the instruction becomes a "conditional instruction" if it is executed immediately after loading the instruction to set/reset the status flag according to the condition determined by some previous instruction.

The status flag is initialized to "1" at initialization, and is also set to "1" after the contents have been saved in the stack when the interrupt is accepted. The contents saved in the stack is restored by the (RETI) instruction.

#### (4) General Flag (GF)

This is a single-bit general purpose flag, being set or reset, and also used in a test by a program. This can be used for any purpose in the user program.

1.7 Port (PORT)

Data transfer to/from the external circuitry, and command/ status/data transfer between the built-in periferal circuitry are carried out by the input/output instructions.

- (a) Input/Output port : Data transfer to/from external circuitry.

- (b) Command/data output : Control of circuitry of built-in peripheral circuitry, and output of data.

(c) Status/data input : Input of status signal<sup>(Note)</sup> and data from the built-in peripheral circuitry.

Note : Status signal is provided from serial port and hold control circuit, and is different from the status flag (SF).

To transfer the data or to control the circuitry, each port or register is selected by designating the address (Port address) by input/output operational instructions (13 instructions) in the same way as the memory.

The port address is composed of 5 bits (addresses 0 - 31). The address to be accessed differs according to a instruction. By way of caution, the port address space is independent of the program memory address space and the data memory address space.

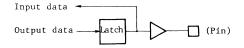

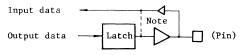

Every output port contains a latch in order to hold the output data. Since every input port is operated without latching, it is desired to externally hold the data to be input from the external devices till the data is completely read out, or to read the data several times to confirm the contents.

The details to specify the input/output circuit format of ports and initialization of the output latch are 2.6 (2) Input/Output Circuit Format.

| -     | 0 1 . 1   |                                                                                         | Input/Output Instructions |             |           |           |          |           |      |    |

|-------|-----------|-----------------------------------------------------------------------------------------|---------------------------|-------------|-----------|-----------|----------|-----------|------|----|

| Port  | Symbol    | Port, Register                                                                          |                           |             |           |           |          |           | SET  | @L |

| ad-   | (Input/   | (Input/Output)                                                                          | IN %P, A                  | OUT A ,%P   |           |           | SET%P,b  | TEST %P,b | CLR  | @L |

| dress | Output)   |                                                                                         |                           |             | OUT#K,%P  | OUTB @HL  |          | TESTP%P,b | TEST | @L |

| 00    | IP00/0P00 | K <sub>0</sub> Input port / P <sub>1</sub> Output<br>P <sub>1</sub> Output latch/ P ort | 0                         |             |           |           |          | 0         |      |    |

| 01    | IP01/OP01 | P1Output latch/ port                                                                    | 0                         | 0           | 0         |           | 0        | 0         |      |    |

| 02    | IP02/0P02 | P <sub>2</sub> " /P <sub>2</sub> "                                                      | 0                         | 0           | 0         |           | 0        | 0         |      |    |

| 03    | IP03/0P03 |                                                                                         |                           |             |           |           |          |           |      |    |

| 04    | IP04/OP04 | R <sub>4</sub> I/O port                                                                 | 0                         | 0           | 0         |           | 0        | 0         | 0    |    |

| 05    | IP05/0P05 | R5 ''                                                                                   | 0                         | 0           | 0         |           | 0        | 0         | 0    |    |

| 06    | IP06/OP06 | R6 "                                                                                    | . 0                       | 0           | 0         |           | 0        | 0         | 0    |    |

| 07    | IP07/0P07 | R7 "                                                                                    | 0                         | 0           | 0         |           | 0        | 0         | 0    |    |

| 08    | IP08/0P08 | Re "                                                                                    | 0                         | 0           | 0         |           | 0        | 0         |      |    |

| 09    | IP09/0P09 | R9 ''                                                                                   | 0                         | 0           | 0         |           | 0        | 0         |      |    |

| 0A    | IPOA/OPOA |                                                                                         |                           |             | I         |           |          |           |      |    |

| ОВ    | IPOB/OPOB |                                                                                         | (*) 60.                   | rial buffer | - registe | r (Recent | ion)     |           |      |    |

| 0C    | IPOC/OPOC |                                                                                         |                           | rial buffer |           |           |          |           |      |    |

| OD    | IPOD/OPOD |                                                                                         | () Sel                    | LIAI DUITE  | , registe | r (rransm | 13310117 |           |      |    |

| 0E    |           | Status input/                                                                           | 0                         |             |           |           |          | 0         |      |    |

| OF    | IPOF/OPOF | (*) / (**)                                                                              | 0                         | 0           | 0         |           |          |           |      |    |

| 10    | /OP10     | / (a)                                                                                   |                           |             |           |           |          |           |      |    |

| 11    | /OP11     | /P2.P1 output port                                                                      |                           |             |           | 0         |          |           | ,    |    |

| 11    |           | (8-bit output)                                                                          |                           |             |           |           |          |           |      |    |

| 12    | /OP12     | /                                                                                       |                           |             |           |           |          |           |      |    |

| 13    | /OP13     |                                                                                         |                           |             |           |           |          |           |      |    |

| 14    | /OP14     | /                                                                                       |                           |             |           |           |          |           |      |    |

| 15    | /OP15     | /                                                                                       | (a) Hold                  | l control   |           |           |          |           |      |    |

| 16    | /OP16     | /                                                                                       |                           | rol with t  | -imor int | errupt of | divider  |           |      |    |

| 17    | /OP17     | /                                                                                       |                           | er/Counter  |           |           | arviage  |           |      |    |

| 18    | /OP18     |                                                                                         | (C) 1100                  |             |           | T         |          |           |      |    |

| 19    | /OP19     | / (b)                                                                                   |                           | 0           | I         | I         |          |           |      |    |

| 1A    | /OP1A     | /                                                                                       |                           | er/Counter  |           | 1 .       |          |           |      |    |

| 1B    | /OP1B     |                                                                                         | (e) Ser:                  | ial port co | ontrol    | 1         |          |           |      |    |

| 1C    | /OP1C     | / (c)                                                                                   |                           | 0           | I         |           |          |           |      |    |

| 1D    | /OP1D     | (b) /                                                                                   |                           | 0           |           |           |          |           |      |    |

| 1E    | /OP1E     | /                                                                                       |                           |             |           |           |          |           |      |    |

| 1F    | /OP1F     | / (e)                                                                                   |                           | 0           |           |           |          |           |      |    |

396

Note 1: Inputs (IP10 - IP1F) of port addresses 10 - 1F remain undefined.

Note 2: Port addresses with "----" mark are reserved addresses and cannot be used at user's program.

Note 3: OP11 is automatically accessed by (OUTB @HL) instruction, but cannot be done by the instructions other than this one.

Table 1.7.1 Port Address Allocation and Input/Output Instructions

Joshiba T

INTEGRATED CIRCUIT

TECHNICAL DATA

TMP47C40P TMP47C20P

Levenin Date

| TMP47C40P |

|-----------|

| TMP47C20P |

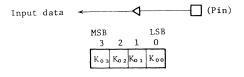

(1) K<sub>0</sub> (K<sub>03</sub>  $\sim$  K<sub>00</sub>) Port

This is a 4-bit port used for input.

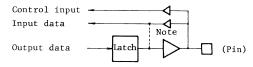

Fig. 1.7.1 Ko Port

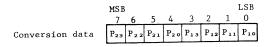

(2)  $P_1 (P_{13} \sim P_{10}), P_2 (P_{23} \sim P_{20})$  Port

These ports are 4-bit ports with a latch used for output. The latch data can be read by the instruction.

These two ports can independently access by specifying port addresses IPO1/OPO1, and IPO2/OPO2. In addition, they can output 8-bit data by the (OUTB @HL) instruction.

PLA data conversion

A hardware PLA is not contained in the system; however, the function equivalent to it can be performed by access to the PLA data conversion table provided in the RCM by use of the (CUTB @HL) instruction.

The PLA referring instruction (OUTB @HL): This instruction reads out the 8-bit data stored in the program memory, whose address is determined by the contents of the data memory indicated by the contents of the H and L registers as well as the contents of the carry flag, and outputs the data to 8-bit ports P2 and P1. At this time OP11 is automatically selected as the port address.

INTEGRATED CIRCUIT

TMP47C20P

TMP47C40P

TRELIMINARY

TECHNICAL DATA

Ports Pl and P2 are capable of reading the latch data by the instruction, so that the data output by the PLA referring instruction can be qualified or modified; that is, the convert pattern can be changed or the numbers of pattern will be increased.

Fig. 1.7.2 P1 and P2 Ports

(3)  $R_4(R_{43} \sim R_{40})$ ,  $R_5(R_{53} \sim R_{50})$ ,  $R_6(R_{63} \sim R_{60})$ ,  $R_7(R_{73} \sim R_{70})$  Port

Each of these ports is a 4-bit I/O port with a latch. The latch should be set to "1" when the port is used as an input port. (But, these ports are only used to output ports with some input/output circuits.)

Pins R<sub>73</sub> - R<sub>40</sub> can be used for bit scanning for set/reset and test according to the contents of the L register by executing the (SET @L), (CLR @L) and (TEST @L) instructions. Table 1.7.2 shows the pins corresponding to the contents of the L register.

|         | Correspond-<br>ing Pin | Lregister<br>3210 | Correspand-<br>ing Pin |

|---------|------------------------|-------------------|------------------------|

| 0000    | R40                    | 1000              | R60                    |

| 0001    | R41                    | 1001              | R61                    |

| 0010    | R42                    | 1010              | R62                    |

| 0011    | R43                    | 1011              | R63                    |

| 0100    | R <sub>50</sub>        | 1 1 0 0           | R <sub>70</sub>        |

| 0 1 0 1 | R51                    | 1 1 0 1           | R71                    |

| 0 1 1 0 | R52                    | 1110              | R72                    |

| 0 1 1 1 | R53                    | 1111              | R73                    |

Table 1.7.2 Correspondence of Individual Bits of L Register and I/O Port

TECHNICAL DATA

TMP47C40P TMP47C20P

泛

Toshiba

Note : For bit set/reset of port, latch output serves as input data.

Fig. 1.7.3  $R_4 \sim R_7$  Ports

(4) R<sub>8</sub> (R<sub>83</sub> ∿ R<sub>80</sub>) Port

This is a 4-bit I/O port with a latch. The latch should be set to "1" when the port is used as an input port.

It is a port common to external interrupt input or external timer/ counter input. When it is driven by the external circuitry, such as external interrupt input or external timer/counter input, the latch must be set to "1". When it is used as normal I/O port, some measures, such as inhibition of the external interrupt input acceptance or disable of the mode depending on the external input of the timer/counter should be taken in a program.

(Note) When pin R82 ( $\overline{INTI}$ ) is used as a port, INT1 interrupt request takes place because the falling edge of the pin input/output is detected (interrupt enabling master F/F is normally set to "1"). This causes the CPU to process a dummy interrupt acceptance [e.g. the (RETI) instruction only is executed]. When pin R<sub>80</sub> ( $\overline{INT2}$ ) is used, INT2 interrupt request also takes place in the same manner as the case of pin R<sub>82</sub>, but the interrupt request is not accepted by merely resetting the LSB (EIR<sub>0</sub>) of the enable interrupt register to "0" in advance. Therefore, the above processing is not required.

TECHNICAL DATA

Note: For bit set/reset of port, latch output serves as input data.

Fig. 1.7.4 Re Port

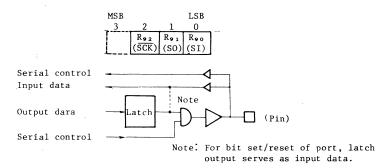

(5) R9(R92 ∿ R90) Port

This is a 3-bit I/O port with a latch, and the latch must be set to "1" when it is used as input port. The R9 port is also used as serial port. The latch must be set to "1" when R9 port is used as serial port. The port used as normal I/O port is not entirely influenced by disabling the serial port. Pin R93 is not mounted in the port, but "1" is read by accessing to pin R93 in a program.

Fig. 1.7.5 R, Port

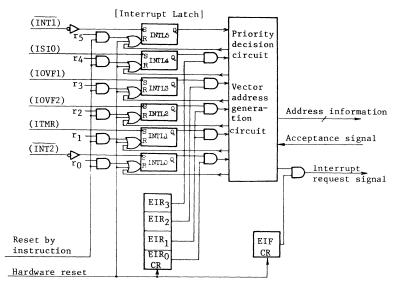

1.8 Interrupt control circuit (INTR)

Interrupt factors are composed of two from the external circuitry, and four from the internal circuitry. By setting the interrupt latch provided for each factor, an interrupt request is generated to the CPU. The interrupt latch is set when the edge of the input signal is detected.

The interrupt request is not always accepted by the CPU if generated. It is not accepted till the priority in the six factors determined according to the hardware and the enabling/disabling control by the program become all affirmative.

In order to control enabling/disabling of interrupt by the program, an F/F (EIF) and a 4-bit register (EIR) are provided. By using these means, preferential acceptance of the interrupt factors by the program, and multiple interrupt control can be realized.

TECHNICAL DATA

TMP47C40P TMP47C20P PREI MINARY

| Factor     |                                          |         | Priority<br>according<br>to hardware | Interrupt<br>Latch | Enable con-<br>dition accord-<br>ing to program | Vector<br>Address |

|------------|------------------------------------------|---------|--------------------------------------|--------------------|-------------------------------------------------|-------------------|

| Exte       | ernal interrupt l                        | (INT1)  | (Higher)<br>1                        | INTL5              | (Note 1)<br>EIF = 1                             | 002               |

|            | Serial<br>Input/Output<br>interrupt      | (1510)  | 2                                    | INTL <sub>4</sub>  | $EIF \cdot EIR_3 = 1$                           | 004               |

| interrupt  | Timer counter l<br>Overflow<br>interrupt | (IOVF1) | 3                                    | INTL <sub>3</sub>  | $EIF \cdot EIR_2 = 1$                           | 006               |

| Internal i | Timer counter 2<br>Overflow<br>interrupt | (10VF2) | 4                                    | INTL <sub>2</sub>  | (Note 2)<br>EIF·EIR <sub>1</sub> = 1            | 008               |

| L          | Timer interrupt<br>of divider            | (ITMR)  | 5                                    | intl <sub>1</sub>  | (Note 2)<br>EIF·EIR <sub>1</sub> = 1            | 00A               |

| Exte       | ernal interrupt 2                        | (INT2)  | 6<br>(Lower)                         | intl <sub>o</sub>  | $EIF \cdot EIR_0 = 1$                           | 00C               |

Interrupt enabling master F/F

Interrupt enabling register (EIR)

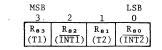

| MSB<br>3 | 2                | 1       | LSB<br>0 |

|----------|------------------|---------|----------|

| EIR3     | EIR <sub>2</sub> | $EIR_1$ | EIRO     |

- (Note 1) Since EIR register cannot make disabling of the INT1 interrupt, this interrupt is always accepted under the interrupt enabled condition (EIF = 1). Therefore, this should be used for the interrupt requiring the first priority such as emregency interrupt.

- (Note 2) The given acceptance condition by the program is the same in IOVF2 and ITMR; accordingly, the action of these interrupts to the acceptance/inhibition control is the same.

Table 1.8.1 Interrupt Factors

#### TECHNICAL DATA

TMP47C40P

TMP47C20P

Fig. 1.8.1 Interrupt Control Circuit

PREI ININA RY

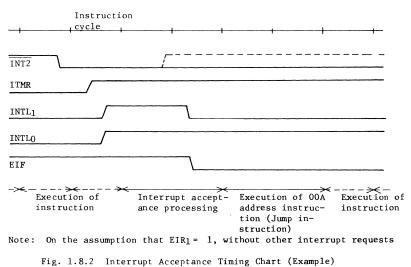

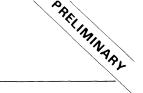

#### (1) Interrupt processing

The interrupt request signal to be sent to the CPU is held by the interrupt latch till the request is accpeted or the latch is reset by the initialization operation or instruction.

The processing for the interrupt acceptance is performed within two instruction cycle time after the completion of the execution of instruction (after the completion of the timer/counter processing if it is required).

The following operations are performed by the interrupt service program.

- The contents of the program counter and flag are saved in the stack.

- (2) The vector address is set to the program counter according to the interrupt factor.(A jump instruction to each interrupt service program is usually

stored in the program memory corresponding to the vector address.)

- (3) The status flag is set to "1".

- (4) The interrupt enabling master F/F is reset to "0" to inhibit the subsequent interrupt acceptance for a time.

- (5) The interrupt latch of the accepted interrupt factor is reset to "0".

- (6) The instruction stored in the vector address is executed.

The interrupt service program terminates after the execution of the (RETI) instruction.

The following operations are performed by the (RETI) instruction.

"KELININARY

(2) The interrupt enabling master F/F is set to "1".

When the multiple interrupt is accepted, the interrupt enabling master F/F should be set by the instruction. At this time, the enabling/disabling for each interrupt factor can be changed by updating the interrupt enabling register by the (XCH A, EIR) instruction.

The program counter and flag are automatically saved/restored in the interrupt processing. However, if saving/restoring of the accumulator and other registers is necessary, it should be designated by a program.

(2) Interrupt control by program

#### EIF

This is an enabling interrupt master F/F. Interrupt is put in the interrupt acceptance enabling state by setting the EIF to "1". It is reset to "0" immediately after having accepted an interrupt to inhibit the subsequent interrupt acceptance for a time, but is set to "1" again by the (RETI) instruction after the completion of the interrupt service program to return the enable state again. And then the other interrupt can be received.

The EIF can be set/reset in a program by using the (EICLR IL,r) and (DICLR IL, r) instructions. It is reset to "0" at initialization operation.

#### EIR register

This is a 4-bit register used for selection/control of enabling/disabling of the interrupt acceptance in a program.

TECHNICAL DATA

TMP47C40P TMP47C20P

Read/write operation is performed by use of the (XCH A, EIR) instruction. It is set to "O" at the initialization operation.

#### Interrupt latch

The interrupt latches  $(INTL_5 - INTL_0)$  provided for each interrupt factor are set by the rising edge of the input signal if the interrupt is caused by the internal factors, and are set by the falling edge of the input pin if it is caused by the external factors. Then, interrupt request signal is sent to the CPU. The interrupt latch holds the signal till the interrupt request is accepted, and is reset to "0" immediately after the interrupt has been accepted.

Since the interrupt latch can be reset to "O" by the (EICLR IL, r), (DICLR IL, r) and (CLR IL, r) instructions, the interrupt request signal can be initialized by a program. The latch is reset to "O" at the initialization operation.

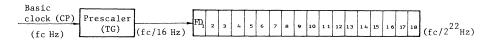

#### 1.9 Frequency divider (FD)

The divider  $({\rm FD}_1$  –  ${\rm FD}_{18})$  is made up 18-stage binary counter, and its output is used to generate various internal timing.

The basic clock (fc Hz) is divided into sixteen by the timing generator and input to the divider; therefore, the output frequency at the last stage is  $fc/2^{22}$  Hz.

It is reset to "O" at the initialization operation.

#### Timer Interrupt of divider (ITMR)

The divider is capable of sending the interrupt request for a certain frequency. Four different frequencies can be selected for timer interrupt by instructions.

Toshiba **R Z**

TECHNICAL DATA

TMP47C40P TMP47C20P

The command register is accessed as port address OP19, and is reset to "O" at time of the initialization.

The timer interrupt of divider is caused from the rising edge of the first output of the divider after the data has been written in the command resister.

(a) Structure of frequency divider

|                                    | MSB |   |   | LSB |                                     |

|------------------------------------|-----|---|---|-----|-------------------------------------|

| Port address                       | 3   | 2 | 1 | 0   |                                     |

| ( <sup>1011</sup> address)<br>OP19 |     |   |   |     | (*: don't care)                     |

|                                    | *   | 0 | * | *   | : Disable                           |

|                                    | *   | 1 | 0 | 0   | : Interrupt frequency $fc/2^{10}Hz$ |

|                                    | *   | 1 | 0 | 1   | : " fc/211H2                        |

|                                    | *   | 1 | 1 | 0   | : " fc/212Hz                        |

|                                    | *   | 1 | 1 | 1   | : " fc/213Hz                        |

| Interrupt fre- | For example,   |

|----------------|----------------|

| quency (Hz)    | fc=4.194304MHz |

| fc/210         | 4,096 Hz       |

| fc/211         | 2,048 Hz       |

| fc/212         | 1,024 Hz       |

| fc/213         | 512 Hz         |

<sup>(</sup>b) Command register

| Fig. | 1.9.1 | Frequency | Divider |

|------|-------|-----------|---------|

|------|-------|-----------|---------|

ТМР47С40Р ТМР47С20Р

1.10 Timer/Counter (TC<sub>1</sub>, TC<sub>2</sub>)

Two channels of 12-bit binary counter is contained to count time or event.

Since the RAM address with 4-bit unit is allocated to the timer/counter, the initial value setting and the content reading of the timer/counter can be executed by the RAM manipulated instructions.

|                    | LSB         |             |             |

|--------------------|-------------|-------------|-------------|

| (Timer/Counter 1)  |             |             |             |

| (IImer/oouncer I)  | TC1H        | TC1M        | TC1L        |

| (RAM Address)      | (F6)        | (F5)        | (F4)        |

|                    |             |             |             |

|                    | MSB         |             | LSB         |

| (Times (Geoster 2) | MSB         | TC2         | LSB         |

| (Timer/Counter 2)  | MSB<br>TC2H | TC2<br>TC2M | LSB<br>TC2L |

Fig. 1.10.1 Timer/Counter

#### (1) Timer/Counter Control

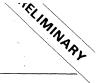

The timer/counter is controlled by the command specifying the operation mode. The command register for the timer/counter 1 and timer/counter 2 is accessed as port addresses OPIC and OPID, respectively. It is reset to "0" at the initialization operation. The count operation is started from the first rising edge of the count pulse applied by setting the value (mode) to the command register.

When the timer/counter is not used, the RAM addresses corresponding to the timer/counter can be used to store the user processing data by selecting the "disable" state. In the timer mode, the external input pins can be used as I/O ports  $[R_{83}$  (T1),  $R_{81}$  (T2)].

TECHNICAL DATA

| (; | a) | Command | register |

|----|----|---------|----------|

|----|----|---------|----------|

| Internal Pulse     | Max. Setting        | For example, fc=            |                            |

|--------------------|---------------------|-----------------------------|----------------------------|

| Rate (Hz)          | Time (SEC)          | Internal Pulse<br>Rate (Hz) | Max. Setting<br>Time (SEC) |

| fc/2 <sup>10</sup> | 2 <sup>22</sup> /fc | 4,096                       | 1                          |

| fc/2 <sup>14</sup> | 2 <sup>26</sup> /fc | 256                         | 16                         |

| fc/2 <sup>18</sup> | 2 <sup>30</sup> /fc | 16_                         | 256                        |

| fc/2 <sup>22</sup> | 2 <sup>34</sup> /fc | 1                           | 4,096                      |

(b) Selection of timer rate

Fig. 1.10.2 Control of Timer/Counter

TECHNICAL DATA

TMP47C40P TMP47C20P

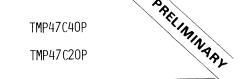

#### (2) Count Operation

When the rising edge of the count pulse is detected, the count latch is set to send a count request to the CPU.

The count operation of the timer/counter is performed requiring one instruction cycle time after completion of the instruction execution. The execution of the next instruction and the acceptance of the interrupt request are kept waiting during the operation. When the count request is sent from the timer/counter 1 and 2, at the same time, the count request of the timer/counter 1 is preferentially executed.

The maximum frequency applied to the external input pin under the event counter mode is fc/64 Hz if one channel is used. When two channels are used, fc/64 Hz is applied to the timer/counter 1, and fc/80 Hz to the timer/counter 2.

In the timer mode, the maximum frequency is determined by a command.

The maximum frequency applied to the external input pin in the pulse width measurement mode should be the frequency level available for analyzing the count value in the program. Normally, the frequency sufficiently slower than the designated internal pulse rate is applied to the external input pin.

Fig. 1.10.3 Mode and Count Value of Timer/Counter

# Decrease in execution speed of instruction due to count operation

The CPU carries out the count operation requiring one instruction cycle time for the count request. Therefore, this causes the decrease in the apparent speed of instruction execution. Some examples are shown below :

(a) In the timer mode with count pulse rate of fc/2  $^{10}~{\rm Hz}$  :

The count operation is inserted once every  $6^{2}$ -instruction cycle time, so that the apparent speed is decreased by 1/63=1.6% instruction execution speed. For example, the apparent speed is 4.063µs to 4µs instruction execution speed.

(b) In the event count mode :

It depends on the count pulse rate applied to the external input pin. In the worst case, when the timer/counter 1 and 2 are operated at the same time with the maximum count pulse rate, the count operation is inserted once every 4-instruction cycle time for the timer/counter 1, and once every 5-instruction cycle time for the timer/counter 2.

TECHNICAL DATA

TMP47C40P TMP47C20P PREIMINARY

The apparent speed of the instruction execution, therefore, decreases by 9/11 = .82%. The apparent speed is  $7.28\mu$ s to  $4\mu$ s instruction execution speed.

(3) Interrupt by overflow (IOVF1, IOVF2)

At the time when the overflow occurs, the timer/counter generates the interrupt request.

That is, the interrupt request is generated when the count value of FFF is changed to 000. The counting is continued after the interrupt request signal is generated. Assuming that the CPU provides the interrupt enabling state, and that the interrupt is accepted as soon as the overflow interrupt has been generated, the interrupt processing can be performed in the sequence illustrated in Fig. 1.10.4.

| <b>.</b>                | Instruction<br>cycle |                                  |                                       |                                       |

|-------------------------|----------------------|----------------------------------|---------------------------------------|---------------------------------------|

| Count pulse             |                      |                                  |                                       |                                       |

| Count <u>request</u>    |                      |                                  |                                       |                                       |

| Detection of ov         | verflow              | л                                |                                       |                                       |

| Occurr <u>ence of I</u> | OVF                  |                                  |                                       |                                       |

| Execu<br>of in<br>struc | - Count              | Execution<br>of in-<br>struction | Interrupt<br>acceptance<br>processing | Execution of<br>instruction<br>(jump) |

| Fig.                    | 1.10.4 Timing (      | Chart of Timer                   | /Counter in                           |                                       |

Interrupt by Overflow

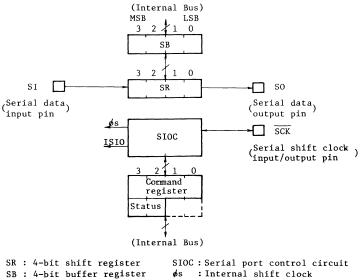

1.11 Serial Port (SIO)

A 4-bit serial port with a buffer is provided to transfer the serial data from/to the external circuitry. It is connected to the external circuitry through three pins [R92 ( $\overline{SCK}$ ), R91 (S0), R90 (SI)]. Since these pins are also used as port R9, the output latch of the R9 port should be set to "1" when the serial port is used. When it is not used, the pins can be used as I/O port R9.

Pin R90 in the transmit mode and pin  ${\rm R}_{91}$  in the receive mode are also available as  ${\rm I}/0$  port pin.

## (1) Circuit configuration

The serial port consists of a 4-bit shift register, a 4-bit buffer register, and its control circuit.

ISIO : Interrupt request

Fig. 1.11.1 Circuit Configuration of Serial Port

TECHNICAL DATA

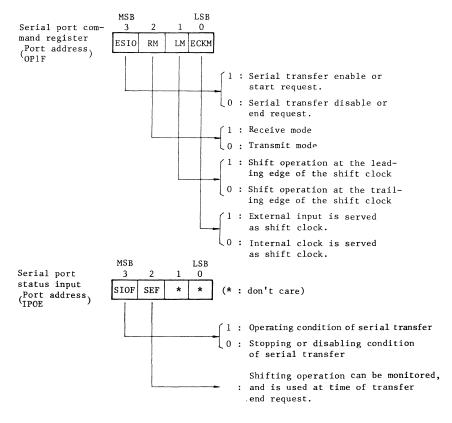

# (2) Serial port control

The serial port operation is controlled by the command. The command register is accessed with port address OPIF, and reset to "O" at the initialization operation. The operation status can be informed through the status input, which is accessed with port address IPOE.

Fig. 1.11.2 Command Register, Status Input

Toshiba **A** Z

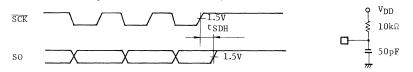

# (3) Shift clock (SCK)

The following shift clock modes can be selected by the contents of the command register.

- (a) Clock source (External/internal mode)

- (b) Shift edge of clock (Leading edge/trailing edge mode)

# Internal clock mode

$fc/2^7$  Hz is used for the shift clock (when the basic clock frequency fc is 4.194304 MHz, the shift clock frequency is 32.768 kHz.). At this time, the clock is supplied to the external devices through the  $\overline{SCK}$  pin. If the data setting (transmit mode) or the data reading (receive mode) rate by the program cannot follow the clock rate, the shift clock is automatically stopped and the next shift operation is suspended until the data processing is completed ("Wait" operation).

# External clock mode

The shift operation is performed by the clock provided from the external circuitry since the  $\overline{SCK}$  pin serves as an input.

#### Leading edge shift mode

Data is transmitted (transmit mode) or received (receive mode) at the leading edge of the  $\overline{SCK}$  pin signal.

## Trailing edge shift mode

Data is received (receive mode) at the trailing edge of the  $\overline{\text{SCK}}$  pin signal.

The  $\overline{SCK}$  pin must be set to the "high" level when the serial transfer is started. In the internal clock mode, the  $\overline{SCK}$  pin is automatically set to the "high" level because it serves as an output.

TMP47C40P TMP47C20P PREIMINARY

# (4) Operation mode

Selection of the following three transfer modes is available by changing the combination of the RM bit and LM bit of the command register.

| RM<br>(Bit 2) | LM<br>(Bit 1) | ECKM<br>(Bit 0) | Operation Mode                                                 |

|---------------|---------------|-----------------|----------------------------------------------------------------|

| 0             | 0             | 1/0             | Can not be used                                                |

| 0             | 1             | 1/0             | Transmit mode (Note)<br>(External/Internal clock)              |

| 1             | 0             | 1/0             | Receive(Trailing edge shift) mode<br>(External/Internal clock) |

| 1             | 1             | 1/0             | Receive(Leading edge shift) mode<br>(External/Internal clock)  |

(Note) Leading edge shift operation is performed.

Table 1.11.1 Operation Mode of Serial Port

In the transmit mode, the 4-bit data written to the buffer register from the CPU is shifted out by the shift register, and is output in the SO pin from the data of the LSB in sequence. The buffer register is accessed as the port address OPOF.

In the receive mode, the data to be input to the SI pin is shifted toward the LSB by the shift register in sequence, and is set in the buffer register after the 4-bit data has been received.

The CPU reads the contents of the buffer register, which is accessed as the port address IPOF.

TECHNICAL DATA

TMP47C40P TMP47C20P

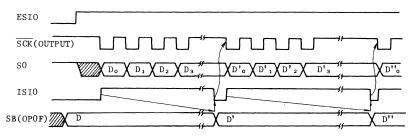

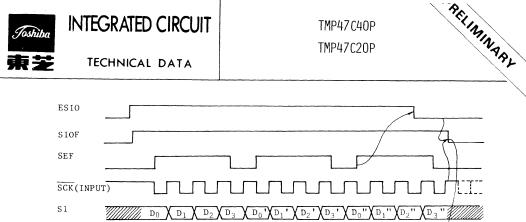

# Transmit mode

After this mode is set in the command register, the first transmit data (4-bit) is written in the buffer register (the data cannot be written in the buffer register, if the transmit mode is not set). Then the data can be transmitted by setting the ESIO (MSB of command register) to "1". The content of the buffer register is transferred to the shift register by the first shift clock, and the data in the LSB ( $D_0$ ) is output to the S0 pin. The buffer register ter then becomes empty, so that the interrupt (ISIO) requesting the next data takes place (buffer empty). After that, the remaining data ( $D_1 - D_3$ ) is automatically shifted out by the shift register by one data at a shift clock. The control by use of a program is not necessary in this operation.

Data is written in the buffer register by outputting the next transmit data (4-bit) to the port address OPOF in the interrupt service program, and at the same time the interrupt request is reset to "0".

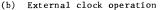

## Internal clock operation

In case of  $fc/2^7$  Hz internal clock operation, if the next data is not set in the buffer register (OPOF has not been accessed by the program) though the 4-bit data has been entirely shifted out, the shift clock automatically stops, and the wait operation is taking place until the data is set.

The maximum transmission rate is 31250 bit/sec. at the 4 MHz basic clock.

417

TECHNICAL DATA

TMP47C40P TMP47C20P

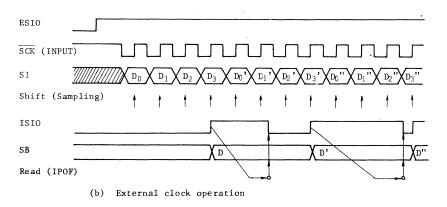

# External clock operation

Since the shift operation synchronizes entirely with the clock provided from the external circuitry, the data should have been written in the buffer register before the next 4-bit data is shifted out. Therefore, the transfer rate is determined by the maximum time lag from the receipt of interrupt request (ISIO) to the writing of data in the buffer register by the interrupt service program.

(a) Internal clock operation (with wait operation)

Fig. 1.11.3 Transmit Mode

# TECHNICAL DATA

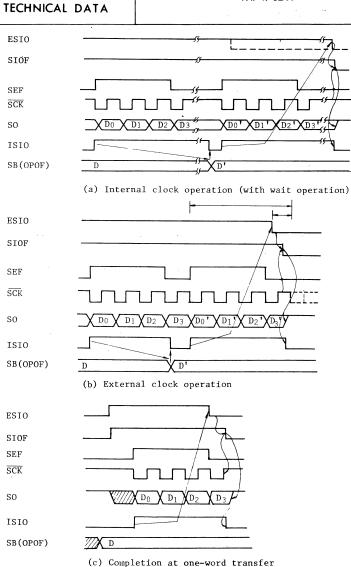

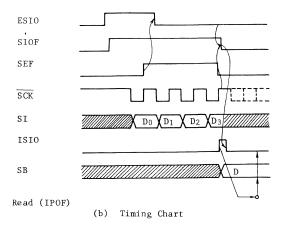

# Completion of transmission

When the buffer register becomes empty, the interrupt occurs to request the next data. In case where the transmission is desired to be completed after the data is entirely transferred, the transmit operation can be stopped upon completion of transferring the current data shifted out, by resetting the ESIO to "0" without outputting the data. Whether or not the transfer operation is completed can be sensed in a program by the SIOF (MSB of the status input).

In the external clock operation, the ESIO must be reset to "0" before the next data is shifted out as in the data updating operation (however, the data is not updated when the operation is completed). When the wait operation have been already performed in the internal clock operation, the data transfer is terminated immediately after ESIO = 0.

One word transfer can be terminated by ESIO = 0 in the interrupt service program on receipt of the interrupt caused by the buffer empty.

419

TMP47C40P TMP47C20P

Fig. 1.11.4 Completion of Transmission

Toshiba 東芝

# TECHNICAL DATA

TMP47C40P TMP47C20P

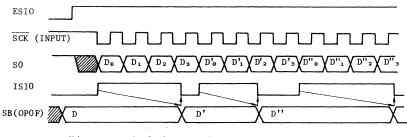

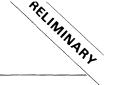

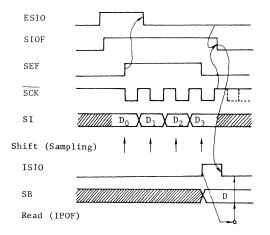

#### Receive (trailing edge shift) mode

Data can be received by setting the receive mode in the command register as well as by setting the ESIO (MSB of command register) to "1". When the four data are received from the SI pin, the 4-bit data is transferred from the shift register to the buffer register. At the same time, interrupt (ISIO) takes place to request the data reading (buffer full). Since the shift register has been transferring the data to the buffer register, the shift operation is continued without waiting for the data being read.

When the data received from the port address IPOF is read in the interrupt service program, the interrupt request is reset. And then the next 4-bit data is transferred from the shift register to the buffer register if the buffer register has been full.

## Internal clock operation

During the operation of the internal clock of  $fc/2^7$ Hz, if the next 4bit data is not read out of the buffer register (the IPOF has not been accessed) in the program though the 4-bit data has been entirely input, the shift clock automatically stops, and the wait operation is taking place until the data is read out.

The maximum receiving rate is 31250 bit/sec at the 4 MHz basic clock.

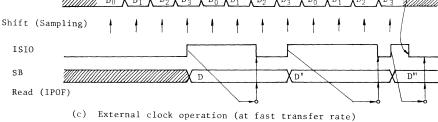

# External clock operation

Since the shift operation synchronizes entirely with the clock provided from the external circuitry, the current data should have been read by the instruction before the next 4-bit data is transferred to the buffer register. The transfer rate is, therefore, determined by the maximum time lag from the receipt of interrupt request (ISIO) to the read of the data in the buffer register by the interrupt service program.

421

PREI MINARY

Fig. 1.11.5 Receive (trailing edge shift) Mode

# Completion of receiving

When all of the data are read, the receiving of data can be completed upon termination of the current data transfer, by resetting the ESIO to "O".

Whether or not the data transmission is terminated can be sensed in a program by the SIOF (MSB of status input).

To complete the receive operation when the synchronization is desired between the serial transfer and interrupt service program (indicates data reading or completion of receiving), there are two ways according to the speed of shift clock.

The receive/transmit mode must be maintained without switching the mode until the last data is read out even if the completion of the data transfer is indicated; otherwise the contents of the buffer register will be lost.

(a) Sufficiently slow data transfer rate (external clock operation)

If the timing, operated by the external clock, is slow enough to reset the ESIO to "0" prior to the generation of the next shift clock, the ESIO can be reset to "O" in the interrupt service program which is loaded to read out the last data. Thereafter the last data is read.

Fig. 1.11.6 Completion of Receiving (at slow transfer rate)

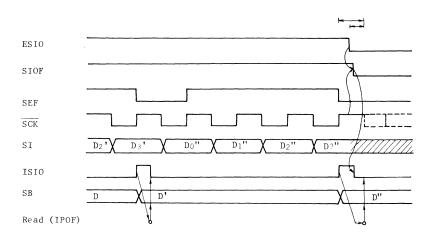

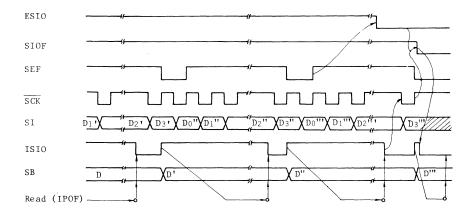

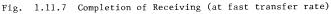

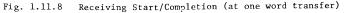

#### (b) Fast transfer rate

If the shift operation for the next data may start before the current data is read out by receipt of the interrupt request becuase the transfer rate is too fast, the interrupt service program which is loaded to read out the last data but one should be used to reset the ESIO to "0" after confirming that the SEF (bit 2 of status input) has been set to "1".

Thereafter, the data should be read. No operation is required to complete the data transfer in the interrupt service program for reading the last data.

TMP47C40P TMP47C20P

The method mentioned above is usually taken for the internal clock operation. In the external clock operation, however, the reset of the ESIO and the read of data must be completed before the last data is transferred to the buffer register.

(a) Program sequence of receive end indication

(b) Timing Chart (in case of internal clock operation with wait operation)

TECHNICAL DATA

TMP47C40P TMP47C20P

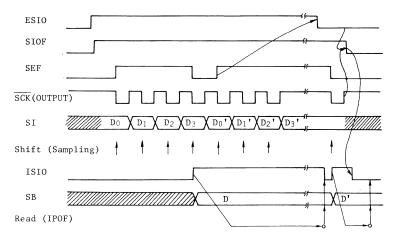

# (c) One word transfer

The data receive operation starts after the ESIO is set to "1". Then, the ESIO is reset to "0" after confirming that the SEF status is set to "1". In this sequence, one interrupt casued by the buffer full takes place; therefore, the data should be read out by the service program.

(a) Program sequence of receiving start/end indication

TMP47C40P TMP47C20P

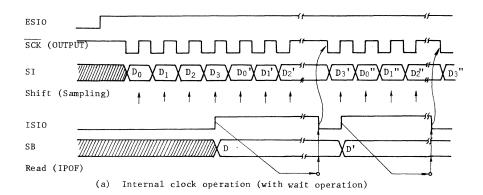

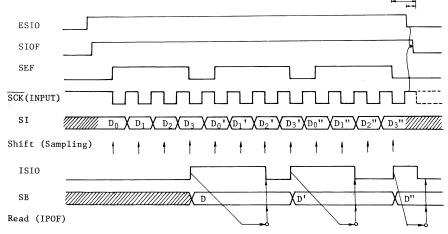

# Receive (leading edge shift) mode

With this mode set in the command register, the data can be received by setting the ESIO (MSB of command register) to "1".

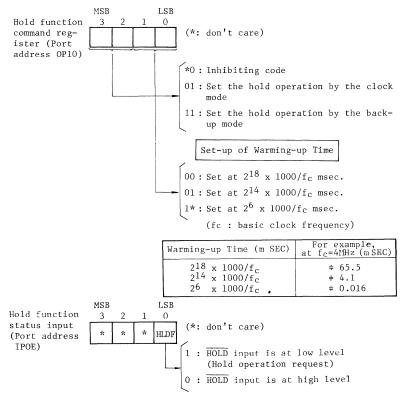

When the four data are received from the SI pin, the 4-bit data is transferred from the shift register to the buffer register. At the same time, the interrupt (ISIO) occurs to request the data reading (buffer full). Since the shift register is transferring the data to the buffer register, the shift operation has been continued without waiting for the data being read.