## **TOSHIBA**

TOSHIBA Original CMOS 8-Bit Microcontroller

TLCS-870/C Series

TMP86FM25FG

TOSHIBA CORPORATION

Semiconductor Company

# Revision History

| Date      | Revision |                  |

|-----------|----------|------------------|

| 2008/3/6  | 1        | First Release    |

| 2008/8/29 | 2        | Contents Revised |

## Caution in Setting the UART Noise Rejection Time

When UART is used, settings of RXDNC are limited depending on the transfer clock specified by BRG. The combination "O" is available but please do not select the combination "-".

The transfer clock generated by timer/counter interrupt is calculated by the following equation:

Transfer clock [Hz] = Timer/counter source clock [Hz] ÷ TTREG set value

|                                                                 |                        |                            | RXDNO                                                   | setting                                                 |                                                             |

|-----------------------------------------------------------------|------------------------|----------------------------|---------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|

| BRG setting                                                     | Transfer<br>clock [Hz] | 00<br>(No noise rejection) | 01<br>(Reject pulses shorter<br>than 31/fc[s] as noise) | 10<br>(Reject pulses shorter<br>than 63/fc[s] as noise) | 11<br>(Reject pulses shorter<br>than 127/fc[s] as<br>noise) |

| 000                                                             | fc/13                  | 0                          | 0                                                       | 0                                                       | <u> </u>                                                    |

| 110                                                             | fc/8                   | 0                          | (7/1                                                    | - 6                                                     | → -                                                         |

| (When the transfer clock gen-<br>erated by timer/counter inter- | fc/16                  | 0                          | (V)                                                     | \$-\C\                                                  | /                                                           |

| rupt is the same as the right side column)                      | fc/32                  | 0                          | 0                                                       | 0                                                       | _                                                           |

| The setting except the                                          | above                  | 0                          |                                                         |                                                         | 0                                                           |

## **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Pb free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a temporary substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

1. Part number

Example: TMPxxxxxxFG TMPxxxxxxFG

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C

LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

Ι

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page.

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

TOSHIBA TMP86FM25

### 1. Part number

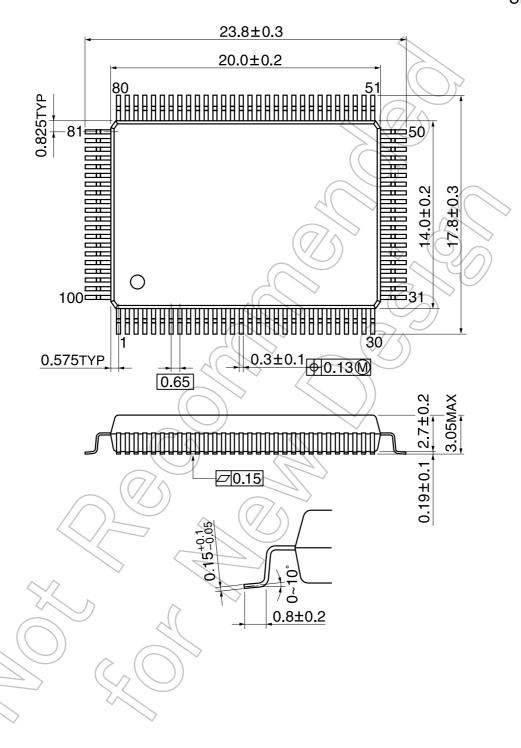

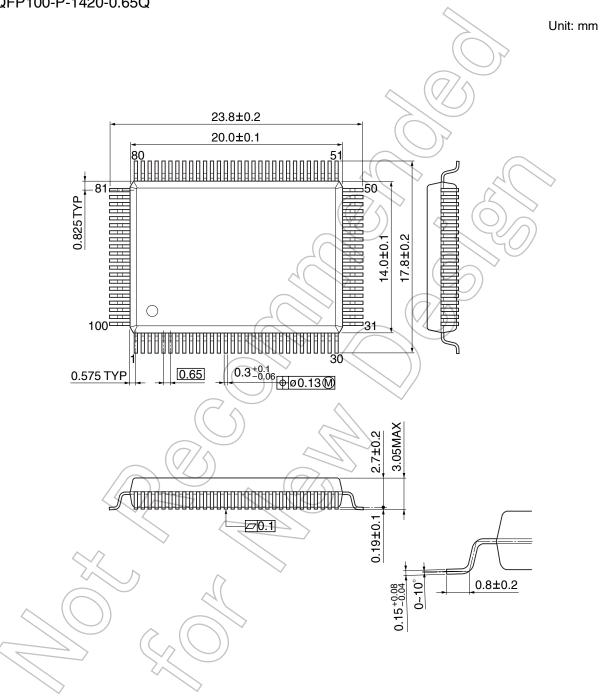

### 2. Package code and dimensions

| Previous Part Number (in Body Text) | Previous Package Code<br>(in Body Text) | New Part Number | New Package Code    | ОТР |

|-------------------------------------|-----------------------------------------|-----------------|---------------------|-----|

| TMP86FM25F                          | P-QFP100-1420-0.65A                     | TMP86FM25FG     | QFP100-P-1420-0.65Q | _   |

<sup>\*:</sup> For the dimensions of the new package, see the attached Package Dimensions diagram.

### 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

Lead solderability of Pb-free devices (with the G suffix)

| Test          | Test Conditions      | Remark                                                                |

|---------------|----------------------|-----------------------------------------------------------------------|

| Solderability | (1) Use of Lead (Pb) | Leads with over 95% solder coverage till lead forming are acceptable. |

### 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

#### RESTRICTIONS ON PRODUCT USE

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airlane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations that

regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring

as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

### 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

TOSHIBA TMP86FM25

(Annex)

## Package Dimensions

QFP100-P-1420-0.65Q

III 2008-03-06

Comparison table of TMP86CM25F/CS25F/PS25F/C925XB and TMP86CM25AF/FM25F Difference

|                                         | TMP86CM25F/<br>TMP86CS25F          | TMP86PS25F                    | TMP86C925XB<br>(Emulation chip) | TMP86FM25F                          | TMP86CM25AF          |

|-----------------------------------------|------------------------------------|-------------------------------|---------------------------------|-------------------------------------|----------------------|

| ROM                                     | 32 K (Mask ROM)<br>60 K (Mask ROM) | 60 K (OTP)                    | -                               | 32 K (Flash)                        | 32 K (Mask ROM)      |

| RAM                                     | 2                                  | K                             | -                               | 2                                   | K                    |

| I/O                                     | 42                                 | pin                           | 42 pin (MCU part)               | 42                                  | pin                  |

| External<br>Interrupt                   |                                    | 5 pin                         |                                 | 5                                   | pin                  |

| AD Converter                            |                                    | 8-bit AD converter $\times$ 8 | ch                              | 8-bit AD convert                    | er × 8 ch (Note 3)   |

| Timer Counter                           |                                    | 18-bit timer $\times$ 1 ch    |                                 | 18-bit tim                          | ner × 1 ch           |

| Timer Counter                           |                                    | 8-bit timer × 4 ch            |                                 |                                     | er × 4 ch            |

| Serial Interface                        | 8-bit SIO × 2 ch                   |                               |                                 |                                     | O × 2 ch             |

| Ochai interiace                         | UART × 1 ch                        |                               |                                 | UART                                | ×1 ch                |

| LCD                                     |                                    | 60 seg × 16 com               |                                 | 60 seg × 16                         | com (Note 4)         |

| Key-on<br>Wakeup                        |                                    | 4 ch                          |                                 | 4                                   | ch                   |

| Operating                               | 1.8 to 5.5 V                       | at 4.2 MHz                    | 1.8 to 5.25 V at 4.2 MHz        | 1.8 to 3.6 V at 4.2 N               | MHz (External clock) |

| Voltage                                 | 2.7 to 5.5 \                       | / at 8 MHz                    | 2.7 to 5.25 V at 8 MHz          | 1.8 to 3.6 V at 8 MHz (Resonator)   |                      |

| in MCU Mode                             | 4.5 to 5.5 V                       | at 16 MHz                     | 4.5 to 5.25 V at 16 MHz         | 2.7 to 3.6 \                        | / at 16 MHz          |

| Operating<br>Temperature<br>in MCU Mode | −40 tc                             | -40 to 85°C 0 to 60°C         |                                 | -40 to                              | o 85°C               |

| Writing to Flash Memory                 |                                    | - 4                           |                                 | 2.7 to 3.6V at 16 MHz<br>25°C ± 5°C |                      |

| Package                                 | P-QFP100-                          | 1420-0.65A                    | FBGA272                         | P-QFP100-                           | 1420-0.65A           |

| CPU Wait (Note 1)                       |                                    | N/A                           | ,                               | // Available                        | e (Note 2)           |

Note 1: The CPU wait is a CPU halt function for stabilizing of power supply of Flash memory. The CPU wait period is as follows. In the CPU wait period except RESET, CPU is halted but peripheral functions are not halted. Therefore, if the interrupt occurs during the CPU wait period, the interrupt latch is set. In this case, if the IMF has been set to "1", the interrupt service routine is executed after CPU wait period. For details refer to 1.1 "Flash Memory" in TMP86FM25F data sheet.

| Condition                                                                      | Wait Time              | Halt/Operate |             |

|--------------------------------------------------------------------------------|------------------------|--------------|-------------|

| Condition                                                                      | Wall Tillle            | CPU          | Peripherals |

| After reset release                                                            | 2 <sup>10</sup> /fc[s] | Halt         | Halt        |

| Changing from STOP mode to NORMAL mode (at EEPCR <mnpwdw> = "1")</mnpwdw>      | 2 <sup>10</sup> /fc[s] | Halt         | Operate     |

| Changing from STOP mode to SLOW mode (at EEPCR <mnpwdw> = "1")</mnpwdw>        | 2 <sup>3</sup> /fs[s]  | Halt         | Operate     |

| Changing from IDLE0/1/2 mode to NORMAL mode (at EEPCR <atpwdw> = "0")</atpwdw> | 2 <sup>10</sup> /fc[s] | Halt         | Operate     |

| Changing from SLEEP0/1/2 mode to SLOW mode (at EEPCR <atpwdw> = "0")</atpwdw>  | 2 <sup>3</sup> /fs[s]  | Halt         | Operate     |

- Note 2: Though the TMP86CM25AF does not have a Flash memory, the CPU wait function is inserted in TMP86CM25A to keep the compatibility with Flash product (TMP86FM25F).

- Note 3: AD conversion time of TMP86CM25A/FM25 is different from that of TMP86CM25/CS25/PS25/C925. For details, refer to 2.12 "8-Bit AD Converter (ADC)".

- Note 4: The reference voltage of TMP86CM25A/FM25 is different from that of TMP86CM25/CS25/PS25/C925. For details, refer to "Electrical Characteristics".

### CMOS 8-Bit Microcontroller TMP86FM25F

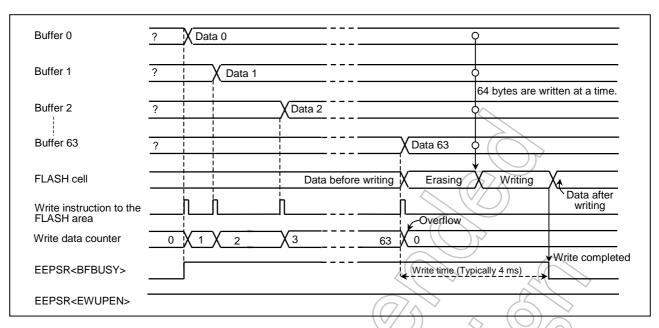

The TMP86FM25 is a Flash type MCU which includes 32 Kbytes Flash memory. It is a pin compatible with a mask ROM product "A" version of the TMP86CM25A. Writing the program to built-in Flash memory, the TMP86FM25 operates as the same way as the TMP86CM25A. The TMP86FM25 has a 2 Kbytes BOOT ROM (Masked ROM) for programming to Flash memory.

| Product No. | Flash Memory  | BOOT ROM     | RAM            | Package             |

|-------------|---------------|--------------|----------------|---------------------|

| TMP86FM25F  | 32 K × 8 bits | 2 K × 8 bits | 2.0 K × 8 bits | P-QFP100-1420-0.65A |

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general

can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are

requipment, onlice equipment, measuring equipment, moustrain hobbits, domestic appliances, etc.). These Toshba products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all typics of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

The products described in this document are subject to the foreign exchange and foreign trade laws.

TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

2004-03-01 86FM25-1

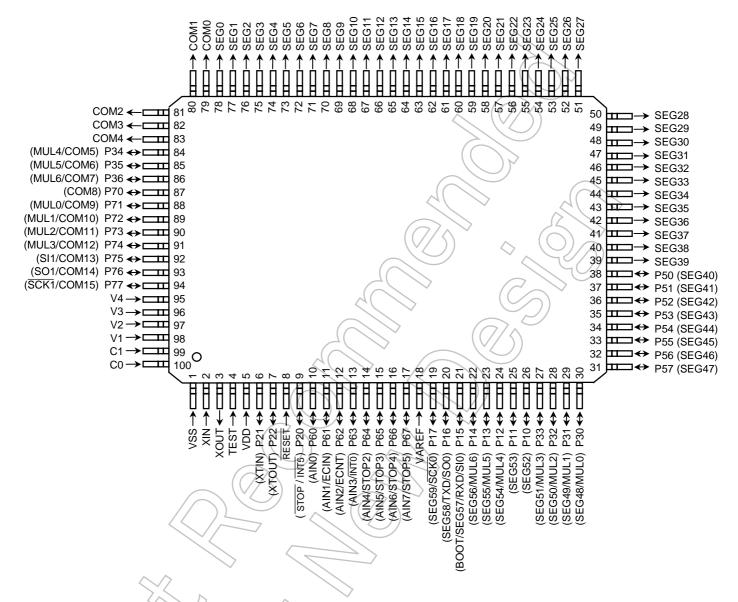

### Pin Assignments (Top view)

P-QFP100-1420-0.65A

Note1: The masked ROM product (TMP86CM25AF/CM25F/CS25F), the OTP product (TMP86PS25F) and the emulation chip (TMP86C925XB) don't have a BOOT function in P15 pin.

Note2: Ports assigned as MUL6 to MUL0 can switch pin assignment by the multifunction register (MULSEL). For functions assigned to each pin, see the table below.

| Pin Name | Function                | Pin Assignment |

|----------|-------------------------|----------------|

| MUL0     | DVO                     | P30 or P71     |

| MUL1     | PDO3 , PWM3 ,TC3        | P31 or P72     |

| MUL2     | PDO4 , PWM4 , PPG4 ,TC4 | P32 or P73     |

| MUL3     | PDO6, PWM6, PPG6, TC6   | P33 or P74     |

| MUL4     | INT1                    | P12 or P34     |

| MUL5     | INT2                    | P13 or P35     |

| MUL6     | INT3                    | P14 or P36     |

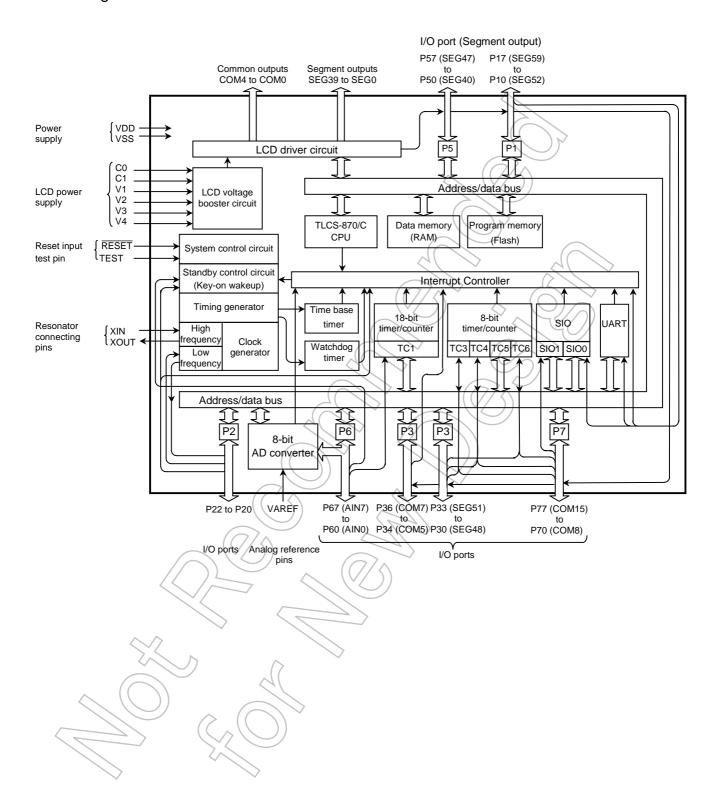

### **Block Diagram**

86FM25-3 2004-03-01

### Pin Funtions

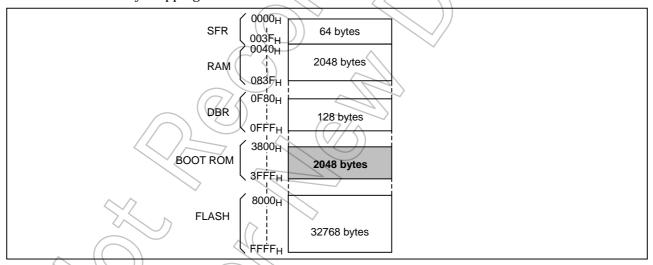

The TMP86FM25 has MCU mode and serial PROM mode.

#### (1) MCU mode

In the MCU mode, the TMP86FM25 is a pin compatible with the TMP86CM25A (Make sure to fix the TEST pin to low level).

### (2) Serial PROM mode

In the Serial PROM mode, programming to Flash memory is available by executing BOOT ROM.

In the serial PROM mode, TXD (P16) and RXD (P15) pins are used as a serial interface pin. Therefore, if the programming is executed on-board after mounting, these pins should be released from the other devices for communication in serial PROM mode.

86FM25-4 2004-03-01

### 1.1 FLASH Memory

#### 1.1.1 Outline

The TMP86FM25 incorporates 32768 bytes of FLASH memory (Address 8000H to FFFFH). The writing to FLASH is controlled by FLASH control register (EEPCR), FLASH status register (EEPSR).

To write data to the FLASH, execute the Serial PROM mode. For details about the Serial PROM mode, refer to "2.1 Serial PROM Mode".

The FLASH memory of the TMP86FM25 features:

- The FLASH memory is constructed of 512 pages FLASH memory and one page size is 64 bytes (512 pages × 64 bytes = 32768 bytes).

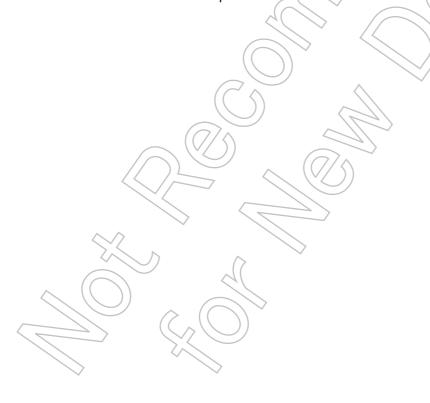

- The TMP86FM25 incorporates a 64-byte temporary data buffer. The data written to FLASH memory is temporarily stored in this data buffer. After 64 bytes data have been written to the temporary data buffer, the writing to FLASH memory automatically starts by page writing (The 64 bytes data are written to specified page of FLASH simultaneously). At the same time, page-by-page erasing occurs automatically. So, it is unnecessary to erase individual pages in advance.

- The FLASH control circuit incorporates an oscillator dedicated to the FLASH. So FLASH writing time is independent of the system clock frequency (fc). In addition, because an FLASH control circuit controls writing time for each FLASH memory cell, the writing time varies in each page (Typically 4 ms per page).

- Controlling the power for the FLASH control circuit (Regulator and voltage step-up circuit) achieves low power consumption if the FLASH is not in use (Example: When the program is executed in RAM area).

### 1.1.2 Conditions for Accessing the FLASH Areas

The conditions for accessing the FLASH areas vary depending on each operation mode. The following tables shows FLASH are access conditions.

Table 1.1.1 FLASH Area Access Conditions

|              | Area           | Oper              | ation Mode                 |

|--------------|----------------|-------------------|----------------------------|

| 7            | Alea           | MCU Mode (Note 1) | Serial PROM Mode (Note 2)  |

| FLASH memory | 8000H to FFFFH | Read/Fetch only   | Write/Read/Fetch supported |

Note 1: "MCU Mode" shows NORMAL1/2 and SLOW1/2 modes.

Note 2: "Serial PROM Mode" shows the FLASH controlling mode. For details, refer to 2.1 "Serial PROM Mode".

Note 3: "Fetch" means reading operation of FLASH data as an instruction by CPU.

86FM25-5 2004-03-01

### 1.1.3 Differences among Product Series

The specifications of the FLASH product (TMP86FM25) are different from TMP86CM25A (Masked ROM "A" version), TMP86C925XB (Emulation chip), TMP86CM25F/CS25F (Masked ROM) and TMP86PS25 (OTP) as listed below. See 1.2.2 "Control" for explanations about the control registers.

| -                                                                                                                                                          |                                       |                                                                                                                                                                                                                  |                                                                                                                                                               |                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                            |                                       | FLASH Product<br>(TMP86FM25)                                                                                                                                                                                     | Masked ROM<br>"A" Version<br>(TMP86CM25AF)                                                                                                                    | The Current Products TMP86C925XB (Emulation chip) TMP86CM25F/CS25F (Mask ROM) TMP86PS25F (OTP)                                                     |

| Rewriting the EEPCR register <eepmd, eeprs,="" mnpwdw=""></eepmd,>                                                                                         |                                       | It is possible to rewrite the EEPCR register only when the program execution area in use is RAM/BOOT-ROM.  Neither the EEPMD nor EEPRS itself does not function.                                                 |                                                                                                                                                               | The FLASH function is not executed because the emulation chip and the MASK (except "A" version)/OTP products don't have EEPCR and EEPSR registers. |

| FLASH write time                                                                                                                                           |                                       | Typically 4 ms<br>(Independent of the<br>system clock)                                                                                                                                                           | (Writing to an area that corresponds to the FLASH area causes nothing.)                                                                                       | Therefore, the software including the FLASH register can not be emulated by the emulation chip. If the software including the FLASH                |

| Executing a read instruction/for 8000H to FFFFH area when EEPSR <bfbusy> = "1".</bfbusy>                                                                   | etch to the                           | If EEPSR <bfbusy> = "1", executing a read instruction/fetch to the FLASH area causes FFH to be read regardless of what the current ROM data is. Fetching FFH results in a software interrupt occurring.</bfbusy> | Always masked ROM data is read.                                                                                                                               | register is executed in the MASK (except "A" version)/OTP or the emulation chip, the software process differs from the FLASH product.              |

| Executing a write instruction to the 8000H to FFFFH area when EEPCR <eepmd> = "0011" EEPSR<ewupen> = "1" and EEPSR<bfbusy> = "0"</bfbusy></ewupen></eepmd> | MCU<br>mode<br>Serial<br>PROM<br>mode | The EEPSR <bfbusy> st disabled):  The EEPSR<bfbusy> is set to "1" (Write enabled).</bfbusy></bfbusy>                                                                                                             | ays at <sup>9</sup> 0" (Write                                                                                                                                 |                                                                                                                                                    |

| CPU wait for Flash (Wait period for stabilizing of the power supply of Flash control circuit)                                                              |                                       | The wait period is inserted Reset, STOP mode (EEPC and JDLE/SLEEP mode (E"0").  Even if the FLASH register the wait period is inserted                                                                           | CR <mnpwdw> = "1") EPCR<atpwdw> = ris not used for software,</atpwdw></mnpwdw>                                                                                | The wait period is not inserted. Even if the FLASH register is not used for software, the Reset and STOP process differs from the FLASH product.   |

| 2 Kbytes a                                                                                                                                                 |                                       | 2 Kbytes are included in<br>the 3800H to 3FFFH<br>area.                                                                                                                                                          | No BOOT-ROM is included. Executing a read/fetch to the 3800H to 3FFFH area causes "FFH" to be read. Fetching "FFH" results in a software interrupt occurring. | The current products don't have BOOT-ROM. Therefore, the serial PROM mode can not be emulated in the current products.                             |

| Operating voltage (VDD)                                                                                                                                    | S.                                    | 1.8 to 3.6 V (1 MHz to 4.2<br>1.8 to 3.6 V (1 MHz to 8 M<br>2.7 to 3.6 V (1 MHz to 16 M                                                                                                                          | Hz: Resonator)                                                                                                                                                | 1.8 to 5.5 V (1 MHz to 4.2 MHz) 2.7 to 5.5 V (1 MHz to 8 MHz) 4.5 to 5.5 V (1 MHz to 16 MHz) The maximum voltage of the TMP86C925XB is 5.25 V.     |

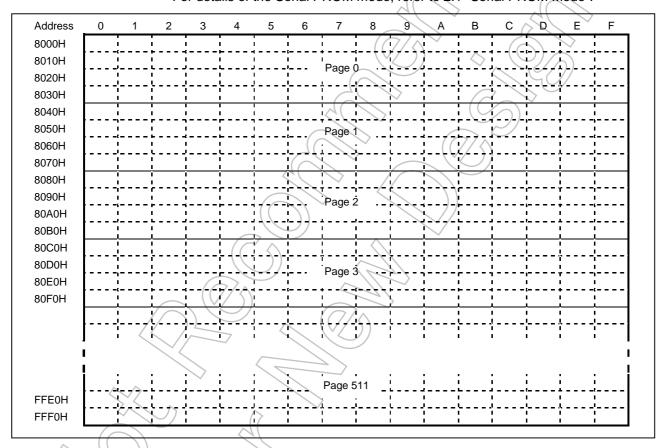

### 1.1.4 FLASH Memory Configuration

64 consecutive bytes in the FLASH area are treated as one group, which is defined as a page. The TMP86FM25 incorporates a one-page temporary data buffer. Writing data to FLASH is temporarily stored in this 64-byte data buffer. After 64 bytes data have been written to the temporary data buffer, these data are written to specified page of FLASH at a time. However, data can be read from any address byte by byte.

### 1.1.4.1 Page Configuration

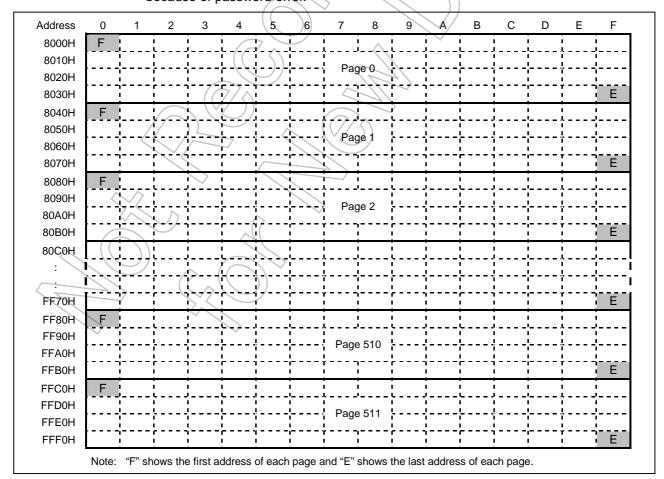

The FLASH area has a page configuration of 64 bytes/page as shown below. The total number of bytes in it is  $512 \text{ pages} \times 64 \text{ bytes}$  (= 32768 bytes). The writeable area is 8000 H to FFFFH in Serial PROM mode.

Note: The FLASH area (8000H to FFFFH) can be written only in the Serial PROM mode. For details of the Serial PROM mode, refer to 2.1 "Serial PROM Mode".

Figure 1.1.1 Page Configuration

86FM25-7 2004-03-01

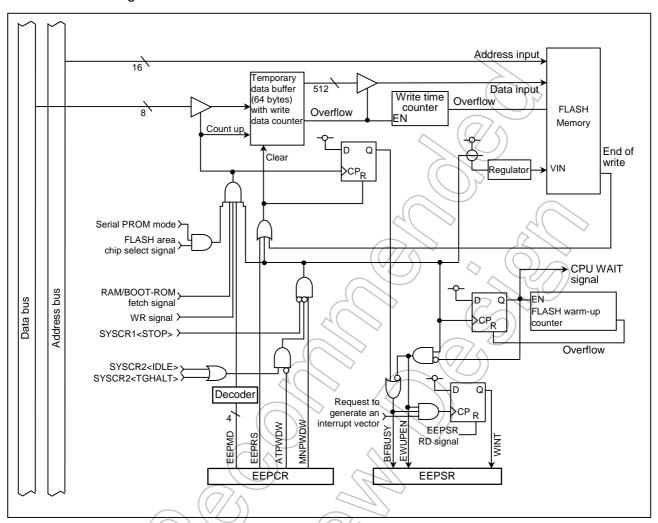

### 1.2 FLASH Memory Control Circuit

### 1.2.1 Configuration

Figure 1.2.1 FLASH Memory Control

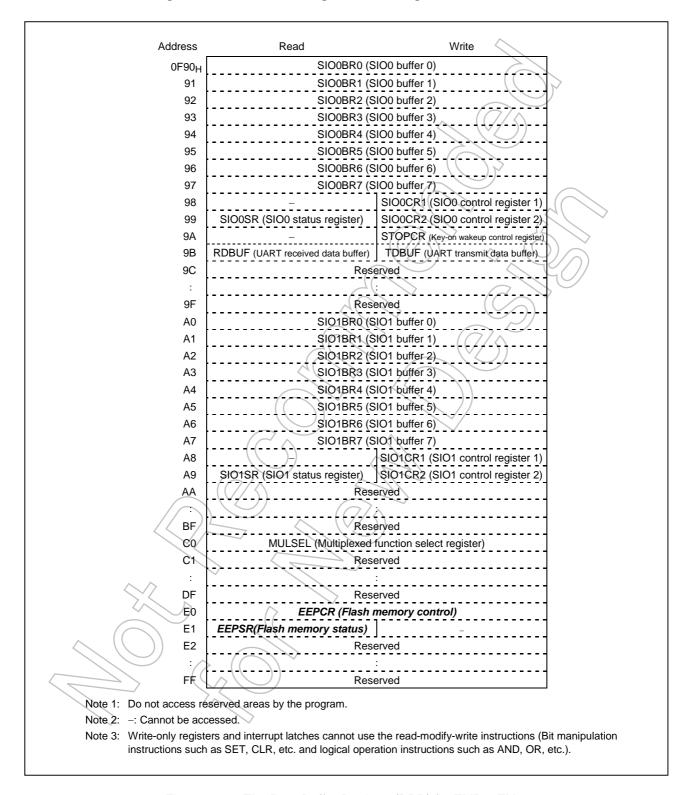

### 1.2.2 Control

The FLASH memory is controlled by FLASH control register (EEPCR) and FLASH status register (EEPSR). These registers are assigned to DBR.

Figure 1.2.1 The Data Buffer Register (DBR) for TMP86FM25

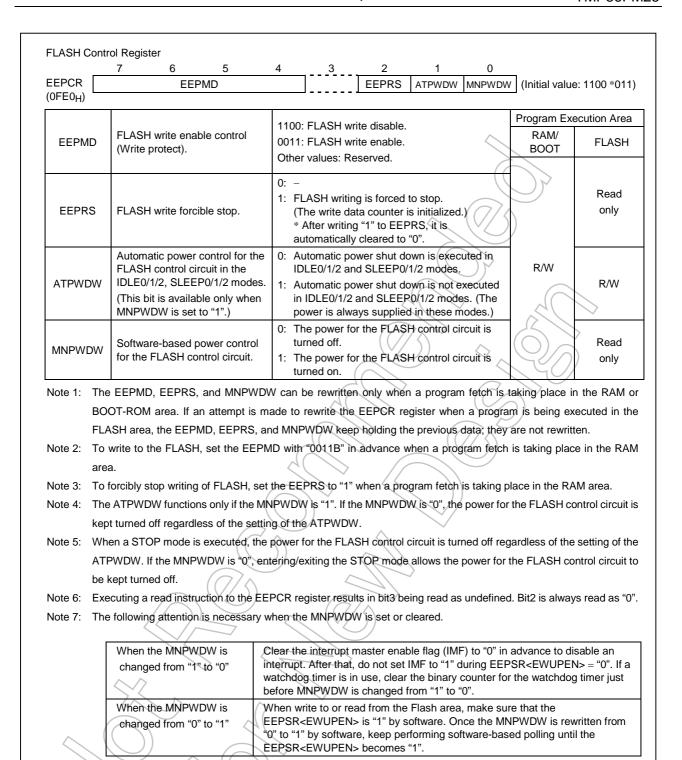

Figure 1.2.2 FLASH Control Register

In MCU mode, the EEPMD and EEPRS should be set to "1100B" and "0".

| WINT   | Interrupt detection du               | ring a write to        | O: Not detected  Detected (Interrupt occurred)  * WINT is automatically cleared to "0" when read instruction is executed to EEPSR. |         | n read      |                 |              |

|--------|--------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|-----------------|--------------|

|        | ELA OLL a cartacl                    | Control circuit status | Operating (Power on)                                                                                                               |         | Halt (Power | off) or warm-up | Read<br>only |

| EWUPEN | FLASH control circuit status monitor | FLASH status           | Temporary data buffer empty                                                                                                        | Writing | Di          | sable           | •            |

|        |                                      |                        | 1                                                                                                                                  | 1 ( (   |             | 0               |              |

| BFBUSY | FLASH write busy flag                |                        | 0                                                                                                                                  | 1       | J)          | 1               |              |

- Note 1: If a nonmaskable interrupt occurs during a write to the FLASH, the WINT is set to "1" and the writing is discontinued, and then warm-up period (CPU wait) for the control circuit of Flash memory is executed. (The write data counter is initialized.) If WINT = "1" is detected in the nonmaskable interrupt service routine, a write is not completed successfully. So, it is necessary to try a write again. The content of the page to which a write is taking place may be changed to an unexpected value depending on the timing when the WINT becomes "1".

- Note 2: Even if a nonmaskable interrupt occurs during an FLASH warm-up, the CPU stays at a halt until the warm-up is finished.

- Note 3: The WINT is automatically cleared to "0" when a read instruction is executed to the EEPSR register.

- Note 4: When MNPWDW is changed from "0" to "1", EWUPEN becomes "1" after taking 2<sup>10</sup>/fc [s] (if SYSCK = "0") or 2<sup>3</sup>/fs [s] (if SYSCK = "1"). Before accessing the FLASH, make sure that the EWUPEN is "1" in the RAM area.

- Note 5: If the BFBUSY is "1", executing a read instruction or fetch to the FLASH area causes FFH to be read. Fetching FFH results in a software interrupt occurring.

- Note 6: In the TMP86CM25A, if the EWUPEN is "1", writing to the masked ROM area that corresponds to the FLASH area does not set the BFBUSY of the TMP86CM25A to "1".

Figure 1.2.3 FLASH Status Register

### 1.2.3 FLASH Write Enable Control (EEPCR<EEPMD>)

In the FLASH product, the control register can be used to disable a write to the FLASH (Write protect) in order to prevent a write to the FLASH from occurring by mistake because of a program error or microcontroller malfunction. To enable a write to the FLASH, set the EEPCR<EEPMD> with 0011B. To disable a write to the FLASH, set the EEPCR<EEPMD> with 1100B. A reset initializes the EEPCR<EEPMD> to 1100B to disable a write to the FLASH. Usually, set the EEPCR<EEPMD> with 1100B, except when it is necessary to write to the FLASH.

- Note 1: The FLASH memory (8000H to FFFFH) can be written only in the serial PROM mode.

- Note 2: The EEPCR<EEPMD> can be rewritten only when a program is being executed in the RAM area. Executing a write instruction to the EEPCR<EEPMD> in the FLASH area does not change its setting.

- Note 3: In the TMP86CM25A, executing a write instruction to the EEPCR<EEPMD> changes its setting; however, the new setting does not take effect.

- Note 4: This function can be used in serial PROM mode. In MCU mode, the EEPCR<EEPMD> should be always set to "1100B".

### 1.2.4 FLASH Write Forcible Stop (EEPCR<EEPRS>)

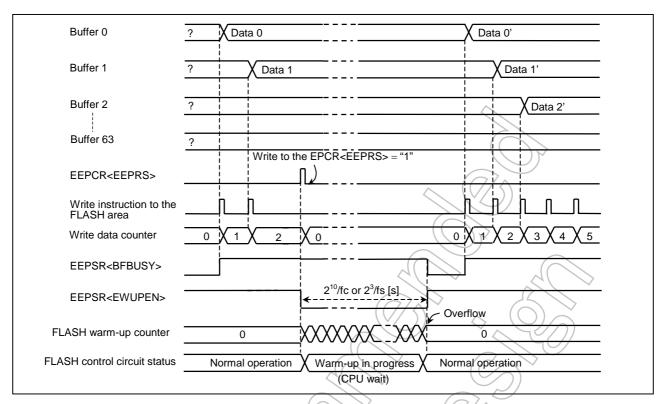

To forcibly stop a write to the FLASH, set the EEPCR<EEPRS> to "1". Setting the EEPCR<EEPRS> to "1" initializes the write data counter of data buffer and forcibly stops a write, and then a warm-up period (CPU wait) for the control circuit of Flash memory is executed. After warm-up period, the EEPSR<BFBUSY> is cleared to "0". The warm-up period is  $2^{10}$ /fc (SYSCK = "0") or  $2^{3}$ /fs (SYSCK = "1"). After this, if writing to FLASH starts again, data is stored as the first byte of the temporary data buffer and sets the EEPSR<BFBUSY> to "1". Therefore, it is necessary to write 64 bytes data to the temporary data buffer.

After 1 to 63 bytes are saved to the temporary data buffer, if the EEPCR<EEPRS> is set to "1" the specified page of flash is not written. (It keeps previous data.)

- Note 1: After 64 bytes are written to the temporary data buffer, the setting the EEPCR<EEPRS> to "1" may cause the writing the page of FLASH to an unexpected value

- Note 2: The EEPCR<EEPRS> can be rewritten only when a program is being executed in the RAM area. In the FLASH area, executing a write instruction to the EEPCR<EEPRS> does not affect its setting.

- Note 3: During the warm-up period for Flash memory (CPU wait), the peripheral circuits continue operating, but the CPU stays at a halt until the warm-up is finished. Even if an interrupt latch is set to "1" by generating of interrupt request, an interrupt sequence doesn't start till the end of warm up. If interrupts occur during a warm-up period with IMF = "1", the interrupt sequence which depends on interrupt priority will start after warm-up period.

- Note 4: When the EEPCR<EEPRS> is set to "1" with EEPSR<BFBUSY> = "0", a warm-up period is not executed.

- Note 5: If executed a write or read instruction to the Flash area immediately after setting EEPCR<EEPRS>, insert one or more machine cycle instructions after setting EEPCR<EEPRS>.

Example: Reads the Flash memory data immediately after setting EEPCR<EEPRS> to "1".

LD HL,8000H

LD (EEPCR),3FH ; Set EEPCR<EEPRS> to "1".

NOP ; NOP

(Do not execute read instruction immediately after setting

EEPCR<EEPRS>.)

A,(HL) ; Reads the data of address 8000H.

(Read instruction to the Flash memory.)

Note 6: This function can be used in serial PROM mode. In this mode, the EEPCR<EEPRS> should be always set to "0".

86FM25-13 2004-03-01

Figure 1.2.4 Write Data Counter Initialization and Write Forcible Stop

### 1.2.5 Power Control for the FLASH Control Circuit

For the FLASH product, it is possible to turn off the power for FLASH control circuit (such as a regulator) to suppress power consumption if the FLASH area is not accessed. For the TMP86CM25A, the register setting and the CPU wait functions behave in the same manner as for the FLASH product to maintain compatibility; however, power consumption is not suppressed.

The EEPCR<MNPWDW> and EEPCR<ATPWDW> are used to control the power for the FLASH control circuit. If the power for the FLASH control circuit is turned off according to the setting of these registers, starting to use the circuits again needs to allow warm-up time for the power supply.

Table 1.2.1 Power Supply Warm-up Time (CPU wait) for the FLASH Control Circuit

| NORMAL1/2               | SLOW1/2                | STOP Mode (when EEF                         | PCR <mnpwdw> = "1")</mnpwdw>               |

|-------------------------|------------------------|---------------------------------------------|--------------------------------------------|

| IDLE0/1/2 Mode          | SLEEP0/1/2 Mode        | To Return to a NORMAL Mode                  | To Return to a SLOW Mode                   |

| 2 <sup>10</sup> /fc [s] | 2 <sup>3</sup> /fs [s] | STOP warm-up time + 2 <sup>10</sup> /fc [s] | STOP warm-up time + 2 <sup>3</sup> /fs [s] |

| (64 μs at 16 MHz)       | (244 μs at 32.768 kHz) | STOF Warming time + 2 /IC[S]                | 310F waini-up tillie + 27is [s]            |

### 1.2.5.1 Software-based Power Control for the FLASH Control Circuit (EEPCR<MNPWDW>)

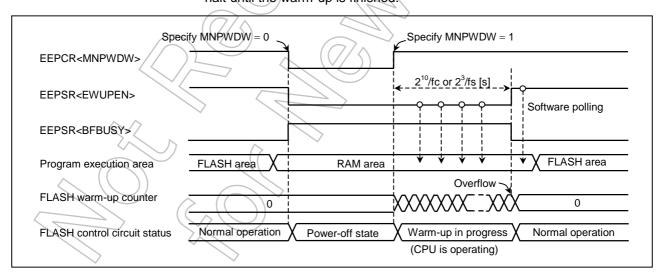

The EEPCR<MNPWDW> is a software-based power control bit for the FLASH control circuit. When a program is being executed in the RAM area, setting this bit enables software-based power control. Clearing the EEPCR<MNPWDW> to "0" immediately turns off the power for the FLASH control circuit. Once the EEPCR<MNPWDW> is switched from "0" to "1", before attempting a read or fetch from the FLASH area, it is necessary to insert a warm-up period by software until the power supply is stabilized. In this case, because the CPU wait is not executed, any other instructions except accessing to Flash (write or read) are available. When MNPWDW is changed from "0" to "1", EWUPEN becomes "1" after taking 210/fc [s] (SYSCK = "0") or 23/fs [s] (SYSCK = "1"). Usually software-based polling should be performed until the EEPSR<EWUPEN> becomes "1". An example of setting is given below.

### (1) Example of controlling the EEPCR<MNPWDW>

- Transfer a program for controlling the EEPCR<MNPWDW> to the RAM area.

- 2. Release an address trap in the RAM area (set up the WDTCR1 and WDTCR2 registers).

- 3. Jump to the control program transferred to the RAM area.

- 4. Clear the interrupt master enable flag (IMF  $\leftarrow$  "0").

- 5. Clear the binary counter if the watchdog timer is in use.

- 6. To turn off the power for the FLASH control circuit, clear the EEPCR<MNPWDW> to "0".

- 7. Perform CPU processing as required.

- 8. To access the FLASH area again, set the EEPCR<MNPWDW> to "1".

- 9. Keep program polling until the EEPSR<EWUPEN> becomes "1". (Upon completion of an FLASH warm-up, the EEPSR<EWUPEN> is set to "1". It takes 2<sup>10</sup>/fc (SYSCK = "0") or 2<sup>3</sup>/fs (SYSCK = "1") until EWUPEN becomes "1".)

This procedure enables the FLASH area to be accessed.

86FM25-15 2004-03-01

If the EEPCR<MNPWDW> is "1", entering a STOP mode forcibly turns off the power for the FLASH control circuit. When the STOP mode is released, a STOP mode oscillation warm-up is carried out, and then the CPU wait period (warm-up for stabilizing of FLASH power supply circuit) is automatically performed. If the EEPCR<MNPWDW> is "0", entering/exiting the STOP mode keeps the power for the FLASH control circuit turned off.

- Note 1: If the EEPSR<EWUPEN> is "0", do not access (Fetch, read, or write) the FLASH area. Executing a read instruction or fetch to the FLASH area causes FFH to be read. Fetching FFH results in a software interrupt occurring. For the TMP86CM25A, however, masked ROM data is always read regardless of the state of the EEPSR<EWUPEN>.

- Note 2: To clear the EEPCR<MNPWDW> to "0", clear the interrupt master enable flag (IMF) to "0" in advance to disable an interrupt. After that, do not set IMF to "1" during EEPSR<EWUPEN> = "0".

- Note 3: If the EEPCR<MNPWDW> is "0", generating a nonmaskable interrupt automatically rewrites the MNPWDW to "1" to warm-up the FLASH control circuit (CPU wait). That time, the peripheral circuits continue operating, but the CPU stays at a halt until the warm-up is finished.

- Note 4: The EEPCR<MNPWDW> can be rewritten only when a program is being executed in the RAM area. In the FLASH area, executing a write instruction to the EEPCR<MNPWDW> does not affect its setting.

- Note 5: If a watchdog timer is used as an interrupt request, clear the binary counter for the watchdog timer just before MNPWDW is changed from "1" to "0".

- Note 6: During the warm-up period with a software polling of EEPSR<EWUPEN>, if a nonmaskable interrupt occurs during an FLASH warm-up, the CPU stays at a halt until the warm-up is finished.

Figure 1.2.5 Software-based Power Control for the FLASH Control Circuit (EEPCR<MNPWDW>)

Example: Performing software-based power control for the FLASH control circuit sRAMAREA: DI Disable an interrupt (IMF  $\leftarrow$  "0"). LD (WDTCR2),4Eh Clear the binary counter if the watchdog timer CLR (EEPCR).0 Clear the EEPCR<MNPWDW> to "0". Set the EEPCR<MNPWDW> to "1". sLOOP1: SET (EEPCR).0 **TEST** (EEPSR).1 Monitor the EEPSR<EWUPEN> register. JRS T,sLOOP1 Jump to sLOOP1 if EEPSR<EWUPEN> = "0". JΡ MAIN Jump to the FLASH area.

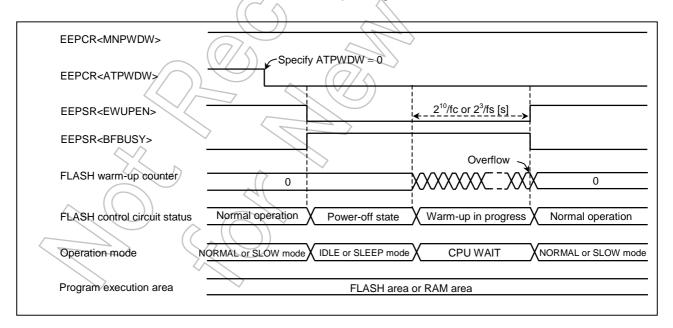

#### 1.2.5.2 Automatic Power Control for the FLASH Control Circuit (EEPCR<ATPWDW>)

The EEPCR<ATPWDW> is an automatic power control bit for the FLASH control circuit. It is possible to suppress power consumption by automatically shutting down the power for the FLASH control circuit when an operation mode is changed to IDLE0/1/2 and SLEEP0/1/2 modes. This bit can be specified regardless of the area in which a program is being executed.

After the EEPCR<ATPWDW> is cleared to "0", entering an operation mode (IDLE0/1/2 or SLEEP0/1/2) where the CPU is at a halt automatically turns off the power for the FLASH control circuit. Once the operation mode is released, the warm-up time (CPU wait) is automatically counted to resume normal processing. The CPU wait period is either  $2^{10}$ /fc (SYSCK = "0") or  $2^{3}$ /fs (SYSCK = "1"). If the EEPCR<ATPWDW> is "1", releasing the operation mode does not cause the CPU wait.

If EEPCR<MNPWDW> = "1", executing a STOP mode forcibly turns off the power for the FLASH control circuit regardless of the setting of the EEPCR<ATPWDW>. When the STOP mode is released, a STOP mode oscillation warm-up is carried out, and then an FLASH control circuit warm-up (CPU wait) is automatically performed. If the EEPCR<MNPWDW> is "0", entering/exiting a STOP mode allows the power for the FLASH control circuit to be kept turned off.

- Note 1: The EEPCR<ATPWDW> functions only if the EEPCR<MNPWDW> is "1". If the EEPCR<MNPWDW> is "0", the power for the FLASH control circuit is kept turned off when an operation mode is executed or released.

- Note 2: During an FLASH warm-up (CPU wait), the peripheral circuits continue operating, but the CPU stays at a halt. Even if an interrupt latch is set under this condition, no interrupt process occurs until the CPU wait is completed. If the IMF is "1" when the interrupt latch is set, interrupt process takes place according to the interrupt priority after the CPU has started operating.

Figure 1.2.6 Automatic Power Control for the FLASH Control Circuit (EEPCR<ATPWDW>)

### 1.2.6 Accessing to the FLASH Memory

During the writing to the FLASH area, neither a read nor fetch can be performed for the 8000H to FFFFH area. Therefore, to write the FLASH area, the program should be executed in the BOOTROM or RAM area. Basically, to write the FLASH area, the program can be executed in BOOTROM area by using the FLASH writing mode of the Serial PROM mode, but it can be also executed any user program in RAM area by using the RAM loader mode of the Serial PROM mode.

Explanation here is made of only the method of FLASH programming in RAM area. For detail about each operation mode of the Serial PROM mode, refer to 2.1 "Serial PROM Mode".

Although the writing to FLASH is executed on page-by-page, the reading from FLASH is executed on byte-by-byte.

If a nonmaskable interrupt occurs during a write to the FLASH (EEPSR<BFBUSY> = "1"), the WINT is set to "1" and the writing is discontinued, and then the warm-up period for control circuit of Flash memory is executed (The write data counter is also initialized). If WINT = "1" is detected in the nonmaskable interrupt service routine, a write is not completed successfully. So, it is necessary to try a write again. The warm-up period is  $2^{10}$ /fc (SYSCK = "0") or  $2^3$ /fs (SYSCK = "1"). After 1 to 63 bytes are saved to the temporary data buffer, if an interrupt generates, the specified page of FLASH is not written. (It keeps previous data.)

- Note 1: Writing to the FLASH area is enabled only in serial PROM mode. For details of serial PROM mode, refer to 2.1 "Serial PROM Mode".

- Note 2: After 64 bytes are written to the temporary data buffer, the generating of an interrupt may cause the writing the page of FLASH to an unexpected value.

- Note 3: During the warm-up period for Flash memory (CPU wait), the peripheral circuits continue operating, but the CPU stays at a halt until the warm-up is finished. Even if an interrupt latch is set to "1" by generating of interrupt request, an interrupt sequence doesn't start till the end of warm-up. If interrupts occur during a warm-up period with IMF = "1", the interrupt sequence which depends on interrupt priority will start after warm-up period.

- Note 4: When write the data to Flash memory from RAM area, disable all the non-maskable interrupt by clearing interrupt master enable flag (IMF) to "0" beforehand.

### 1.2.6.1 FLASH Writing Program in the RAM Area

To develop the program in RAM, the write control program should be loaded from external device by using RAM loader mode in Serial PROM mode. Given below is an example of writing the control program in the RAM area.

- (1) Example of writing program in the RAM area

- 1. Monitor the EEPSR<EWUPEN>. If it is "0", set the EEPCR<MNPWDW> to "1", and then start and keep polling until the EEPSR<EWUPEN> becomes "1".

- 2. Clear the interrupt master enable flag ( $\widehat{IMF} \leftarrow "0"$ ).

- 3. Set the EEPCR with "3BH" (to enable a write to the FLASH).

- 4. Execute a write instruction for 64 bytes to the FLASH area.

- 5. Start and keep polling by software until the EEPSR<BFBUSY> becomes "0". (Upon completion of an erase and write to the FLASH cells, the EEPSR<BFBUSY> is set to "1". For the FLASH product, the required write time is typically 4 ms. For the emulation chip, it is the value specified in the EEPEVA register.)

- 6. Set the EEPCR with "CBH" (to disable a write to the FLASH).

Note: See (2), "Method of specifying an address for a write to the FLASH", for a description about the FLASH address to be specified at step 4 above.

86FM25-20 2004-03-01

### (2) Method of specifying an address for a write to the FLASH

The FLASH page to be written is specified by the 10 high-order bits of the address of the first byte data. The first byte data is stored at the first address of the temporary data buffer. If the data to be written is, for example, 8040H, page 1 is selected, and the data is stored at the first address of the temporary data buffer. Even if the 6 low-order bits of the specified address is not 000000B, the first byte data is always stored at the first address of the data buffer.

Any address can be specified as the second and subsequent address within FLASH area (8000H to FFFFH). The write data bytes are stored in the temporary data buffer in the sequence they are written, regardless of what address is specified. Usually, the address that is the same as the first byte is specified for the second and subsequent address. A 16-bit transfer instruction (LDW) can also be used for writing to the temporary data buffer.

```

Example: Data bytes 00H to 3FH are written to page 1.

(Figure 1.2.9 shows the example of data buffer and pages.)

DI

Disable an interrupt (IMF \leftarrow "0").

LD

C,00H

LD

HL,EEPCR

Specify the EEPCR register address.

LD

IX,8040H

Specify a write address.

LD

(HL),3BH

Specify the EEPCR.

sLOOP1:

(IX),C

LD

Store data to the temporary data buffer.

(A write page is selected when the first

byte is written.)

INC

C = C + 1.

CMP

C,40H

Jump to sLOOP1 if C is not 40H.

NZ,sLOOP1

JR

sLOOP2:

TEST

(EEPSR).0

JRS

F,sLOOP2

Jump to sLOOP2 if EEPSR<BFBUSY> =

LĎ

(HL),0CBH

Specify the EEPCR.

```

Note: If the BFBUSY is "1", executing a read instruction or fetch to the FLASH area causes "FFH" to be read. Fetching "FFH" results in a software interrupt occurring.

86FM25-21 2004-03-01

|         | 0   | 1   | 2      | 3   | 4      | 5   | 6   | 7      | 8         | 9      | Α   | В   | С   | D   | Е      | F        |                   |

|---------|-----|-----|--------|-----|--------|-----|-----|--------|-----------|--------|-----|-----|-----|-----|--------|----------|-------------------|

|         | 00H | 01H | 02H    | 03H | 04H    | 05H | 06H | 07H    | 08H       | 09H    | 0AH | 0BH | 0CH | 0DH | 0EH    | 0FH      | <b> </b>          |

|         | 10H | 11H | 12H    | 13H | 14H    | 15H | 16H | Temp   |           | 19H    |     |     |     |     |        |          |                   |

|         | 1   |     |        |     |        |     | 26H | data l | ouffer    | 29H    | 2AH | 2BH | 2CH | 2DH | 2EH    | 2FH      | ( )               |

|         | 30H | 31H | 32H    | 33H | 34H    | 35H | 36H | 37H    | 38H       | 39H    | ЗАН | 3BH | 3СН | 3DH | 3EH    | 3FH      | ] ]               |

|         |     |     | _      |     | _      |     |     | _      | _         | _      | _   |     | _   | _   | _      | _        | <del>-</del><br>- |

| Address | 0   | 1   | 2      | 3   | 4      | 5   | 6   | 7      | 8         | 9      | Α   | В   | \C\ | D   | E      | F        |                   |

| 8030H   |     |     | ;<br>/ |     | ;<br>! |     |     |        |           | ;<br>  | L   |     |     |     | ;<br>! | <u>.</u> |                   |

| 8040H   | 00H | 01H | 02H    | 03H | 04H    | 05H | 06H | 07H    | 08H       | 09H    | 0AH | 0BH | осн | ODH | 0EH    | 0FH      | $\Gamma$          |

| 8050H   | 10H | 11H | 12H    | 13H | 14H    | 15H | 16H | Pag    | i<br>ie 1 | 19H    | 1AH | 1BH | 1CH | 1DH | 1EH    | 1FH      |                   |

| 8060H   | 20H | 21H | 22H    | 23H | 24H    | 25H | 26H |        | ·         | 29H    | 2AH | 2BH | 2CH | 2DH | 2EH    | 2FH      | ] [               |

| 8070H   | 30H | 31H | 32H    | 33H | 34H    | 35H | 36H | 37H    | 38H       | 39H    | 3AH | звн | зсн | 3DH | 3EH    | 3FH      | ]]                |

|         |     |     | I<br>I |     | I<br>I |     | I   |        |           | I<br>I | ((  |     |     |     | I<br>I | I<br>I   |                   |

Figure 1.2.7 Data Buffer and Write Page (Example)

Figure 1.2.8 Write to the FLASH Area

Unit

M

MHz

### 2.1 Serial PROM Mode

### 2.1.1 Outline

The TMP86FM25 has a 2-Kbyte BOOT-ROM for programming to FLASH memory. This BOOT-ROM is a mask ROM that contains a program to write the FLASH memory on-board. The BOOT-ROM is available in a serial PROM mode and it is controlled by P11 pin, BOOT (P15) pin, TEST pin and  $\overline{\text{RESET}}$  pin, and is communicated via TXD (P16) and RXD (P15) pins. There are four operation modes in a serial PROM mode: FLASH writing mode, RAM loader mode, FLASH memory SUM output mode and Product discrimination code output mode. Operating area of serial PROM mode differs from that of MCU mode. The operating area of serial PROM mode shows in Table 2.1.1.

Parameter Min Max

Operating voltage 2.7 3.6

Table 2.1.1 Operating Area of Serial PROM Mode

Note: Even though included in above operating area, part of frequency can not be supported in serial PROM mode. For details, refer to Table 2.1.6.

$25 \pm 5$

### 2.1.2 Memory Mapping

High frequency (Note)

Temperature

The BOOT-ROM is mapped in address 3800H to 3FFFH. The Figure 2.1.1 shows a memory mapping.

Figure 2.1.1 Memory Address Maps

86FM25-24 2004-03-01

### 2.1.3 Serial PROM Mode Setting

### 2.1.3.1 Serial PROM Mode Control Pins

To execute on-board programming, start the TMP86FM25 in serial PROM mode. Setting of a serial PROM mode is shown in Table 2.1.2.

Table 2.1.2 Serial PROM Mode Setting

| Pin                | Setting |  |  |  |  |  |

|--------------------|---------|--|--|--|--|--|

| BOOT/RXD pin (P15) | High    |  |  |  |  |  |

| P11 pin            | Low     |  |  |  |  |  |

| RESET , TESTpin    |         |  |  |  |  |  |

#### 2.1.3.2 Pin Function

In the serial PROM mode, TXD (P16) and RXD (P15) pins are used as a serial interface pin.

Table 2.1.3 Pin Function in the Serial PROM Mode

|                         |                         | Tie Till Talletiell III tile Gellal I New Wede      |            |

|-------------------------|-------------------------|-----------------------------------------------------|------------|

| Pin Name                | Input/                  | Function                                            | Pin Name   |

| (Serial PROM mode)      | Output                  |                                                     | (MCU mode) |

| TXD                     | Output                  | Serial data output                                  | P16        |

| RXD/BOOT                | Input                   | Serial PROM mode control/Serial data input (Note 1) | P15        |

| RESET                   | Input                   | Serial PROM mode control                            | RESET      |

| TEST                    | Input                   | Serial PROM mode control                            | TEST       |

| P11                     | Input                   | Serial PROM mode control (Fix to "L" level)         | P11        |

| VDD                     |                         | 2.7 V to 3.6 V                                      |            |

| VSS                     | Power supply            | 0 V                                                 |            |

| VAREF                   |                         | Open or equal with VDD                              |            |

| P10, P12 to P14,<br>P17 |                         |                                                     |            |

| P20 to P22              |                         |                                                     |            |

| P30 to P36              | 1/0                     | Placed in High-Z state during serial PROM mode.     |            |

| P50 to P57              |                         |                                                     |            |

| P60 to P67              |                         |                                                     |            |

| P70 to P77              |                         | $\langle \langle \langle \rangle \rangle \rangle$   |            |

| SEG39 to SEG0           | Output                  |                                                     |            |

| COM4 to COM0            | Output                  | Open                                                |            |

| C0, C1, V4 to V1        | LCD voltage booster pin | Орол                                                |            |

| XIN                     | Input                   | Resonator connecting pins for high-frequency clock. | (Note 2)   |

| XOUT                    | l. (Note 2)             |                                                     |            |

Note 1: When the device is used as on-board writing and other parts are already mounted in place, be careful no to affect these communication control pins.

Note 2: Operating area of high frequency in serial PROM mode is from 2 MHz to 16 MHz.

86FM25-25 2004-03-01

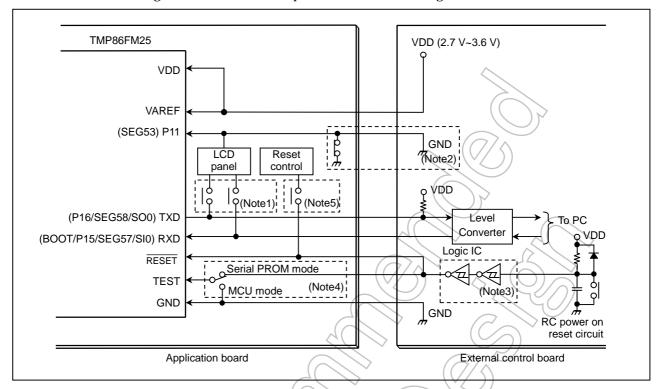

To set a serial PROM mode, connect device pins as shown in Figure 2.1.2.

Figure 2.1.2 Serial PROM Mode Port Setting

### 2.1.3.3 Activating Serial PROM Mode

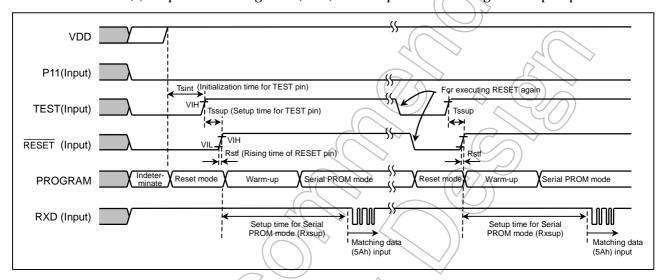

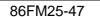

The following is a procedure of setting of serial PROM mode. Figure 2.1.3 shows a serial PROM mode timing.

- (1) Turn on the power to the VDD pin.

- (2) Set the P11 pin, TEST pin and RESET pin to low level.

- (3) Set the BOOT/RXD pin (P15) to high level.

- (4) Wait until the power supply and clock sufficiently stabilize.

- (5) Set the TEST pin from low level to high level.

- (6) Release the  $\overline{RESET}$ . (Set to high level)

- (7) Input a matching data (5AH) to RXD pin after waiting for setup sequence.

Figure 2.1.3 Serial PROM Mode Timing

Table 2.1.4 Serial PROM Mode Timing characteristics

| Parameter                                                        | Cymphol | The Number of | Required Minimum Time |                |  |  |

|------------------------------------------------------------------|---------|---------------|-----------------------|----------------|--|--|

| Palameter                                                        | Symbol  | Clock (fc)    | at fc = 2 MHz         | at fc = 16 MHz |  |  |

| Setup time for TEST pin Rstf > 512 / fc [s]                      | Tssup   | -             | 1 ms                  |                |  |  |

| Rstf < 512 / fc [s]                                              |         | -             | 0 *\                  | lote1          |  |  |

| Initialization time for TEST pin                                 | Tsint   | -             | 1ms                   |                |  |  |

| Time from reset release until acceptance of start bit of RXD pin | RXsup   | 110000        | 55 ms                 | 6.9 ms         |  |  |

Note 1: If Rstf is shorter than 512 / fc[s] due to using CMOS-type reset IC or Logic IC, the TEST pin can input the same pulse as the RESET pin input. (TEST pin can be directly connected to the RESET pin.) However, drive the pins carefully not to affect the pin's input level, as the TEST pin and the RESET pin have pull-down resistor and pull-up resistor built-in.

Note 2: fc; High-frequency clock

86FM25-27 2004-03-01

### 2.1.3.4 Examples of On-board writing

Figure 2.1.4 shows examples of On-board writing.

Figure 2.1.4 Examples of Onboard writing

- Note 1: If capacity for LCD panel and other devices on the application board affect UART communication in Serial PROM mode, disconnect these pins by using a jumper or a switch.

- Note 2: Set the P11 pin to GND. There are two ways. Set P11 pin to GND on the external board, or set it to GND by setting a jumper on the application board.

- Note 3: If input signal has analog delay due to the use of such circuit as RC power on reset circuit, connect both TEST pin and RESET pin to logic ICs (Schmitt input IC such as TC74HC14). In this case, control the pin capacity to require the condition Rstf<512/fc[s].

- Note4: In MCU mode, the TEST pin can be disconnected as it has a pull-down resistor built-in. However, we recommend connecting it to GND level to avoid noise influence.

- Note5: If the RESET control circuit on the application board affects the Serial PROM mode to start, disconnect it by using a jumper, etc.

### 2.1.4 Interface Specifications for UART

The following shows the UART communication format used in serial PROM mode.

Before on-board programming can be executed, the communication format on the external controller side must also be set up in the same way as for this product.

Note that although the default baud rate is 9600 bps, it can be changed to other values as shown in Table 2.1.5. The Table 2.1.6 shows an operating frequency and baud rate in serial PROM mode. Except frequency which is not described in Table 2.1.6 can not use in serial PROM mode.

Baud rate (Default): 9600 bps

Data length: 8 bits Parity addition: None Stop bit length: 1 bit

Table 2.1.5 Baud Rate Modification Data

| Baud rate modification data | 04H   | 05H   | 06H   | 07H   | 0AH   | 18H   | 28H     |

|-----------------------------|-------|-------|-------|-------|-------|-------|---------|

| Baud rate (bps)             | 76800 | 62500 | 57600 | 38400 | 31250 | 19200 | 9600    |

| Saud rato (pps)             | 7000  | 52555 | 7     | >>    |       |       | A And A |

|                             | (~    |       |       |       |       |       |         |

86FM25-29 2004-03-01

|          |                                 | Baud Rate<br>ps) | 768                   | 300   | 625   | 500   | 576   | 600   | 384      | 400   | 312   | 250           | 192   | 200   | 96    | 600   |

|----------|---------------------------------|------------------|-----------------------|-------|-------|-------|-------|-------|----------|-------|-------|---------------|-------|-------|-------|-------|

| (Note 3) | Baud Rate<br>Modification Data  |                  | 04                    | ıН    | 05    | БН    | 06    | ЭН    | 07       | 7H    | O.A   | λН            | 18    | ВН    | 28    | ЗН    |

|          | Reference<br>Frequency<br>(MHz) | Area<br>(MHz)    | Baud<br>Rate<br>(bps) | (%)   | (bps) | (%)   | (bps) | (%)   | (bps)    | (%)   | (bps) | (%)           | (bps) | (%)   | (bps) | (%)   |

| 1        | 2                               | 1.91~2.10        | -                     | ı     | -     | ı     | -     | ı     | -        | -     | -     |               | 1     | ı     | 9615  | +0.16 |

| 2        | 4                               | 3.82~4.19        | -                     | -     | -     | -     | -     | -     | -        | -     | 31250 | 0.00          | 19231 | +0.16 | 9615  | +0.16 |

|          | 4.19                            | 3.82~4.19        |                       |       |       |       | -     | -     | -        | -     | 32734 | +4.75         | 20144 | +4.92 | 10072 | +4.92 |

| 3        | 4.9152                          | 4.70~5.16        | -                     | -     | -     | -     | -     | -     | 38400    | 0.00  | +(    | (/-()         | 19200 | 0.00  | 9600  | 0.00  |

| 3        | 5                               | 4.70~5.16        | -                     | -     | -     | -     | -     | -     | 39063    | +1.73 | /-/   |               | 19531 | +1.73 | 9766  | +1.73 |

| 4        | 6                               | 5.87~6.45        | -                     | -     | -     | -     | -     | -     | -        | -((   | _/    | -             | -     | -     | 9375  | -2.34 |

| 4        | 6.144                           | 5.87~6.45        | -                     | -     | -     | -     | -     | ı     | -        | -/    |       |               | -     | ı     | 9600  | 0.00  |

| 5        | 7.3728                          | 7.05~7.74        | -                     | -     |       | -     | 57600 | 0.00  | - /      |       | )     | -             | 19200 | 0.00  | 9600  | 0.00  |

| 6        | 8                               | 7.64~8.39        | -                     | -     | 62500 | 0.00  | -     | -     | 38462    | +0.16 | 31250 | 0.00          | 19231 | +0.16 | 9615  | +0.16 |

| 7        | 9.8304                          | 9.40~10.32       | 76800                 | 0.00  | -     | -     | -     | -     | 38400    | 0.00  | -     | -             | 19200 | 0.00  | 9600  | 0.00  |

| ,        | 10                              | 9.40~10.32       | 78125                 | +1.73 | -     | -     | -     | - (   | 39063    | +1.73 | - <   | - (           | 19531 | +1.73 | 9766  | +1.73 |

|          | 12                              | 11.75~12.90      | -                     | -     | -     | -     | 57692 | +0.16 | <u> </u> | //-   | 31250 | 0.00          | 18750 | -2.34 | 9375  | -2.34 |

| 8        | 12.288                          | 11.75~12.90      | -                     | ı     | -     | ı     | 59077 | +2.56 | )        | -     | 32000 | +2.40         | 19200 | 0,00  | 9600  | 0.00  |

|          | 12.5                            | 11.75~12.90      | 1                     | ı     | 60096 | -3.85 | 60096 | +4.33 | 7        | -     | 30048 | -3.85         | 19531 | +1.73 | 9766  | +1.73 |

| 9        | 14.7456                         | 14.10~15.48      | -                     | -     | -     | -     | 57600 | 0.00  | 38400    | 0.00  | - (   | $\leq \wedge$ | 19200 | 0.00  | 9600  | 0.00  |

| 10       | 16                              | 15.27~16.77      | 76923                 | +0.16 | 62500 | 0.00  |       | 1-    | 38462    | +0.16 | 31250 | 0.00          | 19231 | +0.16 | 9615  | +0.16 |

Table 2.1.6 Operating Frequency and Baud Rate in Serial PROM Mode

- Note 1: "Reference Frequency" and "Area" show the high-frequency area supported in serial PROM mode. Except the above frequency can not be supported in serial PROM mode even though the high frequency is included in area from 2 MHz to 16 MHz.

- Note 2: The total error of frequency must be kept within +/-3% so that the auto-detection of frequency is executed correctly.

- Note 3: An external controller should transmit a matching data repeatedly till the TMP86FM25 transmit an echo back data. Above number indicates a transmission number of times of matching data till transmission of echo back data.

## 2.1.5 Command

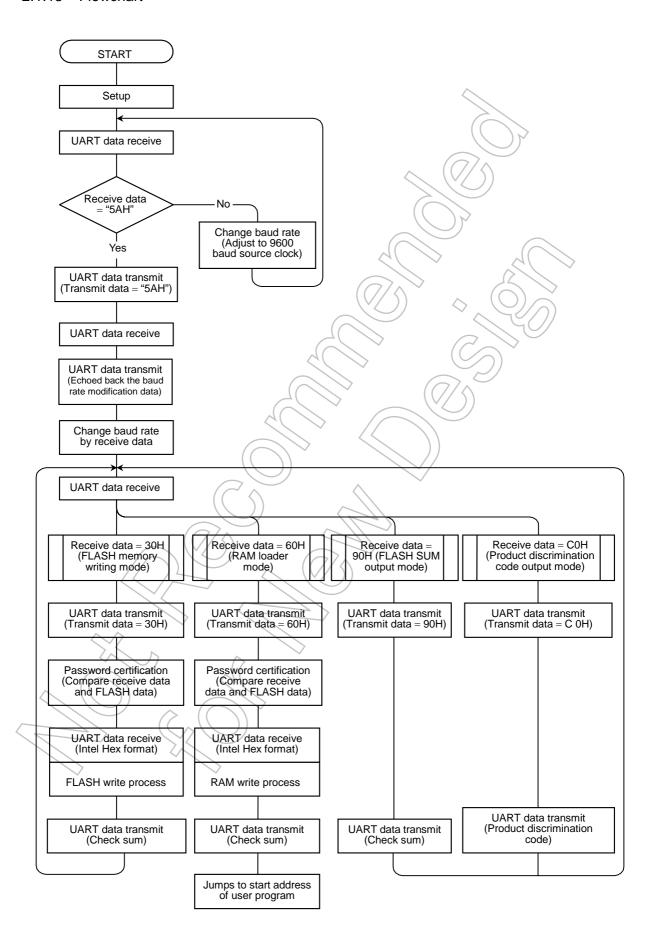

There are five commands in serial PROM mode. After reset release, the TMP86FM25 waits a matching data (5AH).

Table 2.1.7 Command in Serial PROM Mode

| Command Data | Operation Mode                     | Remarks                                                                                                          |

|--------------|------------------------------------|------------------------------------------------------------------------------------------------------------------|

| 5AH          | Setup                              | Matching data. Always start with this command after reset release.                                               |

| 30H          | FLASH memory writing               | Writing to area from 8000H to FFFFH is enable.                                                                   |

| 60H          | RAM loader                         | Writing to area from 0050H to 082FH is enable.                                                                   |

| 90H          | FLASH memory SUM output            | The checksum of entire FLASH area (from 8000H to FFFFH) is output in order of the upper byte and the lower byte. |

| СОН          | Product discrimination code output | Product discrimination code, that is expressed by 13 bytes data, is output.                                      |

## 2.1.6 Operation Mode

There are four operating modes in serial PROM mode: FLASH memory writing mode, RAM loader mode, FLASH memory SUM output mode and Product discrimination code output mode. For details about these modes, refer to (1) FLASH memory writing mode through (4) Product discrimination code output mode.

## (1) FLASH memory writing mode

The data are written to the specified FLASH memory addresses. The controller should send the write data in the Intel Hex format (Binary). For details of writing data format, refer to 2.1.7 "FLASH Memory Writing Data Format")

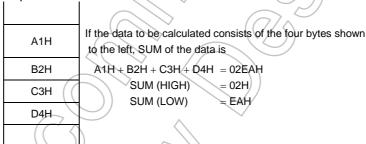

If no errors are encountered till the end record, the SUM of 32 Kbytes of FLASH memory is calculated and the result is returned to the controller.

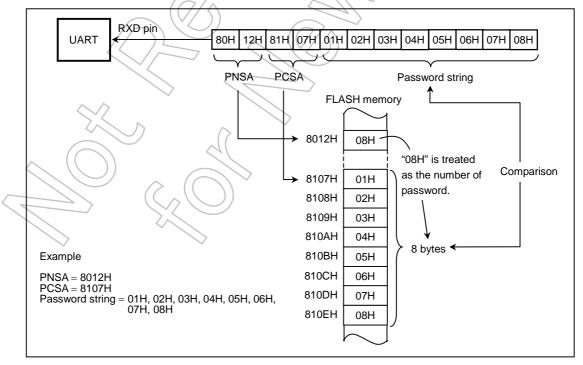

To execute the FLASH memory writing mode, the TMP86FM25 checks the passwords except a blank product. If the passwords did not match, the program is not executed.

#### (2) RAM loader mode

The RAM loader transfers the data into the internal RAM that has been sent from the controller in Intel Hex format. When the transfer has terminated normally, the RAM loader calculates the SUM and sends the result to the controller before it starts executing the user program. After sending of SUM, the program jumps to the start address of RAM in which the first transferred data has been written. This RAM loader function provides the user's own way to control on-board programming.

To execute the RAM loader mode, the TMP86FM25 checks the passwords except a blank product. If the passwords did not match, the program is not executed.

## (3) FLASH memory SUM output mode

The SUM of 32 Kbytes of FLASH memory is calculated and the result is returned to the controller.

The BOOT ROM does not support the reading function of the FLASH memory. Instead, it has this SUM command to use. By reading the SUM, it is possible to manage Revisions of application programs.

## (4) Product discrimination code output mode

The product discrimination code is output as a 13-byte data, that includes the start address and the end address of ROM (In case of TMP86FM25, the start address is 8000H and the end address is FFFFH). Therefore, the controller can recognize the device information by using this function.

## 2.1.6.1 FLASH Writing Mode (Operation command: 30H)

Table 2.1.8 shows FLASH memory writing mode process.

Table 2.1.8 FLASH Writing Mode Process

|             | Number of Bytes<br>Transferred      | Transfer Data from External<br>Controller to TMP86FM25            | Baud Rate                                      | Transfer Data from TMP86FM25 to External Controller                            |

|-------------|-------------------------------------|-------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------|

| BOOT<br>ROM | 1st byte<br>2nd byte                | Matching data (5AH) -                                             | 9600 bps<br>9600 bps                           | - (Baud rate auto set) OK: Echo back data (5AH) Error: Nothing transmitted     |

|             | 3rd byte                            | Baud rate modification data (See Table 2.1.5)                     | 9600 bps                                       | 77                                                                             |

|             | 4th byte                            | _                                                                 | 9600 bps                                       | OK: Echo back data<br>Error: A1H × 3, A3H × 3 , 62H × 3<br>(Note 1)            |

|             | 5th byte<br>6th byte                | Operation command data (30H) -                                    | Changed new baud rate<br>Changed new baud rate | -<br>OK: Echo back data (30H)<br>Error: A1H × 3, A3H × 3 , 63H × 3<br>(Note 1) |

|             | 7th byte<br>8th byte                | Address 15H to 08H in which to store Password count (Note 4)      | Changed new baud rate<br>Changed new baud rate | OK: Nothing transmitted Error: Nothing transmitted                             |

|             | 9th byte<br>10th byte               | Address 07H to 00H in which to store Password count (Note 4)      | Changed new baud rate<br>Changed new baud rate | OK: Nothing transmitted<br>Error: Nothing transmitted                          |

|             | 11th byte<br>12th byte              | Address 15H to 08H in which to start Password comparison (Note 4) | Changed new baud rate<br>Changed new baud rate | OK: Nothing transmitted<br>Error: Nothing transmitted                          |

|             | 13th byte<br>14th byte              | Address 07H to 00H in which to start Password comparison (Note 4) | Changed new baud rate<br>Changed new baud rate | OK: Nothing transmitted     Error: Nothing transmitted                         |

|             | 15th byte<br>:<br>m'th byte         | Password string (Note 5)                                          | Changed new baud rate Changed new baud rate    | OK: Nothing transmitted Error: Nothing transmitted                             |

|             | m'th + 1 byte<br>:<br>n'th - 2 byte | Intel Hex format (Binary)<br>(Note 2)                             | Changed new baud rate                          | _                                                                              |

|             | n'th – 1 byte                       |                                                                   | Changed new baud rate                          | OK: SUM (High) (Note 3) Error: Nothing transmitted                             |

|             | n'th byte                           | -                                                                 | Changed new baud rate                          | OK: SUM (Low) (Note 3) Error: Nothing transmitted                              |

|             | n'th + 1 byte                       | (Wait for the next operation)<br>(Command data)                   | Changed new baud rate                          | _                                                                              |

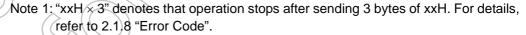

Note 1: "xxH × 3" denotes that operation stops after sending 3 bytes of xxH. For details, refer to 2.1.8 "Error Code".

Note 2: Refer to 2.1.10 "Intel Hex Format (Binary)".

Note 3: Refer to 2.1.9 "Checksum (SUM)".

Note 4: Refer to 2.1.11 "Passwords".

Note 5: If all data of addresses from FFE0H to FFFFH are "00H" or "FFH", the passwords comparison is not executed because the device is considered as blank product. However, it is necessary to specify the password count storage addresses and the password comparison start address even though it is a blank product. If a password error occurs, the UART function of TMP86FM25 stops without returning error code to the controller. Therefore, when a password error occurs, the TMP86FM25 should be reset by RESET pin input.

86FM25-32 2004-03-01

Description of FLASH memory writing mode

- 1. The receive data in the 1st byte is the matching data. When the boot program starts in serial PROM mode, TMP86FM25 (Mentioned as "device" hereafter) waits for the matching data (5AH) to receive. Upon receiving the matching data, it automatically adjusts the UART's initial baud rate to 9,600bps.

- 2. When the device has received the matching data, the device transmits the data "5AH" as an echo back to the controller. If the device can not receive the matching data, the device does not transmit the echo back data and waits for the matching data again with changing baud rate. Therefore, the controller should send the matching data continuously until the device transmits the echo back data. An external controller should transmit a matching data repeatedly till the device transmit an echo back data. The transmission number of times of matching data varies by the frequency of device. For details, refer to Table 2.1.6.

- 3. The receive data in the 3rd byte is the baud rate modification data. The seven kinds of baud rate modification data shown in Table 2.1.5 are available. Even if baud rate changing is no need, be sure to send the initial baud rate data (28H: 9,600 bps).