#### CMOS 8-BIT MICROCONTROLLERS

# TMP91C642AN/TMP91C642AF

#### 1. OUTLINE AND CHARACTERISTICS

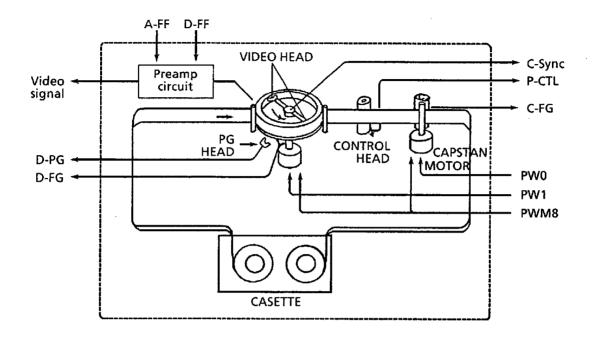

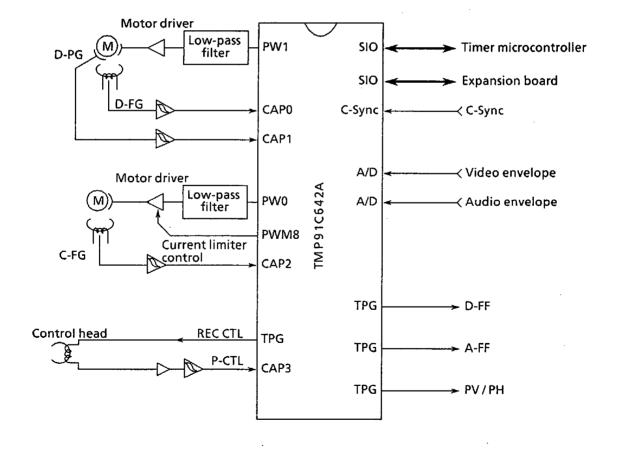

The TMP91C642A is an advanced-function and highly integrated 8-bit microcontroller which is developed for use with software servos.

In addition to I/O ports and other basic components, the TMP91C642A has high-speed high-precision signal measuring circuit, PWM dedicated output, and high-precision timing pulse circuit that simplify control of VCR systems and servo motors.

The TMP91C642AN is a 64-pin shrink DIP product. (SDIP64-P-750)

The TMP91C642AF is a 64-pin flat package product. (QFP64-P-1420A)

The characteristics of the TMP91C642A include:

(1) Efficient instructions

163 basic instructions

Instructions for multiplication, division, 16-bit arithmetic operations, bit manipulation

- (2)Minimum execution time: 400 ns (at 10 MHz oscillation frequency)

- (3)Internal ROM: 16 K bytes

- (4)Internal RAM: 320 bytes

- (5)18-bit time base counter

- Servo input control pins: drum FG / PG, Capstan FG, P-CTL, and EXT

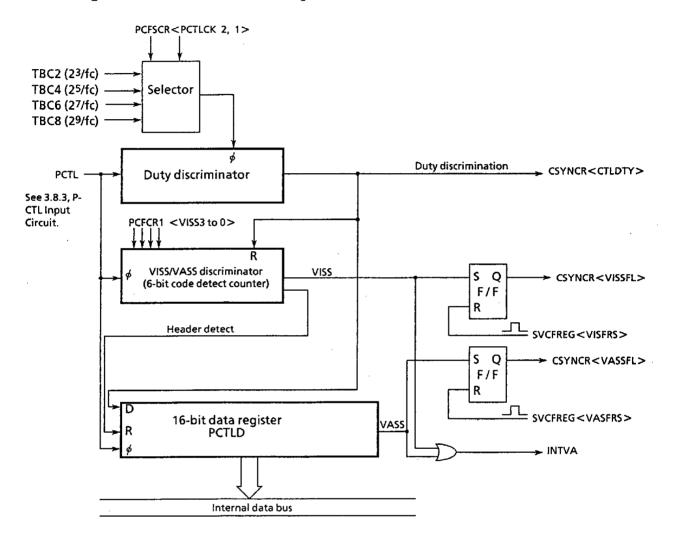

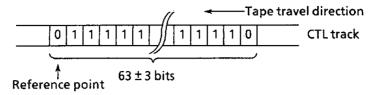

- VISS / VASS detection (7)

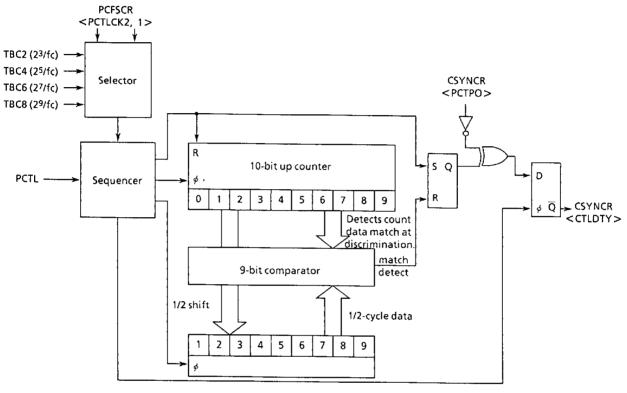

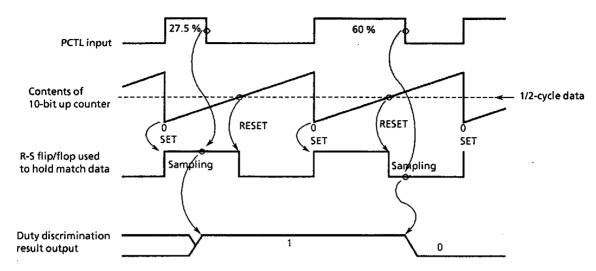

- P-CTL Duty discriminator

- 16-bit VASS data latch

- (8) Composite sync (C-sync) input

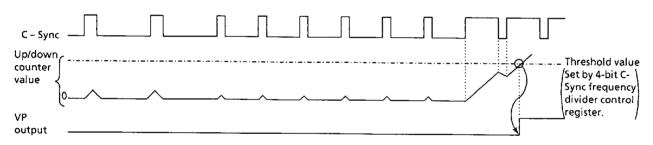

- Vertical sync signal (V-sync) separation

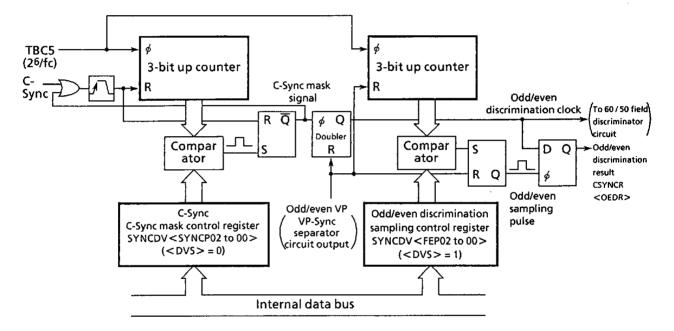

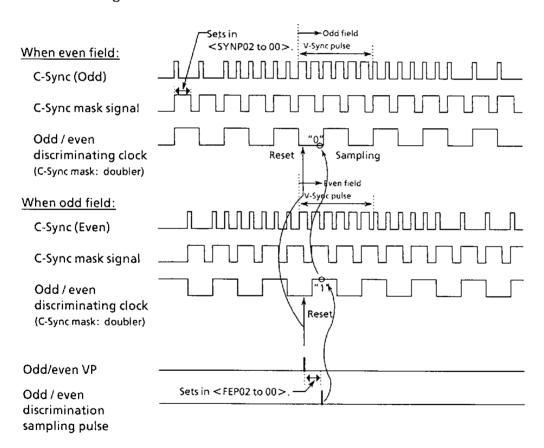

- Odd-even field discriminator

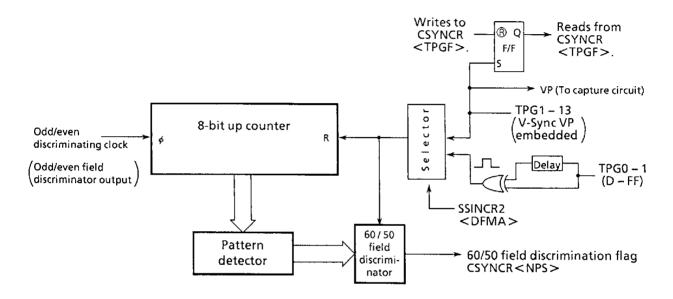

- 60/50 Field discriminator

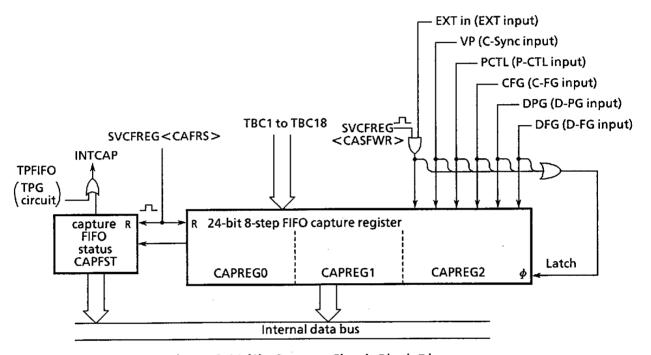

- (9) 24-bit time base counter capture with 8-step FIFO

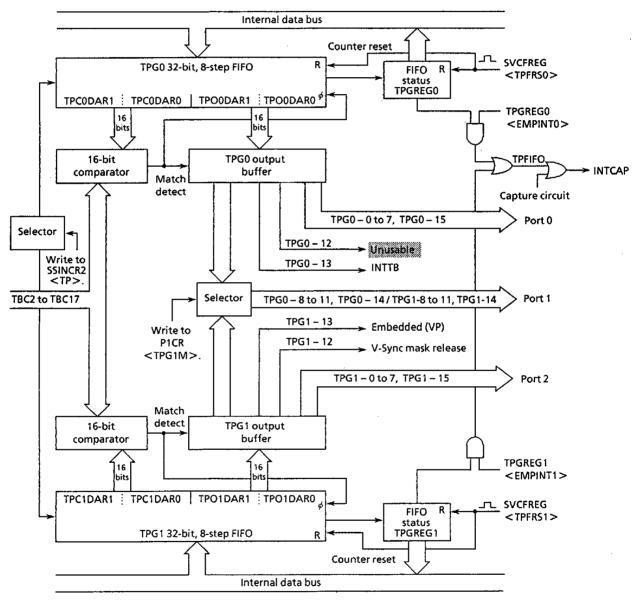

- MAJ.com (10) 32-bit timing pulse generator with 8-step FIFO (16-bit comparate data × 2, 16-bit timing output × 2, maximum 20-bit output MCU90-1

9097249 0043268 365 simultaneously)

- (11) Servo control output pins (drum motor, capstan motor, current limitter control)

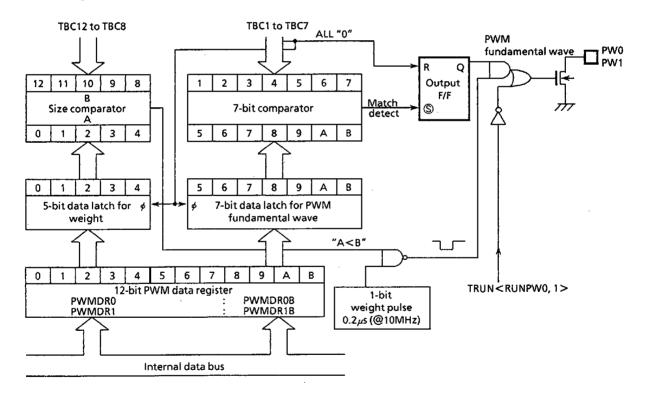

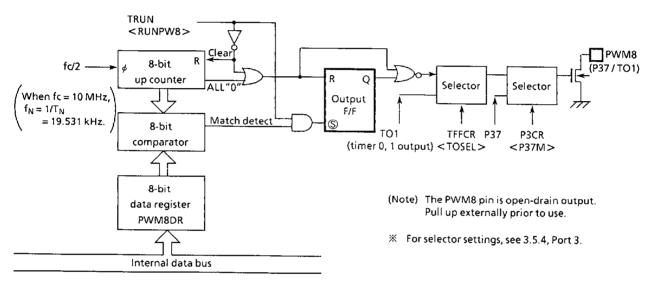

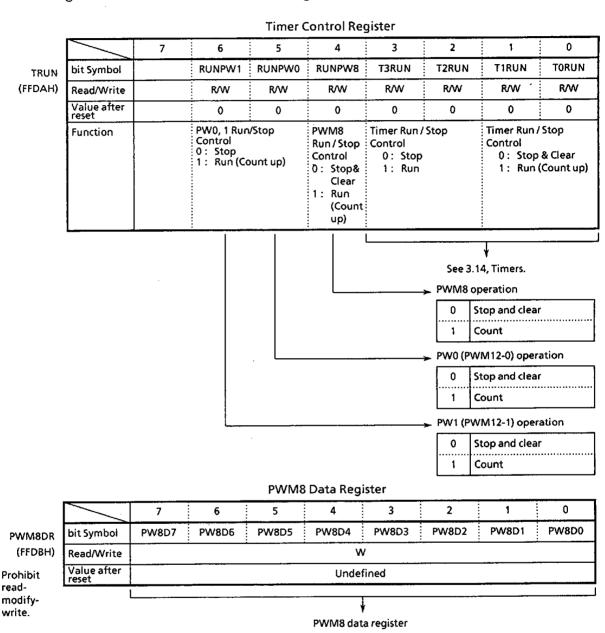

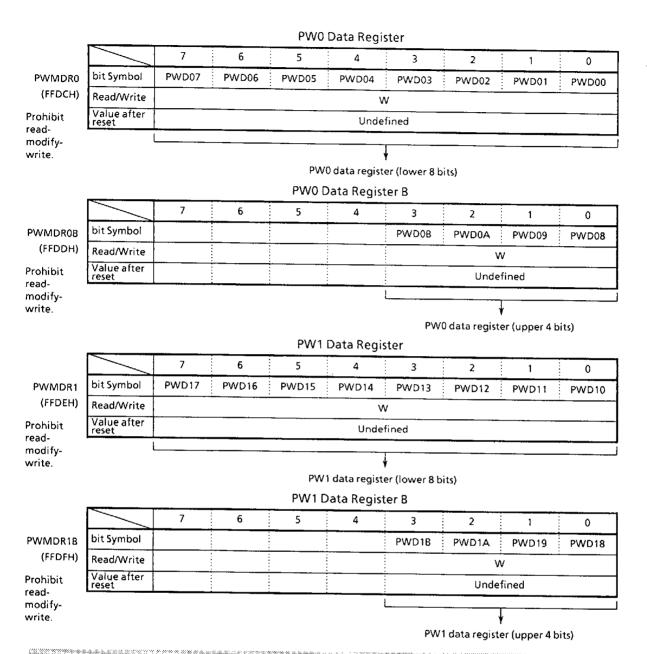

- 12-bit PWM output (2 channels)8-bit PWM output (1 channel)

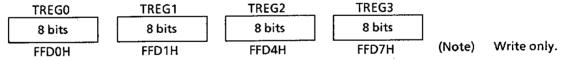

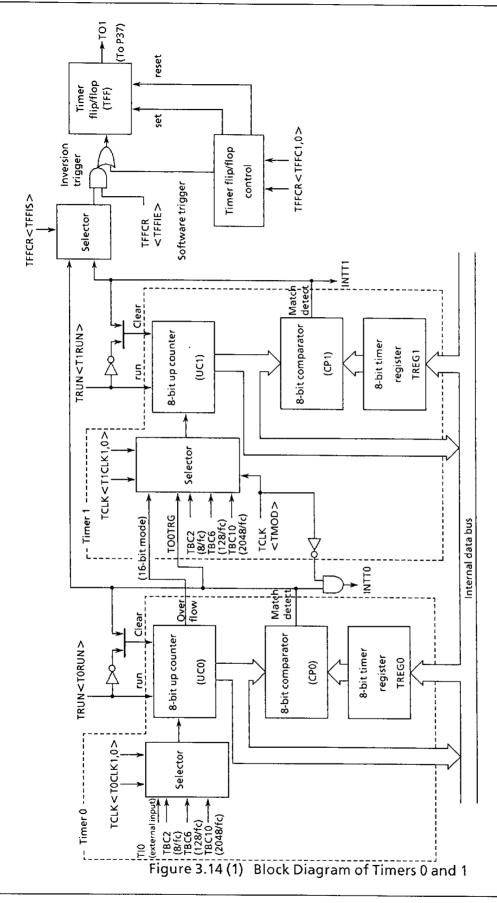

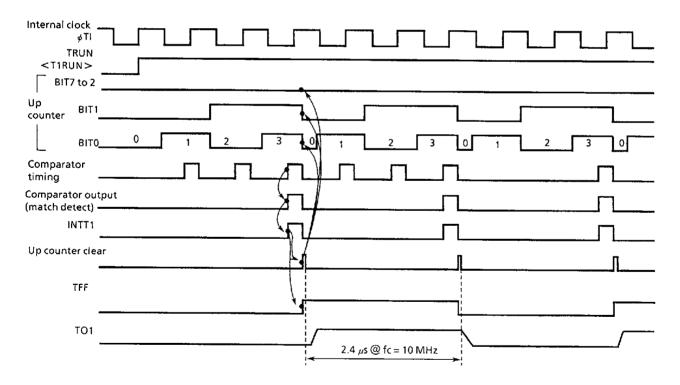

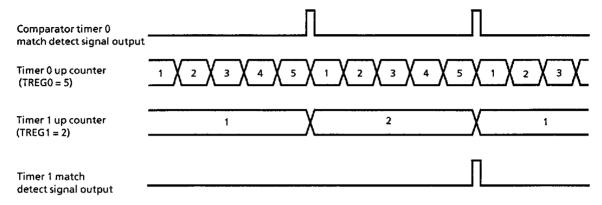

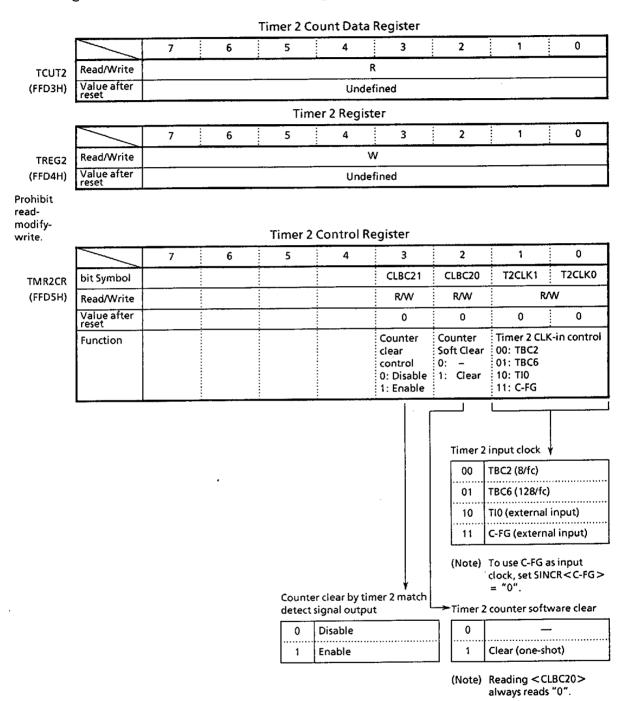

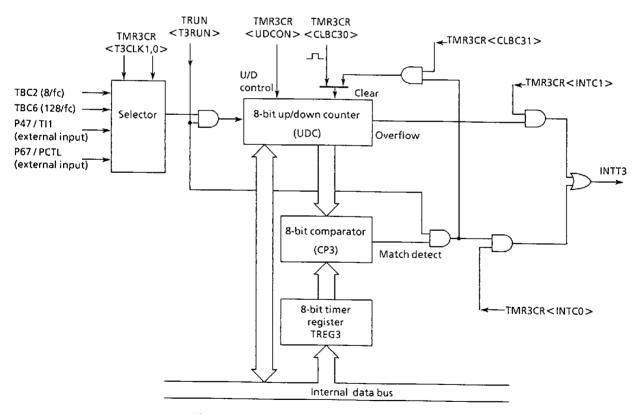

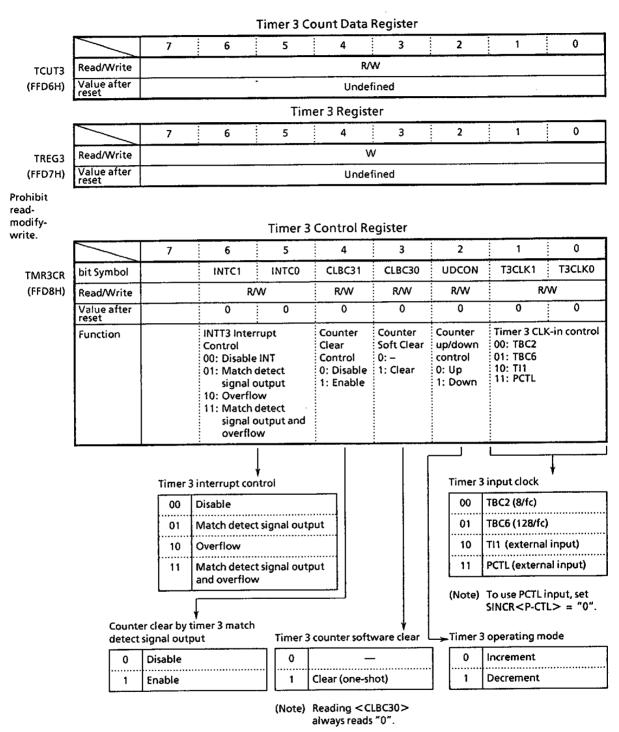

- (12) 8-bit timer / counter (4 channels)

- 1 channel for reloadable timer with up / down mode

- Readable counter data (writable for one channel)

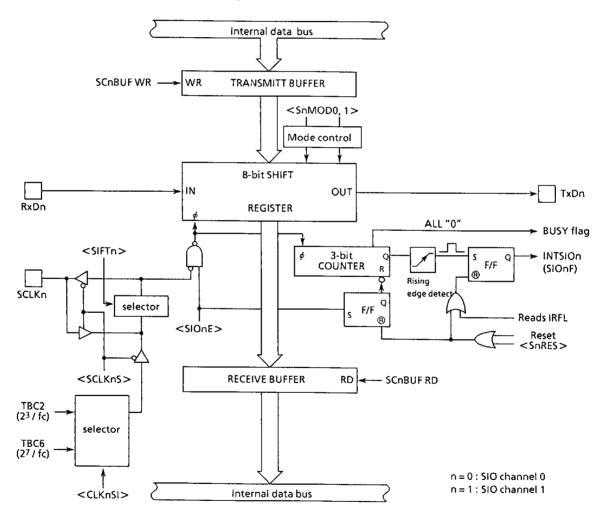

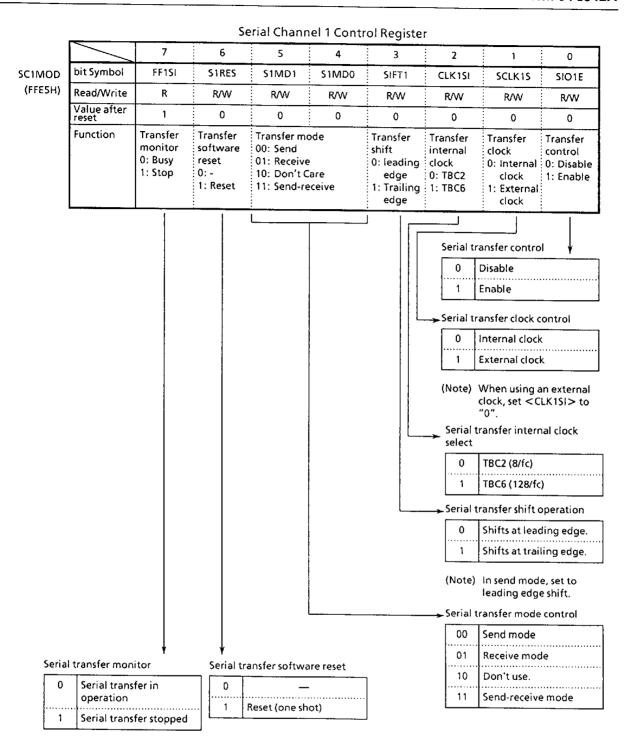

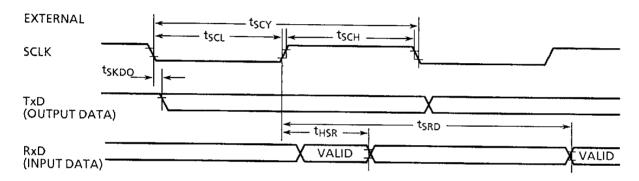

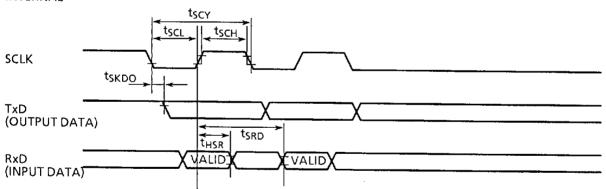

- (13) General-purpose synchronized serial interface (2 channels)

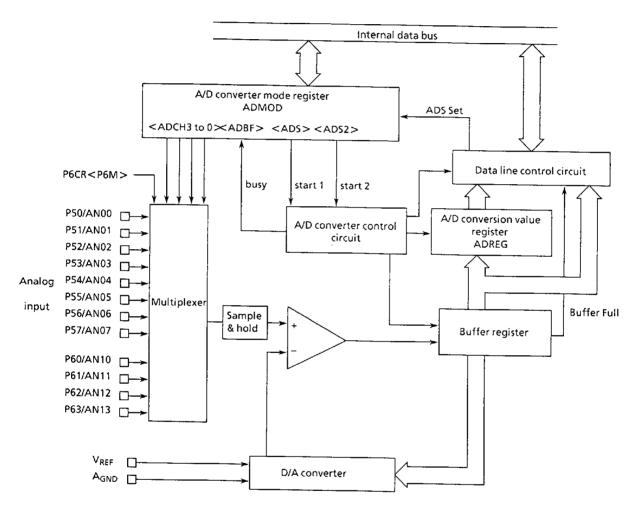

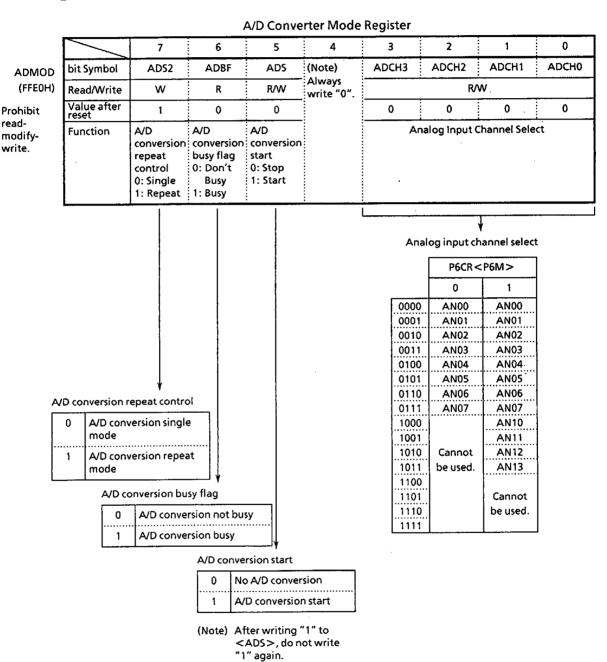

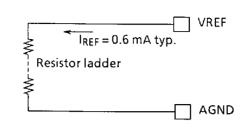

- (14) High-precision 8-bit A/D converter (8 + 4 channels)

- (15) Input / Output ports: 54 pins

- (16) Interrupt function: 10 internal interrupts and 3 external interrupts

- (17) Micro Direct Memory Access (DMA) function (10 channels)

- (18) Watchdog timer

- (19) Standby function (2 HALT mode)

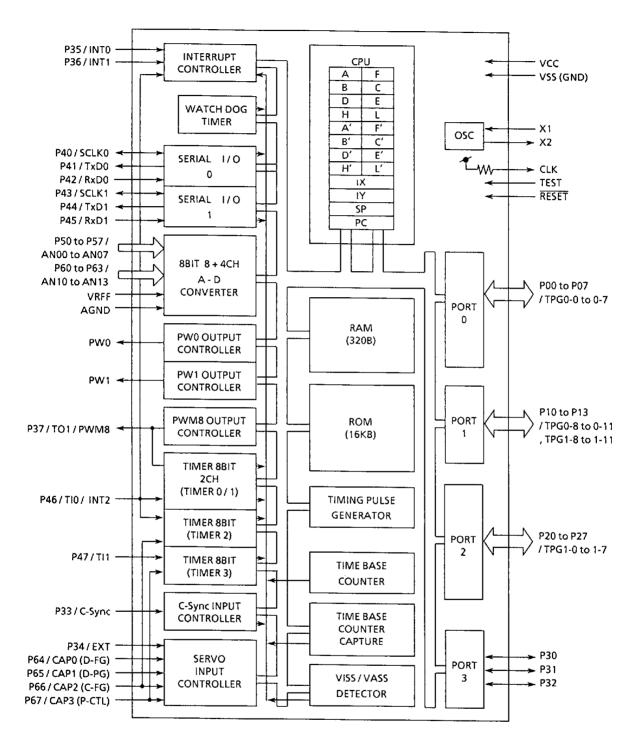

Figure 1 TMP91C642A Block Diagram

MCU90-3

■ 9097249 0043270 Tl3 **■**

TOSHIBA TMP91C642A

## 2. PIN ASSIGNMENT AND FUNCTIONS

The assignment of input/output pins, their names and functions are as shown below.

### 2.1 Pin Assignment

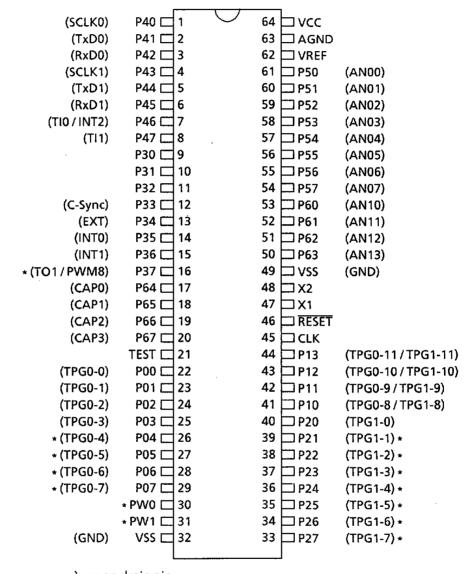

Figure 2.1 (1) shows pin assignment of the TMP91C642AN.

\*) open drain pin

Figure 2.1 (1) Pin Assignment (shrink DIP)

160793

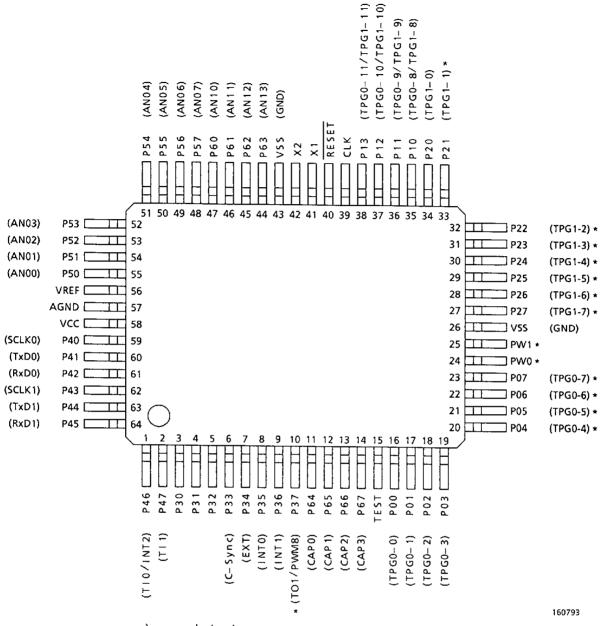

Figure 2.1 (2) shows pin assignment of the TMP91C642AF.

\*) open drain pin

Figure 2.1(2) Pin Assignment (flat package)

MCU90-5

**1097249 0043272 896**

# 2.2 Pin Names and Functions

The name of input / output pins and their functions are summarized in Table 2.2.

Table 2.2 Pin Names and Functions (1/3)

| Pin name                                   | Number<br>of pins | I/O or 3-state                         | Function                                                                                                                                                                          |  |

|--------------------------------------------|-------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P00/TPG0-0                                 | 8                 | I/O, 3-state*                          | Port 0: 8-bit I/O port. I/O specifiable in units of bytes.                                                                                                                        |  |

| to<br>P07 / TPG0-7                         |                   | P04 to P07 are open drain output pins. | Timing pulse generator (TPG) output: Can also be used as TPG0-0 to TPG0-7 output pins. *P00 only can be set to 3-state by internal signals to TPG0-15.                            |  |

| P10/TPG0-8                                 | 4                 | I/O, 3-state*                          | Port 1: 4-bit I/O port. I/O specifiable in units of bits.                                                                                                                         |  |

| /TPG1-8<br>to<br>P13 /TPG0-11<br>/ TPG1-11 |                   |                                        | Timing pulse generator (TPG) output: Can also be used as TPG0-8 to TPG0-11/TPG1-8 to TPG1-11 output pins. *P10 only can be set to 3-state by internal signals to TPG0-14/TPG1-14. |  |

| P20 / TPG1-0                               | 8                 | I/O, 3-state*                          | Port 2: 8-bit I/O port. I/O specifiable in units of bits.                                                                                                                         |  |

| to<br>P27 / TPG1-7                         | i                 | P21 to P27 are open drain output pins. | Timing pulse generator (TPG) output: Can also be used as TPG1-0 to TPG1-7 output pins. *P20 only can be set to 3-state by internal signals to TPG1-15.                            |  |

| P30 to P32                                 | 3                 | 1/0                                    | Port 3: 3-bit I/O port. I/O specifiable in units of bits.                                                                                                                         |  |

| P33                                        | 1                 | 1/0                                    | Port 3: 1-bit I/O port. I/O specifiable.                                                                                                                                          |  |

| / C-Sync                                   |                   |                                        | Composite sync input                                                                                                                                                              |  |

| P34                                        | 1                 | 1/0                                    | Port 3: 1-bit I/O port. I/O specifiable.                                                                                                                                          |  |

| / EXT                                      |                   |                                        | Servo signal trigger input                                                                                                                                                        |  |

| P35                                        | 1                 | Input                                  | Port 3 : 1-bit input port.                                                                                                                                                        |  |

| /INTO                                      |                   | •                                      | Interrupt request pin 0: Level and rising edge are programmable.                                                                                                                  |  |

| P36                                        | 1                 | Input                                  | Port 3: 1-bit input port.                                                                                                                                                         |  |

| /INT1                                      |                   |                                        | Interrupt request pin 1 : at rising edge.                                                                                                                                         |  |

| P37                                        | 1                 | Open drain                             | Port 3: 1-bit output port.                                                                                                                                                        |  |

| / PWM8<br>/ TO1                            |                   | output                                 | Motor control output : PWM8 output                                                                                                                                                |  |

|                                            |                   |                                        | Timers 0 and 1 output : timer 0 and 1 output.                                                                                                                                     |  |

(Note) \*: Only 1 put can be set to the 3-state.

Table 2.2 Pin Names and Functions (2/3)

| Pin name         | Pin<br>name | I/O or 3-state       | Function                                                      |  |

|------------------|-------------|----------------------|---------------------------------------------------------------|--|

| P40/SCLKO,       | 2           | 1/0                  | Port 4: 2-bit I/O port. I/O specifiable in units of bits.     |  |

| P43 / SCLK1      |             |                      | Serial clock I/O 0 and 1                                      |  |

| P41/TxD0,        | 2           | 1/0                  | Port 4: 2-bit I/O port. I/O specifiable in units of bits.     |  |

| P44 / TxD1       |             |                      | Serial send data 0 and 1                                      |  |

| P42 / RxD0,      | 2           | 1/0                  | Port 4: 2-bit I/O port. I/O specifiable in units of bits.     |  |

| P45 / RxD1       |             |                      | Serial receive data 0 and 1                                   |  |

| P46              | 1           | 1/0                  | Port 4: 1-bit I/O port. I/O specifiable.                      |  |

| /TI0<br>/INT2    |             |                      | Timer 0/timer 2 count input                                   |  |

|                  |             |                      | Interrupt request pin 2 : at rising edge                      |  |

| P47              | 1           | 1/0                  | Port 4 : 1-bit I/O port. I/O specifiable.                     |  |

| /TI1             |             | -                    | Timer 3 count input                                           |  |

| P50 / AN00       | 8           | Input                | Port 5: 8-bit input port. I/O specifiable.                    |  |

| to<br>P57 / AN07 |             |                      | Analog input 0 : 8 analog inputs to A/D converter             |  |

| P60 / AN10       | 4           | 1/0                  | Port 6: 4-bit I/O port. I/O specifiable in units of bits.     |  |

| to<br>P63 / AN13 |             |                      | Analog input 1 : 4 analog inputs to A/D converter             |  |

| P64/CAP0         | 4           | Input                | Port 6 : 4-bit input port.                                    |  |

| to<br>P67/CAP3   |             |                      | Servo signal trigger input                                    |  |

| PW0              | 1           | Open drain<br>output | Motor control output : PWM0 output                            |  |

| PW1              | 1           | Open drain<br>output | Motor control output : PWM1 output                            |  |

| VREF             | 1           | -                    | A/D converter reference voltage input                         |  |

| AGND             | 1           | _                    | Grauond pin for A/D converter                                 |  |

| CLK              | 1           | -                    | Pulled up internally<br>(Do not connect an external circuit.) |  |

Table 2.2 Pin Names and Functions (3/3)

| Pin name  | Number<br>of pins | I/O or 3-state | Function                                                       |  |

|-----------|-------------------|----------------|----------------------------------------------------------------|--|

| TEST      | 1                 | -              | Test pin (normally pulled up)                                  |  |

| RESET     | 1                 | Input          | Reset: Initializes the TMP91C642A. (Built-in pull-up registor) |  |

| X1/X2     | 2                 | I/O            | Crystal oscillator connector pin                               |  |

| VSS (GND) | 2                 | _              | GND pin (0 V)                                                  |  |

| vcc       | 1                 | . –            | Power supply pin ( + 5 V)                                      |  |

## 3. OPERATION

This chapter covers the functions and basic operations of the TMP91C642A by blocks.

#### 3.1 CPU

TMP91C642A includes a high-performance 8-bit CPU. For the function of the CPU, see the previous chapter "TLCS-90 CPU".

This chapter explains exclusively the functions of the CPU of TMP91C642A which are not discribed in the chapter "TLCS-90 CPU".

#### 3.1.1 Reset

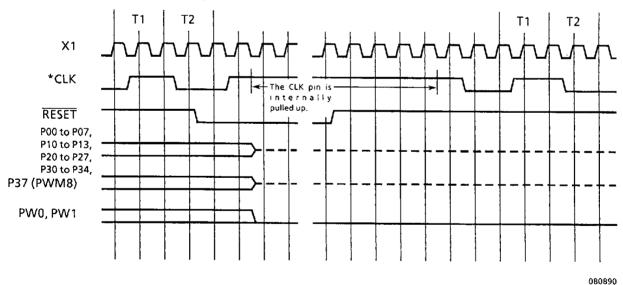

Figure 3.1 shows the basic timing of reset.

To reset the TMP91C642A, the power supply voltage must be within the operating voltage and oscillation by the internal oscillator must be stable. Also, the  $\overline{\text{RESET}}$  input must be maintained at level 0 for at least 10 system clocks (10 states : 2  $\mu$ s at 10 MHz clock oscillation).

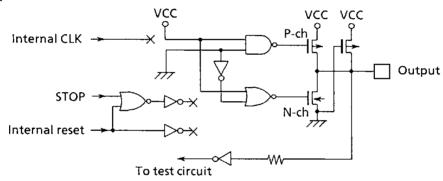

When a reset is accepted, all I/O ports (port 0, port 1, port 3 (P30 to P34), port 4, and port 6 (P60 to P63) are set to input (high impedance). Output dedicated port \*CLK is set to "1" and P37 (PWM8) to high impedance. The other output dedicated ports (PW0 and PW1) are set to "0". The input dedicated ports remain the same.

The CPU registers do not change. The program counter (PC) and interrupt enable flag IFF are cleared to "0". Register A becomes indeterminate.

When a reset is cleared, the CPU starts execution from address 0000H.

Figure 3.1 Reset Timing

(Note) \* With the TMP91C642A, CLK is always internally pulled up to "1".

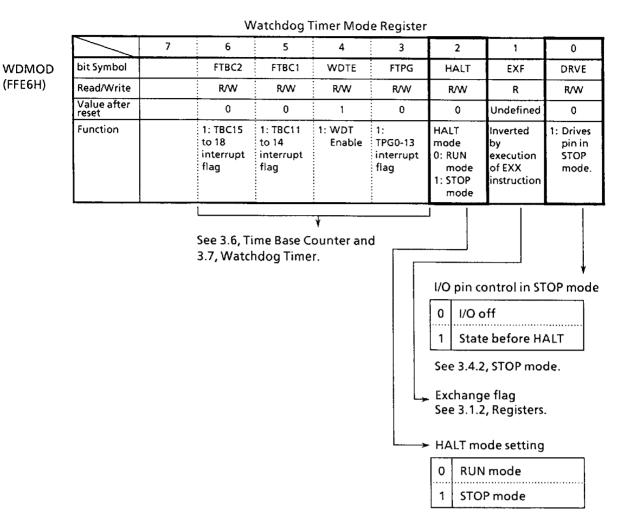

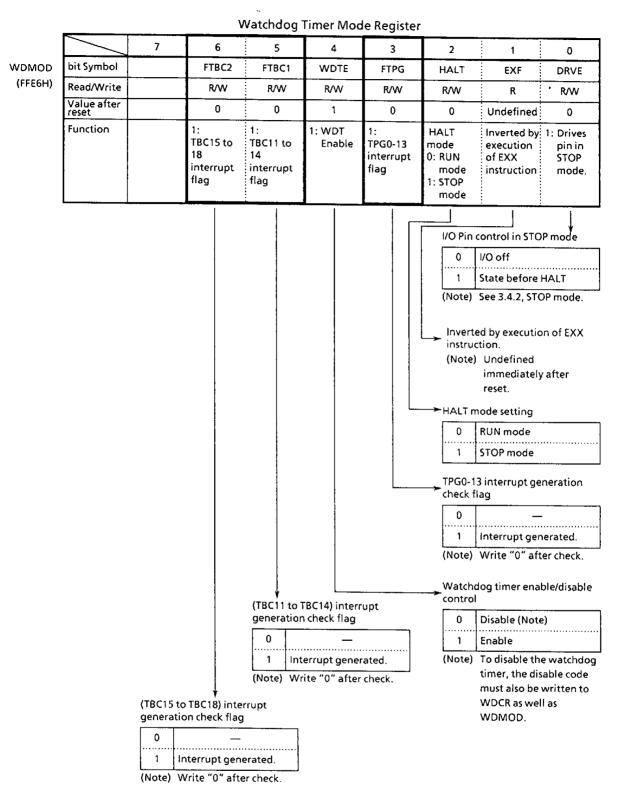

## 3.1.2 Exchange Flag (EXF)

The EXF register is inverted by execution of data exchange instruction EXX, which exchanges data between the main and the auxiliary registers. The TMP91C642A allocates the EXF register to bit 1 at address FFE6H in memory.

The EXF register is not initialized by the reset operation.

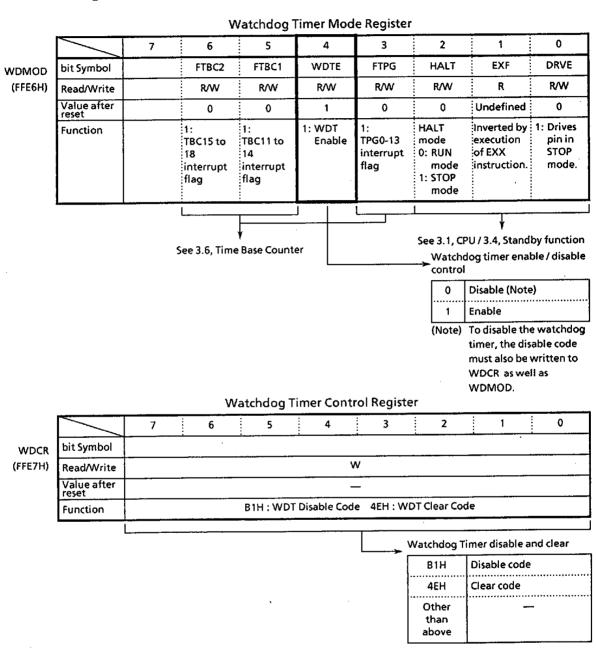

| Watchdog | Timer | Mode | Register |

|----------|-------|------|----------|

| watthuou | HIME  | Moue | neuistei |

## WDMOD (FFE6H)

|                   | 7 | 6                                      | 5                                      | 4                | 3                               | 2                                  | 1                                         | 0                                 |

|-------------------|---|----------------------------------------|----------------------------------------|------------------|---------------------------------|------------------------------------|-------------------------------------------|-----------------------------------|

| bit Symbol        |   | FTBC2                                  | FTBC1                                  | WDTE             | FTPG                            | HALT                               | EXF                                       | DRVE                              |

| Read/Write        | • | R/W                                    | R/W                                    | R/W              | R/W                             | R/W                                | R                                         | R/W                               |

| Value after reset |   | 0                                      | 0                                      | 1                | 0                               | 0                                  | Underfined                                | 0                                 |

| Function          |   | 1: TBC15 to<br>18<br>interrupt<br>flag | 1: TBC11 to<br>14<br>interrupt<br>flag | 1: WDT<br>Enable | 1: TPG0-13<br>interrupt<br>flag | HALT mode 0: RUN mode 1: STOP mode | Inverted by execution of EXX instruction. | 1: Drives pin<br>in STOP<br>mode. |

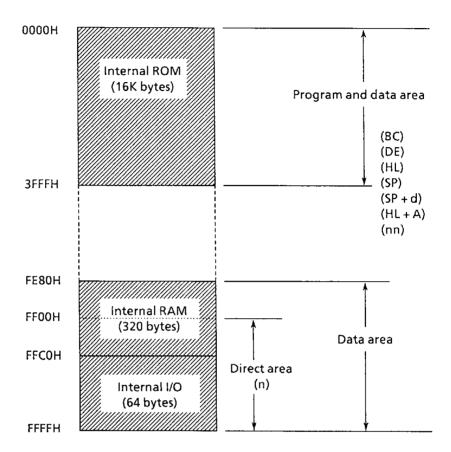

## 3.2 Memory Map

## (1) Internal ROM

The TMP91C642A integrates a 16K-byte ROM. The ROM is allocated to the address space from 0000H to 3FFFH. After reset, the CPU starts execution of the program from address 0000H.

Addresses 0010H to 007FH in the ROM are used as the interrupt entry area by the interrupt processing.

#### (2) Internal RAM

The TMP91C642A integrates a 320-byte RAM. The RAM is allocated to the address space from FE80H to FFBFH. The CPU can access part of the RAM (FF00H to FFBFH, 192-byte area) using direct addressing mode with short instruction codes.

Addresses FF10H to FF7FH in the RAM are used as the micro-DMA parameter area. (Note that when the DMA is not in use, the area can be freely used.)

### (3) Internal I/O

The TMP91C642A uses 64-byte address space as an internal I/O area. The area is allocated to the address area from FFC0H to FFFFH. This I/O area can be accessed by the CPU using a short opcode in the "direct addressing mode".

Figure 3.2 shows the memory map and the CPU addressing mode access ranges.

Figure 3.2 Memory Map

TOSHIBA TMP91C642A

## 3.3 Interrupt Functions

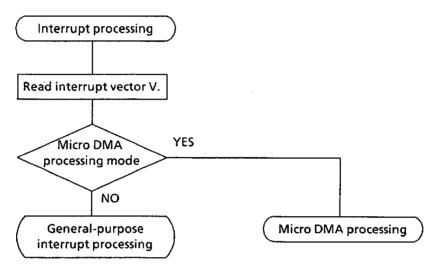

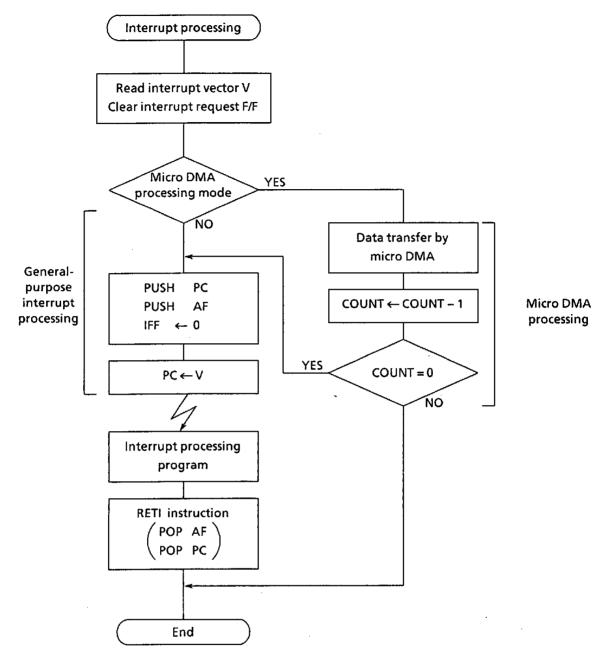

The TMP91C642A supports general-interrupt processing mode used to respond to internal and external interrupt requests and micro DMA processing mode used for automatic data transfer by the CPU.

After a reset is cleared, all interrupt requests are set to general-purpose interrupt processing mode. By using the DMA enable register described later, interrupt requests can be set to micro DMA processing mode.

Figure 3.3. (1) shows the interrupt response flow.

Figure 3.3 (1) Interrupt Response Flow

When an interrupt request is generated, the interrupt source notifies the CPU using the internal interrupt controller. The CPU starts the interrupt processing if the non-maskable or maskable interrupt request is enabled (interrupt enable flag (IFF in register F) = "1"). If the request is non-maskable and interrupt is disabled (IFF = "0"), the CPU ignores the request. (The CPU samples interrupt requests at the falling edge of the \*CLK signal.)

Accepting the interrupt, to determine the interrupt source, the CPU reads the interrupt vector from the internal interrupt controller.

Then, the CPU checks whether the interrupt requests general-purpose or micro DMA interrupt processing and starts processing accordingly.

The CPU reads an interrupt vector during internal operation cycle, the bus cycle results in dummy cycle.

(Note) \* With the TMP91C642A, CLK is always internally pulled up to 1.

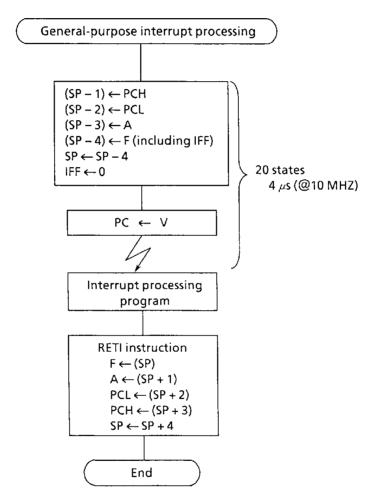

## 3.3.1 General-purpose Interrupt Processing

Figure 3.3 (2) shows the flow of general-purpose interrupt processing.

The CPU first saves contents of the PC and register AF (contains the IFF indicating the interrupt status just before the interrupt generation), then resets interrupt enable flag IFF to "0" (interrupt disable mode). The CPU copies contents V of the interrupt vector to the PC and jumps to the interrupt processing program.

The overhead from accepting an interrupt to jumping to the interrupt processing program is 20 states.

Figure 3.3 (2) General-Purpose Processing Flow

The interrupt processing program ends with the RETI instruction for both non-maskable and maskable interrupts.

Executing the RETI instruction restores the contents of the PC and register AF from the stack. (The status returns to that of the interrupt enable flag just before the interrupt generation.)

When the CPU reads the interrupt vector, the interrupt source acknowledges that the CPU accepts the interrupt and clears the interrupt request.

Non-maskable interrupts cannot be disabled by program. On the other hand, maskable interrupts can be enabled/disabled by program. Bit 5 in register F is the interrupt enable flag (IFF). The CPU can select interrupt enable / disable by setting IFF to "1" using the EI (enable interrupt) instruction; reset to "0" using the DI (disable interrupt). IFF is reset by a reset or acceptance of an interrupt including non-maskable interrupt.

Interrupts are enabled after the instruction subsequent to the EI instruction. Table 3.3 (1) shows interrupt sources.

| Priority | Туре     | Interrupt source              | Vector<br>value /8 | Vector<br>value V | General-purpose<br>interrupt<br>processing start<br>address | Micro DMA<br>processing<br>parameter<br>start address |

|----------|----------|-------------------------------|--------------------|-------------------|-------------------------------------------------------------|-------------------------------------------------------|

| 1        | Non-     | SWI instruction               |                    | 10H               | 0010H                                                       | <del></del>                                           |

| 2        | maskable | INTWD (watchdog timer)        |                    | 20H               | 0020H                                                       |                                                       |

| 3        |          | INTO (External input 0)       | 05H                | 28H               | 0028H                                                       | FF28H                                                 |

| 4        |          | INTCAP (Capture interrupt)**1 | 06H                | 30H               | 0030H                                                       | FF30H                                                 |

| 5        |          | INTAD (A/D converter)**2      | 07H                | 38H               | 0038H                                                       | FF38H                                                 |

| 6        |          | INTSIO (Serial I / O)*3       | 08H                | 40H               | 0040H                                                       | <b>※4</b>                                             |

| 7        |          | INTTO (Timer 0)               | 09H                | 48H               | 0048H                                                       | FF48H                                                 |

| 8        | Maskable | INTT1 (Timer 1)               | 0AH                | 50H               | 0050H                                                       | FF50H                                                 |

| 9        |          | INTT2 (Timer 2)               | 0BH                | 58H               | 0058H                                                       | FF58H                                                 |

| 10       |          | INTT3 (Timer 3)               | 0CH                | 60H               | 0060Н                                                       | FF60H                                                 |

| 11       |          | INTTB (Divider)               | 0DH                | 68H               | 0068H                                                       | FF68H                                                 |

| 12       |          | INT1 (External input 1)       | 0EH                | 70H               | 0070H                                                       | FF70H                                                 |

| 13       |          | INTVA (VASS) *5               | 0FH                | 78H               | 0078H                                                       | FF78H                                                 |

| 13       |          | INT2 (External input 2) *5    | 0FH                | 78H               | 0078H                                                       | FF78H                                                 |

Table 3.3 (1) Interrupt Sources

(Note) %1) C-FG, D-FG, D-PG, P-CTL, EXT, VP (C-Sync)/TPFIFO

※2) INTAD cannot be used.

$\times 3$ ) SIO<sub>1</sub>/SIO<sub>2</sub>

※4) INTSIO cannot use micro DMA processing.

※5) INTVA or INT2 is selected according to INT2 interrupt select register INTEH < INT2S >.

"Priority" in table 3.3 (1) shows the priority of interrupt sources to be acknowledged by the CPU when multiple interrupt requests are generated simultaneously.

For example, when interrupts with priorities 3 and 4 are generated simultaneously, the CPU accepts the interrupt with priority 3 first. After processing of the interrupt with priority 3 is ended by the RETI instruction, the interrupt with priority 4 is accepted. However, a lower priority interrupt can be acknowledged immediately by executing an EI instruction in a program that processes a higher priority interrupt.

The internal interrupt controller only determines priorities of interrupt sources to be acknowledged by the CPU when multiple interrupt requests are generated. It does not compare the priority of the currently-processed interrupt and that of the interrupt being requested.

To enable other interrupts during interrupt processing, set the interrupt enable flag of the interrupt source to be enabled and perform the EI instruction.

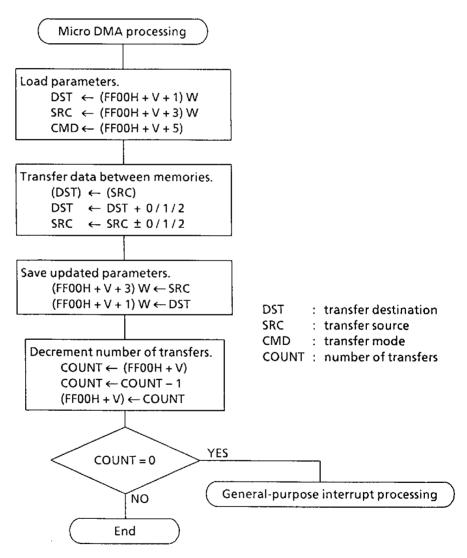

## 3.3.2 Micro DMA processing

Figure 3.3 (3) shows the flow of the micro DMA processing. The CPU loads the parameters (transfer source, destination addresses and transfer mode) necessary for data transfer between memories from the address modified by the interrupt vector, transfers data between memories according to the parameters, then saves the updated parameters back. The CPU decrements the number of transfers. If the value is other than 0, the micro DMA processing ends. If the value is 0, the general-purpose processing is performed.

Figure 3.3 (3) Micro DMA Processing Flow

Most of the interrupt processing consists of simple data transfer. The previous processing depends on software. On the other hand, the micro DMA processing only uses hardware to improve interrupt processing speed. The CPU registers are not influenced by the micro DMA processing.

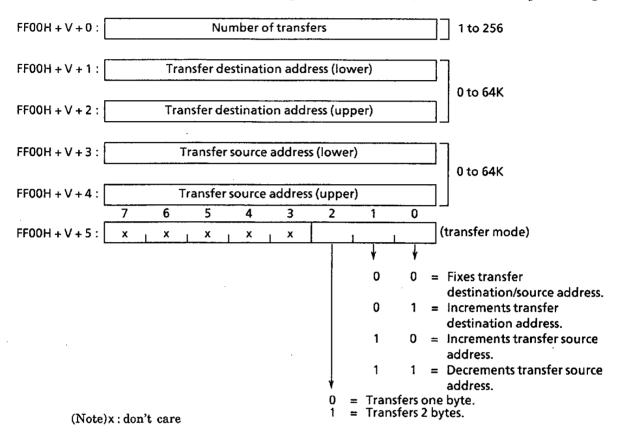

Figure 3.3 (4) shows the functions of parameters used by the micro DMA processing.

Figure 3.3 (4) Micro DMA Parameters

The micro DMA parameters are allocated to the internal RAM. (See Table 3.3 (1), Interrupt Sources.) Each micro DMA processing parameter start address is determined by "FF00H + interrupt vector value". A parameter uses 6 bytes starting from the start address. When the micro DMA processing mode is not in use, the area can be freely used as user memory.

A parameter consists of the number of transfers, transfer source address, and transfer mode. Specify the number of data transfers to be accepted by the micro DMA processing as the number of transfers. The micro DMA processing transfers 1 or 2 bytes of data at a time. When the value of the number of transfers is 00H, the number of transfers is 256. Specify the transfer destination and source addresses in two data bytes. The micro DMA processing can use the address area from 0000H to FFFFH.

Specify in bits 0 and 1 transfer mode for updating the transfer destination or source address. Specify in bit 2 the transfer data length, as 1 or 2 bytes.

Table 3.3 (2) shows transfer modes and transfer destination and source address increment/decrement.

Table 3.3 (2) Micro DMA Address Increment/Decrement

| Transfer<br>mode | Function                                                          | Transfer<br>destination<br>address | Transfer<br>source<br>address |

|------------------|-------------------------------------------------------------------|------------------------------------|-------------------------------|

| 000              | 1-byte transfer, Fixes transfer destination and source addresses. | 0                                  | 0                             |

| 001              | 1-byte transfer, Increments transfer destination address.         | + 1                                | 0                             |

| 010              | 1-byte transfer, Increments transfer source address.              | 0                                  | + 1                           |

| 011              | 1-byte transfer, Decrements transfer source address.              | 0                                  | <b>– 1</b>                    |

| 100              | 2-byte transfer, Fixes transfer destination and source addresses. | 0                                  | 0                             |

| 101              | 2-byte transfer, Increments transfer destination address.         | + 2                                | 0                             |

| 110              | 2-byte transfer, Increments transfer source address.              | 0                                  | + 2                           |

| 111              | 2-byte transfer, Decrements transfer source address.              | 0                                  | <b>-</b> 2                    |

In 2-byte transfer mode, data are transferred as follows:

```

(transfer destination address) ← (transfer source address)

(transfer destination address + 1) ← (transfer source address + 1)

```

In a mode where the transfer source address is decremented, data are transferred as above, but the address is updated as shown in Table 3.3.(2).

The micro DMA updates addresses taking I/O transfer into consideration. Therefore, either transfer destination or transfer source address is fixed.

The execution time (the number of transfers is other than 0 due to decrement) of the micro DMA processing is 46 states (9.2  $\mu$ s at 10 MHz oscillation frequency) regardless of 1-byte or 2-byte mode.

Figure 3.3 (5) shows the flow of overall interrupt processing.

Figure 3.3 (5) Interrupt Processing Flow

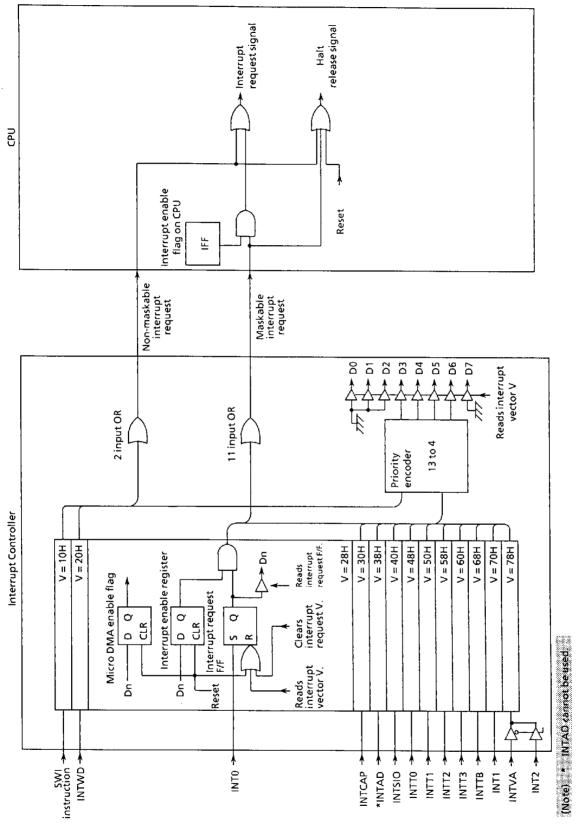

# 3.3.3 Interrupt Controller

Figure 3.3 (7) outlines the interrupt circuit. The left half of the figure shows the interrupt controller. The right half shows the CPU interrupt request signal circuit and halt release circuit (for halt, see 3.4 Standby Function).

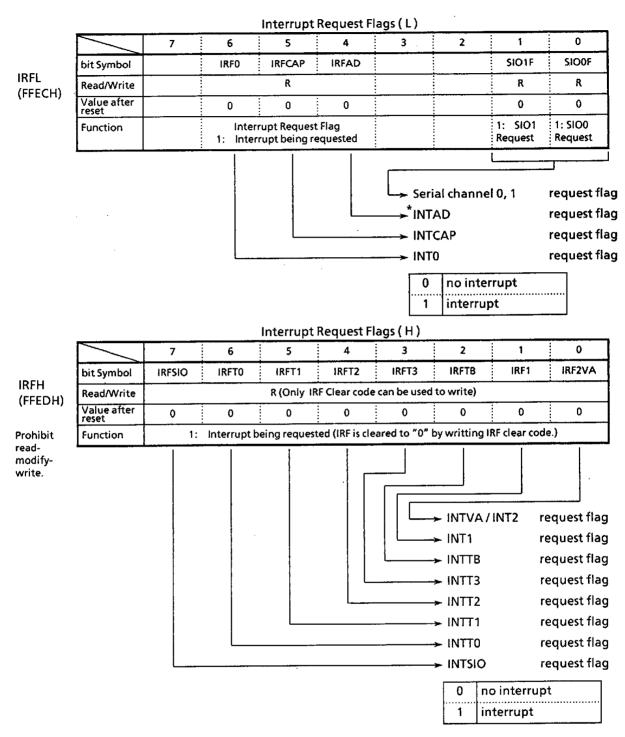

The interrupt controller has an interrupt flip / flop, interrupt enable register, and micro DMA enable flag for each channel (total of 12 channels). The interrupt request flip / flop is used to latch an interrupt request. The interrupt request flip / flop is reset to "0" at reset, when the CPU accepts an interrupt and reads the vector, or when the instruction used to clear the interrupt request of the channel (writes vector value / 8) to address FFEDH in memory) is performed. For example, when executing the following:

LD (FFEDH), 30H/8

the interrupt request flip / flop of channel INTCAP whose vector value is 30H is reset to "0". (To clear the flip / flop, even if the interrupt request flag is assigned to FFECH, write to FFEDH.)

The status of the interrupt flip / flop can be determined by reading address FFECH or FFEDH in memory. "0" indicates no interrupt request; "1" indicates an interrupt request. Figure 3.3 (6) shows the bit configuration of the interrupt request flip / flop.

(Note) Writing vector value / 8 to address FFEDH in memory clears the specified interrupt request flip/flop.

\* INTAD cannot be used.

Figure 3.3 (6) Interrupt Request Flip / Flop

MCU90-20

**9097249 0043287 217**

Figure 3.3 (7) Interrupt Circuit

MCU90-21

**9**097249 0043288 **1**53 **=**

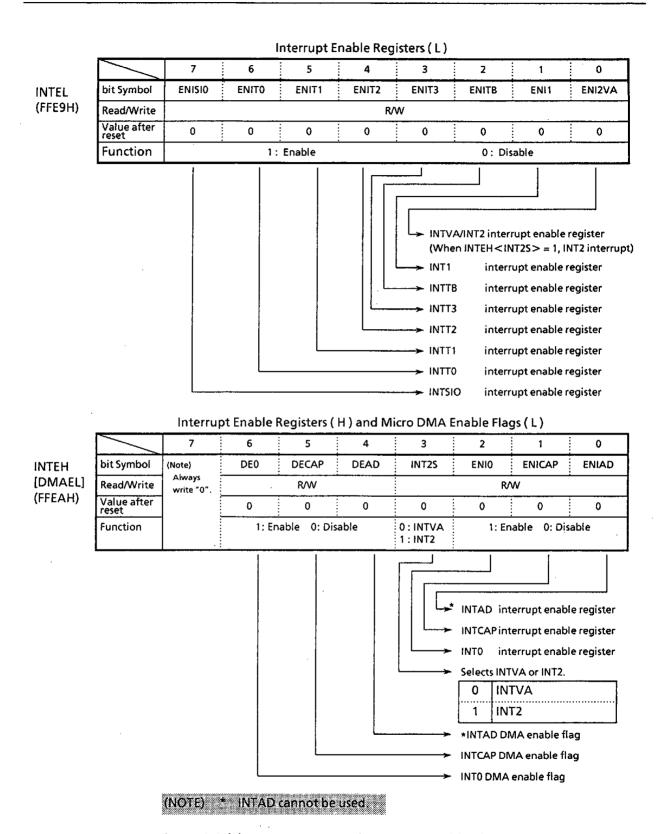

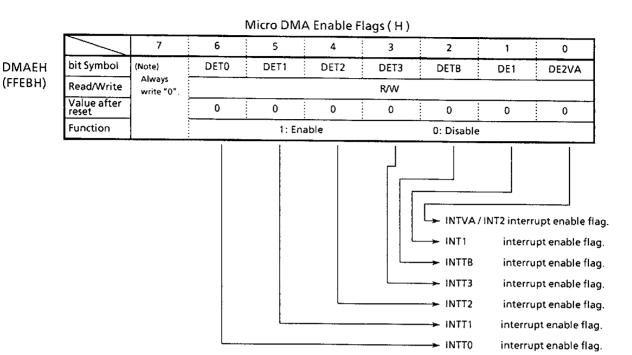

The interrupt enable register for each interrupt request channel is assigned to address FFE9H or FFEAH in memory. Setting the flag to "1" enables an interrupt to the channel. Reset resets the flag to "0".

Clear an interrupt request flag when interrupts are disabled.

The micro DMA enable flag for each interrupt request channel is assigned to address FFEAH or FFEBH in memory. Setting the flag to "1" sets the mode to micro DMA processing mode for interrupts to the channel. Reset resets the flag to "0" (that is general-purpose interrupt processing mode).

Figure 3.3 (8) shows the bit configuration of interrupt enable registers and micro DMA enable flags.

INT2, which is an interrupt by external input 2, and INTVA, which is an interrupt by the VASS flag, share the same interrupt request channel. After reset, INTVA is input to the interrupt controller. When using INT2, set INTVA / INT2 select bit (<INT2S>: bit 3 at FFEAH in memory) to "1".

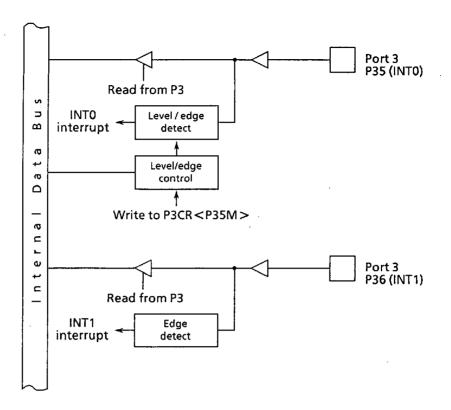

External interrupt functions are as listed below:

| Interrupt | Shared pin | Mode           | Setting           |

|-----------|------------|----------------|-------------------|

|           |            | level          | P3CR < P35M > = 0 |

| INT0      | P35        | f rising edge  | P3CR < P35M > = 1 |

| INT1      | P36        | _√ rising edge |                   |

| INT2      | P46        | rising edge    |                   |

For the pulse width of the external interrupt function, see 4.7, Interrupt Operation.

Note that the following 4 items are exceptional circuits.

| INTO level mode | The interrupt request flip / flop function is cancelled because an interrupt is not edge-type. A peripheral interrupt request passes through the flip / flop S input and becomes Q output. When the mode is changed from edge to level, the previous interrupt request flag is automatically cleared.  After changing INTO from "0" to "1", when the CPU enters the interrupt response sequence, INTO must be maintained at "1" until the second bus cycle of the interrupt response sequence is complete. To use INTO level mode for releasing HALT, INTO must be changed from "0" to "1" and be maintained at "1" until halt is released. (Make sure that it is not set to "0" due to noise.)  When the mode is changed from level to edge, an interrupt request flag accepted in level mode is not cleared. Clear the interrupt request flag in the following sequence.  DI  LD (0FFC7H), 20H Changes from level to edge.  LD (0FFC7H), 20H; Clears interrupt request flag El |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTCAP          | The interrupt request flip / flop is cleared depending on the source: source from the capture circuit or source from TPG. When an interrupt is generated by the capture circuit, the interrupt request flip/flop is cleared by reading all the data from capture FIFO status CAPFST.  The flip / flop can also be cleared by writing "1" to SVCFREG < CARFS >.  When an interrupt request is generated from TPG, the interrupt request flip/flop is cleared by writing data to FIFO of TPG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

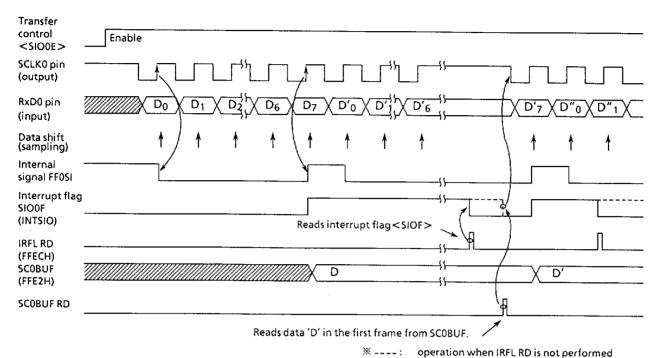

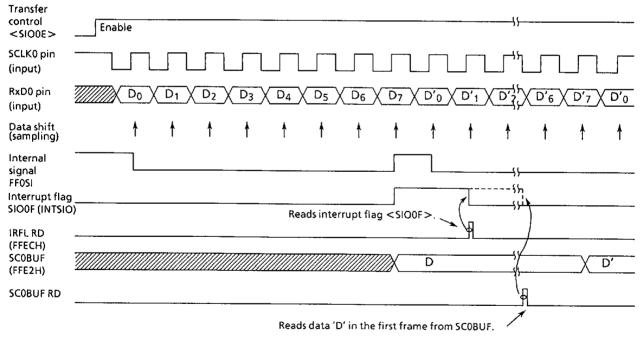

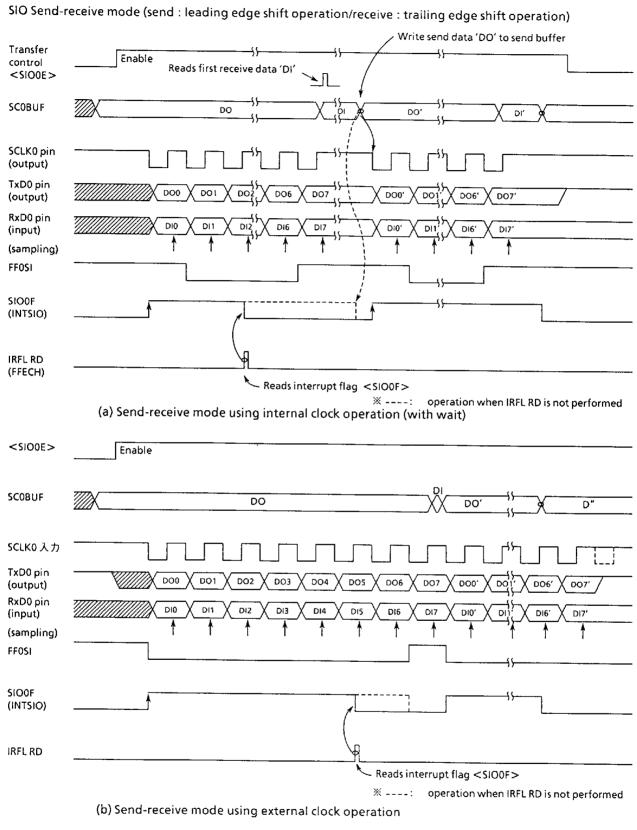

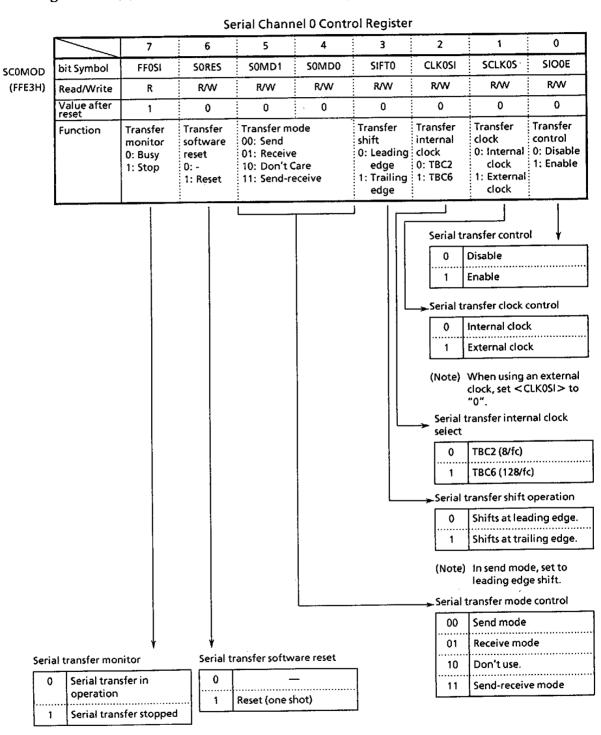

| INTSIO          | The interrupt request flip / flop is cleared by reset or by reading data from the receive data buffer of the serial channel. It cannot be cleared by instructions.  Reading IRFL clears the interrupt request flag (IRFSIO) and the channel information (SIO1F, SIO0F).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INTVA / INT2    | When an interrupt source is cleared (INTAD↔INTT2), the previous interrupt request flag is automatically cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Figure 3.3 (8) - 1 Interrupt / Micro DMA Enable Flags

MCU90-24

**--** 9097249 0043291 748 **--**

Figure 3.3 (8) - 2 Interrupt / Micro DMA Enable Flags

## 3.4 Standby Function

Executing the HALT instruction sets the TMP91C642A to RUN or STOP mode according to the halt mode setting register (bit 2 at address FFE6H in memory). Features of these modes are as follows:

(1) RUN: Only suspends the CPU. Power consumption remains the same.

(2) STOP: Suspends all internal circuits including the internal oscillator.

Power consumption is greatly reduced.

The above halt states are released by an interrupt request or reset\*. Table 3.4 (2) lists halt release sources. If interrupts are enabled (EI) by the CPU for non-maskable or maskable interrupts, an interrupt is accepted and interrupt processing starts. If interrupts are disabled (DI) by the CPU for maskable interrupts, execution resumes from the instruction subsequent to the HALT instruction; the interrupt request flag remains "1".

If interrupts are disabled (DI) and an interrupt request is generated before execution of the HALT instruction and latched by the interrupt request flag, HALT is released immediately after execution of the HALT instruction (does not enter HALT state.) Therefore, to enter HALT state, clear the interrupt request flag or disable the interrupt enable flag (IFF) before executing the HALT instruction.

Example) Enters stop mode when interrupts are disabled (DI) and releases halt by INTO.

(Internal I/O just use timer 0.)

DI ; Disables interrupts.

SET 2, (INTEH); Enables INTO for releasing halt.

RES 6, (INTEL); Disables timer 0 interrupts.

LD (WDMOD), 04H ; STOP mode HALT ; HALT

Program to be executed after releasing HALT.

\* When halt is released by reset, the states (including those of the internal RAM) before halt state was entered can be maintained. However, if the HALT instruction is executed within the internal RAM, the contents of the RAM may not be maintained. In this case, we recommend releasing the halt state using INTO.

Figure 3.4 (1) HALT Mode Setting Register

### 3.4.1 RUN Mode

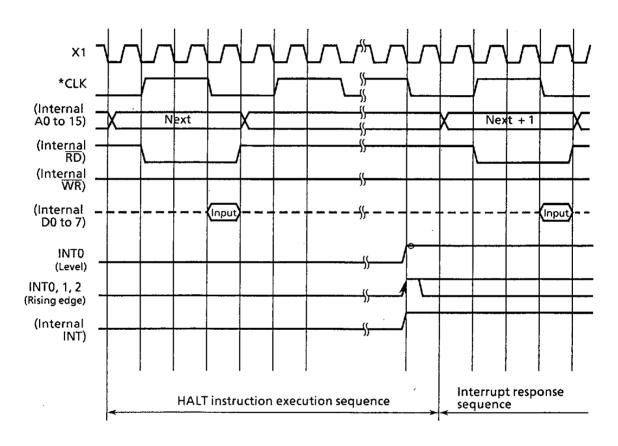

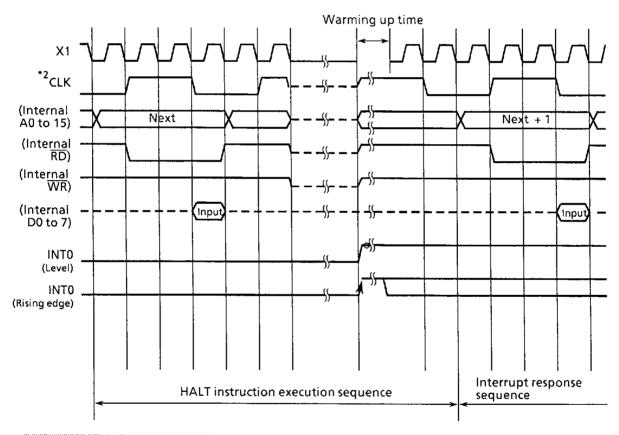

Figure 3.4 (2) shows the timing for releasing halt state by an interrupt in RUN mode. In RUN mode, the internal MCU system clock does not stop after the HALT instruction is executed. The CPU stops only execution of instructions. Therefore, the CPU repeats dummy cycles until the halt state is released. Interrupt requests are sampled at the falling edge of the CLK\* signal in halt state.

(Note) The watchdog timer is also in operation.

\* With the TMP91C642A, CLK is always internally pulled up to "1".

Figure 3.4 (2) Timing for Releasing Halt State by Interrupt in RUN Mode

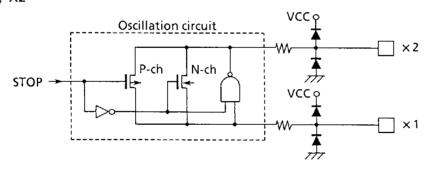

#### 3.4.2 STOP Mode

Figure 3.4 (3) shows the timing for releasing halt state by an interrupt in STOP mode. In STOP mode, all internal circuits including the internal oscillator.

In STOP mode, almost all pins are disconnected from the MCU and set to high impedance. Table 3.4 (1) lists the pin states in STOP mode.

If the WDMOD<DRVE> (drive enable: bit 0 at FFE6H in memory) in the internal I/O register is set to "1", pin functions remain unchanged. The register is reset to "0" by reset.

When the CPU accepts an interrupt request, the internal oscillator restarts. To obtain stabilized oscillation, the system clock starts outputting after the time set by the warming up counter (\*1).

(Note) \*1 Warming up takes a maximum of 220/fc seconds.

(Note) \*2 With the TMP91C642A, CLK is always internally pulled up to "1".

Figure 3.4 (3) Timing Chart for Releasing HALT State by Interrupt in STOP Mode

Inputting a 0-level voltage to the CPU RESET pin also restarts the internal oscillator. However, for quick response at power on, the warming up counter does not operate. As a result, the unstabilized clock immediately after restart of the internal oscillator may cause incorrect operation. The voltage input at 0-level must be maintained for sufficient time when releasing halt state by reset in STOP mode.

To release STOP mode in INTO level mode, INTO must be maintained at "1" until the second bus cycle of the interrupt response sequence is complete.

Table 3.4 (1) Pin States in STOP Mode

| Pin name   | Input/Output | Sta               | ate               |

|------------|--------------|-------------------|-------------------|

| Pin name   | mparoutput   | <drve> = 0</drve> | <drve> = 1</drve> |

| P0         | Input mode   | <del></del>       | <del></del>       |

|            | Output mode  | Output            | Output            |

| P1         | Input mode   |                   | Input             |

|            | Output mode  |                   | Output            |

| P2         | Input mode   |                   | Input             |

|            | Output mode  |                   | Output            |

| P30 to P32 | Input mode   |                   | Input             |

|            | Output mode  |                   | Output            |

| P33, P34   | Input mode   | <del></del>       | Input             |

|            | Output mode  |                   | Output            |

| P35 (INTO) | Input pin    | Input             | Input             |

| P36 (INT1) | Input pin    | <del></del>       | Input             |

| P37        | Output pin   |                   | Output            |

| P4         | Input mode   |                   | Input             |

|            | Output mode  |                   | Output            |

| P5         | Input pin    |                   | Input             |

| P60 to P63 | Input mode   |                   | Input             |

|            | Output mode  |                   | Output            |

| P64 to P67 | Input pin    | <del></del>       | Input             |

| PW0, PW1   | Output pin   | Output            | Output            |

| CLK        | Output pin   | *                 | "1"               |

| RESET      | Input pin    | Input             | Input             |

| X1         | Input pin    |                   | <del></del>       |

| X2         | Output pin   | ″1″               | ″1″               |

: Input is invalid for input mode or input pin; high impedance for output mode or output pin.

Input

: Input enabled.

Input

: Input gate is in operation. To prevent input pin from floating, fix input voltage to

"0" or "1".

Output: Output state.

(Note)\* With the TMP91C642A, CLK is always internally pulled up to "1".

Table 3.4 (2) I/O Operations in Halt State and Halt Release

|                     | ŀ                 | Halt mode                                                | RUN               | STOP              |

|---------------------|-------------------|----------------------------------------------------------|-------------------|-------------------|

| WDMOD <halt></halt> |                   |                                                          | 0                 | 1                 |

| CPU                 |                   |                                                          | Ha                | It                |

|                     | I/Oport           |                                                          | ※ Maintains state | See Table 3.4 (1) |

|                     | Time v            | ase counter                                              |                   |                   |

| <u> </u>            | Watchdog timer    |                                                          |                   |                   |

| 0                   |                   | ASS detection circuit                                    |                   |                   |

| ٩                   | C-Sync            | input processing circuit<br>e circuit<br>pulse generator |                   |                   |

| i 0 i               | Captur            | e circuit                                                | Operation         | Halt              |

| Operation block     | Timing            | pulse generator                                          |                   |                   |

| )<br>p e            | PWM c             |                                                          |                   |                   |

|                     | 8-bit timer       |                                                          |                   |                   |

|                     | Serial inter-face |                                                          |                   |                   |

| į                   | A/D converter     |                                                          |                   |                   |

|                     | Interru           | ıpt controller                                           |                   |                   |

|                     |                   | INTWD                                                    | 0                 | _                 |

|                     |                   | INT0                                                     | 0                 | 0                 |

|                     |                   | INTCAP                                                   | 0                 | _                 |

| 9                   |                   | *INTAD                                                   | 0                 | _                 |

| source              | pt                | INTSIO                                                   | 0                 |                   |

| Į.                  | Interrupt         | INTTO                                                    | 0                 | _                 |

| 3 S e               | ı t e             | INTT1                                                    | 0                 | _                 |

| releas              | -                 | INTT2                                                    | 0                 | _                 |

|                     |                   | INTT3                                                    | 0                 |                   |

| Ha l t              |                   | INTTB                                                    | 0                 |                   |

| Ha                  |                   | INT1                                                     | 0                 | _                 |

|                     |                   | INTVA (VASS)                                             | 0                 |                   |

| 1                   |                   | INT2                                                     | 0                 | -                 |

|                     |                   | Reset                                                    | 0                 | 0                 |

(Note)\* INTAD cannot be used.

: Can be used for releasing halt state.

—: Cannot be used for releasing halt state.

Maintains state at execution of halt instruction.

TOSHIBA TMP91C642A

#### 3.5 Function of Ports

The TMP91C642A supports a total of 54-pin I/O ports. Port pins function not only as general-purpose I/O ports but also as I/O ports for internal CPU or internal I/O. Table 3.5 shows port pin functions.

Table 3.5 Function of Ports

| Port name | Pin name   | Number<br>of pins | Input/<br>output | Unit | State<br>after<br>reset | Pin name for internal function    |

|-----------|------------|-------------------|------------------|------|-------------------------|-----------------------------------|

| Port 0    | P00 to P07 | 8                 | I/O              | Byte | Input                   | TPG0-0 to TPG0-7                  |

| Port 1    | P10 to P13 | 4                 | 1/0              | Bit  | Input                   | TPG0-8 / 1-8 to<br>TPG0-11 / 1-11 |

| Port 2    | P20 to P27 | 8                 | 1/0              | Bit  | Input                   | TPG1-0 to TPG1-7                  |

| Port 3    | P30 to P32 | 3                 | 1/0              | Bit  | Input                   |                                   |

|           | P33        | 1                 | 1/0              | Bit  | Input                   | C – Sync                          |

|           | P34        | 1                 | I/O              | Bit  | Input                   | EXT                               |

|           | P35        | 1                 | Input            |      | Input                   | INTO                              |

|           | P36        | 1                 | Input            |      | Input                   | INT1                              |

|           | P37        | 1                 | Output           | _    | Output                  | PWM8/TO1                          |

| Port 4    | P40        | 1                 | 1/0              | Bit  | Input                   | SCLK0                             |

|           | P41        | 1                 | I/O              | Bit  | Input                   | TxD0                              |

|           | P42        | 1                 | I/O              | Bit  | Input                   | RxD0                              |

|           | P43        | 1                 | I/O              | Bit  | Input                   | SCLK1                             |

|           | P44        | 1                 | I/O              | Bit  | Input                   | TxD1                              |

|           | P45        | 1                 | I/O              | Bit  | Input                   | RxD1                              |

|           | P46        | 1                 | 1/0              | Bit  | Input                   | INT2/TIO                          |

|           | P47        | 1                 | I/O              | Bit  | Input                   | TI1                               |

| Port 5    | P50 to P57 | 8                 | Input            |      | Input                   | AN00 to AN07                      |

| Port 6    | P60 to P63 | 4                 | 1/0              | Bit  | Input                   | AN10 to AN13                      |

|           | P64 to P67 | 4                 | Input            |      | Input                   | CAP0 to CAP3                      |

Reset sets port pins to general-purpose I/O ports. Port pins which can be programmed as input or output are set to input ports. To use port pins for internal functions, make settings by program.

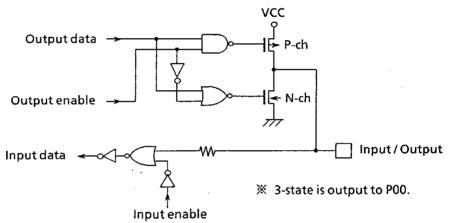

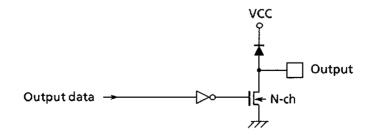

# 3.5.1 Port 0 (P00 to P07)

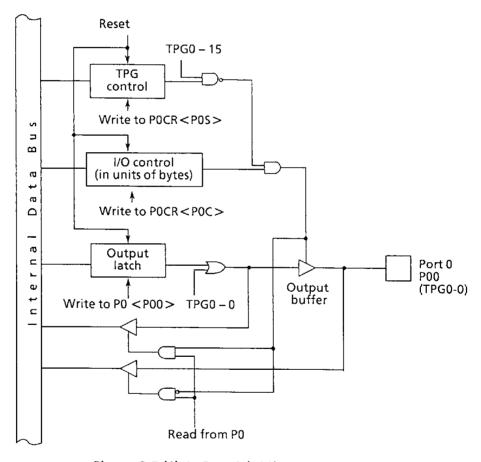

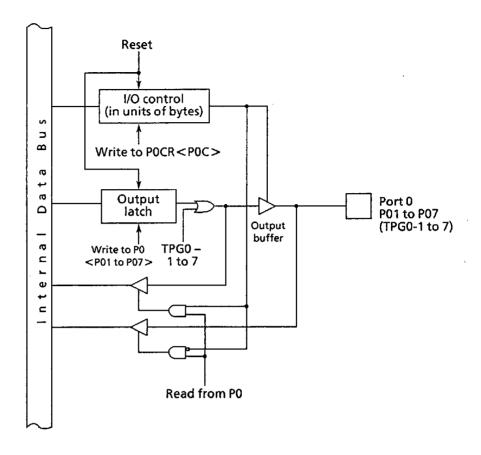

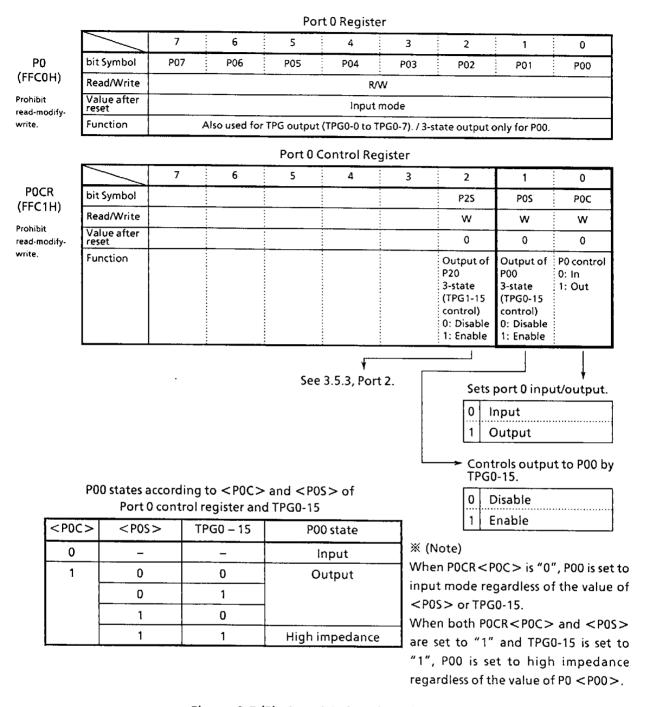

Port 0 is an 8-bit general-purpose I/O port P0 (address FFC0H in memory) to which I/O can be specified in units of bytes. To specify I/O, use control register P0CR < P0C > (bit 0 at address FFC1H in memory). Output to P00 can also be controlled by signals (TPG0-15) from the timing pulse generator and control register P0CR < P0S > (bit 1 at address FFC1H in memory).

Reset resets all bits in the control register and the output latch register to "0" and to input mode.

In addition to its general-purpose I/O port function, port 0 (TPG0-0 to TPG0-7) is used for output by the timing pulse generator (TPG).

To use port 0 as a general-purpose I/O port, write "0" to the bit which is also used as a port in TPG output data register TPO0DAR0. To use port 0 for TPG output, write "0" to the port 0 data register P0.

Do not use the bit modify instruction with the port 0 register.

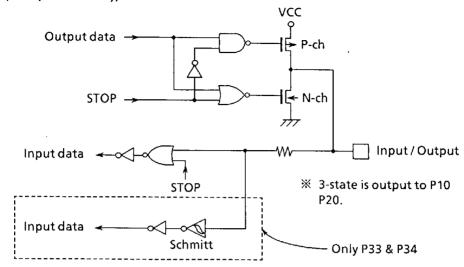

Figure 3.5 (1)-1 Port 0 (P00)

(Note) P04 to P07 outputs are open drain.

Figure 3.5 (1)-2 Port 0 (P01 to P07)

Figure 3.5 (2) Port 0 Related Registers

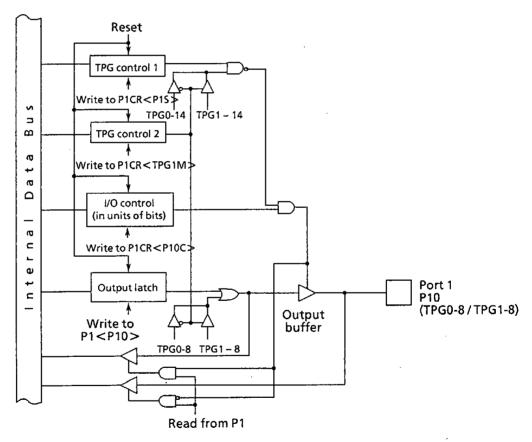

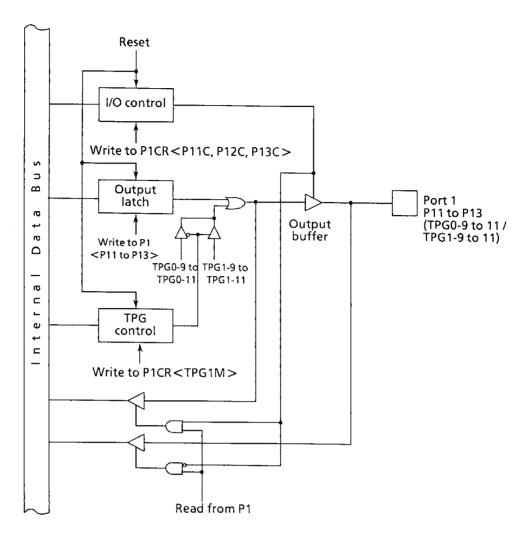

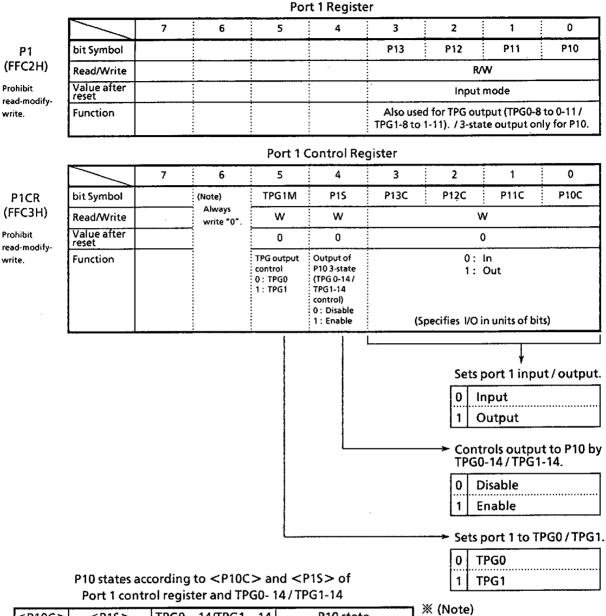

## 3.5.2 Port 1 (P10 to P13)

Port 1 is a 4-bit general-purpose I/O port (address FFC2H in memory) to which I/O can be specified in units of bits. To specify I/O, use control register P1CR < P10C, P11C, P12C, and P13C > (bits 0 to 3 at address FFC3H in memory). Output to P10 can also be controlled by signals (TPG0-14/TPG1-14) from the timing pulse generator.

Reset resets all bits in the control register and the output latch register to "0" and to input mode.

In addition to its general-purpose I/O port function, port 1 is also used for output (TPG0-8/TPG1-8/TPG0-11/TPG1-11) by the timing pulse generator (TPG).

To use port 1 as a general-purpose I/O port, write "0" to the bit which is also used as a port in TPG output data registers TPO0DAR1 <TPO08 to 0B> and TPO1DAR1 <TPO18 to 1B>. To use port 1 for TPG output, write "0" to the port 1 data register. When using the TPG output function, specify I/O in units of 4 bits.

Do not use the bit modify instruction with the port 1 register.

Figure 3.5 (3) - 1 Port 1 (P10)

Figure 3.5 (3)-2 Port 1 (P11 to P13)

| <p10c></p10c> | <p15></p15> | TPG0 – 14/TPG1 – 14 | P10 state      |

|---------------|-------------|---------------------|----------------|

| 0             | _           | _                   | Input          |

| 1             | 0           | 0                   | Output         |

| [             | 0           | 1                   |                |

|               | 1           | 0                   |                |

|               | 1           | 1                   | High impedance |

When P1CR<P10C> is "0", P10 is set to input mode regardless of the value of <P1S> or TPG0-

14/TPG1-14.

When both P1CR < P10C > and < P1S > are set to "1" and TPG0-14/TPG1-14 is set to "1", P10 is set to high impedance regardless of the value of P1 < P10 > .

Figure 3.5 (4) Port 1 Related Registers

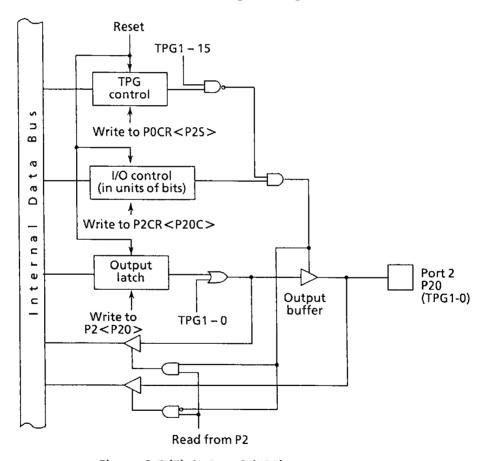

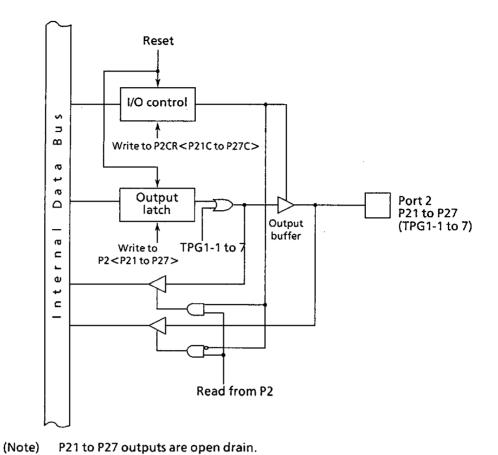

#### 3.5.3 Port 2 (P20 to P27)

Port 2 is a 4-bit general-purpose I/O port (address FFC4H in memory) to which I/O can be specified in units of bits. To specify I/O, use control register P2CR (address FFC5H in memory). Output to P20 can also be controlled by signals (TPG1-15) from the timing pulse generator.

Reset resets all bits in the control register and the output latch register to "0" and to input mode.

In addition to its general-purpose I/O port function, port 2 is also used for output (TPG1-0 to TPG1-7) by the timing pulse generator (TPG).

To use port 2 as a general-purpose I/O port, write "0" to the bit which is also used as a port in TPG output data register TPO1DAR0. To use port 2 for TPG output, write "0" to the port 2 data register P2. When using the TPG output function, specify I/O in units of bytes.

Do not use the bit modify instruction with the port 2 register.

Figure 3.5 (5)-1 Port 2 (P20)

Figure 3.5 (5)-2 Port 2 (P21 to P27)

|                    |                   |      |               | Por        | rt 2 Registe  | er          |                                                                   |                                                                                |                                              |

|--------------------|-------------------|------|---------------|------------|---------------|-------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------------------|

|                    |                   | 7    | 6             | 5          | 4             | 3           | 2                                                                 | 1                                                                              | 0                                            |

| P2                 | bit Symbol        | P27  | P26           | P25        | P24           | P23         | P22                                                               | P21                                                                            | P20                                          |

| C4H)               | Read/Write        |      |               |            | R/            | w           |                                                                   | •                                                                              | <u> </u>                                     |

| iibit<br>I-modify- | Value after reset |      |               |            | Input         | mode        | ···                                                               |                                                                                |                                              |

| е.                 | Function          | -    | Also used for | TPG output | (TPG 1-0 to 7 | TPG1-7)./3- | state output o                                                    | only for P20.                                                                  |                                              |

|                    |                   |      |               | Port 2 (   | Control Re    | gister      |                                                                   |                                                                                |                                              |

|                    |                   | 7    | 6             | 5          | 4             | 3           | 2                                                                 | 1                                                                              | 0                                            |

| 2CR                | bit Symbol        | P27C | P26C          | P25C       | P24C          | P23C        | P22C                                                              | P21C                                                                           | P20C                                         |

| C5H)               | Read/Write        |      |               |            | · \           | N           | <del></del>                                                       | ·                                                                              | <u>.                                    </u> |

| ibit<br>-modify-   | Value after reset |      |               |            |               | 0           |                                                                   | · · · · · · · · · · · · · · · · · · ·                                          | **************************************       |

| -moarry-<br>e.     | Function          |      |               | 0 : In     | •             | 1:          | Out (Speci                                                        | fies I/O in un                                                                 | its of bits.)                                |

|                    |                   |      |               | Port 0 (   | Control Re    | gister      | 0                                                                 | Input<br>Output                                                                | ••••••                                       |

|                    |                   | 7    | 6             | 5          | 4             | 3           | 2                                                                 | 1                                                                              | 0                                            |

| 0CR                | bit Symbol        |      | :             |            |               |             | P2S                                                               | POS                                                                            | P0C                                          |

| C1H)               | Read/Write        | ***  |               | :          |               |             | w                                                                 | w                                                                              | W                                            |

| iibit<br>I-modify  | Value after reset |      |               |            |               |             | 0                                                                 | 0                                                                              | 0                                            |

| modify-            | Function          |      |               |            |               | -           | Output of                                                         | 10                                                                             | P0 contro                                    |

| e.                 |                   |      |               |            |               |             | P20<br>3-state<br>(TPG1-15<br>control)<br>0: Disable<br>1: Enable | Output of<br>P00<br>3-state<br>(TPG0-15<br>control)<br>0: Disable<br>1: Enable | 0: In<br>1: Out                              |

| <p20c></p20c> | <p2s></p2s> | TPG0 - 15 | P20 state      |

|---------------|-------------|-----------|----------------|

| 0             | -           | _         | Input          |

| 1             | 0           | 0         | Output         |

| ] [           | 0           | 1         |                |

|               | 1           | 0         |                |

|               | 1           | 1         | High impedance |

※ (Note)

When P2CR < P2OC > is "0", P2O is set to input mode regardless of the value of <P2S> or TPG1-15.

When both P2CR < P20C > and POCR < P2S > are set to "1" and TPG1-15 is set to "1", P20 is set to high impedance regardless of the value of P2<P20>.

Figure 3.5 (6) Port 2 Related Registers

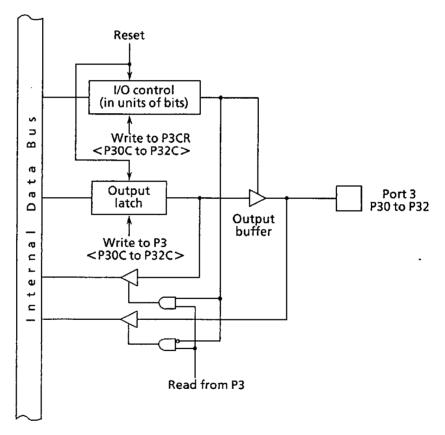

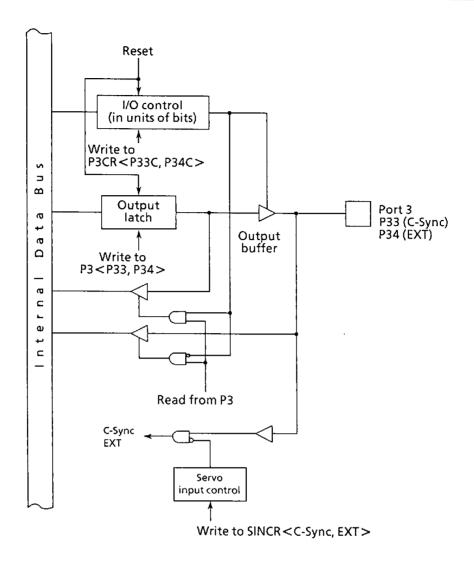

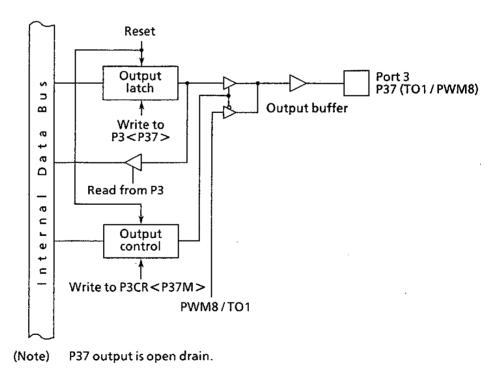

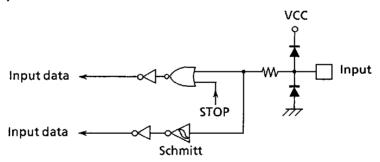

#### 3.5.4 Port 3 (P30 to P37)

Port 3 (address FFC6H in memory) consists of a 5-bit general-purpose I/O port to which I/O can be specified in units of bits, and a 3-bit general-purpose I/O port to which input or output is fixed.

To specify I/O for P30 to P34, use control register P3CR (bits 0 to 4 at address FFC7H in memory).

Reset resets all bits in the control register and the output latch register to "0"; I/O port (P30 to P32) and input-fixed port (P33 and P34) to input mode; output-fixed port (P37) to PWM8 output.

P33 / C-Sync is also used for input from the C-Sync input processing circuit. P34 / EXT is also used for servo signal trigger input. P35 and P36 are also used as interrupt control pins (INT0 and INT1).

After reset, servo input function is enabled. P33 can be used for C-Sync input; P34, for EXT input.

Figure 3.5 (7)-1 Port 3 (P30 to P32)

Figure 3.5 (7)-2 Port 3 (P33 and P34)

Figure 3.5 (7)-3 Port 3 (P35 and P36)

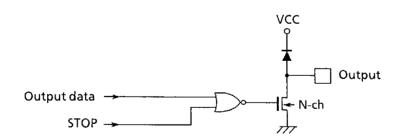

Figure 3.5 (7)-4 Port 3 (P37)

MCU90-44

**--** 9097249 0043311 366 **--**

Port 3 Register

P3 (FFC6H)

|                      | 7                                 | 6                   | 5                   | 4                  | 3                     | 2   | 1   | 0                                              |  |

|----------------------|-----------------------------------|---------------------|---------------------|--------------------|-----------------------|-----|-----|------------------------------------------------|--|

| bit Symbol           | P37                               | P36                 | P35                 | P34                | P33                   | P32 | P31 | P30                                            |  |

| Read/Write           | R/W (Note)                        | I                   | ₹                   | R/W                |                       |     |     | <u>.                                      </u> |  |

| Value after<br>reset | PWM8<br>output                    | Input               | only                | Input mode         |                       |     |     |                                                |  |

| Function             | Also used<br>for PWM8<br>and TO1. | Also used for INT1. | Also used for INTO. | Also used for EXT. | Also used for C-Sync. |     |     |                                                |  |

(Note) <P37> data can be read from the port output latch.

The port function is output only.

Port 3 Control Register

P3CR (FFC7H)

(Note)To select PWM8 or TO1, use the TFFCR<TOSEL> (FFD9H).

| <p37m> TFFCR <tosel></tosel></p37m> | 0    | 1      |

|-------------------------------------|------|--------|

| 0                                   | PWM8 | Output |

| 1                                   | TO1  | to P37 |

0 PWM8/TO1 1 P37

#### Servo Input Control Register

SINCR (FFCEH)

|                   | 7 | 6 | 5      | 4   | 3                             | 2    | 1           | 0    |

|-------------------|---|---|--------|-----|-------------------------------|------|-------------|------|

| bit Symbol        |   |   | C-Sync | EXT | P-CTL                         | C-FG | D-PG        | D-FG |

| Read/Write        |   |   | R/W    | R/W | R/W                           | R/W  | R/W         | R/W  |

| Value after reset |   |   | 0      | 0   | 0                             | 0    | 0           | 0    |

| Function          |   |   |        |     | Servo Inp<br>0 : Er<br>1 : Di |      | <del></del> |      |

Figure 3.5 (8) Port 3 Related Registers

MCU90-45

■ 9097249 0043312 2T2 ■

TOSHIBA

#### TMP91C642A

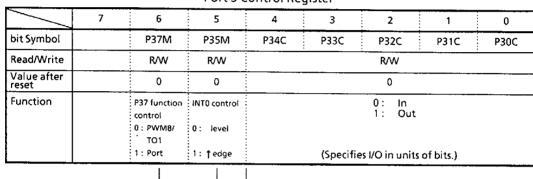

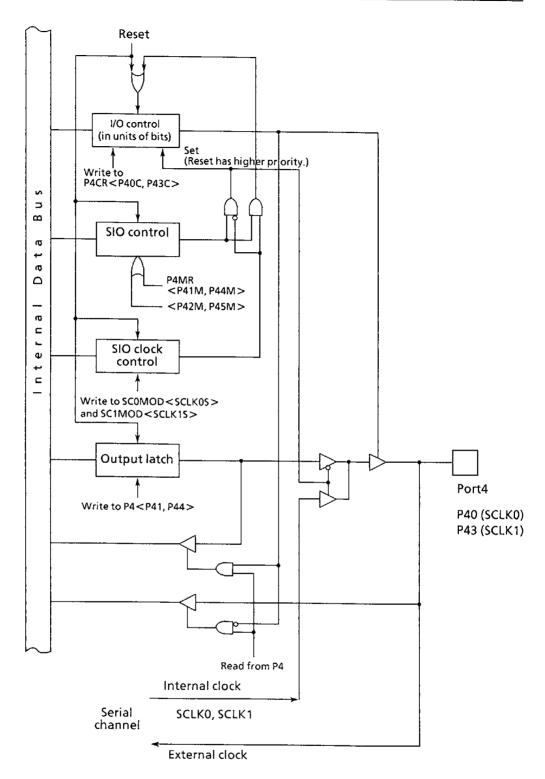

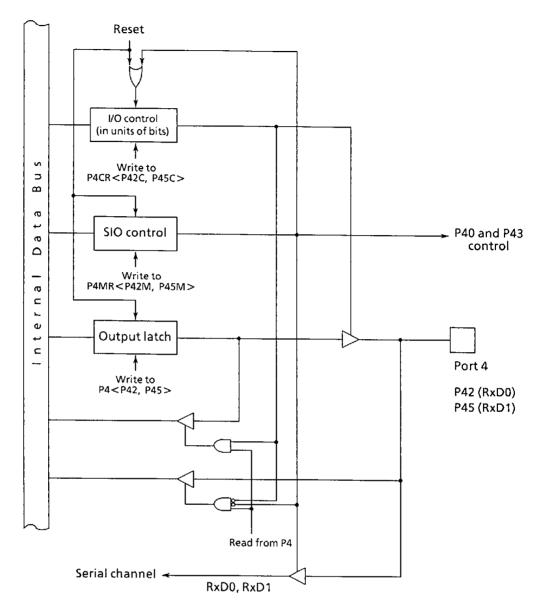

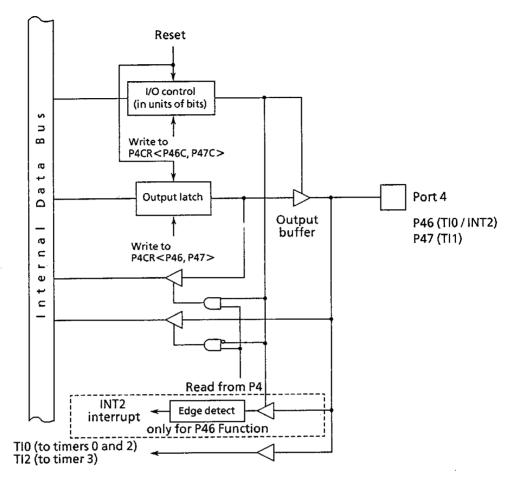

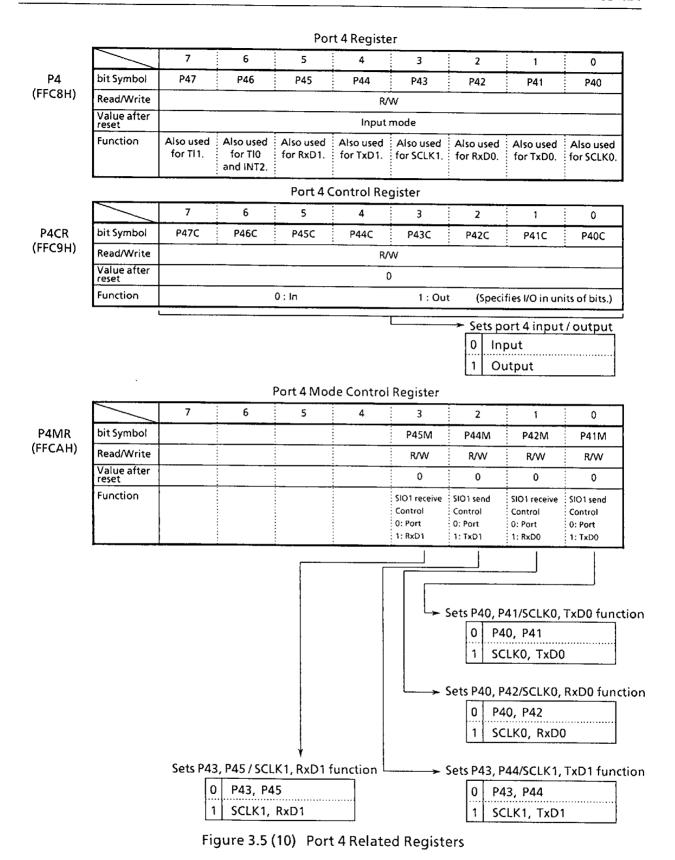

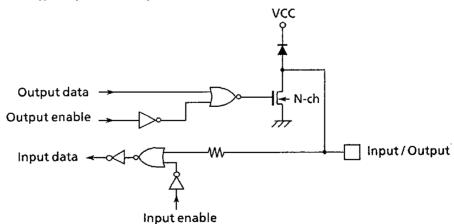

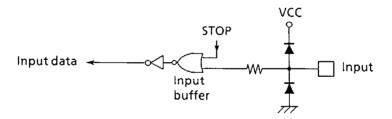

# 3.5.5 Port 4 (P40 to P47)

Port 4 an 8-bit general-purpose I/O port P4 (address FFC8H in memory) to which I/O can be specified in units of bits. To specify I/O, use control register P4CR (address FFC9H in memory).

Reset resets all bits in the control register and the output latch register to "0" and to input mode.

In addition to its general-purpose I/O port function, other port 4 functions are: serial channel (SIO0, SIO1) input/output (SCLK0, 1 / TxD0,1 / RxD0,1), and interrupt and timer (INT2 / TI0, TI1) input.

To use port 4 for serial channel, set the I/O pin settings using port 4 mode control register P4MR (address FFCAH in memory).

Figure 3.5 (9) - 1 Port 4 (P40 and P43)

Figure 3.5 (9) - 2 Port 4 (P41 and P44)

Figure 3.5 (9) - 3 Port 4 (P42 and P45)

Figure 3.5 (9) - 4 Port 4 (P46 and P47)

MCU90-51

■ 9097249 0043318 710 **■**

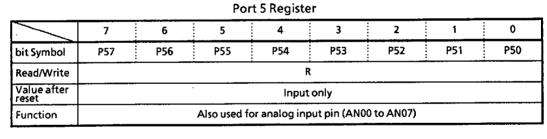

Р5

(FFCBH)

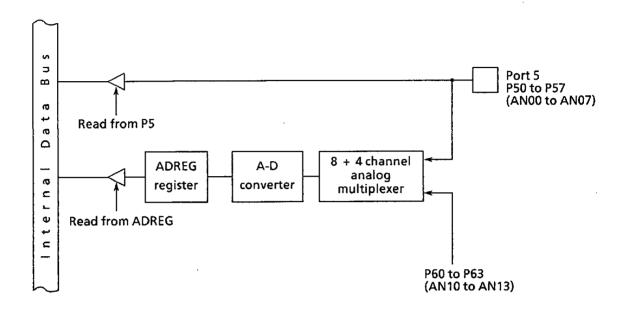

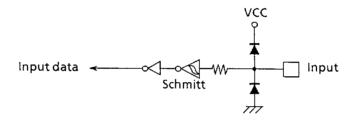

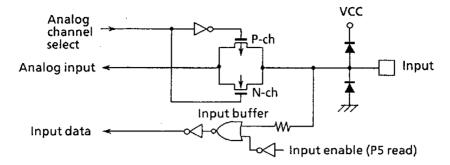

## 3.5.6 Port 5 (P50 to P57)

Port 5 is an 8-bit input port (address FFCBH in memory) which is also used for analog input (AN00 to AN07).

Figure 3.5 (11) Port 5

Figure 3.5 (12) Port 5 Related Registers

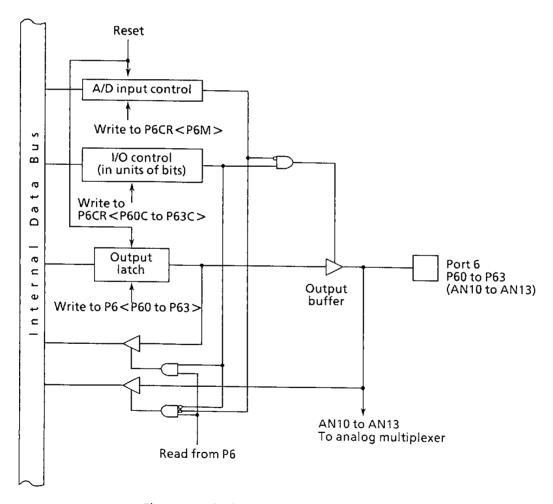

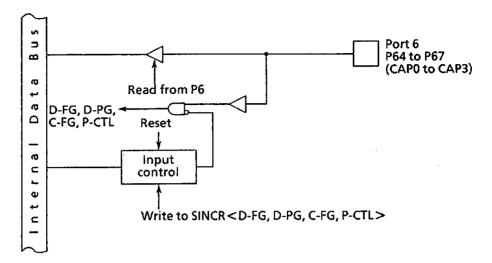

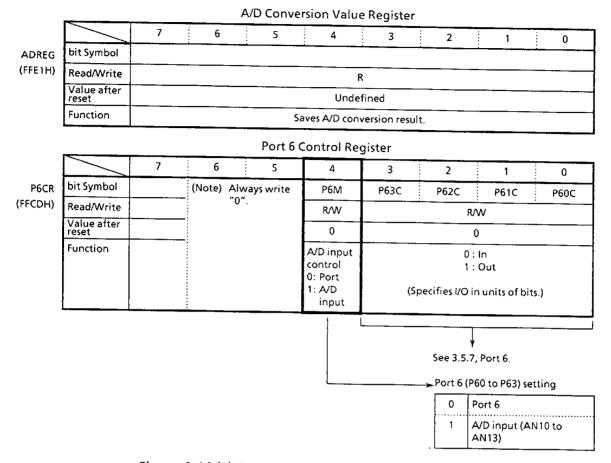

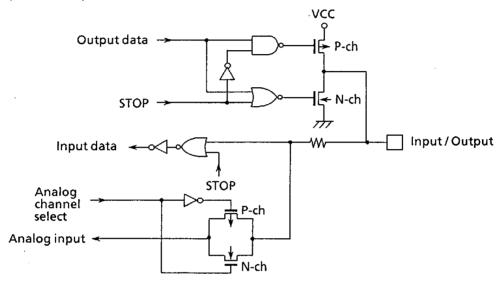

# 3.5.7 Port 6 (P60 to P67)

Port 6 is a general-purpose I/O port consisting of 4 bits to which I/O can be specified in units of bits, and 4 bits to which input is fixed.

To specify I/O for the pins from P60 to P63, use control register P6CR < P60C, P61C, P62C, P63C > (bits 0 to 3 at address FFCDH in memory).

Reset resets all bits in the control register and the output latch register to "0" and to input mode.

In addition to its general-purpose I/O port function, port 6 is used for A/D input (AN10 to AN13) and servo signal trigger input (CAP0 to CAP3).

After reset, servo input function is enabled. P64 to P67 can be used for CAP0 to CAP3 input.

(Note) When using P60 to P63 for A/D input (P6CR < P6M > = 1), I/O port function cannot be used.

Figure 3.5 (13) -1 Port 6 (P60 to P63)

Figure 3.5 (13) -2 Port 6 (P64 to P67)

MCU90-54

#### Port 6 Register 7 6 5 3 2 0 P6 bit Symbol P67 P66 P65 P64 P63 P62 P61 P60 (FFCCH) Read/Write R R/W Value after reset Input only Input mode Also used servo signal trigger input (CAPO to CAP3) Function Also used for analog input pin (AN10 to AN13) Port 6 Control Register 6 4 2 0 P6CR bit Symbol Note : Always write "0" P6M P63C P62C P61C P60C (FFCDH) Read/Write R/W R/W Value after reset 0 0 Function A/D 0: In input 1: Out control 0: Port 1: A/D (Specifies I/O in units of bits.) input Sets port 6 (P60 to P63) input / output Input Output ► Sets port 6 (P60 to P63) function Port 6 A/D input (AN10 to AN13)

Servo Input Control Register

SINCR (FFCEH)

|                   |   |   | •      |     | -                             |      |      |      |

|-------------------|---|---|--------|-----|-------------------------------|------|------|------|

|                   | 7 | 6 | 5      | 4   | 3                             | 2    | 1    | 0    |

| bit Symbol        |   |   | C-Sync | EXT | P-CTL                         | C-FG | D-PG | D-FG |

| Read/Write        |   |   | R/W    | R/W | R/W                           | R/W  | R/W  | R/W  |

| Value after reset |   |   | 0      | 0   | 0                             | 0    | 0    | 0    |

| Function          |   |   |        |     | Servo Inp<br>0: End<br>1: Dis |      | •    | ·    |

Figure 3.5 (14) Port 6 Related Registers

TOSHIBA TMP91C642A

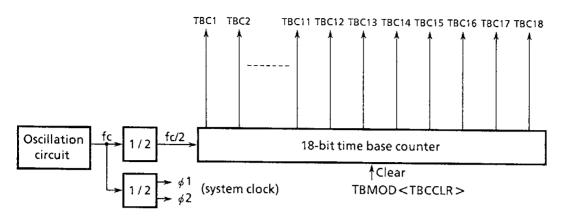

#### 3.6 Time Base Counter (TBC)

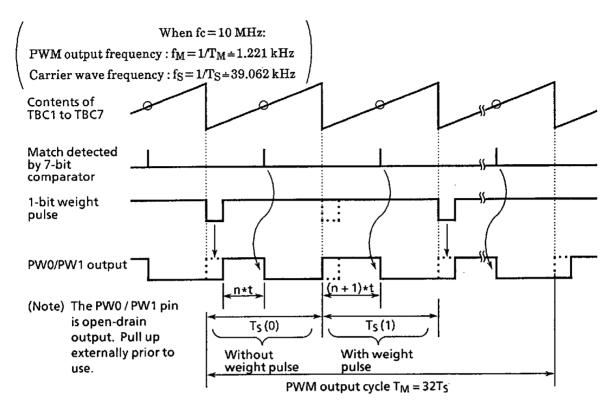

The TMP91C642A has an 18-bit time base counter which generates operation timing reference signals. The software servo is controlled by system time, which is based on the contents of the time base counter. A clock obtained by dividing the fundamental clock (fc) by two is input to the time base counter.

The time base counter outputs (TBC1 to TBC18) are used as reference signals for timers 0 to 3, 24-bit capture, timing pulse generator, 12-bit PWM, and watchdog timer. Figure 3.6 (1) is the block diagram of the time base counter.

#### 3.6.1 Operation

The time base counter value can be cleared by time base counter operating mode register TBMOD<TBCCLR>. Setting <TBCCLR>=1 zero-clears the counter value. During reset, <TBCCLR> is cleared to "0". Releasing reset starts the timer base counter from "0".

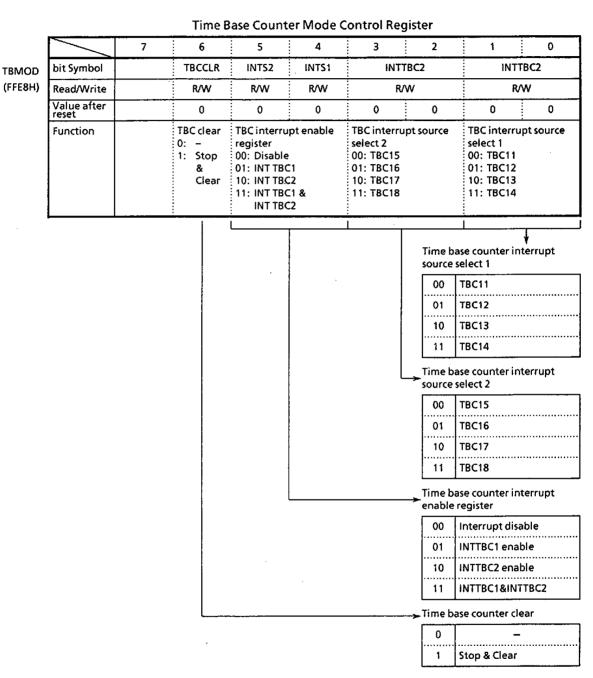

The time base counter has two interrupt sources. It can select an interrupt source according to control register TBMOD<INTS2,1>. Both interrupt generating circuits use control register TBMOD<INTTBC2,1> to select one of the four TBC output signals and generate an INTTB interrupt. These interrupts are output to TPG0-13, also used for output by the timing pulse generating circuit. Reading <FTBC2, 1><FTPG> of watchdog timer mode register WDMOD identifies the interrupt source.

When using an INTTB interrupt for the TBC, do not share the interrupt (TPG0-13) with the TPG. (If an INTTB interrupt is shared with TPG, interrupt timing may be incorrect.)

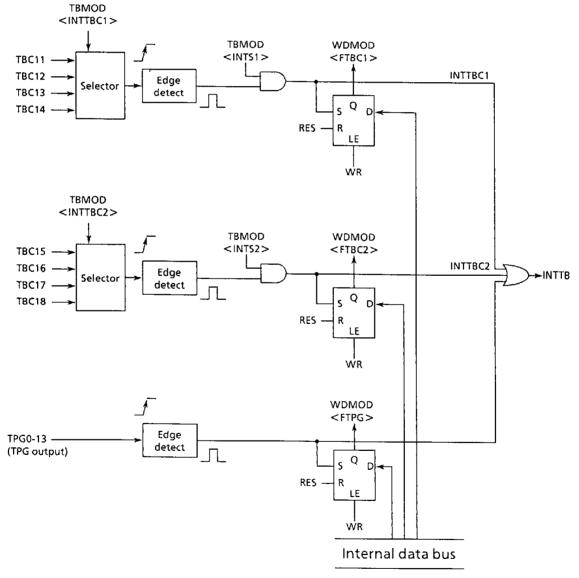

Figure 3.6 (2) is the INTTB interrupt generation block diagram.

Table 3.6 lists time base counter outputs and cycles.

TBC TBC TBC Cycle (µs) Cycle (µs) Cycle (µs) Output signal Output signal Output signal 1638.4 TBC1 (22/fc) 0.4 TBC7 (28/fc) 25.6 TBC13 (214/fc) 3276.8 8 (29/fc) 51.2 14 (2<sup>15</sup>/fc) 2 (23/fc) 8.0 9 (210/fc) 102.4 15 (216/fc) 6553.6 1.6 3 (24/fc) 10 (211/fc) 204.8 (217/fc)13107.2 4 (25/fc) 3.2 11 (2<sup>12</sup>/fc) 409.6 (218/fc) 26214.4 5 (26/fc) 6.4 17 819.2 52428.8 6 (27/fc) 12.8 12 (213/fc) 18 (219/fc)

Table 3.6 Time Base Counter Outputs and Cycles

@ fc = 10 MHz

Figure 3.6 (1) Time Base Counter (TBC) Block Diagram

Figure 3.6 (2) INTTB Interrupt Generation Block Diagram

MCU90-57

**--** 9097249 0043324 T14 **--**

# 3.6.2 Control Registers

The time base counter is controlled by two control registers: TBMOD and WDMOD. Figure 3.6 (3) shows the TBC related register.

Figure 3.6 (3)-1 TBC Related Registers

Figure 3.6 (3) - 2 TBC Related Registers

# 3.7 Watchdog Timer (Malfunction Detection Timer)

When the CPU starts misoperation (that is, malfunction) due to noise or some other cause, the watchdog timer (WDT) detects looping and brings the CPU back to normal operation. The malfunction is detected, a non-maskable interrupt is generated and the CPU is notified of malfunction.

#### 3.7.1 Configuration

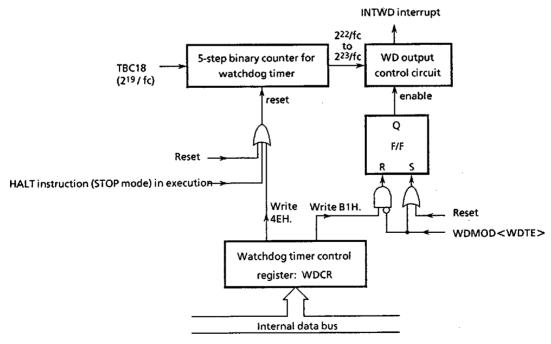

Figure 3.7 (1) is the block diagram of the watchdog timer.

The watchdog timer consists of a 5-step binary counter which uses TBC18 as an input clock, a flip / flop for watchdog timer output enable / disable, and control registers.

The watchdog timer generates an INTWD interrupt after a minimum detection time of  $2^{22}$ /fc. The binary counter of the watchdog timer is zero-cleared before an INTWD interrupt generated by software (instruction). If the CPU misoperates due to noise or other cause and an instruction to clear the binary counter is not executed, the binary counter overflows and an INTWD interrupt is generated. Then the CPU detects the misoperation; normal operation can be resumed using a program to deal with malfunction.

The watchdog timer resumes operation immediately after reset is released.

The watchdog timer is stopped only in STOP mode. After STOP mode is released, the watchdog timer resumes operation after the warming up time.

The watchdog timer operates in RUN mode (the other HALT mode). It can be disabled before entering RUN mode.

Figure 3.7 (1) Watchdog Timer Block Diagram

### 3.7.2 Operation

(1) Watchdog timer enable/disable control (WDMOD < WDTE >)

The watchdog timer is enabled because it is initialized < WDTE>=1 by reset.

To disable the watchdog timer, WDTE must be zero-cleared and the disable code (B1H) must be written to watchdog timer control register WDCR.

To enable the watchdog timer, set < WDTE > to "1".

(2) Watchdog timer control register (WDCR)

Used to control disabling the watchdog timer and clearing the 5-step binary counter.

① Watchdog timer disable control

Writing "0" to WDMOD<br/> <WDTE>, then writing the disable code (B1H) to WDCR disables the watch<br/>dog timer.

Setting example:

② Clear control of watchdog timer binary counter

Writing the clear code (4EH) to WDCR clears the binary counter and performs recount.

During reset or halt execution after setting the mode to STOP mode, the clear signal is input and the watchdog timer is reset.

Setting example:

Clear control by writing clear code

WDCR

$$\leftarrow 0 \ 1 \ 0 \ 0 \ 1 \ 1 \ 1 \ 0$$

Writes the clear code (4EH).

Clear control by HALT mode

WDMOD

$$\leftarrow$$

- - - - 1 x x Sets to STOP mode.

Executes HALT instruction. Sets to HALT mode.

# 3.7.3 Control Register

The watchdog timer (WDT) is controlled by two control registers: WDMOD and WDCR. Figure 3.7 (2) shows the WDT related register.

Figure 3.7 (2) Watchdog Timer Related Registers

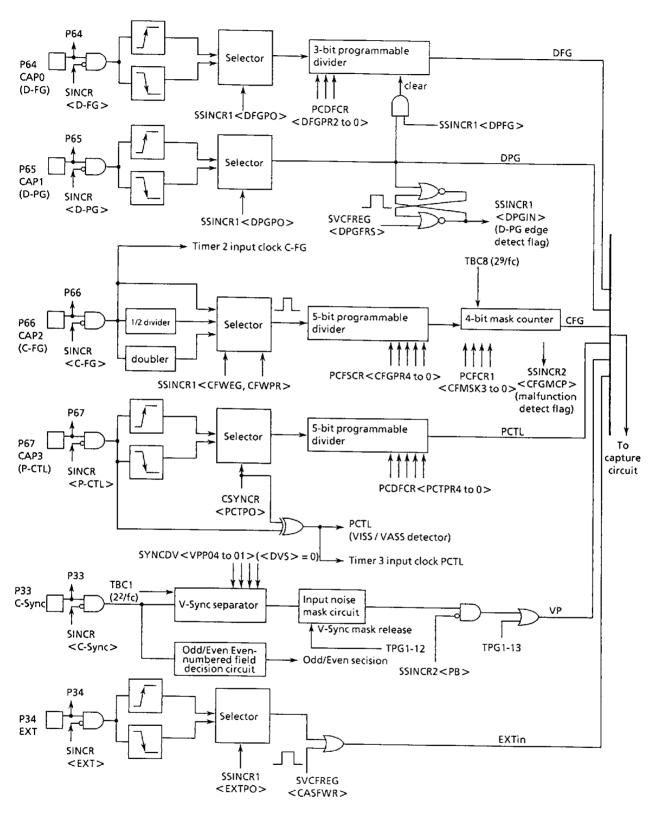

#### 3.8 Servo Input Circuit

TMP91C642A incorporates the following servo input dedicated circuits and signal processing circuits to efficiently perform servo operation by software.

- D-FG/D-PG input processing circuit

- C-FG programmable divider

- C-FG mask counter

- P-CTL programmable divider

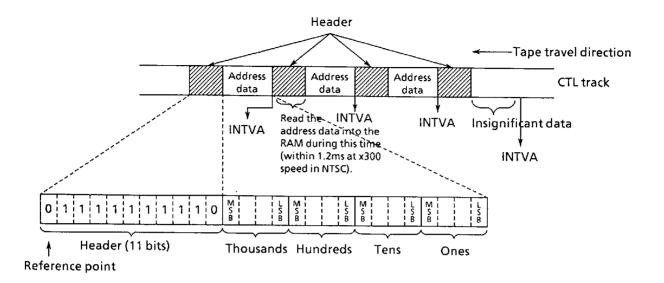

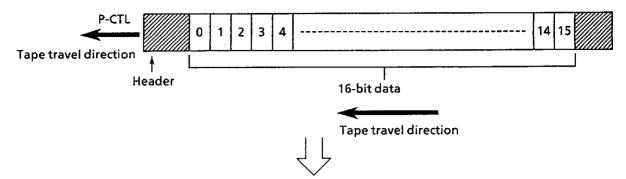

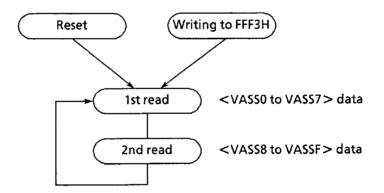

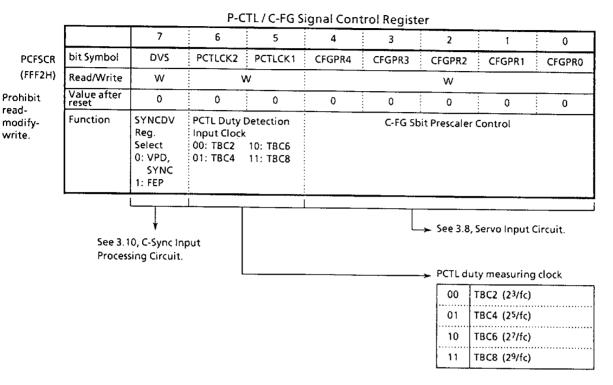

- VISS / VASS detector (explained in 3.9, VISS / VASS detector.)

- C-Sync input processing circuit (explained in 3.10, C-Sync Input Circuit.)

# 3.8.1 D-FG / D-PG Input Circuit / P64 (CAP0) · P65 (CAP1)

There are three commonly-used methods (2PG, 2PG/FG, and 1PG/FG) of generating frequencies and pulses for VCR servo control using a drum. The D-FG/D-PG input circuit incorporates a detect-edge selector and a 3-bit programmable divider for processing the D-FG input signal used to synchronize the D-FG input with the D-PG input signal.

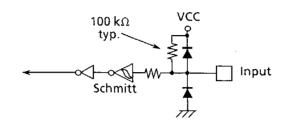

0V-5V logical-level signals are obtained by amplifying and shaping, using the sense amp of the external circuit, the small signals from the frequency generator (FG) and pulse generator (PG) on the drum motor. These logical-level signals are used as the D-FG/D-PG input signals.

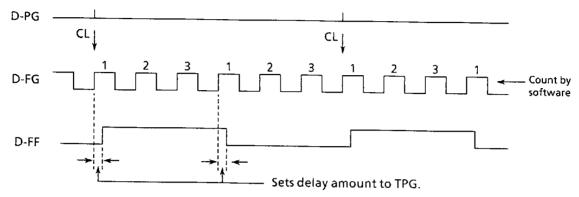

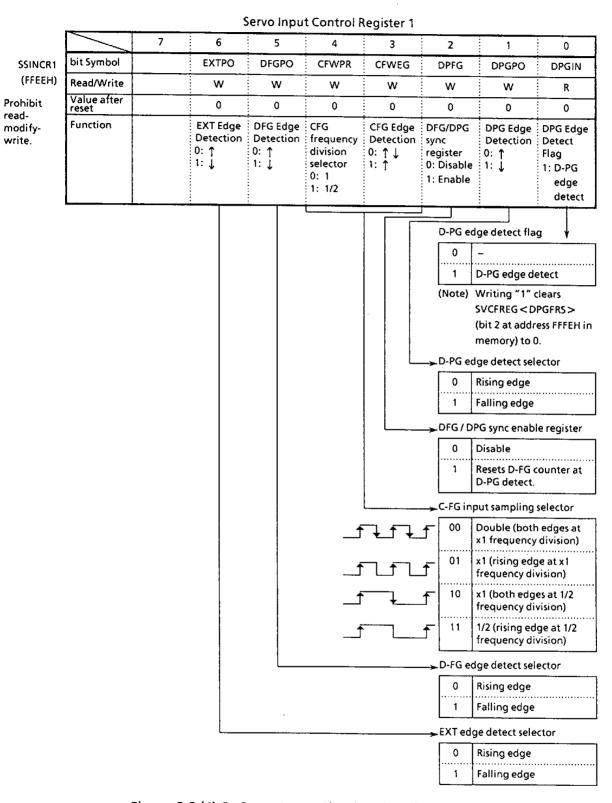

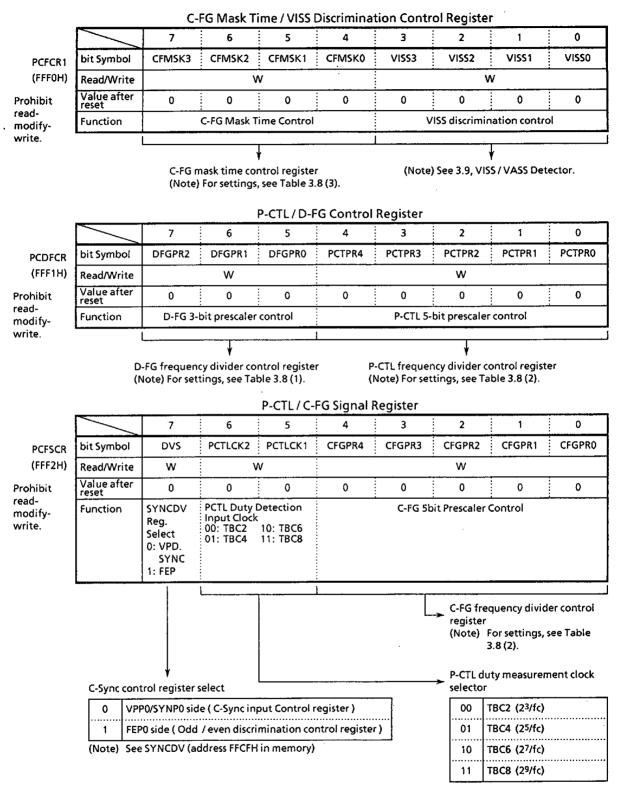

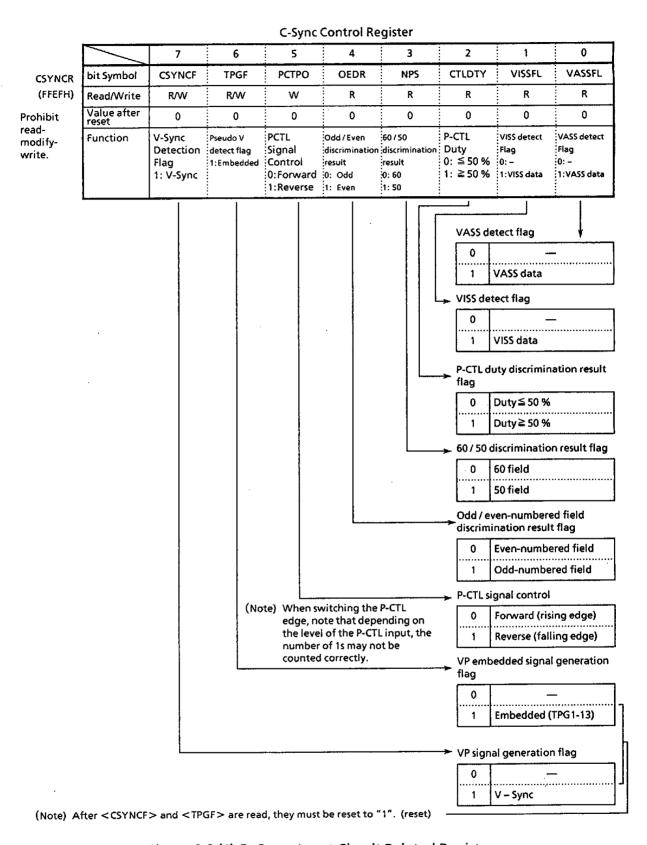

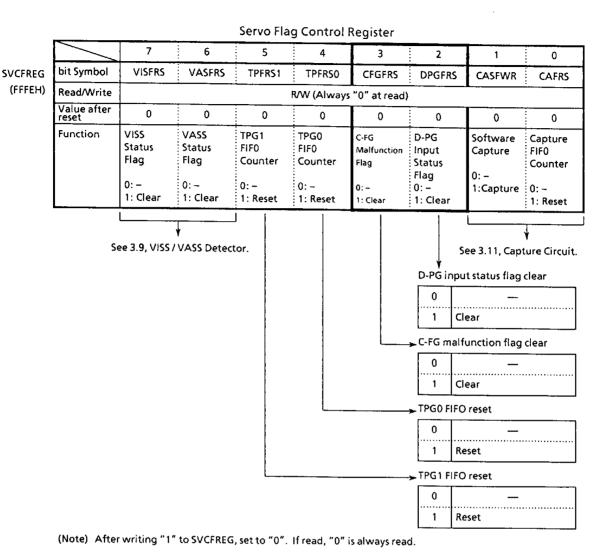

Edge detection of D-FG / D-PG is controlled by servo input control register SSINCR1<DFGPO, DPGPO> (bits 5 and 1 at address FFEEH in memory). The 3-bit programmable divider can set the frequency division ratio from 1 to 1/8 in the D-FG frequency divider control register, PCDFCR<DFGPR2 to 0> (bits 7 to 5 at address FFF1H in memory).

The frequency dividing counter is reset when a D-PG edge detect pulse is generated with SSINCR1 < DPFG > = 1. In the 1PG / FG method, this operation is used to divide the D-FG signal.

Table 3.8 (1) lists settings of the D-FG frequency divider control register and D-FG signal frequency division ratios.

Table 3.8 (1) Settings of D-FG Frequency Divider Control Register and D-FG Signal Frequency Division Ratios

| PCDFCR | <dfgpr< th=""><th>2 to 0 &gt;</th><th>D-FG input signal</th></dfgpr<> | 2 to 0 > | D-FG input signal                          |