# CMOS 16-Bit Microcontroller TMP93CF76/CF77/CW76/CU76/CT76

#### 1. Outline and Feature

TMP93CF76/CF77/CW76/CU76/CT76 are a high-speed advanced 16-bit microcontroller developed for application with VCR system control, software servo motor control, VFT driver and timer control.

In addition to basics such as I/O ports, the TMP93CF76/CF77/CW76/CU76/CU76 have highspeed/high-precision signal measuring circuit, PWM (Pulse-Width-Modulator) and high-precision real timing pulse generator.

The device characteristics are as follows:

- (1) Original 16-bit CPU (900/L CPU)

- TLCS-90 instruction mnemonic upward compatible

- 16 Mbyte linear address space •

- General-purpose registers and register bank system

- 16-bit multiplication/division and bit transfer/arithmetic instructions .

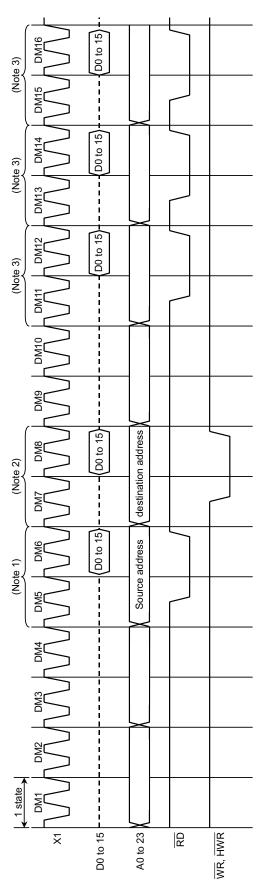

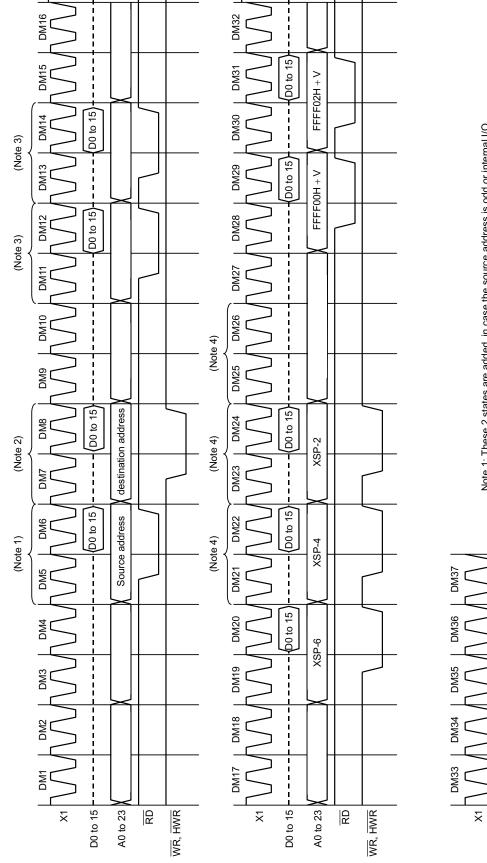

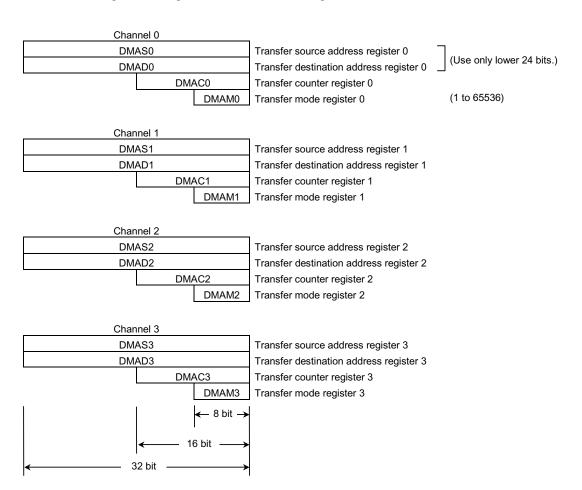

- High-speed micro DMA: 4 channels (2 µs/2 byte at 16 MHz)

- (2) Minimum instruction execution time: 250 ns at 16 MHz

- (3) Internal ROM:

| TMP93CF76 | 192 KB |

|-----------|--------|

| TMP93CF77 | 160 KB |

| TMP93CW76 | 128 KB |

| TMP93CU76 | 96 KB  |

| TMP93CT76 | 72 KB  |

#### (4) Internal RAM:

| TMP93CF76 | 4.0 KB |

|-----------|--------|

| TMP93CF77 | 4.0 KB |

| TMP93CW76 | 2.5 KB |

| TMP93CU76 | 2.5 KB |

| TMP93CT76 | 2.0 KB |

000707EBP1

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.. The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended for varianted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document

- shall be made at the customer's own risk. The products described in this document are subject to the foreign exchange and foreign trade laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.

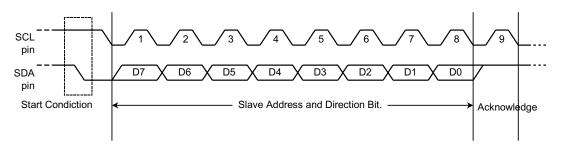

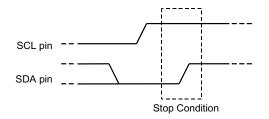

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

- (5) 20-bit time-base-counter (TBC)

- Free running counter

- Accuracy: 125 ns (at fc = 16 MHz)

- Overflow: 131 ms (at fc = 16 MHz)

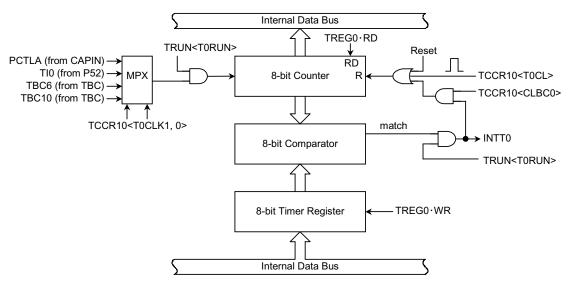

- (6) 8-bit timer (TC0): 1 channel

- For CTL linear time counter

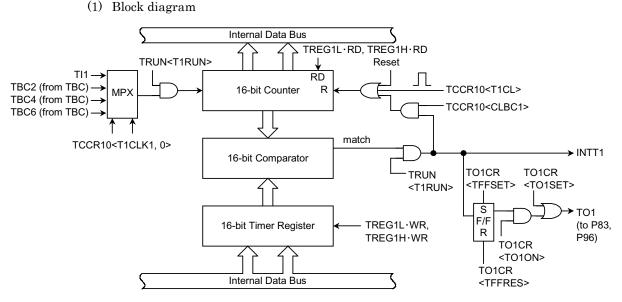

- (7) 16-bit timer (TC1 to 5): 5 channels

- C.sync count, capstan FG count, general: 3 channels

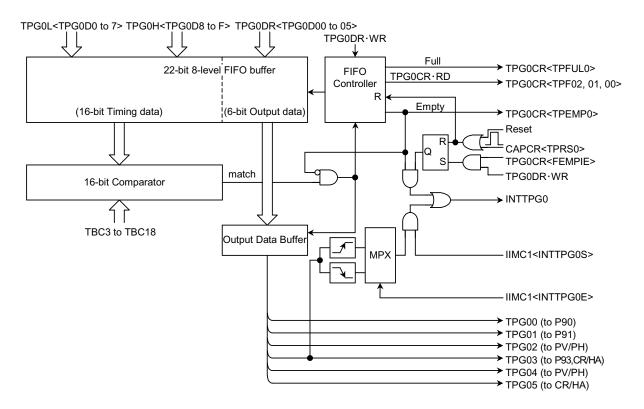

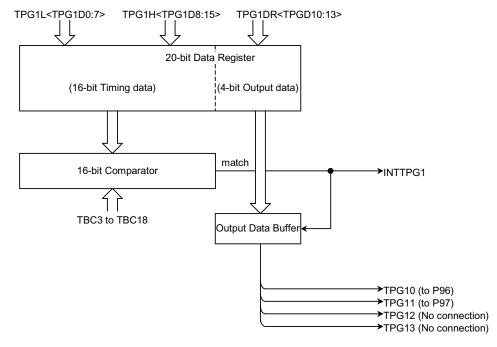

- (8) Timing pulse generator (TPG): 2 channels

- (16-bit timing data + 6-bit output data) with 8-stages FIFO : 1 channel

- (16-bit timing data + 4-bit output data) :1 channel

- Accuracy: 500 ns (at 16 MHz)

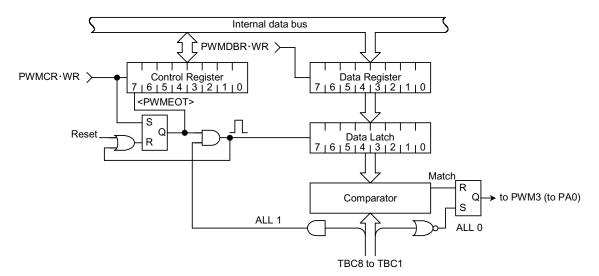

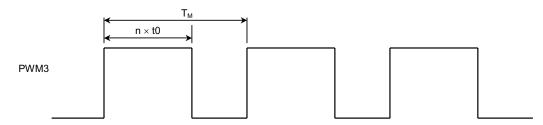

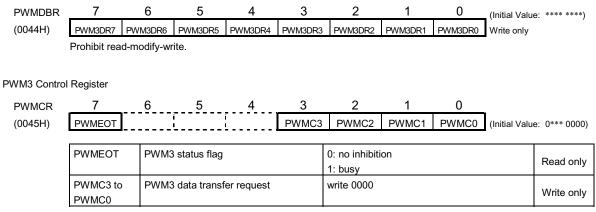

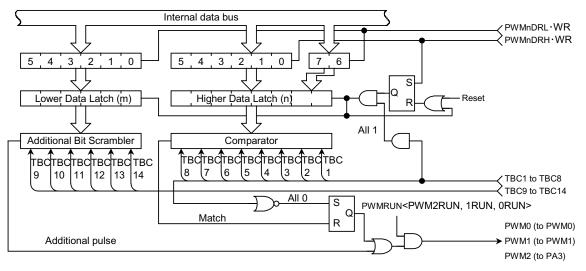

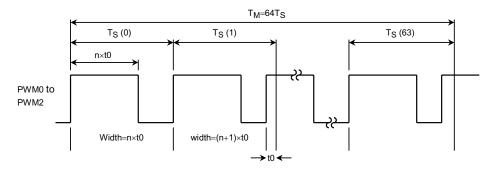

- (9) Pulse width modulation outputs (PWM)

- 14-bit PWM: 3 channels (for controlling capstan, drum and tuner)

- 8-bit PWM: 1 channel (for controlling volume)

- Carrier frequency: 31.25 kHz (at 16 MHz)

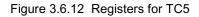

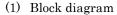

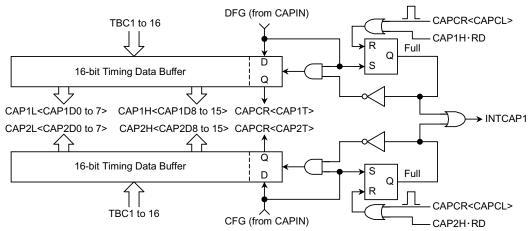

- (10) 24-bit time base counter capture circuit (Capture 0)

- (18-bit timing data + 6 bit trigger data) with 8-stages FIFO: 1 channel

- Capture input sources: Remote-control-input (RMTIN), V.sync, CTL, Drum-PG, general (1 channel)

- Accuracy: 500 ns (at 16 MHz)

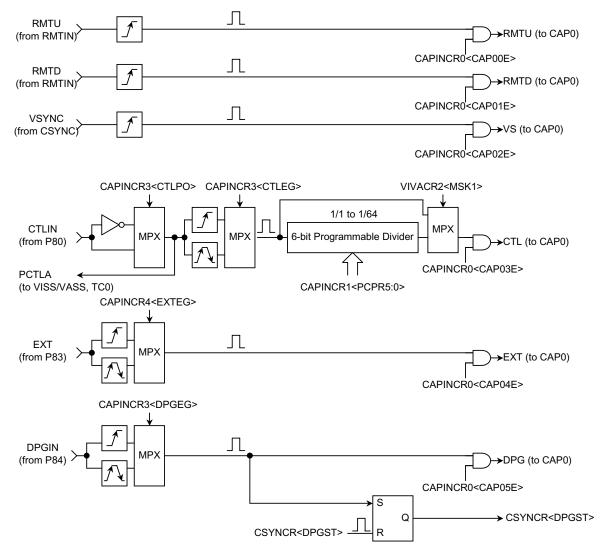

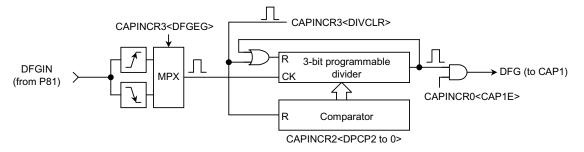

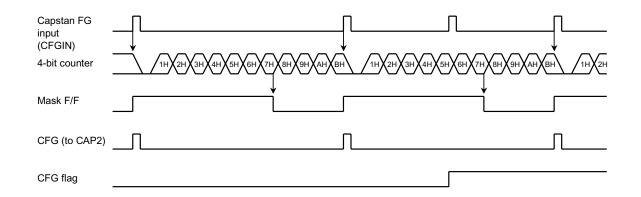

- (11) 17-bit time base counter capture circuit (Capture 1/2)

- (16-bit timing data + 1-bit trigger data): 2 channels

- Capture input sources: Drum-FG, Capstan-FG

- Accuracy: 125 ns (at 16 MHz)

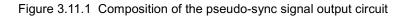

- (12) VISS/VASS detection circuit (VISS/VASS)

- CTL duty detection

- VASS data 16-bit latch

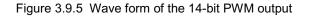

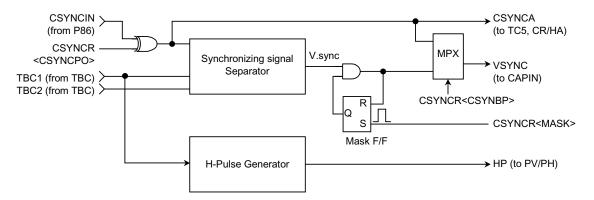

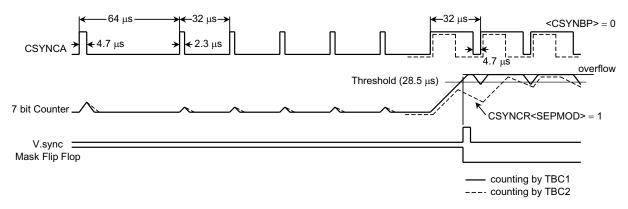

- (13) Composite-sync-signal (C.sync) input

- Vertical-sync-signal (V.sync) separation

- Horizontal-sync-signal (H.sync) separation

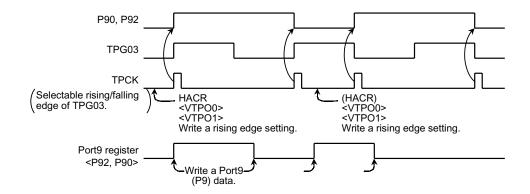

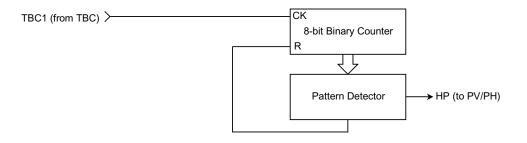

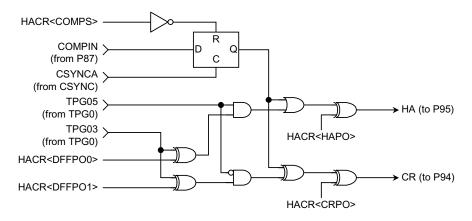

- (14) Head Amp switch/Color Rotary control (HA/CR)

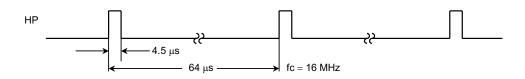

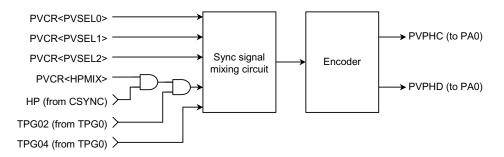

- (15) Pseudo-V/H generator (PV/PH)

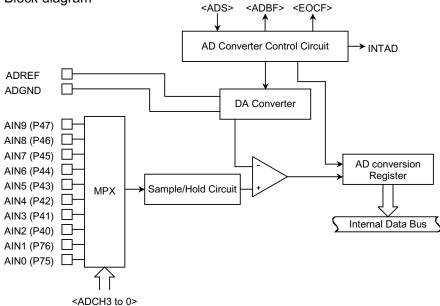

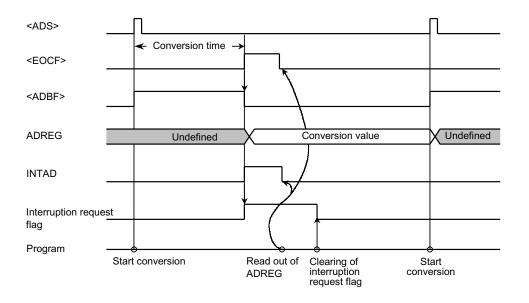

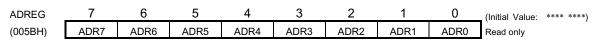

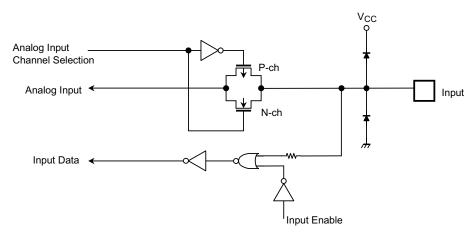

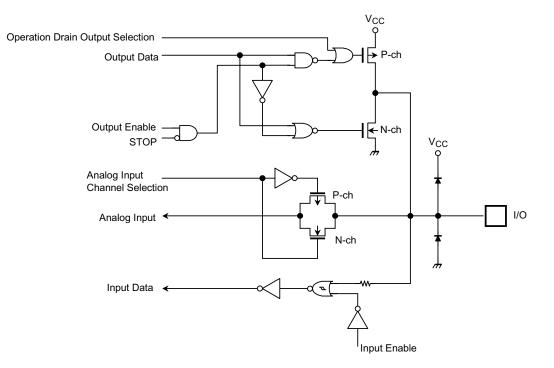

- (16) 8-bit AD converter (ADC): 10 channels

- Conversion speed: 95 states (11.8 µs at 16 MHz)

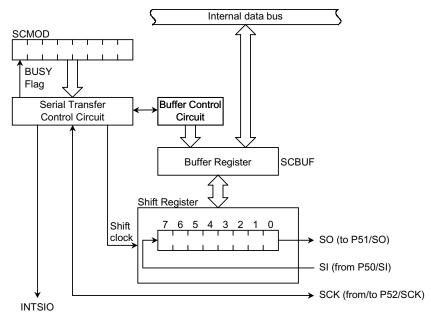

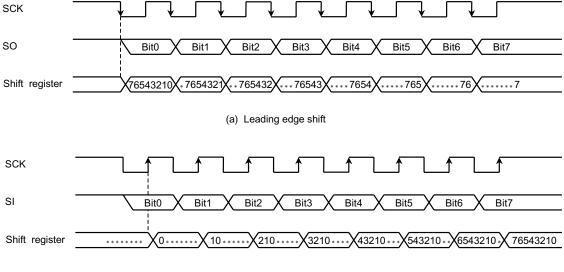

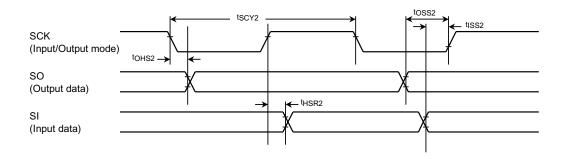

- (17) Serial Channel (SIO): 1channel

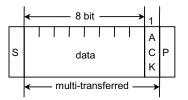

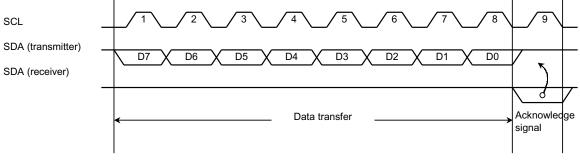

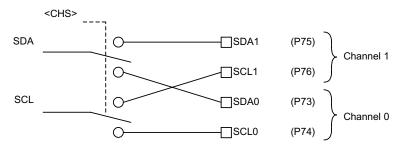

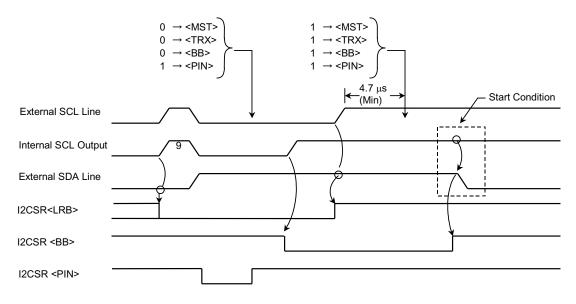

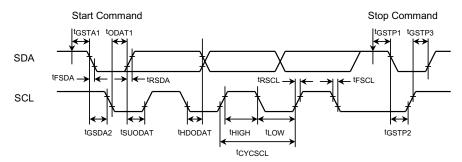

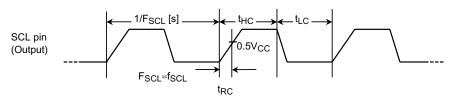

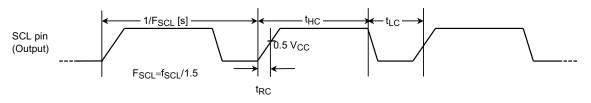

- (18) Serial bus I/F

- I<sup>2</sup>C bus with 8-stages FIFO: 1 channel/2 ports

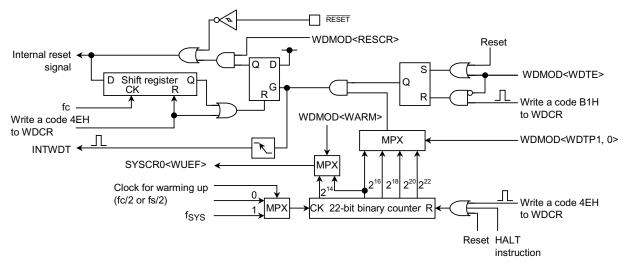

- (19) Watch dog timer (WDT)

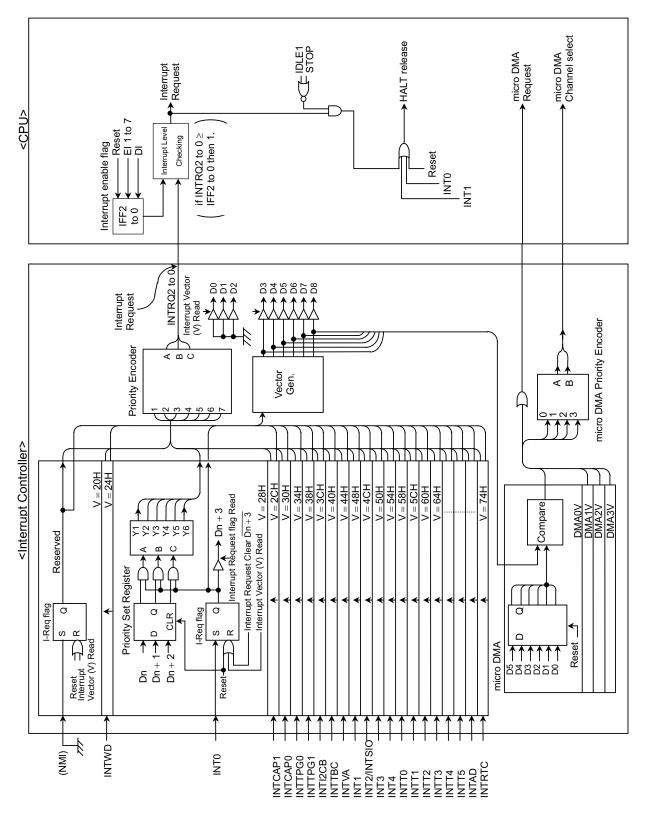

(20) Interrupt controller (INTC)

- CPU: 8 sources  $\rightarrow$  SWI instruction and illegal instruction

- Internal: 17 sources 7-level priority can be set.

- External: 5 sources

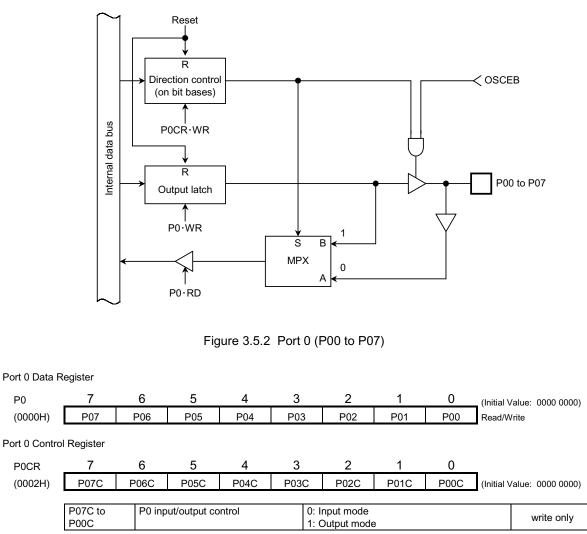

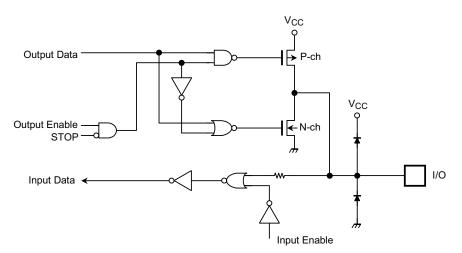

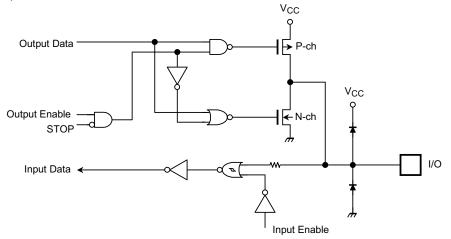

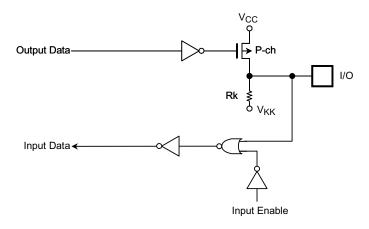

- (21) I/O ports

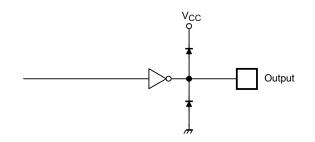

- 67 I/O ports (multiplexed functional pins.) High Break Down Voltage PortE, F are Included: 14 I/O ports

- 8 input ports (P40/AIN2 to P47/AIN9)

- 10 output ports PC0/G0 to PC7/G7, PD0/G8 to PD1/G9: High Break Down Voltage

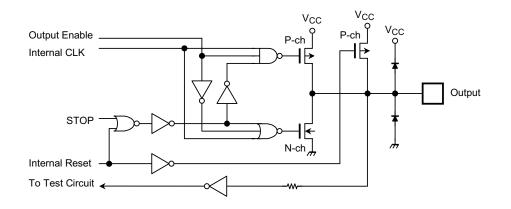

(22) Standby function: 4 halt modes (RUN, IDLE2, IDLE1, STOP)

(23) System clock function

Dual clock operation 16 MHz (High-speed: normal)/32 kHz (Low-speed:slow)

… 17-bit Real Time Counter built in

(24) Operating Voltage

- Vcc = 2.7 to 5.5 V (at 32 kHz)

- Vcc = 4.5 to 5.5 V (at 16 MHz)

(25) Package

- 100 pin QFP 14 mm × 20 mm (Pin pitch: 0.65 mm)

- Product name: P-QFP100-1420-0.65A

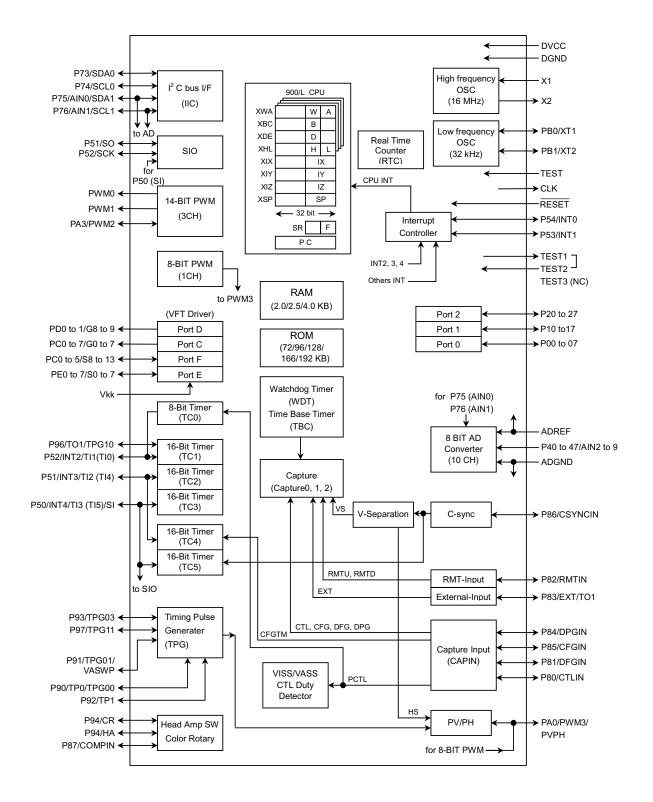

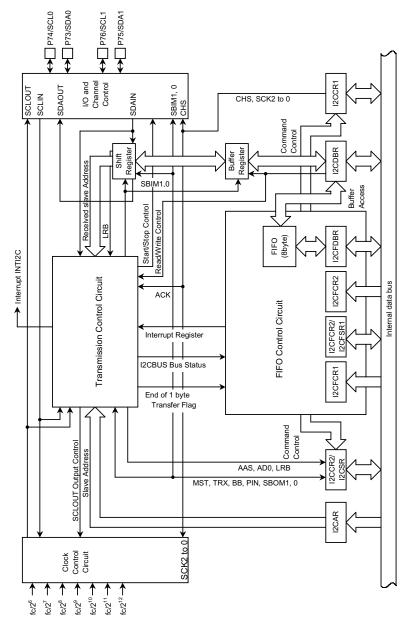

Figure 1.1 TMP93CF76/CF77/CW76/CU76/CT76 block diagram

# 2. Pin Assignment and Functions

The assignment of input and output pins for the TMP93CF76/CF77/CW76/CU76/CT76, their names and functions are described below.

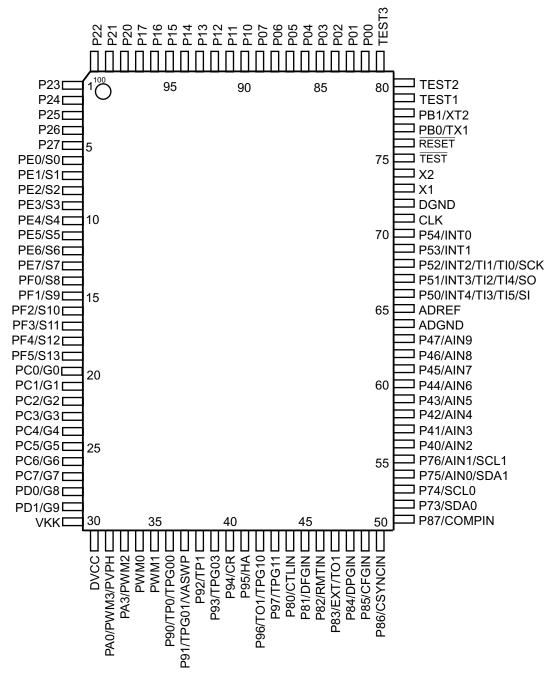

### 2.1 Pin Assignment

Figure 2.1.1 shows pin assignment of the TMP93CF76/CF77/CW76/CU76/CT76.

Figure 2.1.1 Pin assignment (100-pin QFP)

# 2.2 Pin Names and Functions

The names of input/output pins and their functions are described below.

| Pin name     | Number<br>of pins | I/O    | Functions                                                                     |

|--------------|-------------------|--------|-------------------------------------------------------------------------------|

| P00 to P07   | 8                 | I/O    | port0: I/O ports                                                              |

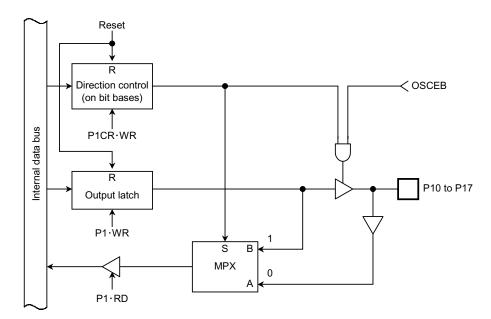

| P10 to P17   | 8                 | I/O    | port1: I/O ports                                                              |

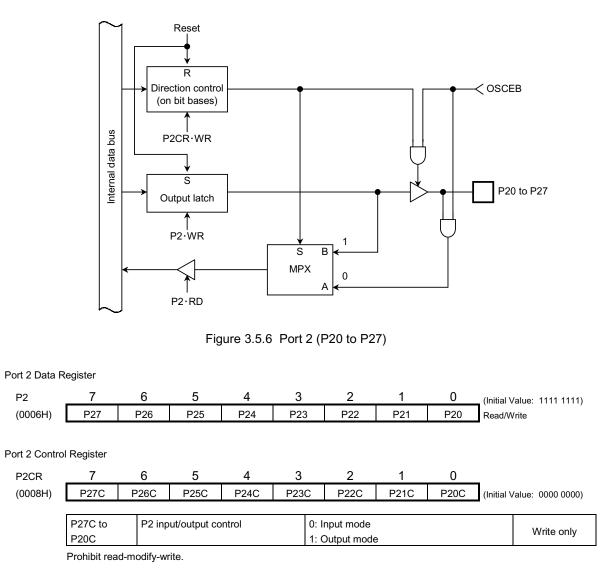

| P20 to P27   | 8                 | I/O    | port2: I/O ports                                                              |

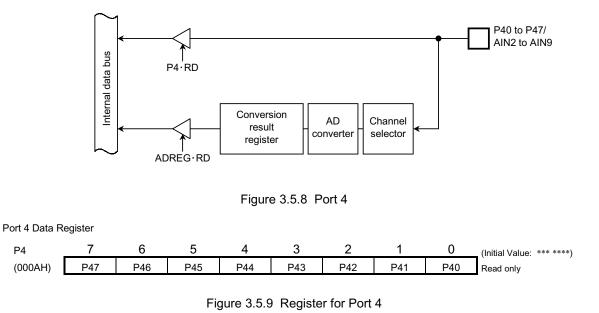

| P40 to P47   | 8                 | Input  | port4: Input ports                                                            |

| AIN2 to AIN9 |                   | Input  | Analog input: Input to AD converter                                           |

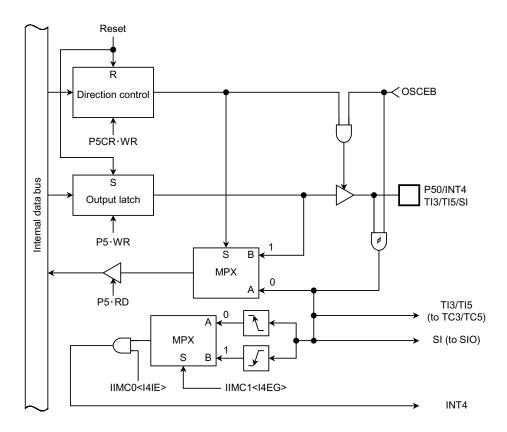

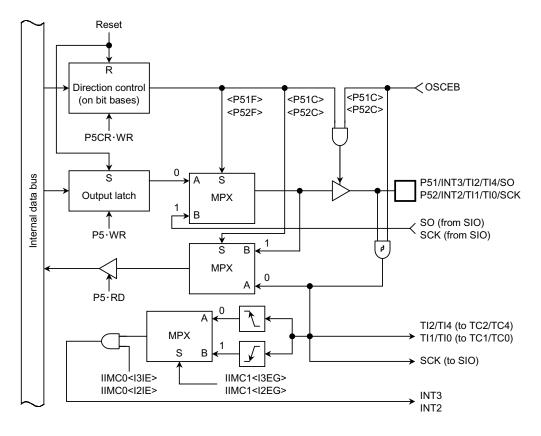

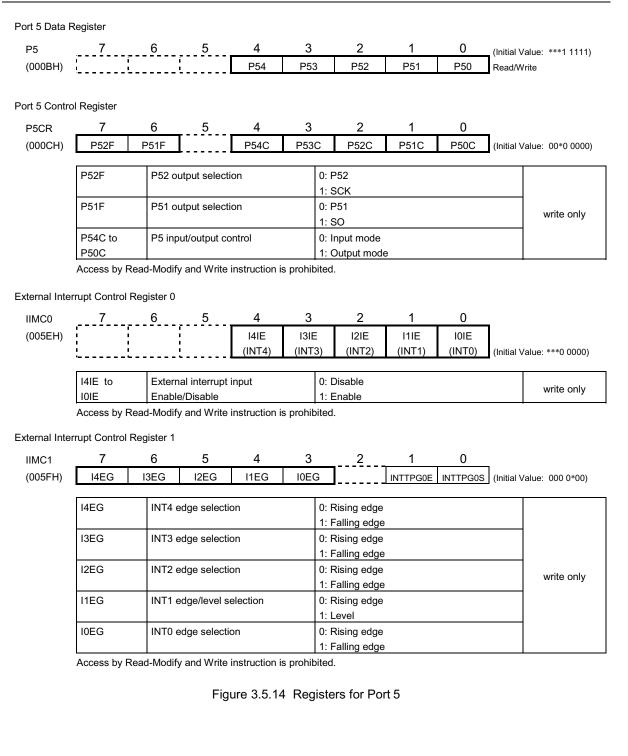

| P50          | 1                 | I/O    | Port50: I/O port (schmitt input)                                              |

| INT4         |                   | Input  | External Interrupt request input 4: Rising edge/Falling edge programable      |

| TI3          |                   | Input  | 16-bit timer3 (TC3) Input 3                                                   |

| TI5          |                   | Input  | 16-bit timer5 (TC5) input 5                                                   |

| SI           |                   | Input  | SIO received data                                                             |

| P51          | 1                 | I/O    | Port51: I/O port (schmitt input)                                              |

| INT3         |                   | Input  | External Interrupt request input 3: Rising edge/Falling edge programable      |

| TI2          |                   | Input  | 16-bit timer2 (TC2): Input 2                                                  |

| TI4          |                   | Input  | 16-bit timer4 (TC4): input 4                                                  |

| SO           |                   | Output | SIO sending data                                                              |

| P52          | 1                 | I/O    | Port52: I/O port (schmitt input)                                              |

| INT2         |                   | Input  | External Interrupt request input 2: Rising edge/Falling edge programable      |

| TI1          |                   | Input  | 16-bit timer1 (TC1) Input 1                                                   |

| TIO          |                   | Input  | 8-bit Timer0 (TC0) Input 0                                                    |

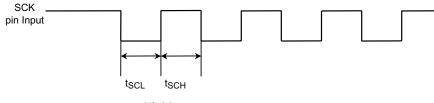

| SCK          |                   | I/O    | SIO clock line                                                                |

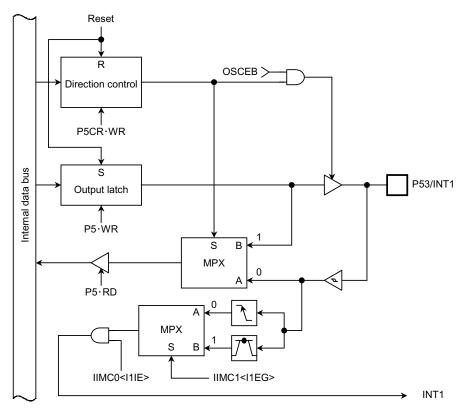

| P53          | 1                 | I/O    | Port53: I/O port (schmitt input)                                              |

| INT1         |                   | Input  | External Interrupt request pin1: Rising edge/Level programable                |

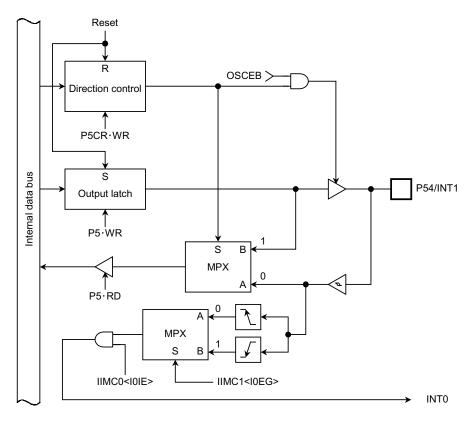

| P54          | 1                 | I/O    | Port54: I/O port (schmitt input)                                              |

| INTO         |                   | Input  | External Interrupt request pin0: Rising edge/Falling edge programable         |

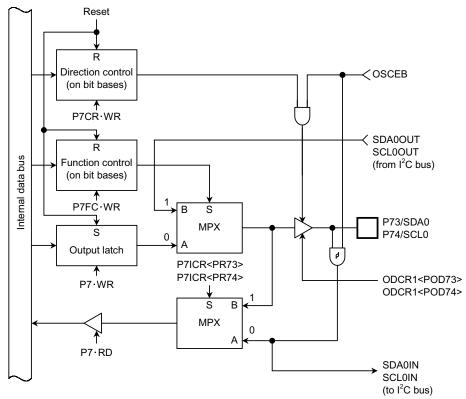

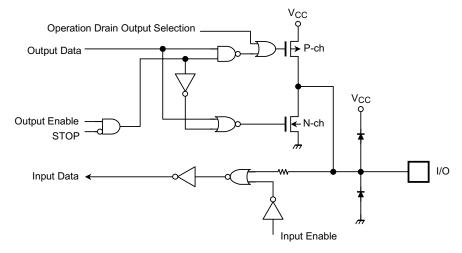

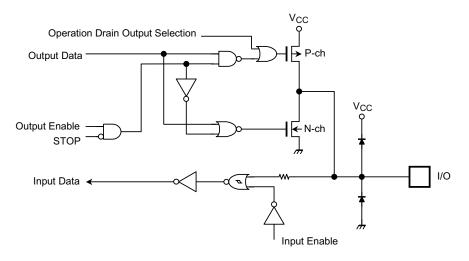

| P73          | 1                 | I/O    | Port73: I/O port (schmitt input, Push-pull or open-drain output selectable)   |

| SDA0         |                   | I/O    | I <sup>2</sup> C bus SDA0 line                                                |

| P74          | 1                 | I/O    | Port74: I/O port (schmitt input, Push-pull or open-drain output selectable)   |

| SCL0         |                   | I/O    | I <sup>2</sup> C bus SCL0 line                                                |

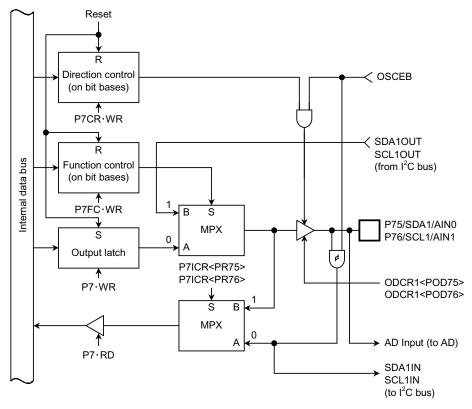

| P75          | 1                 | I/O    | Port75: I/O port (schmitt input, Push-pull or open-drain output selectable)   |

| SDA1         |                   | I/O    | I <sup>2</sup> C bus SDA1 line                                                |

| AIN0         |                   | Input  | Analog input 0: Analog input signal for AD converter                          |

| P76          | 1                 | I/O    | Port76: Input port (schmitt input, Push-pull or open-drain output selectable) |

| SCL1         |                   | I/O    | I <sup>2</sup> C bus SCL1 line                                                |

| AIN1         |                   | Input  | Analog input 1: Analog input signal for AD converter                          |

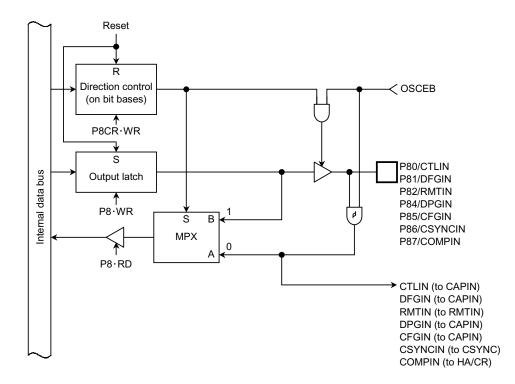

| P80          | 1                 | I/O    | Port80: I/O port (schmitt input)                                              |

| CTLIN        |                   | Input  | CTL Capture input (Capture 0)                                                 |

| P81          | 1                 | I/O    | Port81: I/O port (schmitt input)                                              |

| DFGIN        |                   | Input  | DFG Capture input (Capture 1)                                                 |

| Table 2.2.1 Pin names and funct |

|---------------------------------|

|---------------------------------|

|          | Number  |        |                                                              |

|----------|---------|--------|--------------------------------------------------------------|

| Pin name | of pins | I/O    | Functions                                                    |

| P82      | . 1     | I/O    | Port82: I/O port (schmitt input)                             |

| RMTIN    |         | Input  | Remote Control Signal Capture input                          |

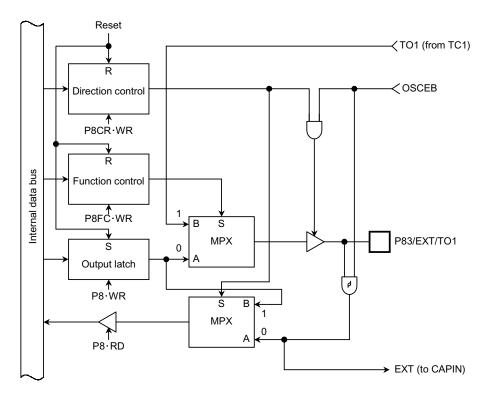

| P83      | 1       | I/O    | Port83: I/O port (schmitt input)                             |

| EXT      |         | Input  | External Capture input (Capture 0)                           |

| TO1      |         | Output | Timer Out 1                                                  |

| P84      | 1       | 1/O    | Port84: I/O port (schmitt input)                             |

| DPGIN    |         | Input  | DPG Capture input (Capture 0)                                |

| P85      | 1       | I/O    | Port85: I/O port (schmitt input)                             |

| CFGIN    |         | Input  | CFG Capture input (Capture 2)                                |

| P86      | 1       | I/O    | Port86: I/O port (schmitt input)                             |

| CSYNCIN  |         | Input  | C.sync Capture input                                         |

| P87      | 1       | I/O    | Port87: I/O port (schmitt input)                             |

| COMPIN   |         | Input  | Envelope Comparate Input (to HA/CR)                          |

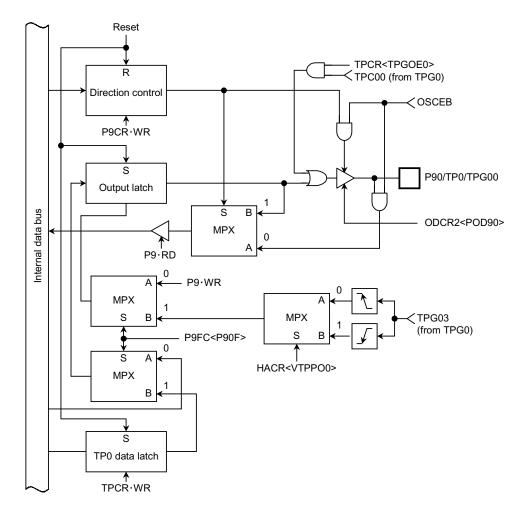

| P90      | 1       | I/O    | Port90: I/O port (Push-pull or open-drain output selectable) |

| TP0      |         | Output | Timing Pulse output 0                                        |

| TPG00    |         | Output | TPG00: TPG0 output                                           |

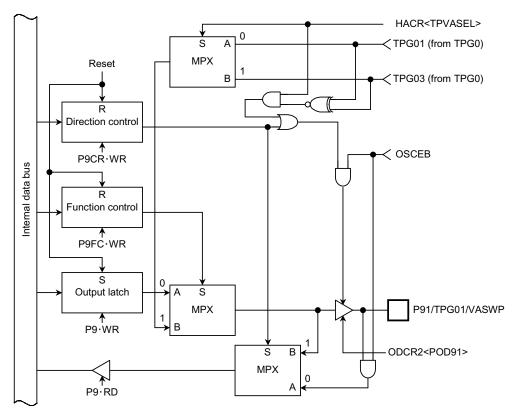

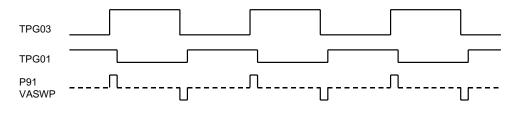

| P91      | 1       | I/O    | Port91: I/O port (Push-pull or open-drain output selectable) |

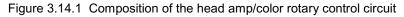

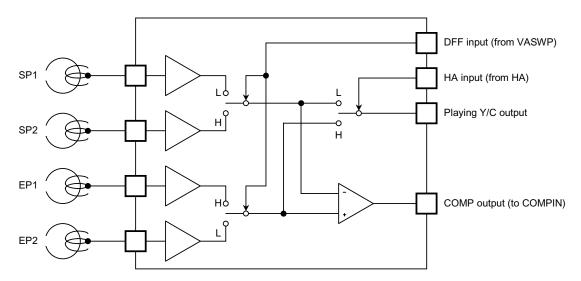

| VASWP    |         | Output | Video/Audio head switching control signal output             |

| TPG01    |         | Output | TPG01: TPG0 output                                           |

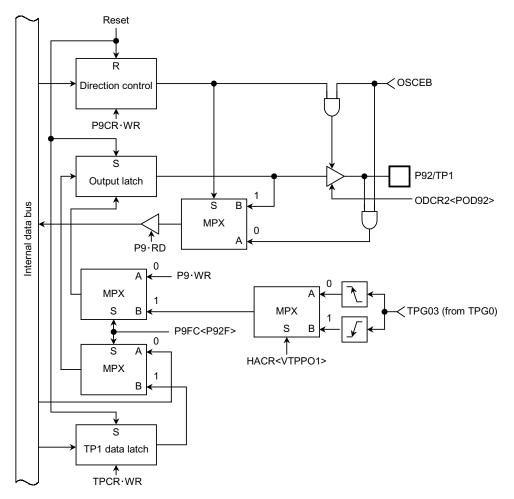

| P92      | 1       | I/O    | Port92: I/O port (Push-pull or open-drain output selectable) |

| TP1      |         | Output | Timing Pulse output 1                                        |

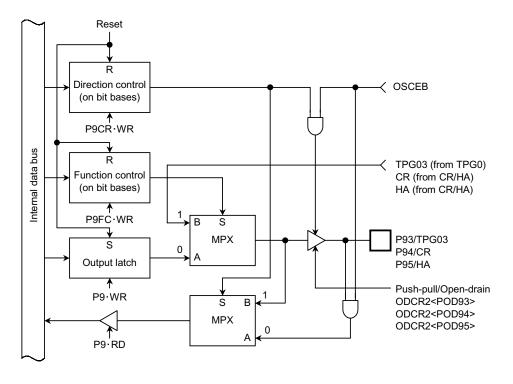

| P93      | 1       | I/O    | Port93: I/O port (Push-pull or open-drain output selectable) |

| TPG03    |         | Output | TPG03: TPG0 output                                           |

| P94      | 1       | I/O    | Port94: I/O port (Push-pull or open-drain output selectable) |

| CR       |         | Output | Color Rotary Output                                          |

| P95      | 1       | I/O    | Port95: I/O port (Push-pull or open-drain output selectable) |

| НА       |         | Output | Head Amp Switching Control Output                            |

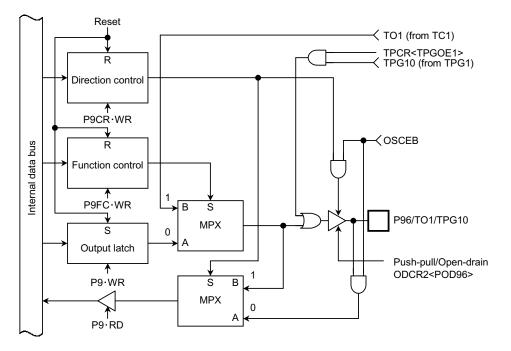

| P96      | 1       | I/O    | Port96: I/O port (Push-pull or open-drain output selectable) |

| TO1      |         | Output | Timer Out 1                                                  |

| TPG10    |         | Output | TPG10: TPG1 output                                           |

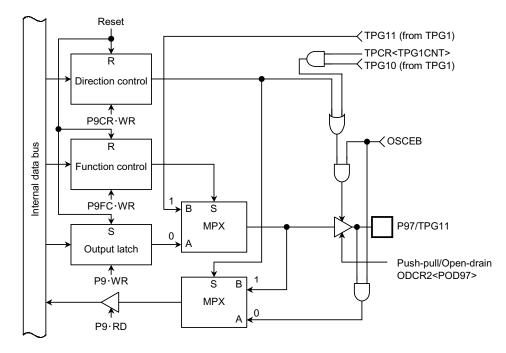

| P97      | 1       | I/O    | Port97: I/O port (Push-pull or open-drain output selectable) |

| TPG11    |         | Output | TPG11: TPG1 output                                           |

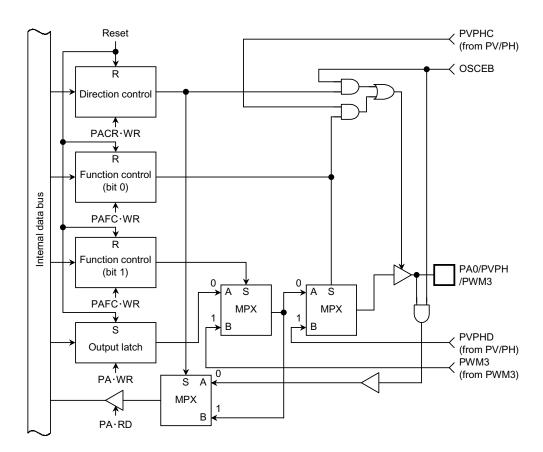

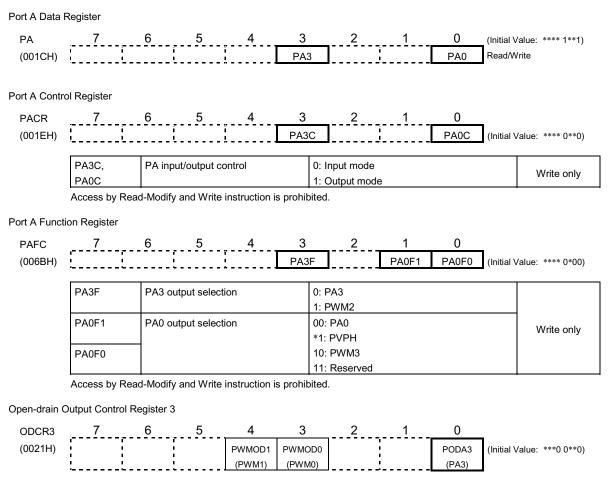

| PA0      | 1       | I/O    | PortA0: I/O port                                             |

| PVPH     |         | Output | PVPH 3-state Output                                          |

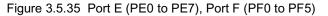

| PWM3     |         | Output | PWM(8 bits) output 3                                         |

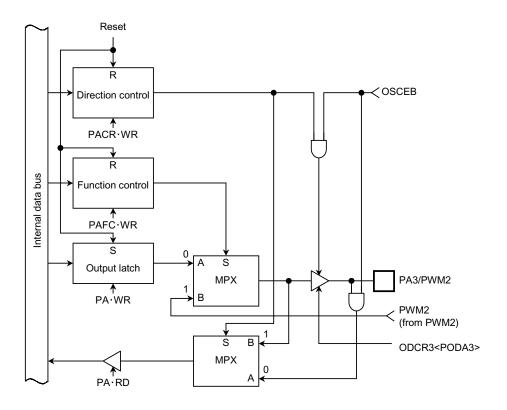

| PA3      | 1       | I/O    | PortA3: I/O port (Push-pull or open-drain output selectable) |

| PWM2     |         | Output | PWM(14 bits) output 2                                        |

| Table 2.2.1 | Pin | names a  | and  | function | (2/3)        |

|-------------|-----|----------|------|----------|--------------|

|             |     | mannoo c | anna | lanouoli | $(-, \circ)$ |

| Pin name   | Number<br>of pins | I/O    | Functions                                                                  |

|------------|-------------------|--------|----------------------------------------------------------------------------|

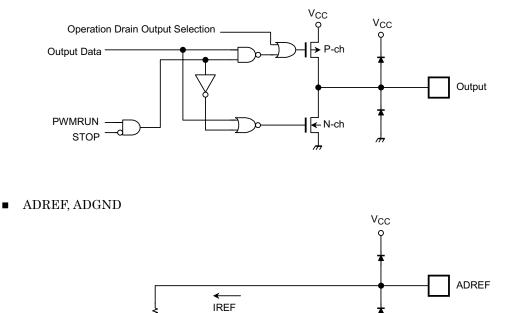

| PWM0       | 1                 | Output | PWM(14 bits) output 0 (Push-pull or open-drain output selectable)          |

| PWM1       | 1                 | Output | PWM(14 bits) output 1 (Push-pull or open-drain output selectable)          |

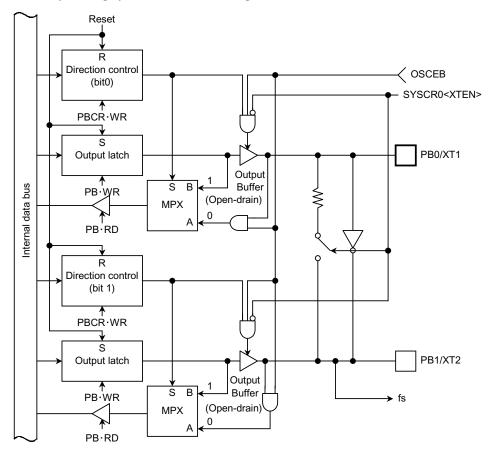

| PB0        | 1                 | I/O    | PortB0: I/O port (Open-drain Output)                                       |

| XT1        |                   | Input  | Low Frequency Oscillator connecting pin                                    |

| PB1        | 1                 | I/O    | PortB1: I/O port (Open-drain Output)                                       |

| XT2        |                   | Output | Low Frequency Oscillator connecting pin                                    |

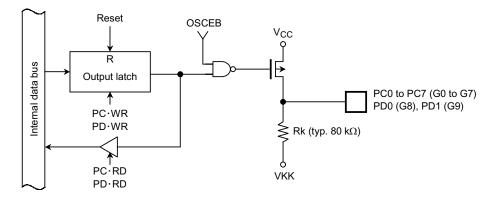

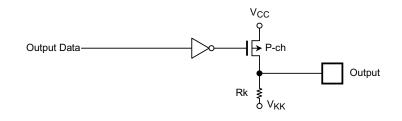

| PC0 to PC7 | 8                 | Output | PortC: Output (High break down voltage outputs with pull-down resistor)    |

| G0 to G7   |                   | Output | Grid Drivers                                                               |

| PD0,1      | 2                 | Output | PortD: Output (High break down voltage outputs with pull-down resistor)    |

| G8, 9      |                   | Output | Grid Drivers                                                               |

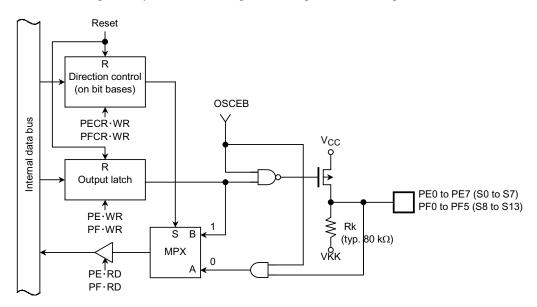

| PE0 to PE7 | 8                 | I/O    | PortE: I/O ports (High break down voltage outputs with pull-down resistor) |

| S0 to S7   |                   | Output | Segment Drivers                                                            |

| PF0 to PF5 | 6                 | I/O    | PortF: I/O ports (High break down voltage outputs with pull-down resistor) |

| S8 to S13  |                   | Output | Segment Drivers                                                            |

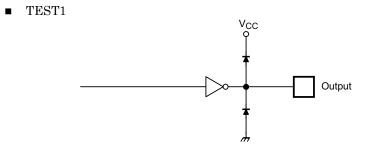

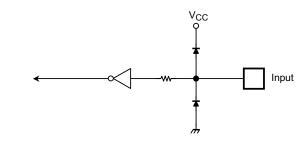

| TEST1      | 1                 | Output | TECT4 should be connected with TECT2 pin                                   |

| TEST2      | 1                 | Input  | TEST1 should be connected with TEST2 pin.                                  |

| TEST3(NC)  | 1                 | Output | TEST3 should be open connection.                                           |

| CLK        | 1                 | Output | Clock output: Output (System Clock ÷ 2) clock.                             |

|            |                   |        | Pulled-up during reset.                                                    |

|            |                   |        | Can be set to output disable for reducing noise. (Initial Disable)         |

| TEST       | 1                 | Input  | Test pin: Always set to "Vcc" level                                        |

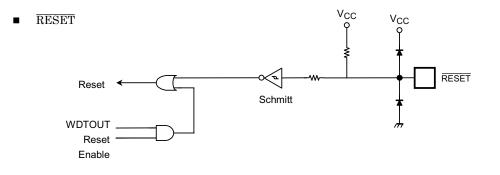

| RESET      | 1                 | Input  | Reset: Initializes LSI. (with pull-up resistor)                            |

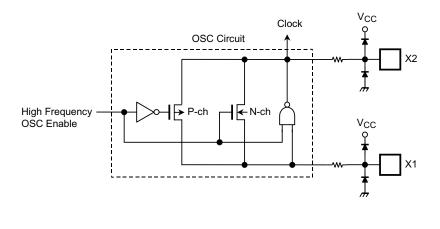

| X1         | 1                 | Input  | High Frequency Oscillator connecting pins (16 MHz)                         |

| X2         | 1                 | Output | High Frequency Oscillator connecting pins (16 MHz)                         |

| VKK        | 1                 |        | VFT Driver power supply pin                                                |

| DVCC       | 1                 |        | Power supply pin                                                           |

| DGND       | 1                 |        | GND pin (0 V)                                                              |

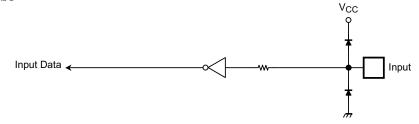

| ADREF      | 1                 |        | Reference voltage input for AD converter                                   |

| ADGND      | 1                 |        | GND pin for AD converter                                                   |

Table 2.2.1 Pin names and function (3/3)

# 3. Operation

This section describes the functions and basic operational blocks of TMP93CF76/CF77/CW76/CU76/CT76 devices.

See the "7. Points of Concern and Restrictions" for the using notice and restrictions for each block.

### 3.1 CPU

TMP93CF76/CF77/CW76/CU76/CT76 devices have a built-in high-performance 16-bit CPU (900/L CPU). (For CPU operation, see TLCS-900/L CPU in the previous section).

This section describes CPU functions unique to the TMP93CF76/CF77/CW76/CU76/CT76 that are not described in the previous section.

#### 3.1.1 Reset

To reset the TMP93CF76/CF77/CW76/CU76/CT76, the RESET input must be kept at 0 for at least 10 system clocks. (1.25  $\mu s$  at 16 MHz) within the operating voltage range and with a stable oscillation.

When reset is accepted, the CPU sets as follows:

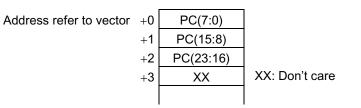

• Program Counter (PC) according to Reset Vector that is stored FFFF00H to FFFF02H.

| PC (7:0)   | $\leftarrow$ stored data in location FFFF00H |

|------------|----------------------------------------------|

| PC (15:8)  | $\leftarrow$ stored data in location FFFF01H |

| PC (23:16) | $\leftarrow$ stored data in location FFFF02H |

- Stack pointer (XSP) for system mode to 100H.

- IFF2 to 0 bits of status register to 111. (Sets mask register to interrupt level 7.)

- MAX bit of status register to 1. (Sets to maximum mode)

- Bits RFP2 to 0 of status register to 000. (Sets register banks to 0.)

When reset is released, instruction execution starts from PC (reset vector). CPU internal registers other than the above are not changed.

When reset is accepted, processing for built-in I/Os, ports, and other pins is as follows

- Initializes built-in I/O registers as per specifications.

- Sets port pins (including pins also used as built-in I/Os) to general-purpose input/output port mode.

- Note: By resetting, register in the CPU except program counter (PC), status register (SR) and stack pointer (XSP) and the data in internal RAM are not changed.

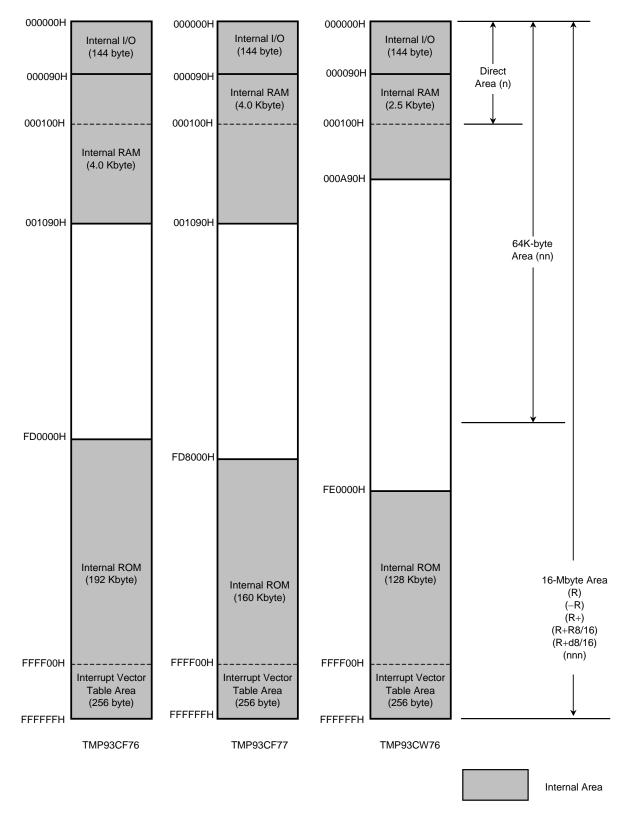

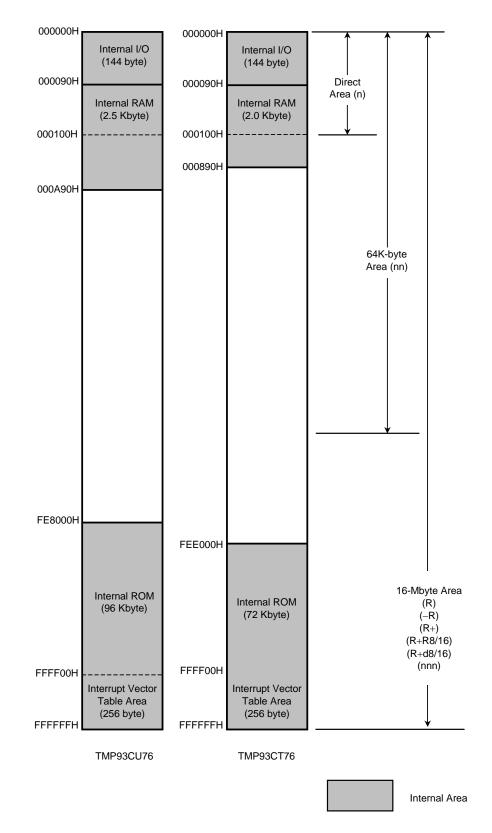

### 3.2 Memory Map

Figure 3.2.1 is a memory map of the TMP93CF76/CF77/CW76/CU76/CT76.

Figure 3.2.1 Memory map (1/2)

Figure 3.2.1 Memory map (2/2)

### 3.3 Dual Clock, Standby Function

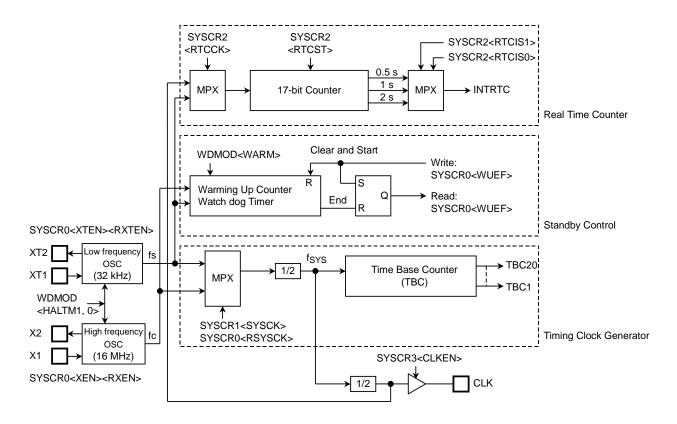

Dual Clock, Stand by Control Circuits consist of System clock Controller, Timing clock Generator for I/O Block, Real Time Clock Generator, and Standby Controller.

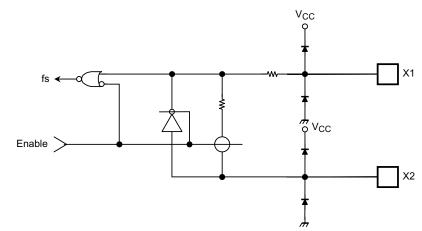

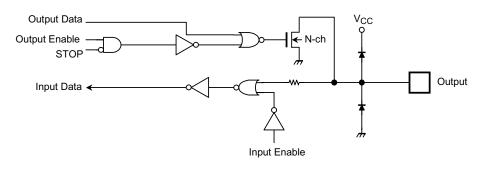

The Oscillator operating mode is classified to Single Clock mode (only X1, X2 pin) and Dual Clock mode (X1, X2, XT1, XT2 pin).

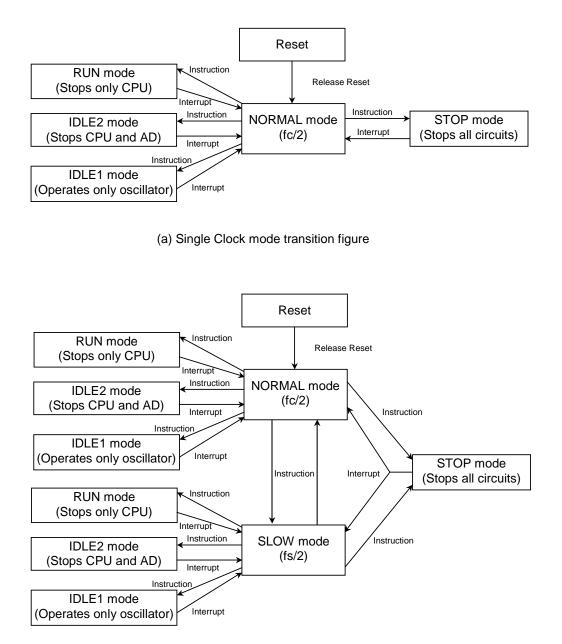

Figure 3.3.1 shows a transition figure. Figure 3.3.2 shows the block diagram.

Figure 3.3.3 shows I/O registers. Table 3.3.1 shows the internal operation and system clock.

(b) Dual Clock mode transition figure

Figure 3.3.1 Transition figure

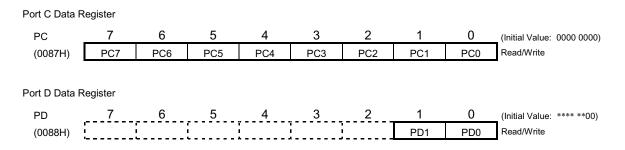

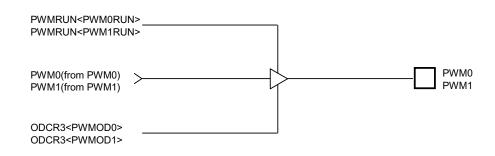

The clock frequency input from X1, X2 pin is called fc, and the clock frequency input from XT1, XT2 pin is called fs. The clock frequency selected by SYSCR1<SYSCK> is called system clock  $f_{FPH}$ . The devided clock of  $f_{FPH}$  is called system clock  $f_{SYS}$ , and the 1 cycle of  $f_{SYS}$  is called 1 state.

| Operating       |        | Oscillator                                            |                            |         |              | System clock                |

|-----------------|--------|-------------------------------------------------------|----------------------------|---------|--------------|-----------------------------|

| •               | /lode  | High                                                  | Low                        | CPU     | Internal I/O | -                           |

|                 | NOUE   | Frequency (fc)                                        | Frequency (fs)             |         |              | fsys                        |

|                 | RESET  |                                                       |                            | Reset   | Reset        |                             |

|                 | NORMAL |                                                       |                            | Operate | Operate      |                             |

| Single<br>Clock | RUN    | Oscillation                                           | Stop                       |         | Operate      | fc/2                        |

|                 | IDLE2  |                                                       |                            | Stop    | Stop only AD |                             |

|                 | IDLE1  |                                                       |                            |         | Stop         |                             |

|                 | STOP   | Stop                                                  |                            |         |              | Stop                        |

|                 | RESET  | Oscillation                                           | Stop                       | Reset   | Reset        | fc/2                        |

|                 | NORMAL | Oscillation                                           | Progamable                 | Operate |              | IC/Z                        |

| Dual            | SLOW   | Programable                                           | Oscillation                | Operate | Operate      | fs/2                        |

| Dual<br>Clock   | RUN    | Oscillator being used as system<br>clock: oscillation |                            |         |              |                             |

|                 | IDLE2  |                                                       |                            | Stop    | Stop only AD | Programable<br>(fc/2, fs/2) |

|                 | IDLE1  | Other oscillator: pre                                 | r oscillator: programmable |         | Stop         | (10/2, 15/2)                |

|                 | STOP   | Stop                                                  |                            |         | Stop         | Stop                        |

| Table 3.3.1 | Internal | operation | and system | clock |

|-------------|----------|-----------|------------|-------|

|-------------|----------|-----------|------------|-------|

Note: The TMP93CF76/CF77/CW76/CU76/CT76 does not have a clock gear circuit.

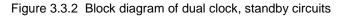

System Clock Control Register 0

| SYSCR0  | 7   | 6    | 5    | 4     | 3      | 2    | 1 | 0 | _                          |

|---------|-----|------|------|-------|--------|------|---|---|----------------------------|

| (006EH) | XEN | XTEN | RXEN | RXTEN | RSYSCK | WUEF |   |   | (Initial Value: 1010 00**) |

|         |     |      |      |       |        |      |   |   |                            |

| XEN    | High Frequency oscillator (fc)       | 0: Stop              |       |

|--------|--------------------------------------|----------------------|-------|

|        |                                      | 1: Oscillation       |       |

| XTEN   | Low Frequency oscillator (fs)        | 0: Stop              |       |

|        |                                      | 1: Oscillation       |       |

| RXEN   | High Frequency oscillator (fc) after | 0: Stop              |       |

|        | released STOP mode                   | 1: Oscillation       |       |

| RXTEN  | Low Frequency oscillator (fs) after  | 0: Stop              |       |

|        | released STOP mode                   | 1: Oscillation       | R/W   |

| RSYSCK | Clock selection after released       | 0: fc                | 10,00 |

|        | STOP mode                            | 1: fs                |       |

| WUEF   | Warm-Up Timer                        | (READ)               |       |

|        |                                      | 0: End warmming-up   |       |

|        |                                      | 1: Under warmming-up |       |

|        |                                      | (WRITE)              |       |

|        |                                      | 0: Don't care        |       |

|        |                                      | 1: Timer start       |       |

Note: The bit 1 to 0 are always read out as 1.

System Clock Control Register 1

SYSCR1

7

6

5

4

3

2

1

0

(006FH)

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

<t

| SYSCK | System clock selection | 0: fc | R/W |

|-------|------------------------|-------|-----|

|       |                        | 1: fs |     |

Note 1: The bit 7 should be cleared to 0.

Note 2: The bit 6 to 4 are always read out as 1.

Note 3: Writing 0 to SYSCR1<SYSCK> enables the high-frequency oscillator regardless of the value of SYSCR0<XEN>. Additionally, writing 1 to SYSCR1<SYSCK> enables the low-frequency oscillator regardless of the value of SYSCR0<XTEN>.

System Clock Control Register 2

| SYSCR2  | 7 | 6 | 5 | 4     | 3     | 2      | 1      | 0                          |

|---------|---|---|---|-------|-------|--------|--------|----------------------------|

| (006CH) | 0 | 0 |   | RTCCK | RTCST | RTCIS1 | RTCIS0 | (Initial Value: 00*0 000*) |

| RTCCK  | RTC input clock select       | 0: fs (32 kHz)                                              |     |

|--------|------------------------------|-------------------------------------------------------------|-----|

|        |                              | 1: f <sub>SYS</sub> /2                                      |     |

| RTCST  | RTC count control            | 0: Stop & Clear                                             | Ī   |

|        |                              | 1: Start                                                    | DAA |

| RTCIS1 | Interval time control of RTC | 00: f <sub>SYS</sub> /2 <sup>16</sup> or fs/2 <sup>15</sup> | R/W |

|        | interrupt                    | 01: f <sub>SYS</sub> /2 <sup>17</sup> or fs/2 <sup>16</sup> |     |

| RTCIS0 |                              | 10: f <sub>SYS</sub> /2 <sup>15</sup> or fs/2 <sup>14</sup> |     |

|        |                              | 11: Reserved                                                |     |

Note 1: The bit 7 and 6 should be cleared to 0.

Note 2: When SYSCR2<RTCCK> is 1, RTC input clock is fc/4 or fs/4 depending on operation mode.

| Watchdog Tir | mer Control | Register |                            |              |        |                                                                                                |       |      |                 |            |  |

|--------------|-------------|----------|----------------------------|--------------|--------|------------------------------------------------------------------------------------------------|-------|------|-----------------|------------|--|

| WDMOD        | 7           | 6        | 5                          | 4            | 3      | 2                                                                                              | 1     | 0    |                 |            |  |

| (005CH)      | WDTE        | WDTP1    | WDTP0                      | WARM         | HALTM1 | HALTM0                                                                                         | RESCR | DRVE | (Initial Value: | 1000 0000) |  |

|              | WDTE        | WDT      | control                    |              | -      | Disable<br>Enable                                                                              |       |      |                 |            |  |

|              | WDTP1       | WDT      | detection tir              | ne           |        | 2 <sup>15</sup> /f <sub>SYS</sub>                                                              | 4     |      |                 |            |  |

|              |             |          |                            |              |        | 2 <sup>17</sup> /f <sub>SYS</sub>                                                              |       |      |                 |            |  |

|              | WDTP0       |          |                            |              |        | 10: 2 <sup>19</sup> /fsys                                                                      |       |      |                 |            |  |

|              |             |          |                            |              | 11     | 2 <sup>21</sup> /f <sub>SYS</sub>                                                              |       |      |                 |            |  |

|              | WARM        |          | ing-up time                | r source clo |        | 0: 2 <sup>14</sup> / selected clock frequency<br>1: 2 <sup>16</sup> / selected clock frequency |       |      |                 |            |  |

|              |             | select   | ion                        |              | 1:3    | R/W                                                                                            |       |      |                 |            |  |

|              | HALTM1      | HALT     | mode selec                 | ction        | 00     | 00: RUN mode                                                                                   |       |      |                 |            |  |

|              |             |          |                            |              | 01     | STOP mod                                                                                       |       |      |                 |            |  |

|              | HALTM0      |          |                            |              | 10     | 10: IDLE1 mode                                                                                 |       |      |                 |            |  |

|              |             |          |                            |              | 11     | IDLE2 mo                                                                                       | 4     |      |                 |            |  |

|              | RESCR       | WDT      | WDT internal reset control |              |        | _                                                                                              |       |      |                 |            |  |

|              |             |          |                            |              | 1:     | Connects W                                                                                     | 4     |      |                 |            |  |

|              | DRVE        | Pin co   | ontrol of ST               | OP mode      | 0:     | I/O off                                                                                        |       |      |                 |            |  |

|              |             |          |                            |              | 1:     | Remains the                                                                                    |       |      |                 |            |  |

Figure 3.3.3 I/O registers about dual clock, standby

#### TOSHIBA

#### 3.3.1 System Clock Controller

The system clock controller generates system clock (f<sub>SYS</sub>) for CPU core and internal I/O. It contains two oscillation circuits. The register SYSCR1<SYSCK> changes system clock to either fc or fs, SYSCR0<XEN>, <XTEN> controls enable/disable each oscillator.

The system clock (fsys) is set to fc/2 because of  $\langle XEN \rangle = 1$ ,  $\langle XTEN \rangle = 0$ ,  $\langle SYSCK \rangle = 0$  by resetting.

For example, fSYS is set to 8 MHz by resetting the case of 16-MHz oscillator is connected to X1, X2 pins.

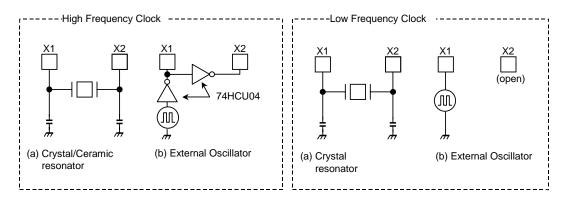

The high frequency (fc) and low frequency (fs) clocks can be easily obtained by connecting a resonator to the X1/X2, XT1/XT2 pins, respectively. Clock input from an external oscillator is also possible.

The XT1, XT2 pins have also Port PB0, PB1 function. Therefore the case of single clock mode, the XT1, XT2 pins can be used as I/O port pins.

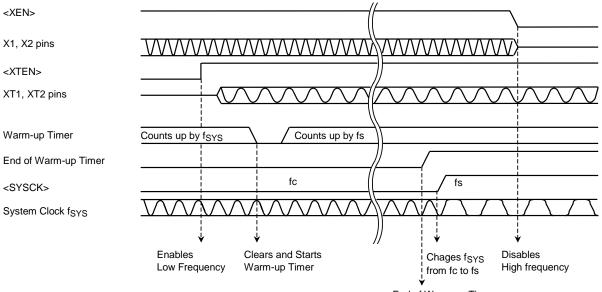

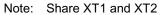

Figure 3.3.4 Examples of resonator connection

Note: In connecting the low frequency resonator to ports PB0 and PB1, it is necessary to make the following settings to reduce the power consumption. Connecting with resonators PBCR<PB0C, PB1C> = 11, PB<PB0, PB1> = 00 Connecting with oscillators PBCR<PB0C, PB1C> = 11, PB<PB0, PB1> = 10 (1) Switching from NORMAL to SLOW mode or from SLOW to NORMAL mode

When the resonator is connected to X1, X2, or XT1, XT2 pin, the warm-up timer is used to change the operation frequency after getting stabilized oscillation.

The warm-up time can be selected by WDMOD<WARM>.

This starting and ending of warm-up timer are performed like the following example 1, 2 by program.

- Note 1: The warm-up timer is also used as a watchdog timer. So, when it is used as a warm-up timer, the watchdog timer must be disabled.

- Note 2: The case of using oscillator (not resonator) with stabilized oscillation, a warmup timer is not need.

- Note 3: The warm-up timer is operated by a oscillation clock. Therefore, warm-up time has an error.

| Warm-up Time<br>WDMOD <warm></warm> | Change to NORMAL | Change to SLOW |  |  |

|-------------------------------------|------------------|----------------|--|--|

| 0 (2 <sup>14</sup> /frequency)      | 1.024 ms         | 500 ms         |  |  |

| 1 (2 <sup>16</sup> /frequency)      | 4.096 ms         | 2000 ms        |  |  |

Table 3.3.2 Warm-up time (at fc = 16 MHz, fs = 32.768 kHz)

Clock Setting Example 1:

Changing from the high frequency (fc) to the low frequency (fs).

| SYSCR0 | EQU | 006EH       |                                                        |

|--------|-----|-------------|--------------------------------------------------------|

| SYSCR1 | EQU | 006FH       |                                                        |

| WDCR   | EQU | 005DH       |                                                        |

| WDMOD  | EQU | 005CH       |                                                        |

|        | RES | 7,(WDMOD)   | ;]                                                     |

|        | LD  | (WDCR),0B1H | ' } Disables Watchdog Timer.                           |

|        | SET | 4,(WDMOD)   | ; Sets Warm-up Time to 2 <sup>16</sup> /fs.            |

|        | SET | 6,(SYSCR0)  | ; Enables Low Frequency (fs).                          |

|        | SET | 2,(SYSCR0)  | ; Clears and stars Warm-up Timer.                      |

| WUP:   | BIT | 2,(SYSCR0)  | ; ] <b>,</b> , <b>, , , , , , , , , , , , , , , , </b> |

|        | JR  | NZ,WUP      | <pre>     Detects End of Warm-up Timer. </pre>         |

|        | SET | 3,(SYSCR1)  | ; Changes f <sub>SYS</sub> from fc to fs.              |

|        | RES | 7,(SYSCR0)  | ; Disables High Frequency Oscillation.                 |

|        | SET | 7,(WDMOD)   | ; Enables Watchdog Timer.                              |

End of Warm-up Timer

Clock Setting Example 2:

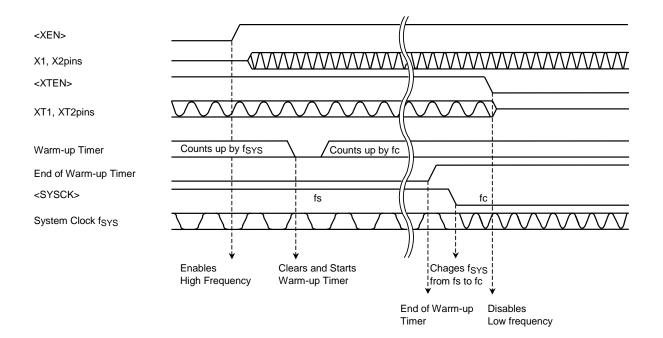

Changing from the low frequency (fs) to the high frequency (fc).

| SYSCR0<br>SYSCR1 | EQU<br>EQU | 006EH<br>006FH |                                             |

|------------------|------------|----------------|---------------------------------------------|

| WDCR             | EQU        | 005DH          |                                             |

| WDMOD            | EQU        | 005CH          |                                             |

|                  | RES        | 7,(WDMOD)      | ; ]                                         |

|                  | LD         | (WDCR),0B1H    | <pre>     Disables Watchdog Timer. </pre>   |

|                  | RES        | 4,(WDMOD)      | ; Sets Warm-up Time to 2 <sup>14</sup> /fc. |

|                  | SET        | 7,(SYSCR0)     | ; Enables High Frequency (fc).              |

|                  | SET        | 2,(SYSCR0)     | ; Clears and stars Warm-up Timer.           |

| WUP:             | BIT        | 2,(SYSCR0)     |                                             |

|                  | JR         | NZ,WUP         | ' } Detects End of Warm-up Timer.           |

|                  | RES        | 3,(SYSCR1)     | ; Changes f <sub>SYS</sub> from fs to fc.   |

|                  | RES        | 6,(SYSCR0)     | ; Disables Low Frequency Oscillation.       |

|                  | SET        | 7,(WDMOD)      | ; Enables Watchdog Timer.                   |

### 3.3.2 Timing Clock Generator

The timing clock generator generates sorts of system clock from the basic clock (fc or fs), providing for CPU core and peripheral hardwares.

#### (1) Architecture

The timing clock generator consists of the system clock generator and the Time Base Counter (TBC) which generates system clock for peripheral hardwares. After resetting, the system clock is generated from high frequency clock (fc) (NORMAL mode). Both executing the instruction and operating the internal hardwares are synchronized by this system clock.

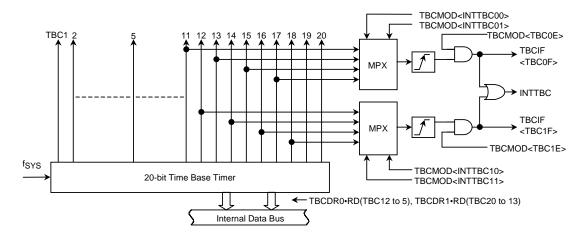

#### (2) Time Base Counter (TBC)

The time base counter consists of a 20-bit up-counter counted by a basic clock fSYS, 16-bit data register and control register.

Figure 3.3.5 Shows the composition of the time base counter.

Figure 3.3.5 Composition of time base counter (TBC)

Time Base Counter mode Register

| TBCMOD  | 7        | 6                                      | 5            | 4          | 3      | 2            | 1        | 0        | _                  |          |

|---------|----------|----------------------------------------|--------------|------------|--------|--------------|----------|----------|--------------------|----------|

| (0023H) | 0        | 0                                      | TBC1E        | TBC0E      | INTTBO | C11 INTTBC10 | INTTBC01 | INTTBC00 | (Initial Value: ** | 00 0000) |

|         |          |                                        |              |            |        |              |          |          |                    |          |

|         | TBC1E    | INTTE                                  | BC Interrupt | Enable/Dis | able   | 00: INTTBC0/ | ble      |          |                    |          |

|         |          |                                        |              |            |        | 01: INTTBC0  |          |          |                    |          |

|         | TBC0E    |                                        |              |            |        | 10: INTTBC1  |          |          |                    |          |

|         |          |                                        |              |            |        | 11: INTTBC0/ | ble      |          |                    |          |

|         | INTTBC11 | INTTE                                  | BC1 Interru  | pt Source  | Clock  | 00: TBC12    |          |          |                    |          |

|         |          | Select                                 | ion          |            |        | 01: TBC14    |          |          |                    |          |

|         | INTTBC10 |                                        |              |            |        | 10: TBC16    |          | 10,00    |                    |          |

|         |          |                                        |              |            |        | 11: TBC18    |          |          |                    |          |

|         | INTTBC01 | NTTBC01 INTTBC0 Interrupt Source Clock |              |            | Clock  | 00: TBC11    |          |          |                    |          |

|         |          | Select                                 | ion          |            |        | 01: TBC13    |          |          |                    |          |

|         | INTTBC00 |                                        |              |            |        | 10: TBC15    |          |          |                    |          |

|         |          |                                        |              |            |        | 11: TBC17    |          |          |                    |          |

Note 1: The bit 7 and 6 should be cleared to 0.

Note 2: The bit 7 and 6 are always read out as 1.

Note 3: Prohibt read-modify-write.

Time Base Counter Data Register 0

| TBCDR0  | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0    | _                                    |

|---------|-------|-------|-------|------|------|------|------|------|--------------------------------------|

| (0024H) | TBC12 | TBC11 | TBC10 | TBC9 | TBC8 | TBC7 | TBC6 | TBC5 | (Initial Value: 0000 0000) Read only |

Time Base Counter Data Register 1

| TBCDR1  | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _                                    |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------------------|

| (0025H) | TBC20 | TBC19 | TBC18 | TBC17 | TBC16 | TBC15 | TBC14 | TBC13 | (Initial Value: 0000 0000) Read only |

Note: A value of TBC20 to 13 is latched to TBCDR1 at reading out TBCDR0. TBCDR1 must be read out after reading TBCDR0.

Time Base Counter Interrupt Flag Register 0

| TBCIF<br>(0026H) | 7     | 6 5 4 3<br>0 TBC1F TBC0F    | 2 1 0<br>0 (Initial Value: 000                     | 00 *0**) |

|------------------|-------|-----------------------------|----------------------------------------------------|----------|

|                  | TBC1F | TBC1 interrupt request flag | (write) 0: Clear request flag<br>1: Don't set to 1 |          |

|                  |       |                             | (read) 0: —<br>1: Interrupt request                |          |

|                  | TBC0F | TBC0 interrupt request flag | (write) 0: Clear request flag<br>1: Don't set to 1 | R/W      |

|                  |       |                             | (read) 0: —                                        |          |

|                  |       |                             | 1: Interrupt request                               |          |

Note 1: The bit 7, 6 and 2 should be cleared to 0.

Note 2: The bit 7, 6 and 2 are always read as 1.

Note 3: Prohibit read-midify-write.

#### a. Operation

Time base counter outputs (TBC1 to TBC20) are used as clock source or timing data for Timer/Counter, Capture (CAP0/CAP1/CAP2), timing pulse generator (TPG) and other peripheral I/O blocks. The contents of time base counter outputs TBC5 to TBC20 can be read by reading the time base counter data registers, TBCDR0 and TBCDR1. Note that the data registers must be read in order of TBCDR0 and then TBCDR1.

Time base counter interrupt requests (INTTBC) can be generated on the rising edges of counter outputs TBC11 to TBC18. The interrupt source is selected by the time base counter mode register TBCMOD <INTTBC11, INTTBC10, INTTBC01 and INTTBC00>. The INTTBC interrupt requests are comprised of two interrupt request signals INTTBC0 and INTTBC1 that are logical OR' ed to generate an interrupt request. Which interrupt is requested can be identified by reading the time base counter interrupt request flag register TBCIF <TBC0F> and <TBC1F>.

The INTTBC0 flag <TBC0F> and INTTBC1 flag <TBC1F> can be cleared by writing 0 in the register.

Table 3.3.3 lists the interval time of time base counter outputs.

|                        | Table 3.3.3 The value of time base counter |                                  |                                  |                                  |                     |                                  |                                  |                                  |                                  |                                   |  |  |  |

|------------------------|--------------------------------------------|----------------------------------|----------------------------------|----------------------------------|---------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|-----------------------------------|--|--|--|

|                        | TBC1                                       | TBC2                             | TBC3                             | TBC4                             | TBC5                | TBC6                             | TBC7                             | TBC8                             | TBC9                             | TBC10                             |  |  |  |

| Interval Time<br>[s]   | 2/f <sub>SYS</sub>                         | 2 <sup>2</sup> /f <sub>SYS</sub> | 2 <sup>3</sup> /f <sub>SYS</sub> | 2 <sup>4</sup> /f <sub>SYS</sub> | 2⁵/f <sub>SYS</sub> | 2 <sup>6</sup> /f <sub>SYS</sub> | 2 <sup>7</sup> /f <sub>SYS</sub> | 2 <sup>8</sup> /f <sub>SYS</sub> | 2 <sup>9</sup> /f <sub>SYS</sub> | 2 <sup>10</sup> /f <sub>SYS</sub> |  |  |  |

| at fc = 16 MHz<br>[µs] | 0.25                                       | 0.5                              | 1.0                              | 2.0                              | 4.0                 | 8.0                              | 16.0                             | 32.0                             | 64.0                             | 128.0                             |  |  |  |

Table 3.3.3 Interval time of time base counter

| ĺ | TBC11                             | TBC12                             | TBC13                             | TBC14                             | TBC15                             | TBC16                             | TBC7                              | TBC18                             | TBC19                             | TBC20                             |

|---|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|

|   | 2 <sup>11</sup> /f <sub>SYS</sub> | 2 <sup>12</sup> /f <sub>SYS</sub> | 2 <sup>13</sup> /f <sub>SYS</sub> | 2 <sup>14</sup> /f <sub>SYS</sub> | 2 <sup>15</sup> /f <sub>SYS</sub> | 2 <sup>16</sup> /f <sub>SYS</sub> | 2 <sup>17</sup> /f <sub>SYS</sub> | 2 <sup>18</sup> /f <sub>SYS</sub> | 2 <sup>19</sup> /f <sub>SYS</sub> | 2 <sup>20</sup> /f <sub>SYS</sub> |

| ĺ | 256                               | 512                               | 1024                              | 2048                              | 4096                              | 8192                              | 16384                             | 32768                             | 65536                             | 131072                            |

#### 3.3.3 Real Time Counter (RTC)

The TMP93CF76/CF77/CW76/CU76/CT76 have the real time counter (RTC) which generates a periodic interrupt request. The RTC is controlled by System Control Register2 (SYSCR2).

The RTC is a 17bit binary counter and its clock source is selected either low frequency clock (fs) or system clock (fSYS/2) by <RTCCK>. To start/stop the counter is controlled by <RTCST>.

The period of interrupt request INTRTC is selected from 3 types by setting <RTCIS1, RTCIS0>.

Table 3.3.4 shows the period of interrupt request INTRTC.

System Clock Control Register 2

```

SYSCR2

7

6

5

4

3

2

1

0

(006CH)

0

0

RTCCK

RTCST

RTCIS1

RTCIS0

(Initial Value: 00*0 0000)

```

| RTCCK  | RTC input clock select       | 0: fs                                                                                                                                                                                     |      |

|--------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|        |                              | 1: f <sub>SYS</sub> /2                                                                                                                                                                    |      |

| RTCST  | RTC count control            | 0: Stop & Clear                                                                                                                                                                           |      |

|        |                              | 1: Start                                                                                                                                                                                  | 5.44 |

| RTCIS1 | Interval time control of RTC | 00: f <sub>SYS</sub> /2 <sup>16</sup> or fs/2 <sup>15</sup>                                                                                                                               | R/W  |

| DTOIOO | interrupt                    | 01: f <sub>SYS</sub> /2 <sup>17</sup> or fs/2 <sup>16</sup>                                                                                                                               |      |

| RTCIS0 |                              | 00: f <sub>SYS</sub> /2 <sup>16</sup> or fs/2 <sup>15</sup><br>01: f <sub>SYS</sub> /2 <sup>17</sup> or fs/2 <sup>16</sup><br>10: f <sub>SYS</sub> /2 <sup>15</sup> or fs/2 <sup>14</sup> |      |

|        |                              | 11: Reserved                                                                                                                                                                              |      |

Note 1: When SYSCR2<RTCCK> is set to 1, RTC input clock is assigned to fc/4 or fs/4 depending on the peration mode.

Note 2: The bit 7 and 6 must be cleared to 0.

| <rtcck></rtcck>                                                               | <rtcis></rtcis> | INTRTC interrupt<br>interval      |

|-------------------------------------------------------------------------------|-----------------|-----------------------------------|

| 0<br>(fs = 32.768 kHz)                                                        | 00<br>01<br>10  | 1 s<br>2 s<br>0.5 s               |

| $\begin{bmatrix} 1 \\ f_{SYS} = fc/2 \\ f_{c} = 16 \text{ MHz} \end{bmatrix}$ | 00<br>01<br>10  | 8.192 ms<br>16.384 ms<br>4.096 ms |

| $f_{SYS} = fs/2$ $f_{s} = 32.768 \text{ kHz}$                                 | 00<br>01<br>10  | 4 s<br>8 s<br>2 s                 |

#### Table 3.3.4 INTRTC interrupt interval

# 3.3.4 Standby Controller

(1) Halt mode

When the HALT instruction is executed, the operating mode changes into RUN, IDLE2, IDLE1 or STOP mode depending on the contents of watchdog timer mode register WDMOD<HALTM1,0>. Figure 3.3.6 shows the alternative states of watchdog timer mode registers.

#### Watchdog Timer Mode Register

| WDMOD   | 7    | 6     | 5     | 4    | 3      | 2      | 1     | 0    | _                          |

|---------|------|-------|-------|------|--------|--------|-------|------|----------------------------|

| (005CH) | WDTE | WDTP1 | WDTP0 | WARM | HALTM1 | HALTM0 | RESCR | DRVE | (Initial Value: 1000 0000) |

| WDTE   | WDT timer enable/disable control        | 0: Disable                                    |       |

|--------|-----------------------------------------|-----------------------------------------------|-------|

|        |                                         | 1: Enable                                     |       |

| WDTP1  | WDT detection time                      | 00: 2 <sup>15</sup> /f <sub>SYS</sub>         |       |

|        |                                         | 01: 2 <sup>17</sup> /f <sub>SYS</sub>         |       |

| WDTP0  |                                         | 10: 2 <sup>19</sup> /f <sub>SYS</sub>         |       |

|        |                                         | 11: 2 <sup>21</sup> /f <sub>SYS</sub>         |       |

| WARM   | Warming-up timer source clock           | 0: 2 <sup>14</sup> / selected clock frequency |       |

|        | selection                               | 1: 2 <sup>16</sup> / selected clock frequency | R/W   |

| HALTM1 | HALTM1 HALT mode selection 00: RUN mode |                                               | 10,00 |

|        |                                         | 01: STOP mode                                 |       |

| HALTM0 |                                         | 10: IDLE1 mode                                |       |

|        |                                         | 11: IDLE2 mode                                |       |

| RESCR  | WDT internal reset control              | 0: —                                          |       |

|        |                                         | 1: Connects WDT output to RESET internaly     | ļ     |

| DRVE   | Pin control of STOP mode                | 0: I/O off                                    |       |

|        |                                         | 1: Remains the state before HALT              |       |

Figure 3.3.6 Watchdog timer mode register

The features of RUN, IDLE2, IDLE1 and STOP modes are as follows.

- a. RUN: Only the CPU halts; power consumption remains unchanged.

- b. IDLE2: The built-in oscillator and the specified I/O operates.

- The Power Consumption is redced to 1/2 than that during NORMAL operation.

- c. IDLE1: Only the built-in oscillator operates, while all other built-in circuits stop. The Power Consumption is reduced to 1/5 or less than that during NORMAL operation.

- d. STOP: All internal circuits including the built-in oscillator stop. This greatly reduces power consumption.

The operations in the halt state is described in Table 3.3.5.

Note: CAPCR<TPRS0> must be set to 1 before setting HALT mode such as STOP, IDLE1, IDLE2. Otherwise Icc may be increased.

| Halt mode                        | RUN                 | IDLE2                  | IDLE1         | STOP                 |  |  |

|----------------------------------|---------------------|------------------------|---------------|----------------------|--|--|

| WDMOD <haltm1,0></haltm1,0>      | 00                  | 11                     | 10            | 01                   |  |  |

| CPU                              | Stop                |                        |               |                      |  |  |

| I/O port                         | Keep the state when | the "HALT" instruction | was executed. | Refer to Table 3.3.8 |  |  |

| 8-bit Timer(TC0)                 |                     |                        |               |                      |  |  |

| 16-bit Timer (TC1,2,3,4,5)       |                     |                        |               |                      |  |  |

| Dual Clock                       |                     |                        |               |                      |  |  |

| Watchdog Timer                   |                     |                        |               |                      |  |  |

| Interrupt controller             | Ope                 | rate                   | St            | юр                   |  |  |

| SIO                              |                     |                        |               |                      |  |  |

| I <sup>2</sup> C bus             |                     |                        |               |                      |  |  |

| 8-bit PWM                        |                     |                        |               |                      |  |  |

| 14-bit PWM                       |                     |                        |               |                      |  |  |

| Timing Pulse Generator (TPG 0,1) |                     |                        |               |                      |  |  |

| Color Rotary                     |                     |                        |               |                      |  |  |

| VISS/VASS                        |                     |                        |               |                      |  |  |

| CSYNC                            |                     |                        |               |                      |  |  |

| PV/PH                            |                     |                        |               |                      |  |  |

| Capture input (Capture1/2)       |                     |                        |               |                      |  |  |

| Capture 0                        |                     |                        |               |                      |  |  |

| Remote Control Input (RMTIN)     |                     |                        |               |                      |  |  |

| Time Base Counter (TBC)          |                     |                        |               |                      |  |  |

| AD Converter                     |                     |                        |               |                      |  |  |

| Real Time Counter (RTC)          |                     |                        |               |                      |  |  |

Table 3.3.5 I/O operation during Halt mode

(2) How to Release the Halt mode

These HALT states can be released by resetting or requesting an interrupt. The HALT release sources are determined by the combinations between the states of interrupt mask register  $\langle IFF2:0 \rangle$  and the halt modes. The details for releasing the HALT status are shown in Table 3.3.6.

• Released by requesting an interrupt

The operating released from the HALT mode depends on the interrupt enabled status. When the interrupt request level set before executing the HALT instruction exceeds the value of the interrupt mask register, the interrupt due to the source is processed after releasing the halt mode, and CPU starts executing an instruction that follows the HALT instruction. When the interrupt request level set before executing the HALT instruction is less than the value of the interrupt mask register, releasing the halt mode is not executed. (in non-maskable interrupts, interrupt processing is processed after releasing the halt mode so the value of the mask register.)

However only for INT0 and INT1 interrupts, even if the interrupt request level set before executing the HALT instruction is less than the value of the interrupt mask register, releasing the halt mode is executed. In this case, interrupt processing is not processed, and CPU starts executing the instruction next to the HALT instruction, but the interrupt request flag is held at 1.

Note: Usually, interrupts can release all halts status. However, the interrupts = (INT0, INT1), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of fc or fs) with IDLE1 or STOP mode (IDLE2 is not applicable to this case). (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

• Release by resetting

Releasing all halt status is executed by resetting.

When the STOP mode is released by RESET, it is necessary enough resetting time (3 ms or more) to set the operation of the oscillator to be stable.

When releasing the halt mode by resetting, the internal RAM data keeps the state before the "HALT" instruction is executed. However the other setting contents are initialized. (Releasing due to interrupts keep the state before the "HALT" instruction is executed.)

| Inte      | Interrupt Receiving Status |             | Interrupt Enable |                                    |       | Interrupt Disable |                                    |       |       |      |

|-----------|----------------------------|-------------|------------------|------------------------------------|-------|-------------------|------------------------------------|-------|-------|------|

|           |                            |             | (Interru         | (Interrupt level)≥(Interrupt mask) |       |                   | (Interrupt level)<(Interrupt mask) |       |       |      |

|           | Halt m                     | node        | RUN              | IDLE2                              | IDLE1 | STOP              | RUN                                | IDLE2 | IDLE1 | STOP |

|           |                            | INTWD       | •                | ×                                  | ×     | ×                 | _                                  | _     |       |      |

|           |                            | INT0,1      | •                | •                                  | •     | ♦*1               | 0                                  | 0     | 0     | O*1  |

| Halt      | Interrupt                  | INTCAP0, 1  | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

| releasing |                            | INTTTG0, 1  | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

| source    |                            | INTI2CB     | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           |                            | INTTBC      | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           |                            | INTSIO      | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           |                            | INTVA       | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           |                            | INT2, 3, 4  | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           |                            | INTT0 to 5  | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           |                            | INTAD       | •                | ×                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           |                            | INTRTC      | •                | •                                  | ×     | ×                 | ×                                  | ×     | ×     | ×    |

|           | F                          | Reset Input | •                | •                                  | •     | •                 | •                                  | •     | •     | •    |

#### Table 3.3.6 Halt releasing source and Halt releasing operation

• : After releasing the halt mode, CPU starts interrupt processing (RESET initalizes LSI)

$\ensuremath{\mathsf{O}}$  : After releasing the halt mode, CPU starts executing an instruction that follows the HALT instruction.

$\times$  : It can not be used to release the halt mode.

---: This combination type does not exist because the priority level (interrupt request level) of non-maskable interrupts is fixed to highest priority level 7.

\*1: Releasing the halt mode is executed after passing the warming-up time.

Note: When releasing the halt mode is executed by INT1 interrupt of the level mode in the interrupt enabled status, hold level "H" until starting interrupt processing. If level "L" is set before starting interrupt processing, interrupt processing is incorrently started.

#### (Example releasing "IDLE1" mode)

INTO interrupt releases HALT state when the IDLE mode is on.

| Address | ł         |               |                                          |

|---------|-----------|---------------|------------------------------------------|

| 8200H   | LD        | (IIMC0),01H   | ; INT0 interrupt input enable            |

| 8203H   | LD        | (IIMC1),00H   | ; Selects interrupt rising edge for INT0 |

| 8206H   | LD        | (INT0CP1),06H | ; Sets interrupt level to 6 for INT0     |

| 8209H   | EI        | 5             | ; Sets interrupt level to 5 for CPU      |

| 820BH   | LD        | (WDMOD),08H   | ; Sets HALT mode to 'IDLE1'              |

| 820EH   | HALT<br>¦ |               | ;halts CPU                               |

| INT0 _  |           |               | INT0 Interrupt routine                   |

| 820FH   |           | XX            | RETI                                     |

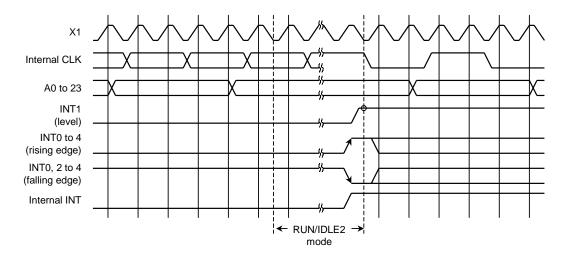

- (3) Operation

- a. RUN mode

In the RUN mode, the system clock continues to operate even after a HALT instruction is executed. Only the CPU stops executing the instruction. In the HALT state, an interrupt request is sampled with the falling edge of the internal "CLK" signal.

Releasing the RUN mode is executed by the external/internal interrupts. (See Table 3.3.6 Halt releasing source and Halt releasing operation.)

Figure 3.3.7 shows the interrupt timing for releasing the HALT state by interrupts in the RUN/IDLE2 mode.

Figure 3.3.7 Timing chart for releasing the HALT state by Interrupt in RUN/IDLE2 modes

b. IDLE2 mode

In the IDLE2 mode, the system clock is supplied to only specific internal I/O devices, and the CPU stops executing the current instruction.

In the IDLE2 mode, the HALT state is released by an interrupt with the same timing as in the RUN mode. The IDLE2 mode is released by external/internal interrupt, except INTWD/INTAD interrupts. (See table 3.3.6 Halt releasing source and Halt releasing operation.)

In the IDLE2 mode, the watchdog timer should be disabled before entering the halt status to prevent the watchdog timer interrupt occurring just after releasing the halt mode.

c. IDLE1 mode

In the IDLE1 mode, only the internal oscillator operates. The system clock in the MCU stops.

In the HALT state, and interrupt request is sampled aynchronunsly with the system clock, however the HALT release (restart of operation) is performed synchronously with it.

IDLE1 mode is released by external interrupts (INT0, INT1). (See table 3.3.6 Halt releasing source and Halt releasing operation.)

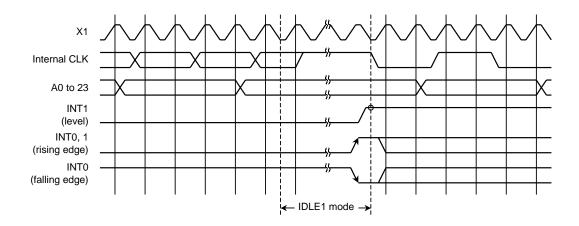

Figure 3.3.8 illustrates the timing for releasing the HALT state by interrupts in the IDLE1 mode.

Figure 3.3.8 Timing chart of HALT released by interrupts in IDLE1 mode

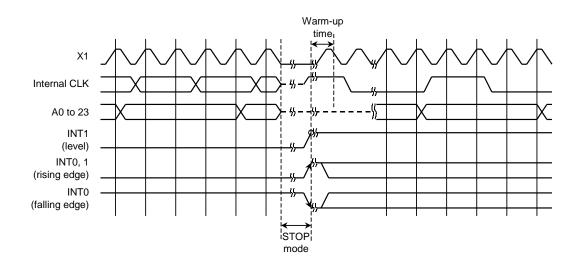

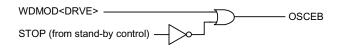

d. STOP mode

The STOP mode is selected to stop all internal circuits including the internal oscillator. The pin status in the STOP mode depends on setting of a bit in the watchdog timer mode register WDMOD<DRVE>. (See Figure 3.3.6 for setting of WDMOD <DRVE>.) Table 3.3.8 summarizes the state of these pins in the STOP mode.

The STOP mode is released by external interrupts (INT0, INT1). When the STOP mode is released, the system clock output starts after warm-up time required to attain stable oscillation. The warm-up time can be set using WDMOD<WARM>. See the example of warm-up time (Table 3.3.7).

Figure 3.3.9 illustrates the timing for releasing the HALT state by interrupts during the STOP mode.

Figure 3.3.9 Timing chart of HALT state release by interrupts in STOP mode

| Clock Operation Frequency | Warm-up                              | Clock Frequency         |                 |

|---------------------------|--------------------------------------|-------------------------|-----------------|

| after the Stop Mode       | WDMOD <warm> <math>= 0</math></warm> | WDMOD <warm> = 1</warm> |                 |

| fc                        | 1.024                                | 4.096                   | fc = 16 MHz     |

| fs                        | 500                                  | 2000                    | fs = 32.768 kHz |

Table 3.3.7 The example of warm-up time after releasing the stop mode

How to calculate the warm-up time

WDMOD<WARM> = 0:  $2^{14}$ /selected clock frequency

WDMOD<WARM> = 1:  $2^{16}$ /selected clock frequency

The NORMAL/SLOW mode selection is possible after released STOP mode.

This is selected by SYSCR0 <RSYSCK>. Therefore, Setting to <RSYSCK>, <RXEN>, <RXTEN> is necessary before "HALT" instruction is executed.

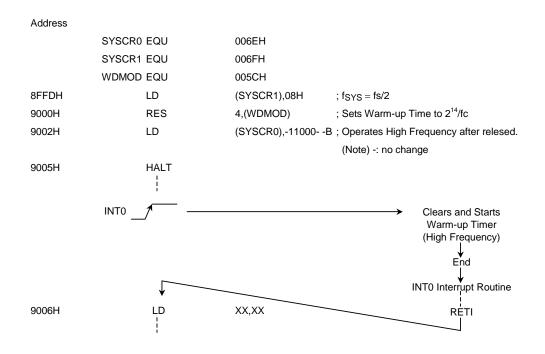

#### Example:

The STOP mode is entered when the low frequency (fs) operates, and after that high frequency (fc) operates after releasing by INTO.

Note: When different modes are used before and after STOP mode as the above mentioned, there is possible to release the HALT mode without changing the operation mode by acceptance of the halt release interrupt request during execution of "HALT" instruction (during 8 states). In the system which accepts the interrupts during execution "HALT" instruction, set the same operation mode before and after the STOP mode.

|                                     |              | TMP93CF76/CF77          | /CW76/CU76/CT76         |  |

|-------------------------------------|--------------|-------------------------|-------------------------|--|

| Pin Name                            | I/O          | WDMOD                   | WDMOD                   |  |

|                                     |              | <drve> = 0</drve>       | <drve> = 1</drve>       |  |

| CLK                                 | Output       | High-Z                  | "H" Level Output        |  |

| X1                                  | Input        |                         |                         |  |

| X2                                  | Output       | "H" Level Output        | "H" Level Output        |  |

| PB0/PB1                             | Input/Output | — /High-Z               | —/Output                |  |

| XT1                                 | Input        | —                       | —                       |  |

| XT2                                 | Output       | "H" Level Output        | "H" Level Output        |  |

| P40 to P47/AIN2 to AIN9             | Input        | _                       | —                       |  |

| P00 to P07, P10 to P17, P20 to P27, | Input        |                         | —                       |  |

| P50 to P54, P73 to P76, P80 to P87, | Output       | High-Z                  | Output                  |  |

| P90 to P97, PA0, PA3                |              |                         |                         |  |

| PWM0, 1                             | Output       | High-Z                  | Output                  |  |

| PE0 to PE7, PF0 to PF5              | Input        |                         |                         |  |

|                                     | Output       | High-Z                  | Output                  |  |

| PD0, PD1,PC0 to PC7                 | Output       | High-Z                  | Output                  |  |

| P53/INT1, P54/INT0                  | Input        | Input                   | Input                   |  |

|                                     | Output       | High-Z                  | Output                  |  |

| TEST                                | Input        | "H" Level fixed         | "H" Level fixed         |  |

| RESET                               | Input        | Input                   | Input                   |  |

| ADREF                               | Input        | Open state is available | Open state is available |  |

#### Table 3.3.8 Pin states in STOP mode

— : Inputs are not accepted.

Input : Input gate in operation. Fix input voltage level to "L" or "H" so that the input pin stays constant.

Output: Output state

High-Z: High-Impedance

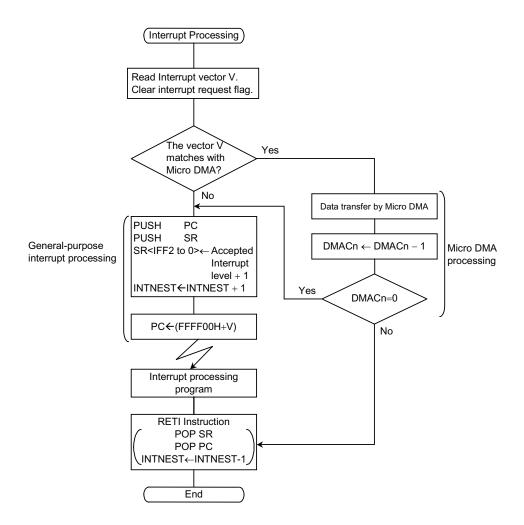

### 3.4 Interrupts

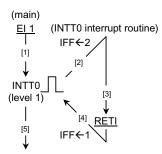

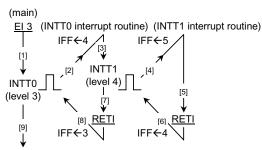

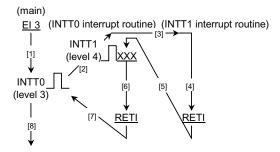

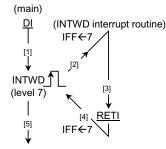

The interrupts are controlled by the CPU interrupt mask flip-flop <IFF2 to 0> and the built-in interrupt controller.

Altogether the TMP93CF76/CF77/CW76/CU76/CT76 have the following 30 interrupt sources:

- Interrupts from the CPU: 8 sources (software interrupt and illegal instrction execution interrupt)

- Interrupts from the internal peripheral function blocks: 17 sources

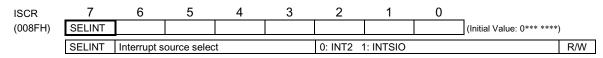

- External interrupts (INT0 to INT4): 5 sources