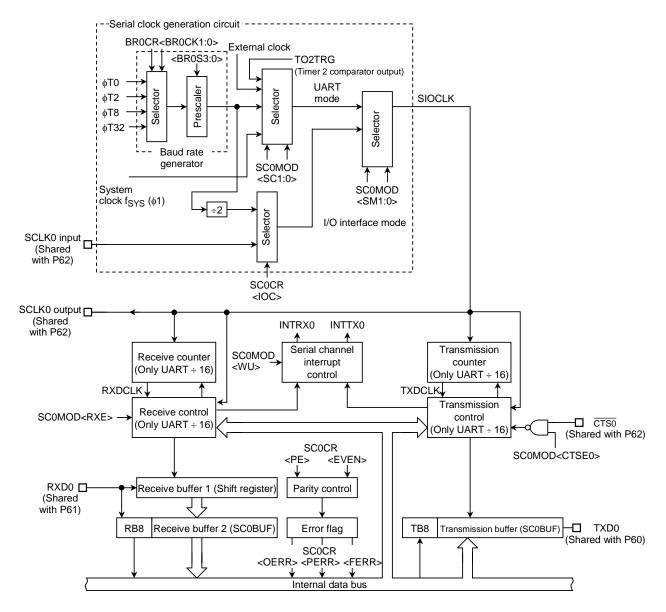

Low Voltage/Low Power

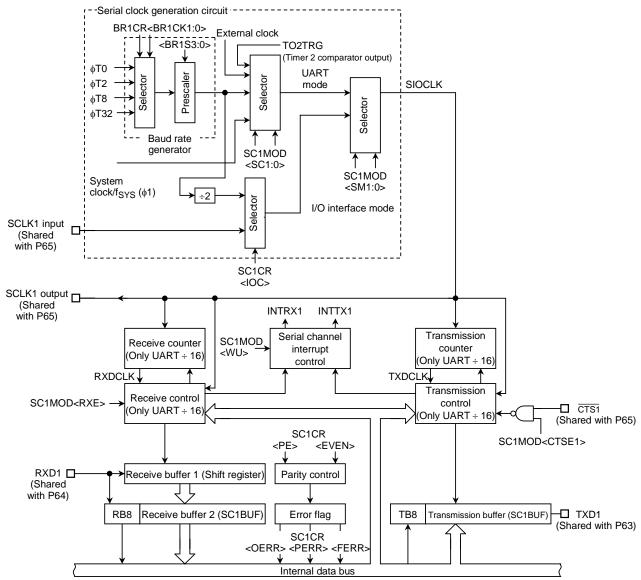

# CMOS 16-bit Microcontrollers TMP93CS44F/TMP93CS45F

## Outline and Device Characteristics

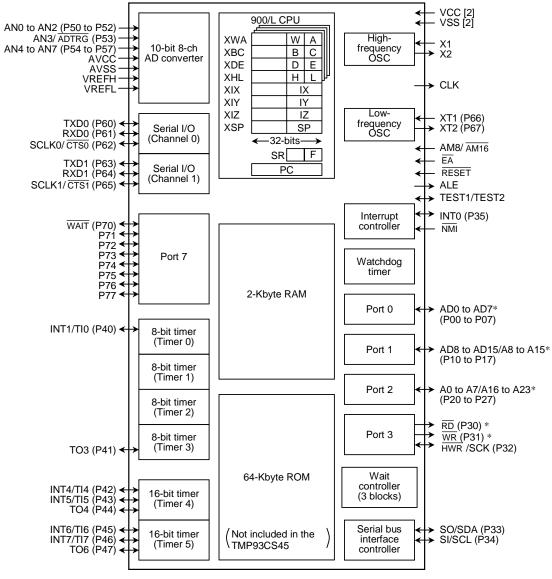

The TMP93CS44/TMP93CS45 are high-speed, advanced 16-bit microcontrollers developed for controlling medium to large-scale equipment. The TMP93CS45 does not have a ROM, the TMP93CS44 has a built-in ROM. Otherwise, the devices function in the same way.

The TMP93CS44F/TMP93CS45F are housed in 80-pin flat package (P-LQFP80-1212-0.50E).

The device characteristics are as follows:

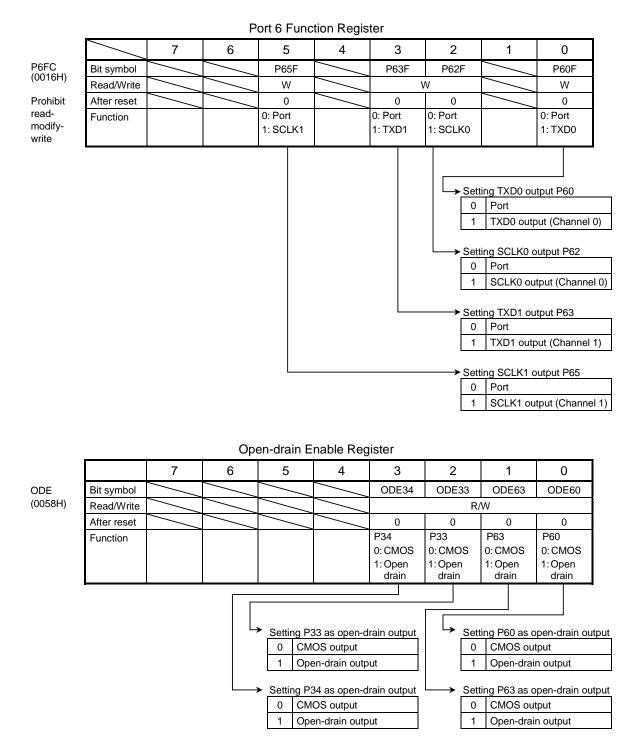

- (1) Original 16-bit CPU (900/L CPU)

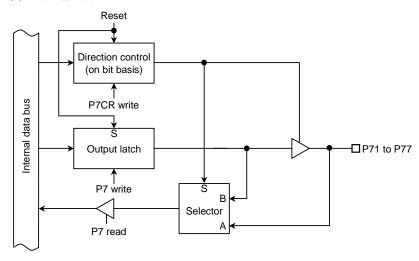

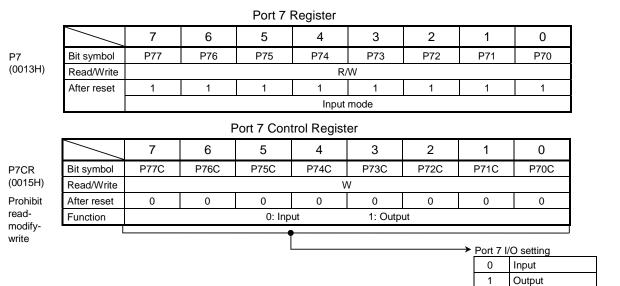

- TLCS-90 instruction mnemonic upward compatible

- 16-Mbyte linear address space

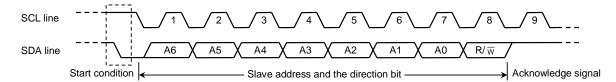

- General-purpose registers and register bank system

- 16-bit multiplication/division and bit transfer/arithmetic instructions

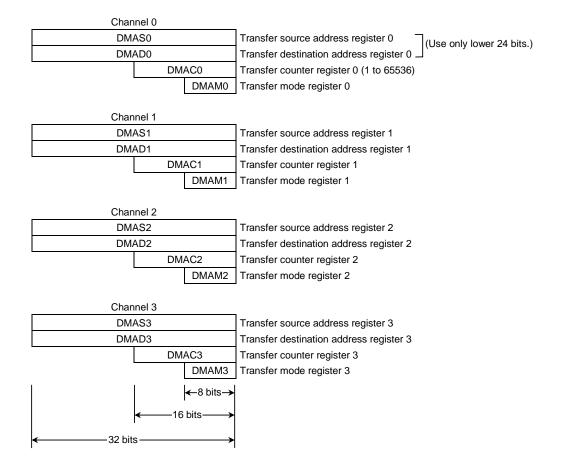

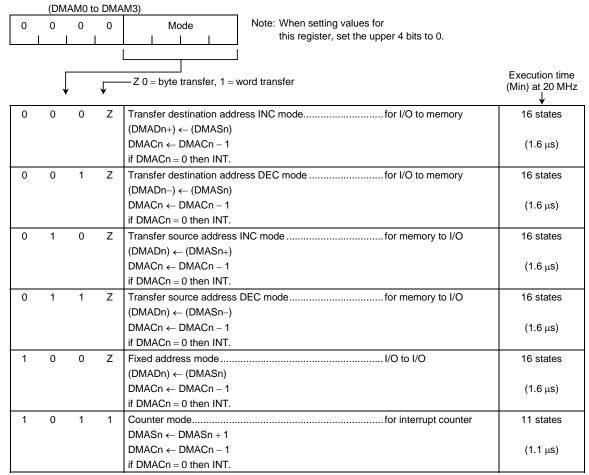

- Micro DMA: 4 channels (1.6 µs per 2 bytes at 20 MHz)

- (2) Minimum instruction execution time: 200 ns at 20 MHz

- (3) Internal RAM: 2 Kbytes

Internal ROM:

TMP93CS44

64-Kbyte ROM

TMP93CS45

None

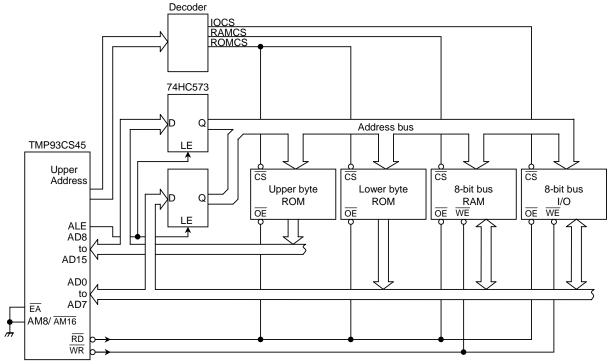

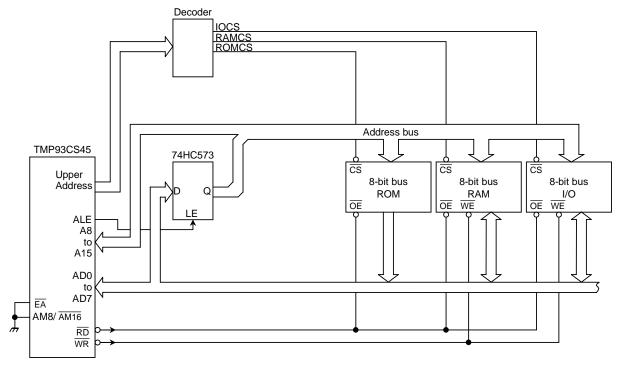

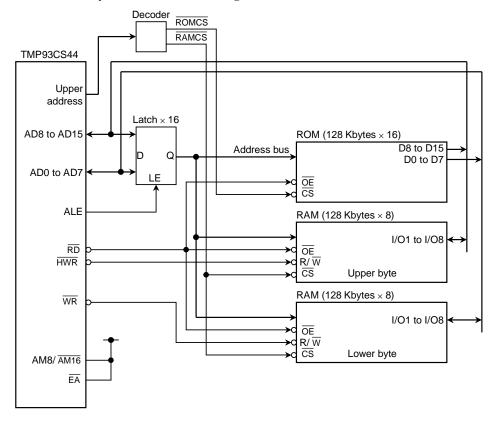

- (4) External memory expansion

- Can be expanded up to 16 Mbytes (for both programs and data)

- AM8/ AM16 pin (Select the external data bus width)

- Can mix 8- and 16-bit external data buses (Dynamic bus sizing)

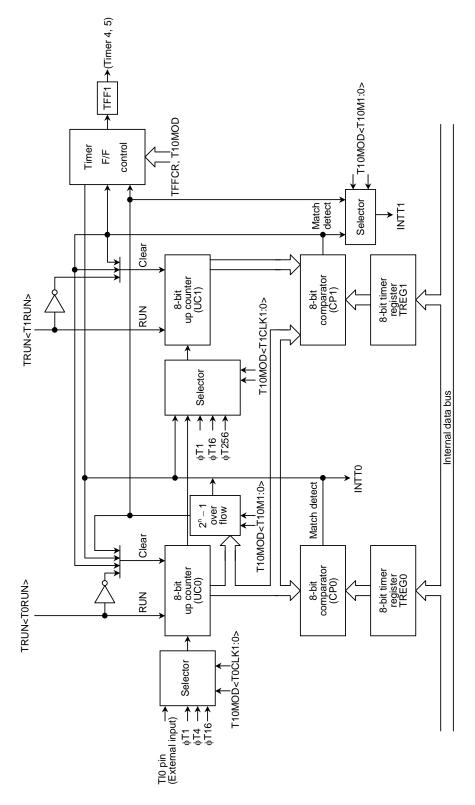

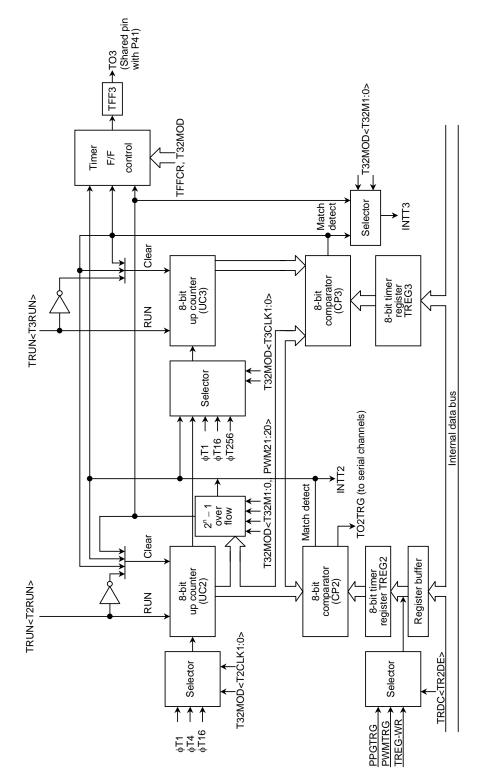

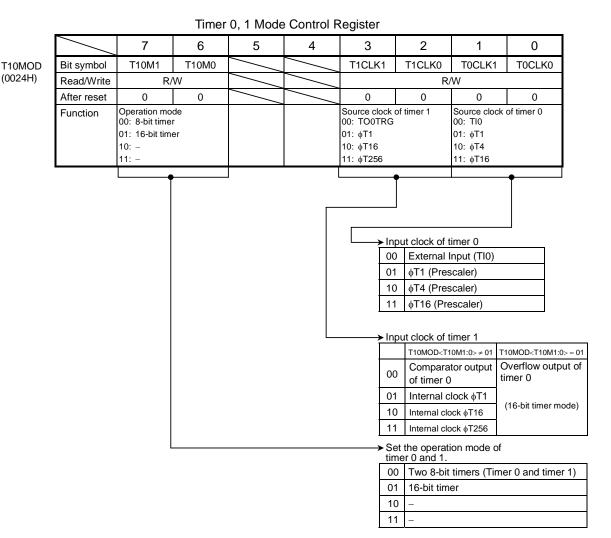

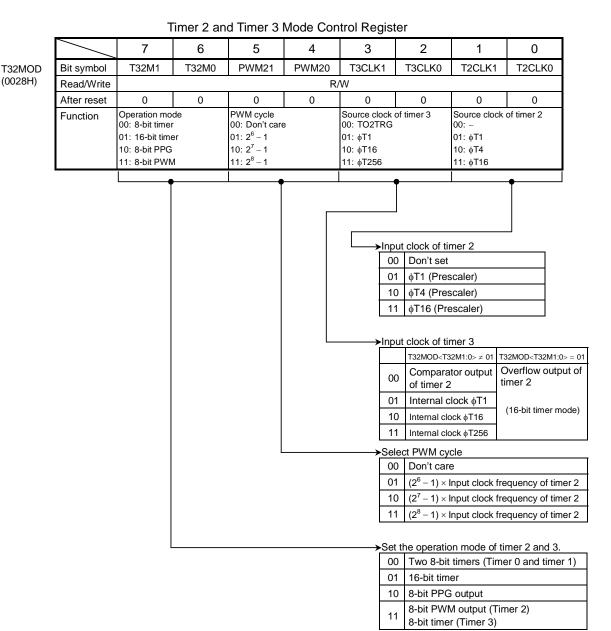

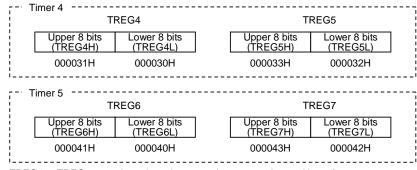

- (5) 8-bit timer: 4 channels

- (6) 16-bit timer: 2 channels

030619EBP1

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general

can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer,

when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid

situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to

property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

93CS44-1 2004-02-10

- (7) Serial interface: 2 channels

- (8) Serial bus interface: 1 channel

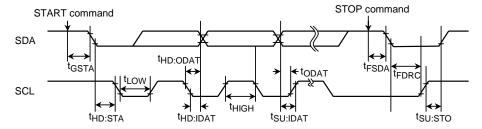

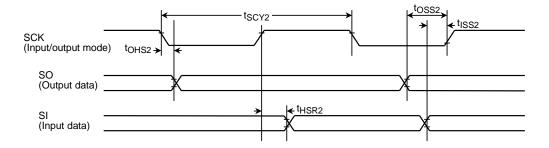

- I2C bus mode

- Clocked-synchronous 8-bit serial interface mode

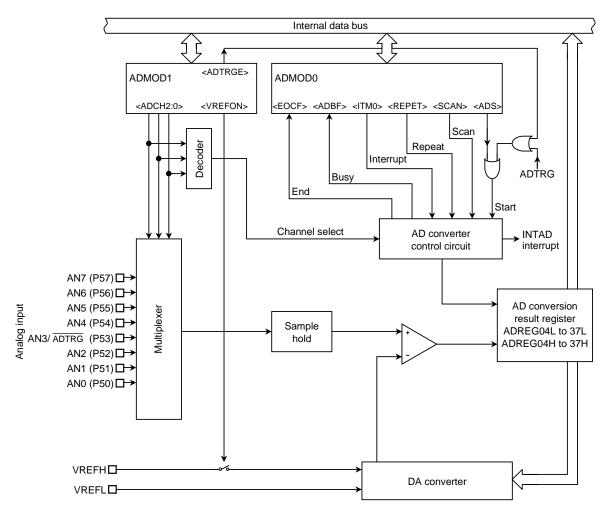

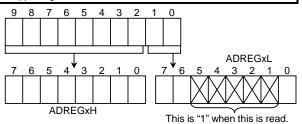

- (9) 10-bit AD converter: 8 channels

- (10) High current output: 8 ports

- (11) Watchdog timer

- (12) Bus width/wait controller: 3 blocks

- (13) Interrupt functions: 33

- 9 CPU interrupts

- 17 internal interrupts

7 external interrupts

7-level priority can be set (except NMI and INTWD)

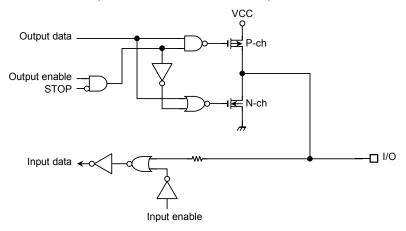

- (14) I/O ports

| TMP93CS44 | 62 pins |

|-----------|---------|

| TMP93CS45 | 44 pins |

- (15) Standby function: 4 HALT modes (RUN, IDLE2, IDLE1, STOP)

- (16) Clock gear function

- Dual clock operation

- High-frequency clock can be changed from fc to fc/16

- (17) Wide range of operating voltage

- $V_{CC} = 2.7 \text{ to } 5.5 \text{ V}$

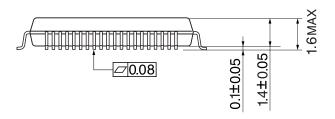

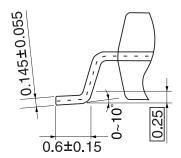

- (18) Package

| Type Number              | Package             |

|--------------------------|---------------------|

| TMP93CS44F<br>TMP93CS45F | P-LQFP80-1212-0.50E |

Note: The pin state after reset.

| Product             | AM8/ AM16 | Pin Function after Reset                                                                                                                  |

|---------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| TMP93CS44           | "H" level | Item in parentheses ( ) are the initial setting after reset.                                                                              |

|                     | "H" level | Except for "*" pins, item in parentheses ( ) are the initial setting after reset.                                                         |

| TMP93CS45 "L" level |           | Except for "*" pins, item in parentheses ( ) are the initial setting after reset. However, port 1 is initialized item of out parentheses. |

Figure 1.1 TMP93CS44/TMP93CS45 Block Diagram

# 2. Pin Assignment and Functions

The assignment of input and output pins for the TMP93CS44/TMP93CS45, their names and functions are described below.

# 2.1 Pin Assignment

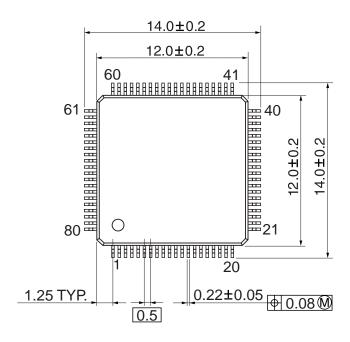

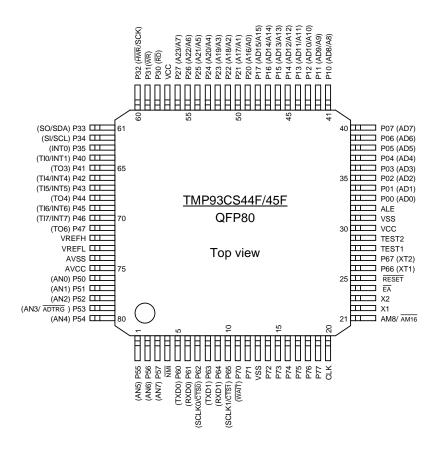

Figure 2.1.1 shows pin assignment of the TMP93CS44F/TMP93CS45F.

Figure 2.1.1 Pin Assignment (P-LQFP80-1212-0.50E)

# 2.2 Pin Names and Functions

The names of input/output pins and their functions are described below. Table 2.2.1 to Table 2.2.3 show "Pin Names and Functions".

Table 2.2.1 Pin Names and Functions (1/3)

| Pin Names       | Number of Pins | I/O      | Functions                                                                            |  |

|-----------------|----------------|----------|--------------------------------------------------------------------------------------|--|

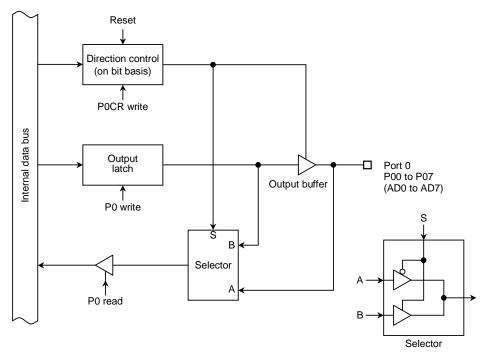

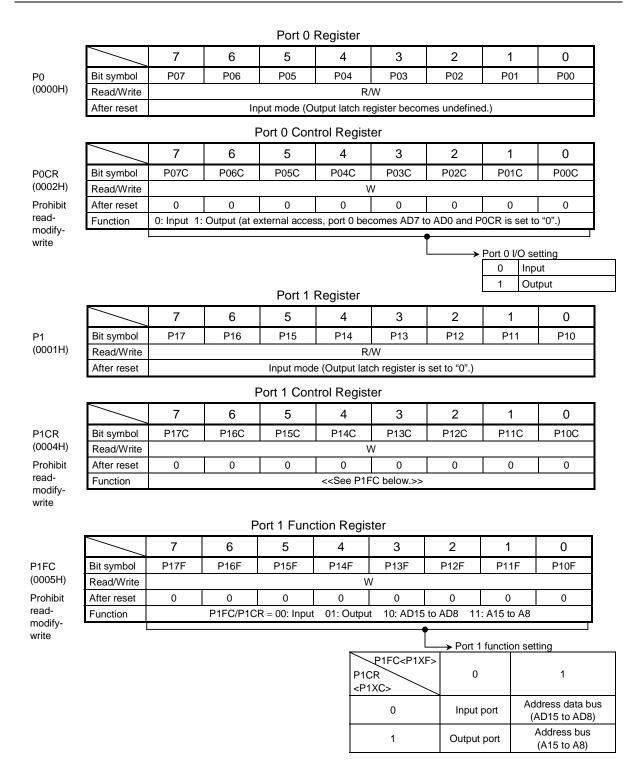

| P00 to P07      | 8              | I/O      | Port 0: I/O port that allows selection of I/O on a bit basis                         |  |

| AD0 to AD7      |                | 3 states | Address/data (Lower): Bits 0 to 7 for address/data bus                               |  |

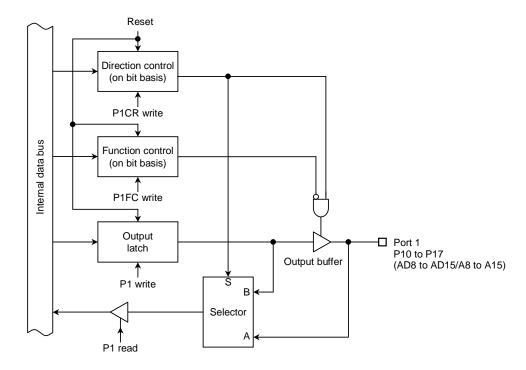

| P10 to P17      | 8              | I/O      | Port 1: I/O port that allows selection of I/O on a bit basis                         |  |

| AD8 to AD15     |                | 3 states | Address/data (Upper): Bits 8 to 15 for address/data bus                              |  |

| A8 to A15       |                | Output   | Address: Bits 8 to 15 for address bus                                                |  |

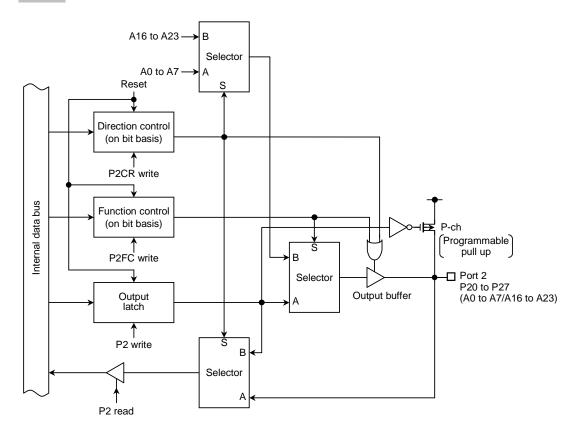

| P20 to P27      | 8              | I/O      | Port 2: I/O port that allows selection of I/O on a bit basis (with pull-up resistor) |  |

| A0 to A7        |                | Output   | Address: Bits 0 to 7 for address bus                                                 |  |

| A16 to A23      |                | Output   | Address: Bits 16 to 23 for address bus                                               |  |

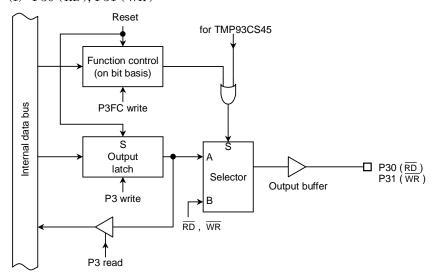

| P30             | 1              | Output   | Port 30: Output port                                                                 |  |

| RD              |                | Output   | Read: Strobe signal for reading external memory                                      |  |

| P31             | 1              | Output   | Port 31: Output port                                                                 |  |

| $\overline{WR}$ |                | Output   | Write: Strobe signal for writing data on pins AD0 to AD7                             |  |

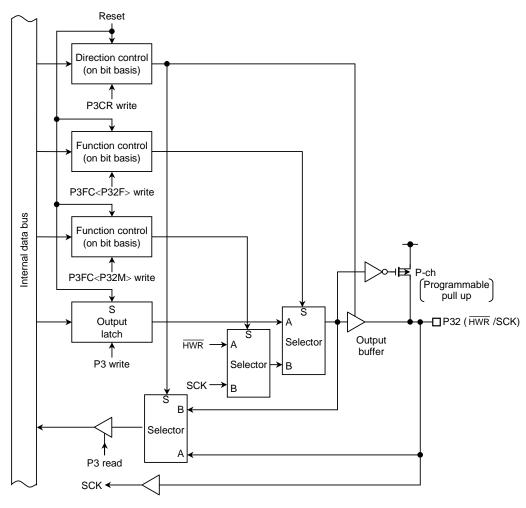

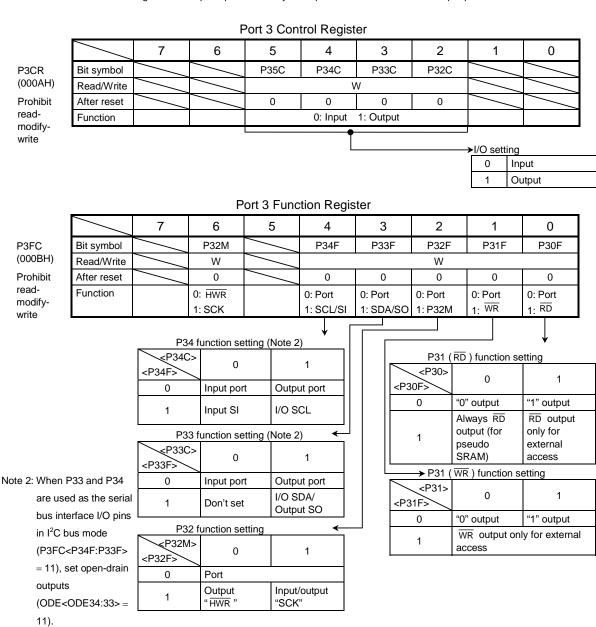

| P32             | 1              | I/O      | Port 32: I/O port (with pull-up resistor)                                            |  |

| HWR             |                | Output   | High write: Strobe signal for writing data on pins AD8 to AD15                       |  |

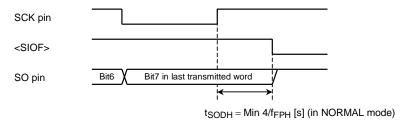

| SCK             |                | I/O      | Mode clock SBI SIO mode clock                                                        |  |

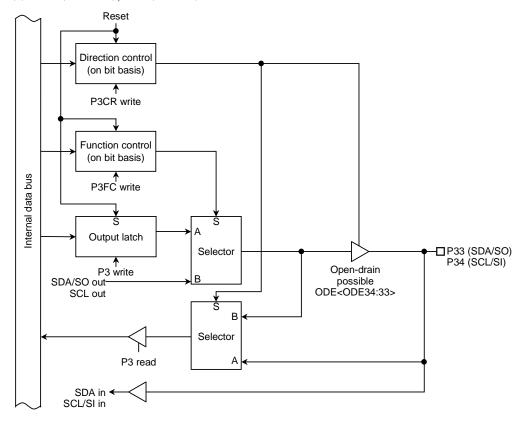

| P33             | 1              | I/O      | Port 33: I/O port                                                                    |  |

| SO              |                | Output   | Serial send data                                                                     |  |

| SDA             |                | I/O      | SBI I <sup>2</sup> C bus mode channel data                                           |  |

| P34             | 1              | I/O      | Port 34: I/O port                                                                    |  |

| SI              |                | Input    | Serial receive data                                                                  |  |

| SCL             |                | I/O      | SBI I <sup>2</sup> C bus mode clock                                                  |  |

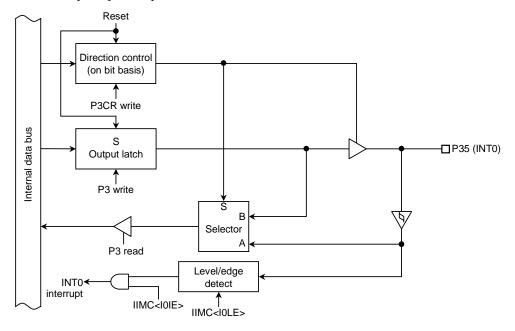

| P35             | 1              | I/O      | Port 35: I/O port                                                                    |  |

| INT0            |                | Input    | Interrupt request pin 0: Interrupt request pin with programmable level/rising edge   |  |

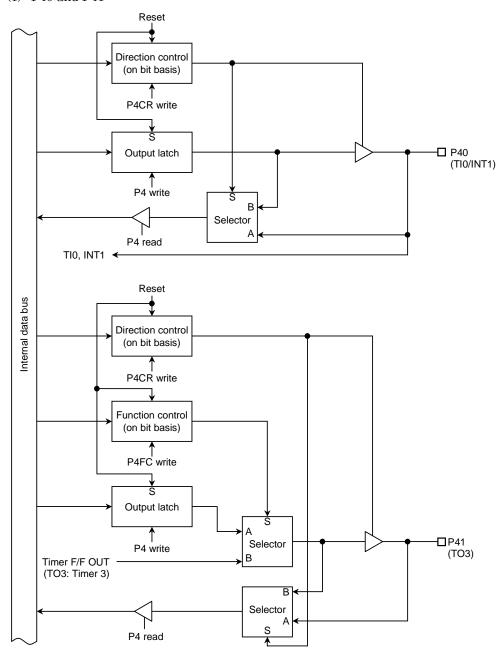

| P40             | 1              | I/O      | Port 40: I/O port                                                                    |  |

| TI0             |                | Input    | Timer input 0: Timer 0 input                                                         |  |

| INT1            |                | Input    | Interrupt request pin 1: Interrupt request pin with rising edge                      |  |

| P41             | 1              | I/O      | Port 41: I/O port                                                                    |  |

| TO3             |                | Output   | Timer output 3: 8-bit timer 3 output                                                 |  |

| P42             | 1              | I/O      | Port 42: I/O port                                                                    |  |

| TI4             |                | Input    | Timer input 4: Timer 4 input                                                         |  |

| INT4            |                | Input    | Interrupt request pin 4: Interrupt request pin with programmable rising/falling edge |  |

Table 2.2.2 Pin Names and Functions (2/3)

| Pin Names                 | Number of Pins | I/O    | Functions                                                                            |  |  |  |

|---------------------------|----------------|--------|--------------------------------------------------------------------------------------|--|--|--|

| P43                       | 1              | I/O    | Port 43: I/O port                                                                    |  |  |  |

| TI5                       |                | Input  | Timer input 5: Timer 4 input                                                         |  |  |  |

| INT5                      |                | Input  | Interrupt request pin 5: Interrupt request pin with rising edge                      |  |  |  |

| P44                       | 1              | I/O    | Port 44: I/O port                                                                    |  |  |  |

| TO4                       |                | Output | Timer output 4: Timer 4 output pin                                                   |  |  |  |

| P45                       | 1              | I/O    | Port 45: I/O port                                                                    |  |  |  |

| TI6                       |                | Input  | Timer input 6: Timer 5 input                                                         |  |  |  |

| INT6                      |                | Input  | Interrupt request pin 6: Interrupt request pin with programmable rising/falling edge |  |  |  |

| P46                       | 1              | I/O    | Port 46: I/O port                                                                    |  |  |  |

| TI7                       |                | Input  | Timer input 7: Timer 5 input                                                         |  |  |  |

| INT7                      | İ              | Input  | Interrupt request pin 7: Interrupt request pin with rising edge                      |  |  |  |

| P47                       | 1              | I/O    | Port 47: I/O port                                                                    |  |  |  |

| TO6                       |                | Output | Timer output 6: Timer 5 output pin                                                   |  |  |  |

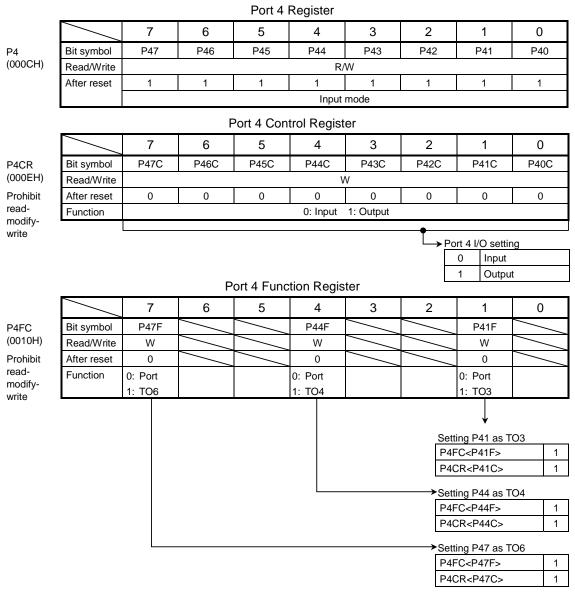

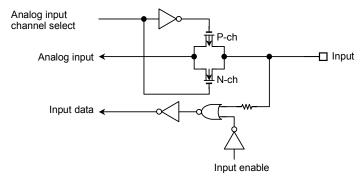

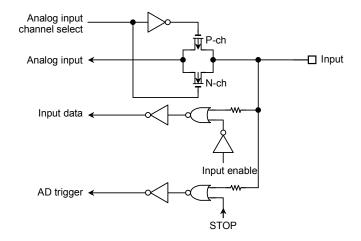

| P50 to P52,<br>P54 to P57 | 7              | Input  | Port 50 to Port 52, Port 54 to Port 57: Input port                                   |  |  |  |

| AN0 to AN2,<br>AN4 to AN7 |                | Input  | Analog input: Analog signal input for AD converter                                   |  |  |  |

| P53                       | 1              | Input  | Port53: Input port                                                                   |  |  |  |

| AN3                       |                | Input  | Analog input: Analog signal input for AD converter                                   |  |  |  |

| ADTRG                     |                | Input  | AD converter external start trigger input                                            |  |  |  |

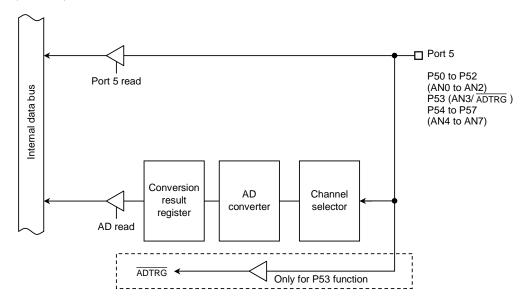

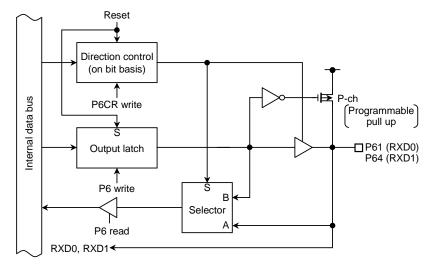

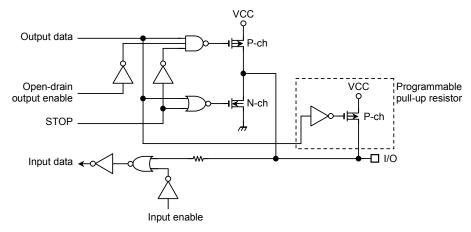

| P60                       | 1              | I/O    | Port 60: I/O port (with pull-up resistor)                                            |  |  |  |

| TXD0                      |                | Output | Serial send data 0                                                                   |  |  |  |

| P61                       | 1              | I/O    | Port 61: I/O port (with pull-up resistor)                                            |  |  |  |

| RXD0                      |                | Input  | Serial receive data 0                                                                |  |  |  |

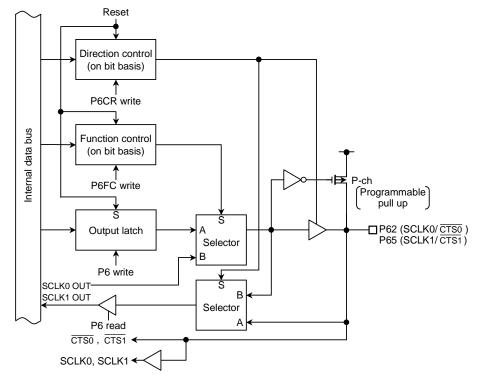

| P62                       | 1              | I/O    | Port 62: I/O port (with pull-up resistor)                                            |  |  |  |

| SCLK0                     |                | I/O    | Serial clock I/O 0                                                                   |  |  |  |

| CTS0                      |                | Input  | Serial data send enable 0 (Clear to send)                                            |  |  |  |

| P63                       | 1              | I/O    | Port 63: I/O port (with pull-up resistor)                                            |  |  |  |

| TXD1                      |                | Output | Serial send data 1                                                                   |  |  |  |

| P64                       | 1              | I/O    | Port 64: I/O port (with pull-up resistor)                                            |  |  |  |

| RXD1                      |                | Input  | Serial receive data 1                                                                |  |  |  |

| P65                       | 1              | I/O    | Port 65: I/O port (with pull-up resistor)                                            |  |  |  |

| SCLK1                     | İ              | I/O    | Serial clock I/O 1                                                                   |  |  |  |

| CTS1                      |                | Input  | Serial data send enable 1 (Clear to send)                                            |  |  |  |

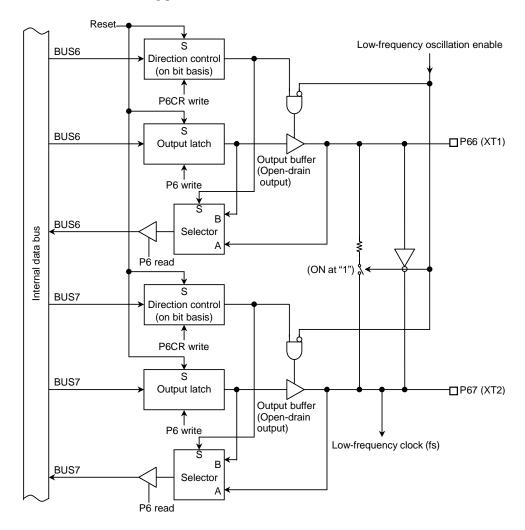

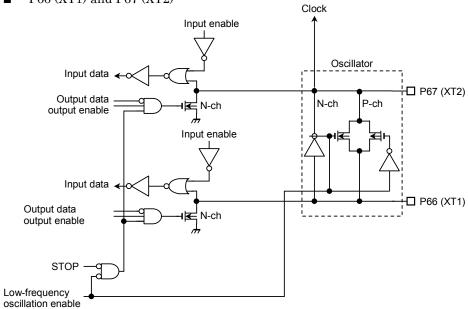

| P66                       | 1              | I/O    | Port 66: I/O port (Open-drain output)                                                |  |  |  |

| XT1                       |                | Input  | Low-frequency oscillator connecting pin                                              |  |  |  |

| P67                       | 1              | I/O    | Port 67: I/O port (Open-drain output)                                                |  |  |  |

| XT2                       |                | Output | Low-frequency oscillator connecting pin                                              |  |  |  |

Table 2.2.3 Pin Names and Functions (3/3)

| Pin Names   | Number of Pins | I/O          | Functions                                                                                                                                 |  |  |  |

|-------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

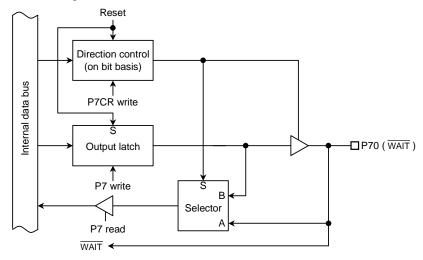

| P70         | 1              | I/O          | Port 70: I/O port (High current output available)                                                                                         |  |  |  |

| WAIT        |                | Input        | WAIT: Pin used to request CPU bus wait (It is active in (1 + N) WAIT mode. Set by the bus-width/wait control register)                    |  |  |  |

| P71 to P77  | 7              | I/O          | Port 71 to Port 77: I/O port (High current output available)                                                                              |  |  |  |

| AVCC        | 1              | Input        | Power supply pin for AD converter                                                                                                         |  |  |  |

| AVSS        | 1              | Input        | GND pin for AD converter (0 V)                                                                                                            |  |  |  |

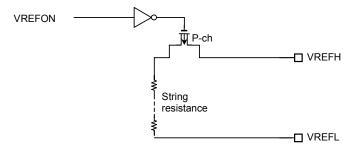

| VREFH       | 1              | Input        | Pin for high-level reference voltage input to AD converter                                                                                |  |  |  |

| VREFL       | 1              | Input        | Pin for low-level reference voltage input to AD converter                                                                                 |  |  |  |

| NMI         | 1              | Input        | Non-maskable interrupt request pin: Interrupt request pin with falling edge. Can also be operated at falling and rising edges by program. |  |  |  |

| X1          | 1              | Input        | High-frequency oscillator connecting pin                                                                                                  |  |  |  |

| X2          | 1              | Output       | High-frequency oscillator connecting pin                                                                                                  |  |  |  |

| RESET       | 1              | Input        | Reset: Initializes TMP93CS44/S45. (with pull-up resistor)                                                                                 |  |  |  |

| ALE         | 1              | Output       | Address latch enable. Can be disabled for reducing noise.                                                                                 |  |  |  |

| CLK         | 1              | Output       | Clock output: Outputs "f <sub>SYS</sub> ÷ 2" clock.                                                                                       |  |  |  |

|             |                |              | Pulled-up during reset.                                                                                                                   |  |  |  |

|             |                |              | Can be disabled for reducing noise.                                                                                                       |  |  |  |

| ĒĀ          | 1              | Input        | External access:                                                                                                                          |  |  |  |

|             |                |              | "0" should be inputted with TMP93CS45.                                                                                                    |  |  |  |

|             |                |              | "1" should be inputted with TMP93CS44.                                                                                                    |  |  |  |

| AM8/ AM16   | 1              | Input        | Address mode: Selects external data bus width.                                                                                            |  |  |  |

|             |                |              | (The case of TMP93CS44)                                                                                                                   |  |  |  |

|             |                |              | "1" should be inputted. The data bus width for external access is set by chip select/WAIT control register, port 1 control register.      |  |  |  |

|             |                |              | (The case of TMP93CS45) "0" should be inputted with fixed 16-bit bus width or 16-bit bus interlarded with 8-bit                           |  |  |  |

|             |                |              | bus. "1" should be inputted with fixed 8-bit bus width.                                                                                   |  |  |  |

| VCC         | 2              | Input        | Power supply pin (All VCC pins should be connected with GND (0 V).)                                                                       |  |  |  |

| VSS         | 2              | Input        | GND pin (0 V) (All VSS pins should be connected with GND (0 V).)                                                                          |  |  |  |

| TEST1/TEST2 | 2              | Output/Input | TEST1 should be connected with TEST2 pin. Do not connect to any other pins.                                                               |  |  |  |

Note: Built-in pull-up resistors can be released from the pins other than the  $\overline{\text{RESET}}$  pin by software.

# 3. Operation

This section describes the functions and basic operational blocks of TMP93CS44/S45 devices. See the 7. "Points of Note and Restriction" for the using notice and restrictions for each block.

#### 3.1 CPU

TMP93CS44/S45 devices have a built-in high-performance 16-bit CPU (900/L CPU). (For CPU operation, see TLCS-900/L CPU in the previous section.)

This section describes CPU functions unique to the TMP93CS44/S45 that are not described in the previous section.

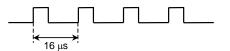

### 3.1.1 Reset

When resetting the TMP93CS44/S45 microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then set the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks (16  $\mu$ s at 20 MHz). Thus, when turn on the switch, be set to the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks.

Clock gear is initialized 1/16 mode by reset operation. It means that the system clock mode fsys is set to fc/32 (= fc/16  $\times$  1/2).

When reset is accepted, the CPU sets as follows:

Program counter (PC) according to reset vector that is stored FFFF00H to FFFF02H.

PC<7:0> ← Stored data in location FFFF00H PC<15:8> ← Stored data in location FFFF01H PC<23:16> ← Stored data in location FFFF02H

- Stack pointer (XSP) for system mode to 100H.

- Bits IFF2 to IFF0 of status register to 111. (Sets mask register to interrupt level 7.)

- MAX bit of status register to 1. (Sets to maximum mode.)

- Bits RFP2 to RFP0 of status register to 000. (Sets register banks to 0.)

When reset is released, instruction execution starts from PC (Reset vector). CPU internal registers other than the above are not changed.

When reset is accepted, processing for built-in I/Os, ports, and other pins is as follows.

- Initializes built-in I/O registers as per specifications.

- Sets port pins (including pins also used as built-in I/Os) to general-purpose input/output port mode.

- Pulls up the CLK pin to "H" level.

- Sets the ALE pin to "L" level (the case of TMP93CS45), to High-impedance (High-Z) (the case of TMP93CS44).

Note 1: By resetting, register in the CPU except program counter (PC), status register (SR) and stack pointer (XSP) and the data in internal RAM are not changed.

Note 2: The CLK pin is pulled up to "H" level during reset. When the voltage is put down externally, there is possible to cause malfunctions.

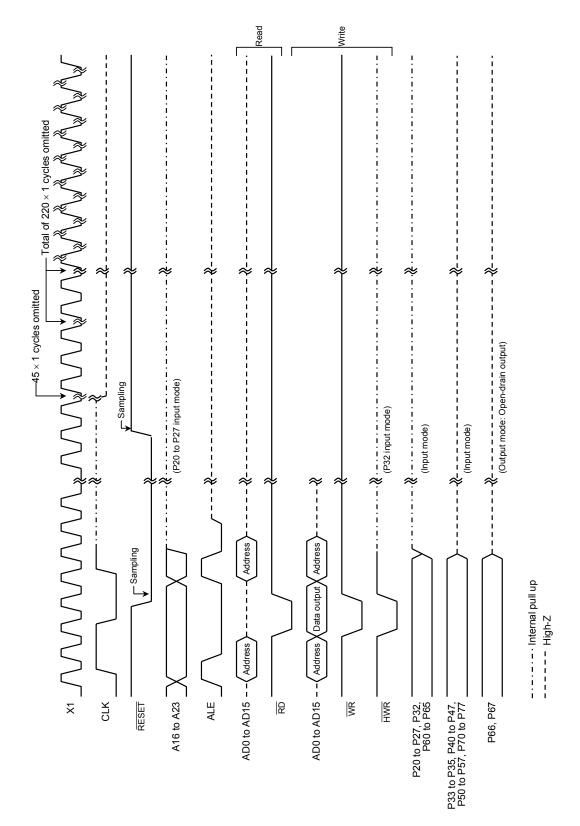

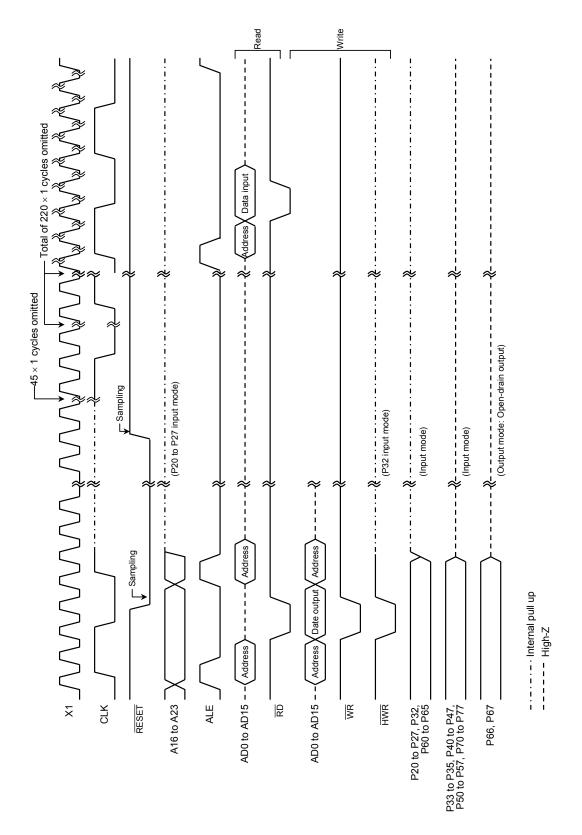

Figure 3.1.1 and Figure 3.1.2 show the reset timing chart of TMP93CS44 and TMP93CS45.

93CS44-8 2004-02-10

Figure 3.1.1 TMP93CS44 Reset Timing Chart

93CS44-9 2004-02-10

Figure 3.1.2 TMP93CS45 Reset Timing Chart

## 3.1.2 AM8/ AM16 pin

#### (1) TMP93CS44

Set this pin to "H". After reset, the CPU accesses the internal ROM with 16-bit bus width. The bus width when the CPU accesses an external area is set by bus width/wait control registers and the registers of port 1, which are described in section 3.6.3. (The value of this pin is ignored and the value set by register is active.)

#### (2) TMP93CS45

With fixed 16-bit data bus external 16-bit data bus or 8-bit data bus is selectable

Set this pm to "L". Port 1, AD8 to AD15 and A8 to A15 pins are fixed to AD8 to

AD15 functions. The values set in port 1 control register and port 1 function

register are invalid.

The external data bus width is set by the bus width/wait control register which is described in section 3.6.3.

It is necessary to set the program memory to be accessed to 16-bit data bus after reset.

#### 2. With fixed external 8-bit data bus

Set this pin to "H". Port l, AD8 to AD15 and A8 to A15 pins are fixed to A8 to A15 functions. The values set in port 1 control register and port 1 function register are invalid.

The values of bit4 <B0BUS>, <B1BUS> and <B2BUS> in the bus width/wait control register described in section 3.6.3 are invalid. The external 8-bit data bus is fixed.

# 3.2 Memory Map

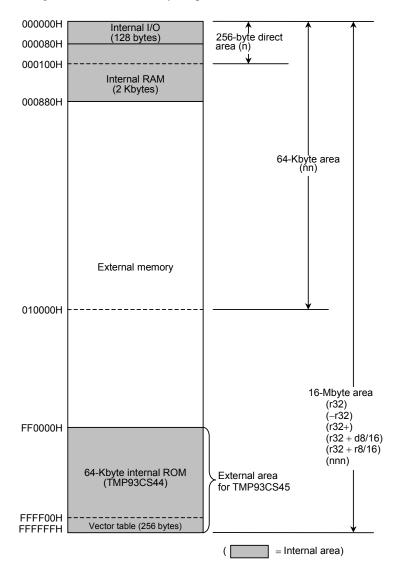

Figure 3.2.1 is a memory map of the TMP93CS44/S45.

Figure 3.2.1 Memory Map

# 3.3 Dual Clock, Standby Function

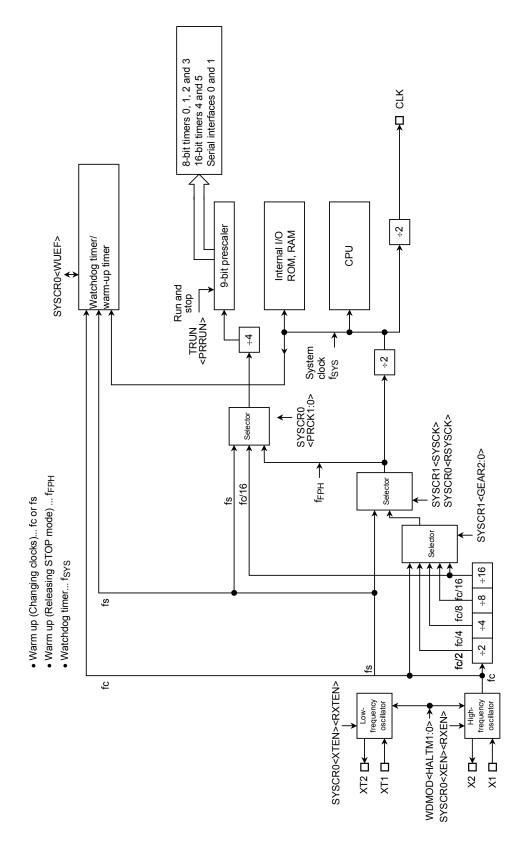

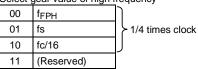

Dual clock, standby control circuits consist of (1) System clock controller, (2) Prescaler clock controller and (3) Standby controller.

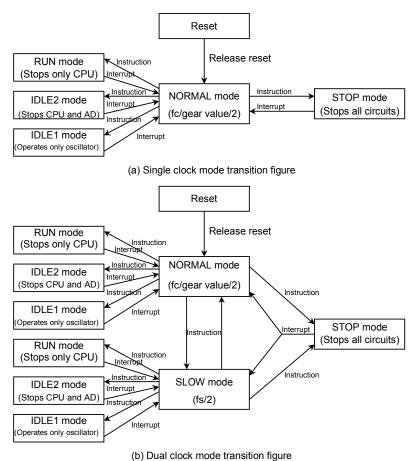

The oscillator operating mode is classified to (a) Single clock mode (Only X1 and X2 pin), and (b) Dual clock mode (X1, X2, XT1 and XT2 pin).

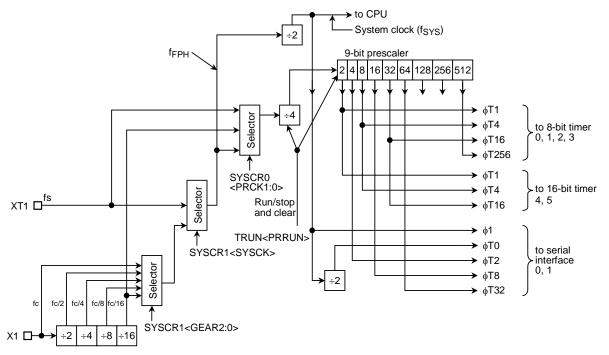

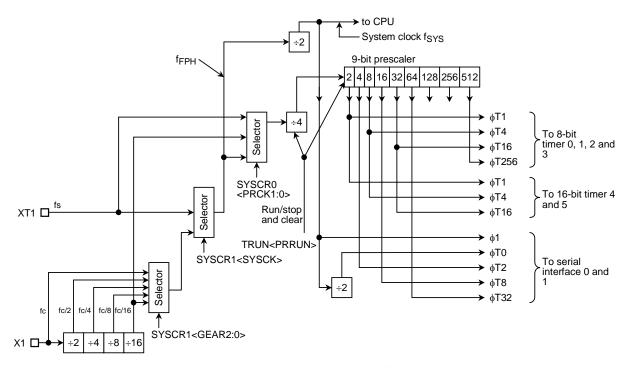

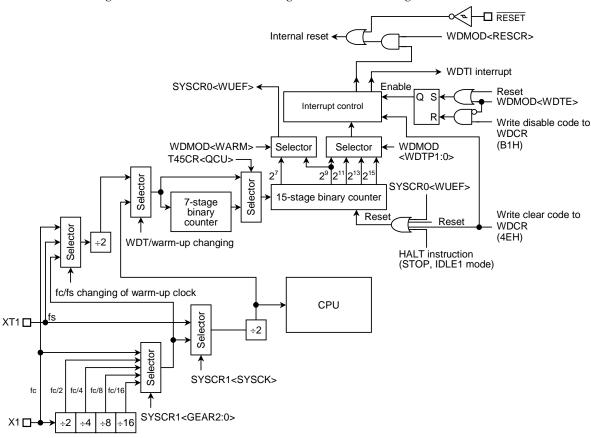

Figure 3.3.1 shows a transition figure. Figure 3.3.2 shows the block diagram. Figure 3.3.3 shows I/O registers. Table 3.3.1 shows the internal operation and system clock.

Figure 3.3.1 Transition Figure

The clock frequency input from X1, X2 pin is called fc and the clock frequency input from XT1, XT2 pin is called fs. The clock frequency selected by SYSCR1<SYSCK> is called system clock  $f_{FPH}$ . The devided clock of  $f_{FPH}$  is called system clock  $f_{SYS}$ , and the 1 cycle of  $f_{SYS}$ , is called 1 state.

Table 3.3.1 Internal Operation and System Clock

|                |        | Osci                           | llator                   |           |              | System Clock                                  |  |

|----------------|--------|--------------------------------|--------------------------|-----------|--------------|-----------------------------------------------|--|

| Operating Mode |        | High Frequency (fc)            | lency Low Frequency (fs) |           | Internal I/O | f <sub>SYS</sub>                              |  |

|                | RESET  |                                |                          | Reset     | Reset        | fc/32                                         |  |

|                | NORMAL |                                |                          | Operate   | Operate      |                                               |  |

| Single         | RUN    | Oscillation                    | Stop                     |           | Operate      | Programmable (fc/2, fc/4, fc/8,               |  |

| clock          | IDLE2  |                                | Stop                     | Stop      | Stop only AD | fc/16, fc/32)                                 |  |

|                | IDLE1  |                                |                          | Stop      | Stop         |                                               |  |

|                | STOP   | Stop                           |                          |           | Stop         | Stop                                          |  |

|                | RESET  | 0 "" "                         | Stop                     | Reset     | Reset        | fc/32                                         |  |

|                | NORMAL | Oscillation                    | Programmable             | Operate   |              | Programmable (fc/2, fc/4, fc/8, fc/16, fc/32) |  |

| Dual           | SLOW   | Programmable                   | Oscillation              | - portion | Operate      | fs/2                                          |  |

| clock          | RUN    | Oscillator being               | used as system           |           |              | Programmable                                  |  |

|                | IDLE2  | clock: Oscillation             | , i                      | Stop      | Stop only AD | (fc/2, fc/4, fc/8,                            |  |

|                | IDLE1  | Other oscillator: Programmable |                          | Stop      | Stop         | fc/16, fc/32, fs/2)                           |  |

|                | STOP   | St                             | ор                       |           | Stop         | Stop                                          |  |

Figure 3.3.2 Block Diagram of Dual Clock, Standby Circuits

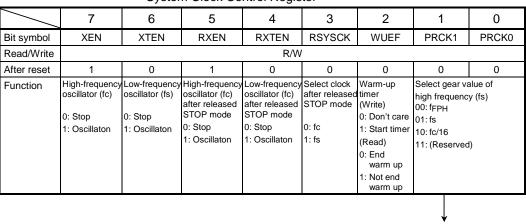

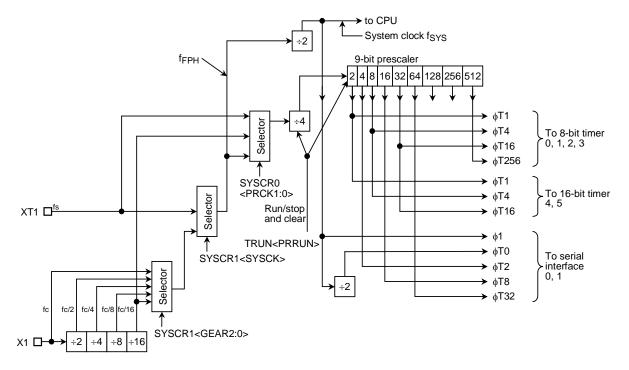

## System Clock Control Register 0

SYSCR0 (006EH)

|             | 7                                                                | 6                                                               | 5                                                                                                    | 4                                                                                                   | 3                                                                | 2                                                                                                                      | 1                                                                 | 0     |

|-------------|------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|

| Bit symbol  | XEN                                                              | XTEN                                                            | RXEN                                                                                                 | RXTEN                                                                                               | RSYSCK                                                           | WUEF                                                                                                                   | PRCK1                                                             | PRCK0 |

| Read/Write  |                                                                  |                                                                 |                                                                                                      | R/                                                                                                  | W                                                                |                                                                                                                        |                                                                   |       |

| After reset | 1                                                                | 0                                                               | 1                                                                                                    | 0                                                                                                   | 0                                                                | 0                                                                                                                      | 0                                                                 | 0     |

| Function    | High-<br>frequency<br>oscillator<br>(fc)  0: Stop 1: Oscillation | Low-<br>frequency<br>oscillator<br>(fs)  0: Stop 1: Oscillation | High-<br>frequency<br>oscillator<br>(fc) after<br>released<br>STOP mode<br>0: Stop<br>1: Oscillation | Low-<br>frequency<br>oscillator<br>(fs) after<br>released<br>STOP mode<br>0: Stop<br>1: Oscillation | Select clock<br>after<br>released<br>STOP mode<br>0: fc<br>1: fs | Warm-up<br>timer<br>(Write)<br>0: Don't care<br>1: Start timer<br>(Read)<br>0: End<br>warm up<br>1: Not end<br>warm up | Select presca<br>00: fFPH<br>01: fs<br>10: fc/16<br>11: (Reserved |       |

## System Clock Control Register 1

SYSCR1 (006FH)

|             | 7 | 6 | 5 | 4 | 3                                           | 2                                                                                                                             | 1     | 0            |

|-------------|---|---|---|---|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|--------------|

| Bit symbol  |   |   |   |   | SYSCK                                       | GEAR2                                                                                                                         | GEAR1 | GEAR0        |

| Read/Write  |   |   |   |   |                                             | R/                                                                                                                            | W     |              |

| After reset |   |   |   |   | 0                                           | 1                                                                                                                             | 0     | 0            |

| Function    |   |   |   |   | Select<br>system<br>clock<br>0: fc<br>1: fs | Select gear v<br>000: fc<br>001: fc/2<br>010: fc/4<br>011: fc/8<br>100: fc/16<br>101: (Reserv<br>110: (Reserv<br>111: (Reserv | red)  | equency (fc) |

## Clock Output Control Register

CKOCR (006DH)

|             | 7              | 6      | 5 | 4 | 3 | 2 | 1                                                     | 0                                                                 |

|-------------|----------------|--------|---|---|---|---|-------------------------------------------------------|-------------------------------------------------------------------|

| Bit symbol  | _              | -      |   |   |   |   | ALEEN                                                 | CLKEN                                                             |

| Read/Write  | R/             | W      |   |   |   |   |                                                       | W                                                                 |

| After reset | 0              | 0      |   |   |   |   | 0/1 (Note 2)                                          | 0/1 (Note 2)                                                      |

| Function    | Always write t | o "0". |   |   |   |   | ALE pin output control 0: High-Z output 1: ALE output | CLK pin<br>output control<br>0: High-Z<br>output<br>1: CLK output |

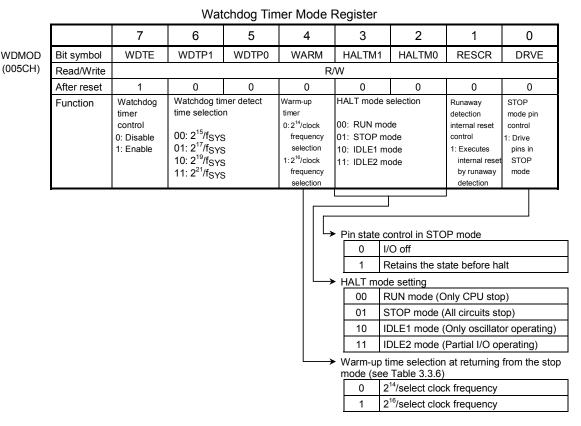

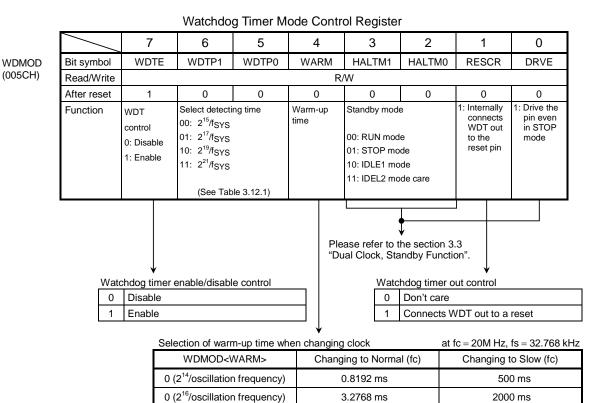

## Watchdog Timer Mode Control Register

WDMOD (005CH)

|             |                                   |                                                                                                                           | <u> </u> |                                                                                                                    |                                                                             |         |                                                               |                                                                                                 |

|-------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|             | 7                                 | 6                                                                                                                         | 5        | 4                                                                                                                  | 3                                                                           | 2       | 1                                                             | 0                                                                                               |

| Bit symbol  | WDTE                              | WDTP1                                                                                                                     | WDTP0    | WARM                                                                                                               | HALTM1                                                                      | HALTM0  | RESCR                                                         | DRVE                                                                                            |

| Read/Write  |                                   |                                                                                                                           |          | R/                                                                                                                 | W                                                                           |         |                                                               |                                                                                                 |

| After reset | 1                                 | 0                                                                                                                         | 0        | 0                                                                                                                  | 0                                                                           | 0       | 0                                                             | 0                                                                                               |

| Function    | WDT control  0: Disable 1: Enable | WDT detection  00: 2 <sup>15</sup> /fSYS  01: 2 <sup>17</sup> /fSYS  10: 2 <sup>19</sup> /fSYS  11: 2 <sup>21</sup> /fSYS | time     | Warm-up<br>timer<br>0: 2 <sup>14</sup> /<br>frequency<br>inputted<br>1: 2 <sup>16</sup> /<br>frequency<br>inputted | HALT mode<br>00: RUN mode<br>01: STOP mod<br>10: IDLE1 mod<br>11: IDLE2 mod | e<br>le | 0: Don't care 1: Connects WDT output to RESET pin internally. | Pin state<br>control in<br>STOP mode<br>0: I/O off<br>1: Remains<br>the state<br>before<br>halt |

- Note 1: SYSCR1<br/>bit7:4> and CKOCR<br/>bit5:2> are read as "1".

- Note 2: In the TMP93CS44, resetting sets <ALEEN>, <CLKEN> bit to "0" (High-impedance ALE and CLK). In the TMP93CS45, resetting sets <ALEEN>, <CLKEN> bit to "1" (output ALE and CLK). The CLK pin is internally pulled up during reset regardless of the product types.

- Note 3: Writing "0" to SYSCR1<SYSCK> enables the high-frequency oscillator regardless of the value of SYSCR0<XEN>. Additionally, writing "1" to <SYSCK> register enables the low-frequency oscillator regardless of th value of SYSCR0<XTEN>.

Figure 3.3.3 I/O Registers about Dual Clock, Standby

## 3.3.1 System Clock Controller

The system clock controller generates system clock (fsys) for CPU core and internal I/O. It contains two oscillation circuits and clock gear circuit for high frequency (fc). The register SYSCR1<SYSCK> changes system clock to either fc or fs, SYSCR0<XEN>, <XTEN> controls enable/disable each oscillator, SYSCR1<GEAR2:0> changes high-frequency clock gear to either 1, 2, 4, 8 or 16 (fc, fc/2, fc/4, fc/8 or fc/16), and these functions can reduce the power consumption of the equipment in which the device is installed.

The system clock (fsys) is set to fc/32 (fc/16  $\times$  1/2) because of  $\langle XEN \rangle = "1"$ ,  $\langle XTEN \rangle = "0"$ ,  $\langle SYSCK \rangle = "0"$ ,  $\langle GEAR2:0 \rangle = "100"$  by resetting. For example, fsys is set to 0.625 MHz by resetting the case of 20 MHz oscillator is connected to X1, X2 pins.

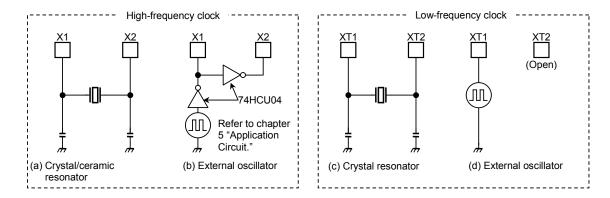

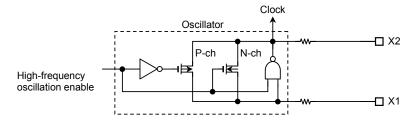

The high-frequency (fc) and low-frequency (fs) clocks can be easily obtained by connecting a resonator to the X1/X2, XT1/XT2 pins, respectively. Clock input from an external oscillator is also possible.

The XT1, XT2 pins have also port 66, 67 function. Therefore the case of single clock mode, the XT1, XT2 pins can be used as I/O port pins.

Figure 3.3.4 Examples of Resonator Connection

Note 1: Note on using the low-frequency oscillation circuit.

In connecting the low-frequency resonator to ports 66 and 67, it is necessary to make the following settings to reduce the power consumption.

(Connecting with resonators)

P6CR<P66C:67C> = "11", P6<P66:67> = "00"

(Connecting with oscillators)

P6CR<P66C:67C> = "11", P6<P66:67> = "10"

Note 2: Accurate adjustment of the oscillation frequency.

The CLK pin outputs at 1/2 the system clock frequency ( $f_{SYS}/2$ ) is used to monitor the oscillation clock. With a system requiring adjustment of the oscillation frequency, an adjusting program must be written.

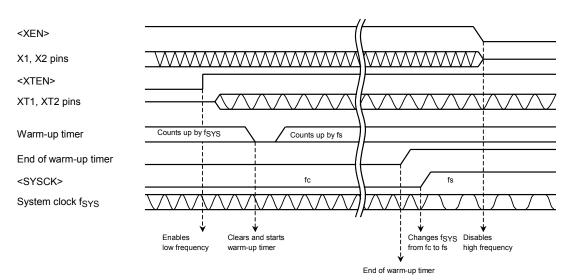

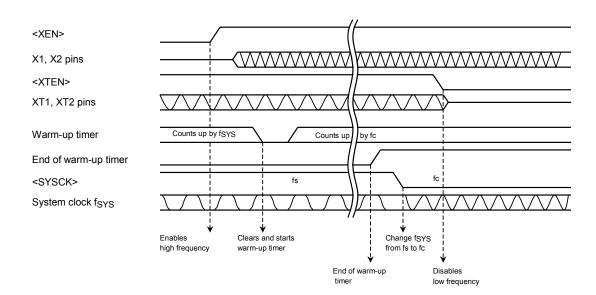

## (1) Switching from NORMAL to SLOW mode

When the resonator is connected to X1, X2, or XT1, XT2 pin, the warm-up timer is used to change the operation frequency after getting stabilized oscillation.

The warm-up time can be selected by WDMOD<WARM>.

This starting and ending of warm-up timer are performed like the following example 1, 2 by program.

- Note 1: The warm-up timer is also used as a watchdog timer. So, when it is used as a warm-up timer, the watchdog timer must be disabled.

- Note 2: The case of using oscillator (Not resonator) with stabilized oscillation, a warm-up timer is not need.

- Note 3: The warm-up timer is operated by a oscillation clock. Therefore, warm-up time has an error.

Table 3.3.2 Warm-up Time

| Warm-up Time<br>WDMOD <warm></warm> | Change to NORMAL | Change to SLOW |

|-------------------------------------|------------------|----------------|

| 0 (2 <sup>14</sup> /frequency)      | 0.8192 (ms)      | 500 (ms)       |

| 1 (2 <sup>16</sup> /frequency)      | 3.2768 (ms)      | 2000 (ms)      |

at fc = 20 MHz, fs = 32.768 kHz

## Clock setting example 1:

Changing from the high frequency (fc) to the low frequency (fs).

| SYSCR0 | EQU | 006EH       |                                             |

|--------|-----|-------------|---------------------------------------------|

| SYSCR1 | EQU | 006FH       |                                             |

| WDCR   | EQU | 005DH       |                                             |

| WDMOD  | EQU | 005CH       |                                             |

|        | RES | 7, (WDMOD)  | ; Disables watchder times                   |

|        | LD  | (WDCR), B1H | ; Disables watchdog timer.                  |

|        | SET | 4, (WDMOD)  | ; Sets warm-up time to 2 <sup>16</sup> /fs. |

|        | SET | 6, (SYSCR0) | ; Enables low-frequency oscillation         |

|        | SET | 2, (SYSCR0) | ; Clears and starts warm-up timer.          |

| WUP:   | BIT | 2, (SYSCR0) | ; Detects and of warm up timer              |

|        | JR  | NZ, WUP     | ) Detects end of warm-up timer.             |

|        | SET | 3, (SYSCR1) | ; Changes f <sub>SYS</sub> from fc to fs.   |

|        | RES | 7, (SYSCR0) | ; Disables high-frequency oscillation.      |

|        | SET | 7, (WDMOD)  | ; Enables watchdog timer.                   |

## Clock setting example 2:

Changing from the low frequency (fs) to the high frequency (fc).

| SYSCR0 | EQU | 006EH       |                                             |

|--------|-----|-------------|---------------------------------------------|

| SYSCR1 | EQU | 006FH       |                                             |

| WDCR   | EQU | 005DH       |                                             |

| WDMOD  | EQU | 005CH       |                                             |

|        | RES | 7, (WDMOD)  | ;                                           |

|        | LD  | (WDCR), B1H | ; Disables watchdog timer.                  |

|        | SET | 4, (WDMOD)  | ; Sets warm-up time to 2 <sup>14</sup> /fc. |

|        | SET | 7, (SYSCR0) | ; Enables high-frequency (fc).              |

|        | SET | 2, (SYSCR0) | ; Clears and starts warm-up timer.          |

| WUP:   | BIT | 2, (SYSCR0) | ; Detects end of warm-up timer.             |

|        | JR  | NZ, WUP     | ; Detects end of warm-up timer.             |

|        | SET | 3, (SYSCR1) | ; Changes f <sub>SYS</sub> from fs to fc.   |

|        | RES | 6, (SYSCR0) | ; Disables low-frequency oscillation.       |

|        | SET | 7, (WDMOD)  | ; Enable watchdog timer.                    |

### (2) Clock gear controller

When the high-frequency clock fc is selected at SYSCR1<SYSCK> = "0", the clock gear select register SYSCR1<GEAR2:0> sets fFPH to either fc, fc/2, fc/4, fc/8, fc/16. Switching fFPH with the clock gear reduces the power consumption.

Clock setting example 3:

Changing gear value of the high-frequency clock

SYSCR1 EQU 006FH

LD (SYSCR1), XXXX0000B ; Changes f<sub>SYS</sub> to fc/2. LD (SYSCR1), XXXX0100B ; Changes f<sub>SYS</sub> to fc/32.

X: Don't care

(High-frequency clock gear changing)

To change the frequency of the clock gear, write the value to SYSCR1<GEAR2:0> register. It is necessary to continue the warm-up time until changing after writing the register value.

There is a possibility that the instruction next to the clock gear changing instruction is executed by the clock gear before changing. To execute the instruction next to the clock gear changing instruction by the clock gear after changing, input the dummy instruction (Instruction to execute the write cycle) as follows.

Example: SYSCR1 EQU 006FH

LD (SYSCR1), XXXX0001B ; Changes f<sub>SYS</sub> to fc/4.

LD (DUMMY), 00H ; Dummy instruction.

Instruction to be executed by the clock gear after changing

X: Don't care

#### 3.3.2 Prescaler Clock Controller

The 9-bit prescaler provides a clock to 8-bit timer 0, 1, 2, 3, 16-bit timer 4, 5, and serial interface 0, 1.

The clock input to the 9-bit prescaler is selected either fFPH, fc/16, or fs by SYSCR0<PRCK1:0> register.

<PRCK1:0> register is initialized to "00" by resetting.

When the IDLE 1 mode (Operates only oscillator) is used, set TRUN<PRRUN> to "0" to stop 9 bit prescaler before "HALT" instruction is executed.

### 3.3.3 Internal Clock Pin Output Function

CLK pin outputs fsys divided by 2 internal clock.

Outputs are specified by the clock output control register CKOCR<CLKEN>. Writing "1" sets clock output, and writing "0" sets high impedance.

After reset, CKOCR<CLKEN> is depended on each product types. It is necessary to set for each usage. Table 3.3.3 shows the value and operation after reset.

During reset, CLK pin is internally pulled up regardless of the value of <CLKEN> register. See "TMP93CS44/S45 Reset Timing Chart" in Figure 3.1.1 and Figure 3.1.2.

Table 3.3.3 < CLKEN> and CLK Pin Operation after Reset

| Type Number | CKOCR <clken></clken> | CLK Pin Operation                |

|-------------|-----------------------|----------------------------------|

| TMP93CS44   | 0                     | High impedance                   |

| TMP93CS45   | 1                     | f <sub>SYS</sub> /2 clock output |

Note: To set <CLKEN> = "0" and set CLK pin to high impedance, pull up externally to prevent through current which follows to the input buffer of CLK pin.

## 3.3.4 Standby Controller

#### (1) HALT mode

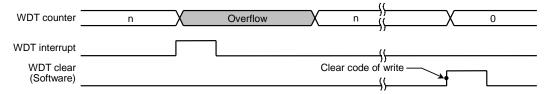

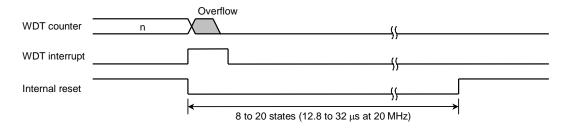

When the HALT instruction is executed, the operating mode changes RUN, IDLE2, IDLE1 or STOP mode depending on the contents of the HALT mode setting register WDMOD<HALTM1:0>. Figure 3.3.5 shows the alternative states of watchdog timer mode registers.

Figure 3.3.5 Watchdog Timer Mode Register

The futures of RUN, IDLE2, IDLE1 and STOP modes are as follows.

- 1. RUN: Only the CPU halts; power consumption remains unchanged.

- IDLE2: The built-in oscillator and the specified I/O operates.

The power consumption is reduced to 1/2 than that during NORMAL operation.

- 3. IDLE1: Only the built-in oscillator operates, while all other built-in circuits stop.

Consumption is reduced to 1/5 or less than that during NORMAL operation.

- 4. STOP: All internal circuits including the built-in oscillator stop.

This greatly reduces power consumption.

HALT mode RUN IDLE2 IDLE1 STOP WDMOD<HALTM1:0> 00 11 10 01 CPU I/O Port See Table 3.3.7 Keep the state when the "HALT" instruction was executed. 8-bit timer 16-bit timer **BLOCK** Serial channel Serial bus interface Operate Stop AD converter Watchdog timer

The operations in the halt state is described in Table 3.3.4.

# Table 3.3.4 I/O Operation during HALT Mode

### (2) How to release the HALT mode

Interrupt controller

These halt states can be released by resetting or requesting an interrupt. The halt release sources are determined by the combinations between the states of interrupt mask register <IFF2:0> and the HALT modes. The details for releasing the halt status are shown in Table 3.3.5.

#### Released by requesting an interrupt

The operating released from the HALT mode depends on the interrupt enabled status. When the interrupt request level set before executing the HALT instruction exceeds the value of the interrupt mask register, the interrupt due to the source is processed after releasing the HALT mode, and CPU starts executing an instruction that follows the HALT instruction. When the interrupt request level set before executing the HALT instruction is less than the value of the interrupt mask register, releasing the HALT mode is not executed (in non-maskable interrupts, interrupt processing is processed after releasing the HALT mode regardless of the value of the mask register.)

However only for INTO interrupts, even if the interrupt request level set before executing the HALT instruction is less than the value of the interrupt mask register, releasing the HALT mode is executed. In this case, interrupt processing is not processed, and CPU starts executing the instruction next to the HALT instruction, but the interrupt request flag is held at "1".

Note: Usually, interrupts can release all halts status. However, the interrupts = (NMI) INT0) which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of f<sub>EPH</sub>) with IDLE1 or STOP mode (RUN and IDLE2 are not applicable to this case). (In this case, an interrupt request is kept on hold internally.) If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with

### Release by resetting

Releasing all halt status is executed by resetting.

When the STOP mode is released by RESET, it is necessary enough resetting time (3 ms or more) to set the operation of the oscillator to be stable.

higher priority is handled first followed by the other interrupt.

When releasing the HALT mode by resetting, the internal RAM data keeps the state before the "HALT" instruction is executed. However the other setting contents are initialized. (Releasing due to interrupts keep the state before the "HALT" instruction is executed.)

| Int            | Interrupt Receiving Status |                    |     | Interrupt Enable<br>(Interrupt level) ≥ (Interrupt mask) |           |             | Interrupt Disable<br>(Interrupt level) < (Interrupt mask) |          |             |          |

|----------------|----------------------------|--------------------|-----|----------------------------------------------------------|-----------|-------------|-----------------------------------------------------------|----------|-------------|----------|

|                | НА                         | LT mode            |     | · · · · · ·                                              | · · · · · |             |                                                           | l .=. == | · · · · · · |          |

|                |                            |                    | RUN | IDLE2                                                    | IDLE1     | STOP        | RUN                                                       | IDLE2    | IDLE1       | STOP     |

|                |                            | NMI                | •   | •                                                        | •         | <b>♦</b> *1 | -                                                         | -        | -           | -        |

|                |                            | INTWDT             | •   | ×                                                        | ×         | ×           | _                                                         | _        | _           | _        |

|                |                            | INT0               | •   | •                                                        | •         | <b>♦</b> *1 | 0                                                         | 0        | 0           | 0*1      |

|                |                            | INT1, INT4 to INT7 | •   | •                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

|                |                            | INTT0 to INTT3     | •   | •                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

| Halt releasing | Interrupt                  | INTTR4 to INTTR7   | •   | •                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

| source         |                            | INTTO4, INTTO5     | •   | •                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

|                |                            | INTRX0, INTTX0     | •   | •                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

|                |                            | INTRX1, INTTX1     | •   | •                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

|                |                            | INTS2              | •   | •                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

|                |                            | INTAD              | •   | ×                                                        | ×         | ×           | ×                                                         | ×        | ×           | ×        |

|                | R                          | ESET               | •   | •                                                        | •         | •           | <b>*</b>                                                  | •        | •           | <b>*</b> |

Table 3.3.5 Halt Releasing Source and Halt Releasing Operation

- ♦: After releasing the HALT mode, CPU starts interrupt processing. (RESET initializes LSI.)

- After releasing the HALT mode, CPU starts executing an instruction that follows the HALT instruction

- x: It can not be used to release the HALT mode.

- -: This combination type does not exist because the priority level (Interrupt request level) of non-maskable interrupts is fixed to highest priority level "7".

- \*1: Releasing the HALT mode is executed after passing the warm-up time.

Note: When releasing the HALT mode is executed by INT0 interrupt of the level mode in the interrupt enabled status, hold level "H" until starting interrupt processing. If level "L" is set before holding level "L", interrupt processing is correctly started.

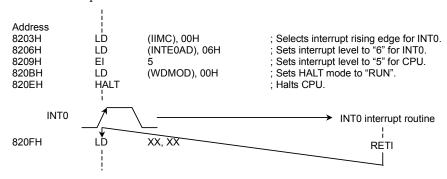

#### (Example releasing "RUN" mode)

INTO interrupt releases halt state when the RUN mode is on.

When halt is released by reset, the states (Including those of the internal RAM) before halt state was entered can be maintained. However, if the HALT instruction is executed within the internal RAM, the contents of the RAM may not be maintained. In this case, we recommend releasing the halt state using INTO.

#### (3) Operation

#### 1. RUN mode

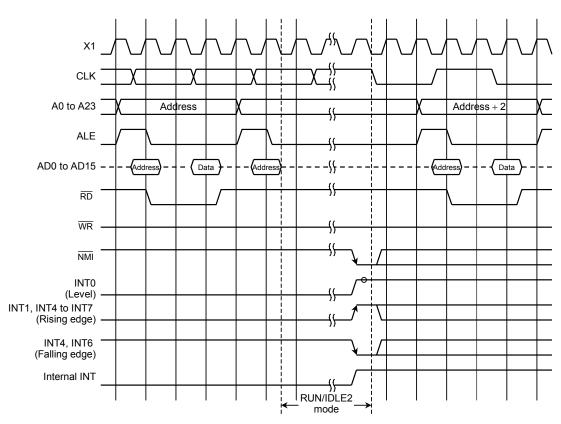

In the RUN mode, the system clock continues to operate even after a HALT instruction is executed.

Only the CPU stops executing the instruction. In the halt state, an interrupt request is sampled with the falling edge of the "CLK" signal.

Releasing the RUN mode is executed by the external/internal interrupts. (See Table 3.3.5 "Halt Releasing Source and Halt Releasing Operation".)

Figure 3.3.6 shows the interrupt timing for releasing the halt state by interrupts in the RUN/IDLE2 mode.

Figure 3.3.6 Timing Chart for Releasing the Halt State by Interrupt in RUN/IDLE2 Modes

#### 2. IDLE2 mode

In the IDLE2 mode, the system clock is supplied to only specific internal I/O devices, and the CPU stops executing the current instruction.

In the IDLE2 mode, the halt state is released by an interrupt with the same timing as in the RUN mode. The IDLE2 mode is released by external/internal interrupt, except INTWDT/INTAD interrupts. (See Table 3.3.5 "Halt Releasing Source and Halt Releasing Operation".)

In the IDLE2 mode, the watchdog timer should be disabled before entering the halt status to prevent the watchdog timer interrupt occurring just after releasing the HALT mode.

## 3. IDLE1 mode

In the IDLE1 mode, only the internal oscillator operates. The system clock in the MCU stops, the CLK pin is fixed at the level "H" in the output enable (CKOCR<CLKEN>="1").

In the halt state, and interrupt request is sampled asynchronously with the system clock, however the halt release (Restart of operation) is performed synchronously with it.

IDLE1 mode is released by external interrupts (NMI, INT0). (See Table 3.3.5 "Halt Releasing Source and Halt Releasing Operation".)

When the IDLE1 mode is used, setting TRUN<PRRUN> to "0" to stop 9-bit prescaler before "HALT" instruction reduces the power consumption.

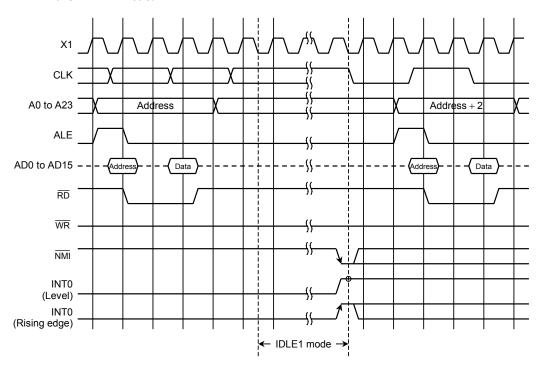

Figure 3.3.7 illustrates the timing for releasing the halt state by interrupts in the IDLE1 mode.

Figure 3.3.7 Timing Chart of Halt Released by Interrupts in IDLE1 Mode

## 4. STOP mode

The STOP mode is selected to stop all internal circuits including the internal oscillator. The pin status in the STOP mode depends on setting of a bit in the watchdog timer mode register WDMOD<DRVE>. (See Figure 3.3.5 for setting of WDMOD<DRVE>.) Table 3.3.7 summarizes the state of these pins in the STOP mode.

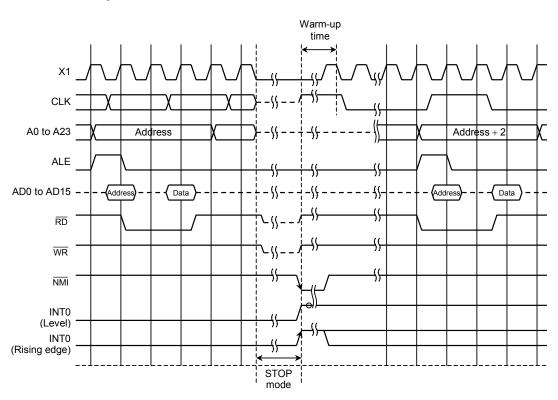

The STOP mode is released by external interrupts (NMI, INTO). When the STOP mode is released, the system clock output starts after warm-up time required to attain stable oscillation. The warm-up time can be set using WDMOD<WARM>. See the example of warm-up time (Table 3.3.6).

In a system which supplies stable clock generated by an external oscillator, the warm-up time can be reduced by using the setting of T45CR<QCU>.

Figure 3.3.8 illustrates the timing for releasing the halt state by interrupts during the STOP mode.

Figure 3.3.8 Timing Chart of Halt State Release by Interrupts in STOP Mode

| Clock Operation Frequency | Warm-up                 | Clock Frequency         |                   |  |

|---------------------------|-------------------------|-------------------------|-------------------|--|

| after the STOP Mode       | WDMOD <warm> = 0</warm> | WDMOD <warm> = 1</warm> | Olock i requericy |  |

| fc                        | 0.8192                  | 3.2768                  |                   |  |

| fc/2                      | 1.6384                  | 6.5536                  |                   |  |

| fc/4                      | 3.2768                  | 13.1072                 | fc = 20  MHz      |  |

| fc/8                      | 6.5536                  | 26.2144                 |                   |  |

| fc/16                     | 13.1072                 | 52.4288                 |                   |  |

| fs                        | 500                     | 2000                    | fs = 32.768 kHz   |  |

Table 3.3.6 The Example of Warm-up Time after Releasing the STOP Mode

How to calculate the warm-up time

WDMOD<WARM> = 0: Clock operation frequency after the  $2^{14}$ /STOP mode. WDMOD<WARM> = 1: Clock operation frequency after the  $2^{16}$ /STOP mode.

The NORMAL/SLOW mode selection is possible after released STOP mode. This is selected by SYSCR0<RSYSCK>. Therefore, Setting to <RSYSCK>, <RXEN>, <RXTEN> is necessary before "HALT" instruction is executed.

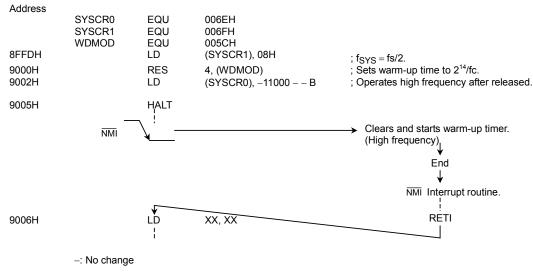

Setting example: The STOP mode is entered when the low-frequency (fs) operates, and after that high-frequency operates after releasing by  $\overline{\text{NMI}}$ .

Note: When different modes are used before and after STOP mode as the above mentioned, there is possible to release the HALT mode without changing the operation mode by acceptance of the halt release interrupt request during execution of "HALT" instruction (during 8 states). In the system which accepts the interrupts during execution "HALT" instruction, set the same operation mode before and after the STOP mode.

Table 3.3.7 Pin States in STOP Mode

| Din Name           | 1/0                             | TMP9              | 3CS44             | TMP93CS45                 |                   |  |

|--------------------|---------------------------------|-------------------|-------------------|---------------------------|-------------------|--|

| Pin Name           | I/O                             | <drve> = 0</drve> | <drve> = 1</drve> | <drve> = 0</drve>         | <drve> = 1</drve> |  |

| P00 to P07         | Input mode                      | <b>A</b>          | <b>A</b>          | ×                         | ×                 |  |

|                    | Output mode                     | High-Z            | Output            | ×                         | ×                 |  |

|                    | AD0 to AD7                      | High-Z            | High-Z            | High-Z                    | High-Z            |  |

| P10 to P17         | Input mode                      | <b>A</b>          | <b>A</b>          | ×                         | ×                 |  |

|                    | Output mode/A8 to A15           | High-Z            | Output            | ×                         | ×                 |  |

|                    | AD8 to AD15                     | High-Z            | High-Z            | High-Z                    | High-Z            |  |

| P20 to P27         | Input mode                      | <b>A</b>          | <b>A</b> .        | <b>A</b>                  | <b>A</b> .        |  |

|                    | Output mode A0 to A7/A16 to A23 | <b>A</b>          | Output            | <b>A</b>                  | Output            |  |

| P30 (RD), P31 (WR) | Output                          | High-Z            | Output            | High-Z                    | "H" level output  |  |

| P32 (HWR/SCK)      | Input mode                      | PU*               | PU                |                           |                   |  |

|                    | Output mode                     | PU*               | Output            |                           |                   |  |

| P33 to P35         | Input mode                      | Invalid           | Invalid           |                           |                   |  |

|                    | Output mode                     | High-Z            | Output            |                           |                   |  |

| P40 to P47         | Input mode                      | Invalid           | Invalid           |                           |                   |  |

|                    | Output mode                     | High-Z            | Output            |                           |                   |  |

| P50 to P57         | Input                           | <b>A</b>          | <b>A</b>          | The same as for           |                   |  |

| P60 to P65         | Input mode                      | PU*               | PU                | The same as for TMP93CS44 |                   |  |

|                    | Output mode                     | PU*               | Output            | TMF93C344                 |                   |  |

| P70 to P77         | Input mode                      | Invalid           | Invalid           |                           |                   |  |

|                    | Output mode                     | High-Z            | Output            |                           |                   |  |

| NMI                | Input                           | Input             | Input             |                           |                   |  |

| ALE                | Output ( <aleen> = 1)</aleen>   | "L" level output  | "L" level output  |                           |                   |  |

| CLK                | Output ( <clken> = 1)</clken>   | High-Z            | "H" level output  |                           |                   |  |

| RESET              | Input                           | Input             | Input             |                           |                   |  |

| ĒĀ                 | Input                           | "H" level fix     | "H" level fix     | "L" level fix             | "L" level fix     |  |

| AM8/ AM16          | Input                           | "H" level fix     | "H" level fix     | Input                     | Input             |  |

| X1                 | Input                           | Invalid           | Invalid           |                           |                   |  |

| X2                 | Output                          | "H" level output  | "H" level output  |                           |                   |  |

| P66                | Input mode                      | Invalid           | Invalid           |                           |                   |  |

|                    | Output mode                     | High-Z            | Output*           | The san                   | ne as for         |  |

|                    | XT1                             | •                 | •                 | TMP9                      | 3CS44             |  |

| P67                | Input mode                      | Invalid           | Invalid           |                           |                   |  |

|                    | Output mode                     | High-Z            | Output*           |                           |                   |  |

|                    | XT2                             | •                 | •                 |                           |                   |  |

Input: Input gate in operation. Fix input voltage to 0 or 1 so that the input pin stays constant.

Output: Output state.

Output\*: Open-drain output state. Input gate in operation. Set output to "L" or attach pull up on pin so that the input gate stays

constant.

Invalid: Input is not accepted.

High-Z: PU: Output is at high impedance.

Programmable pull-up pin in input gate in operation. Fix the pin to avoid through current since the input gate operates when a pull-up pin resistor is not set.

PU\*: Programmable pull-up pin in input gate disable state. No through current even if the pin is set to high impedance. When a HALT instruction is executed and the CPU stops at the address of the port register, an input gate operates. ▲:

Fix the pin to avoid through current, and change the program.

Cannot set. ×:

To connect a low-frequency resonator to port 66 and port 67, it is necessary to set the following procedures to reduce

the consumption power supply. (Connecting to a resonater)

Set P6CR<P66C:67C> = "11", P6<P66:67> = "00"

(Connecting to an oscillator) Set P6CR<P66C:67C> = "11", P6<P66:67> = "10"

Note: Port registers are used for controlling programmable pull up. If a pin is also used for an output function (e.g., TO3) and the output function is specified, whether pull up is selected depends on the output function data. If a pin is also used for an input function, whether pull up is selected depends on the port register setting value only.

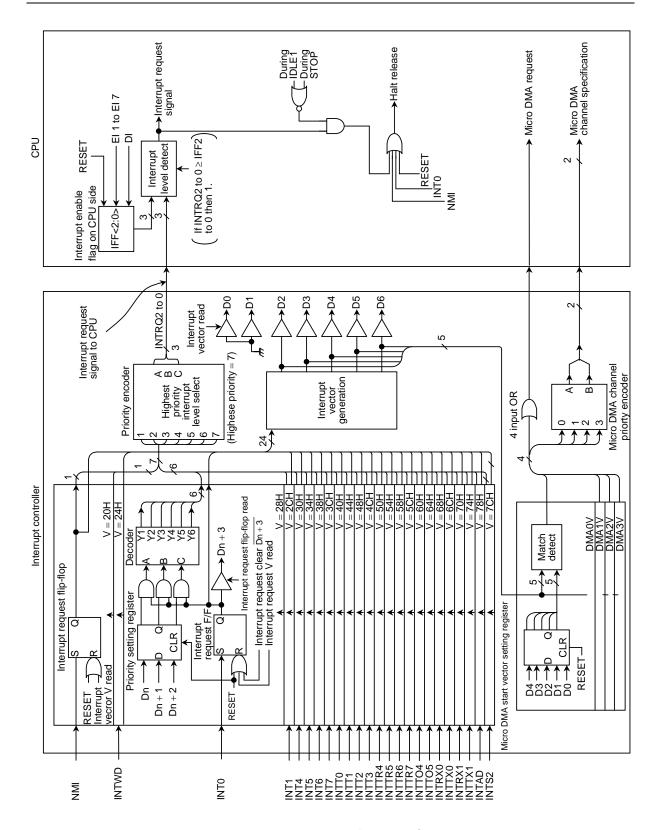

## 3.4 Interrupts

TLCS-900 interrupts are controlled by the CPU interrupt mask flip-flop <IFF2:0> and the built-in interrupt controller.

Altogether the TMP93CS44/S45 have the following 33 interrupt sources:

- Software interrupts: 8

- Illegal instruction execution: 1

- Interrupts from built-in I/Os: 17

External interrupts ...... 7

• External pins (NMI, INT0, INT1, INT4, to INT7)

A fixed individual interrupt vector number is assigned to each interrupt source; six levels of priority can also be assigned to each maskable interrupt. Non-maskable interrupts have a fixed priority of 7.

When an interrupt is generated, the interrupt controller sends the value of the priority of the interrupt source to the CPU. When more than one interrupt is generated simultaneously, the interrupt controller sends the value of the highest priority (7 for non-maskable interrupts is the highest) to the CPU.

The CPU compares the value of the priority sent with the value in the CPU interrupt mask register <IFF2:0>. If the value is greater than that the CPU interrupt mask register, the interrupt is accepted. The value in the CPU interrupt mask register <IFF2:0> can be changed using the EI instruction (Executing EI n changes the contents of <IFF2:0> to n). For example, programming EI 3 enables acceptance of maskable interrupts with a priority of 3 or greater, and non-maskable interrupts which are set in the interrupt controller. The DI instruction (<IFF2:0> = 7) operates in the same way as the EI 7 instruction. Since the priority values for maskable interrupts are 0 to 6, the DI instruction is used to disable acceptance of maskable interrupts. The EI instruction becomes effective immediately after execution (with the TLCS-90, the EI instruction becomes effective after execution of the subsequent instruction).

In addition to the general-purpose interrupt processing mode described above, there is also a micro DMA processing mode. Micro DMA is a mode used by the CPU to automatically transfer byte or word data. It enables the CPU to process interrupts such as data saves to built-in I/Os at high speed.

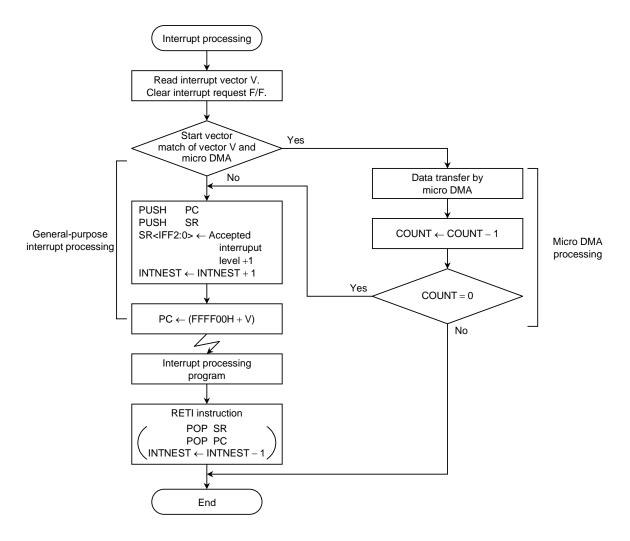

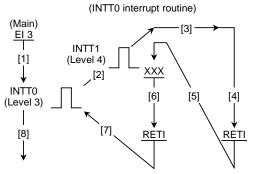

Figure 3.4.1 is a flowchart showing overall interrupt processing.

Figure 3.4.1 Interrupt Processing Flowchart

## 3.4.1 General-purpose Interrupt Processing

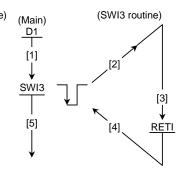

When accepting an interrupt, the CPU operates as follows. In the cases of software interrupts or interrupts generated by the CPU because of attempts to execute illegal instructions, the following steps (1) and (3) are not executed.

- (1) The CPU reads the interrupt vector from the interrupt controller. When more than one interrupt with the same level is generated simultaneously, the interrupt controller generates interrupt vectors in accordance with the default priority (which is fixed as follows: The smaller the vector value, the higher the priority), then clears the interrupt request.

- (2) The CPU pushes the program counter and the status register to the system stack area (Area indicated by the system mode stack pointer (XSP)).

- (3) The CPU sets a value in the CPU interrupt mask register <IFF2:0> that is higher by 1 than the value of the accepted interrupt level. However, if the value is 7, 7 is set without an increment.

- (4) The CPU increments the INTNEST (Interrupt nesting counter).

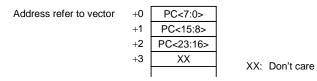

- (5) The CPU jumps to address stored at FFFF00H + interrupt vector, then starts the interrupt processing routine.

| mı e ii ·              | 1.      | 1      | 11  | . 1  | 1     |            |               |  |

|------------------------|---------|--------|-----|------|-------|------------|---------------|--|

| The following          | diagram | shows  | яII | the  | ahove | nrocessing | state number  |  |

| I II C I CII C W III S | aragram | DIIOWD | an  | ULIC | above | processing | budge mamber. |  |

| Bus Width of Stack<br>Area | Bus Width of<br>Interrupt Vector Area | Interrupt Processing State<br>Number |  |

|----------------------------|---------------------------------------|--------------------------------------|--|

| 8 bits                     | 8 bits                                | 35                                   |  |

| o bits                     | 16 bits                               | 31                                   |  |

| 16 bits                    | 8 bits                                | 29                                   |  |

| TO DIES                    | 16 bits                               | 25                                   |  |

To return to the main routine after completion of the interrupt processing, the RETI instruction is usually used. Executing this instruction restores the contents of the program counter and the status registers and decrements INTNEST (Interrupt nesting counter).

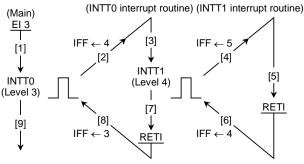

Though acceptance of non-maskable interrupts cannot be disabled by program, acceptance of maskable interrupts can. A priority can be set for each source of maskable interrupts. The CPU accepts an interrupt request with a priority higher than the value in the CPU mask register <IFF2:0>. The CPU mask register <IFF2:0> is set to a value higher by 1 than the priority of the accepted interrupt. Thus, if an interrupt with a level higher than the interrupt being processed is generated, the CPU accepts the interrupt with the higher level, causing interrupt processing to nest.

The interrupt request with a priority higher than the accepted now interrupt during the CPU is processing above (1) to (5) is accepted before the 1'st instruction in the interrupt processing routine, causing interrupt processing to nest. (This is the same case of over lapped each non-maskable interrupt (level 7).) The CPU does not accept an interrupt request of the same level as that of the interrupt being processed.

Resetting initializes the CPU mask registers <IFF2:0> to 7; therefore, maskable interrupts are disabled.

The following (1) to (5) show a flowchart of interrupt processing.

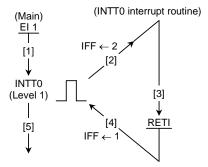

#### (1) Maskable interrupt

During execution of the main program, the CPU accepts an interrupt request. The CPU increments the IFF so that the interrupts of level 1 are not accepted during processing the interrupt routine.

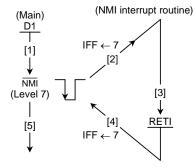

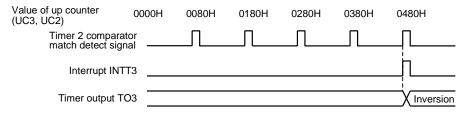

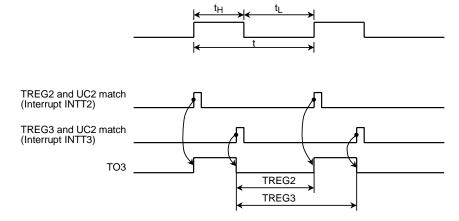

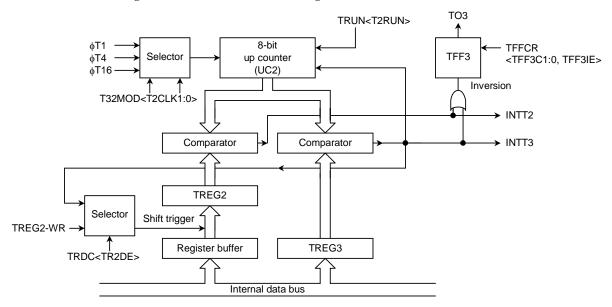

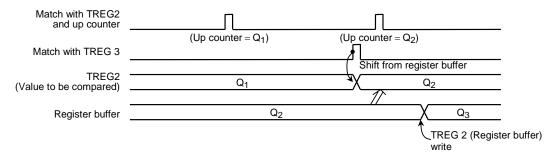

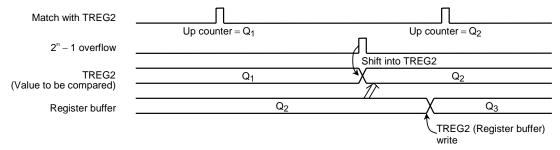

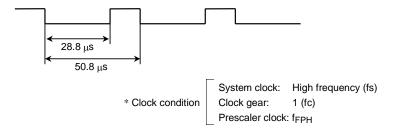

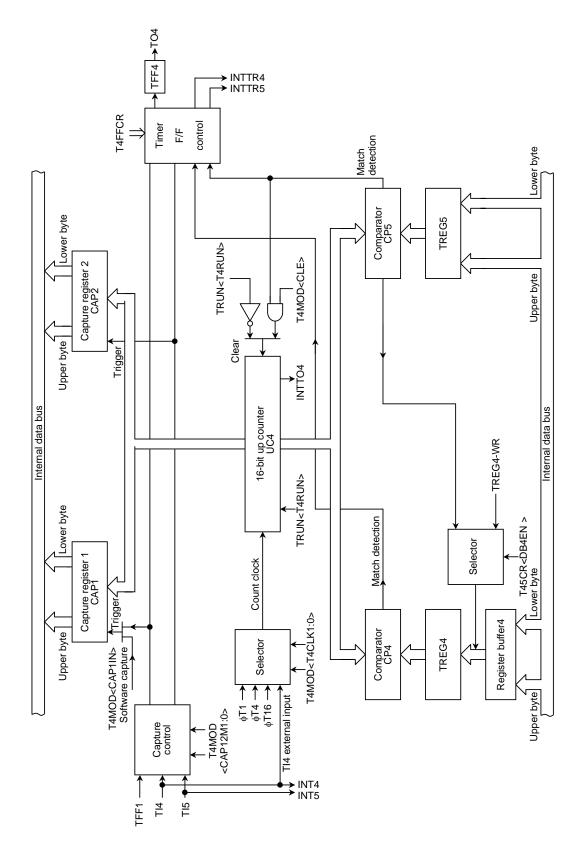

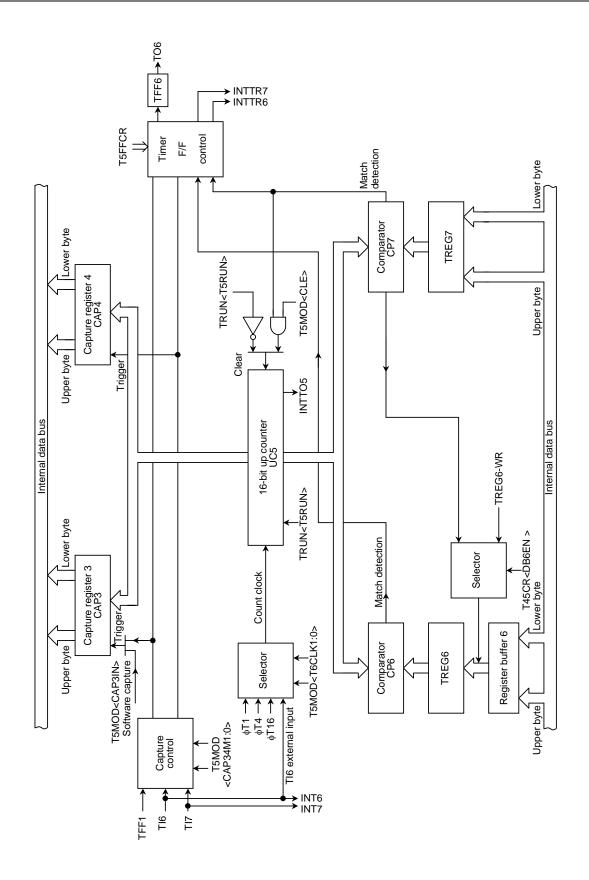

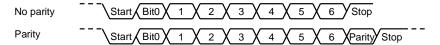

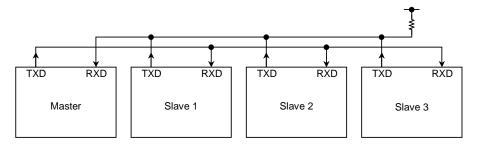

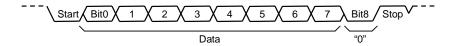

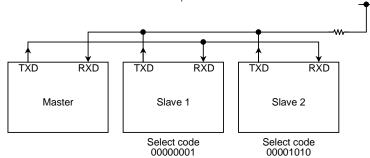

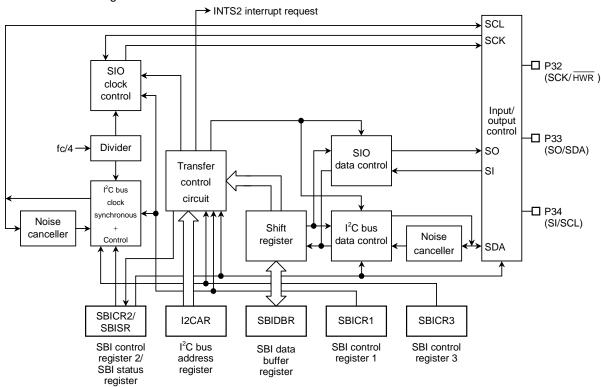

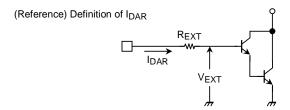

#### (2) Non-maskable interrupt