# **TOSHIBA**

TOSHIBA Original CMOS 16-Bit Microcontroller

TLCS-900/H Series

TMP95C001FG

# **TOSHIBA CORPORATION**

Semiconductor Company

# **Preface**

Thank you very much for making use of Toshiba microcomputer LSIs.

Before use this LSI, refer the section, "Points of Note and Restrictions".

Especially, take care below cautions.

#### \*\*CAUTION\*\*

How to release the HALT mode

Usually, interrupts can release all halts status. However, the interrupts = (NMI, INTO), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of X1) with IDLE or STOP mode. (In this case, an interrupt request is kept on hold internally.)

If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

# **Document Change Notification**

The purpose of this notification is to inform customers about the launch of the Po-free version of the device. The introduction of a Pb-free replacement affects the datasheet. Please understand that this notification is intended as a substitute for a revision of the datasheet.

Changes to the datasheet may include the following, though not all of them may apply to this particular device.

1. Part number

Example:  $TMPxxxxxxF \rightarrow TMPxxxxxxFG$

All references to the previous part number were left unchanged in body text. The new part number is indicated on the prelims pages (cover page and this notification).

2. Package code and package dimensions

Example: LQFP100-P-1414-0.50C → LQFP100-P-1414-0.50F

All references to the previous package code and package dimensions were left unchanged in body text. The new ones are indicated on the prelims pages.

3. Addition of notes on lead solderability

Now that the device is Pb-free, notes on lead solderability have been added.

4. RESTRICTIONS ON PRODUCT USE

The previous (obsolete) provision might be left unchanged on page 1 of body text. A new replacement is included on the next page.

5. Publication date of the datasheet

The publication date at the lower right corner of the prelims pages applies to the new device.

#### 1. Part number

| Previous Part Number (in Body Text) | New Part Number |

|-------------------------------------|-----------------|

| TMP95C001F                          | TMP95C001FG     |

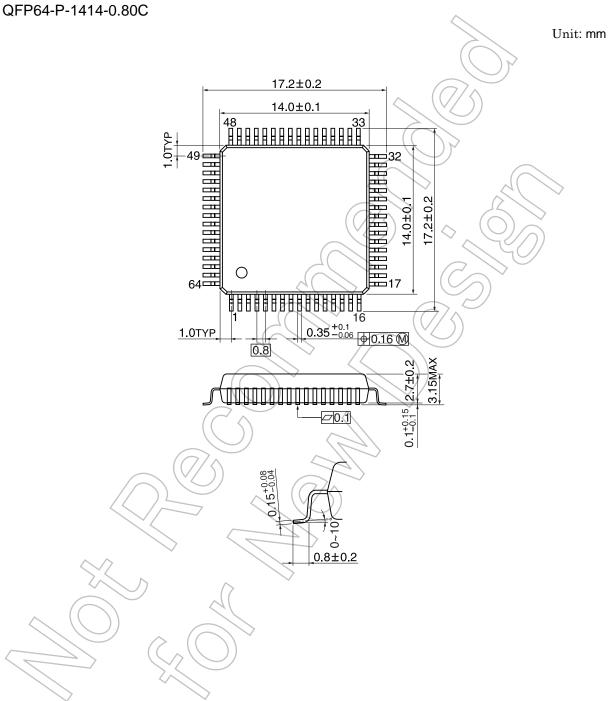

#### 2. Package code and dimensions

| Previous Package Code (in Body Text) | New Package Code   |

|--------------------------------------|--------------------|

| P-QFP64-1414-0.80A                   | QFP64-P-1414-0.80C |

<sup>\*:</sup> For the dimensions of the new package, see the attached Package Dimensions diagram.

#### 3. Addition of notes on lead solderability

The following solderability test is conducted on the new device.

#### Solderability of lead free products

| Test Parameter | Test Condition                                                                                                                                                                                                                                                                                  | Note                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Solderability  | Use of Sn-37Pb solder Bath Solder bath temperature = 230°C, Dipping time = 5 seconds The number of times = one, Use of R-type flux Use of Sn-3.0Ag-0.5Cu solder bath Solder bath temperature = 245°C, Dipping time = 5 seconds The number of times = one, Use of R-type flux (use of lead free) | Pass:<br>Solderability rate until forming<br>≥ 95% |

#### 4. RESTRICTIONS ON PRODUCT USE

The following replaces the "RESTRICTIONS ON PRODUCT USE" on page 1 of body text.

#### RESTRICTIONS ON PRODUCT USE

20070701-EN

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which

manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its

use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations that

regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring

as a result of noncompliance with applicable laws and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

#### 5. Publication date of the datasheet

The publication date of this datasheet is printed at the lower right corner of this notification.

TMP95C001 **TOSHIBA**

(Annex)

# Package Dimensions

III2008-02-20

# CMOS 16-Bit Microcontroller TMP95C001F

## 1. Outline and Features

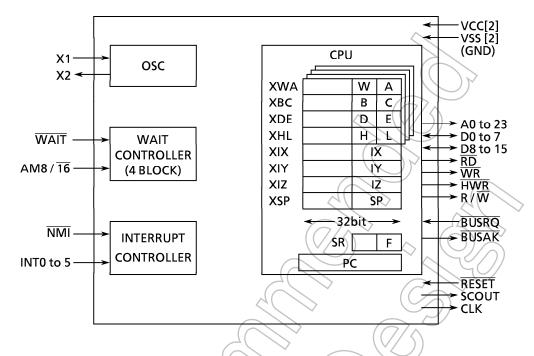

TMP95C001F is a 16-bit microcontroller of a high-speed 16-bit CPU (TLCS-900/H) core. It has only an indispensable function such as a wait controller, an interrupt controller, and etc.

TMP95C001F is presented in a 64-pin flat package. Its features are as follows.

- (1) High-speed 16-bit CPU (TLCS-900/H CPU)

- Instruction mnemonics upwardly compatible with TLCS-90/900

- 16M-byte linear address space

- General-purpose registers using register bank system

- 16-bit multiplication / division instructions, bit transfer / arithmetic instructions

- Micro DMA: four channels (640 ns / 2 bytes at 25 MHz)

- (2) Minimum instruction execution time: 160 ns (at 25 MHz)

- (3) Internal RAM : No Internal ROM : No

- (4) External memory expansion

- Expandable to 16 Mbytes (common to programs and data)

- External data bus width selection pin  $(AM8 / \overline{16})$

- Can use both 8- and 16-bit external buses ··· dynamic bus sizing

- (5) Wait controller: four blocks

- (6) Interrupt function

- Interrupt sources : 20

Internal interrupt: 13

External interrupt: 7

(7) Standby function

Three HALT modes (RUN, IDLE, STOP)

000707EBP1

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

**95C001-1** 2003-03-31

Figure 1 TMP95C001 Block Diagram

## 2. Pin Assignment and Functions

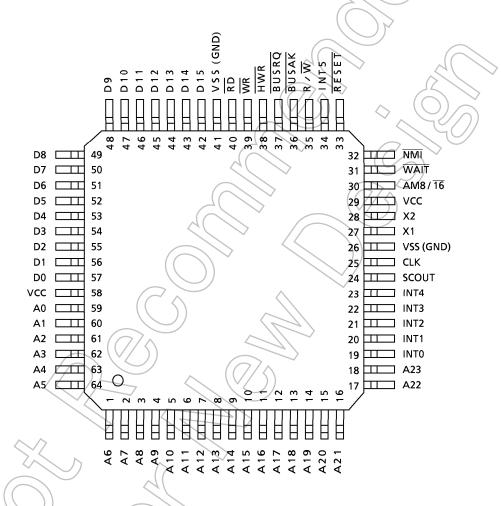

The assignment of input/output pins for TMP95C001F their name and outline functions are described below.

## 2.1 Pin Assignment

Figure 2.1 shows pin assignment of TMP95C001F.

Figure 2.1 Pin Assignment (64-pin QFP)

#### 2.2 Pin Names and Functions

Table 2.2 shows the I/O pin names and their functions.

Table 2.2 Pin Names and Functions

| Pin Name  | Pin<br>Number | Input /<br>Output | Function                                                                                                                                                                  |

|-----------|---------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

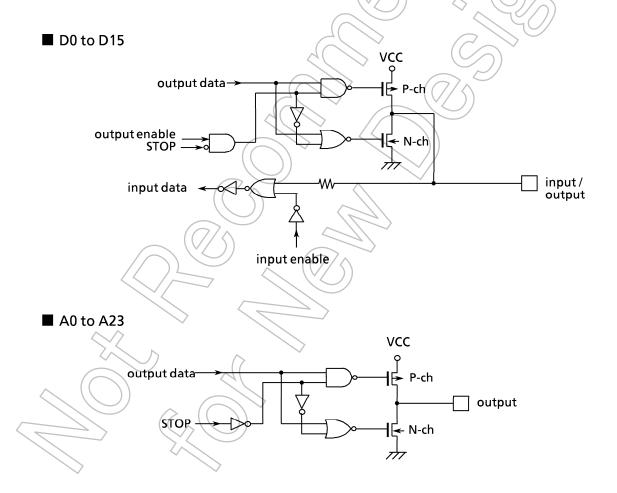

| D0 to D15 | 16            | Input /<br>Output | Data: Data bus 0 to 15                                                                                                                                                    |

| A0 to A23 | 24            | Output            | Address : Address bus 0 to 23                                                                                                                                             |

| RD        | 1             | Output            | Read: Strobe signal to read external memory Setting RSRAM mode outputs RD even when reading internal areas.                                                               |

| WR        | 1             | Output            | Write: Strobe signal to write data of pins D0 to 7.                                                                                                                       |

| HWR       | 1             | Output            | Upper write: Strobe signal for writing data of pins D8 to 15.                                                                                                             |

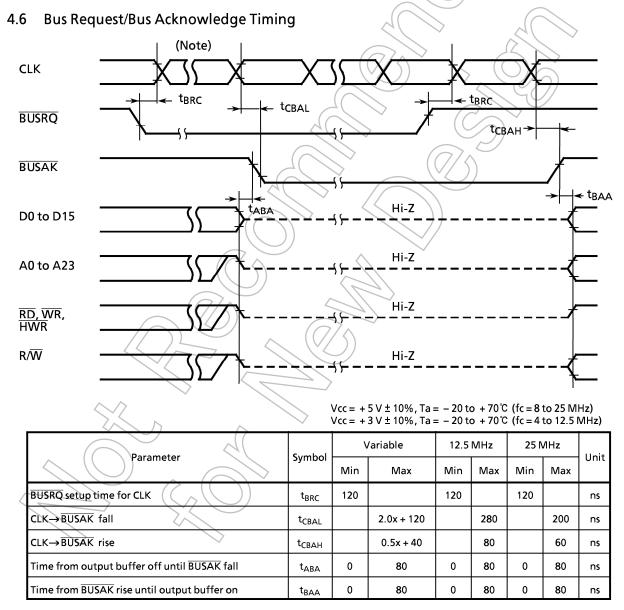

| BUSRQ     | 1             | Input             | Input Bus request: Signal to request external bus release.                                                                                                                |

| BUSAK     | 1             | Output            | Bus acknowledge: Signal to indicate external bus is released after receiving BUSRQ.                                                                                       |

| R/W       | 1             | Output            | Read/write: "T" indicates read or dummy cycle; "0" indicates write cycle.                                                                                                 |

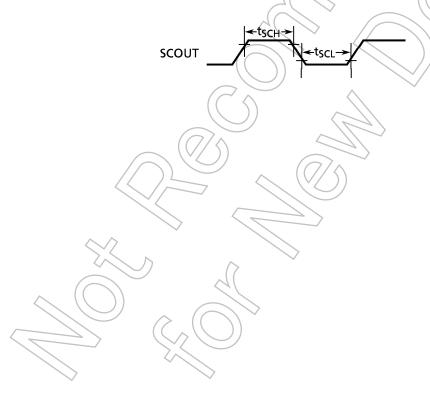

| SCOUT     | 1             | Output            | System clock output: Outputs system clock (external clock divided by 2).                                                                                                  |

| WAIT      | 1             | Input             | Wait: CPU bus wait request pin. (enabled in 1+N or 0+N WAIT mode).                                                                                                        |

| INT0      | 1             | Input             | Interrupt request pin 0: Can be programmed for level or rising-edge detection.                                                                                            |

| INT1 to 4 | 4             | Input//           | Interrupt request pin 1 to 4: Rising-edge interrupt request pin                                                                                                           |

| INT5      | 1//           | Input             | Interrupt request pin 5: Can be programmed for level or rising-edge detection.                                                                                            |

| NMI       | 1             | Input             | Non-maskable interrupt request pin: Can be programmed for falling-edge or falling-rising-edge detection.                                                                  |

| CLK       | \$2           | Output            | Clock output: Outputs external input clock X1 divided by 4. Pulled up during reset.                                                                                       |

| AM8/16    |               | Input             | Address mode: External data bus width selection pin. Set to 0 when using fixed 16-bit external bus or dual 8/16-bit external bus. Set to 1 with 8-bit external bus fixed. |

| RESET     | 1             | Input             | Reset: Initializes TMP95C001.<br>(with pull-up)                                                                                                                           |

| X1/X2     | 2             | Input/<br>Output  | Oscillator connecting pins                                                                                                                                                |

| VCC       | 2             |                   | Power supply pin (All Vcc pins should be connected with the power supply pin.)                                                                                            |

| VSS (GND) | 2             |                   | Ground pin (0 V) (All Vss pins should be connected with GND (0 V).)                                                                                                       |

Note: Connect all VCC pins to power supply and all VSS pins to GND.

## 3. Operation

The following is a block-by-block description of the functions and basic operation of TMP95C001.

Note that the description concludes with cautions and restrictions for each block in 7, Usage Cautions and Restrictions.

#### 3.1 CPU

TMP95C001 contains an advanced, high-speed 16-bit CPU (the TLCS-900/H\_CPU). The CPU is described in the TLCS-900 CPU section in the previous chapter.

The following describes the CPU functions unique to TMP95C001 that are not described in "TLCS-900 CPU".

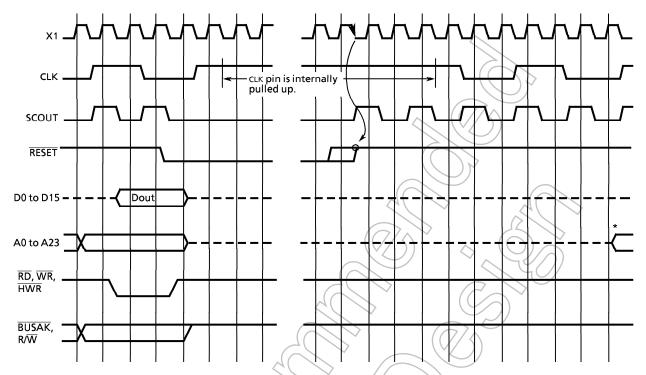

#### 3.1.1 Reset Operation

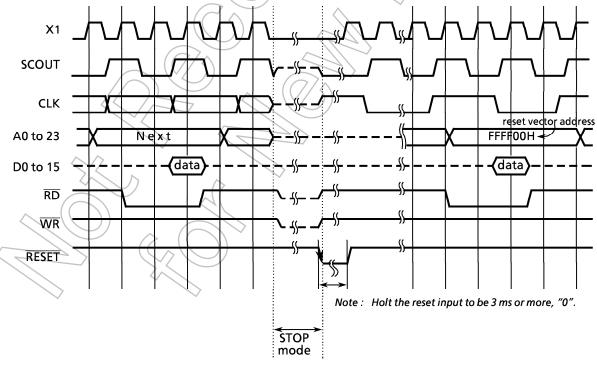

Figure 3.1 (1) shows reset timing.

At TMP95C001 reset, the power supply voltage must be within the operating range and internal oscillation must be stable. Set the RESET input to 0 for at least ten system clocks (= 10 states:  $0.8 \mu s$  for a 25-MHz clock).

When the reset is accepted, the CPU:

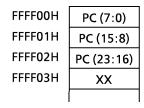

• Sets the program counter (PC) to the reset vector stored at addresses FFFF00H to FFFF02H.

PC (7:0)  $\leftarrow$  value at address FFFF00H PC (15:8)  $\leftarrow$  value at address FFFF01H

$PC(23:16) \leftarrow value at address FFFF02H$

- Sets the stack pointer (XSP) to 100H

- Sets bits IFF2 to 0 of the status register (SR) to 111 (this sets the interrupt level mask register to level 7).

- Sets the MAX bit of the status register (SR) to 1 (this sets maximum mode). (Note: This product does not support minimum mode. Do not set the MAX bit to 0.)

- Clears bits RFP2 to 0 of the status register (SR) to 000 (this sets the register banks to 0).

After reset is released, the CPU begins execution from the instruction at the location specified in the PC. Other than the changes described above, reset does not alter any internal CPU registers.

When reset is accepted, processing of the internal I/O and other pins are as follows:

- Initializes the internal I/O registers as per specifications.

- Pulls up the clock pin to 1.

**95C001-5** 2003-03-31

A0 to A23 are output at the rising of X1 with the 10th or the 12th clock after acknowledging  $\overline{RESET} = 1$ .

Figure 3.1 (1) TMP95C001 reset timing

#### 3.1.2 External Data Bus Size Selection Pin (AM8/ $\overline{16}$ )

TMP95C001 selects an external data bus size by sampling inputs to  $AM8/\overline{16}$  pin at the rising of a reset signal.

• AM8/16=0 (In case with 8 bit bus interlarded with 16 bit bus or fixed 16 bit bus)

D0 to D15 function as a 16 bit data bus.

The data bus size for external access is set by the wait control register. (Refer to "Wait control register" in section 3.5.2.).

• AM8/ $\overline{16}$  = 1 (In case with fixed 8 bit bus)

D0 to D7 function as an 8 bit data bus.

The values set in the wait control registers, <B0BUS>, <B1BUS>, <B2BUS>, <B3BUS> and <BEXBUS> are invalid, and it is fixed to an 8 bit data bus.

When using in case with fixed 8 bit bus, D8 to D15 should be fixed to 1 or 0.

#### 3.1.3 **Clock Output**

TMP95C001 has two clock output pins.

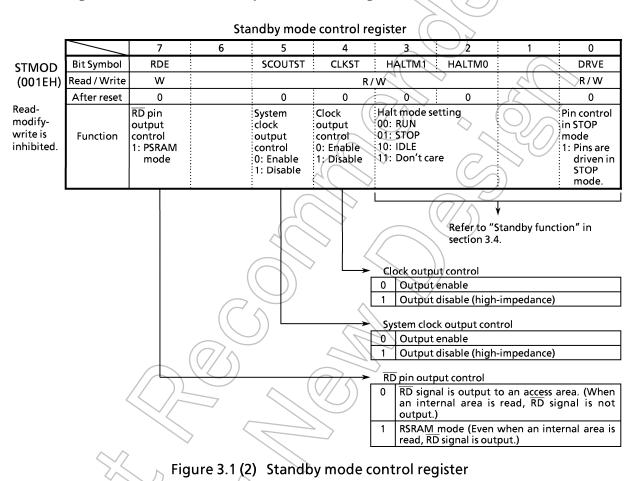

Setting a standby mode control register (STMOD) can control a clock output.

#### (1)Clock output pin (CLK)

- Setting STMOD < CLKST > to "1" disables output (high-impedance). When CLK pins are in the high-impedance condition, the pull-up register should be needed externally because of preventing the through current flowed into an input buffer of CLK pins.

- An output starts just after reset cancel.

(2)System clock output pin (SCOUT)

- Setting STMOD < SCOUTST > to "1" disables output (high-impedance).

- An output starts just after reset cancel.

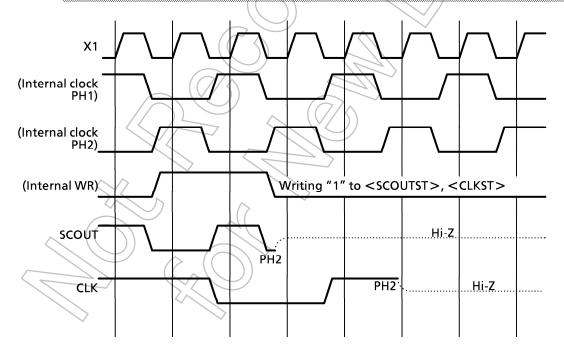

Figure 3.1 (2) shows a standby mode control register.

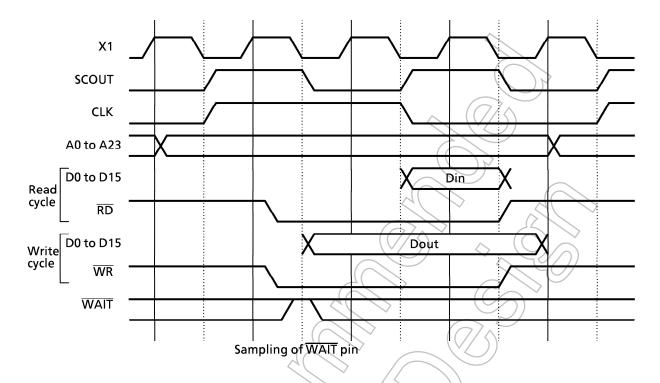

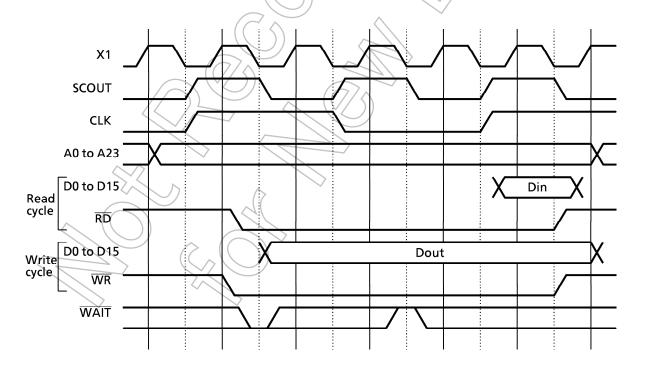

A timing Hi-Z (output disable) of SCOUT and CLK pins is shown as below figure.

<CLKST> and <SCOUTST> can be cleared by only a reset. These bits should not be written by "0".

Hi-Z at the rising of PH2 just after writing <SCOUTST > of WR · PH1. CLK

Hi-Z at the rising of PH2 following to PH2 and PH1 after writing to

<CLKST> of WR · PH1.

95C001-7 2003-03-31

#### 3.1.4 Pseudo SRAM Support

TMP95C001 has PSRAM mode to use a pseudo SRAM externally. Using PSRAM mode outputs  $\overline{RD}$  signal even when an internal area is read. Thus, an external PSRAM is refreshed. Writing "1" to the standby mode control register (STMOD) < RDE > can set PSRAM mode.

Figure 3.1(2) shows a standby mode control register.

**95C001-8** 2003-03-31

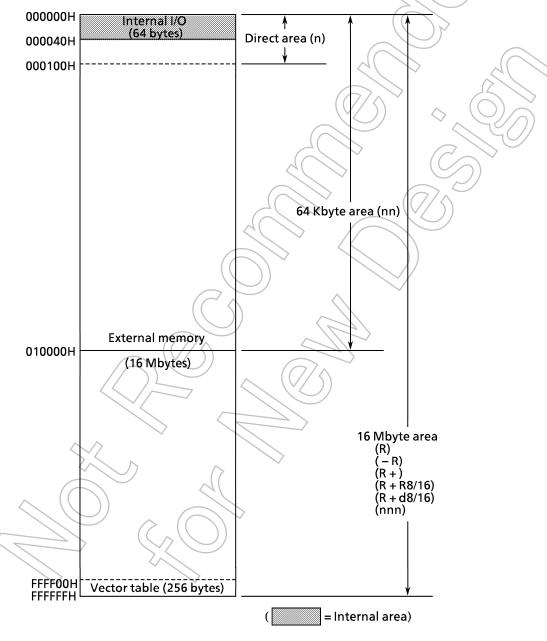

## 3.2 Memory Map

TMP95C001 uses an address area of 64 bytes as an internal I/O area.

This is allocated at addresses 000000H to 00003FH. The CPU can also access this internal I/O using a short instruction code according to "direct addressing mode".

Figure 3.2 shows an accessing area in the respective addressing modes for the memory map and the CPU.

Note: After reset, the stack pointer (XSP) is set to 100H.

Figure 3.2 TMP95C001 Memory Map

**95C001-9** 2003-03-31

## 3.2.1 Operation at internal I/O area access

TMP95C001 uses 64 bytes of address space (0H to 3FH) as an internal I/O area. Internal I/O registers are mapped on this area.

Operation of the internal I/O area access is different from that of the other address area access about following two points.

(1) In the internal I/O area access,  $\overline{RD}$ ,  $\overline{WR}$  and  $\overline{HWR}$  strobe signals are nonactive and fixed to high level.

However, in PSRAM mode set by STMOD<RDE>register,  $\overline{RD}$  strobe signal becomes active also in the internal I/O area access. (See 3.1.4 Pseudo SRAM Support.)

(2) In the internal I/O area access, the number of waits becomes zero or one depending on the internal state of the CPU. This wait can't be controlled by wait controller (see 3.5 Wait Controller). When the specified address area overlaps with the internal I/O area, the operation as the internal I/O area takes priority of the specified address area.

#### 3.3 Interrupts

TLCS-900 interrupts are controlled by the CPU interrupt mask flip-flops <IFF2 to 0> and the internal interrupt controller. Interrupts can come from a total of 20 sources:

Internal interrupts ··· 13

• Software interrupts : 8

• Illegal instructions : 1

• Interrupts from micro DMA : 4

External interrupts ... 7

• Interrupts from external pins (NMI, INTO to INT5)

Individual interrupt vector numbers (fixed) are allocated to each interrupt source. Seven levels of priority (variable) can be allocated to maskable interrupts. The priority of non-maskable interrupts is fixed at "7" (the highest priority).

When an interrupt is generated, the interrupt controller sends the priority value of that interrupt to the CPU. If more than one interrupt is generated simultaneously, the interrupt with the highest priority (7 non-maskable interrupts is the highest) is sent to the CPU.

The CPU compares the priority value with the value of the CPU interrupt mask register <IFF2 to 0>, and accepts the interrupt if the priority is higher or equal to the value in the CPU interrupt mask register. However, software interrupts and illegal instruction interrupts generated by the CPU are processed without comparison with the IFF <2:0> value.

The value of the interrupt mask register <IFF2 to 0> can be modified using the EI instruction (EI num sets IFF <2:0> to num). For example, executing "EI 3" enables acceptance of non-maskable interrupts and maskable interrupts with a priority of 3 or higher set in the interrupt controller.

However programming EI 0 enables acceptance of maskable interrupts with a priority of 1 or greater, and non-maskable interrupts. (It operates as the same as EI 1.)

The DI instruction (sets IFF <2:0 > to "7") is operationally the same as specifying "EI 7". As maskable interrupts have priorities in the range of 0 to 6, the DI instruction disables acceptance of maskable interrupts. The EI instruction is valid immediately after its execution. (With the TLCS-90, the EI instruction becomes valid only after the instruction following it is executed.)

As well as the general-purpose interrupt processing mode described above, the TLCS-900 also supports micro DMA processing mode. In micro DMA mode, the CPU transfers data automatically, thus accelerating interrupt processing such as data transfer to, or from, internal I/Os.

In addition to using an interrupt to start a micro DMA request, TMP95C001 also supports the "software start function", which start micro DMA requests by software.

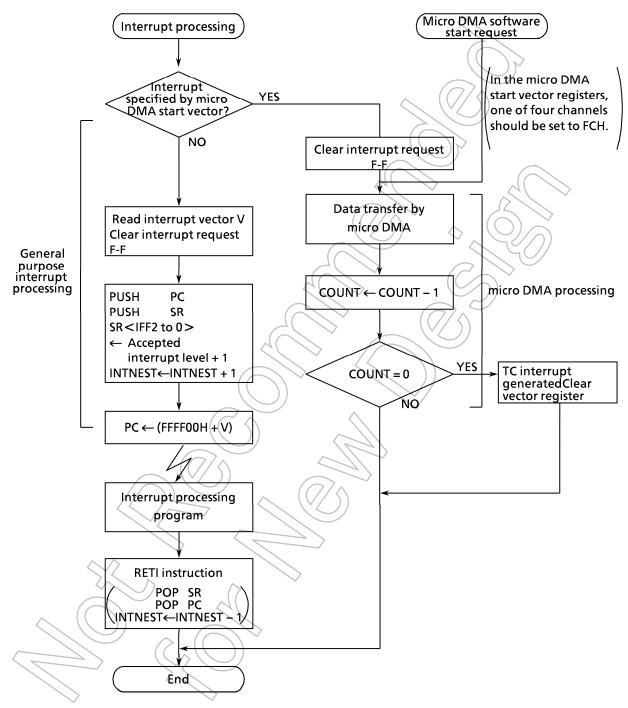

Figure 3.3 (1) is a flowchart of overall interrupt processing.

Figure 3.3 (1) Interrupt and Micro DMA Processing Flowchart

#### 3.3.1 General-Purpose Interrupt Processing

On receiving an interrupt, the CPU operates as follows

However, in the case of software interrupts and illegal instruction interrupts generated by the CPU, the CPU skips (1) and (3) and executes steps (2), (4), and (5).

- (1) The CPU reads the interrupt vector from the interrupt controller. When more than one interrupt with the same level is generated at the same time, the interrupt controller generates an interrupt vector in accordance with the default priority (the smaller the vector value, the higher the priority (fixed)), and clears the interrupt request.

- (2) The CPU pushes the program counter (PC) and status register (SR) onto the stack (the area pointed to by XSP).

- (3) The CPU sets the interrupt mask register <IFF2 to 0> value to the level of the received interrupt incremented by 1. If the received interrupt is a level 7 interrupt, the CPU does not increment the interrupt mask register but sets it to "7".

- (4) The CPU increments interrupt nesting counter INTNEST by 1.

- (5) The CPU jumps to the address indicated by the data at address (FFFF00H + interrupt vector) and begins the interrupt processing routine.

Table 3.3 (1) shows the times required by this processing.

|                              | (,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0 |                                                    |                                                     |

|------------------------------|-----------------------------------------|----------------------------------------------------|-----------------------------------------------------|

| Stack Area Bus<br>Width      | Interrupt Vecter<br>Area Bus Width      | Number of Interrupt<br>Processing Execution States | Interrupt Processing Time at fc = 25 MHz ( $\mu$ s) |

|                              | 8                                       | 28                                                 | 2.24                                                |

| 0                            | 16                                      | 24                                                 | 1.92                                                |

| $\langle \cdot \rangle_{ic}$ | 8                                       | 22                                                 | 1.76                                                |

| 10                           | 16                                      | 10                                                 | 1 //                                                |

Table 3.3 (1) Interrupt Processing Time

When interrupt processing is complete, the RETI instruction is executed to return processing to the main routine. Executing the RETI instruction restores the program counter (PC) and status register (SR) from the stack, and decrements interrupt nesting counter INTNEST by 1.

Non-maskable interrupts cannot be disabled by program. However, the program can enable or disable maskable interrupts, and can set priorities individually for each maskable interrupt source. (Setting the interrupt priority level to 0 (or 7) disables an interrupt request.)

The CPU accepts interrupt requests with a higher or equal priority than the value of the CPU interrupt mask register <IFF2 to 0>. On accepting an interrupt, the CPU sets the <IFF2 to 0> register to the received interrupt level incremented by 1. This means that if an interrupt is generated with a higher priority than the interrupt currently being processed, the CPU accepts the interrupt request for the higher priority interrupt and nests processing.

If a new interrupt request is generated while the CPU is accepting an interrupt and performing steps (1) to (5) described above, the CPU does not sample the new interrupt until after execution of the first instruction of the interrupt processing routine. Therefore, setting DI as the first instruction disables maskable interrupt nesting.

(Note: The 900 and 900/L series sample the interrupt before executing the first instruction.) Resetting initializes the CPU mask register <IFF2 to 0> to "7". This disables maskable interrupts.

Table 3.3 (2) shows an interrupt vector and a micro DMA start vector tables for TMP95C001. The addresses FFFF00H to FFFFFFH (256 bytes) of the TMP95C001 are assigned for an interrupt vector area.

The interrupt vector area is depended on the derivative products.

Table 3.3 (2) TMP95C001 Interrupt Table

| Default<br>Priority | Туре     | Interrupt Request Source               | Vector "V" | Vector<br>Reference<br>Address | HDMA<br>Start<br>Vector |

|---------------------|----------|----------------------------------------|------------|--------------------------------|-------------------------|

| 1                   |          | Reset, or SWI 0 instruction            | 0 0 0 0 H  | FFFF00H                        | _                       |

| 2                   |          | SWI 1 instruction                      | 0004H      | FFFF04H                        | _                       |

| 3                   |          | INTUNDEF: Illegal instruction or SWI 2 | 0008H      | FFFF08H                        | -                       |

| 4                   | Non-     | SWI 3 instruction                      | 000СН      | FFFF0CH                        | -                       |

| 5                   | maskable | SWI 4 instruction                      | 0010H      | FFFF10H                        | -                       |

| 6                   |          | SWI 5 instruction                      | 0014H      | FFFF14H                        | -                       |

| 7                   |          | SWI 6 instruction                      | 0018H      | FFFF18H                        | -                       |

| 8                   |          | SWI7 instruction                       | 0 0 1 C H  | FFFF1CH                        | -                       |

| 9                   |          | NMI pin                                | 0020H      | FFFF20H                        | -                       |

| _                   |          | (reserved)                             | 0024H      | FFFF24H                        | -                       |

| 10                  |          | INT0 pin                               | 0028H      | FFFF28H                        | 28H                     |

| 11                  |          | INT1 pin                               | 0 0 2 C H  | FFFF2CH                        | 2CH                     |

| 12                  |          | INT2 pin                               | 0030H      | FFFF30H                        | 30H                     |

| 13                  |          | INT3 pin                               | 0034H      | FFFF34H                        | 34H                     |

| 14                  |          | INT4/pin                               | 0038H      | FFFF38H                        | 38H                     |

| 15                  |          | INT5 pin                               | 0 0 3 C H  | FFFF3CH                        | 3CH                     |

| -                   |          | (reserved)                             | 0040H      | FFFF40H                        | -                       |

| 16                  | Maskable | INTTC0 : micro DMA completa (channel0) | 0044H      | FFFF44H                        | -                       |

| 17                  |          | INTTC1 : micro DMA completa (channel1) | 0048H      | FFFF48H                        | -                       |

| 18                  |          | INTTC2 : micro DMA completa (channel2) | 0 0 4 C H  | FFFF4CH                        | _                       |

| 19                  |          | INTTC3 : micro DMA completa (channel3) | 0 0 5 0 H  | FFFF50H                        | _                       |

| -                   |          | (reserved)                             | 0 0 5 4 H  | FFFF54H                        | -                       |

| to                  |          | to                                     | to         | to                             | to                      |

| -                   |          | (reserved)                             | 0 0 F C H  | FFFFCH                         | -                       |

|                     |          | Software micro DMA                     |            |                                | FCH                     |

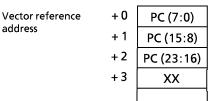

## Setting reset or interrupt vector

① Reset vector

② Interrupt vector (other than reset vector)

(Setting example)

To define the reset vector as address 8100H, the NMI vector as address 9ABCH, and the INT1 vector as address 123456H:

XX : Don't care

#### 3.3.2 MicroDMA Processing

In addition to conventional interrupt processing, TMP95C001 supports micro DMA function. For interrupt requests set for micro DMA, micro DMA processing is performed at the highest priority for maskable interrupts (level 6), regardless of the actual interrupt level set for the interrupt.

Because the function of micro DMA has been implemented with the cooperative operation of CPU, when CPU is a state of stand-by by HALT instruction, the requirement of micro DMA will be ignored (pending).

#### (1) Micro DMA Operation

When an interrupt request occurs for an interrupt specified by the micro DMA start vector register, micro DMA sends the micro DMA request to the CPU with the highest priority for maskable interrupts (level 6), regardless of the actual interrupt level set for the interrupt, and starts micro DMA. The micro DMA function has four channels. This allows micro DMA to be set for up to four interrupts at the same time.

When the micro DMA is accepted, the interrupt request flip flop is cleared, data are automatically transferred from the transfer source address to the transfer destination addresses(the address are set in the control register), and the transfer count is decremented. If the decremented result is other than zero, a value of the micro DMA start vector register retains, and the micro DMA processing terminates. If the decremented result is zero, the CPU sends the micro DMA transfer end interrupt (INTTC0 to 3) to the interrupt controller, clears a value of the micro DMA start vector register to 0, disables the next micro DMA startup, and terminates the micro DMA processing.

If multiple-channel micro DMA requests occur at the same time, the priority is determined by the channel numbers, not the interrupt levels. The lower the channel number, the higher the priority. (CH0 (high)  $\rightarrow$  CH3 (low))

If an interrupt request for the interrupt source used is received between the time that the micro DMA start vector is cleared and the time that it is reset, the CPU performs general-purpose processing at the specified interrupt level. Therefore, if the interrupt source is only being used for starting micro DMA (not used as an interrupt), set the interrupt level to zero.

When simultaneously using the same interrupt resource for both the micro DMA and general-purpose interrupts as described above, set the level of the interrupt source used to start micro DMA lower than the levels of all other interrupt sources. In this case, the cause of general interrupt is limited to the edge interrupt.

Example: When using external interrupts INT0 to 3 for running micro DMA 0 to 3

Set the interrupt level of INT0 to 3 to 1

Set other interrupt levels to 2 to 6

Like other maskable interrupts, the priority of the micro DMA transfer end interrupt is determined by the interrupt level and default priority.

The transfer source and transfer destination addresses are set in 32-bit control registers. However, as only 24-bit addresses are output, the address space available to micro DMA is 16M bytes. (The upper 8 bit of 32 bit is invalid.)

Three transfer modes are supported: 1-byte transfer, 1-word transfer (= two bytes), and 4-byte transfer. For each transfer mode, it is possible to specify whether to increment, decrement, or fix source and destination addresses after transfer. These modes facilitate data transfer from I/O to memory, from memory to I/O, and from I/O to I/O. For transfer mode details, see "3.3.2 (4) Transfer Mode Register Details" later in this manual.

As a 16-bit transfer counter is used, micro DMA can perform a maximum of 65536 transfers (initializing the counter to 0000H specifies the maximum number of transfers).

The 6 interrupt sources (INT0 to INT5) with micro DMA start vectors (as listed in Table 3.3 (2)) can be used to start micro DMA processing. Together with the soft start function, this gives a total of 7 different micro DMA triggers.

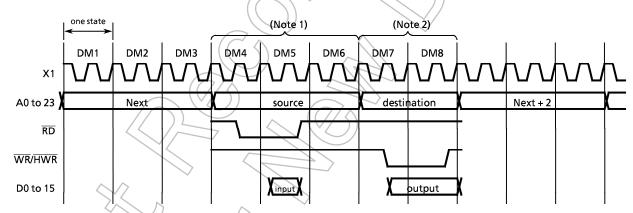

Figure 3.3 (2) shows the micro DMA cycle for 1-word transfer in transfer destination address INC mode (the same apart from counter mode). (In case with an external 16 bit bus width, 0 wait and an even number of a source/destination address).

Figure 3.3 (2) Micro DMA Cycle Diagram

States 1-3: Instruction fetch cycle (prefetches the next instruction code)

If the instruction cue buffer has three or more bytes of instruction code, the cycles are dummy cycles.

States 4-5: Micro DMA read cycles

State 6 : Dummy cycle (address bus remains the same as in state 5)

States 6-8: Micro DMA write cycle

Note 1: If the source address area uses an 8-bit bus, two states are added.

If also the source address area uses a 16-bit bus and the source address is an oddnumbered address, two states are added.

Note 2: If the destination address area uses an 8-bit bus, two states are added.

If also the destination address area uses a 16-bit bus and the destination address is an odd-numbered address, two states are added.

#### (2) Micro DMA Software Start Function

In addition to starting the micro DMA function by conventional interrupts, TMP95C001 includes an micro DMA software start function that starts micro DMA on the generation of the write cycle to the software DMA control register.

To trigger a software start, write the software micro DMA start vector "FCH" to the micro DMA start vector register DMA0V to 3V (memory address 26H, 27H, 28H, 29H). Next, writing data to the software DMA control register SDMACR0 to 3 (memory address 2AH, 2BH, 2CH, 2DH) (a value in the data does not effect a software start operation) causes micro DMA for the corresponding channel to run once. Writing again to the software DMA control register triggers another software start, provided the micro DMA transfer counter is set to other than "0". (It is not necessary to set the software micro DMA start vector again.)

Note that software start requests are one-shot requests and are not held over. If write cycle for the software DMA control register is generated when the software micro DMA start vector is not set, setting the software micro DMA start vector at a later time does not generate a software start. (The micro DMA start vector must be set prior to the micro DMA software start.)

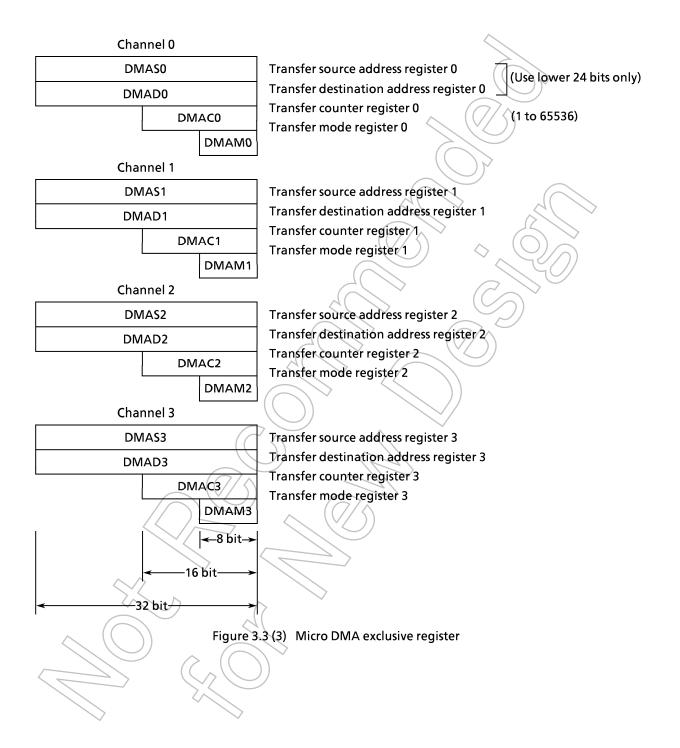

#### (3) Micro DMA exclusive register

Figure 3.3 (3) shows the micro DMA exclusive register. This register is included in the CPU. (Refer to "Control register" in section 3.2.5 of "TLCS-900 CPU" in chapter 3.) It can be set by the LDC instruction.

In this figure, the transfer source address register represents a source address to be transferred, and the transfer destination address register represents a destination address to be transferred. These address register use only lower 24 bit and support 16M area.

The transfer count register can set an execution number of the micro DMA by 1 to 65536.

Setting the transfer mode register is referred to "Transfer mode register details" in section 3.3.2 (4).

Setting the data to the micro DMA exclusive register can be executed by only the "LDC cr,r" instruction.

## (4) Transfer Mode Register Details

The micro DMA transfer mode is set by the transfer mode registers (DMAM0 to 3). Table 3.3 (3) shows the respective modes and the execution state number.

Table 3.3 (3) Micro DMA transfer mode

DMAM0 to 3 0 0 0 Mode Note: When setting values in this register, set the upper three bits to 0.

|                |     |                     | Transfer byte number    | Mode                                                                              | Execution state number (※) | Minimum<br>execution time<br>at fc = 25 MHz |

|----------------|-----|---------------------|-------------------------|-----------------------------------------------------------------------------------|----------------------------|---------------------------------------------|

| 000<br>(fixed) | 000 | 00                  | byte transfer           | Transfer destination address INC mode ··· For I/O to memory                       | 8 states                   | 640 ns                                      |

| (              |     | 01                  | word transfer           | (DMADn +) ← (DMASn)<br>DMACn←DMACn − 1<br>if DMACn = 0, then INTTC                |                            |                                             |

|                |     | 10                  | 4 byte transfer         | generated                                                                         | 12 states                  | 960 ns                                      |

|                | 001 | 00                  | byte transfer           | Transfer destination address DEC mode ··· For I/O to memory (DMADn − ) ← (DMASn)  | 8 states                   | 640 ns                                      |

|                |     | 01                  | word transfer           | DMACn←DMACn − 1<br>if DMACn = 0, then INTTC                                       | 12 states                  | 960 ns                                      |

|                |     | 10                  | 4 byte transfer         | generated                                                                         |                            |                                             |

|                | 010 | 00                  | byte transfer           | Transfer source address INC mode ···<br>For memory to I/O<br>(DMADn) ← (DMASn + ) | 8 states                   | 640 ns                                      |

|                |     | 01                  | word transfer           | DMACn←DMACn – 1                                                                   | /                          |                                             |

|                |     | 10                  | 4 byte transfer         | if DMACn = 0, then INTTC<br>generated                                             | 12 states                  | 960 ns                                      |

|                | 011 | 00                  | byte transfer           | Transfer source address DEC mode For memory to I/O                                | 8 states                   | 640 ns                                      |

|                |     | 01                  | word transfer           | (DMADn) ← (ĎMASn −)<br>DMACn←DMACn − 1                                            |                            |                                             |

|                |     | 10 ,                | 4 byte transfer         | if DMACn = 0, then INTTC generated                                                | 12 states                  | 960 ns                                      |

|                | 100 | 00                  | byte transfer           | Address fixed mode $\cdots$ For I/O to I/O (DMADn) $\leftarrow$ (DMASn)           | 8 states                   | 640 ns                                      |

|                |     | ~01 <sub>&gt;</sub> | word transfer           | DMACn←DMACn – 1<br>if DMACn = 0, then INTTC                                       |                            |                                             |

|                |     | 10                  | 4 byte transfer         | generated                                                                         | 12 states                  | 960 ns                                      |

| <              | 101 | 00                  | DMASn←DMAS<br>DMACn←DMA |                                                                                   | 5 states                   | 400 ns                                      |

<sup>(※)</sup> In an external 16 bit bus width, 0 wait and word/4 byte transfer mode, both the source and the destination addresses should be the even numbers.

Note: n: Corresponding micro DMA channels 0 to 3

DMADn +/DMASn +: Post-increment (increment the register value after transfer)

DMADn -/ DMASn-: Post-decrement (decrement the register value after transfer)

In the above table, "I/O" refers to fixed addresses and "memory" refers to incremented or decremented addresses.

Do not use undefined codes other than the above mentioned for transfer mode registers.

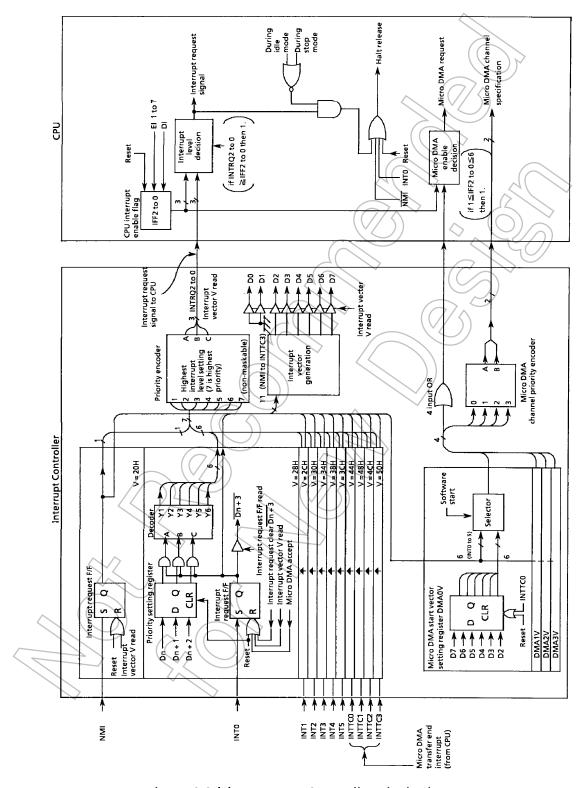

#### 3.3.3 Interrupt Controller

Figure 3.3 (4) is a block diagram of the interrupt circuits. The left half of the diagram shows the interrupt controller; the right half includes the CPU interrupt request signal circuit and the HALT release signal circuit (A halt is referred to "Standby" in section 3.4.)

Each interrupt channel (total of 11 channels: NMI, INTO to 5 and INTTCO to 3) in the interrupt controller has an interrupt request flip-flop (11 channels), an interrupt priority setting register (10 channels of INTO to 5, INTTCO to 3), and a start vector register (4 channels) for the micro DMA processing.

#### (1) Interrupt request flip-flop

The interrupt request flip-flop is used to latch interrupt request from peripheral devices. The channels other than NMI have the bit < IxxC > to clear the interrupt request. (Refer to "Interrupt priority setting register" in figure 3.3(5).) This flip-flop is cleared to "0" by the following operations.

- At reset

- When an interrupt is accepted, and the CPU reads the interrupt channel vector after the acceptance of interrupt

- When the CPU accepts the micro DMA request

- When the CPU executes an instruction that clears the interrupt of that channel (writes "0" in the clear bit < IxxC > of the interrupt priority setting register)

For example, to clear the interrupt request, executed the DI instruction and write "0" to the clear bit.

Ex.) Sets a register to clear INT0 interrupt request.

Note: -: No change

The status of the interrupt request flip-flop is detected by reading the clear bit<IxxC>. Detects whether there is an interrupt request for an interrupt channel. However the interrupt request flip-flop for NMI interrupt channel can not be read.

Figure 3.3 (4) Interrupt Controller Block Diagram

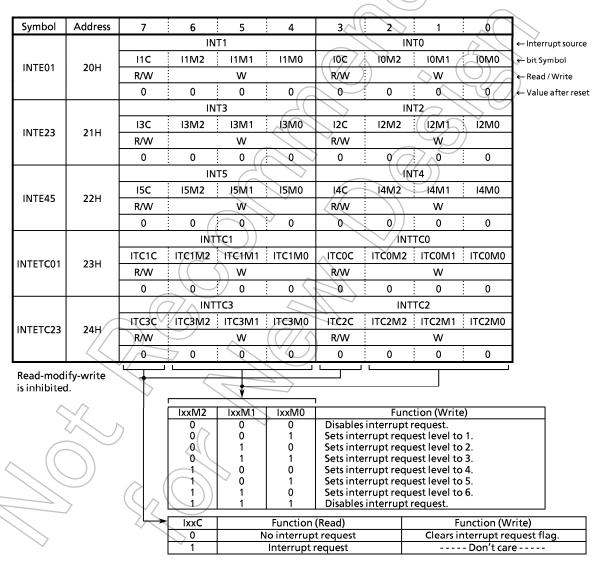

## (2) Interrupt priority setting register

Figure 3.3(5) shows the interrupt priority setting registers. The interrupt request level setting bits < IxxM2 to 0 > are provided for each 10 interrupt channels (INT0 to 5, INTTC0 to 3). Interrupt levels to be set are from 1 to 6. Writing 0 or 7 as the interrupt priority disables the corresponding interrupt request. The priority of the non-maskable interrupt  $(\overline{\text{NMI}} \text{ pin})$  is fixed to 7. If interrupt requests with the same interrupt level are generated simultaneously, interrupts are accepted in accordance with the default priority.

Figure 3.3 (5) Interrupt priority setting register

The interrupt controller sends the interrupt request with the highest priority among the simultaneous interrupts and its vector address to the CPU. The CPU compares the interrupt mask register <IFF2 to 0> set in the Status Register by the interrupt request signal with the priority value sent; if the latter is higher, the interrupt is accepted. Then the CPU sets a value higher than the priority value by 1 in the CPU SR <IFF2 to 0>. Interrupt requests where the priority value equals or is higher than the set value are accepted simultaneously during the previous interrupt routine.

## (3) Micro DMA start vector register

The interrupt controller has the micro DMA start vector registers (4 channels). Writing the start vector of the interrupt source for the micro DMA processing (see Table 3.3 (2)), enables the corresponding interrupt to be processed by micro DMA processing. The values must be set in the micro DMA parameter registers (e.g., DMAS, DMAD, DMAC and DMAM) prior to the micro DMA processing. Figure 3.3.(6) shows the micro DMA start vector registers.

This register is used to assign the micro DMA to an interrupt source. The interrupt source whose the micro DMA start vector matches the vector value set in this register is assigned as the micro DMA start source.

When the micro DMA transfer counter value reaches 0, the interrupt controller is notified of the micro DMA transfer end interrupt (INTTC0 to 3) corresponding to the channel, the micro DMA start vector register is cleared, and the micro DMA start source of the channel is also cleared. To continue the micro DMA processing, the micro DMA start vector register must be set again within the micro DMA transfer end interrupt processing.

If the same vector is set in the micro DMA start vector registers of the multiple channels, the interrupt generated in the channel with the smaller number has a higher priority. Thus, if the same vector is set in the micro DMA start vector registers of two channels, the interrupt generated in the channel with the smaller number is processed until the micro DMA transfer end. If the micro DMA start vector or this channel is not set again, the next the micro DMA is started for the channel with the higher number. (micro DMA chaining)

#### Micro DMA0 start vecter register

DMA0V (0026H)Readmodifywrite is inhibited.

|             | 7            | 6                                                          | 5      | 4      | 3      | 2_    |   |  | 1         |  | 0 |

|-------------|--------------|------------------------------------------------------------|--------|--------|--------|-------|---|--|-----------|--|---|

| bit Symbol  | DMA0V7       | DMA0V6                                                     | DMA0V5 | DMA0V4 | DMA0V3 | DMA0V | 2 |  |           |  |   |

| Read/Write  |              | W                                                          |        |        |        |       |   |  |           |  |   |

| After reset | 0            | 0                                                          | 0      | 0      | 0      | 0 (   |   |  | $\supset$ |  |   |

| Function    | Setting inte | Setting interrupt source to start the micro DMA channel 0. |        |        |        |       |   |  |           |  |   |

#### Micro DMA1 start vector register

DMA1V Readmodify-

(0027H)write is inhibited.

|             |              |                                                            | WINCO DIVIA | 1 Juli Vecto | Tregister |        |   |   |

|-------------|--------------|------------------------------------------------------------|-------------|--------------|-----------|--------|---|---|

|             | 7            | 6                                                          | 5           | 4            | 3         | 2      | 1 | 0 |

| bit Symbol  | DMA1V7       | DMA1V6                                                     | DMA1V5      | DMA1V4       | DMA1V3 [  | DMA1V2 |   |   |

| Read/Write  |              |                                                            | ٧           | ٧            |           | // i   |   |   |

| After reset | 0            | 0                                                          | 0           | 0            | 0         | 0      |   |   |

| Function    | Setting into | Setting interrupt source to start the micro DMA channel 1. |             |              |           |        |   |   |

#### Micro DMA2 start vecter register

DMA2V (0028H)Readmodifywrite is

inhibited.

|             | 7            | 6                                                         | 5      | 4 3           | 2 (1//)/ 0 |  |  |  |

|-------------|--------------|-----------------------------------------------------------|--------|---------------|------------|--|--|--|

| bit Symbol  | DMA2V7       | DMA2V6                                                    | DMA2V5 | DMA2V4 DMA2V3 | DMA2V2     |  |  |  |

| Read/Write  |              |                                                           | V      | <b>y</b>      |            |  |  |  |

| After reset | 0            | 0                                                         | 0 <    | 0 0           | 0          |  |  |  |

| Function    | Setting into | etting interrupt source to start the micro DMA channel 2. |        |               |            |  |  |  |

#### Micro DMA3 start vecter register

DMA3V (0029H)Readmodifywrite is inhibited.

|             | 7            | 6                                                          | 5           | 4 / (  | 3      | 2      | 1 | 0 |

|-------------|--------------|------------------------------------------------------------|-------------|--------|--------|--------|---|---|

| bit Symbol  | DMA3V7       | DMA3V6                                                     | DMA3V5      | DMA3V4 | DMA3V3 | DMA3V2 |   |   |

| Read/Write  |              |                                                            | )) v        | V      |        | /      | : | : |

| After reset | 0            | 0                                                          | <b>)</b> /0 | 0      | 0      | 0      |   |   |

| Function    | Setting into | Setting interrupt source to start the micro DMA channel 3. |             |        |        |        |   |   |

#### Setting micro DMA start source

| Micro DMA start source   | Micro DMA start vector register value |

|--------------------------|---------------------------------------|

| INT 0 Interrupt          | 28H                                   |

| INT 1 Interrupt          | 2CH                                   |

| INT 2 Interrupt          | 30H                                   |

| INT 3 Interrupt          | 34H                                   |

| INT 4 Interrupt          | 38H                                   |

| INT 5 Interrupt          | 3СН                                   |

| Micro DMA software start | FCH                                   |

Figure 3.3 (6) Micro DMA start vector registers and start sources

## (4) External interrupt control

Table 3.3 (4) shows setting of external interrupt pin functions.

TMP95C001 can select operating mode for  $\overline{\text{NMI}}$ , INTO and INT5 pins among the external interrupt functions. (For the pulse width of external interrupt signal, refer to "Interrupt operation" in section 4.5.)

| Interrupt |             | Mode                    | Setting method             |  |  |

|-----------|-------------|-------------------------|----------------------------|--|--|

| NIN /II   |             |                         | IIMC <nmiree> = 0</nmiree> |  |  |

| NMI       |             | Falling and rising edge | IIMC <nmiree> = 1</nmiree> |  |  |

| INITO     | <b>_</b>    | Rising edge             | HMC<10LE> = 0              |  |  |

| INT0      | <b></b>     | Level                   | IMC< 0LE> = 1              |  |  |

| INT1      | <u></u>     | Rising edge             |                            |  |  |

| INT2      | $\int$      | Rising edge             | 4301                       |  |  |

| INT3      | $\int$      | Rising edge             |                            |  |  |

| INT4      | <b>_</b>    | Rising edge             |                            |  |  |

| INITE     | <u></u>     | Rising edge             | IIMC<15LE> = 0             |  |  |

| INT5      | <b>→</b> \_ | Level                   | IIMC<15LE> = 1             |  |  |

Table 3.3 (4) Setting of External Interrupt Pin Functions

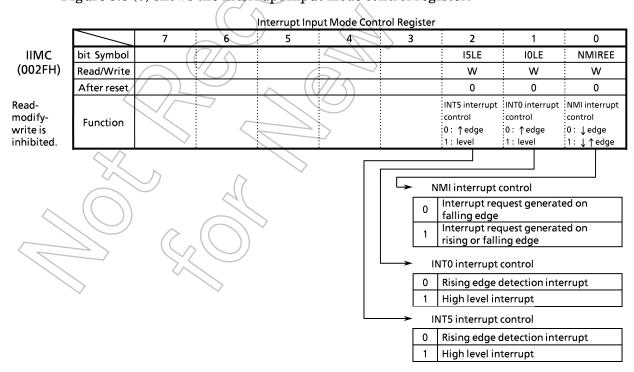

Input modes of NMI, INTO and INT5 interrupts are controlled by setting of the interrupt input mode control register, IIMC.

Figure 3.3 (7) shows the interrupt input mode control register.

Figure 3.3 (7) Interrupt Input Mode Control Register

#### (5) Notes

The instruction execution unit and the bus interface unit of this CPU operate independently. Therefore, immediately before an interrupt is generated, if the CPU fetches an instruction that clears the corresponding interrupt request flag, the CPU may execute the instruction that clears the interrupt request flag between accepting and reading the interrupt vector.

To avoid the above problem, place instructions that clear interrupt request flags after a DI instruction. In the case of setting an interrupt enable again by EI instruction after the execution of clearing instruction, execute EI instruction after clearing instruction and following more than one instruction are executed. When EI instruction is placed immediately after clearing instruction, an interrupt becomes enable before interrupt request flags are cleared.

In the case of changing the value of the interrupt mask register < IFF2 to 0> by execution of POP SR instruction, disable an interrupt by DI instruction before execution of POP SR instruction.

In addition, take care as the following interrupt modes are exceptional and demand special attention.

INT0, INT5 level mode

INTO in level mode is not an edge-detect interrupt, so the interrupt request flip-flop function is canceled. The peripheral interrupt request bypasses the S input of the flip-flop, and acts as the Q output. Changing modes from edge to level automatically clears the interrupt request flag.

If the CPU enters the interrupt response sequence as a result of setting INTO from 0 to 1, INTO must be held at 1 until the interrupt response sequence is completed. If the INTO level mode is used to release a halt, INTO must be held at 1 from the time INTO changes from 0 to 1, to the time when the halt is released. (Ensure that INTO does not go back 0 due to noise before the halt is released.)

When switching modes from level to edge, any interrupt request flag set in level mode is not cleared. Accordingly, clear the interrupt request flag using the following sequence.

DΙ

LD (IIMC), 00H ; Switches from level to edge.

LD (INTE01), 00H ; Clears interrupt request flag.

FΙ

\* INT5 (control register INTE45) needs the same operation, too.

Note: The following instructions or pin changes are equivalent to instructions that clear the interrupt request flag.

INTO, INT5: Instructions that switch to level mode after an interrupt request is generated in edge mode.

The pin input changes from high to low after an interrupt request is generated in level mode. ("H"  $\rightarrow$  "L")

#### 3.4 Standby Function

## (1) HALT mode

In TMP95C001, when the "HALT" instruction is executed, the operating mode changes RUN, IDLE, or STOP mode depending on the contents of the standby mode control registers (STMOD) <HALTM1,0>. Figure 3.4 (1) shows the standby mode control register.

|                                                                      |              |                                                  |   | Standby r                                                       | mode contro                                           | register (                                                    | ( ) \                      |                                                                              |

|----------------------------------------------------------------------|--------------|--------------------------------------------------|---|-----------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------|

|                                                                      |              | 7                                                | 6 | 5                                                               | 4                                                     | 3                                                             | 2                          | 1 0                                                                          |

| STMOD<br>(001EH)                                                     | bit Symbol   | RDE                                              |   | SCOUTST                                                         | CLKST                                                 | HALTM1                                                        | HALTM0                     | DRVE                                                                         |

|                                                                      | Read / Write | w                                                |   | R/W                                                             |                                                       |                                                               | R/W                        |                                                                              |

|                                                                      | After reset  | 0                                                |   | 0                                                               | 0                                                     |                                                               | 0                          | 0                                                                            |

| Read-<br>modify-<br>write is<br>inhibited.                           | Function     | RD pin<br>output<br>control<br>1 : PSRAM<br>mode |   | System<br>clock<br>output<br>control<br>0: Enable<br>1: Disable | Clock<br>output<br>control<br>0: Enable<br>1: Disable | Halt mode s<br>00: RUN<br>01: STOP<br>10: IDLE<br>11: Don't c |                            | Pin control<br>in STOP<br>mode<br>1 : Pins are<br>driven in<br>STOP<br>mode. |

| HALT mode setting    00   RUN mode(Only the CPU halts.)   0   VO off |              |                                                  |   |                                                                 |                                                       |                                                               | effect before entering the |                                                                              |

Figure 3.4 (1) Standby mode control register

The features of RUN, IDLE and STOP mode are as follows.

- ① RUN : Halts the CPU only. Power dissipation remains almost unchanged.

- 2 IDLE: Operates only the internal oscillator, while halts all other circuits.

- 3 STOP: Halts all internal circuits, including the internal oscillator.

Table 3.4 (1) shows each blocks operation during halt.

Table 3.4(1) Each Blocks and Input-output Pins Operation During Halt

| Halt Mode            | RUN  | IDLE | STOP              |  |  |

|----------------------|------|------|-------------------|--|--|

| STMOD < HALTM1, 0>   | 00   | 10   | 01                |  |  |

| D CPU                | Halt |      |                   |  |  |

| Interrupt controller |      |      |                   |  |  |

| I/O function         |      |      | See Table 3.4 (3) |  |  |

#### (2) HALT release

The HALT release is executed by an interrupt request from the external interrupt pins or a reset. The halt release source is depended on the status of the interrupt mask register  $\langle IFF2 \text{ to } 0 \rangle$  and the halt mode. For details, see Table 3.4(2).

When the HALT state is released by INTO and the interrupt request level is smaller than the interrupt mask register value, the CPU does not execute the interrupt processing of INTO.

The HALT state cannot be released by the micro DMA start except for INTO.

Table 3.4 (2) Halt Release Source and Halt Release Operation

| Interrupt mask setting for interrupt |             | Interrupt request level |                                |      | Interrupt request level ※ |                                                             |      |        |

|--------------------------------------|-------------|-------------------------|--------------------------------|------|---------------------------|-------------------------------------------------------------|------|--------|

| request level                        |             |                         | ≧ Interrupt mask 〈 IFF2 to 0 〉 |      |                           | <interrupt (iff2="" 0)<="" mask="" th="" to=""></interrupt> |      |        |

| Halt Mode                            |             |                         | RUN                            | IDLE | STOP                      | RUN                                                         | IDLE | STOP   |

| Source Rele                          | - nt errupt | NMI*                    | 0                              | •    | ×                         | 0                                                           |      | \\\\\\ |

|                                      |             | INT0                    | 0                              |      | ×                         | 0 (                                                         | Con  | ×      |

|                                      |             | INT1 to 5               | 0                              | ×    | ×                         | ×                                                           | (×)  | ×      |

| RESET                                |             | 0                       | 0                              | 0    | <b>6</b> //               | $\bigcirc$                                                  | 0    |        |

- After a halt is released, interrupt processing begins. (Reset initializes the LSI.)

- After a halt is released, processing begins from the next address following the HALT instruction.

- x: Cannot be used to release a halt.

- Same as a case of setting interrupt mask level to 7 by DI instruction before HALT instruction is executed.

- \* : Halt release by NMI or RESET is not depended on the interrupt mask level.

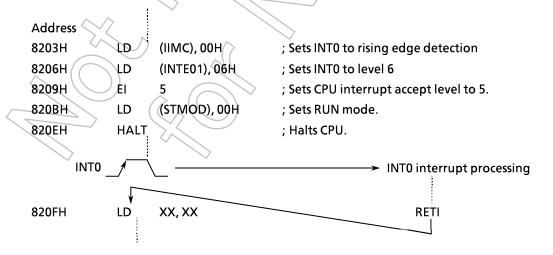

Example of releasing halt.

On execution of the HALT instruction, the device enters standby state in RUN mode. Release halt using INTO.

#### (3) Halt Mode Operation

#### ① RUN mode

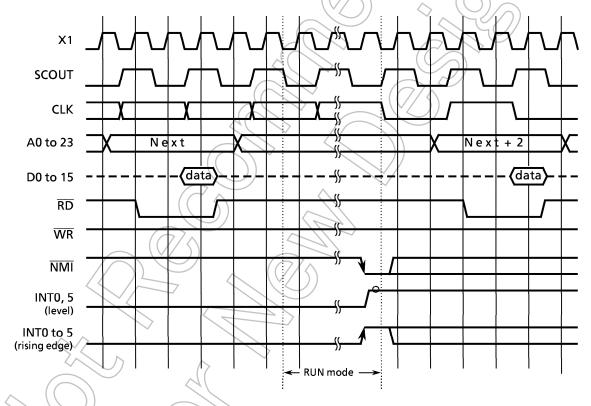

In RUN mode, the MCU internal system clock does not stop after the HALT instruction is executed. Only CPU instruction execution stops. Therefore, the CPU performs repeated dummy cycles until the halt state is released. In the halt state, interrupt requests are sampled on the falling edge of the CLK signal.

The halt state can be released by external interrupts (INTO to 5, NMI) in RUN mode. When the interrupt request level of INT1 to 5 is smaller than the interrupt mask <IFF2 to 0>, the HALT state cannot be released by INT1 to 5.

Figure 3.4 (2) is the timing chart for releasing a halt in RUN mode using an interrupt.

Figure 3.4 (2) Timing Chart for Releasing Halt in RUN Mode Using Interrupt

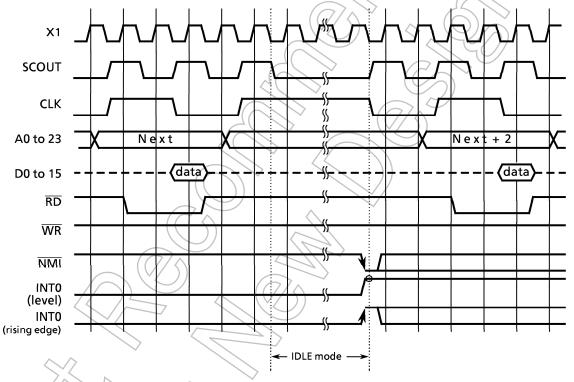

#### ② IDLE mode

In IDLE mode, the MCU internal system clock stops. Only the internal oscillator functions. The CLK pin is fixed at "1".

In the halt state, interrupt requests are sampled asynchronously to the system clock. The release from the halt state (operation restart), however, is synchronized with the clock.

In the IDLE mode, the HALT state can be released by only the external interrupt (NMI, INT0) and a reset.

Figure 3.4 (3) is the timing chart for releasing a halt in IDLE mode using an interrupt.

Figure 3.4 (3) Timing Chart for Releasing Halt in IDLE Mode Using Interrupt

#### ③ STOP mode

The STOP mode is selected to stop all internal circuits including the internal oscillator. In this mode, the state of all pins is depended on the settings of STMOD<DRVE>, see Figure 3.4.(1).)

Table 3.4 (3) shows the pin states in the STOP mode.

In the STOP mode, the HALT state can be released by a reset. To release the HALT state by a reset, hold the reset input level to be 3ms or more, "0". The STMOD<DRVE> is initialized to "0" by a reset.

When the STOP mode is set to the standby state, take care not to input INTO and NMI interrupts.

Note: Usually, interrupts can release all halts status. However, the interrupts = (NMI, INTO), which can release the HALT mode may not be able to do so if they are input during the period CPU is shifting to the HALT mode (for about 3 clocks of X1) with IDLE or STOP mode. (In this case, an interrupt request is kept on hold internally.) If another interrupt is generated after it has shifted to HALT mode completely, halt status can be released without difficultly. The priority of this interrupt is compare with that of the interrupt kept on hold internally, and the interrupt with higher priority is handled first followed by the other interrupt.

Figure 3.4 (4) shows the timing chart for releasing a halt in STOP mode using a reset.

Figure 3.4 (4) Timing Chart for Releasing Halt in STOP Mode Using Reset (Case of STMOD  $\langle DRVE \rangle = 0$ )

Table 3.4 (1) Pin State in STOP Mode

| Pin Name                | Input / Output | <drve> = 0</drve> | <drve> = 1</drve>                      |

|-------------------------|----------------|-------------------|----------------------------------------|

| D0 to D15               | Input / Output | Hi-Z*             | Hi-Z*                                  |

| A0 to A23               | Output         | Hi-Z              | Output                                 |

| RD, WR, HWR, BUSAK, R/W | Output         | Hi-Z              | ) Y Output                             |

| SCOUT                   | Output         | Hi-Z              | "0"                                    |

| BUSRQ, WAIT             | Input          | Invalid           | 0                                      |

| INT0                    | Input          |                   | 0                                      |

| INT1 to 5               | Input          | Invalid           | 0                                      |

| NMI                     | Input          | 0                 | 0                                      |

| CLK                     | Output         | Hi-Z              | "1"                                    |

| RESET                   | Input          | valid             | valid                                  |

| AM 8/ <del>16</del>     | Input (        | 0                 |                                        |

| X1                      | Input (        | Invalid           | Invalid                                |

| X2                      | Output         | "1"               | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

Output : Maintains output states prior to a halt.

: The input gate is disabled.

No through current, even at high impedance.

: Must be driven externally.

valid : Input is valid.

Invalid: Input is invalid. As the input gate is disabled, no through current.

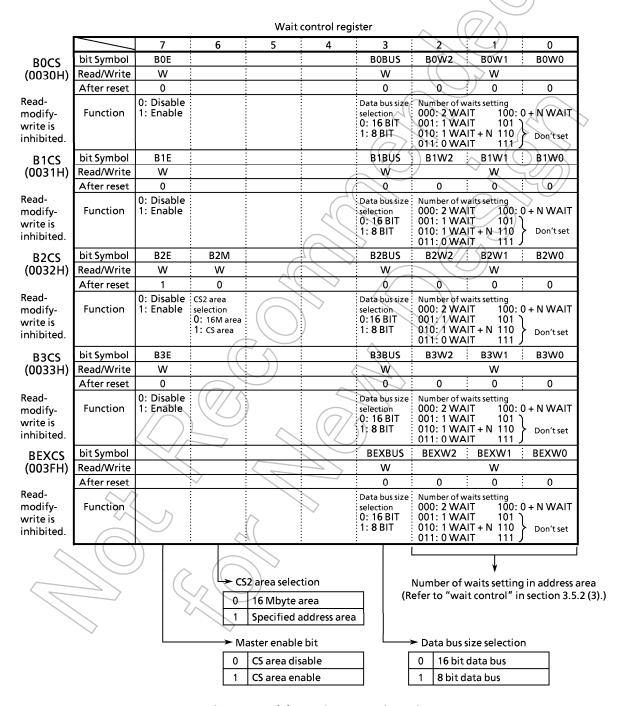

#### 3.5 Wait Controller

TMP95C001 can set a variable 4-block address area (CS0 to CS3 areas), and select the data bus size and number of waits in each address area (CS0 to CS3 areas and another area).

The CS0 to CS3 areas are specified by the memory start address registers MSAR0 to MSAR3 and memory address mask registers MAMR0 to MAMR3.

The master enable, data bus size and number of waits in each address area are specified by the wait control register, BOCS to B3CS and BEXCS.

TMP95C001 also has a bus wait request pin ( $\overline{WAIT}$ ) and external data bus size selection pin ( $\overline{AM8/16}$ ) as input pins to control these states. (Refer to "External data bus size selection pin" in selection 3.1.2.)

#### 3.5.1 Address Area Specification

The CS0 to CS3 areas are specified by the memory start address registers MSAR0 to MSAR3 and memory address mask registers MAMR0 to MAMR3.

At each bus cycle, the wait controller compares the address on the bus with the address of specified areas to CS0 to CS3. If the result of the comparison is a match, this indicates an access to the specified area, and a specified operation by the wait control registers B0CS to B3CS is executed. (Refer to "Wait control register" in section 3.5.2.)

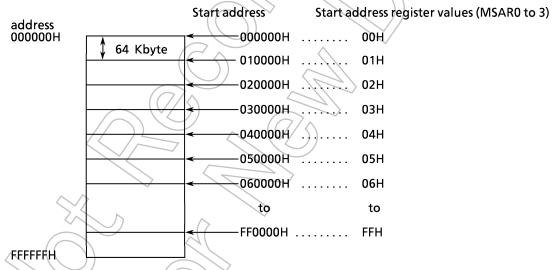

#### (1) Memory start address register

MSAR0 (0034H)

MSAR2 (0038H)

Figure 3.5 (1) shows the memory start address register. The memory start address registers, MSAR0 to MASR3 set the start addresses in CS0 to CS3. The higher 8 bit of the start address (A23 to A16) is set to <S23 to 16>. The lower 16 bit of the start address (A15 to A0) is always set to "0". The start address is set to one of the 64 Kbyte intervals after 000000H. Figure 3.5.(2) shows a relationship between the start address and the start address register value.

|         |             |            |   | Mem | ory S | Start Ac   | dress   | Register (CS        | 0 to C     | S3 are     | ea) |      |   |     |

|---------|-------------|------------|---|-----|-------|------------|---------|---------------------|------------|------------|-----|------|---|-----|

|         |             | 7          |   | 6   |       | 5          |         | 4                   | 3          |            | 2   |      |   | 0   |

| MSAR1   | bit Symbol  | <b>S23</b> | i | S22 | i     | <b>S21</b> |         | 520                 | <b>S19</b> |            | S18 | \$17 | Y | S16 |

| (0036H) | Read/Write  |            |   |     |       |            | (       | R/W                 | 7          |            | (   | 7    |   |     |

| MSAR3   | After reset | 1          |   | 1   |       | 1          |         | $\langle O \rangle$ | 1          | $\Diamond$ | _1  |      | i | 1   |

| (003AH) | Function    |            |   |     |       | Se         | ets sta | rt address fo       | r A23      | to A1      | 6   | 50   |   |     |

|         |             |            |   |     |       |            |         |                     |            | / ~        | /   | / /  |   |     |

Sets CS0 to CS3 start address

Figure 3.5 (1) Memory Start Address Register

Figure 3.5 (2) Relationship between Start Address and Start Address Register Value

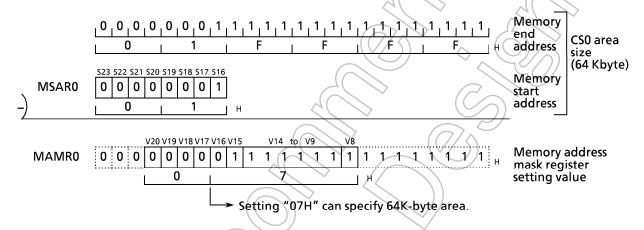

#### (2) Memory address mask register

MAMR1 (0037H)

MAMR2 | MAMR3 (0039H) | (003BH)

Figure 3.5. (3) shows the memory address mask register. The memory address mask registers, MAMR0 to MAMR3 specifies the area size of CS0 to CS3 by specifying a corresponding mask to each bit of the start addresses set by the memory start address register. Whether the address corresponding to the bit written by "0" on the bus is within CS0 to CS3 area is compared.

The CS0 to CS3 areas have different address bits which can be masked by MAMR0 to MAMR3 registers. Thus the area size which can be set differs.

|         |             |     | IVI | emo | ry Addr | ess I | Vlask Reg | gister | (CZ0 s | area) |       |       |   |    |

|---------|-------------|-----|-----|-----|---------|-------|-----------|--------|--------|-------|-------|-------|---|----|

|         |             | 7   | 6   |     | 5       |       | 4         |        | > 3    |       | 2     | 1     |   | 0  |

|         | bit Symbol  | V20 | V19 |     | V18     |       | V17       | ()     | V16    |       | V15   | V14~9 |   | V8 |

| ,       | Read/Write  |     |     |     |         |       |           | R/W    |        |       | 17    |       |   |    |

| (0035H) | After reset | 1   | 1   |     | 1       |       | 1         |        | 1      |       | 7     | 4     | - | 1  |

|         | Function    |     |     |     | Sets C  | S0 ar | ea size   | 0 : 0  | ompa   | re ad | dress |       |   |    |

CSO area size can be set from minimum 256 byte area to maximum 2 Mbyte area.

#### 7 4 3 2 n V21 V19 X 1/7 V16 V15~9 bit Symbol V20 V18 **V8** Read/Write R/W After reset 1 1 Sets CS1 area size 0: Compare address **Function**

Memory Address Mask Register (CS1 area)

CS1 area size can be set from minimum 256 byte area to maximum 4 Mbyte area.

| /           |     |    |     | / / /      |       | _        |     |          |     |         |     |     |     |  |

|-------------|-----|----|-----|------------|-------|----------|-----|----------|-----|---------|-----|-----|-----|--|

|             | 7   | <  | 6   | 5          |       | 4        |     | 3        |     | 2       | :   | 1   | 0   |  |