# CMOS 16-Bit Microcontrollers TMP95CW54AF

#### Outline and Features

TMP95CW54A is a high-speed 16-bit microcontroller designed for the control of various mid- to large-scale equipment.

TMP95CW54A comes in a 100-pin flat package.

Listed below are the features.

- (1) High-speed 16-bit CPU (900/H CPU)

- Instruction mnemonics are upward-compatible with TLCS-90/900

- 16M bytes of linear address space

- General-purpose registers and register banks

- 16-bit multiplication and division instructions; bit transfer and arithmetic instructions

- Micro DMA: Four-channels (667 ns / 2 bytes at 24 MHz)

- (2) Minimum instruction execution time: 167 ns (at 24 MHz)

- (3) Built-in RAM: 4 Kbytes Built-in ROM: 128 Kbyte

- (4) External memory expansion

- Expandable up to 16 Mbytes (shared program/data area)

- External data bus width select pin  $(AM8/\overline{16})$

- Can simultaneously support 8/16-bit width external data bus

- · · · Dynamic data bus sizing

- (5) 8-bit timers: 8 channels

- With event counter function : 2 channels

- (6) 16-bit timer/event counter: 2 channels

#### **RESTRICTIONS ON PRODUCT USE**

030619EBP

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in

general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of

the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system,

and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or

damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

- (7) General-purpose serial interface : 2 channels

- (8) Serial Expansion Interface: 1 channel

- (9) CAN Controller: 1 channel

- (10) 10-bit AD converter: 8 channels

- (11) Watchdog timer

- (12) Bus width/wait controller: 4 blocks

- (13) Interrupts: 49 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 30 internal interrupts : Seven selectable priority levels

- 10 external interrupts : Seven selectable priority levels

- (14) Input/output ports: 81 pins

- (15) Standby mode

- Four HALT modes: RUN, IDLE2, IDLE1, STOP

- (16) Operating voltage

- $V_{CC} = 4.5 \text{ to } 5.5 \text{ V}$

- (17) Package

- P-LQFP100-1414-0.50D

Note: After a reset, functions in parentheses ( ) are selected for the shared pins.

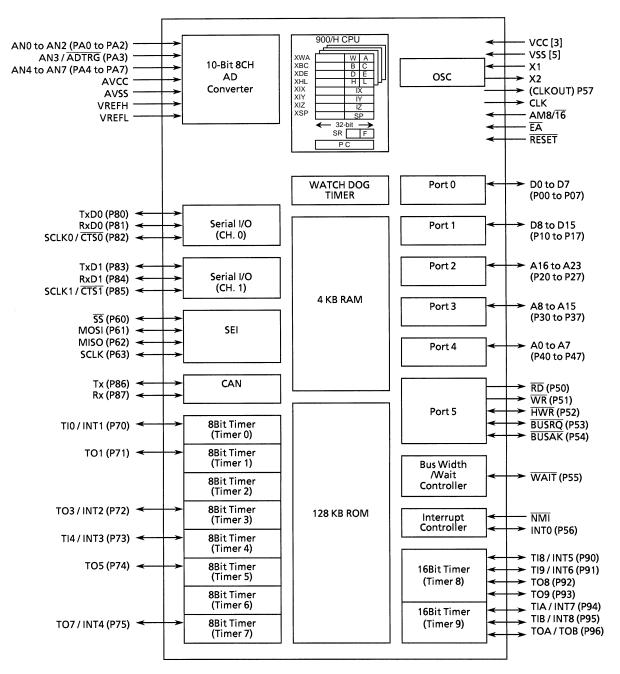

Figure 1.1 TMP95CW54A Block Diagram

# 2. Pin Assignment and Pin Functions

This section shows the TMP95CW54A pin assignment, and the names and an outline of the functions of the input/output pins.

## 2.1 Pin Assignment Diagram

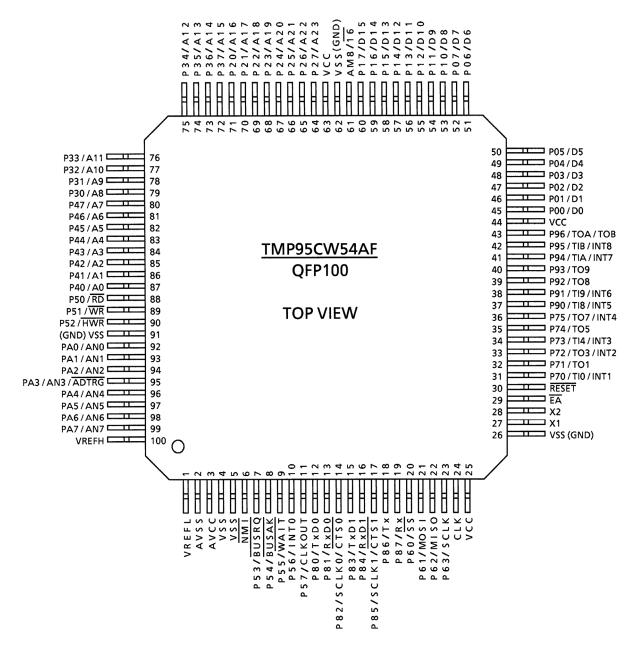

Figure 2.1.1 is a pin assignment diagram for TMP95CW54A.

Figure 2.1.1 Pin assignment diagram (100-Pin LQFP)

## 2.2 Pin Names and Functions

Table 2.2.1 shows the names and functions of the input/output pins.

Table 2.2.1 Pin names and functions (1/4)

| Pin Name     | Number<br>of Pins | Input/Output | Function                                                              |

|--------------|-------------------|--------------|-----------------------------------------------------------------------|

| P00 to P07   | 8                 | Input/output | Port 0: I/O port. Input or output specifiable in units of bits        |

| / D0 to D7   |                   | Input/output | Data: Data bus 0 to 7                                                 |

| P10 to P17   | 8                 | Input/output | Port 1: I/O port. Input or output specifiable in units of bits        |

| / D8 to D15  |                   | Input/output | Data: Data bus 8 to 15                                                |

| P20 to P27   | 8                 | Input/output | Port 2: I/O port. Input or output specifiable in units of bits        |

| / A16 to A23 |                   | Output       | Address: Address bus 16 to 23                                         |

| P30          | 1                 | Input/output | Port 30: I/O port (with built-in pull-up resistor during input mode.) |

| /A8          |                   | Output       | Address: Address bus 8                                                |

| P31 to P37   | 7                 | Input/output | Port 31 to 37: I/O port. Input or output specifiable in units of bits |

| / A9 to A15  |                   | Output       | Address: Address bus 9 to 15                                          |

| P40 to P47   | 8                 | Input/output | Port 4: I/O port. Input or output specifiable in units of bits        |

| / A0 to A7   |                   | Output       | Address: Address bus 0 to 7                                           |

| P50          | 1                 | Output       | Port 50: Output-only port                                             |

| /RD          |                   | Output       | Read: Outputs strobe signal to read external memory (setting P5       |

|              |                   |              | < P50 > = 0 and P5FC $< P50F > = 1$ outputs strobe signal at all read |

|              |                   |              | timings)                                                              |

| P51          | 1                 | Output       | Port 51: Output-only port.                                            |

| / WR         |                   | Output       | Write: Outputs strobe signal to write data on pins D0 to D7           |

| P52          | 1                 | Input/output | Port 52: I/O port (with built-in pull-up resistor)                    |

| / HWR        |                   | Output       | Upper write: Outputs strobe signal to write data on pins D8 to D15    |

| P53          | 1                 | Input/output | Port 53: I/O port (with built-in pull-up resistor)                    |

| / BUSRQ      |                   | Input        | Bus request: Input pin to request external bus release                |

| P54          | 1                 | Input/output | Port 54: I/O port (with built-in pull-up resistor)                    |

| /BUSAK       |                   | Output       | Bus acknowledge: Output pin to acknowledge that CPU received          |

|              |                   |              | BUSRQ and released external bus.                                      |

| P55          | 1                 | Input/output | Port 55: I/O port (with built-in pull up resistor)                    |

| /WAIT        |                   | Input        | Wait: Bus wait request pin for CPU (Effective when 1 WAIT + N mode,   |

|              |                   |              | or 0 + NWAIT mode. Set using bus width/wait control register.)        |

| P56          | 1                 | Input/output | Port 56: I/O port (with built-in pull-up resistor)                    |

| /INT0        |                   | Input        | Interrupt request pin 0: Interrupt request pin with programmable      |

|              |                   |              | level/rising edge.                                                    |

Table 2.2.1 Pin names and functions (2/4)

| Pin Name        | Number<br>of Pins | Input/Output | Function                                                   |

|-----------------|-------------------|--------------|------------------------------------------------------------|

| P57             | 1                 | Output       | Port 57: Output-only port (with built-in pull-up resistor) |

| / CLKOUT        |                   | Output       | CLKOUT output: Outputs external clock divided by 6.        |

|                 |                   |              | Pulled up during reset.                                    |

| P60             | 1                 | Input/output | Port 60: I/O port                                          |

| / <del>SS</del> |                   | Input        | SEI slave select input                                     |

| P61             | 1                 | Input/output | Port 61: I/O port                                          |

| / MOSI          |                   | Input/output | SEI master output, slave input                             |

| P62             | 1                 | Input/output | Port 62: I/O port                                          |

| / MISO          |                   | Input/output | SEI master input, slave output                             |

| P63             | 1                 | Input/output | Port 63: I/O port                                          |

| / SCLK          |                   | Input/output | SEI clock input/output                                     |

| P70             | 1                 | Input/output | Port 70: I/O port                                          |

| /TI0            |                   | Input        | Timer input 0: Input pin for timer 0                       |

| /INT1           |                   | Input        | Interrupt request pin 1: Rising-edge interrupt request pin |

| P71             | 1                 | Input/output | Port 71: I/O port.                                         |

| /TO1            |                   | Output       | Timer output 1: Output pin for timer 0 or 1                |

| P72             | 1                 | Input/output | Port 72: I/O port                                          |

| /TO3            |                   | Output       | Timer output 3: Output pin for timer 2 or 3                |

| /INT2           |                   | Input        | Interrupt request pin 2: Rising-edge interrupt request pin |

| P73             | 1                 | Input/output | Port 73: I/O port                                          |

| /TI4            |                   | Input        | Timer input 4: Input pin for timer 4                       |

| /INT3           |                   | Input        | Interrupt request pin 3: Rising-edge interrupt request pin |

| P74             | 1                 | Input/output | Port 74: I/O port                                          |

| /TO5            |                   | Output       | Timer output 5: Output pin for timer 4 or 5                |

| P75             | 1                 | Input/output | Port 75: I/O port                                          |

| /TO7            |                   | Output       | Timer output 7: Output pin for timer 6 or 7                |

| /INT4           |                   | Input        | Interrupt request pin 4: Rising-edge interrupt request pin |

| P80             | 1                 | Input/output | Port 80: I/O port (with built-in pull-up resistor)         |

| /TxD0           |                   | Output       | Serial transmission data 0                                 |

| P81             | 1                 | Input/output | Port 81: I/O port (with built-in pull-up resistor)         |

| /RxD0           |                   | Input        | Serial receive data 0                                      |

| P82             | 1                 | Input/output | Port 82: I/O port (with built-in pull-up resistor)         |

| /SCLK0          |                   | Input/output | Serial clock input/output 0                                |

| / CTSO          |                   | Input        | Serial data ready to send 0 (Clear-to-send)                |

Table 2.2.1 Pin names and functions (3/4)

| Pin Name     | Number<br>of Pins | Input/Output | Function                                                                             |  |  |  |

|--------------|-------------------|--------------|--------------------------------------------------------------------------------------|--|--|--|

| P83          | 1                 | Input/output | Port 83: I/O port (with built-in pull-up resistor)                                   |  |  |  |

| /TxD1        |                   | Output       | Serial transmission data 1                                                           |  |  |  |

| P84          | 1                 | Input/output | Port 84: I/O port (with built-in pull-up resistor)                                   |  |  |  |

| /RxD1        |                   | Input        | Serial receive data 1                                                                |  |  |  |

| P85          | 1                 | Input/output | Port 85: I/O port (with built-in pull-up resistor)                                   |  |  |  |

| /SCLK1       |                   | Input/output | Serial clock input/output 1                                                          |  |  |  |

| /CTS1        |                   | Input        | Serial data ready to send 1 (Clear-to-send)                                          |  |  |  |

| P86          | 1                 | Input/output | Port 86: I/O port (with built-in pull-up resistor)                                   |  |  |  |

| /Tx          |                   | Output       | CAN transmission data                                                                |  |  |  |

| P87          | 1                 | Input/output | Port 87: I/O port (with built-in pull-up resistor)                                   |  |  |  |

| /Rx          |                   | Input        | CAN receive data                                                                     |  |  |  |

| P90          | 1                 | Input/output | Port 90: I/O port                                                                    |  |  |  |

| /TI8         |                   | Input        | Timer input 8: Input pin for timer 8                                                 |  |  |  |

| /INT5        |                   | Input        | Interrupt request pin 5: Interrupt request pin with programmable                     |  |  |  |

|              |                   |              | rising/falling edge                                                                  |  |  |  |

| P91          | 1                 | Input/output | Port 91: I/O port                                                                    |  |  |  |

| /TI9         |                   | Input        | Timer input 9: Input pin for timer 8                                                 |  |  |  |

| /INT6        |                   | Input        | Interrupt request pin 6: Rising edge interrupt request pin                           |  |  |  |

| P92          | 1                 | Input/output | Port 92: I/O port                                                                    |  |  |  |

| /TO8         |                   | Output       | Timer output 8: Output pin for timer 8                                               |  |  |  |

| P93          | 1                 | Input/output | Port 93: I/O port                                                                    |  |  |  |

| /TO9         |                   | Output       | Timer output 9: Output pin for timer 8                                               |  |  |  |

| P94          | 1                 | Input/output | Port 94: I/O port                                                                    |  |  |  |

| /TIA         |                   | Input        | Timer input A: Input pin for timer 9                                                 |  |  |  |

| /INT7        |                   | Input        | Interrupt request pin 7: Interrupt request pin with programmable rising/falling edge |  |  |  |

| P95          | 1                 | Input/output | Port 95: I/O port                                                                    |  |  |  |

| /TIB         |                   | Input        | Timer input B: Input pin for timer 9                                                 |  |  |  |

| /INT8        |                   | Input        | Interrupt request pin 8: Rising edge interrupt request pin                           |  |  |  |

| P96          | 1                 | Input/output | Port 96: I/O port                                                                    |  |  |  |

| /TOA         |                   | Output       | Timer output A: Output pin for timer 9                                               |  |  |  |

| /ТОВ         |                   | Output       | Timer output B: Output pin for timer 9                                               |  |  |  |

| PA0 to PA2   | 3                 | Input        | Port A0 to A2: Input-only port                                                       |  |  |  |

| / AN0 to AN2 |                   | Input        | Analog input 0 to 2: AD converter input pins                                         |  |  |  |

| PA3          | 1                 | Input        | Port A3: Input-only port                                                             |  |  |  |

| /AN3         |                   | Input        | Analog input 3: AD converter input pin                                               |  |  |  |

| / ADTRG      |                   | Input        |                                                                                      |  |  |  |

Table 2.2.1 Pin names and functions (4/4)

| Pin Name     | Number<br>of Pins | Input/Output | Function                                                          |

|--------------|-------------------|--------------|-------------------------------------------------------------------|

| PA4 to PA7   | 4                 | Input        | Port A4 to A7: Input-only port                                    |

| / AN4 to AN7 |                   | Input        | Analog input 4 to 7: AD converter input pins                      |

| NMI          | 1                 | Input        | Non-maskable interrupt request pin: Interrupt request pin with    |

|              |                   |              | programmable falling edge or both falling and rising edge         |

| CLK          | 1                 | Output       | Clock output: Outputs external clock divided by 4.                |

|              |                   |              | Pulled up during reset.                                           |

| ĒĀ           | 1                 | Input        | External access: Connect to VCC.                                  |

| AM8/16       | 1                 | Input        | Address mode: External data bus width select pin                  |

|              |                   |              | Connect this pin to VCC. Data bus width at external access can be |

|              |                   |              | set by bus width/wait control register.                           |

| RESET        | 1                 | Input        | Reset: Initializes TMP95CW54A (with built-in pull-up resistor)    |

| VREFH        | 1                 | Input        | Reference voltage input pin for AD converter (high)               |

| VREFL        | 1                 | Input        | Reference voltage input pin for AD converter (low)                |

| AVCC         | 1                 |              | Power supply pin for AD converter: Connect to power supply        |

| AVSS         | 1                 |              | GND pin for AD converter: Connect to GND                          |

| X1/X2        | 2                 | Input/output | Oscillator connecting pin                                         |

| VCC          | 3                 |              | Power supply pin: Connect all VCC pins to power supply            |

| VSS          | 5                 |              | GND pin: Connect all VSS pins to GND (0 V)                        |

Note: Disconnect the pull-up resistors from pins other than  $\overline{\text{RESET}}$  pin by software.

P30 is pulled-up during reset and input mode.

P57 and CLK pin are pulled-up only during reset.

# 3. Operation

The following describes the structure and operation of the TMP95CW54A hardware.

This device is created from the TMP95CU54A by expanding its internal ROM size to 128 Kbytes and its internal RAM size to 4 Kbytes. Otherwise, TMP95CW54A is structurally and operationally identical to TMP95CU54A. Accordingly, for functions not described here, see the TMP95CU54A section of the manual.

#### 3.1 MCU Mode

Opening the CLK pin (setting to output) sets MCU mode. In MCU mode, TMP95CW54A operates the same as TMP95CU54A.

#### 3.2 Memory Map

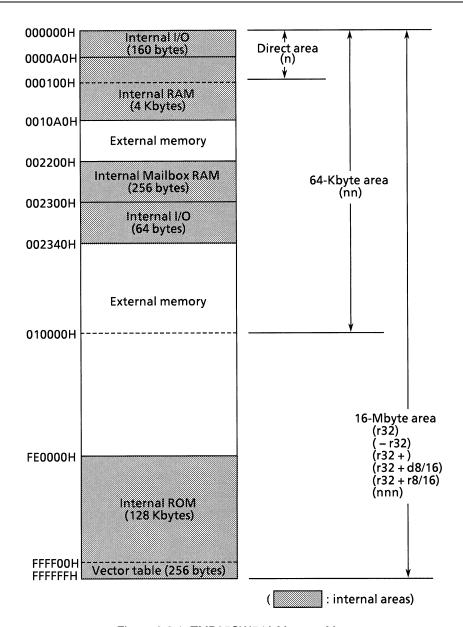

Figure 3.2.1 shows the memory map in MCU mode and the CPU access area in each addressing mode.

Figure 3.2.1 TMP95CW54A Memory Map

## 4. Electrical Characteristics

## 4.1 Absolute Maximum Ratings

| Parameter                       | Symbol           | Rating             | Unit |

|---------------------------------|------------------|--------------------|------|

| Power Supply Voltage            | V cc             | -0.5 to + 6.5      | V    |

| Input Voltage                   | V <sub>IN</sub>  | - 0.5 to Vcc + 0.5 | V    |

| Output current (total)          | Σl <sub>OL</sub> | +120               | mA   |

| Output current (total)          | Σloh             | - 120              | mA   |

| Power Dissipation (Ta = + 85°C) | PD               | 600                | mW   |

| Soldering Temperature (10 s)    | T SOLDER         | +260               | °C   |

| Storage Temperature             | T <sub>STG</sub> | -65 to + 150       | °C   |

| Operating Temperature           | T OPR            | - 40 to + 85       | °C   |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

**TOSHIBA**

## 4.2 DC Electrical Characteristics

$Vcc = +5 V \pm 10\%$ , Ta = -40 to + 85°C (fc = 8 to 24 MHz)

| Parameter                                                                                             | Symbol                              | Test Condition                                                                     | Min                                         | Max                                 | Unit                     |

|-------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------|--------------------------|

| Input Low Voltage (D0 to 15)<br>Port 2 to A<br>(except P56, P70, P72, P73, P75)                       | V IL<br>V IL1                       |                                                                                    | -0.3<br>-0.3                                | 0.8<br>0.3 Vcc                      | V<br>V                   |

| RESET, NMI, INTO to 4<br>EA, AM8/16<br>X1                                                             | V IL2<br>V IL3<br>V IL4             |                                                                                    | -0.3<br>-0.3<br>-0.3                        | 0.25 Vcc<br>0.3<br>0.2 Vcc          | V<br>V<br>V              |

| Input High Voltage (D0 to 15)<br>Port 2 to A<br>(except P56, P70, P72, P73, P75)                      | V <sub>IH</sub><br>V <sub>IH1</sub> |                                                                                    | 2.2<br>0.7 Vcc                              | Vcc + 0.3<br>Vcc + 0.3              | V                        |

| RESET, NMI, INTO to 4<br>EA, AM8/16<br>X1                                                             | V 1H2<br>V 1H3<br>V 1H4             |                                                                                    | 0.75 Vcc<br>Vcc – 0.3<br>0.8 Vcc            | Vcc + 0.3<br>Vcc + 0.3<br>Vcc + 0.3 | V<br>V<br>V              |

| Output Low Voltage                                                                                    | V <sub>OL</sub>                     | I <sub>OL</sub> = 1.6 mA                                                           |                                             | 0.45                                | V                        |

| Output High Voltage                                                                                   | V OH<br>V OH1<br>V OH2              | I <sub>OH</sub> = -400 μA<br>I <sub>OH</sub> = -100 μA<br>I <sub>OH</sub> = -20 μA | 2.4<br>0.75 Vcc<br>0.9 Vcc                  |                                     | ><br>><br>>              |

| Darlington Drive Current<br>(8 Output Pins max.)                                                      | IDAR                                | $V_{EXT} = 1.5 V$<br>R EXT = 1.1 k $\Omega$                                        | <b>–</b> 1.0                                | -3.5                                | mΑ                       |

| Input Leakage Current<br>Output Leakage Current                                                       | I <sub>LI</sub><br>I LO             | 0.0 ≦ Vin ≦ Vcc<br>0.2 ≦ Vin ≦ Vcc – 0.2                                           | 0.02 (Typ)<br>0.05 (Typ)                    | ±5<br>±10                           | μ <b>Α</b><br>μ <b>Α</b> |

| Operating Current (NORMAL)<br>RUN<br>IDLE2<br>IDLE1                                                   | l cc                                | fc = 24 MHz                                                                        | 70 (Typ)<br>35 (Typ)<br>30 (Typ)<br>5 (Typ) | 85<br>50<br>40<br>10                | mA<br>mA<br>mA<br>mA     |

| STOP (Ta = $-40 \text{ to } + 85^{\circ}\text{C}$ )<br>(Ta = $-20 \text{ to } + 70^{\circ}\text{C}$ ) |                                     | 0.2 ≦ Vin ≦ Vcc – 0.2                                                              | 0.5 (Typ)                                   | 100<br>50                           | μ <b>Α</b><br>μ <b>Α</b> |

| Power Down Voltage<br>(@STOP, RAM Back up)                                                            | V STOP                              | V <sub>IL2</sub> = 0.2 Vcc,<br>V <sub>IH2</sub> = 0.8 Vcc                          | 2.0                                         | 6.0                                 | V                        |

| Pull Up Registance                                                                                    | R <sub>RP</sub>                     |                                                                                    | 45                                          | 160                                 | <b>k</b> Ω               |

| Pin Capacitance                                                                                       | C <sub>IO</sub>                     | fc = 1 MHz                                                                         |                                             | 10                                  | рF                       |

| Schmitt Width<br>RESET, NMI, INT0 to 4                                                                | V <sub>TH</sub>                     |                                                                                    | 0.4                                         | 1.0 (Typ)                           | V                        |

Note 1: Typical values are for Ta = +25°C,  $V_{CC} = +5$  V

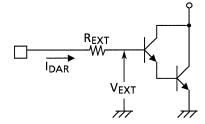

Note 2:  $I_{DAR}$  guarantees up to eight pins from any output port.

Refer: IDAR definition diagram.

## 4.3 AC Electrical Characteristics

$Vcc = +5 V \pm 10\%$ , Ta = -40 to +85°C

(fc = 8 MHz to 24 MHz)

| No   | No. Parameter                                                                                                                                                  |                  | Variable  |           | 24 MHz |     | Unit |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|-----------|--------|-----|------|

| LNO. | raiameter                                                                                                                                                      | Symbol           | Min       | Max       | Min    | Max | Onit |

| 1    | Oscillation cycle $( = x)$                                                                                                                                     | tosc             | 42        | 125       | 42     |     | ns   |

| 2    | Clock pulse width                                                                                                                                              | t <sub>CLK</sub> | 2.0x - 40 |           | 44     |     | ns   |

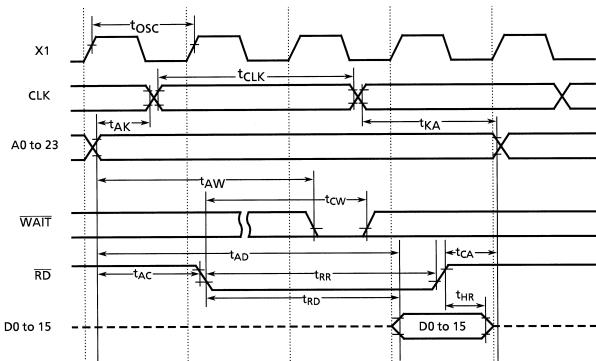

| 3    | A0 to 23 valid → Clock hold                                                                                                                                    | t <sub>AK</sub>  | 0.5x - 20 |           | 1      |     | ns   |

| 4    | Clock valid → A0 to 23 hold                                                                                                                                    | t <sub>KA</sub>  | 1.5x - 60 |           | 3      |     | ns   |

| 5    | A0 to 23 valid $\rightarrow \overline{RD}/\overline{WR}$ fall                                                                                                  | t <sub>AC</sub>  | 1.0x - 20 |           | 22     |     | ns   |

| 6    | $\overline{RD}/\overline{WR}$ rise $\rightarrow$ A0 to 23 hold                                                                                                 | tcA              | 0.5x - 20 |           | 1      |     | ns   |

| 7    | A0 to 23 valid $\rightarrow$ D0 to 15 input                                                                                                                    | t <sub>AD</sub>  |           | 3.5x – 40 |        | 107 | ns   |

| 8    | $\overline{RD}$ fall $\rightarrow$ D0 to 15 input                                                                                                              | t <sub>RD</sub>  |           | 2.5x – 45 |        | 60  | ns   |

| 9    | RD low pulse width                                                                                                                                             | t <sub>RR</sub>  | 2.5x - 40 |           | 65     |     | ns   |

| 10   | $\overline{RD}$ rise $\rightarrow$ D0 to 15 hold                                                                                                               | t <sub>HR</sub>  | 0         |           | 0      |     | ns   |

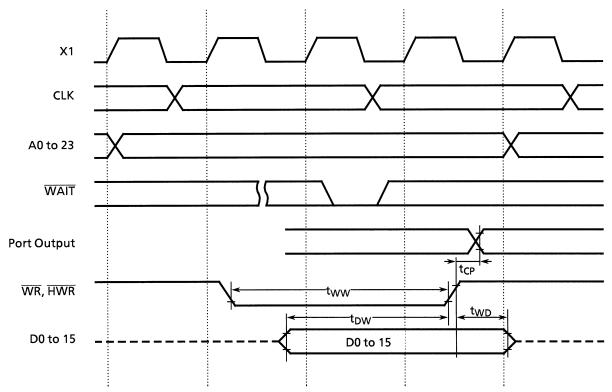

| 11   | WR low pulse width                                                                                                                                             | tww              | 2.5x - 40 |           | 65     |     | ns   |

| 12   | D0 to 15 valid $\rightarrow \overline{WR}$ rise                                                                                                                | t <sub>DW</sub>  | 2.0x - 40 |           | 44     |     | ns   |

| 13   | WR rise →D0 to 15 hold                                                                                                                                         | t <sub>WD</sub>  | 0.5x - 10 |           | 11     |     | ns   |

| 14   | A0 to 23 valid $\rightarrow \overline{WAIT}$ input $\binom{1 \text{ WAIT}}{+ \text{ n mode}}$                                                                  | t <sub>AW</sub>  |           | 3.5x - 90 |        | 57  | ns   |

|      | A0 to 23 valid $\rightarrow \overline{\text{WAIT}}$ input $\binom{0+\eta \text{WAIT}}{\text{mode}}$                                                            | t <sub>AW</sub>  |           | 1.5x – 40 |        | 23  | ns   |

| 15   | $\overline{\text{RD/WR}} \text{ fall} \rightarrow \overline{\text{WAIT}} \text{ hold} \qquad \begin{pmatrix} 1 \text{ WAIT} \\ + \text{ n mode} \end{pmatrix}$ | t <sub>CW</sub>  | 2.5x + 0  |           | 105    |     | ns   |

|      | $\overline{\text{RD/WR}} \text{ fall} \rightarrow \overline{\text{WAIT}} \text{ hold} \qquad \stackrel{\text{(0+n WAIT)}}{\text{mode}}$                        | t <sub>CW</sub>  | 0.5x + 0  |           | 21     |     | ns   |

| 16   | WR rise→ PORT valid                                                                                                                                            | t <sub>CP</sub>  |           | 200       |        | 200 | ns   |

#### AC measuring conditions

- Output level: High 2.2V / Low 0.8V, CL = 50 pF

- Input level: High 2.4V / Low 0.45V (D0 to D15)

High 0.8 x Vcc / Low 0.2 x Vcc (except for D0 to D15)

## (2) Write cycle

## 4.4 Serial Channel Timing

#### (1) I/O interface mode

#### [1] SCLK input mode

$Vcc = +5 V \pm 10\%$ , Ta = -40 to +85°C (fc = 8 to 24 MHz)

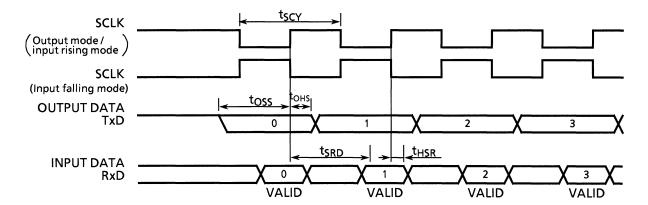

| P                                | C. mala al       | Vari                  | able                        | 24 MHz |     | Unit |

|----------------------------------|------------------|-----------------------|-----------------------------|--------|-----|------|

| Parameter                        | Symbol           | Min                   | Max                         | Min    |     | Unit |

| SCLK cycle                       | t <sub>SCY</sub> | 16x                   |                             | 0.667  |     | μS   |

| Output Data → SCLK rise/fall*    | toss             | $t_{SCY}/2 - 5x - 50$ |                             | 75     |     | ns   |

| SCLK rise/fall*→Output Data hold | tons             | 5x – 100              |                             | 108    |     | ns   |

| SCLK rise/fall*→input data hold  | t <sub>HSR</sub> | 0                     |                             | 0      |     | ns   |

| SCLK rise/fall*→valid data input | t <sub>SRD</sub> |                       | t <sub>SCY</sub> – 5x – 100 |        | 358 | ns   |

<sup>\*)</sup> SCLK rise/fall: In SCLK rising edge mode, SCLK rising edge timing; in SCLK falling edge mode, SCLK falling edge timing

#### [2] SCLK output mode

$Vcc = +5 V \pm 10\%$ , Ta = -40 to +85°C (fc = 8 to 24 MHz)

| Davamatan                           | 6                | Variable                    |                             | 24 MHz |       | Unit |

|-------------------------------------|------------------|-----------------------------|-----------------------------|--------|-------|------|

| Parameter                           | Symbol           | Min                         | Max                         | Min    | Max   | Unit |

| SCLK cycle (programmable)           | t <sub>SCY</sub> | 16x                         | 8192x                       | 0.667  | 341.3 | μS   |

| Output Data → SCLK rising edge      | toss             | t <sub>SCY</sub> – 2x – 150 |                             | 433    |       | ns   |

| SCLK rising edge → Output Data hold | t <sub>OHS</sub> | 2x - 80                     |                             | 3      |       | ns   |

| SCLK rising edge → Input Data hold  | t <sub>HSR</sub> | 0                           |                             | 0      |       | ns   |

| SCLK rising edge → valid data input | t <sub>SRD</sub> |                             | t <sub>SCY</sub> – 2x – 150 |        | 433   | ns   |

#### (2) UART mode (SCLK0 to 1 external input)

$Vcc = +5 V \pm 10\%$ , Ta = -40 to +85°C (fc = 8 to 24 MHz)

| Parameter                   | Symbol            | Vari    | able | 24 1 | Unit       |      |

|-----------------------------|-------------------|---------|------|------|------------|------|

| Parameter                   | Symbol            | Min     | Max  | Min  | MHz<br>Max | Unit |

| SCLK cycle                  | t <sub>SCY</sub>  | 4x + 20 |      | 187  |            | ns   |

| Low-level SCLK pulse width  | t <sub>SCYL</sub> | 2x + 5  |      | 88   |            | ns   |

| High-level SCLK pulse width | t <sub>SCYH</sub> | 2x + 5  |      | 88   |            | ns   |

## 4.5 AD Conversion Characteristics

$Vcc = +5 V \pm 10\%$ , Ta = -40 to +85°C (fc = 8 to 24 MHz)

| Param                                     | eter                  | Symbol            | Test Conditions       | Min               | Тур  | Max               | Unit |

|-------------------------------------------|-----------------------|-------------------|-----------------------|-------------------|------|-------------------|------|

| AD analog reference supply voltage (+)    |                       | V <sub>REFH</sub> |                       | Vcc – 0.2         |      | Vcc               |      |

| AD analog reference supply voltage ( – )  |                       | V <sub>REFL</sub> |                       | Vss               |      | Vss + 0.2         | V    |

| Analog reference voltage                  |                       | AV <sub>CC</sub>  |                       | Vcc – 0.2         |      | Vcc               |      |

| Analog reference voltage                  |                       | AVSS              |                       | Vss               |      | Vss + 0.2         |      |

| Analog input voltage                      | t voltage             |                   |                       | V <sub>REFL</sub> |      | V <sub>REFH</sub> |      |

| Analog reference                          | <vrefon> = 1</vrefon> |                   | $Vcc = +5 V \pm 10\%$ |                   |      | 3.7               | mA   |

| voltage supply<br>current                 | <vrefon> = 0</vrefon> | REF               | Vcc = +5 V ± 10%      |                   | 0.02 | 5.0               | μΑ   |

| Total tolerance<br>(excludes quantization | n error)              | E <sub>T</sub>    | Vcc = +5V±10%         |                   | ± 1  | ±3                | LSB  |

Note 1:  $1LSB = (VREFH - VREFL) / 2^{10}[V]$

Note 2: Power supply current ICC from the VCC pin includes the power supply current from the AVCC pin.

# 4.6 Event Counter (External Input Clocks: TI0, TI4, TI8, TI9, TIA, TIB)

$Vcc = +5 V \pm 10\%$ , Ta = -40 to +85°C (fc = 8 to 24 MHz)

| Damanatan                                   | Complete          | Variable |     | 24 MHz |     | Unit |

|---------------------------------------------|-------------------|----------|-----|--------|-----|------|

| Parameter                                   | Symbol            | Min      | Max | Min    | Max | Unit |

| External input clock cycle                  | t <sub>VCK</sub>  | 8x + 100 |     | 433    |     | ns   |

| External low-level input clock pulse width  | t <sub>VCKL</sub> | 4x + 40  |     | 207    |     | ns   |

| External high-level input clock pulse width | t <sub>VCKH</sub> | 4x + 40  |     | 207    |     | ns   |

# 4.7 Interrupt Operation

$Vcc = +5 V \pm 10\%$ , Ta = -40 to +85°C (fc = 8 to 24 MHz)

| Parameter.                            | Symbol             | Variable |     | 24 MHz |     | Unit |

|---------------------------------------|--------------------|----------|-----|--------|-----|------|

| Parameter                             |                    | Min      | Max | Min    | Max | Unit |

| NMI, INTO to 4 low-level pulse width  | t <sub>INTAL</sub> | 4x       |     | 167    |     | ns   |

| NMI, INTO to 4 high-level pulse width | t <sub>INTAH</sub> | 4x       |     | 167    |     | ns   |

| INT5 to INT8 low-level pulse width    | t <sub>INTBL</sub> | 8x + 100 |     | 433    |     | ns   |

| INT5 to INT8 high-level pulse width   | t <sub>INTBH</sub> | 8x + 100 |     | 433    |     | ns   |

## 4.8 Bus Request/Bus Acknowledge Timing

| Vcc =  | +5V +   | 10% Ta =   | - 40 to | + 85°C (fc = | = 8 to 24 MHz)   |

|--------|---------|------------|---------|--------------|------------------|

| V (( - | T J V - | 1070. Ia - | - 40 10 | T 03 C 11C - | - 0 10 24 111721 |

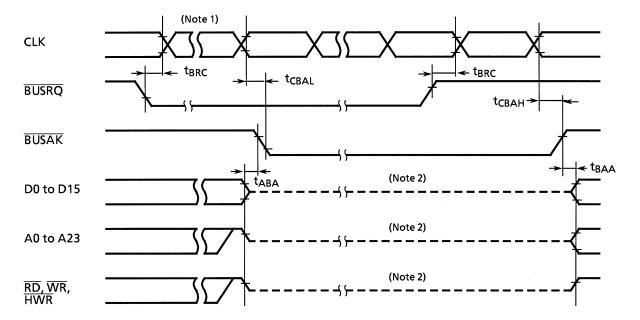

| Parameter.                                           | Symbol            | Variable |            | 24 MHz |     | Unit |

|------------------------------------------------------|-------------------|----------|------------|--------|-----|------|

| Parameter                                            |                   | Min      | Max        | Min    | Max | Unit |

| BUSRQ setup time for CLK                             | t <sub>BRC</sub>  | 120      |            | 120    |     | ns   |

| CLK→BUSAK fall                                       | t <sub>CBAL</sub> |          | 2.0x + 120 |        | 203 | ns   |

| CLK→BUSAK rise                                       | t <sub>CBAH</sub> |          | 0.5x + 40  |        | 61  | ns   |

| Time from output buffer off until BUSAK falling edge | t <sub>ABA</sub>  | 0        | 80         | 0      | 80  | ns   |

| Time from BUSAK rising edge until output buffer on   | t <sub>BAA</sub>  | 0        | 80         | 0      | 80  | ns   |

Note 1: When BUSRQ goes to low level to request bus release, if the current bus cycle is yet complete due to a wait, the bus is not released until the wait completes.

Note 2: The dotted line indicates only that the output buffer is off, not that the signal is at middle level. Immediately after bus release, the signal level prior to the bus release is held dynamically by the external load capacitance. Therefore, designs should allow for the fact that when using an external resistor or similar to fix the signal level while the bus is released, after bus release a delay occurs before the signal goes to its fixed level (due to the CR time constant). The internal programmable pull-up resistor continues to function in accordance with the internal signal level.