# TOSHIBA

# **TOSHIBA 32-bit RISC Microprocessor**

# TX03 Series TMPM320C1DFG

Under development/Tentative

Rev1.05

This data sheet is an interim version that includes contents under editing.

TOSHIBA CORPORATION Semiconductor Company

# Contents

| 1.   | Overview and Features          | <br>TMPM320C1D- | 3    |

|------|--------------------------------|-----------------|------|

| 2.   | Pin Configuration and Function | <br>TMPM320C1D- | 6    |

| 3.   | Operation Description          | <br>TMPM320C1D- | 100  |

| 3.1  | System                         | <br>TMPM320C1D- | 100  |

| 3.2  | Debug Interface                | <br>TMPM320C1D- | 200  |

| 3.3  | Memory Map                     | <br>TMPM320C1D- | 300  |

| 3.4  | CPU                            | <br>TMPM320C1D- | 400  |

| 3.5  | PLL and Clock Controller       | <br>TMPM320C1D- | 500  |

| 3.7  | Interrupt (exceptions)         | <br>TMPM320C1D- | 700  |

| 3.8  | DMA Controller (DMAC)          | <br>TMPM320C1D- | 800  |

| 3.9  | Port Function (GPIO)           | <br>TMPM320C1D- | 900  |

| 3.10 | Memory Controller (SMC)        | <br>TMPM320C1D- | 1000 |

| 3.11 | eDRAM Controller               | <br>TMPM320C1D- | 1100 |

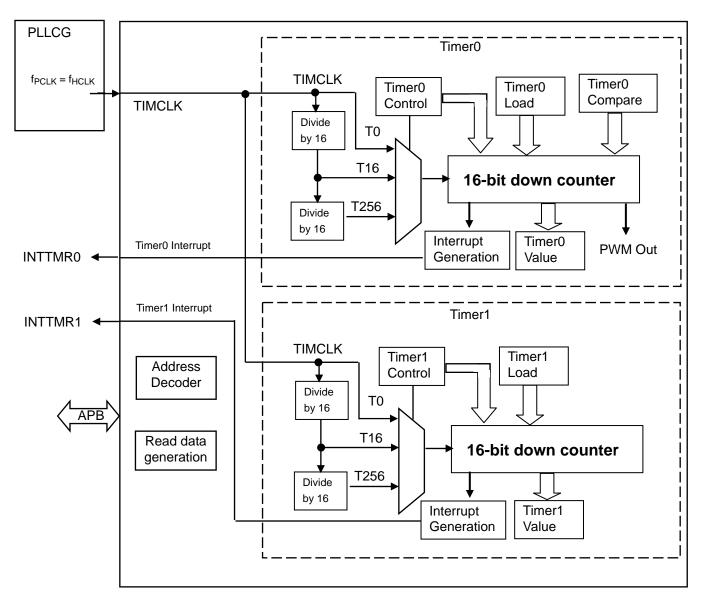

| 3.12 | 16-bit Timer/PWM               | <br>TMPM320C1D- | 1200 |

| 3.13 | UART                           | <br>TMPM320C1D- | 1300 |

| 3.14 | l <sup>2</sup> C Bus           | <br>TMPM320C1D- | 1400 |

| 3.15 | SSP                            | <br>TMPM320C1D- | 1500 |

| 3.16 | USB Host Controller            | <br>TMPM320C1D- | 1600 |

| 3.17 | SD Host Controller             | <br>TMPM320C1D- | 1700 |

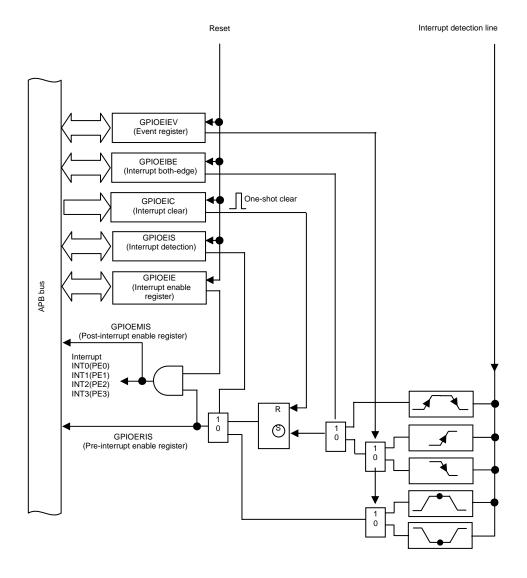

| 3.18 | AD Converter                   | <br>TMPM320C1D- | 1800 |

| 3.19 | Watchdog Timer (WDT)           | <br>TMPM320C1D- | 1900 |

| 3.20 | I2S                            | <br>TMPM320C1D- | 2000 |

| 4.   | Electrical Characteristics     | <br>TMPM320C1D- | 3000 |

| 5.   | Special Function Register      | <br>TMPM320C1D- | 3100 |

| 6.   | Port Equivalent Circuit        | <br>TMPM320C1D- | 3200 |

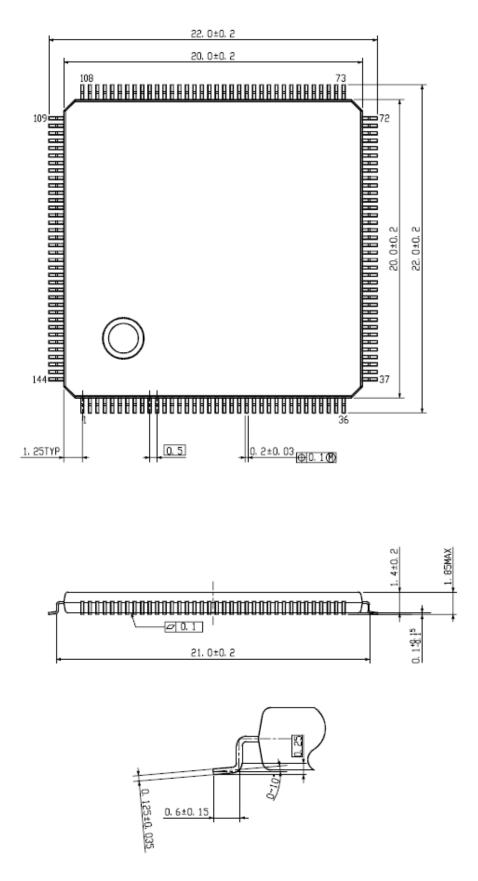

| 7.   | Outside Dimensions             | <br>TMPM320C1D- | 3300 |

|      |                                |                 |      |

#### **RESTRICTIONS ON PRODUCT USE**

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties

which may result from its use. No license is granted by implication or otherwise under any patents or

other rights of TOSHIBA or the third parties.

- Please contact your sales representative for product-by-product details in this document regarding RoHS compatibility. Please use these products in this document in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance with applicable laws and regulations.

ARM, ARM Powered, ARM7TDMI, ARM9TDMI, ADK, ARMulator, Embedded-ICE, Jazelle, MicroPack, ModelGen, MOVE, Multi-ICE, PrimeCell, StrongARM, The Architecture for the Digital World, and Thumb are registered trademarks of ARM Limited in the EU and other countries. ACT, AMBA, Integrator, MultiTrace, PrimXsys, RealView, and SecurCore are trademarks of ARM Limited in the EU and other countries.

## - Introduction - Notes on the registers -

This device has SFR (Special Function Register) each IP (Peripheral circuits). SFR is shown as following in this data book.

a) IP lists

- IP lists show the register name, address and easy descriptions.

- 32bit address is assigned to all registers. It shows as [base address + (specific) address].

|                  |                                             | base address = 0x0000_0000 |

|------------------|---------------------------------------------|----------------------------|

| Register<br>Name | Address<br>(b <del>a</del> se <del></del> ) | Description                |

| SAMPLE 🕻         | 0x0001                                      | Sample register            |

|                  | <b>`</b> '                                  |                            |

Note1: Case of this register (SAMPLE): 00000001 address because 00000000 address (hex)+0001 address (hex) Note2: This register is sample register. There is not this data book.

#### b) SFR (register) description

- Basically, each register is structured 32 bit register. (There is a part of exception.)

- Each description shows Bit, Bit Symbol, Type, Reset value and Description.

| Bit    | Bit<br>Symbol | Туре | Reset<br>Value | Description                                                                                                                            |

|--------|---------------|------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| [31:8] | -             | -    | Undefined      | Read undefined. Write as zero.                                                                                                         |

| [7:6]  | SAMPLE76      | R/W  | 0y00           | Sample setting<br>0y00: Set to Sample mode 0<br>0y01: Set to Sample mode 1<br>0y10: Set to Sample mode 2<br>0y11: Set to Sample mode 3 |

|        |               |      |                |                                                                                                                                        |

$Address = (0x0000_0000) + (0x0001)$

| Note1: Basically 3types. |                   |  |  |  |

|--------------------------|-------------------|--|--|--|

| R/W(READ/WRITE):         | Enable Read/Write |  |  |  |

| RO(READ ONLY) :          | Enable Read only  |  |  |  |

| WO(WRITE ONLY) :         | Enable Write only |  |  |  |

There are exception types (USB device controller and SD host controller). Please refer to those sections.

| Note2: Bit state description: |                        |

|-------------------------------|------------------------|

| Hexadecimal:                  | 0x00FF = 255 (Decimal) |

| Binary:                       | 0y0101 = 5 (Decimal)   |

Note3: 1 Word = 32 bit.

# 32-bit RISC Microprocessor TMPM320C1DFG

# 1. Overview and Features

The TMPM320C1D is a 32-bit RISC microprocessor with a built-in ARM Cortex-M3 core, which is suitable for microcontrollers and built-in processors for applications.

The function overview and features are as follows:

- (1) Cortex-M3 manufactured by ARM is used.

- ARMv7-M architecture

- Thumb-2 command set

- 3-stage pipeline

- (2) Maximum operating frequency: 144 MHz (12 MHz × 12 multiplied)

- (3) Built-in program memory: Data memory

- Built-in RAM RAM: 320 Kbytes (can be used as programs or data) eDRAM: 1 Mbyte (can be used as programs or data)

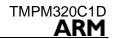

- (4) Memory controller

- Chip-select output: 2 channels

- Supports non-synchronous memories (such as SRAM and NOR Flash memory).

- Separate bus system:

External address23 bits: A0-A22 (Access space of minimum 1 MB to maximum 16 MB × 2ch)External data bus16 bits: D0-D15

- (5) 16-bit timer: 8 channels

- Supports 4-system PWM output by using timers of 4 out of 8 channels.

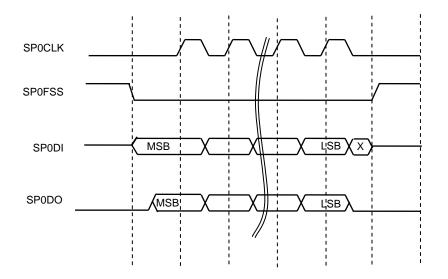

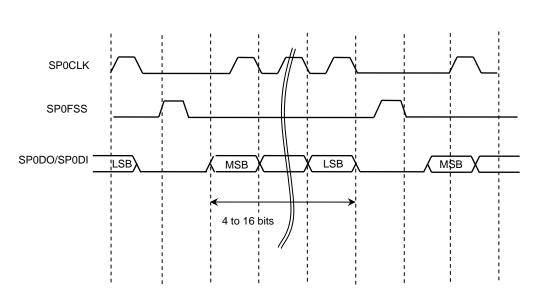

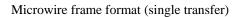

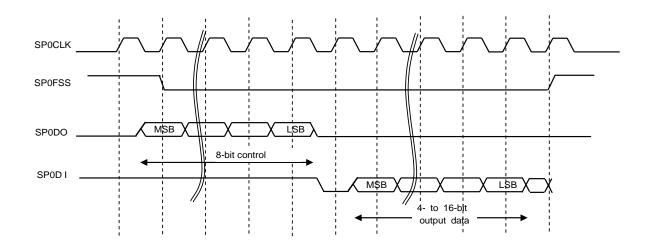

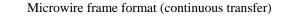

- (6) Synchronous serial bus interface (SSP): 4 channels

- Supports the formats SPI, SSI, and MicroWire.

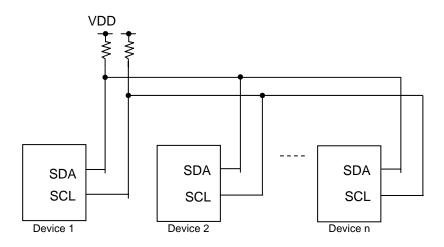

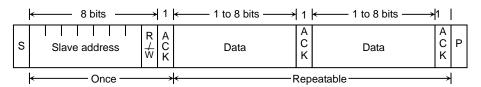

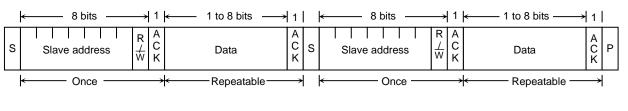

- (7)  $I^2C$  bus interface: 2 channels

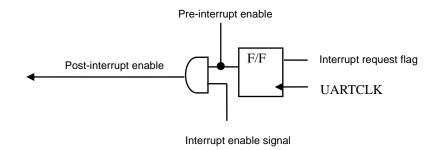

- (8) UART: 4 channels

- Channel0/Channel1: Supports Full UART.

- Channel2/Channel3: Supports only 2 pins: TXD and RXD.

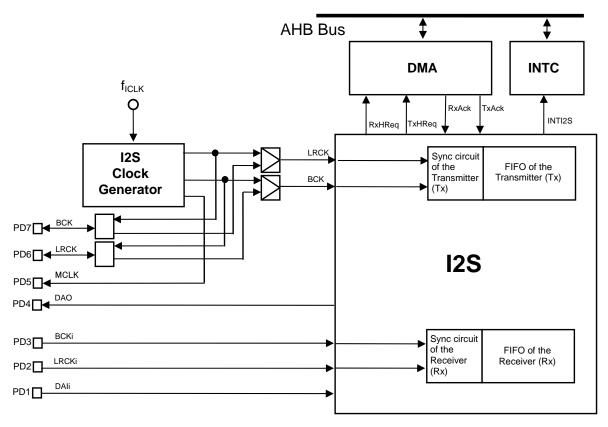

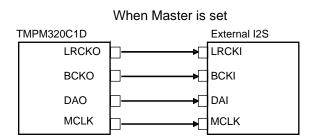

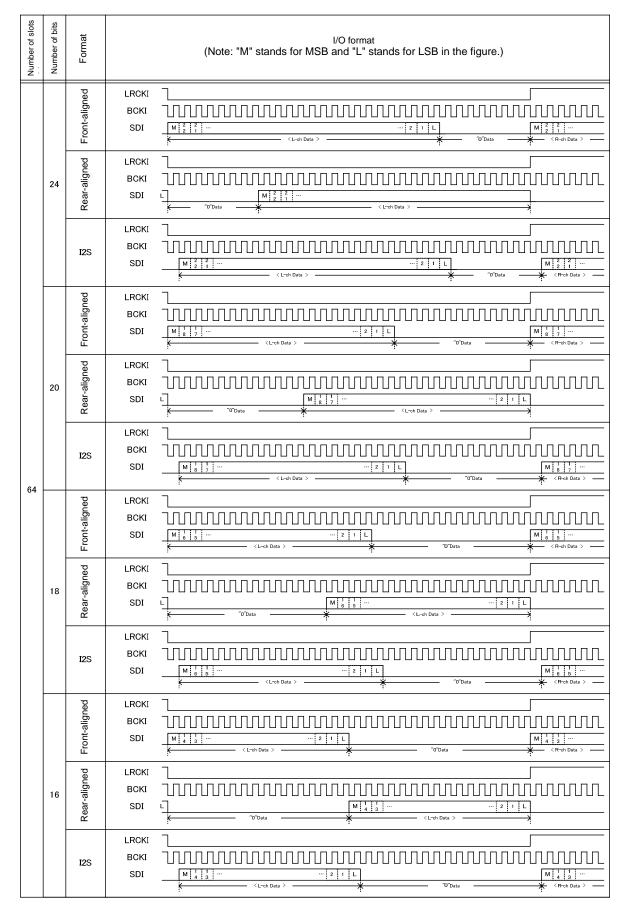

- (9)  $I^2S$  (Inter-IC Sound) bus interface: 2 channels (Input: 1 channel, output: 1 channel)

- Can control input and output independently.

- Supports the formats of each front-aligned, back-aligned, and I2S.

- Supports 16, 18, 20, and 24 bit data length.

- Supports 32, 48, and 64 slots.

Note: For more information on audio standard output frequency errors, refer to Section 3.20.

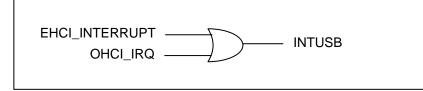

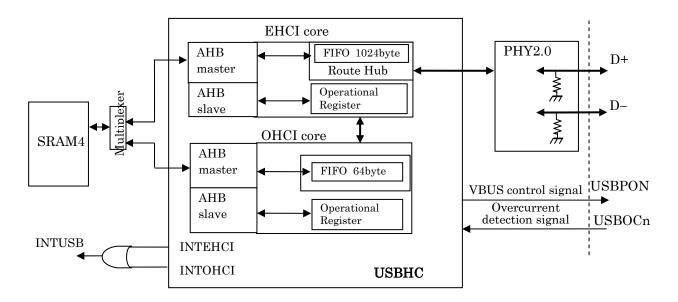

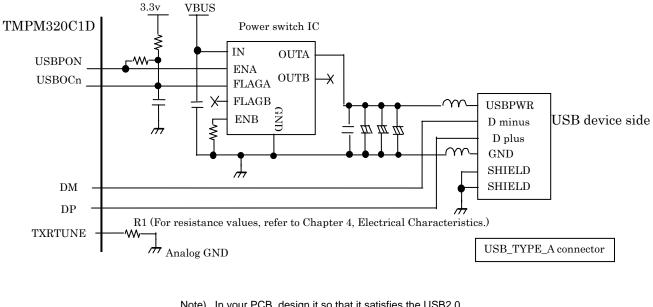

- (10) USB host controller: 1 channel

- Compliant with the USB2.0 Specification revision 2.0

- Enhanced Host Controller Interface (EHCI) Specification revision 1.0

- Complies with Open Host Controller Interface (OHCI) for USB release 1.0a.

- Supports High Speed (480 Mbps) and Full Speed (12 Mbps).

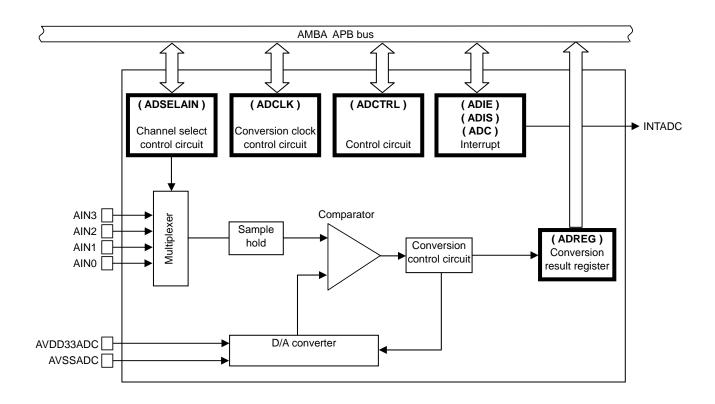

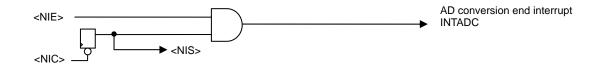

- (11) 10-bit AD converter (with a built-in sample-and-hold circuit): 4 channels

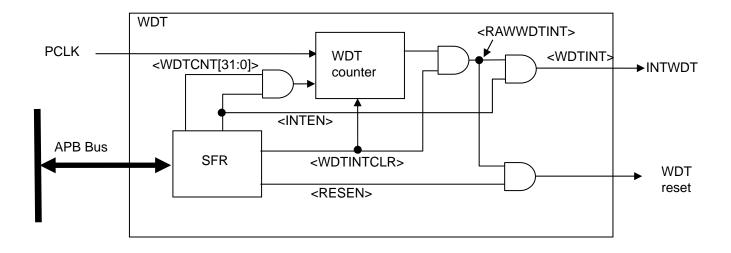

- (12) Watchdog timer

- (13) Interrupt function: 28 types

- External 4 types INT0 to INT3 (edge: rise and fall, level: High and Low)

- Internal 24 types 16-bit timer × 8, A/D converter × 1, UART × 4, I2C × 2, SSP × 4, USB × 1, SD host controller × 1, DMAC × 2, WDT × 1

- (14) Input/output port: 55 terminals

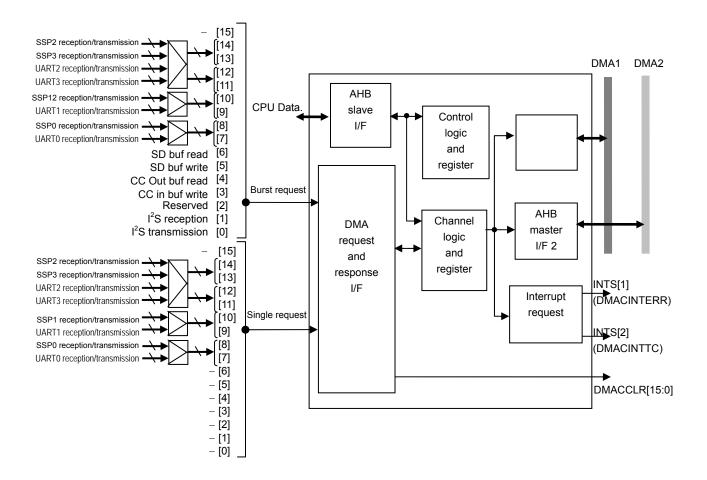

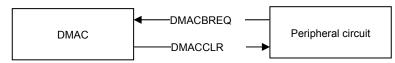

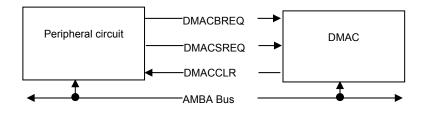

- (15) DMA controller: 8 channels

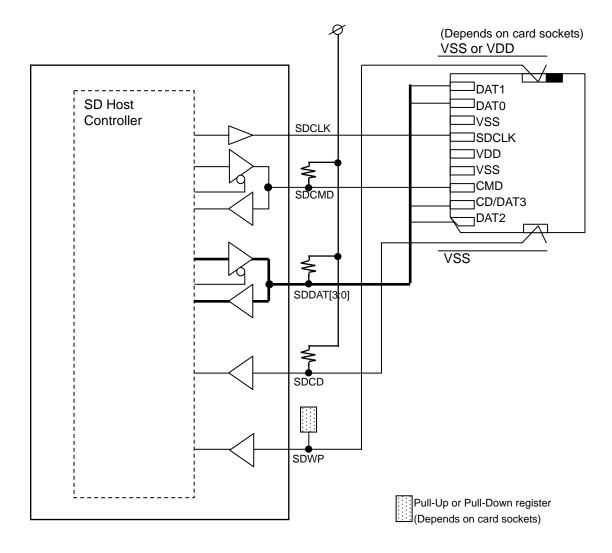

- (16) SD host controller: 1 channel

- Supports SD association(SDA) specifications version 2.00.

- Supports SD card I/F mode (4-bit parallel).

- Built-in 512-byte FIFO buffer

- (17) Clock control function

- Two blocks of built-in clock multiple circuit (PLL) enable an external 12 MHz oscillator to supply USB clock frequency of 480 MHz and clock frequency of 144 MHz to the CPU.

- (18) Debugging function

- Supports on-chip debugging.

- Supports SWD (Serial wire debug) as the debugging function.

- Supports ETM (Embedded trace macrocell) as the tracing function.

- (19) Operating voltage

| ٠ | Power supply for built-in logic | $DVCC12 = 1.2V \pm 0.1V$                                  |

|---|---------------------------------|-----------------------------------------------------------|

| • | Power supply for PLL            | $DVCC12PLL = 1.2V \pm 0.1V$                               |

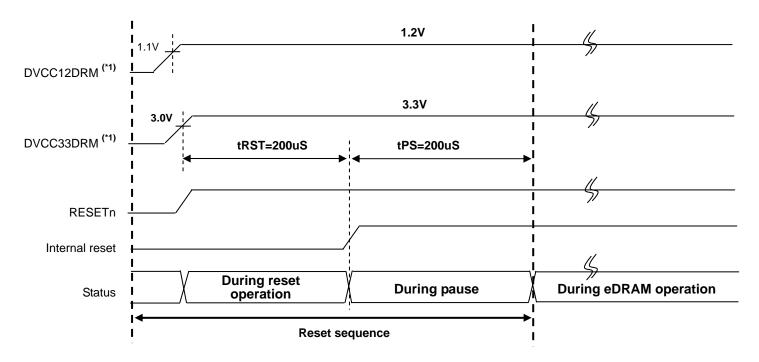

| • | Power supply for eDRAM          | DVCC33DRM = $3.3V \pm 0.3V$ , DVCC12DRM = $1.2V \pm 0.1V$ |

| • | External I/O                    | $DVCC33IO = 3.3V \pm 0.3V$                                |

| • | Power supply for AD converter   | AVDD33ADC = $3.3V \pm 0.3V$                               |

| • | Power supply for USB            | AVDD33USB = $3.3V \pm 0.3V$                               |

|   |                                 | $DVDD12USB = 1.2 \pm 0.1V$                                |

- (20) Temperature range

- -40°C to 85°C

- (21) Package

- 144-pin QFP: LQFP144-P-2020-0.50E

TOSHIBA

Figure 1.1 TMPM320C1D Block Diagram

# 2. Pin Configuration and Function

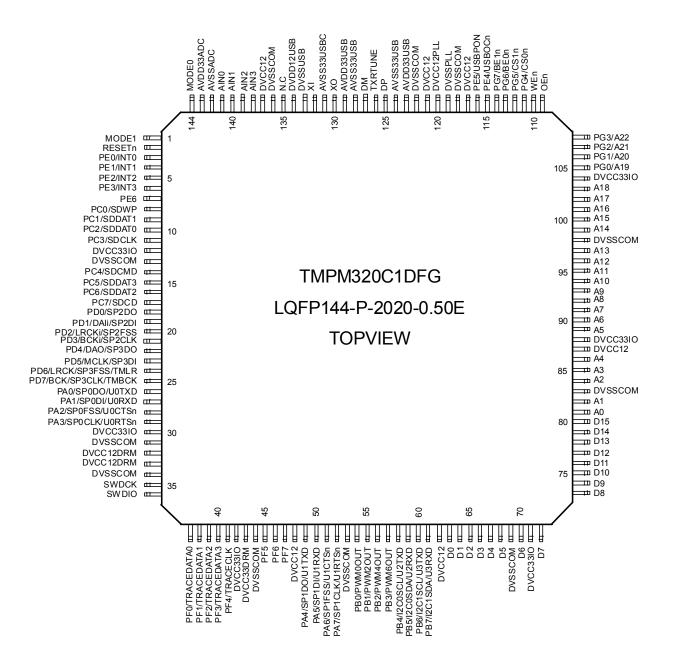

This section provides a pin configuration diagram of the TMPM320C1D, names of I/O pins, and brief description of their functions.

# 2.1 Pin Configuration Diagram (Top View)

Figure 2.1.1 shows the TMPM320C1DFG pin configuration.

Note) Open N.C pins are acceptable.

Figure 2.1.2 Pin configuration diagram

# 2.2 Pin Name and Function

Names and functions of I/O pins are shown below.

Table 2.2.1 Pin names and functions (1/4)

| Pin name  | Number of pins | Input/Output | Function                                                        | Remarks |

|-----------|----------------|--------------|-----------------------------------------------------------------|---------|

| D0 ~ D7   | 8              | Input/Output | Data: Data bus D0 to D7                                         |         |

| D8 ~ D15  | 8              | Input/Output | Data: Data bus D8 to D15                                        |         |

| A0 ~ A7   | 8              | Output       | Address: Address bus A0 to A7                                   |         |

| A8 ~ A15  | 8              | Output       | Address: Address bus A8 to A15                                  |         |

| A16 ( A18 | 3              | Output       | Address: Address bus A16 to A18                                 |         |

| OEn       | 1              | Output       | Out-enable signal for NOR FLASH/SRAM                            |         |

| WEn       | 1              | Output       | Write-enable signal for NOR FLASH/SRAM                          |         |

| PG0 ~ PG3 |                | Input/Output | Port G0 to G3: I/O port                                         |         |

| A19 ~ A22 | 4              | Output       | Address: Address bus A19 to A22                                 |         |

| PG4       |                | Input/Output | Port G4: I/O port                                               |         |

| CS0n      | 1              | Output       | Chip select 0 for NOR-FLASH/SRAM                                |         |

| PG5       |                | Input/Output | Port G5: I/O port                                               |         |

| CS1n      | 1              | Output       | Chip select 1 for NOR-FLASH/SRAM                                |         |

| PG6       |                | Input/Output | Port PG6: I/O port                                              |         |

| BE0n      | 1              | Output       | Byte enable signal (D0 to D7) for SRAM                          |         |

| PG7       |                | Input/Output | Port PG7: I/O port                                              |         |

| BE1n      | 1              | Output       | Byte enable signal (D8 to D15) for SRAM                         |         |

| PA0       |                | Input/Output | Port A0: I/O port                                               |         |

| SP0DO     | 1              | Output       | Data output pin for SSP0                                        |         |

| U0TXD     |                | Output       | UART function 0 transmission data                               |         |

| PA1       |                | Input/Output | Port A1: I/O port                                               |         |

| SP0DI     | 1              | Input        | Data input pin for SSP0                                         |         |

| UORXD     |                | Input        | UART function 0 transmission data                               |         |

| PA2       |                | Input/Output | Port A2: I/O port                                               |         |

| SP0FSS    | 1              | Input/Output | FSS pin for SSP0                                                |         |

| U0CTSn    |                | Input        | UART function 0 CTS data input (Clear to send)                  |         |

| PA3       |                | Input/Output | Port A3: I/O port                                               |         |

| SPOCLK    | 1              | Input/Output | Clock pin for SSP0                                              |         |

| U0RTSn    |                | Output       | UART function 0 output modem control line RTS (Request To Send) |         |

| PA4       |                | Input/Output | Port A4: I/O port                                               |         |

| SP1DO     | 1              | Output       | Data output pin for SSP1                                        |         |

| U1TXD     |                | Output       | UART function 1 transmission data                               |         |

| PA5       |                | Input/Output | Port A5: I/O port                                               |         |

| SP1DI     | 1              | Input        | Data input pin for SSP1                                         |         |

| U1RXD     |                | Input        | UART function 1 transmission data                               |         |

| PA6       |                | Input/Output | Port A6: I/O port                                               |         |

| SP1FSS    | 1              | Input/Output | FSS pin for SSP1                                                |         |

| U1CTSn    |                | Output       | UART function 1 receive data                                    |         |

| PA7       |                | Input/Output | Port A7: I/O port                                               |         |

| SP1CLK    | 1              | Input/Output | Clock pin for SSP1                                              |         |

| U1RTSn    |                | Output       | UART function 1 output modem control line RTS (Request To Send) |         |

| Table 2.2.2 Pin names and functions (2/4) |

|-------------------------------------------|

|-------------------------------------------|

| Pin name | Number of pins | Input/Output | Function                          | Remarks |

|----------|----------------|--------------|-----------------------------------|---------|

| PB0      | 4              | Input/Output | Port B0: I/O port                 |         |

| PWM0OUT  | 1              | Output       | Timer PWM0 output pin             |         |

| PB1      | 4              | Input/Output | Port B1: I/O port                 |         |

| PWM2OUT  | 1              | Output       | Timer PWM1 output pin             |         |

| PB2      | 1              | Input/Output | Port B2: I/O port                 |         |

| PWM4OUT  | 1              | Output       | Timer PWM4 output pin             |         |

| PB3      | 1              | Input/Output | Port B3: I/O port                 |         |

| PWM6OUT  | 1              | Output       | Timer PWM6 output pin             |         |

| PB4      |                | Input/Output | Port B4: I/O port                 |         |

| I2C0SCL  | 1              | Input/Output | Clock input/output pin for I2C0   |         |

| U2TXD    |                | Output       | UART function 2 transmission data |         |

| PB5      |                | Input/Output | Port B5: I/O port                 |         |

| I2C0SDA  | 1              | Input/Output | Data input/output pin for I2C0    |         |

| U2RXD    |                | Input        | UART function 2 receive data      |         |

| PB6      |                | Input/Output | Port B6: I/O port                 |         |

| I2C1SCL  | 1              | Input/Output | Clock input/output pin for I2C1   |         |

| U3TXD    |                | Output       | UART function 3 transmission data |         |

| PB7      |                | Input/Output | Port B7: I/O port                 |         |

| I2C1SDA  | 1              | Input/Output | Data input/output pin for I2C1    |         |

| U3RXD    |                | Input        | UART function 3 receive data      |         |

| PC0      |                | Input/Output | Port C0: I/O port                 |         |

| SDWP     | 1              | Input        | SD: Write-protect signal          |         |

| PC1      |                | Input/Output | Port C1: I/O port                 |         |

| SDDAT1   | 1              | Input/Output | SD: Data 1 input/output pin       |         |

| PC2      |                | Input/Output | Port C2: I/O port                 |         |

| SDDAT0   | 1              | Input/Output | SD: Data 0 input/output pin       |         |

| PC3      |                | Input/Output | Port C3: I/O port                 |         |

| SDCLK    | 1              | Output       | SD: Clock output pin              |         |

| PC4      |                | Input/Output | Port C4: I/O port                 |         |

| SDCMD    | 1              | Output       | SD: Command output pin            |         |

| PC5      |                | Input/Output | Port C5: I/O port                 |         |

| SDDAT3   | 1              | Input/Output | SD: Data 3 input/output pin       |         |

| PC6      |                | Input/Output | Port C6: I/O port                 |         |

| SDDAT2   | 1              | Input/Output | SD: Data 2 input/output pin       |         |

| PC7      |                | Input/Output | Port C7: I/O port                 |         |

| SDCD     | 1              | Input        | SD: Card detection pin            |         |

| Table 2.2.3 Pin names and functions (3/4) | Table 2.2.3 Pin na | ames and fur | nctions (3/4) |

|-------------------------------------------|--------------------|--------------|---------------|

|-------------------------------------------|--------------------|--------------|---------------|

| Pin name          | Number of<br>pins | Input/Output           | Function                                               | Remarks |

|-------------------|-------------------|------------------------|--------------------------------------------------------|---------|

| PD0               |                   | Input/Output           | Port D0: I/O port                                      |         |

| SP2DO             | 1                 | Output                 | Data output pin for SSP2                               |         |

| PD1               |                   | Input/Output           | Port D1: I/O port                                      |         |

| SP2DI             | 1                 | Input                  | Data input pin for SSP2                                |         |

| DAli              |                   | Input                  | DAli data input pin for I2S                            |         |

| PD2               |                   | Input/Output           | Port D2: I/O port                                      |         |

| SP2FSS            | 1                 | Input/Output           | FSS pin for SSP2                                       |         |

| LRCKi             |                   | Input                  | LRCKi clock input pin for I2S                          |         |

| PD3               |                   | Input/Output           | Port D3: I/O port                                      |         |

| SP2CLK            | 1                 | Input/Output           | Clock pin for SSP2                                     |         |

| BCKi              |                   | Input                  | BCKi clock input pin for I2S                           |         |

| PD4               |                   | Input/Output           | Port D4: I/O port                                      |         |

| SP3DO             | 1                 | Output                 | Data output pin for SSP2                               |         |

| DAO               | 1                 | Output                 | DAO data output pin for I2S                            |         |

| PD5               |                   | Input/Output           | Port D5: I/O port                                      |         |

| SP3DI             | 1                 |                        | Data input pin for SSP3                                |         |

|                   | 1                 | Input                  |                                                        |         |

| MCLK              |                   | Output                 | MCLK clock output pin for I2S                          |         |

| PD6               |                   | Input/Output           | Port D6: I/O port                                      |         |

| SP3FSS            | 1                 | Input/Output           | FSS pin for SSP3                                       |         |

| TMLRCK            |                   | Output                 | SSP_LRCK output                                        |         |

| LRCK              |                   | Output                 | LRCK clock output pin for I2S                          |         |

| PD7               |                   | Input/Output           | Port D7: I/O port                                      |         |

| SP3CLK            | 1                 | Input/Output           | Clock pin for SSP3                                     |         |

| TMBCK             |                   | Output                 | SSP_BCK output                                         |         |

| BCK               |                   | Output                 | BCK clock output pin for I2S                           |         |

| PE0<br>INT0       | 1                 | Input/Output<br>Input  | Port PE0: I/O port<br>External interrupt request pin 0 |         |

| PE1               | 4                 | Input/Output           | Port PE1: I/O port                                     |         |

| INT1              | 1                 | Input                  | External interrupt request pin 1                       |         |

| PE2               | 1                 | Input/Output           | Port PE2: I/O port                                     |         |

| INT2<br>PE3       |                   | Input<br>Input/Output  | External interrupt request pin 2<br>Port PE3: I/O port |         |

| INT3              | 1                 | Input                  | External interrupt request pin 3                       |         |

| PE4               | 1                 | Input/Output           | Port PE4: I/O port                                     |         |

| USBOCn            |                   | Input                  | USB OC (over-current) input pin                        |         |

| PE5<br>USBPON     | 1                 | Input/Output<br>Output | Port PE5: I/O port<br>USB PON (power-on) output pin    |         |

| PE6               | 1                 | Input/Output           | Port PE6: I/O port                                     |         |

| PF0               |                   | Input/Output           | Port PF0: I/O port                                     |         |

| TRACEDATA0        | 1                 | Output                 | ETM: Trace data output pin 0                           |         |

| PF1               | 1                 | Input/Output           | Port PF1: I/O port 1                                   |         |

| TRACEDATA1<br>PF2 |                   | Output<br>Input/Output | ETM: Trace data output pin 1<br>Port PF2: I/O port     |         |

| TRACEDATA2        | 1                 | Output                 | ETM: Trace data output pin 2                           |         |

| PF3               | 1                 | Input/Output           | Port PF3: I/O port                                     |         |

| TRACEDATA3        | 1                 | Output                 | ETM: Trace data output pin 3                           |         |

| PF4<br>TRACECLK   | 1                 | Input/Output           | Port PF4: I/O port                                     |         |

| PF5               | 1                 | Output<br>Input/Output | ETM: Trace clock output pin<br>Port PF5: I/O port      |         |

| PF6               |                   | Input/Output           | Port PF6: I/O port                                     |         |

| PF7               | 1                 | Input/Output           | Port PF7: I/O port                                     |         |

| F1 <sup>-7</sup>  | 1                 | input/Output           | רטונדר /. ווט אטונ                                     |         |

# Table 2.2.4 Pin names and functions (4/4)

| Pin name   | Number of<br>pins | Input/Output | Function                                               | Remarks |

|------------|-------------------|--------------|--------------------------------------------------------|---------|

| DP         | 1                 | Input/Output | USB pin (D+)                                           |         |

| TXRTUNE    | 1                 | Input        | Connect to the AVDD33USB at the resistance of 44.20.   |         |

| DM         | 1                 | Input/Output | USB pin (D-)                                           |         |

| AIN0       | 1                 | Input        | Analog input 0: AD converter input pin                 |         |

| AIN1       | 1                 | Input        | Analog input 1: AD converter input pin                 |         |

| AIN2       | 1                 | Input        | Analog input 2: AD converter input pin                 |         |

| AIN3       | 1                 | Input        | Analog input 3: AD converter input pin                 |         |

| SWDCK      | 1                 | Input        | SWD: Clock input pin for SWD (Serial Wire Debug)       |         |

| SWDIO      | 1                 | Input/Output | SWD: Data input/output pin for SWD (Serial Wire Debug) |         |

| RESETn     | 1                 | Input        | Reset: Initializes TMPM320C1D (with Schmitt input)     |         |

| MODE0      | 1                 | Input        | Startup mode input pin 0                               |         |

| MODE1      | 1                 | Input        | Startup mode input pin 1                               |         |

| XI         | 1                 | Input        | High-frequency oscillator connection input pin         |         |

| ХО         | 1                 | Output       | High-frequency oscillator connection output pin        |         |

| DVCC12     | 6                 | Power supply | VCC power supply for internal logic                    |         |

| DVCC33IO   | 6                 | Power supply | VCC power supply for external I/O                      |         |

| DVSSCOM    | 11                | Power supply | Common VSS power supply (GND)                          |         |

| DVCC33DRM  | 1                 | Power supply | VCC power supply for the internal eDRAM                |         |

| DVCC12DRM  | 2                 | Power supply | VCC power supply for the internal eDRAM                |         |

| DVCC12PLL  | 1                 | Power supply | VCC power supply for the internal PLL                  |         |

| DVSSPLL    | 1                 | Power supply | VSS power supply for the internal PLL (GND)            |         |

| AVDD33USB  | 2                 | Power supply | VCC power supply for USB                               |         |

| AVSS33USB  | 2                 | Power supply | VSS power supply for USB (GND)                         |         |

| AVSS33USBC | 1                 | Power supply | VSS power supply for high-frequency oscillator (GND)   |         |

| DVSSUSB    | 1                 | Power supply | VSS power supply for USB                               |         |

| DVDD12USB  | 1                 | Power supply | y VCC power supply for USB                             |         |

| AVDD33ADC  | 1                 | Power supply | VCC power supply for A/D converter                     |         |

| AVSSADC    | 1                 | Power supply | VSS power supply for A/D converter (GND)               |         |

# 3. Operation Description

3.5 System

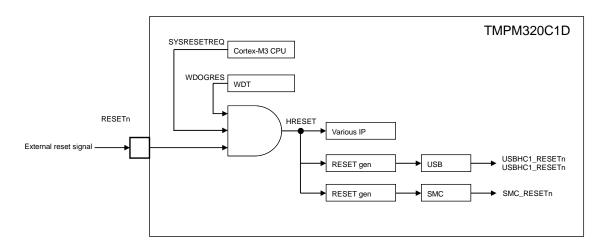

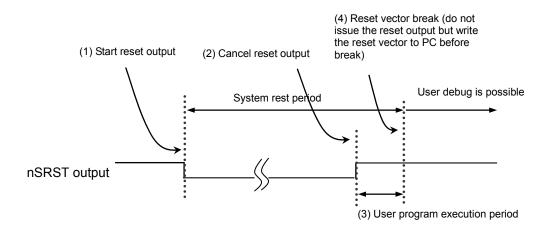

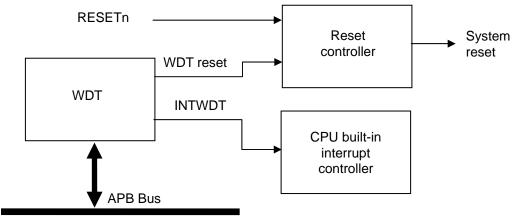

#### 3.5.1 Reset operation

Before resetting TMPM320C1D, make sure that the power supply voltage is within the operating range, oscillation from the internal oscillator is stable at 20 system clock cycles (1.67  $\mu$ s @ X1 = 12 MHz) at least, and the RESETn input pin is set to the "L" level.

After reset, the PLL stops and the PLL output becomes unselected (FCSEL=0).

Therefore, the system clock operates at 12 MHz (X1 = 12 MHz) after reset.

If the reset instruction is accepted, the built-in I/O, I/O ports, and other pins are initialized.

Initializing the internal I/O registers (Refer to the chapter on ports and pins for initial values.)

Note 1) This LSI has a built-in RAM (SRAM and eDRAM), but its data may be lost as a result of reset operation. Initialize data in the built-in RAM after the reset operation.

The Cortex-M3 core interrupt uses the vector method, which sets the 32-bit data (address) stored in the exception address of 0x0000\_0004 into the program counter when reset operation has just been performed.

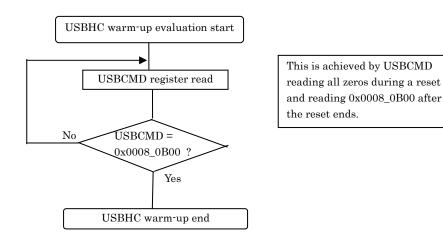

Also, a warm-up time is required for the eDRAM, PLL and USBHC after the reset operation is cancelled. Refer to the chapter on each peripheral for details.

Figure 3.1.1-1 Block Diagram of Reset Input

# 3.5.2 Startup Mode

This microcomputer can use external pin settings to select a startup mode.

# 1. Startup Memory Setting

| Mode setting pin |       | pin   | Operation mode                               |  |  |

|------------------|-------|-------|----------------------------------------------|--|--|

| RESETn           | MODE1 | MODE0 | Operation mode                               |  |  |

|                  | 0     | 0     | Boot mode: Starts from the built-in boot ROM |  |  |

| 1                | 0     | 1     | Normal mode: Starts from the external memory |  |  |

|                  | 1     | 0     | Setting prohibited                           |  |  |

|                  | 1     | 1     | Setting prohibited                           |  |  |

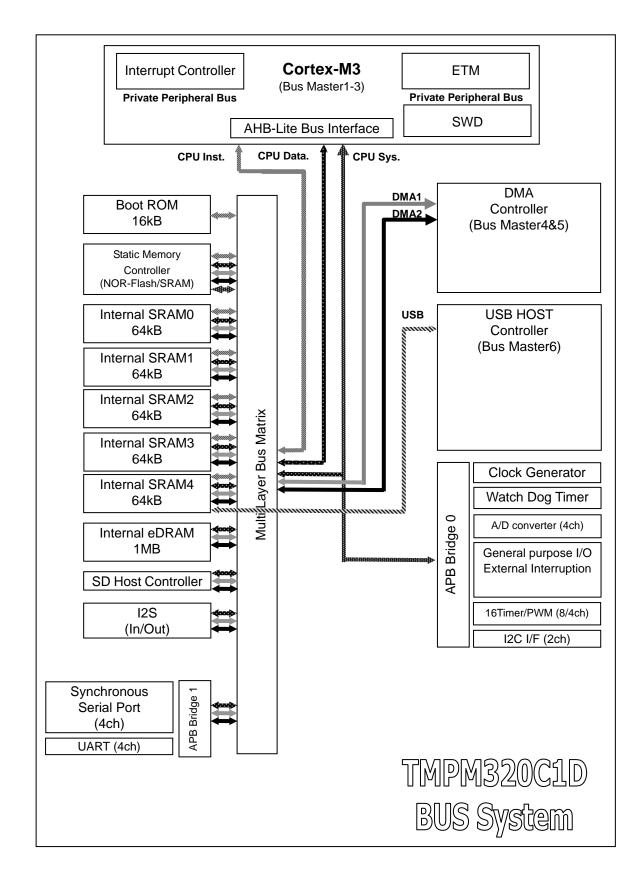

## 3.5.3 Bus Configuration

The TMPM320C1D uses the AHB-Lite bus system in the 6-layer configuration.

#### 3.2 Debug Interface

#### 3.2.1 Overview of Specifications

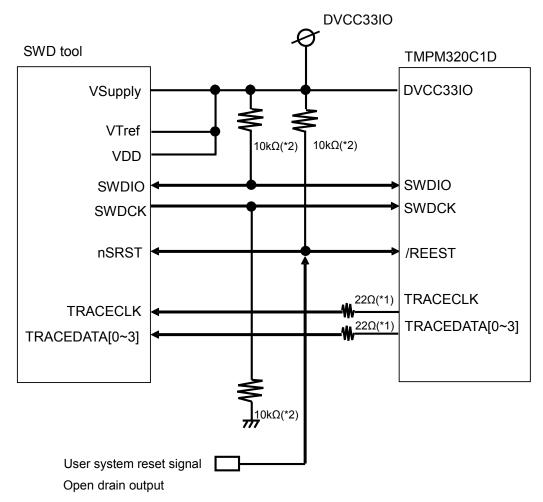

The TMPM320C1D contains the SWD (Serial Wire Debug) unit as the debugging interface for connection to the ICE (In-Circuit Emulator), and the ETM (Embedded Trace Macrocell) unit for tracing and outputting internal programs. ETM outputs signals to dedicated pins (TRACEDATA[0] to [3]) through the TPIU (Trace Port Interface Unit) in the microprocessor.

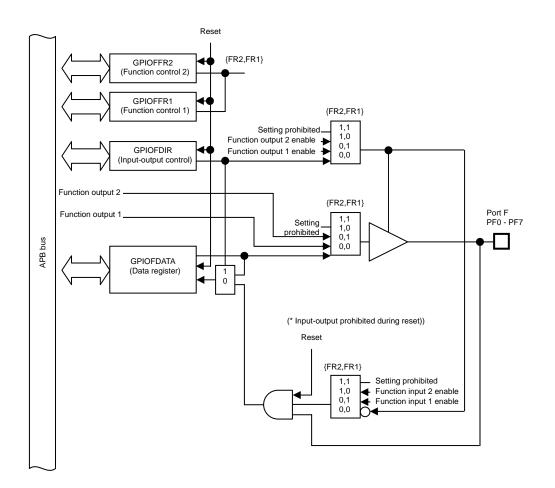

When using the tracing function, you need to enable the corresponding bits in the port function control register GPIOFFR1 of PORTF and the TRACECLKIN output enable bit, CG\_PLLCTRL6< TRACECLKINEN >, in the clock control register 6.

For more information on SWD, ETM, and TPIU, please refer to the documents published by ARM.

Note that the TMPM320C1D does not support connections based on the JTAG (Joint Test Action Group) Standards. Use SWD-compatible tools when connecting the TMPM320C1D to the ICE.

#### 3.2.2 SWD Features

• Supports 2-pin debug interfaces (SWDCK and SWDIO)

#### 3.2.3 ETM Features

• Supports trace output using 4 data signal pins (TRACEDATA[0] to [3]) and 1 clock signal pin (TRACECLK).

- (Note 1) Disable the watchdog timer during debug operation.

- (Note 2) Switch the port function settings before using TRACE.

- (Note 3) For TRACECLK, you can change the output frequency using CG\_PLLCTRL6<FTRACEDIV[17:16]>. For more information, refer to section 3.5, "CG\_PLLCTRL6 (CG PLL Control Register 6)."

- (Note 4) Note that a user program is executed for several tens to hundreds of ms (depending on the SWDCK speed) in order to establish SWD communication with the TMPM320C1D after the reset output from the ICE is cancelled.

#### 3.2.4 Connection example

An example of connections between the TMPM320C1D and the ICE (SWD connection) is shown below.

Figure 3.2.4-2 Connection example with the SWD tool

- (\*1) The resistance is a recommended value. Please select an appropriate resistance value according to the user's needs.

- (\*2) To avoid malfunction of the MPU when the ICE is not connected, pull down at the resistance of 10 kohm.

#### 3.3 Memory Map

The memory map of the TMPM320C1D is as follows:

| Address     |                               | Normal mode<br>(Starts from the external<br>memory) |

|-------------|-------------------------------|-----------------------------------------------------|

| 0x0000_0000 |                               | External NOR-Flash: 16 MB<br>(CS0n)                 |

| 0x0000_2000 |                               | , , , , , , , , , , , , , , , , , , ,               |

| 0x0100_0000 |                               | Built-in SRAM-0: 64 KB                              |

| 0x0101_0000 | Built-in SRAM area            | Built-in SRAM-1: 64 KB                              |

| 0x0102_0000 | (320 KB)                      | Built-in SRAM-2: 64 KB                              |

| 0x0103_0000 | ()                            | Built-in SRAM-3: 64 KB                              |

| 0x0104_0000 |                               | Built-in SRAM-4: 64 KB                              |

| 0x0105_0000 |                               | Unused area                                         |

| 0x2000_0000 |                               | Unused area                                         |

| 0x3000_0000 | Built-in eDRAM<br>area (1 MB) | Built-in eDRAM: 1 MB                                |

| 0x3010_0000 |                               | Unused area                                         |

| 0x4000_0000 |                               | Built-in IO-0 (AHB): 20 KB                          |

| 0x4000_5000 | Built-in peripheral           | Built-in IO-1 (APB): 64 KB                          |

| 0x4001_5000 | area                          | Built-in IO-2 (AHB): 16 KB                          |

|             | (132 KB)                      | Built-in IO-3 (APB): 32 KB                          |

| 0x4002_1000 |                               | Unused area                                         |

| 0x6000_0000 | External<br>NOR-Flash area    | Unused area                                         |

|             | (16 MB)                       |                                                     |

| 0x6100_0000 | External area                 | External: 16 MB                                     |

|             | (16 MB)                       | (CS1n)                                              |

| 0x6200_0000 |                               | Unused area                                         |

| 0xA000_0000 |                               | Unused area                                         |

| 0xE000_0000 |                               | Internal Private Peripheral Bus<br>area             |

| 0xE004_0000 |                               | External Private Peripheral Bus<br>area             |

| 0xE010_0000 |                               | Unused area                                         |

0xFFFF\_FFFF

Note 1) Unused areas must not be accessed.

Note 2) Refer to the documentations published by ARM for details.

Figure 3.3.1 Memory map (details of startup mode, external areas, and internal areas)

TOSHIBA

The following list shows the access relationship between the bus master and slaves (IPs) in normal mode:

| Address     | Normal mode<br>(Starts from the external<br>memory) |                                    | O: Acces | tion relati<br>sible, ∆: <sup>-</sup><br>lable for a<br>CPU(D)<br>M2 | and the<br>The defau | Slave<br>Ilt slave<br>: Must n | responds      | ; |

|-------------|-----------------------------------------------------|------------------------------------|----------|----------------------------------------------------------------------|----------------------|--------------------------------|---------------|---|

| 0x0000_0000 | SMCCS0n<br>External NOR-Flash: 16 MB                |                                    | 0        | 0                                                                    | _                    | 0                              | 0             | Δ |

| 0x0000_2000 |                                                     |                                    |          |                                                                      |                      |                                |               |   |

| 0x0100_0000 | Built-in SRAM-0: 64 KB                              |                                    | 0        | 0                                                                    | -                    | 0                              | 0             | Δ |

| 0x0101_0000 | Built-in SRAM-1: 64 KB                              | Built-in SRAM area                 | 0        | 0                                                                    | -                    | 0                              | 0             | Δ |

| 0x0102_0000 | Built-in SRAM-2: 64 KB                              | (320 KB)                           | 0        | 0                                                                    | -                    | 0                              | 0             | Δ |

| 0x0103_0000 | Built-in SRAM-3: 64 KB                              | ()                                 | 0        | 0                                                                    | -                    | 0                              | 0             | Δ |

| 0x0104_0000 | Built-in SRAM-4: 64 KB                              |                                    | 0        | 0                                                                    | -                    | 0                              | 0             | 0 |

| 0x0105_0000 | Unused area                                         |                                    | Δ        | Δ                                                                    | -                    | Δ                              | Δ             | Δ |

| 0x2000_0000 | Unused area                                         |                                    | _        | -                                                                    | Δ                    | Δ                              | Δ             | Δ |

| 0x3000_0000 | Built-in eDRAM: 1 MB                                | Built-in eDRAM area<br>(1 MB)      | -        | -                                                                    | 0                    | ο                              | 0             | Δ |

| 0x3010_0000 | Unused area                                         |                                    | _        | -                                                                    | Δ                    | Δ                              | Δ             | Δ |

| 0x4000_0000 | Built-in IO-0 (AHB): 20 KB                          |                                    | _        | _                                                                    | 0                    | Δ                              | Δ             | Δ |

|             | Built-in IO-1 (APB): 64 KB                          | Built-in I/O area                  | _        | _                                                                    | 0                    | Δ                              | Δ             | Δ |

| 0x4001_5000 | Built-in IO-2 (AHB): 16 KB                          | (132 KB)                           | _        | _                                                                    | 0                    | Δ                              | Δ             | Δ |

| 0x4001_9000 | Built-in IO-3 (APB): 32 KB                          | · · · ·                            | _        | _                                                                    | 0                    | 0                              | 0             | Δ |

| 0x4002_1000 | Unused area                                         |                                    | _        | -                                                                    | Δ                    | Δ                              | Δ             | Δ |

| 0x6000_0000 | Unused area                                         | External NOR-Flash<br>area (16 MB) | -        | -                                                                    | Δ                    | Δ                              | Δ             | Δ |

| 0x6100_0000 | SMCCS1n<br>External: 16 MB                          | External area<br>(16 MB)           | _        | _                                                                    | ο                    | 0                              | 0             | Δ |

| 0x6200_0000 | Unused area                                         |                                    | _        | _                                                                    | Δ                    | Δ                              | Δ             | Δ |

| 0xA000_0000 | Unused area                                         |                                    | _        | -                                                                    | Δ                    | Δ                              | Δ             | Δ |

| 0xE000_0000 | Internal Private Peripheral Bus<br>area             |                                    | -        | _                                                                    | -                    |                                | ∆<br>(Note 1) |   |

| 0xE004_0000 | External Private Peripheral Bus<br>area             |                                    | -        | _                                                                    | -                    |                                | ∆<br>(Note 2) |   |

| 0xE010_0000 | Unused area                                         |                                    | _        | -                                                                    | Δ                    | Δ                              | Δ             | Δ |

0xFFFF\_FFF

Note 1)Internal Private Peripheral Bus (PPB) access area Note 2)External Private Peripheral Bus (PPB) access area

Figure 3.3.2 Memory map

(details of external areas, and connection relationship between the Bus Master and the Slave)

| Address     | Bus                        | IP                | Register Access Size |

|-------------|----------------------------|-------------------|----------------------|

| 0x4000_0000 |                            | DMAC              | 8,16,32bit           |

| 0x4000_1000 |                            | eDRAMC            | 8,16,32bit           |

| 0x4000_2000 | Built-in IO-0 (AHB): 20 KB | USB(EHCI)         | 8,16,32bit           |

| 0x4000_3000 |                            | USB(OHCI)         | 8,16,32bit           |

| 0x4000_4000 |                            | SMC               | 8,16,32bit           |

| 0x4000_5000 |                            | CG&PLL            | 32bit                |

| 0x4000_6000 |                            | WDT               | 32bit                |

| 0x4000_7000 |                            | ADC               | 32bit                |

| 0x4000_8000 |                            | Port A            | 32bit                |

| 0x4000_9000 |                            | Port B            | 32bit                |

| 0x4000_A000 | 1                          | Port C            | 32bit                |

| 0x4000_B000 |                            | Port D            | 32bit                |

| 0x4000_C000 |                            | Port E            | 32bit                |

| 0x4000_D000 | Built-in IO-1 (APB): 64 KB | Port F            | 32bit                |

| 0x4000_E000 |                            | Port G            | 32bit                |

| 0x4000 F000 |                            | Timer01/PWM0      | 32bit                |

|             |                            | TImer23/PWM2      | 32bit                |

| 0x4001_1000 |                            | Timer45/PWM4      | 32bit                |

| 0x4001_2000 |                            | Timer67/PWM6      | 32bit                |

| 0x4001_3000 |                            | I2C0              | 32bit                |

| 0x4001_4000 |                            | I2C1              | 32bit                |

| 0x4001_5000 |                            | SDHost(DATA)      | 16bit                |

| 0x4001_6000 |                            | I2S               | 32Bit                |

| 0x4001_7000 | Built-in IO-2 (AHB): 16 KB | reserved          | -                    |

|             |                            | SDHost(registers) | 16bit                |

| 0x4001_9000 |                            | UART0             | 32bit                |

| 0x4001_A000 |                            | UART1             | 32bit                |

| 0x4001_B000 |                            | UART2             | 32bit                |

| 0x4001_C000 | Puilt in IO 2 (ADD): 22 KD | UART3             | 32bit                |

| 0x4001_D000 | Built-in IO-3 (APB): 32 KB | SSP0              | 32bit                |

| 0x4001_E000 | 1                          | SSP1              | 32bit                |

| 0x4001_F000 | 1                          | SSP2              | 32bit                |

| 0x4002_0000 |                            | SSP3              | 32bit                |

The following list shows the relationship between the IPs and the register access size:

Note) Access to the SDHost Controller is fixed to 16-bit access including the registers

Figure 3.3.3 Memory map (details of peripherals)

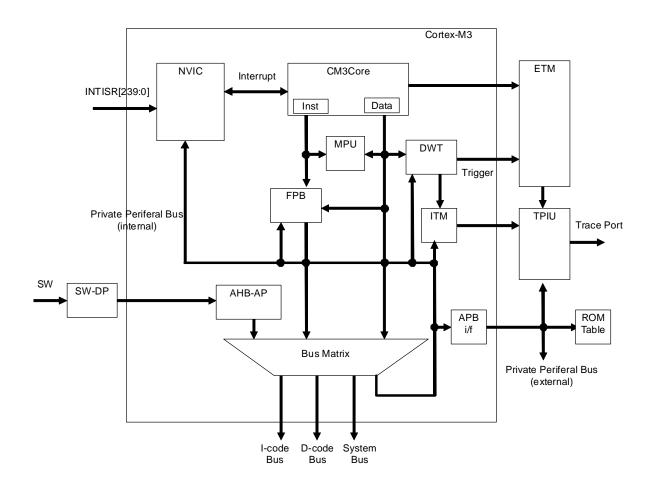

# 3.4 CPU

The TMPM320C1D contains the 32-bit RISC processor core (Cortex-M3 core) made by ARM. This section describes the overview of the Cortex-M3 and the configuration information in the TMPM320C1D. For more information on the Cortex-M3, please refer to the documents published by ARM.

http://www.arm.com/

The following shows the diagram of the Cortex-M3 core:

Figure 3.4.1 Schematic diagram of Cortex-M3 core

#### 3.4.1 Core Configuration

The following shows the Cortex-M3 core configuration selected in the TMPM320C1D:

| Configuration                     | Description                         |

|-----------------------------------|-------------------------------------|

| Number of interrupts              | 29 channels                         |

| Interrupt priority level (Note 1) | 4 bits (16 levels)                  |

| MPU<br>(Memory Protection Unit)   | Installed                           |

| SW / SWJ-DP                       | SW-DP only<br>(SWD connection only) |

| ETM<br>(Embedded Trace Macrocell) | Installed                           |

| Endian                            | Little endian                       |

(Note 1) Refer to pages 102/384, Cortex-M3 Technical Reference Manual.

#### 3.4.2 Exceptions

The following list shows the Cortex-M3 exception types:

INTWDT and the subsequent areas are the vector areas unique to the TMPM320C1D. For more information, refer to section 3.7, "Interrupts."

| Exception     | Address         | Remarks                       |

|---------------|-----------------|-------------------------------|

| Top of Stack  | 0x0000000       | Beginning of a stack          |

| Reset         | 0x0000004       | Reset                         |

| reserved      | 0x0000008       | -                             |

| Hard Fault    | 0x000000C       | Hard fault                    |

| MPU Fault     | 0x0000010       | Memory management             |

| Bus Fault     | 0x0000014       | Bus fault                     |

| Usage Fault   | 0x0000018       | Usage fault                   |

| reserved      | 0x0000001C      | -                             |

| reserved      | 0x0000020       | -                             |

| reserved      | 0x00000024      | -                             |

| reserved      | 0x0000028       | -                             |

| SVCall        | 0x0000002C      | Supervisor call               |

| Debug Monitor | 0x0000030       | Debug monitor                 |

| PendSV        | 0x0000038       | Software pending request      |

| SysTick       | 0x000003C       | SysTick interrupt             |

| INTWDT<br>:   | 0x00000040<br>: | Watchdog timer interrupt<br>: |

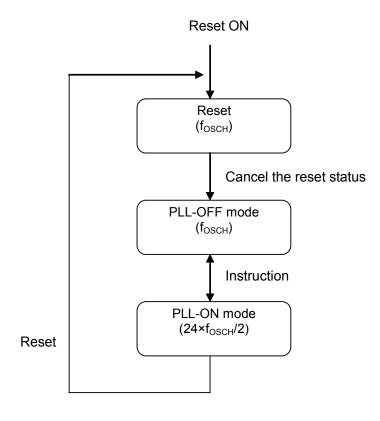

## 3.5 Clock Controller

## 3.5.1 Overview

This block is a circuit that controls the clock for the overall TMPM320C1D. It has the following features:

- a. Writing to registers inside the clock controller is prohibited.

- b. Supplies and stops a clock on an IP basis.

- c. Selects and sets a SYSTICK\_CLK clock (HCLK/2, HCLK/4).

- d. Selects and sets a TRACECLKIN clock (HCLK/2, HCLK/4, HCLK/8, HCLK/16).

- e. Selects and sets an SMC clock (external memory controller) (HCLK/2, HCLK/4).

Figure 3.5-1 Clock mode status transition

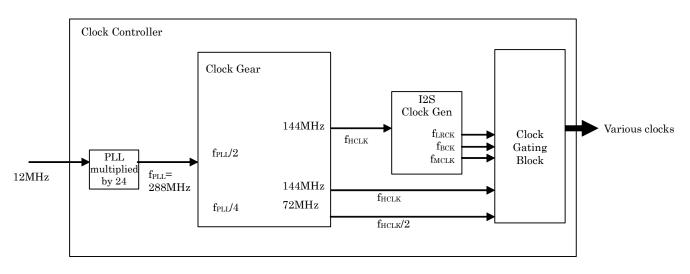

## 3.5.2 Overview of a Block

The following shows the block diagram of the clock controller:

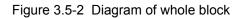

Figure 3.5-3 PLL and clock gear configuration

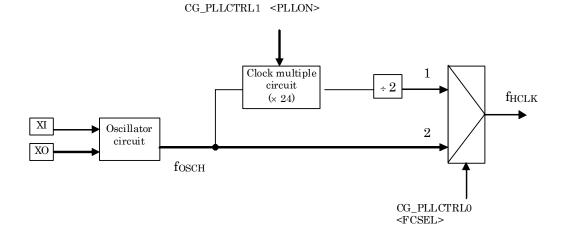

Figure 3.5-4 Clock supply configuration for each block

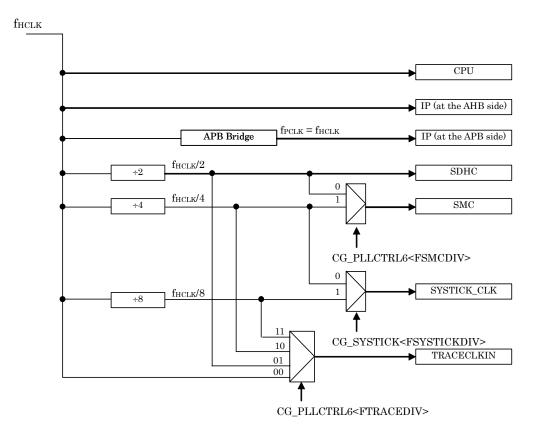

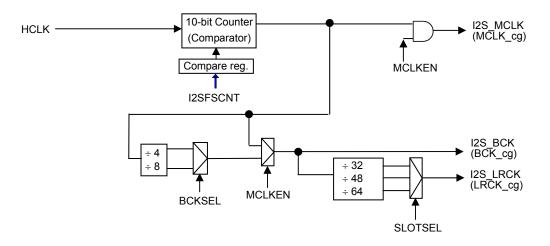

Figure 3.5-5 I2S clock generator

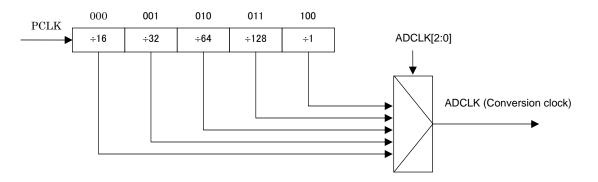

The clock frequency input from the X1 and X2 pins via the USB PHY block shown in Figure 3.5-3 is defined as fOSCH, and the clock for peripheral IP connecting the clock selected by CG\_PLLCTRL0 <FCSEL> to the CPU and AHB bus is defined as fHCLK. In addition, the peripheral IP to be connected to the APB bus is defined as fPCLK (This has the same frequency as fHCLK but a different name).

Furthermore, a clock obtained by dividing fHCLK by 2 or fHCLK by 4 can be selected for the SMC (external memory controller). For the reference clock for SYSTICK, a clock obtained by dividing fHCLK by 4 or fHCLK by 8 can be selected.

The clock supply to TRACECLKIN when using the tracing function (TPIU) can also be selected from the following four types: fHCLK without frequency division, fHCLK divided by 2, fHCLK divided by 4, or fHCLK divided by 8.

The TRACECLK output frequency is driven at the rising edge of TRACECLKIN and thus the output frequency from the pin is as follows: TRACECLK = TRACECLKIN divided by 2.

(Note) For more information on TRACECLKIN and SYSTICK, please refer to the documents published by ARM.

# 3.5.3 Register Functions

The built-in registers and their functions are listed below.

base address = 0x4000\_5000

| Register<br>Name | Address<br>(base+) | Description                              |

|------------------|--------------------|------------------------------------------|

| CG PLLCTRL0      | 0x0000             | CG PLL Control Register 0                |

| CG PLLCTRL1      | 0x0000             | CG PLL Control Register 1                |

|                  | 0x0004             | reserved                                 |

|                  |                    |                                          |

| CG_PLLCTRL3      | 0x000C             | CG PLL Control Register 3                |

| CG_PLLCTRL4      | 0x0010             | CG PLL Control Register 4                |

| CG_PLLCTRL5      | 0x0014             | CG PLL Control Register 5                |

| CG_PLLCTRL6      | 0x0018             | CG PLL Control Register 6                |

| CG_CLKDIS        | 0x0020             | CG Clock Disable Register                |

| CG_FSCTRL        | 0x0100             | CG FS Control Register                   |

| CG_I2SFSCTRL     | 0x0104             | CG I2S FS Control Register               |

| -                | 0x0108             | reserved                                 |

| CG_BSIFCTRL      | 0x0200             | CG Bit Stream Interface Control Register |

| CG_DMASELR       | 0x0300             | DMA Request Select Control Register      |

| _                | 0x0304             | reserved                                 |

| _                | 0x0308             | reserved                                 |

| -                | 0x030C             | reserved                                 |

| CG_SYSTICK       | 0x0310             | SYSTICK Control Register                 |

1. CG\_PLLCTRL0 (CG PLL Control Register 0)

|        |        |      |           | Address = (0x4000_5000) + 0x0000  |

|--------|--------|------|-----------|-----------------------------------|

| D'4    | Bit    | т    | Reset     | Description                       |

| Bit    | Symbol | Туре | Value     | Description                       |

| [31:1] | -      | -    | undefined | Read undefined.                   |

|        |        |      |           | Write as zero.                    |

| [0]    | FCSEL  | R/W  | 0y0       | Selection to use PLL output clock |

|        |        |      |           | 0y0: Selects PLL input clock      |

|        |        |      |           | 0y1: Selects PLL output clock     |

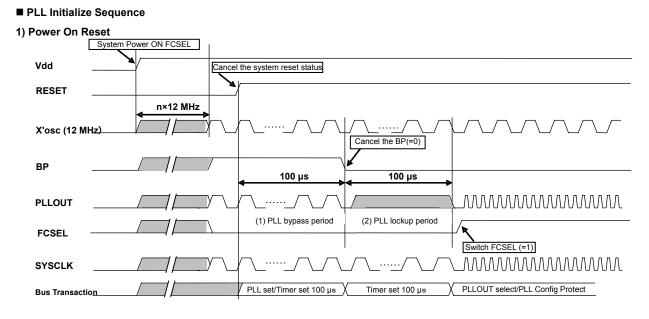

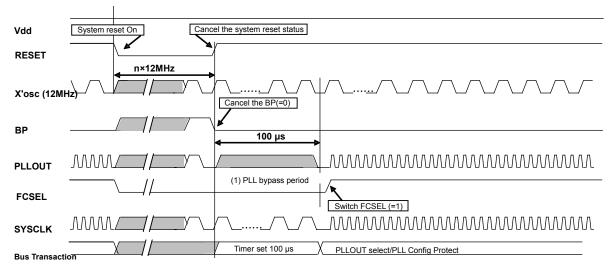

#### [Explanation]

a. <FCSEL>

Selects whether to use PLL output clock or not. By default after reset operation, PLL input clock is selected. After PLL initialize sequence is complete (be sure to check that the output becomes stable after the PLL lockup period has passed), select the PLL output clock whenever possible.

(Note) Do not set to "FCSEL=1" before the multiplied PLL output clock is stabilized.

2. CG\_PLLCTRL1 (CG PLL Control Register 1)

|        |               |      |                | Address = (0x4000_5000) + 0x0004                                                                                                                      |

|--------|---------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit<br>Symbol | Туре | Reset<br>Value | Description                                                                                                                                           |

| [31:1] | -             | -    | undefined      | Read undefined.<br>Write as zero.                                                                                                                     |

| [0]    | PLLON         | R/W  | ОуО            | Signal for controlling PLL operation<br>(Inverts and inputs the setting value to<br>the BP pin)<br>0y0: OFF (bypass mode)<br>0y1: ON (operation mode) |

[Explanation]

a. <PLLON>

By default after reset operation, the PLL bypass mode is set. During the PLL initialize sequence, switch the operation mode to "PLLON=1" if possible after the system reset is cancelled and the bypass period (100  $\mu$ sec) has passed.

3. CG\_PLLCTRL3 (CG PLL Control Register 3)

|        |         |          |           | Address = (0x4000_5000) + 0x000C  |

|--------|---------|----------|-----------|-----------------------------------|

| Dit    | Bit     | <b>T</b> | Reset     | Description                       |

| Bit    | Symbol  | Туре     | Value     | Description                       |

| [31:1] | -       | _        | undefined | Read undefined.                   |

|        |         |          |           | Write as zero.                    |

| [0]    | PROTECT | R/W      | 0у0       | PLL control register protect flag |

|        |         |          |           | 0y0: Protect OFF                  |

|        |         |          |           | 0y1: Protect ON                   |

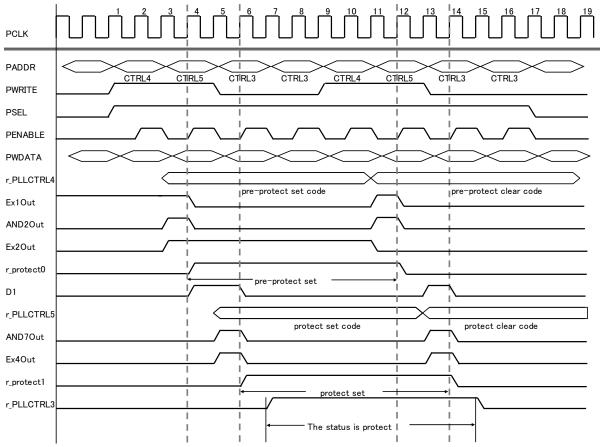

#### [Explanation]

b. <PROTECT>

Indicates the access prohibition (protect ON) status for CG\_PLLCTRL0 and CG\_PLLCTRL1, which is set by the protect settings in CG\_PLLCTRL4 and CG\_PLLCTRL5.

By default after reset operation, this indicates Protect OFF.

#### 4. CG\_PLLCTRL4 (CG Control Register 4)

Address = (0x4000\_5000) + 0x0010

| Bit    | Bit<br>Symbol | Туре | Reset<br>Value | Description                                                                                                             |

|--------|---------------|------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| [31:0] | ProtectCode0  | R/W  | 0x0000000      | CG_PLLCTRL0/1 protect code 0<br>Any value: Protect execution condition<br>0x0ACCE550: protect cancellation<br>condition |

#### [Explanation]

a. <ProtectCode0>

Sets the protect execution condition for inside of the control circuit, which is used to prohibit register access to CG\_PLLCTRL0 and CG\_PLLCTRL1. By default after reset operation, this sets the protect cancellation condition. Write any value in this register to set the protect execution condition. To actually execute the protect operation, write any value other than the cancellation condition in CG\_PLLCRTL5 sequentially after the value written in that register. To cancel the protect operation, write the cancellation condition of "0x0ACCE550" in that register, and sequentially write the cancellation code in CG\_PLLCTRL5.

5. CG\_PLLCTRL5 (CG Control Register 5)

Address = (0x4000\_5000) + 0x0014

| Bit    | Bit<br>Symbol | Туре | Reset<br>Value | Description                                                                                                                  |

|--------|---------------|------|----------------|------------------------------------------------------------------------------------------------------------------------------|

| [31:0] | ProtectCode1  | R/W  | 0x0000000      | CG_PLLCTRL0/1 protect code 1<br>Any value: Executes the protect<br>operation<br>0x1ACCE551: Cancels the protect<br>operation |

#### [Explanation]

a. < ProtectCode1>

Executes the protect operation in the control circuit to prohibit the register access to CG\_PLLCTRL0 and CG\_PLLCTRL1. By default after reset operation, this sets the protect cancellation condition. To execute the protect operation, write any value in this register. To actually execute the protect operation, any value other than the cancellation condition must be written in CG\_PLLCTRL4 before access to this register. To cancel the protect operation, write the cancellation condition in CG\_PLLCTRL4, and sequentially write the cancellation code of "0x1ACCE551."

#### 6. CG\_PLLCTRL6 (CG PLL Control Register 6)

|         |               |      |                | Address = (0x4000_5000) + 0x0018                                                                                                                                                                                                                                                        |

|---------|---------------|------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Bit<br>Symbol | Туре | Reset<br>Value | Description                                                                                                                                                                                                                                                                             |

| [31:19] | -             | -    | undefined      | Read undefined.<br>Write as zero.                                                                                                                                                                                                                                                       |

| [18]    | TRACECLKINEN  | R/W  | 0у0            | TRACECLKIN output enable<br>0y0: Output disabled<br>0y1: Output enabled                                                                                                                                                                                                                 |

| [17:16] | FTRACEDIV     | R/W  | 0у00           | TRACECLKIN clock frequency<br>division select<br>0y00: No division (fHCLK/2)<br>0y01: Divided by 2 (fHCLK/4)<br>0y10: Divided by 4 (fHCLK/8)<br>0y11: Divided by 8 (fHCLK/16)<br>Note: The frequencies shown in the<br>parentheses are the frequencies<br>output from the TRACECLK pin. |

| [15:6]  | -             | -    | undefined      | Read undefined.<br>Write as zero.                                                                                                                                                                                                                                                       |

| [5]     | FSMCDIV       | R/W  | 0y0            | Selects the number of divisions for the<br>SMCCLK clock<br>0y0: Divides by 2<br>0y1: Divides by 4                                                                                                                                                                                       |

| [4:0]   | -             | -    | undefined      | Read undefined.<br>Write as zero.                                                                                                                                                                                                                                                       |

#### [Explanation]

a. <TRACECLKINEN>

Controls the output of the TRACECLKIN output clock supplied for debug use. After reset, output is disabled by default.

#### b. <FTRACEDIV>

Selects the frequency-division circuit for the TRACECLK output clock supplied for debug use.

After reset, "No division" is selected by default. For example, if fHCLK operates at 144 MHz in this setting, the TRACECLK output clock is output at 72 MHz.

#### c. <FSMCDIV>

Selects a divider circuit for the SCM\_CLK output clock to be supplied to the SMC. By default after reset operation, "Divides by 2" is selected.

7. CG\_CLKDIS (CG Clock Disable Register)

|         | Bit       |      | Reset     | Address = (0x4000_5000) + 0x0020                                                             |

|---------|-----------|------|-----------|----------------------------------------------------------------------------------------------|

| Bit     | Symbol    | Туре | Value     | Description                                                                                  |

| [31:20] | -         | -    | undefined | Read undefined.                                                                              |

|         |           |      |           | Write as zero.                                                                               |

| [19]    | DMACHDIS  | R/W  | 0у0       | Disables the bus clock HCLK output for the DMAC                                              |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [18]    | USBHDIS   | R/W  | 0у0       | Disables the bus clock HCLK output for the USB                                               |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [17]    | Reserved  | R/W  | 0y0       | Read undefined.                                                                              |

|         |           |      |           | Write as one.                                                                                |

| [16]    | SDHCHDIS  | R/W  | 0y0       | Disables the bus clock HCLK output<br>for the SDHC                                           |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [15]    | I2SHDIS   | R/W  | 0у0       | Disables the bus clock HCLK output for I2S                                                   |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [14]    | VZOPDIS   | R/W  | ОуО       | Disables the bus clock PCLK output<br>for the clock generator dedicated for<br>the BSIF mode |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [13]    | TMR67PDIS | R/W  | 0у0       | Disables the bus clock PCLK output for the TimerCH6/CH7                                      |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [12]    | TMR45PDIS | R/W  | 0у0       | Disables the bus clock PCLK output<br>for the TimerCH4/CH5                                   |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [11]    | TMR23PDIS | R/W  | 0у0       | Disables the bus clock PCLK output<br>for the TimerCH2/CH3                                   |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [10]    | TMR01PDIS | R/W  | 0у0       | Disables the bus clock PCLK output<br>for the TimerCH0/CH1                                   |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [9]     | I2C1PDIS  | R/W  | 0у0       | Disables the bus clock PCLK output<br>for the I2C CH1                                        |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

| [8]     | I2C0PDIS  | R/W  | 0у0       | Disables the bus clock PCLK output<br>for the I2C CH0                                        |

|         |           |      |           | 0y0: Enables the output                                                                      |

|         |           |      |           | 0y1: Disables the output                                                                     |

# **Interim Specifications**

| Bit | Bit<br>Symbol | Туре | Reset<br>Value | Description                                                                                                  |

|-----|---------------|------|----------------|--------------------------------------------------------------------------------------------------------------|

| [7] | SSP3PDIS      | R/W  | 0у0            | Disables the bus clock PCLK output<br>for the SSPCH3<br>0y0: Enables the output<br>0y1: Disables the output  |

| [6] | SSP2PDIS      | R/W  | 0у0            | Disables the bus clock PCLK output<br>for the SSPCH2<br>0y0: Enables the output<br>0y1: Disables the output  |

| [5] | SSP1PDIS      | R/W  | 0у0            | Disables the bus clock PCLK output<br>for the SSPCH1<br>0y0: Enables the output<br>0y1: Disables the output  |

| [4] | SSPOPDIS      | R/W  | 0у0            | Disables the bus clock PCLK output<br>for the SSPCH0<br>0y0: Enables the output<br>0y1: Disables the output  |

| [3] | UART3PDIS     | R/W  | 0у0            | Disables the bus clock PCLK output<br>for the UARTCH3<br>0y0: Enables the output<br>0y1: Disables the output |

| [2] | UART2PDIS     | R/W  | 0у0            | Disables the bus clock PCLK output<br>for the UARTCH2<br>0y0: Enables the output<br>0y1: Disables the output |

| [1] | UART1PDIS     | R/W  | 0у0            | Disables the bus clock PCLK output<br>for the UARTCH1<br>0y0: Enables the output<br>0y1: Disables the output |

| [0] | UARTOPDIS     | R/W  | ОуО            | Disables the bus clock PCLK output<br>for the UARTCH0<br>0y0: Enables the output<br>0y1: Disables the output |

#### [Explanation]

#### a. <DMACHDIS>

Controls the HCLK output, which is a bus clock for the DMAC. By default after reset operation, the output is enabled.

b. <USBHDIS>

Controls the HCLK output, which is a bus clock for the USB. By default after reset operation, the output is enabled.

c. <SDHCHDIS>

Controls the HCLK output, which is a bus clock for the SDHC. By default after reset operation, the output is enabled.

d. <I2SHDIS>

Controls the HCLK output, which is a bus clock for I2S. By default after reset operation, the output is enabled.

#### e. <VZOPDIS>

Controls the PCLK output, which is a bus clock for the VZO. By default after reset operation, the output is enabled.

#### f. <TMR67PDIS>

Controls the PCLK output, which is a bus clock for the Timer CH6/CH7. By default after reset operation, the output is enabled.

#### g. <TMR45PDIS>

Controls the PCLK output, which is a bus clock for the Timer CH4/CH5. By default after reset operation, the output is enabled.

#### h. <TMR23PDIS>

Controls the PCLK output, which is a bus clock for the Timer CH2/CH3. By default after reset operation, the output is enabled.

#### i. <TMR01PDIS>

Controls the PCLK output, which is a bus clock for the Timer CH0/CH1. By default after reset operation, the output is enabled.

#### j. <I2C1PDIS>

Controls the PCLK output, which is a bus clock for the I2C CH1. By default after reset operation, the output is enabled.

#### k. <I2C0PDIS>

Controls the PCLK output, which is a bus clock for the I2C CH0. By default after reset operation, the output is enabled.

#### l. <SSP3PDIS>

Controls the PCLK output, which is a bus clock for the SSP CH3. By default after reset operation, the output is enabled.

#### m. <SSP2PDIS>

Controls the PCLK output, which is a bus clock for the SSP CH2. By default after reset operation, the output is enabled.

#### n. <SSP1PDIS>

Controls the PCLK output, which is a bus clock for the SSP CH1. By default after reset operation, the output is enabled.

#### o. <SSP0PDIS>

Controls the PCLK output, which is a bus clock for the SSP CH0. By default after reset operation, the output is enabled.

#### p. <UART3PDIS>

Controls the PCLK output, which is a bus clock for the UART CH3. By default after reset operation, the output is enabled.

#### q. <UART2PDIS>

Controls the PCLK output, which is a bus clock for the UART CH2. By default after reset operation, the output is enabled.

#### r. <UART1PDIS>

Controls the PCLK output, which is a bus clock for the UART CH1. By default after reset operation, the output is enabled.

#### s. <UARTOPDIS>

Controls the PCLK output, which is a bus clock for the UART CH0. By default after reset operation, the output is enabled.

#### (Note 1)

The bus clock for each IP can be stopped (output can be disabled) by this register setting without conditions if the reset operation has just been cancelled and no request and interrupt occurs to the IP to be stopped. However, if a request or interrupt occurs in the normal operation, all of those factors must be cleared before stopping the clock (disabling the output). After the clock is stopped, any register settings in the stopped IP that have already been used will be held.

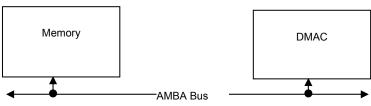

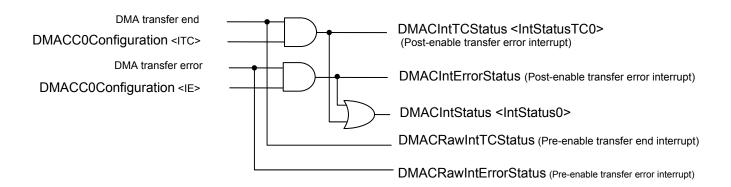

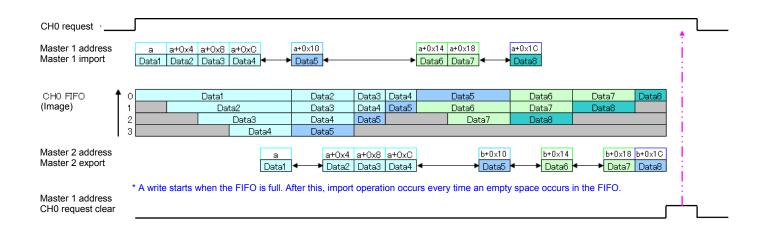

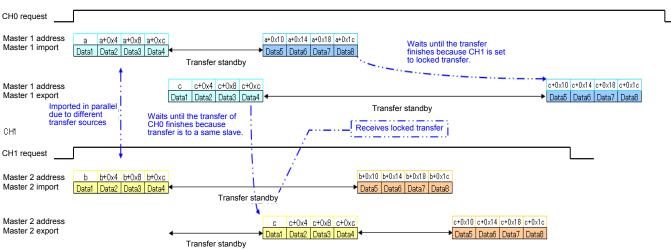

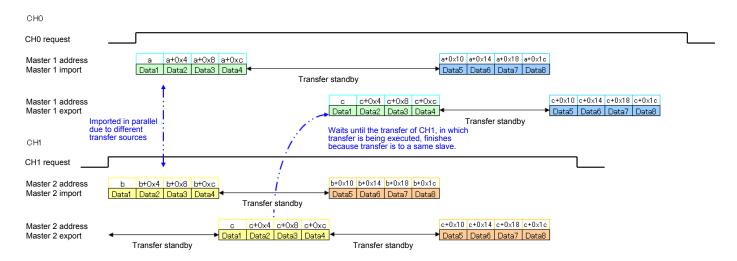

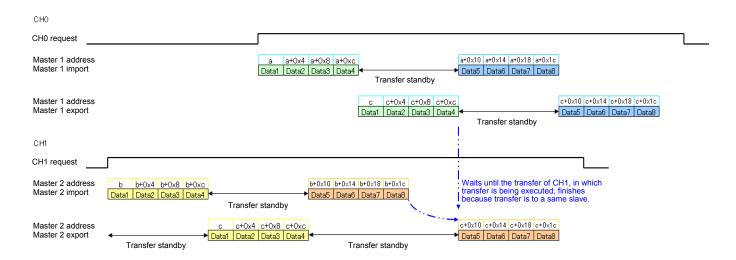

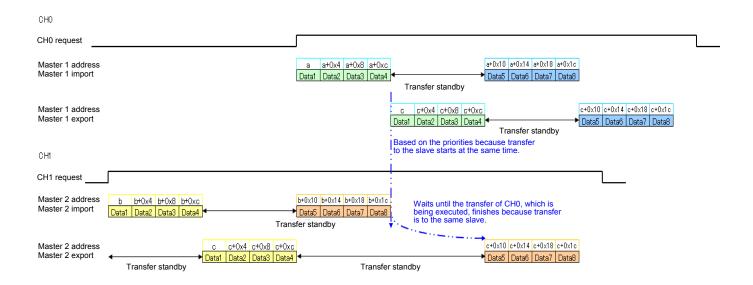

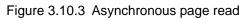

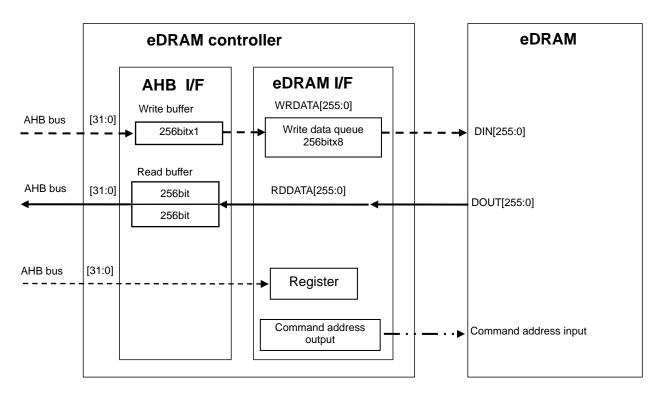

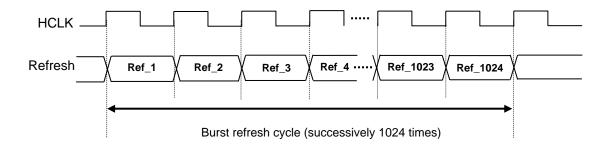

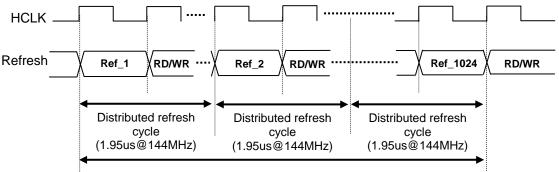

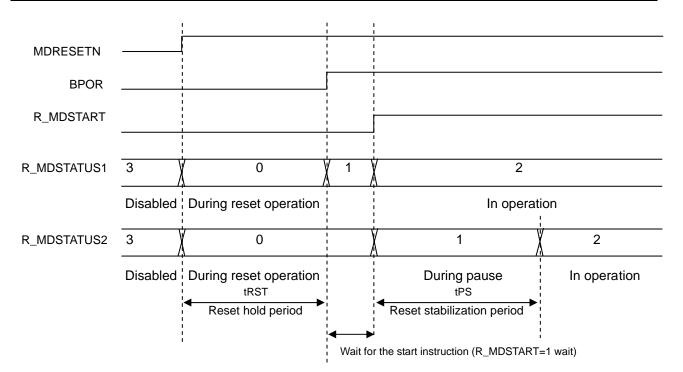

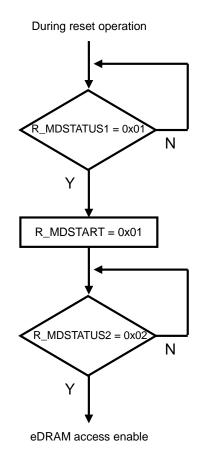

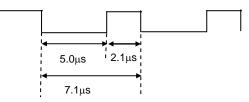

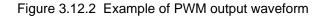

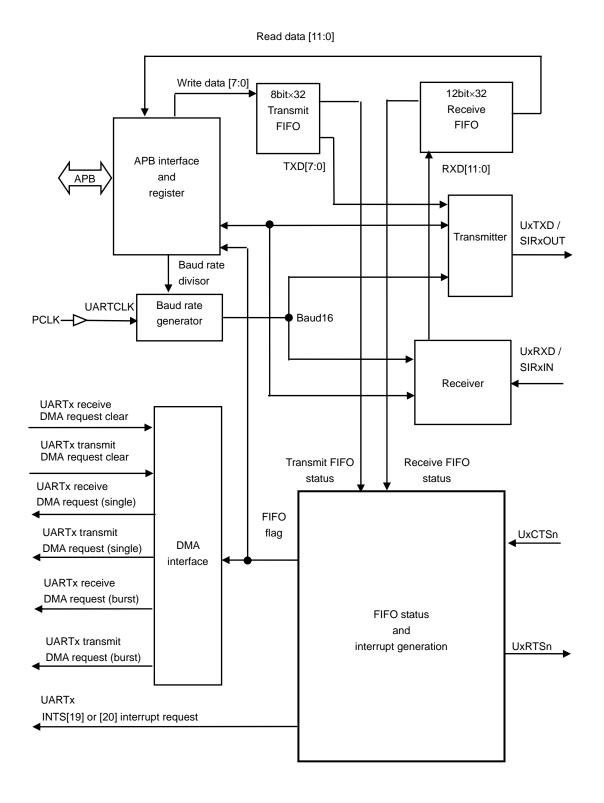

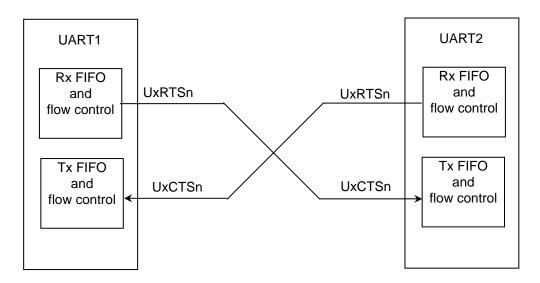

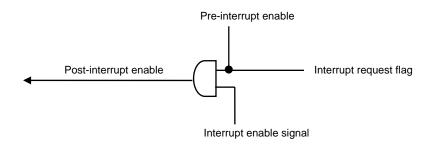

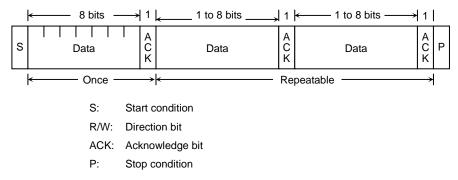

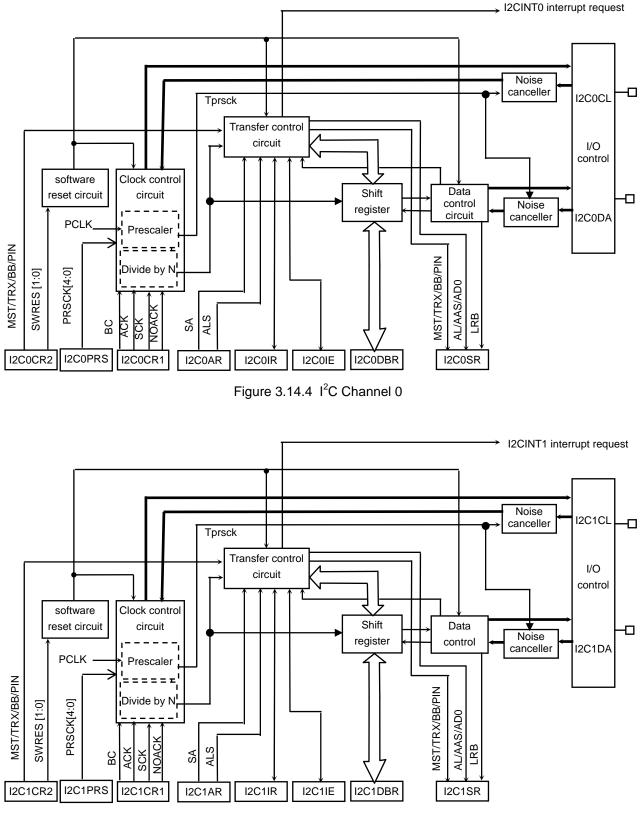

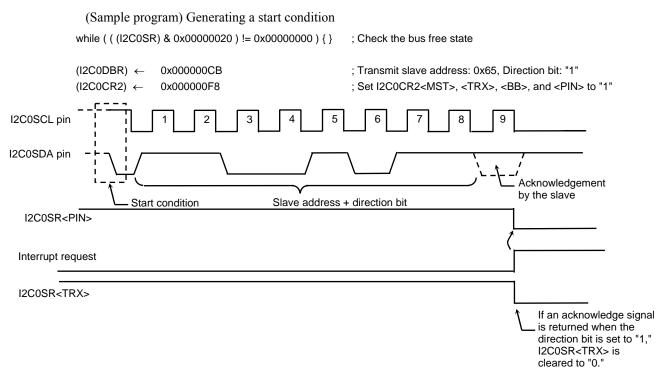

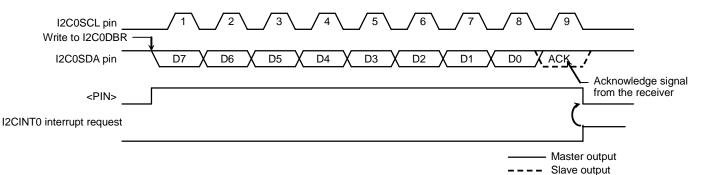

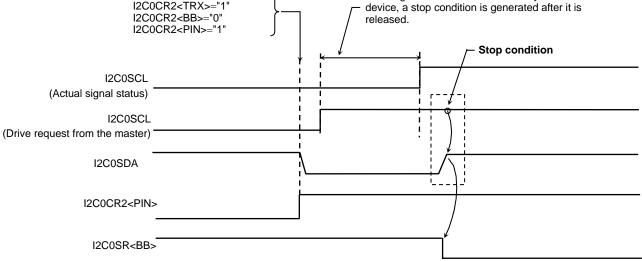

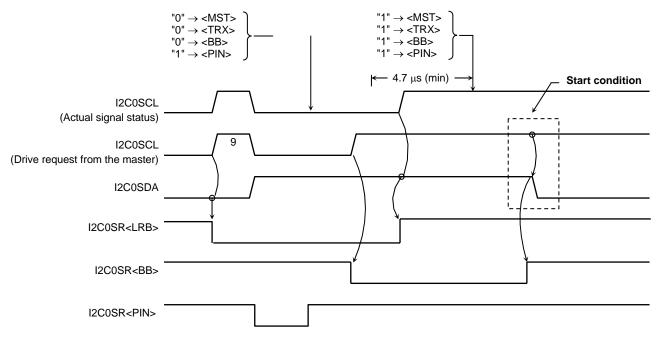

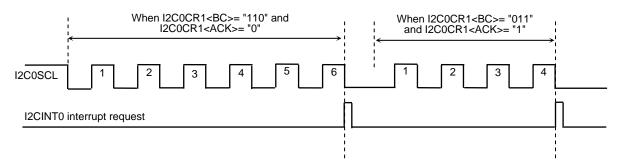

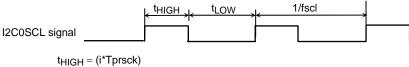

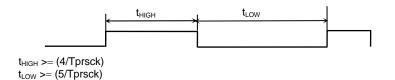

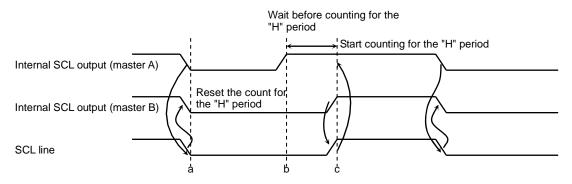

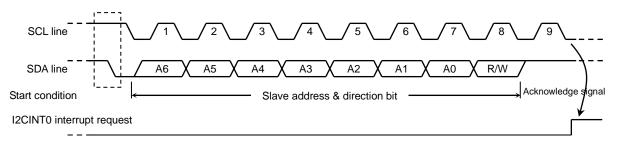

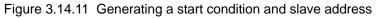

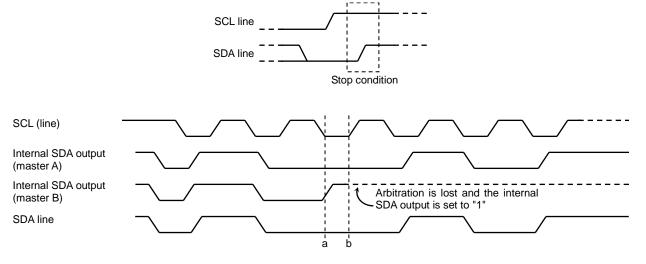

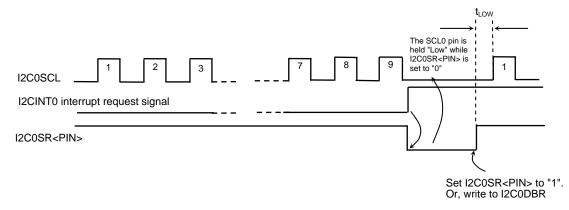

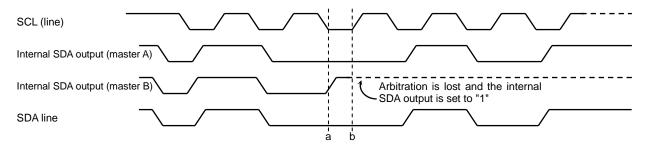

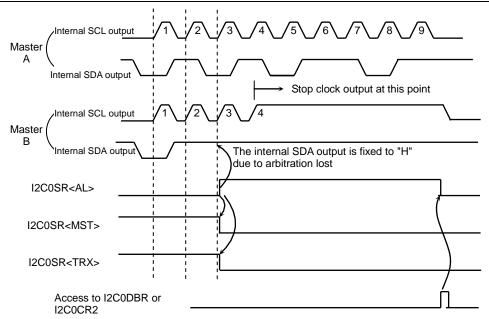

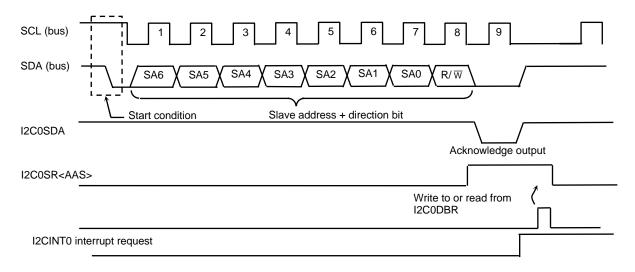

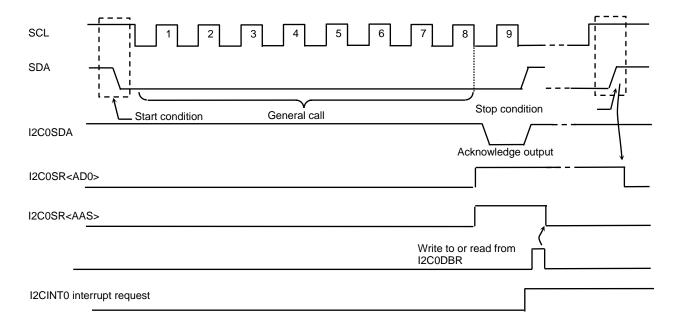

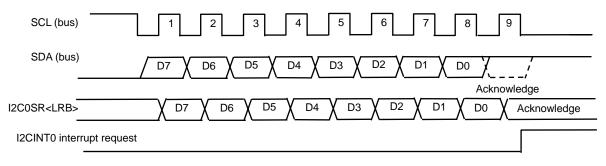

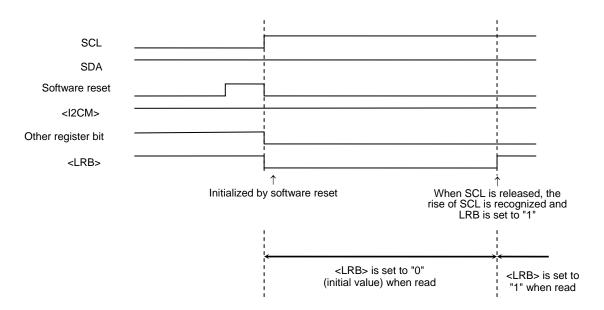

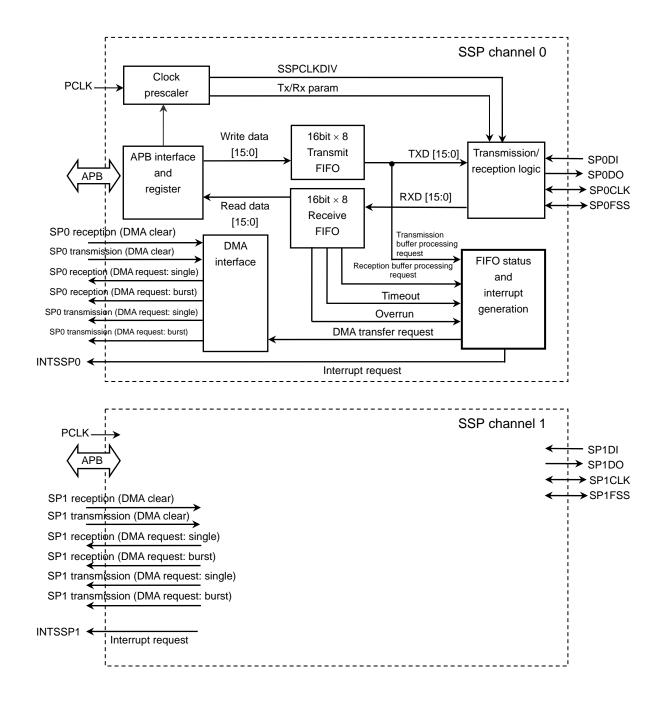

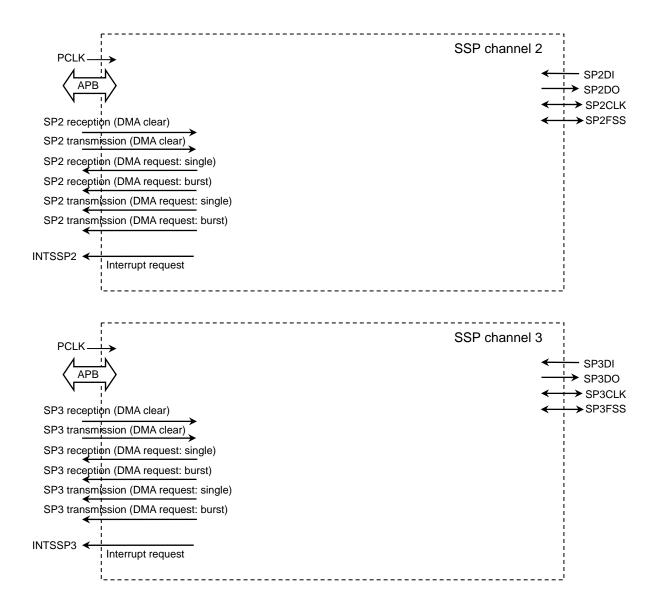

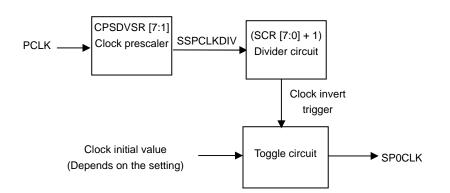

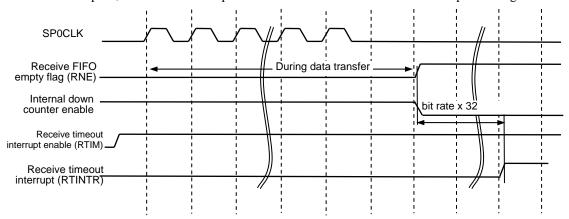

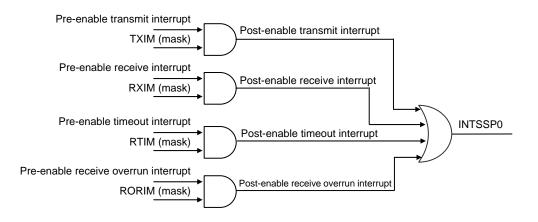

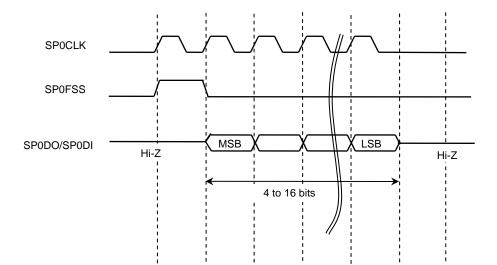

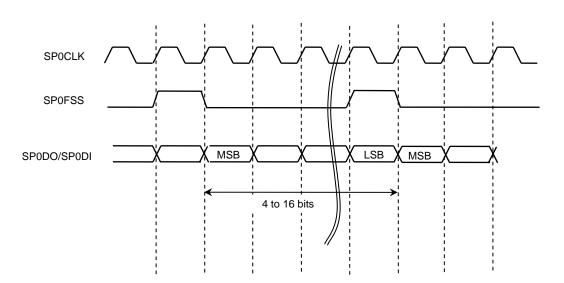

#### (Note 2)