# TOSHIBA

# 32-bit TX System RISC TX03 Series

TMPM322F10FG

# Rev.1.03 17<sup>th</sup>/Dec/2010

# TOSHIBA CORPORATION

Semiconductor Company

Modification history

| Rev  | Date     | Page | Item    |

|------|----------|------|---------|

| 1.03 | 10.12.17 | -    | Release |

ARM, ARM Powered, AMBA, ADK, ARM9TDMI, TDMI, PrimeCell, RealView, Thumb, Cortex, Coresight, ARM9, ARM926EJ-S, Embedded Trace Macrocell, ETM, AHB, APB, and KEIL are registered trademarks or trademarks of ARM Limited in the EU and other countries.

# TX03 Series 32-bit RISC Microprocessor TMPM322F10FG

# 1. Overview and Features

The TX03 Series is comprised of 32-bit RISC microprocessors containing an ARM Cortex<sup>™</sup>-M3 processor core.

The TMPM322F10FG has the following features.

#### 1.1 Features

#### (1) ARMCortex-M3 processor core

- 1) Realizes improved code efficiency through the use of the Thumb-2 instruction set.

- New 16-bit Thumb instructions for improved program flow

- New 32-bit Thumb instructions for improved performance and code density

- 32-bit and 16-bit instruction modes are automatically switched by a compiler.

- 2) Provides both high performance and low power consumption

- High performance

- A 32-bit multiplication ( $32 \times 32 = 32$  bits) can be executed in one clock cycle.

- Division takes 2 to 12 clock cycles.

- Low power consumption

- Optimized design using low power libraries

- Standby function that stops the operation of the processor core

- 3) High-speed interrupt response suitable for real-time control

- Time-consuming instructions can be aborted by interrupts.

- Stack push is automatically handled by hardware.

(2) On-chip program/data memory

| Part Number  | On-chip Flash ROM | On-chip RAM |  |

|--------------|-------------------|-------------|--|

| TMPM322F10FG | 1024 Kbytes       | 64 Kbytes   |  |

- (3) Memory Controller

- Expandable up to 16 Mbytes (Shared program/data area )

- 16-bit width external data bus

- Chip select, wait controller: 4 channel

- (4) DMA controller: 2 channels

- (5) 16-bit timer: 16 channels

- 16-bit interval timer mode

- 16-bit event counter mode

- Input capture function

- 16-bit PPG output (4-phase synchronous output supported)

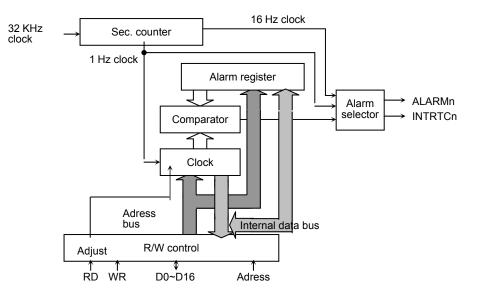

- (6) Real-time clock (RTC): 1 channel

- Clock (hours, minutes and seconds)

- Calendar (month, week, date and leap year)

- Alarm output

- Alarm interrupt

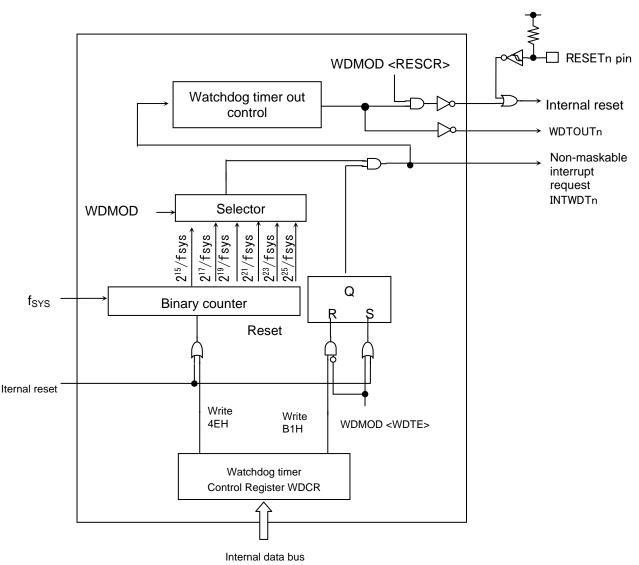

- (7) Watchdog timer: 1 channelWatchdog time-out function

- (8) General-purpose serial interface: 12 channels

- UART or synchronous mode selectable (built-in 4-byte FIFO)

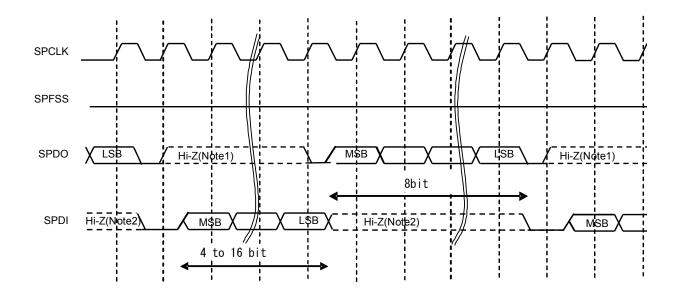

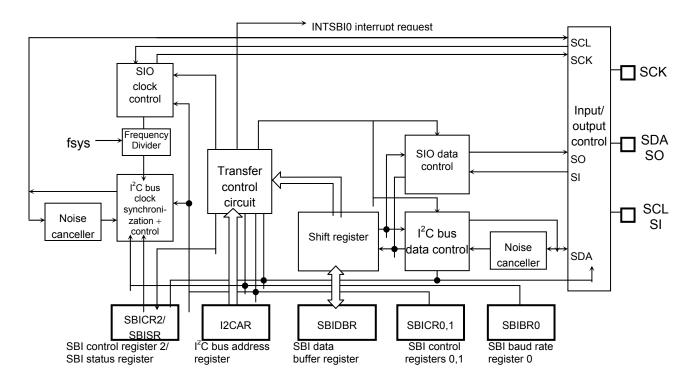

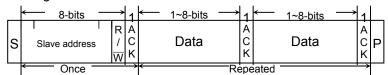

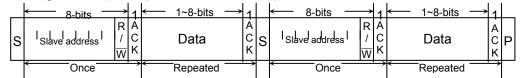

- (9) Serial bus interface: 5 channels

- I<sup>2</sup>C bus or clock synchronous mode selectable

- (10)Synchronous serial bus interface (SSP): 1 channel

- SPI, SSI and Microwire formats supported

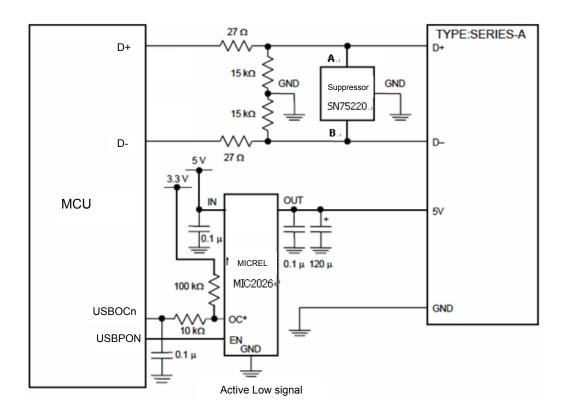

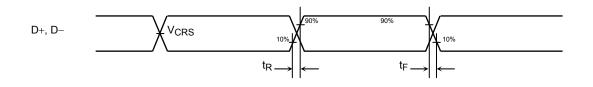

- (11)USB host controller: 1 channel

- Compliant with Universal Serial Bus Specification Rev2.0

- Compliant with OpenHCI for USB Release 1.0a

- 12 Mbps (Full-speed)

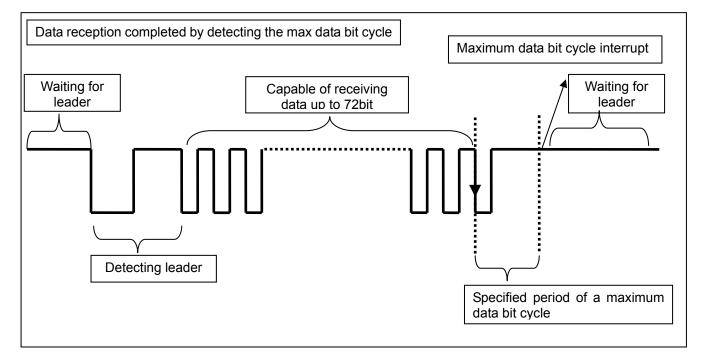

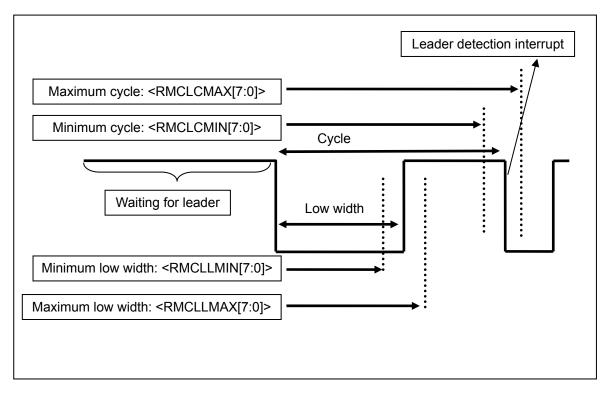

- (12)Remote control signal preprocessor: 2 channels

- Can receive up to 72 bits at a time.

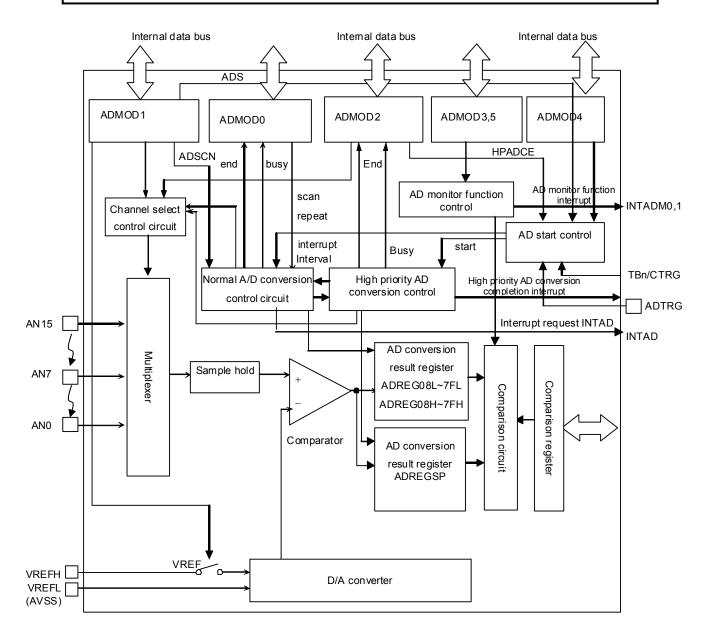

- (13)10-bit AD converter: 16 channels

- Start by an internal timer trigger or external trigger

- Fixed-channel mode and scan mode

- Single mode and repeat mode

- AD monitoring function: 2 channels

(14)Backup module

- Reduces power consumption by shutting off most part of the device except:

- 8-Kbyte backup RAM

- ports (port states before entering BACKUP mode can be retained.)

- remote control signal reception

- real-time clock

- key-on wake-up

(15)Interrupts

- 79 internal sources: Priority can be set in seven levels (excluding the watchdog timer interrupt).

- 15 external sources: Priority can be set in seven levels (including NMI).

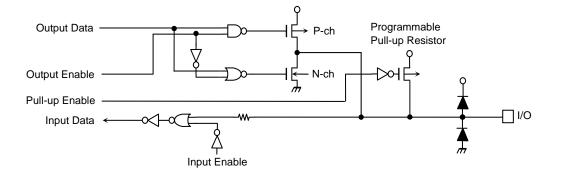

- (16)Input/output ports

- 118 pins: 102 input/output pins + 16 input-only pins

- (17)Standby function

- Standby modes: IDLE2, IDLE1, SLEEP, STOP

- Sub clock operation (32.768 kHz) modes: SLOW

- Backup mode (partial shut-off): BACKUP SLEEP, BACKUP STOP

- (18)Clock generator

- On-chip PLL (4x)

- Clock gearing: The high-frequency clock can be divided by 1, 2, 4 or 8.

- (19)Endian

- Little endian

(20)Maximum operating frequency

- 48 MHz (when using a 12-MHz external resonator)

- (21)Operating voltage range

- 3.0 V to 3.6 V (when operating USBHC and using the internal regulator)

- 2.7 V to 3.6 V (when stopping USBHC and using the internal regulator)

(22) Temperature range

- -40°C to 85°C (operations other than Flash write and erase)

- 0°C to 70°C (Flash write and erase)

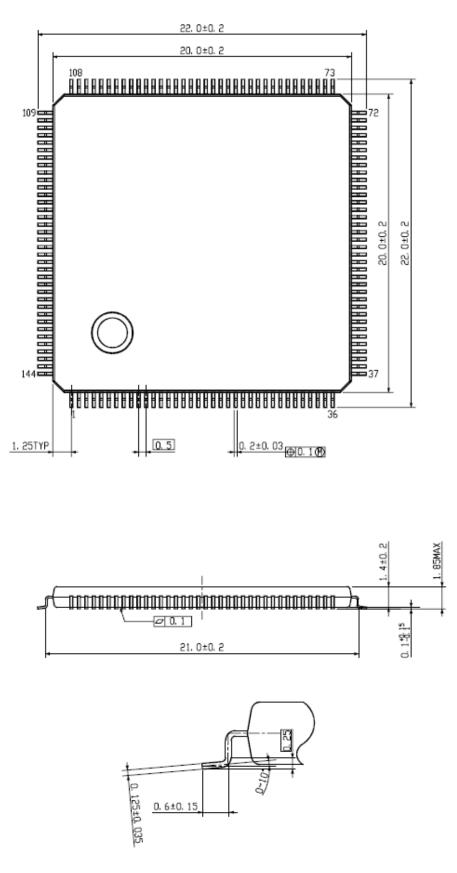

(23) Package

• LQFP144-P-2020-0.50E (20mm × 20mm, 0.50-mm pitch)

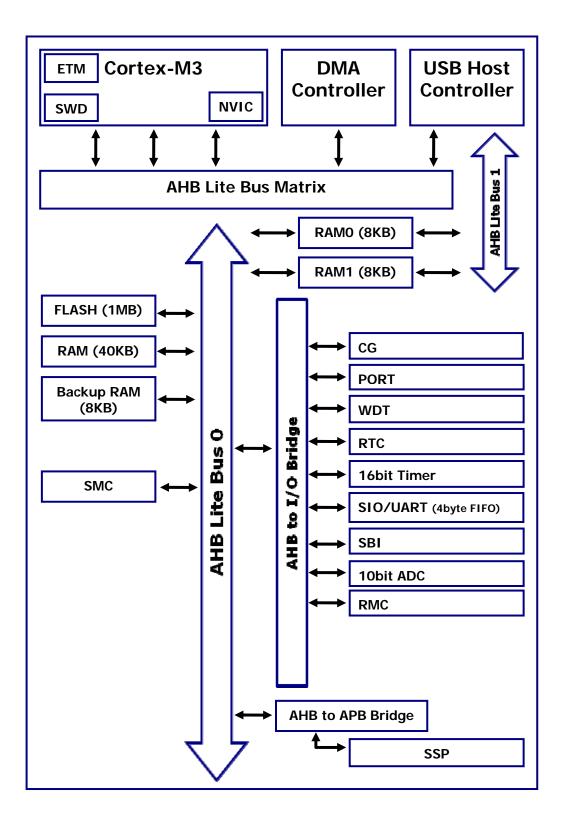

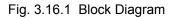

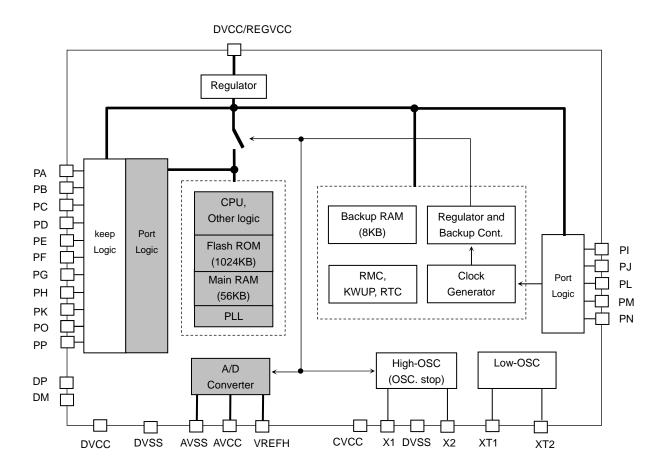

# 1.2 Block Diagram

# 2 Pin Layout and Pin Functions

This chapter describes the pin layout, pin names and pin functions of TMPM322F10FG.

#### 2.1 Pin Layout (Top view)

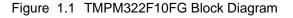

Fig.2.1.1 shows the pin layout of TMPM322F10FG.

Fig.2.1.1 Pin Layout (LQFP144)

#### 2.2 Pin names and Functions

Table 2.2.1 sort the input and output pins of the TMPM322F10FG by pin or port. The table includes alternate pin names and functions for multi-function pins.

#### 2.2.1 Sorted by Pin

| Туре     | # of<br>Pins | Pin Name                        | Input/<br>Output     | Function                                                                                                                       |

|----------|--------------|---------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------|

|          | 1            | PK6<br>AN14                     | 1                    | Input port<br>Analog input                                                                                                     |

| Function | 2            | PK7<br>AN15                     | <br>                 | Input port<br>Analog input                                                                                                     |

|          | 3            | AVSS                            | _                    | A/D converter: GND pin (0V)<br>Tie AVSS to power supply even if the<br>A/D converter is not used.                              |

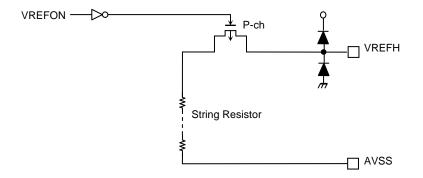

| PS       | 4            | VREFH                           | _                    | Supplying the A/D converter with a reference power supply.<br>Tie VREFH to power supply even if the A/D converter is not used. |

| RESET    | 5            | RESETn                          | 1                    | Reset input pin                                                                                                                |

| Control  | 6            | MODE                            | 1                    | Mode pin: Fix to Low level.                                                                                                    |

|          | 7            | PLO<br>SDA0                     | I/O<br>I/O           | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : data pin<br>-in the SIO mode: data pin                  |

|          |              | TB0OUT                          | 0                    | Timer B output                                                                                                                 |

|          | 8            | PL1<br>SCL0                     | I/O<br>I/O           | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : clock pin<br>-in the SIO mode: data pin                 |

|          |              | TB1OUT                          | 0                    | Timer B output                                                                                                                 |

|          | 9            | PL2<br>SCK0                     | I/O<br>I/O           | I/O port<br>Inputting and outputting a clock<br>if the serial bus interface operates<br>in the SIO mode.                       |

|          |              | TB2OUT                          | 0                    | Timer B output                                                                                                                 |

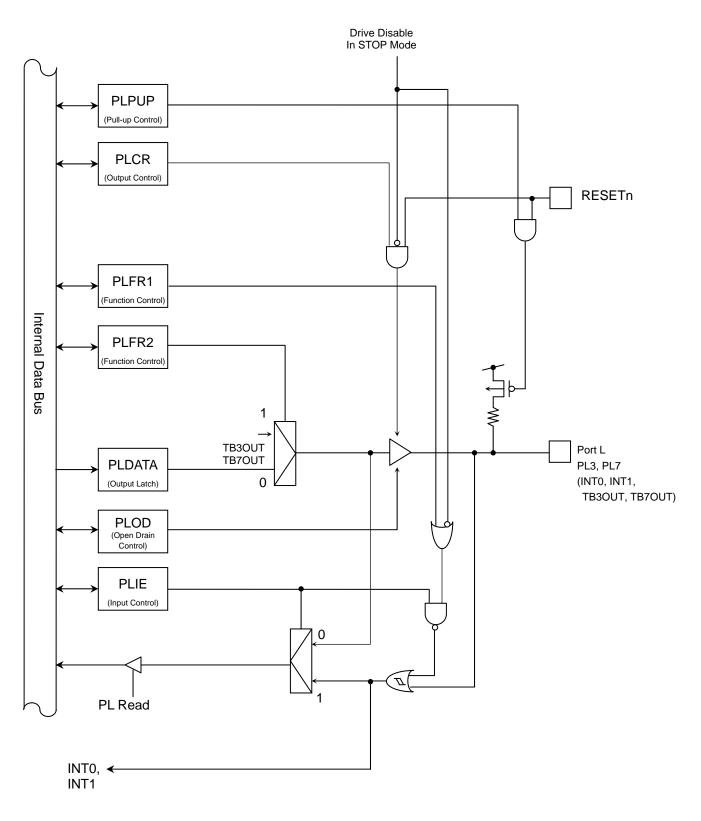

| Function | 10           | PL3<br>INT0<br>TB3OUT           | I/O<br>I<br>O        | I/O port<br>Interrupt request pin<br>Timer B output                                                                            |

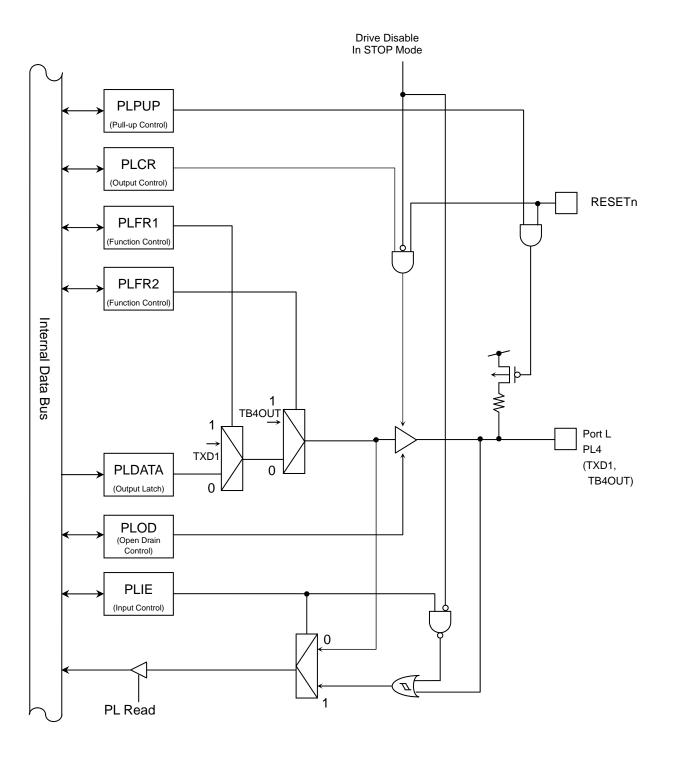

|          | 11           | PL4<br>TXD1<br>TB4OUT           | I/O<br>O<br>O        | I/O port<br>Sending serial data<br>Timer B output                                                                              |

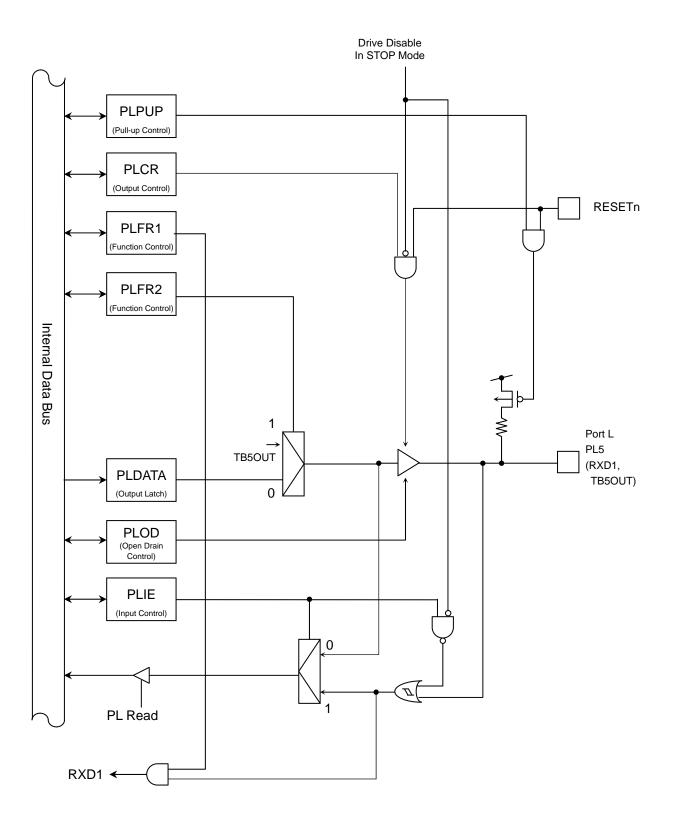

|          | 12           | PL5<br>RXD1<br>TB5OUT           | I/O<br>I<br>O        | I/O port<br>Receiving serial data<br>Timer B output                                                                            |

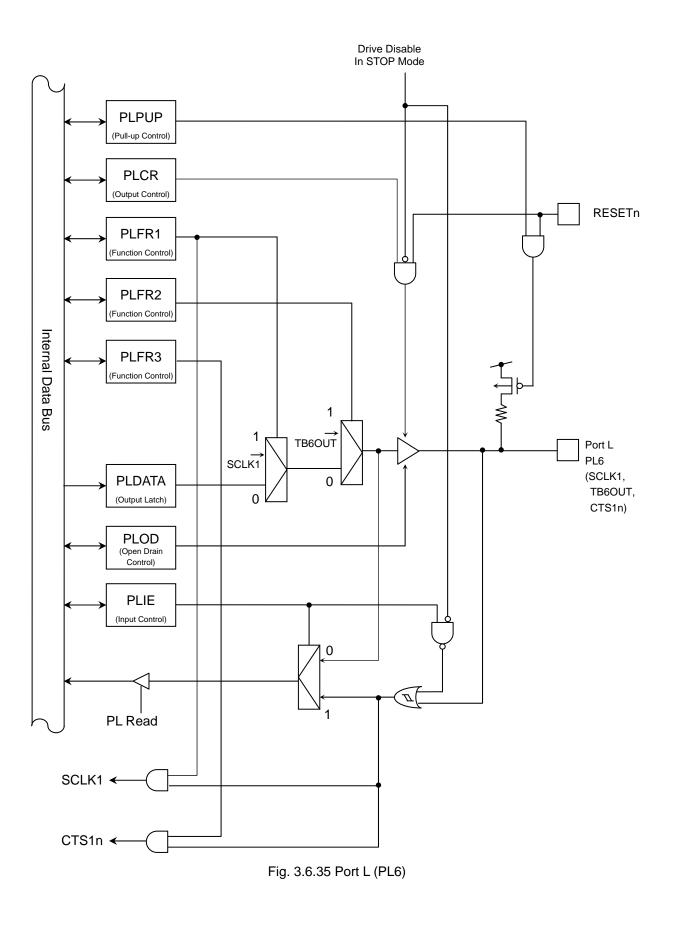

|          | 13           | PL6<br>SCLK1<br>TB6OUT<br>CTS1n | I/O<br>I/O<br>O<br>I | I/O port<br>Serial clock input/ output<br>Timer B output<br>Handshake input pin                                                |

|          | 14           | PL7<br>INT1<br>TB7OUT           | I/O<br>I<br>O        | I/O port<br>Interrupt request pin<br>Timer B output                                                                            |

Table2.2.1 Pin Names and Functions Sorted by Pin (1/10)

| Table2.2.1 Pin Names and Functions Sorted by Pin (2/10) |              |                                 |                      |                                                                                                                     |

|---------------------------------------------------------|--------------|---------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------|

| Туре                                                    | # of<br>Pins | Pin Name                        | Input/<br>Output     | Function                                                                                                            |

| PS                                                      | 15           | DVSS                            | —                    | GND pin                                                                                                             |

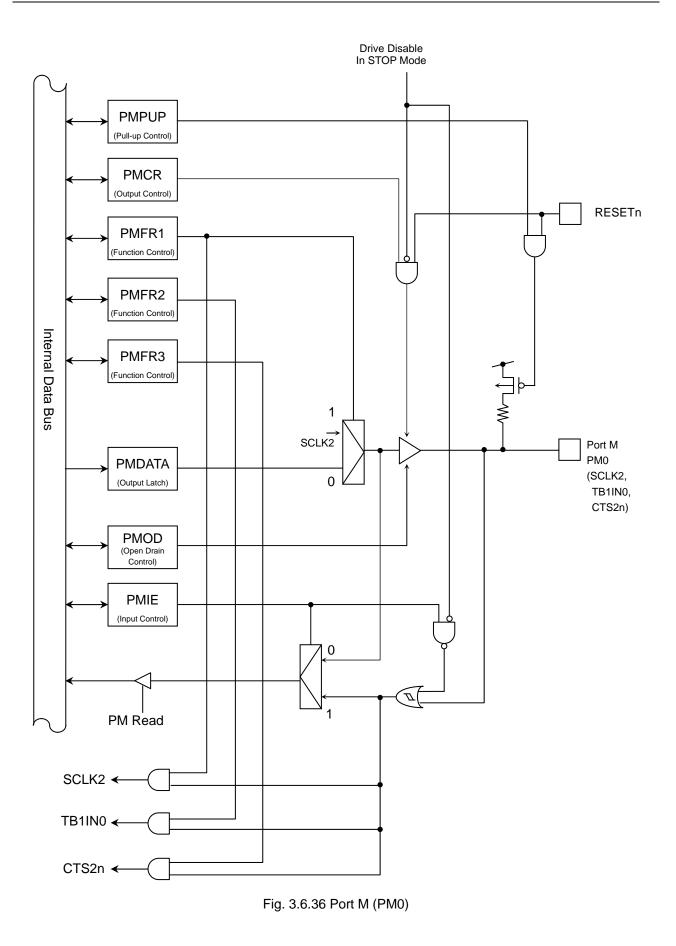

|                                                         | 16           | PM0<br>SCLK2<br>TB1IN0<br>CTS2n | I/O<br>I/O<br>I      | I/O port<br>Serial clock input/ output<br>Inputting the timer B capture trigger<br>Handshake input pin              |

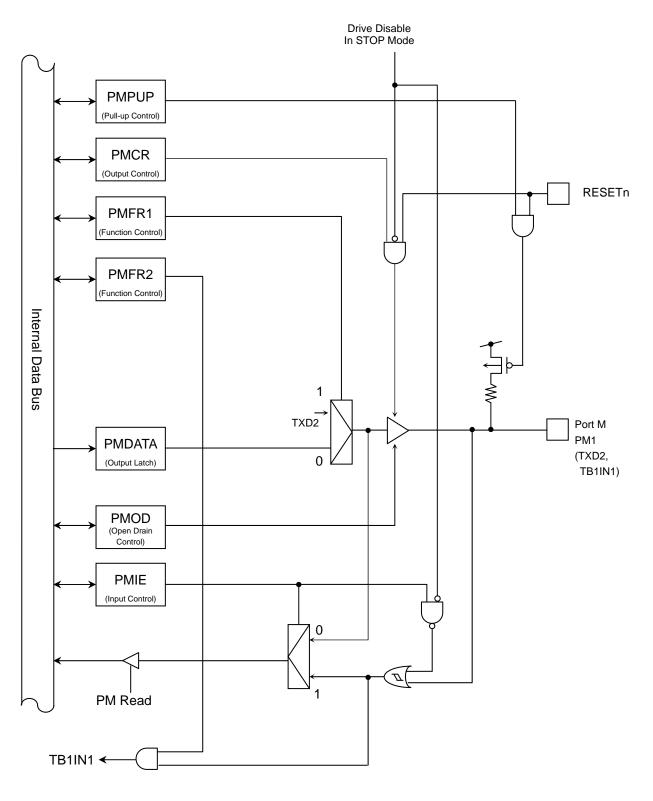

|                                                         | 17           | PM1<br>TXD2<br>TB1IN1           | I/O<br>O<br>I        | I/O port<br>Sending serial data<br>Inputting the timer B capture trigger                                            |

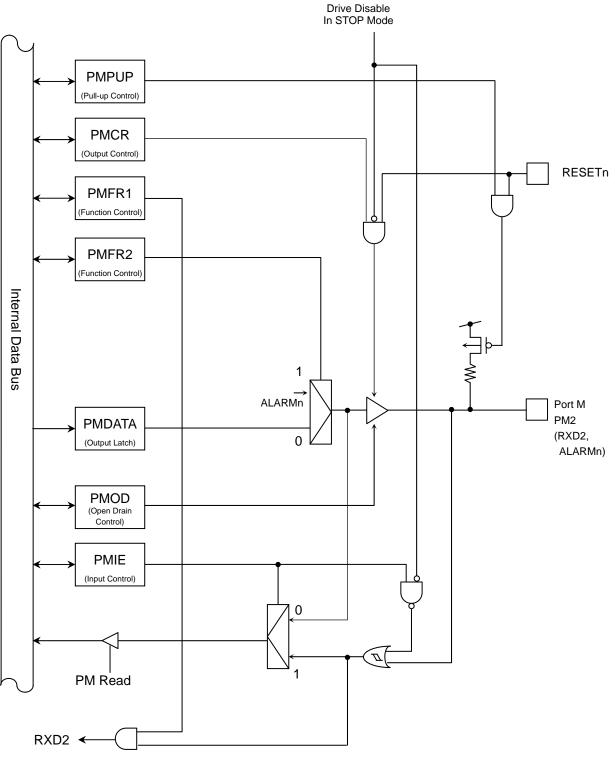

|                                                         | 18           | PM2<br>RDX2<br>ALARMn           | I/O<br>I<br>O        | I/O port<br>Receiving serial data<br>ALARM output                                                                   |

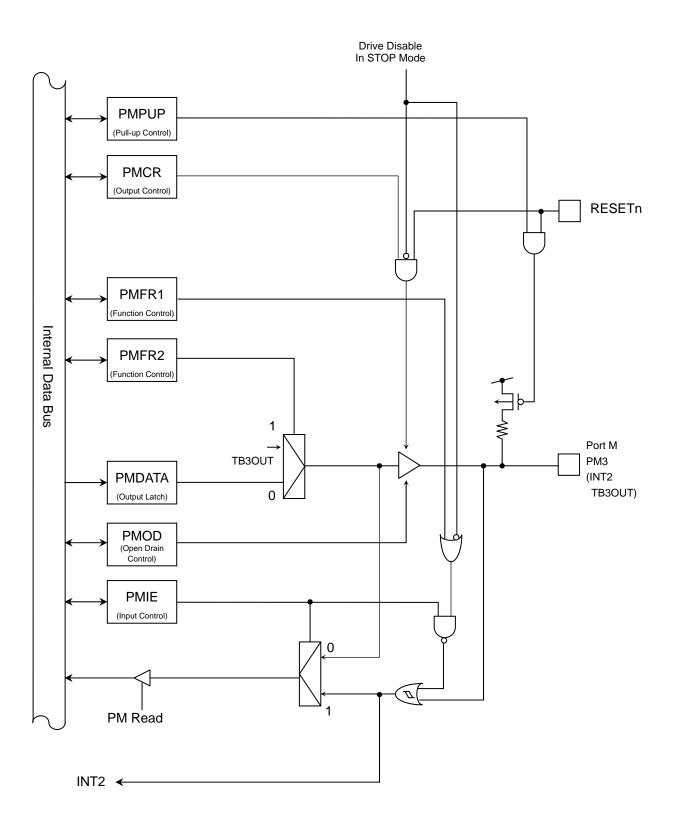

|                                                         | 19           | PM3<br>INT2<br>TB3OUT           | I/O<br>I<br>O        | I/O port<br>Interrupt request pin<br>Timer B output                                                                 |

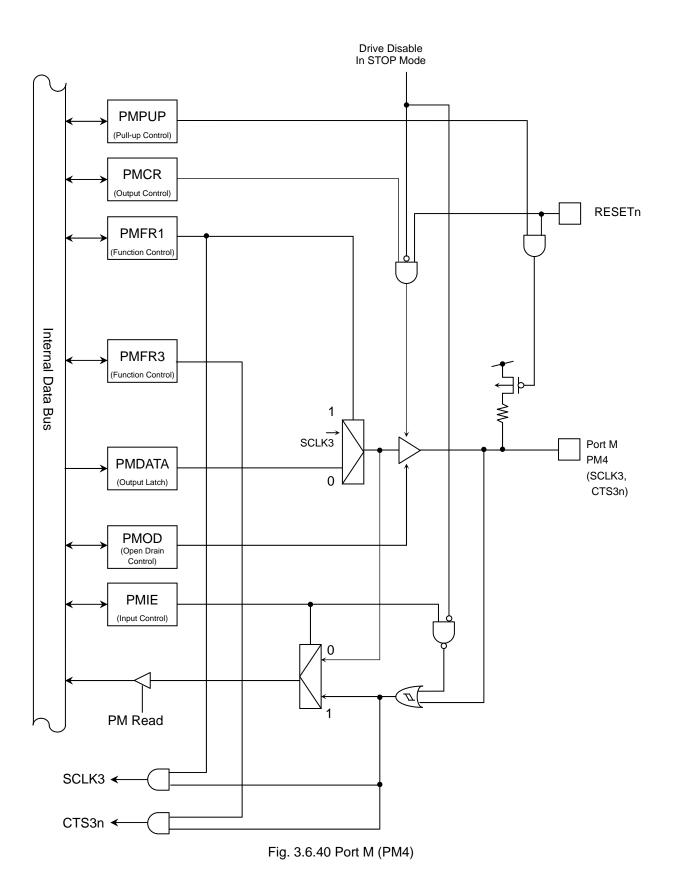

|                                                         | 20           | PM4<br>SCLK3<br>CTS3n           | I/O<br>I/O<br>I      | I/O port<br>Serial clock input/ output<br>Handshake input pin                                                       |

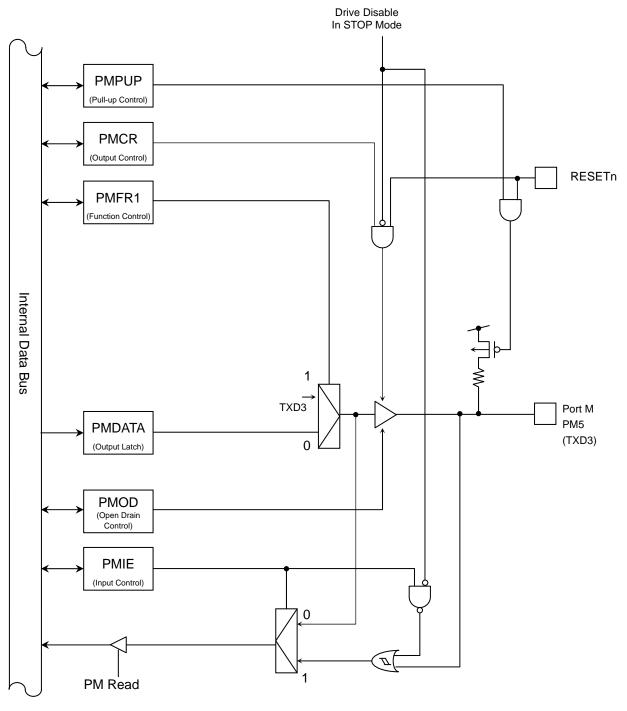

|                                                         | 21           | PM5<br>TXD3                     | I/O<br>O             | I/O port<br>Sending serial data                                                                                     |

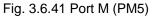

|                                                         | 22           | PM6<br>RXD3                     | I/O<br>I             | I/O port<br>Receiving serial data                                                                                   |

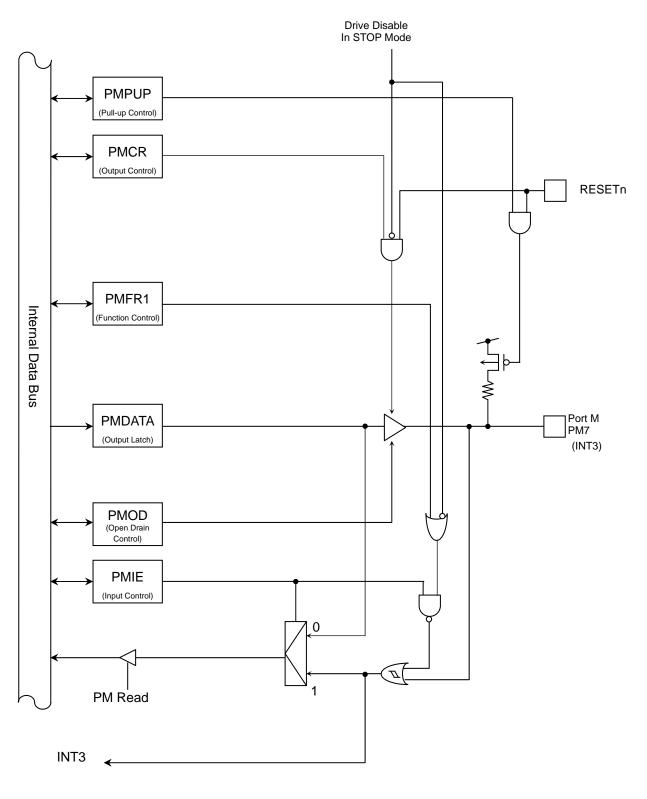

|                                                         | 23           | PM7<br>INT3                     | I/O<br>I             | I/O port<br>Interrupt request pin                                                                                   |

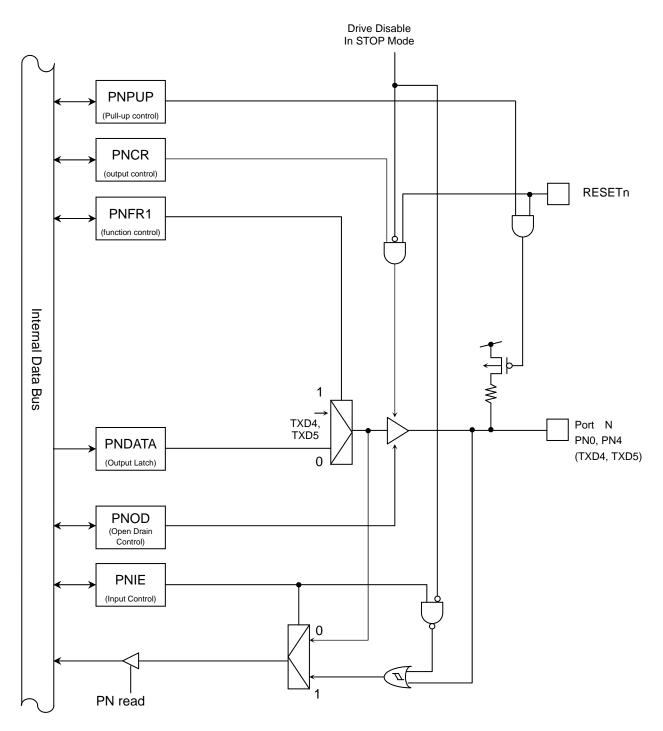

| Function                                                | 24           | PN0<br>TXD4                     | I/O<br>O             | I/O port<br>Sending serial data                                                                                     |

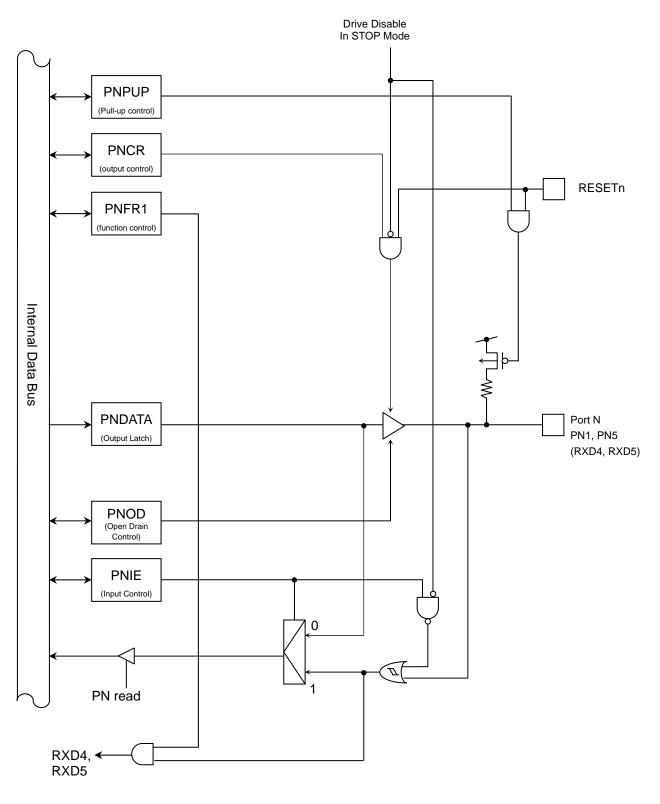

|                                                         | 25           | PN1<br>RXD4                     | I/O<br>I             | I/O port<br>Receiving serial data                                                                                   |

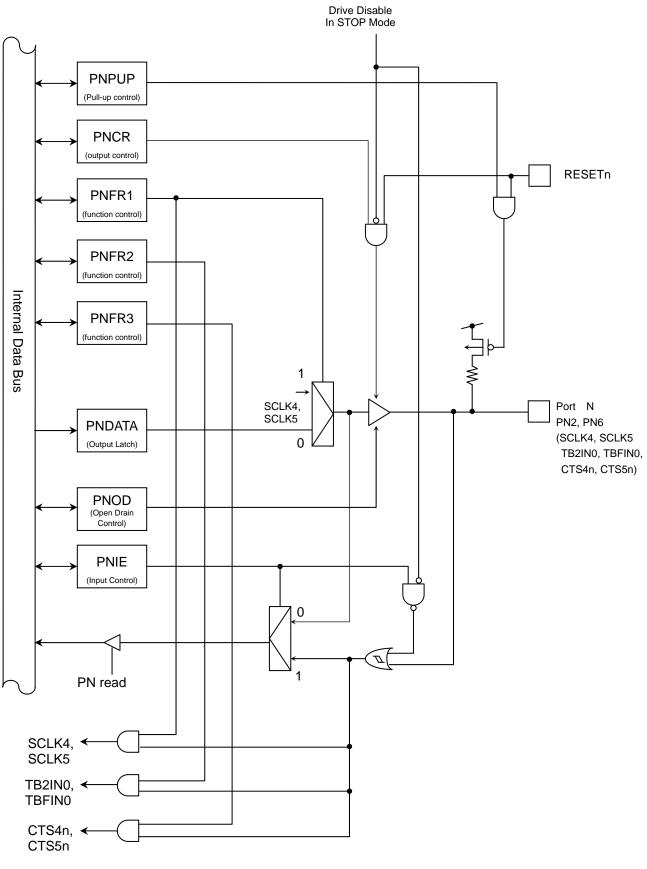

|                                                         | 26           | PN2<br>SCLK4<br>TB2IN0<br>CTS4n | I/O<br>I/O<br>I      | I/O port<br>Serial clock input/ output<br>Inputting the timer B capture trigger<br>Handshake input pin              |

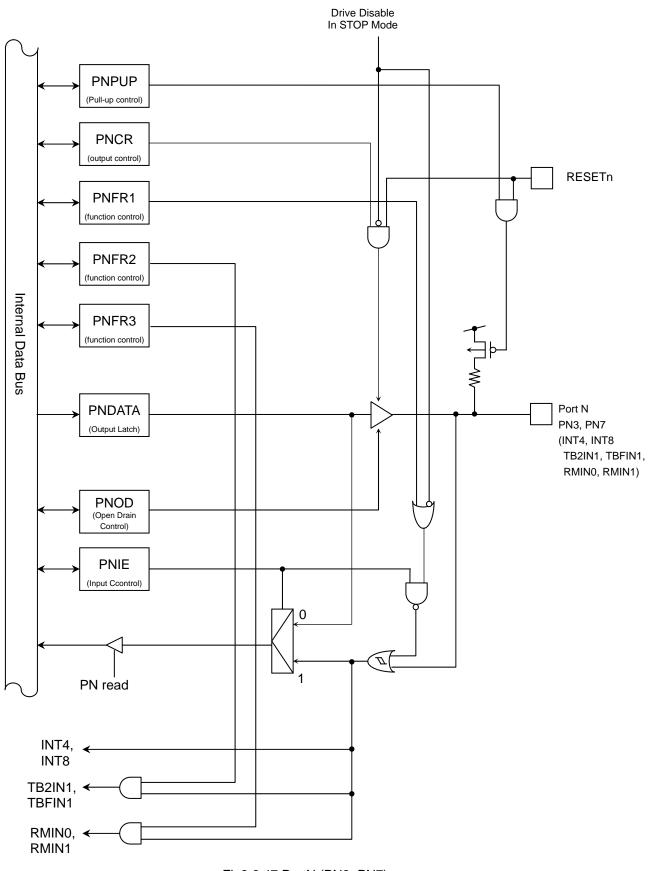

|                                                         | 27           | PN3<br>INT4<br>TB2IN1<br>RMIN0  | I/O<br>I<br>I        | I/O port<br>Interrupt request pin<br>Inputting the timer B capture trigger<br>Inputting signal to remote controller |

|                                                         | 28           | PN4<br>TXD5                     | I/O<br>O             | I/O port<br>Sending serial data                                                                                     |

|                                                         | 29           | PN5<br>RXD5                     | I/O<br>I             | I/O port<br>Receiving serial data                                                                                   |

|                                                         | 30           | PN6<br>SCLK5<br>TBFIN0<br>CTS5n | I/O<br>I/O<br>I<br>I | I/O port<br>Serial clock input/ output<br>Inputting the timer B capture trigger<br>Handshake input pin              |

|                                                         | 31           | PN7<br>INT8<br>TBFIN1<br>RMIN1  | I/O<br>I<br>I        | I/O port<br>Interrupt request pin<br>Inputting the timer B capture trigger<br>Inputting signal to remote controller |

Table2.2.1 Pin Names and Functions Sorted by Pin (2/10)

| Туре     | # of<br>Pins | Pin Name                        | Input/<br>Output     | Function                                                                                               |

|----------|--------------|---------------------------------|----------------------|--------------------------------------------------------------------------------------------------------|

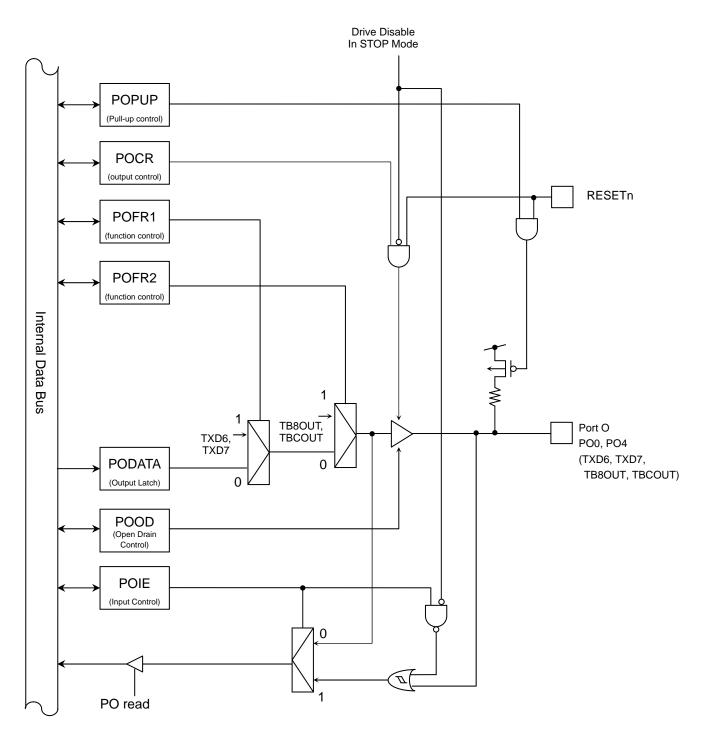

|          | 32           | PO0<br>TXD6<br>TB8OUT           | I/O<br>O<br>O        | I/O port<br>Sending serial data<br>Timer B output                                                      |

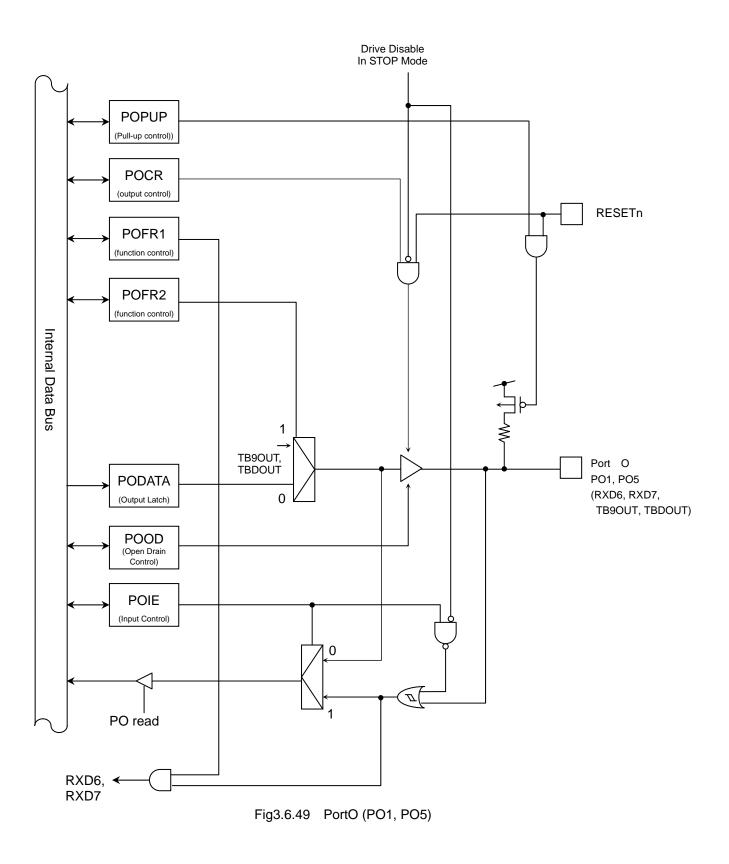

|          | 33           | PO1<br>RXD6<br>TB9OUT           | I/O<br>I<br>O        | I/O port<br>Receiving serial data<br>Timer B output                                                    |

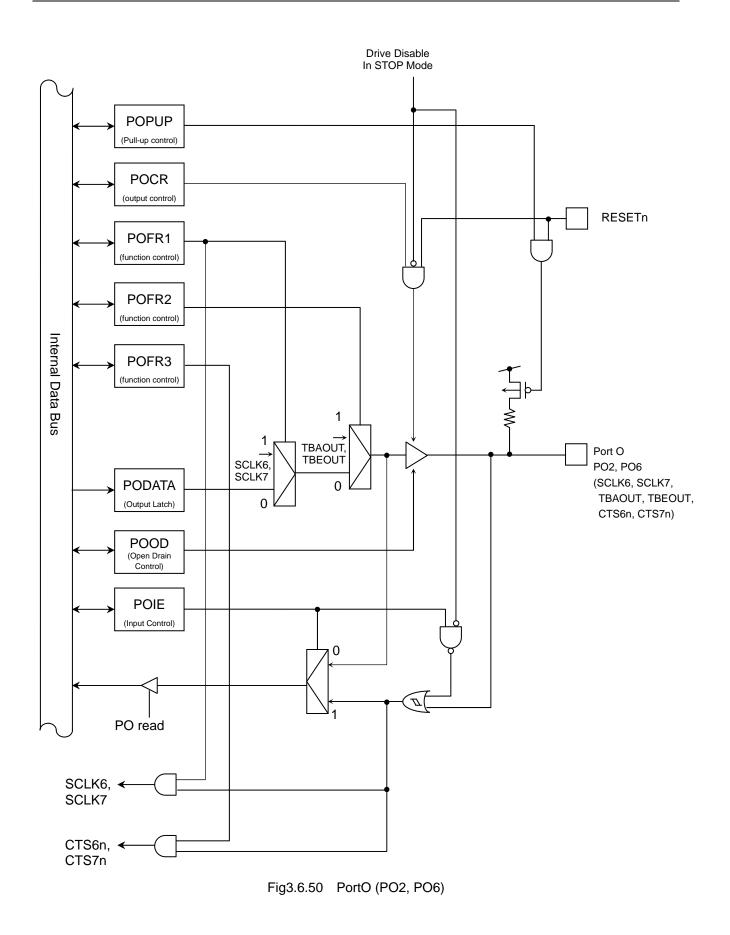

|          | 34           | PO2<br>SCLK6<br>TBAOUT<br>CTS6n | I/O<br>I/O<br>O<br>I | /O port<br>Serial clock input/ output<br>Inputting the timer B capture trigger<br>Handshake input pin  |

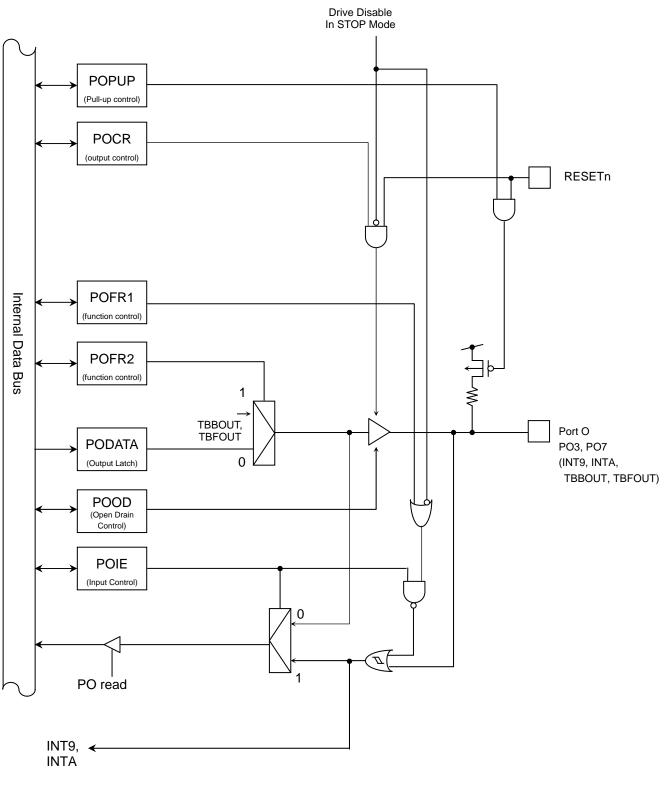

|          | 35           | PO3<br>INT9<br>TBBOUT           | I/O<br>I<br>O        | I/O port<br>Interrupt request pin<br>Timer B output                                                    |

|          | 36           | PO4<br>TXD7<br>TBCOUT           | I/O<br>O<br>O        | I/O port<br>Sending serial data<br>Timer B output                                                      |

|          | 37           | PO5<br>RXD7<br>TBDOUT           | I/O<br>I<br>O        | I/O port<br>Receiving serial data<br>Timer B output                                                    |

| Function | 38           | PO6<br>SCLK7<br>TBEOUT<br>CTS7n | I/O<br>I/O<br>O<br>I | I/O port<br>Serial clock input/ output<br>Inputting the timer B capture trigger<br>Handshake input pin |

|          | 39           | PO7<br>INTA<br>TBFOUT           | I/O<br>I<br>O        | I/O port<br>Interrupt request pin<br>Timer B output                                                    |

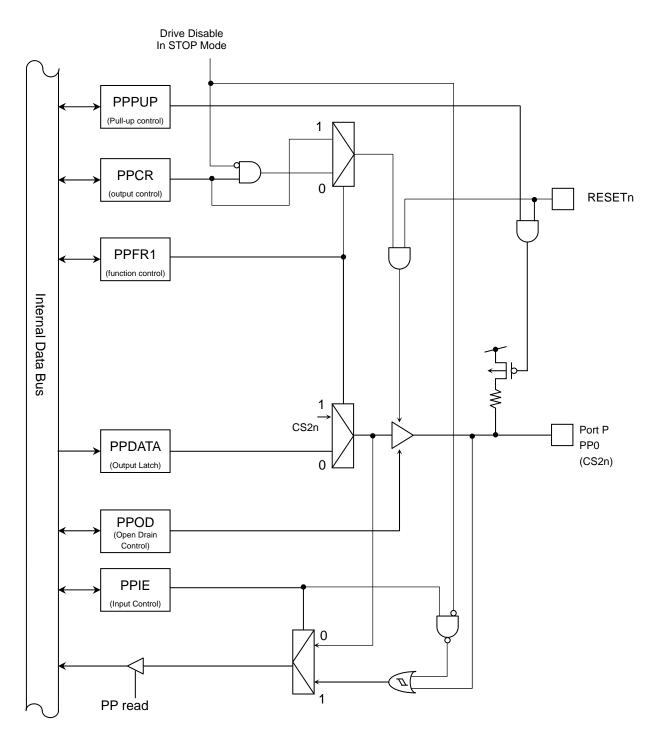

|          | 40           | PP0<br>CS2n                     | I/O<br>O             | I/O port<br>Chip select pin                                                                            |

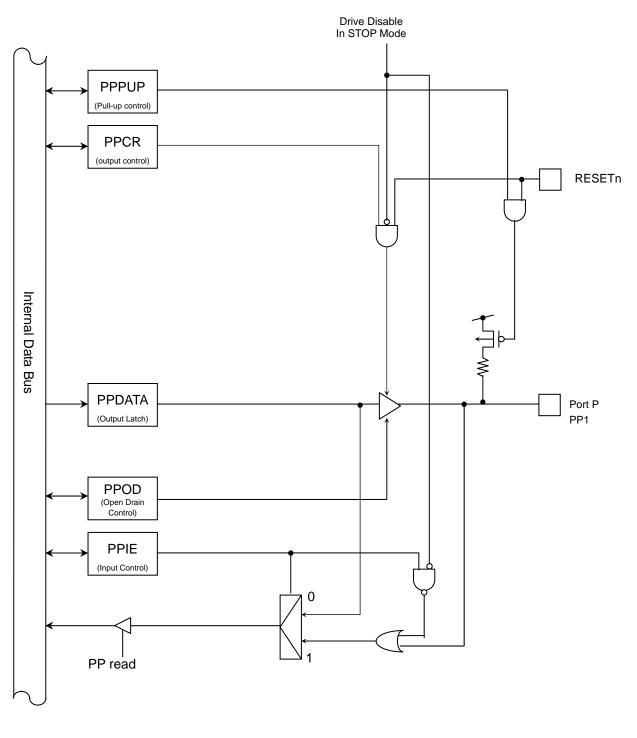

|          | 41           | PP1                             | I/O                  | I/O port                                                                                               |

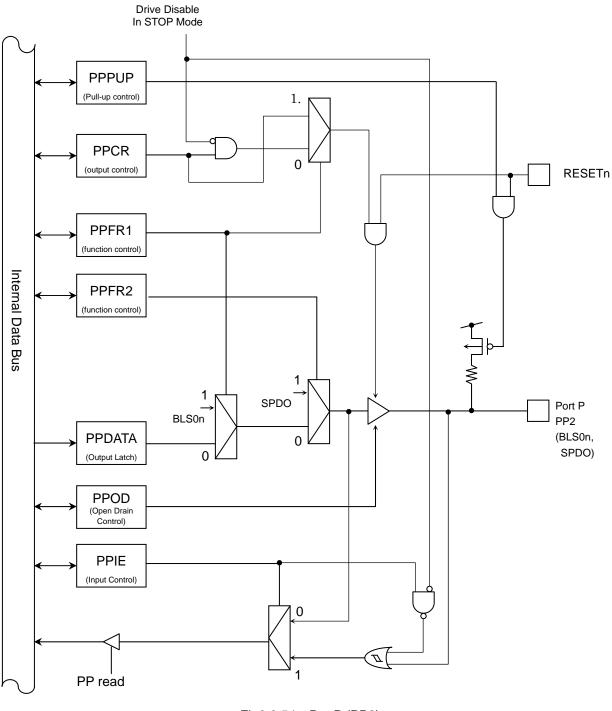

|          | 42           | PP2<br>BLS0n<br>SPDO            | I/O<br>O<br>O        | I/O port<br>Bytelane pin<br>Data output pin for SSP                                                    |

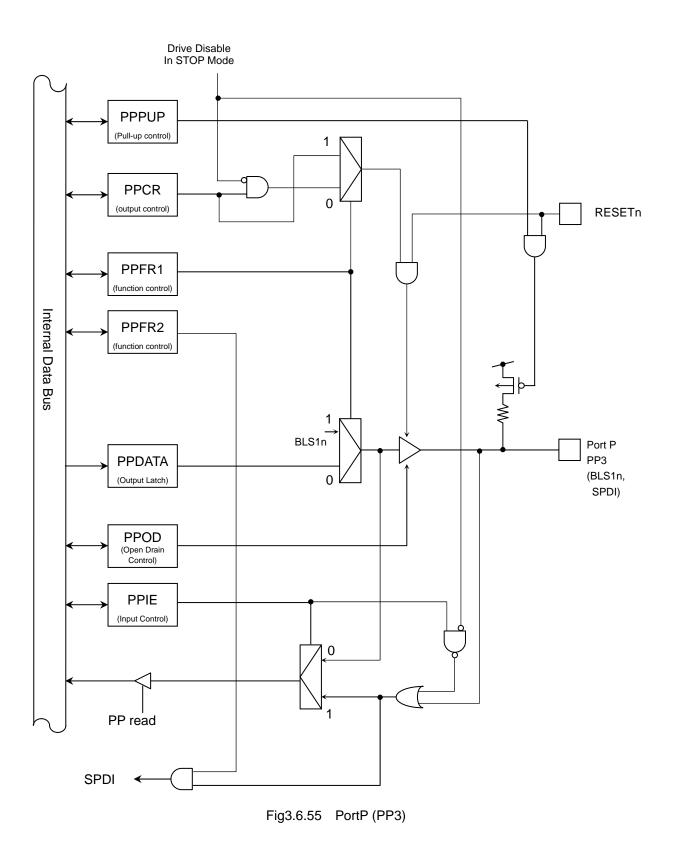

|          | 43           | PP3<br>BLS1n<br>SPDI            | I/O<br>O<br>I        | I/O port<br>Bytelane pin<br>Data input pin for SSP                                                     |

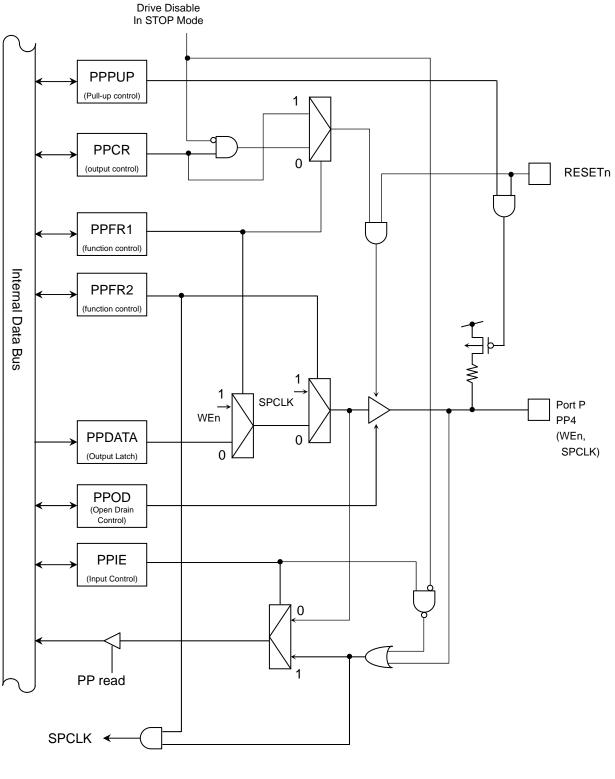

|          | 44           | PP4<br>WEn<br>SPCLK             | I/O<br>O<br>I/O      | I/O port<br>Write strobe pin<br>Clock pin for SSP                                                      |

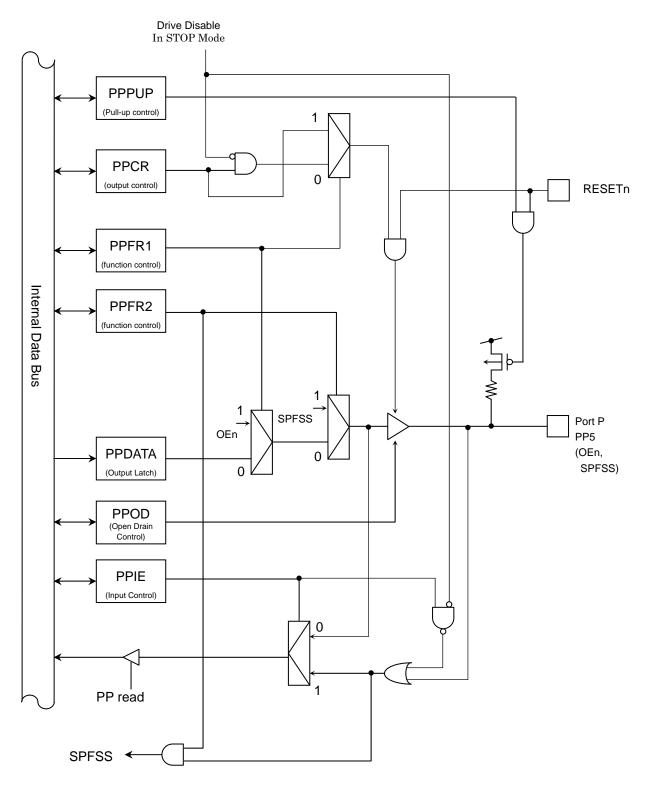

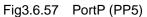

|          | 45           | PP5<br>OEn<br>SPFSS             | I/O<br>O<br>O        | I/O port<br>Output enable pin<br>FSS pin for SSP                                                       |

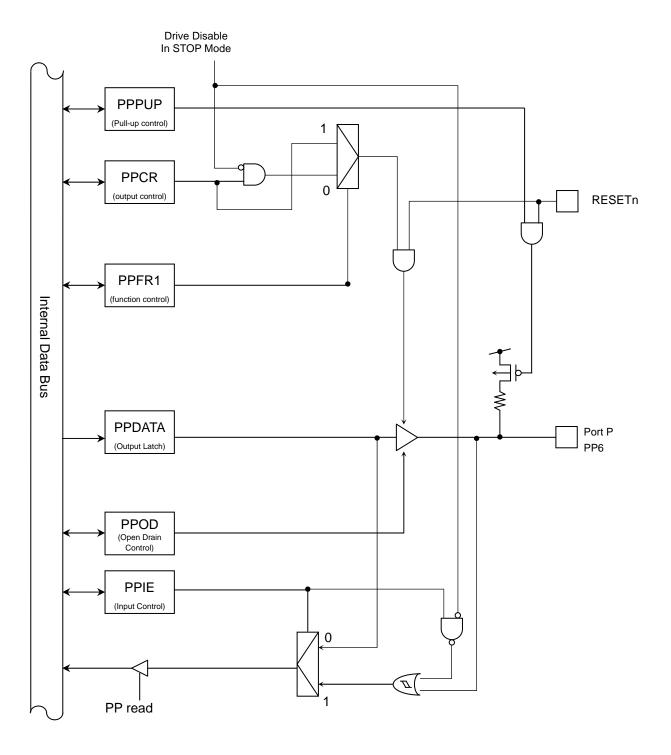

|          | 46           | PP6                             | I/O                  | I/O port                                                                                               |

| PS       | 47           | DVCC                            | —                    | Power supply pin                                                                                       |

| гэ       | 48           | DVSS                            | —                    | GND pin                                                                                                |

Table2.2.1 Pin Names and Functions Sorted by Pin (3/10)

| Туре         | # of<br>Pins | Pin Name   | Input/<br>Output | Functions Sorted by Pin (4/10)<br>Function |

|--------------|--------------|------------|------------------|--------------------------------------------|

|              |              | PA0        | I/O              | I/O Port                                   |

| -            | 49           | D0         | 1/O              | Data bus                                   |

|              |              | PA1        | I/O              | I/O Port                                   |

|              | 50           | D1         | I/O              | Data bus                                   |

|              |              | PA2        | I/O              | I/O Port                                   |

|              | 51           | D2         | I/O              | Data bus                                   |

|              |              | PA3        | I/O              | I/O Port                                   |

|              | 52           | D3         | I/O              | Data bus                                   |

|              | 50           | PA4        | I/O              | I/O Port                                   |

|              | 53           | D4         | I/O              | Data bus                                   |

|              | E A          | PA5        | I/O              | I/O Port                                   |

|              | 54           | D5         | I/O              | Data bus                                   |

|              | 55           | PA6        | I/O              | I/O Port                                   |

|              |              | D6         | I/O              | Data bus                                   |

|              | 56           | PA7        | I/O              | I/O Port                                   |

| Euro eti e e |              | D7         | I/O              | Data bus                                   |

| Function     | 57           | PB0        | I/O              | I/O Port                                   |

|              |              | D8         | I/O              | Data bus                                   |

|              | 58           | PB1        | I/O              | I/O Port                                   |

|              |              | D9         | I/O              | Data bus                                   |

|              | 59           | PB2        | I/O              | I/O Port                                   |

|              | 00           | D10        | I/O              | Data bus                                   |

|              | 60           | PB3        | I/O              | I/O Port                                   |

|              |              | D11        | I/O              | Data bus                                   |

|              | 61           | PB4        | I/O              | I/O Port                                   |

|              | -            | D12        | I/O              | Data bus                                   |

|              | 62           | PB5        | I/O              | I/O Port                                   |

|              |              | D13        | I/O              | Data bus                                   |

|              | 63           | PB6        | I/O              | I/O Port                                   |

|              |              | D14        | 1/O<br>1/O       | Data bus<br>I/O Port                       |

|              | 64           | PB7<br>D15 | 1/O<br>1/O       | Data bus                                   |

|              |              | 010        | 1/0              |                                            |

Table2.2.1 Pin Names and Functions Sorted by Pin (4/10)

|          | # of         |          | Input/ | d Functions Sorted by Pin (5/10) |

|----------|--------------|----------|--------|----------------------------------|

| Туре     | # of<br>Pins | Pin Name | Output | Function                         |

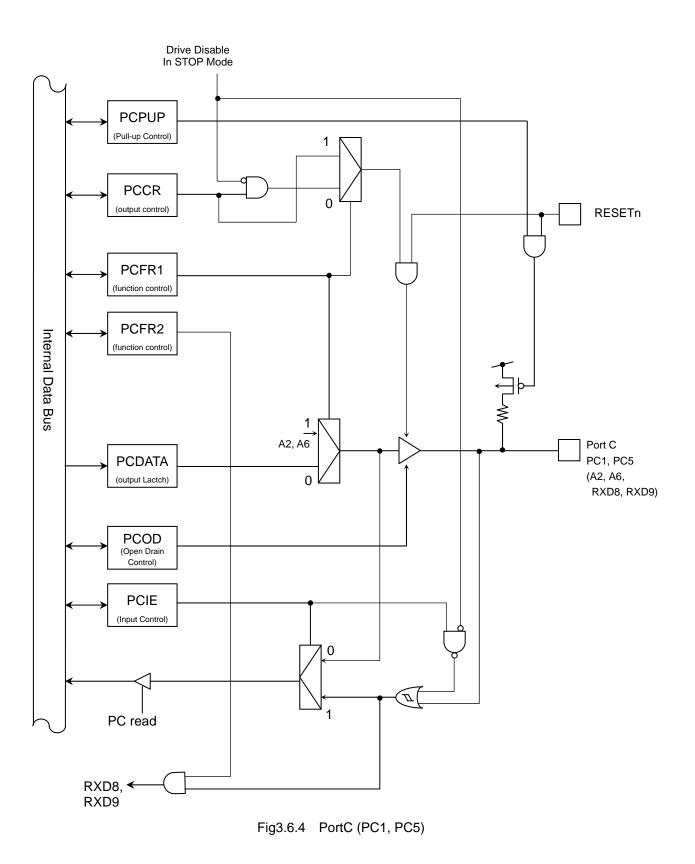

|          |              | PC0      | I/O    | I/O Port                         |

|          | 65           | A1       | 0      | Address Bus                      |

|          |              | TXD8     | 0      | Sending serial data              |

|          |              | PC1      | I/O    | I/O Port                         |

|          | 66           | A2       | 0      | Address Bus                      |

|          |              | RXD8     | I      | Receiving serial data            |

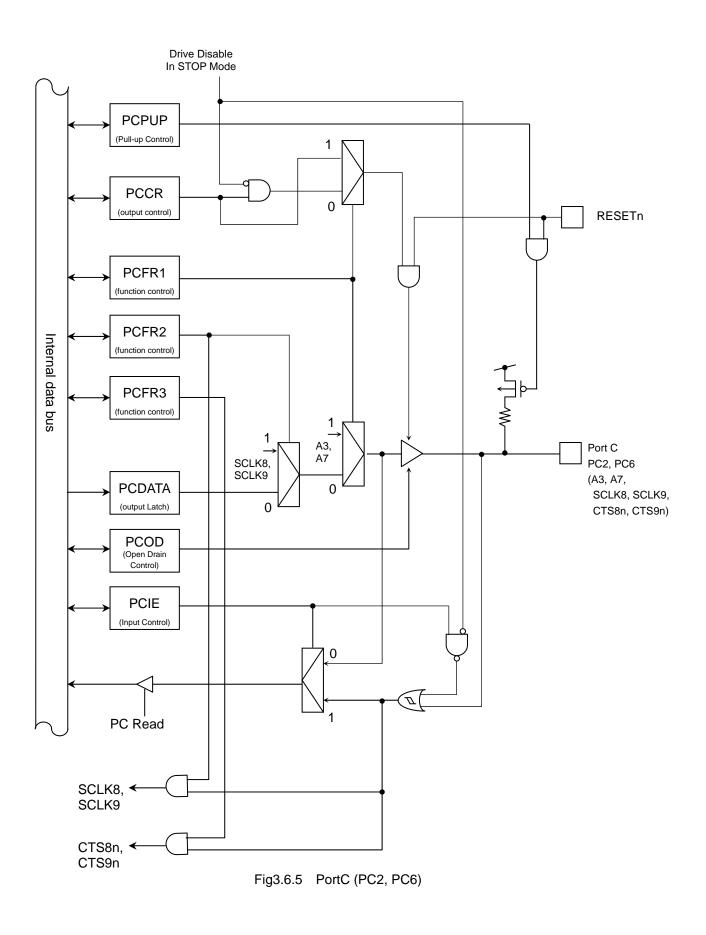

|          |              | PC2      | I/O    | I/O Port                         |

|          | 67           | A3       | 0      | Address Bus                      |

|          | 07           | SCLK8    | I/O    | Serial clock input/ output       |

|          |              | CTS8n    | 1      | Handshake input pin              |

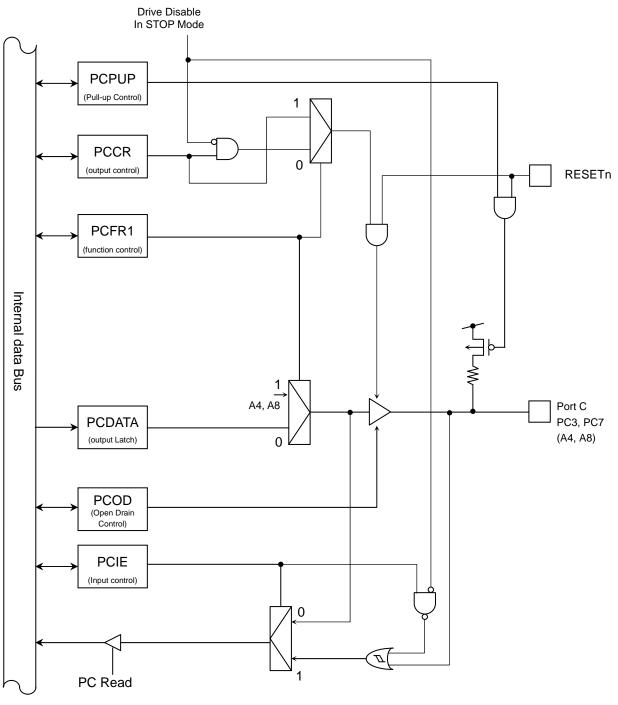

|          | 68           | PC3      | I/O    | I/O Port                         |

|          | 00           | A4       | 0      | Address Bus                      |

|          |              | PC4      | I/O    | I/O Port                         |

|          | 69           | A5       | 0      | Address Bus                      |

|          |              | TXD9     | 0      | Sending serial data              |

|          |              | PC5      | I/O    | I/O Port                         |

|          | 70           | A6       | 0      | Address Bus                      |

|          |              | RXD9     | I      | Receiving serial data            |

|          | 71           | PC6      | I/O    | I/O Port                         |

|          |              | A7       | 0      | Address Bus                      |

|          |              | SCLK9    | I/O    | Serial clock input/ output       |

|          |              | CTS9n    | 1      | Handshake input pin              |

|          | 72           | PC7      | I/O    | I/O Port                         |

|          | 12           | A8       | 0      | Address Bus                      |

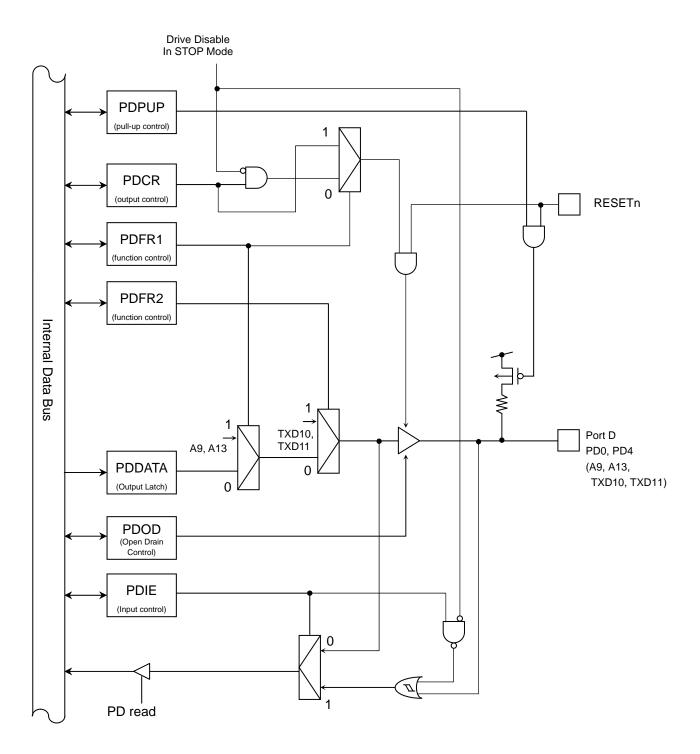

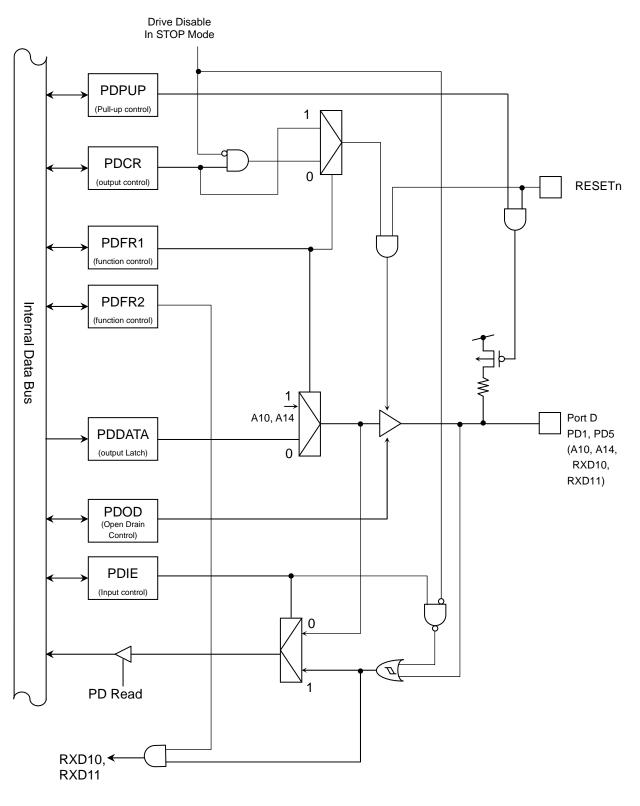

| Function | 73           | PD0      | I/O    | I/O Port                         |

|          |              | A9       | 0      | Address Bus                      |

|          |              | TXD10    | 0      | Sending serial data              |

|          |              | PD1      | I/O    | I/O Port                         |

|          | 74           | A10      | 0      | Address Bus                      |

|          |              | RXD10    | I      | Receiving serial data            |

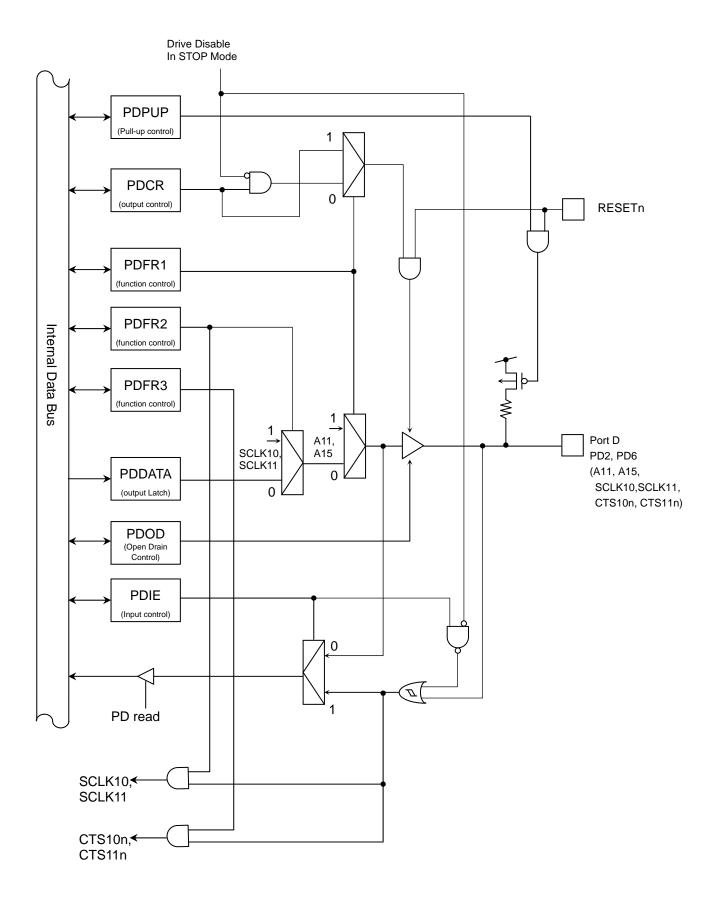

|          |              | PD2      | I/O    | I/O Port                         |

|          | 75           | A11      | 0      | Address Bus                      |

|          | 10           | SCLK10   | I/O    | Serial clock input/ output       |

|          |              | CTS10n   | 1      | Handshake input pin              |

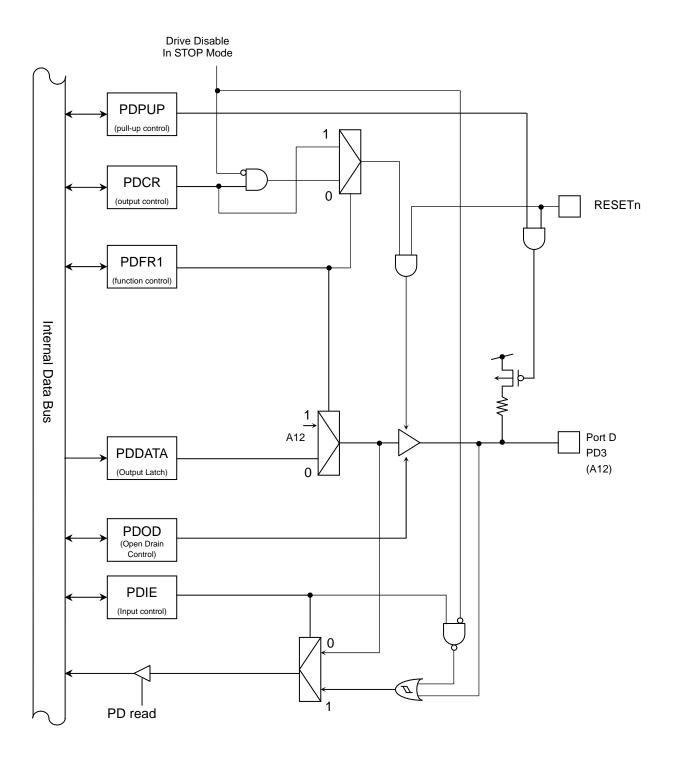

|          | 76           | PD3      | I/O    | I/O Port                         |

|          |              | A12      | 0      | Address Bus                      |

|          |              | PD4      | I/O    | I/O Port                         |

|          | 77           | A13      | 0      | Address Bus                      |

|          |              | TXD11    | 0      | Sending serial data              |

|          |              | PD5      | I/O    | I/O Port                         |

|          | 78           | A14      | 0      | Address Bus                      |

|          |              | RXD11    |        | Receiving serial data            |

|          |              | PD6      | I/O    | I/O Port                         |

|          | 79           | A15      | 0      | Address Bus                      |

|          |              | SCLK11   | I/O    | Serial clock input/ output       |

|          |              | CTS11n   | 1      | Handshake input pin              |

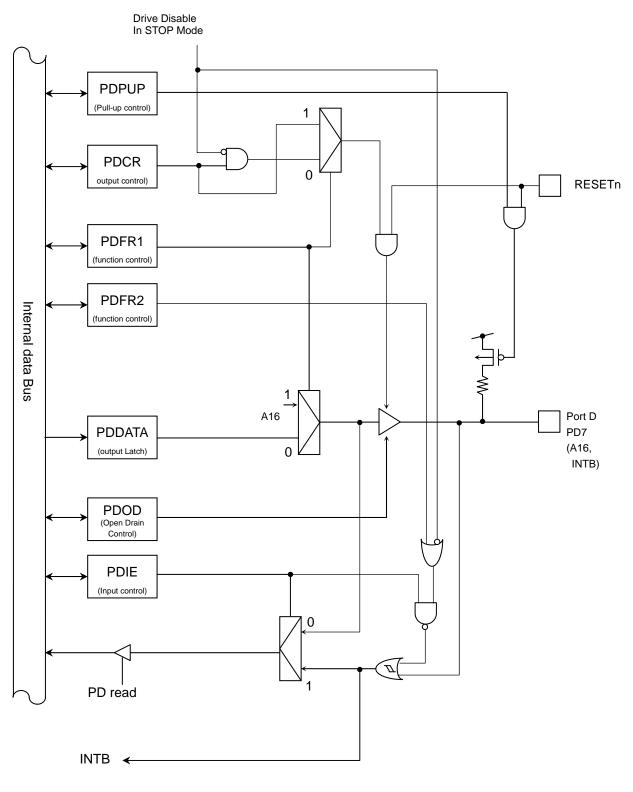

|          |              | PD7      | I/O    | I/O Port                         |

|          | 80           | A16      | 0      | Address Bus                      |

|          |              | INTB     | I      | Interrupt request pin            |

Table2.2.1 Pin Names and Functions Sorted by Pin (5/10)

| Туре      | # of<br>Pins | Pin Name          | Input/<br>Output | Function                              |

|-----------|--------------|-------------------|------------------|---------------------------------------|

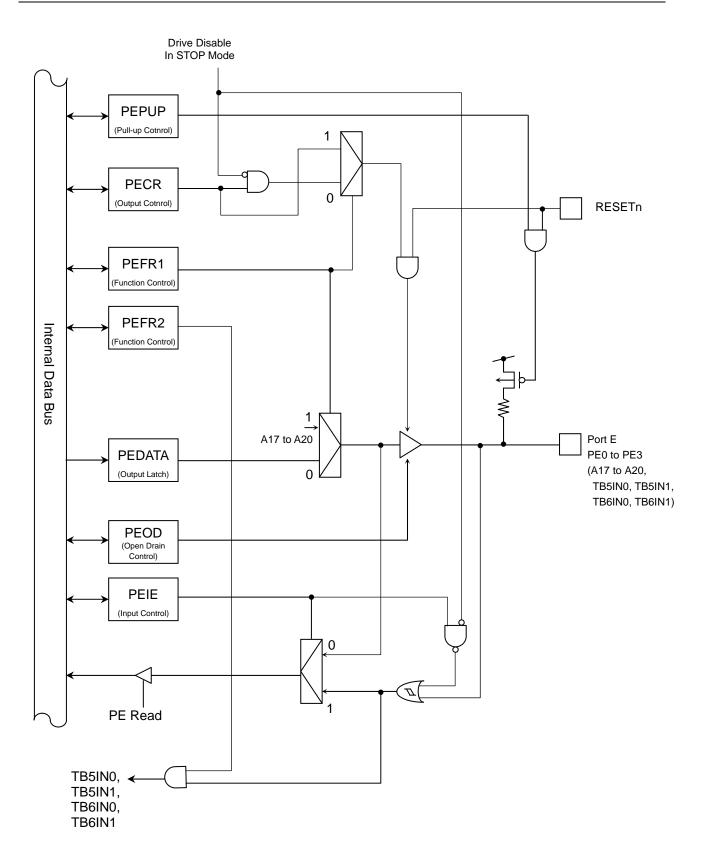

|           |              | PE0               | I/O              | I/O port                              |

|           | 81           | A17               | 0                | Adress bus                            |

|           |              | TB5IN0            | I                | Inputting the timer B capture trigger |

|           |              | PE1               | I/O              | I/O port                              |

|           | 82           | A18               | 0                | Adress bus                            |

|           |              | TB5IN1            | 1                | Inputting the timer B capture trigger |

|           |              | PE2               | I/O              | I/O port                              |

|           | 83           | A19               | 0                | Adress bus                            |

|           |              | TB6IN0            | I                | Inputting the timer B capture trigger |

|           |              | PE3               | I/O              | I/O port                              |

|           | 84           | A20               | 0                | Adress bus                            |

|           |              | TB6IN1            | 1                | Inputting the timer B capture trigger |

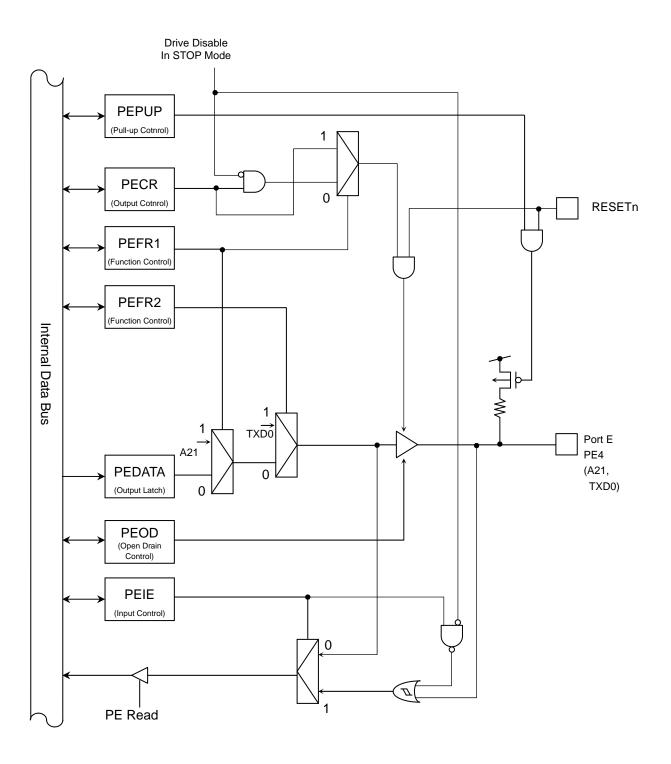

| Function  |              | PE4               | I/O              | I/O port                              |

|           | 85           | A21               | 0                | Adress bus                            |

|           |              | TXD0              | 0                | Sending serial data                   |

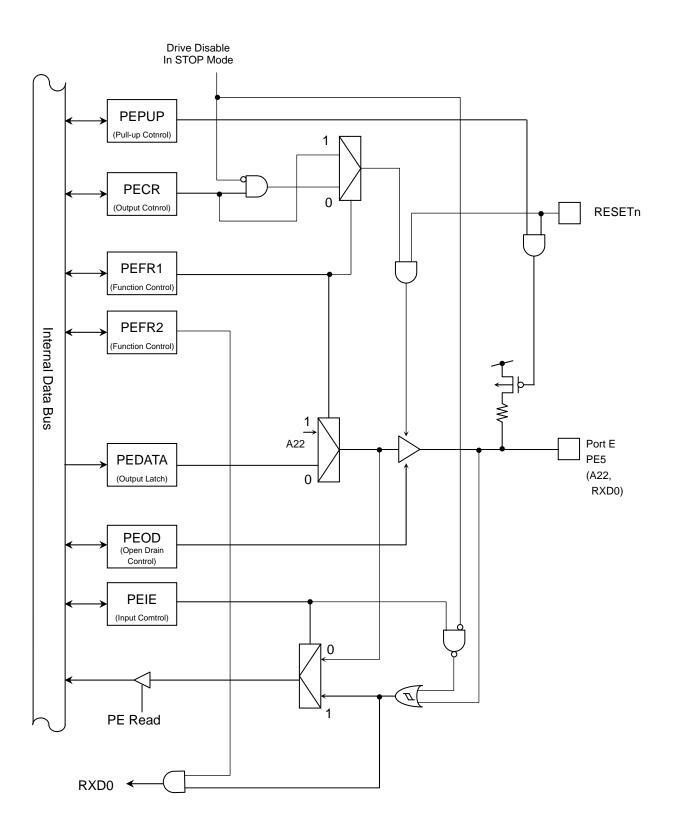

|           |              | PE5               | I/O              | I/O port                              |

|           | 86           | A22               | 0                | Adress bus                            |

|           |              | RXD0              |                  | Receiving serial data                 |

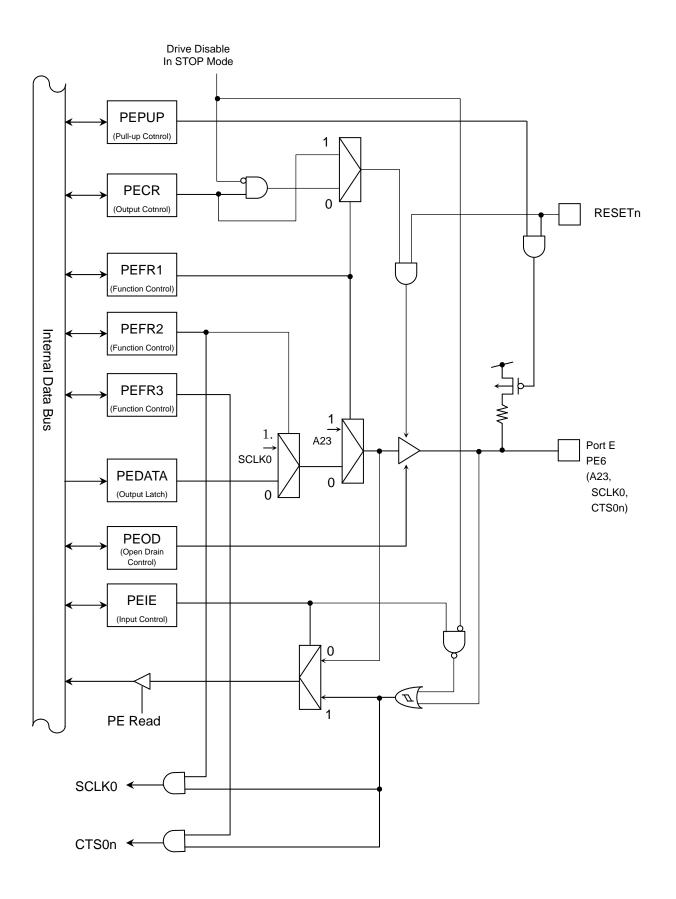

|           | 87           | PE6               | I/O              | I/O port                              |

|           |              | A23               | 0<br>I/O         | Adress bus                            |

|           |              | SCLK0<br>CTS0n    |                  | Serial clock input/ output            |

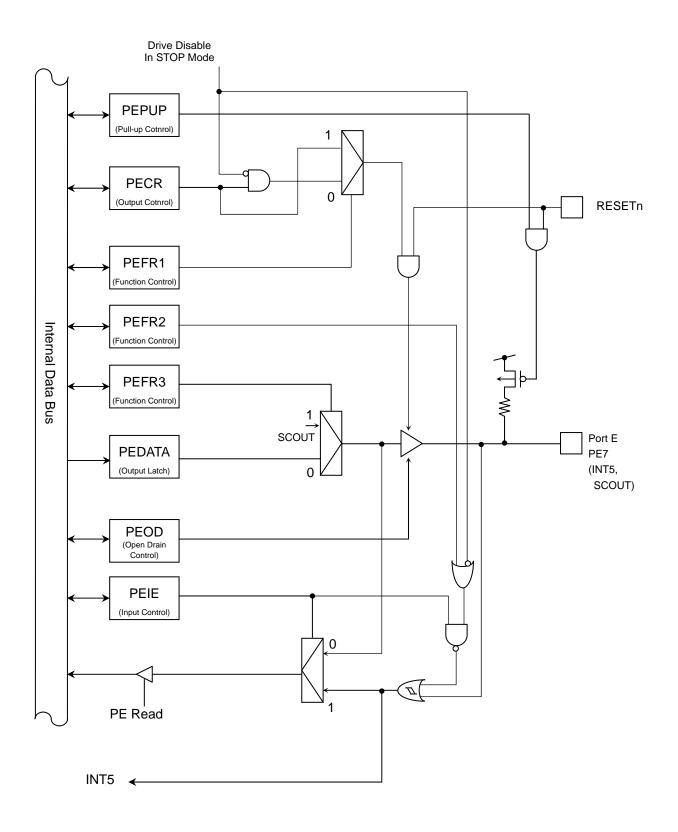

|           |              | PE7               | <br> /O          | Handshake input pin                   |

|           | 88           | INT5              | 1/O              | I/O port<br>Interrupt request pin     |

|           |              | SCOUT             | 0                | System clock output                   |

|           | 80           | DVCC              | -                | Power supply pin                      |

| PS        | 89           |                   | _                | GND pin                               |

|           | 90           | DVSS              | -                |                                       |

|           | 91           | SWDIO             | I/O              | Debug pin                             |

|           | 92           | SWDCK             | I/O              | Debug pin                             |

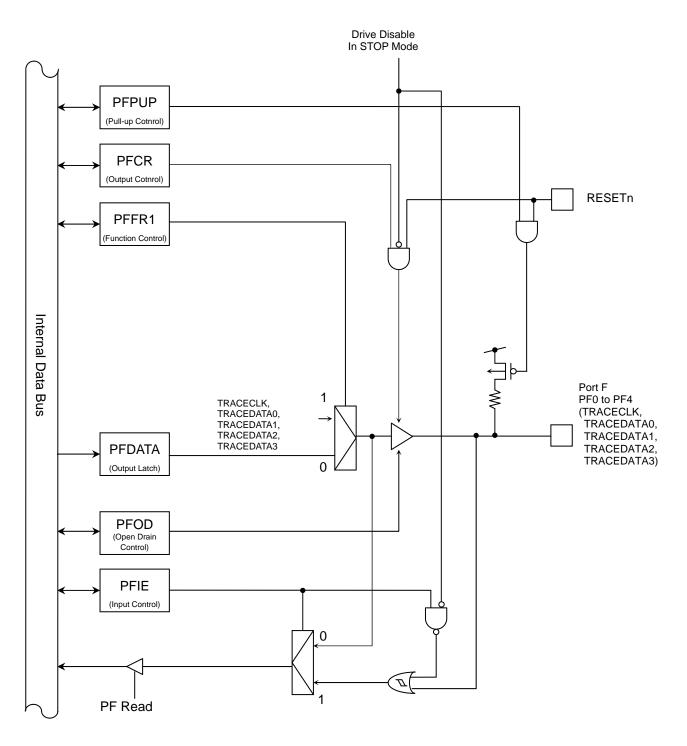

|           | 93           | PF0               | I/O              | I/O port                              |

|           |              | TRACECLK          | 0                | Debug pin                             |

|           | 94           | PF1               | 1/0              | I/O port                              |

| Function/ |              | TRACEDATA0        | 0<br>I/O         | Debug pin                             |

| debug     | 95           | PF2               | 1/O<br>O         | I/O port                              |

|           |              | TRACEDATA1<br>PF3 | 1/0              | Debug pin                             |

|           | 96           | -                 | -                | I/O port<br>Debug pin                 |

|           |              | TRACEDATA2<br>PF4 | 0<br>I/O         |                                       |

|           | 97           |                   |                  | I/O port                              |

|           |              | TRACEDATA3        | 0                | Debug pin                             |

| Table2.2.1 Pin Names  | and Functions  | Sorted by  | v Pin (   | (6/10) |

|-----------------------|----------------|------------|-----------|--------|

| Tablez.z.TT III Names | and r unclions | Soliced by | y i iii ( | 0/10/  |

| Туре     | # of<br>Pins | Pin Name                         | Input/<br>Output       | Function                                                                                                                                                |

|----------|--------------|----------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

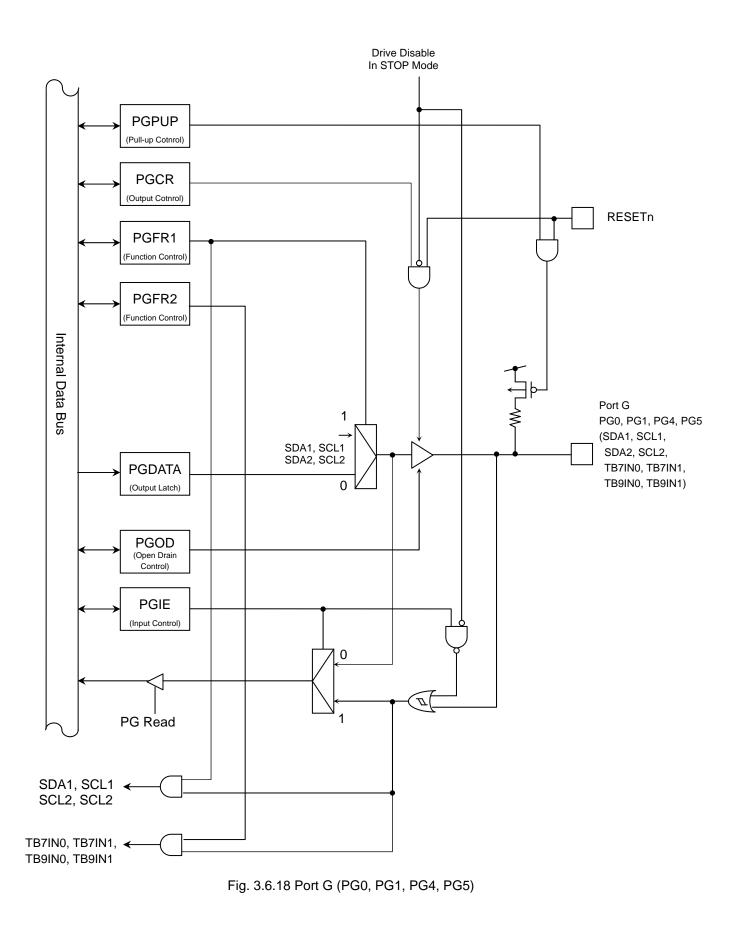

|          | 98           | PG0<br>SDA1<br>TB7IN0            | I/O<br>I/O             | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : data pin<br>-in the SIO mode: data pin<br>Inputting the timer B capture trigger  |

|          | 99           | PG1<br>SCL1<br>TB7IN1            | I/O<br>I/O             | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : clock pin<br>-in the SIO mode: data pin<br>Inputting the timer B capture trigger |

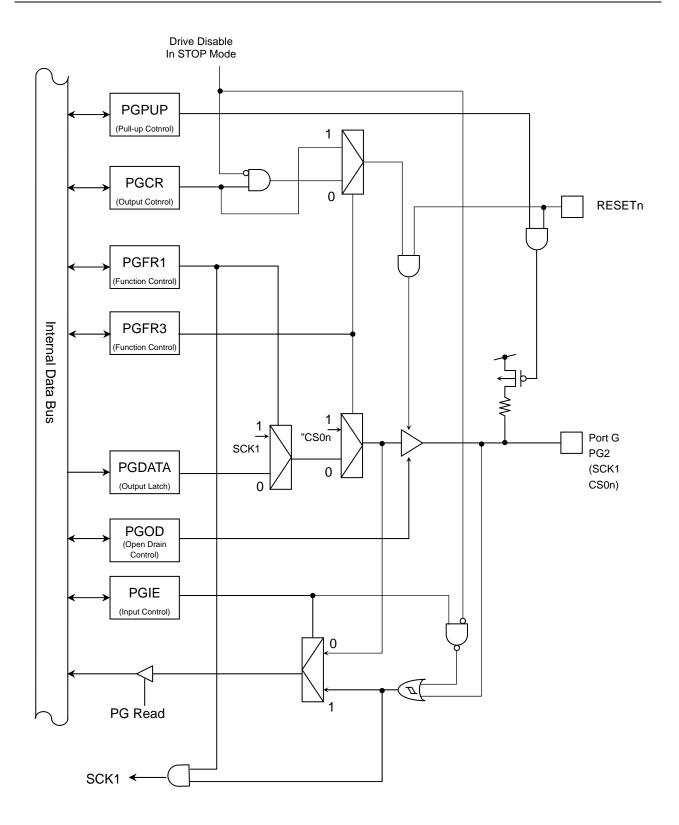

|          | 100          | PG2<br>SCK1<br>CS0n              | I/O<br>I/O             | I/O port<br>Inputting and outputting a clock if the<br>serial bus interface operates in the SIO<br>mode.<br>Chip select pin                             |

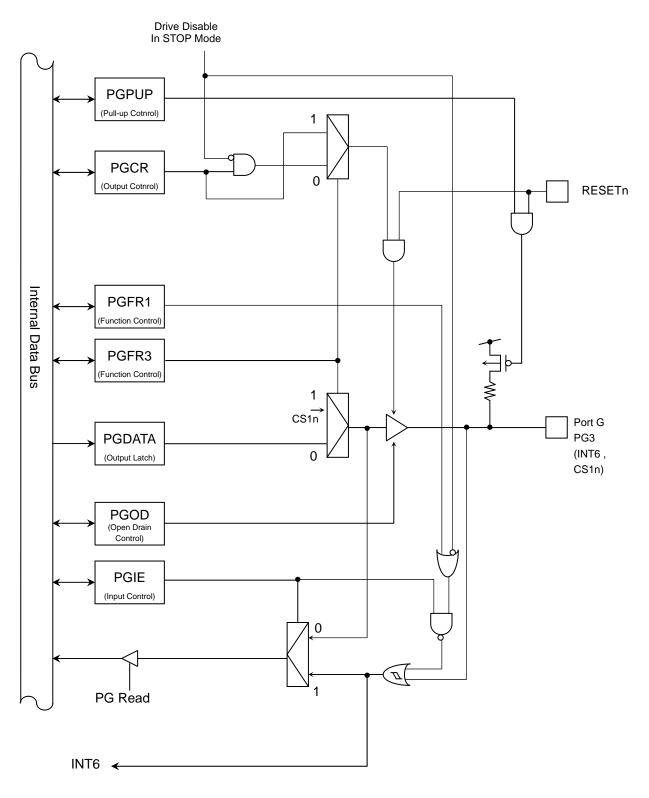

|          | 101          | PG3<br>INT6<br>CS1n              | 1/O<br>1<br>0          | I/O port<br>Interrupt request pin<br>Chip select pin                                                                                                    |

| Function | 102          | PG4<br>SDA2<br>TB9IN0            | I/O<br>I/O             | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : data pin<br>-in the SIO mode: data pin<br>Inputting the timer B capture trigger  |

|          | 103          | PG5<br>SCL2<br>TB9IN1            | I/O<br>I/O             | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : clock pin<br>-in the SIO mode: data pin<br>Inputting the timer B capture trigger |

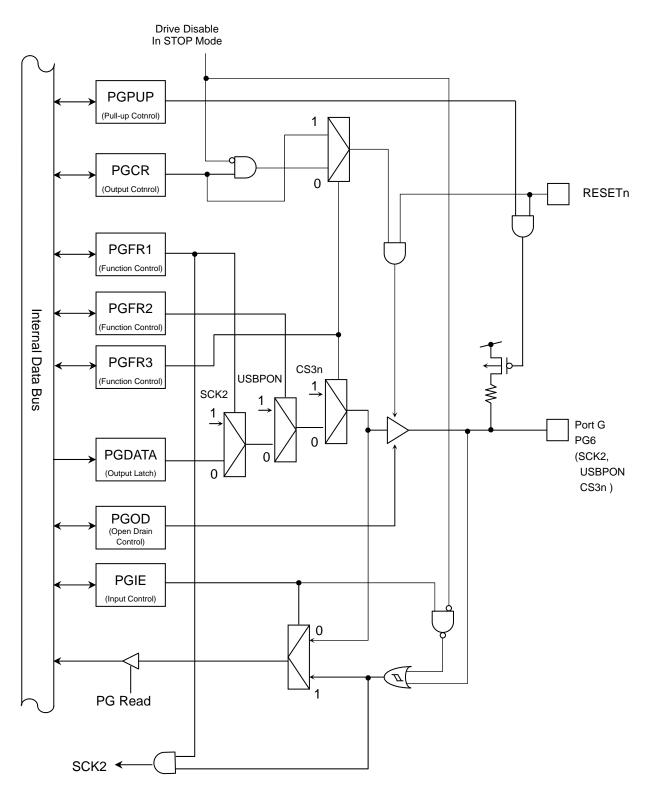

|          | 104          | PG6<br>SCK2<br>USBPON<br>CS3n    | I/O<br>I/O<br>O<br>O   | I/O port<br>Inputting and outputting a clock if the<br>serial bus interface operates in the SIO<br>mode.<br>USB PON output<br>Chip select pin           |

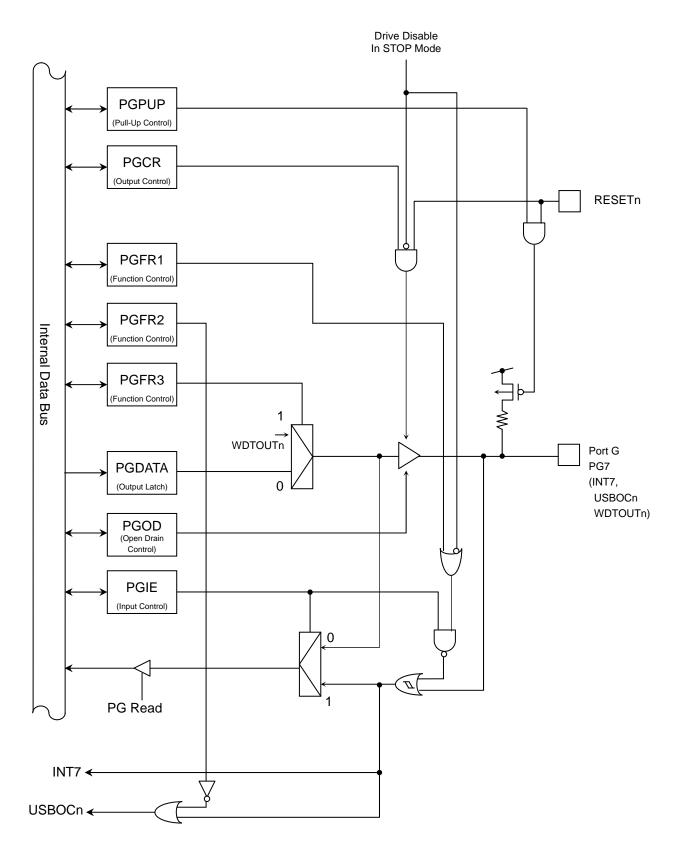

|          | 105          | PG7<br>INT7<br>USBOCn<br>WDTOUTn | /O<br> <br> <br> <br>0 | I/O port<br>Interrupt request pin<br>USB OverCurrent input<br>Watch Dog Timer output                                                                    |

Table2.2.1 Pin Names and Functions Sorted by Pin (7/10)

| Туре | # of<br>Pins | Pin Name              | Input/<br>Output | Function                                                                                                                                               |

|------|--------------|-----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

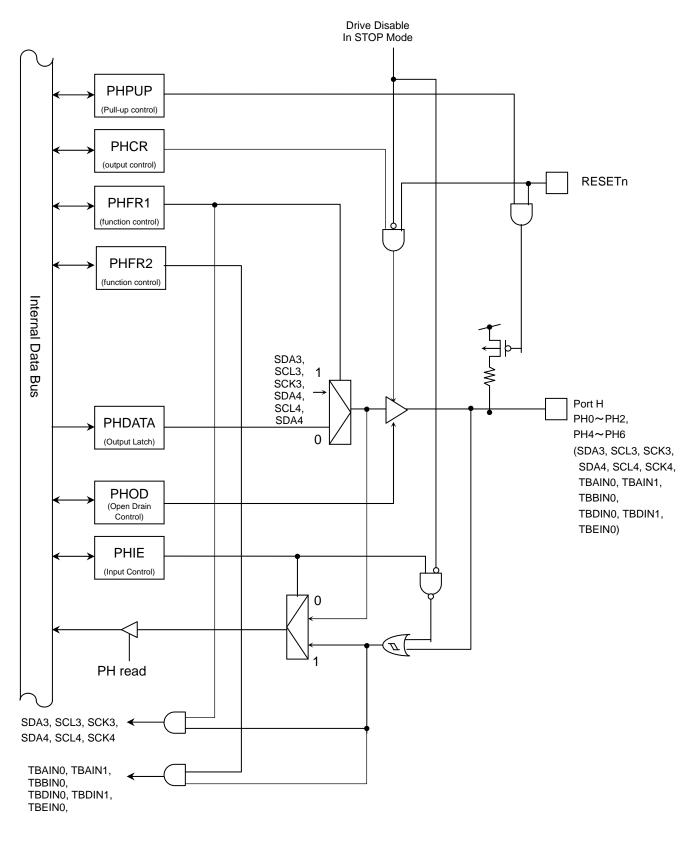

|      | 106          | PH0<br>SDA3<br>TBAIN0 | I/O<br>I/O<br>I  | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : data pin<br>-in the SIO mode: data pin Inputting the<br>timer B capture trigger |

|      | 107          | PH1<br>SCL3<br>TBAIN1 | I/O<br>I/O<br>I  | /O port<br>If the serial bus interface operates<br>-in the I2C mode : clock pin<br>-in the SIO mode: data pin<br>Inputting the timer B capture trigger |

|      | 108          | PH2<br>SCK3<br>TBBIN0 | I/O<br>I/O<br>I  | I/O port<br>Inputting and outputting a clock<br>if the serial bus interface operates<br>in the SIO mode.<br>Inputting the timer B capture trigger      |

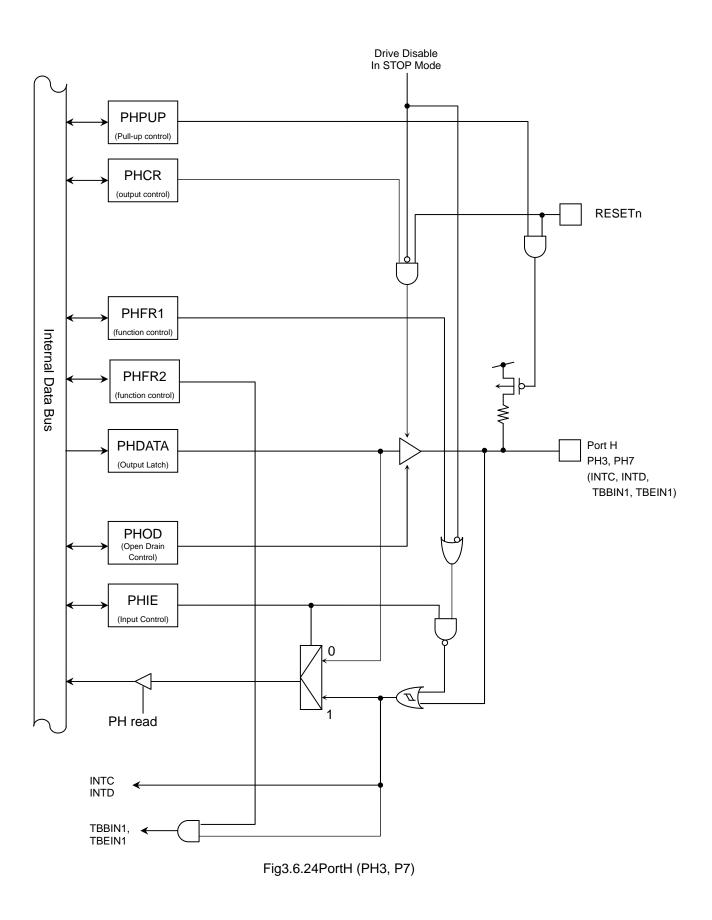

|      | 109          | PH3<br>INTC<br>TBBIN1 | I/O<br>I<br>I    | I/O port<br>Interrupt request pin<br>Inputting the timer B capture trigger                                                                             |

|      | 110          | PH4<br>SDA4<br>TBDIN0 | I/O<br>I/O<br>I  | I/O port<br>If the serial bus interface operates<br>-in the I2C mode : data pin<br>-in the SIO mode: data pin Inputting the<br>timer B capture trigger |

|      | 111          | PH5<br>SCL4<br>TBDIN1 | I/O<br>I/O<br>I  | /O port<br>If the serial bus interface operates<br>-in the I2C mode : clock pin<br>-in the SIO mode: data pin<br>Inputting the timer B capture trigger |

|      | 112          | PH6<br>SCK4<br>TBEIN0 | I/O<br>I/O<br>I  | I/O port<br>Inputting and outputting a clock<br>if the serial bus interface operates<br>in the SIO mode.<br>Inputting the timer B capture trigger      |

|      | 113          | PH7<br>INTD<br>TBDIN1 | I/O<br>I<br>I    | I/O port<br>Interrupt request pin<br>Inputting the timer B capture trigger                                                                             |

Table2.2.1 Pin Names and Functions Sorted by Pin (8/10)

| Туре     | # of<br>Pins | Pin Name       | Input/<br>Output | Functions Solied by Pin (9/10)                                                                                                       |

|----------|--------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| PS       | 114          | REGVCC         | —                | Power supply pin                                                                                                                     |

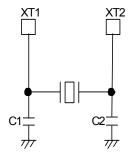

|          | 115          | XT1            | 1                | Connected to a low-speed oscillator.                                                                                                 |

| Clock    | 116          | XT2            | 0                | Connected to a low-speed oscillator.                                                                                                 |

| PS       | 117          | CVCC           | _                | Power supply pin                                                                                                                     |

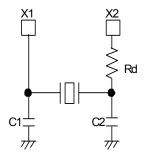

| Clock    | 118          | X1             |                  | Connected to a high-speed oscillator.                                                                                                |

| PS       | 119          | CVSS           | _                | GND pin                                                                                                                              |

| Clock    | 120          | X2             | 0                | Connected to a high-speed oscillator.                                                                                                |

|          | 121          | DVCC           | —                | Power supply pin                                                                                                                     |

| PS       | 122          | DVSS<br>REGVSS | _                | GND pin                                                                                                                              |

|          | 123          | D+             | I/O              | USB D+ Pin                                                                                                                           |

| Function | 124          | D-             | I/O              | USB D- Pin                                                                                                                           |

| FUNCTION | 125          | NMIn           | I                | Non-maskable interrupt<br>In case no use, fix to High level.                                                                         |

|          | 126          | TEST1          | —                | OPEN or fix to Low level.                                                                                                            |

| TEST     | 127          | TEST2          | —                | OPEN or fix to Low level.                                                                                                            |

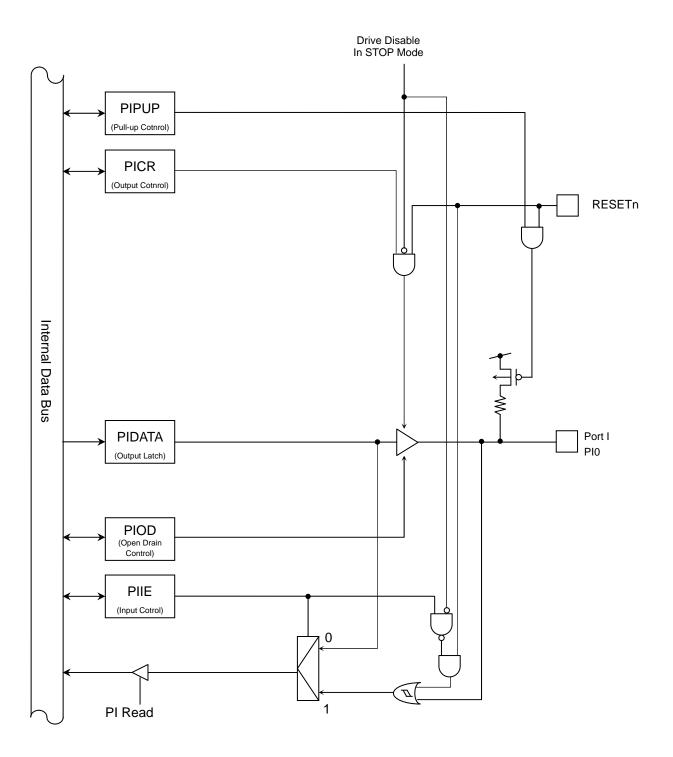

| Function | 128          | PI0            | I/O              | I/O port<br>While "0" inputs RESET pin, PI0 enables<br>input and pull-up. During a reset, "Low<br>level" should not be input to PI0. |

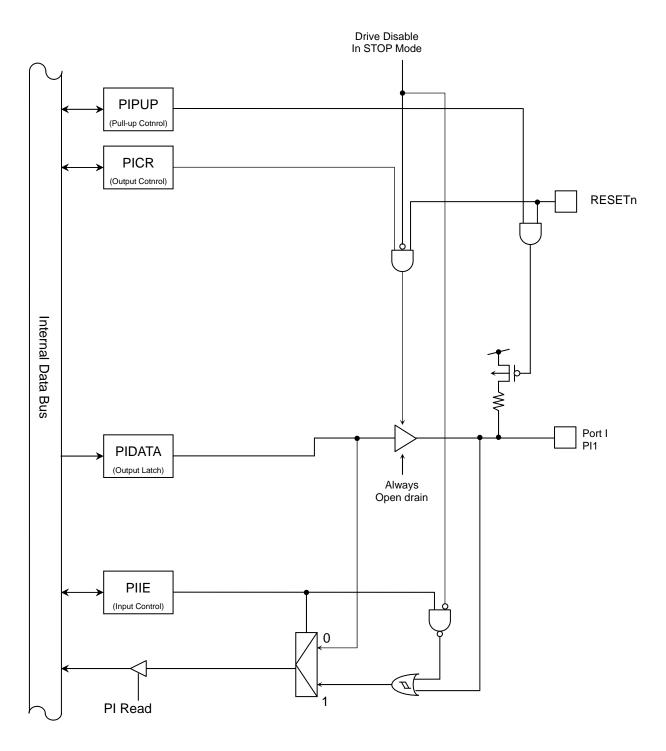

|          | 129          | PI1            | I/O              | I/O port (Note 3)                                                                                                                    |

| PS       | 130          | AVCC           | -                | Power supply pin                                                                                                                     |

| Туре     | # of<br>Pins      | Pin Name | Input/<br>Output | Function                                  |  |  |

|----------|-------------------|----------|------------------|-------------------------------------------|--|--|

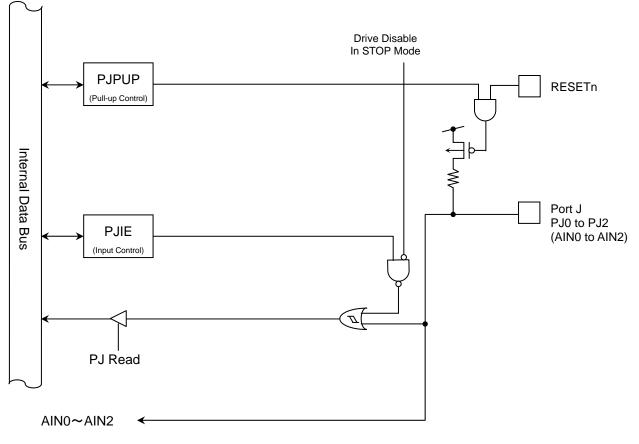

|          |                   | PJ0      |                  | Input port                                |  |  |

|          | 131               | ANO      |                  | Analog input                              |  |  |

|          |                   | PJ1      | 1                | Input port                                |  |  |

|          | 132               | AN1      | 1                | Analog input                              |  |  |

|          | 400               | PJ2      | 1                | Input port                                |  |  |

|          | 133               | AN2      | I                | Analog input                              |  |  |

|          |                   | PJ3      | I                | Input port                                |  |  |

|          | 134               | AN3      | I                | Analog input                              |  |  |

|          |                   | ADTRGn   |                  | Exteral trigger regquest for AD converter |  |  |

|          |                   | PJ4      | I                | Input port                                |  |  |

|          | 135               | AN4      | I                | Analog input                              |  |  |

|          |                   | KWUP0    |                  | Key on Wakeup input                       |  |  |

|          |                   | PJ5      | I                | Input port                                |  |  |

|          | 136               | AN5      | I                | Analog input                              |  |  |

|          |                   | KWUP1    |                  | Key on Wakeup input                       |  |  |

|          |                   | PJ6      | I                | Input port                                |  |  |

| Function | 137               | AN6      | 1                | Analog input                              |  |  |

|          |                   | KWUP2    | 1                | Key On Wakeup input                       |  |  |

|          |                   | PJ7      | 1                | Input port                                |  |  |

|          | 138               | AN7      | 1                | Analog input                              |  |  |

|          |                   | KWUP3    | 1                | Key On Wakeup input                       |  |  |

|          | 139               | PK0      | 1                | Input port                                |  |  |

|          |                   | AN8      | 1                | Analog input                              |  |  |

|          | 140<br>141<br>142 | PK1      | 1                | Input port                                |  |  |

|          |                   | AN9      | 1                | Analog input                              |  |  |

|          |                   | PK2      |                  | Input port                                |  |  |

|          |                   | AN10     | 1                | Analog input                              |  |  |

|          |                   | PK3      | 1                | Input port                                |  |  |

|          | 143               | AN11     | 1                | Analog input                              |  |  |

|          |                   | PK4      | 1                | Input port                                |  |  |

|          |                   | AN12     |                  | Analog input                              |  |  |

|          | 144               | PK5      |                  | Input port                                |  |  |

|          |                   | AN13     | I                | Analog input                              |  |  |

Table2.2.1 Pin Names and Functions Sorted by Pin (10/10)

| (Note 1) | MODE pin must be fix to Low-level.                                                                                             |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| (Note 2) | VREFH/AVCC pin must be connected to power supply and AVSS pin must be connected to GND. even if the A/D converter is not used. |

| (Note 3) | Nch open drain port.                                                                                                           |

# 2.3 Pin Names and Power Supply Pins

|          | Power      |

|----------|------------|

| Pin name | supply     |

| PA       | DVCC       |

| PB       | DVCC       |

| PC       | DVCC       |

| PD       | DVCC       |

| PE       | DVCC       |

| PF       | DVCC       |

| PG       | DVCC       |

| PH       | DVCC       |

| PI       | DVCC       |

| PJ       | AVCC, AVSS |

| PK       | AVCC, AVSS |

| PL       | DVCC       |

| PM       | DVCC       |

| PN       | DVCC       |

| PO       | DVCC       |

| PP       | DVCC       |

| X1, X2   | CVCC, CVSS |

| XT1, XT2 | DVCC       |

| RESETn   | DVCC       |

| NMIn     | DVCC       |

| MODE     | DVCC       |

Table 2.3.1 Pin Names and Power Supplies

# 2.4 Pin Numbers and Power Supply Pins

| Table2.4.1 Pin Numbers and | Power Supplies |

|----------------------------|----------------|

|----------------------------|----------------|

| Power<br>supply | Pin number  | Voltage range                                                                                                         |

|-----------------|-------------|-----------------------------------------------------------------------------------------------------------------------|

| DVCC            | 47, 89, 121 |                                                                                                                       |

| REGVCC          | 114         | 3.0V~3.6V (when operating USBHC)                                                                                      |

| CVCC            | 117         | 2.7V~3.6V (when stopping USBHC)                                                                                       |

| AVCC            | 130         |                                                                                                                       |

| VREFH           | 4           | 3.0V~3.6V (when operating USBHC)<br>2.7V~3.6V (when stopping USBHC)<br>A/D converter with a reference power<br>supply |

# 3. Operation

This section describes the basic components, functions and operation of the TMPM322F10FG.

# 3.1 System

#### 3.1.1 Processor Core

The TMPM322F10FG has a high-performance 32-bit processor core (the ARM Cortex-M3 processor core). For information on the operations of this processor core, please refer to the "Cortex-M3 Technical Reference Manual" issued by ARM Limited. This chapter describes the functions unique to the TMPM322F10FG that are not explained in that document.

#### 3.1.2 Core Information

The following table shows the revision of the processor core in the TMPM322F10FG. For further information on core revision, see the documents issued by ARM Limited.

| Product Name | Core Revision |

|--------------|---------------|

| TMPM322F10FG | R2p0-00rel0   |

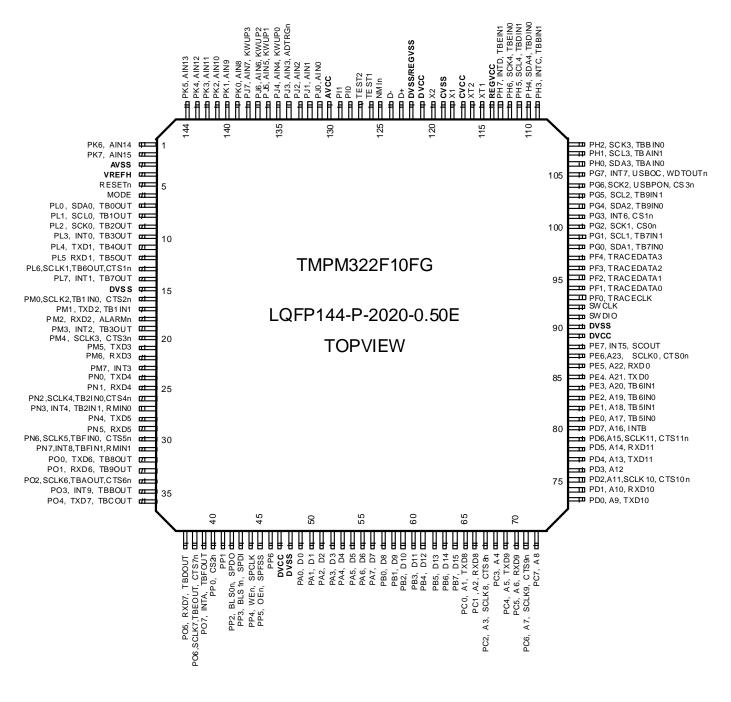

The Cortex-M3 core has the optional blocks. The optional blocks of the revision r2p0 are  $\text{ETM}^{\text{TM}}$ , MPU and WIC. Not MPU, WIC but ETM is contained in the TMPM322F10FG.

### 3.1.3 Core Block Diagram

The following shows the diagram of the Cortex-M3 core:

Figure 3.1.1 Cortex-M3 Core Block Diagram

#### 3.1.4 Core Configuration

The following shows the Cortex-M3 core configuration selected in the TMPM322F10FG:

| Configuration                     | Description                                        |  |  |  |

|-----------------------------------|----------------------------------------------------|--|--|--|

| Number of interrupts              | 100 channels<br>(except Watch Dog Timer Interrupt) |  |  |  |

| Interrupt priority level (Note 1) | 4bit (16 levels)                                   |  |  |  |

| MPU (Memory Protection Unit)      | None                                               |  |  |  |

| WIC                               | None                                               |  |  |  |

|                                   | SW-DP only                                         |  |  |  |

| SW / SWJ-DP                       | (SWD connection only)                              |  |  |  |

| ETM (Embedded Trace Macrocell)    | Installed                                          |  |  |  |

| Endian                            | Little endian                                      |  |  |  |

Table3.1.1 Core Cofiguration

(Note1) Refet to Section5 Exceptions of Cortex-M3 Technical Reference Manual.

#### 3.1.5 Exceptions

The following list shows the Cortex-M3 exception types:

Thethe subsequent areas are the vector areas unique to the TMPM322F10FG. For more information, refer to section 3.5, "Interrupts."

| Table 3.1.2 | List of Exceptions |

|-------------|--------------------|

|-------------|--------------------|

| Exception     | Address     | Remarks                  |

|---------------|-------------|--------------------------|

| Exception     | Address     | Remarks                  |

| Top of Stack  | 0x0000_0000 | Beginning of a stack     |

| Reset         | 0x0000_0004 | Reset                    |

| _             | 0x0000_0008 | Reserved                 |

| Hard Fault    | 0x0000_000C | Hard fault               |

| MPU Fault     | 0x0000_0010 | Memory management        |

| Bus Fault     | 0x0000_0014 | Bus fault                |

| Usage Fault   | 0x0000_0018 | Usage fault              |

| -             | 0x0000_001C | Reserved                 |

| _             | 0x0000_0020 | Reserved                 |

| -             | 0x0000_0024 | Reserved                 |

| _             | 0x0000_0028 | Reserved                 |

| SVCall        | 0x0000_002C | Supervisor call          |

| Debug Monitor | 0x0000_0030 | Debug monitor            |

| PendSV        | 0x0000_0038 | Software pending request |

| SysTick       | 0x0000_003C | SysTick interrupt        |

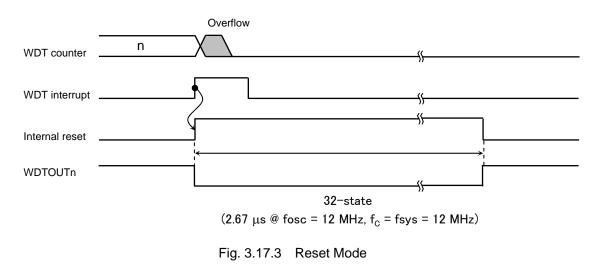

#### 3.1.6 Reset

The TMPM322F10 has three reset sources: an external reset pin, WDT and SYSRESETREQ. For reset from the WDT, refer to the chapter on the WDT. For reset from SYSRESETREQ, refer to "Cortex-M3 Technical Reference Manual".

Note : Do not reset with <SYSRESETREQ> in SLOW mode.

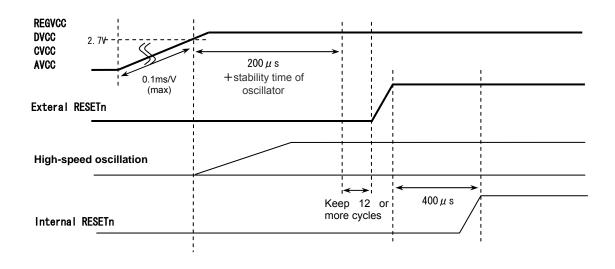

#### 3.1.6.1 Cold Reset

The power-on sequence must include the time for the internal regulator and oscillator to be stable. In the TMPM322F10, the internal regulator requires at least 200  $\mu$ s to be stable. The time required to achieve stable oscillation varies with system. At cold reset, the external reset pin must be kept low for a duration of time sufficiently long enough for the internal regulator and oscillator to be stable. After the external reset (RESETn) signal is released, the internal reset signal remains asserted for a further 400  $\mu$ s.

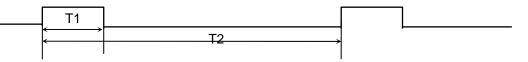

Fig.3.1.2 shows the power-on sequence.

Fig.3.1.2 Cold Reset Sequence

# (Note 1) Turn on the power while the RESETn pin is fixed to "L". Release the RESETn pin while all the power supplies are stabilized within operating voltage.

#### 3.1.6.2 Warm Reset

#### 3.1.6.2.1 Reset Period

As a precondition, ensure that the power supply voltage is within the operating range and the internal high-frequency oscillator is providing stable oscillation. To reset the TMPM322F10, assert the RESETn signal (active low) for a minimum duration of 12 system clocks. After the external reset (RESETn) signal is released, the internal reset signal remains asserted for a further 400 µs.

#### 3.1.6.2.2 After Reset

A warm reset initializes the majority of the Cortex-M3 processor core's system control registers and internal I/O registers. Registers that are only initialized by a cold reset are registers related to the processor core's system debug components (FPB, DWT, ITM), the clock generator's reset flag and the Flash security bit.

After reset, the PLL multiplication circuit is inactive and must be enabled in the CGPLLSEL register if needed.

When the reset exception handling is completed, the program branches to the reset interrupt service routine.

#### (Note 1) The reset operation may alter the internal RAM state.

#### 3.1.7 RAMWAIT

A part of RAM(0x2000\_4000 to 0x2000\_FFFF) is set to "1WAIT" after reset is released. For performance improvement, set to "0WAIT".

### 3.1.7.1 RAMWAIT Register

|               |             |              | RA | MWAIT R | esister      |       |    |    |                    |

|---------------|-------------|--------------|----|---------|--------------|-------|----|----|--------------------|

|               |             | 31           | 30 | 29      | 28           | 27    | 26 | 25 | 24                 |

|               | bit Symbol  | -            | -  | -       | -            | -     | -  | -  | -                  |

| RAMWAIT       | Read/Write  | R            |    |         |              |       |    |    |                    |

| (0x41FF_F058) | After reset | 0            |    |         |              |       |    |    |                    |

|               | Function    |              |    |         | "0"is        | read. |    |    |                    |

|               |             | 23           | 22 | 21      | 20           | 19    | 18 | 17 | 16                 |

|               | bit Symbol  | -            | -  | -       | -            | -     | -  | -  | -                  |

|               | Read/Write  |              |    |         | F            | र     |    |    |                    |

|               | After reset | 0            |    |         |              |       |    |    |                    |

|               | Function    |              |    |         | "0"is        | read. |    |    |                    |

|               |             | 15           | 14 | 13      | 12           | 11    | 10 | 9  | 8                  |

|               | bit Symbol  | -            | -  | -       | -            | -     | -  | -  | -                  |

|               | Read/Write  | R            |    |         |              |       |    |    |                    |

|               | After reset | 0            |    |         |              |       |    |    |                    |

|               | Function    | "O" is read. |    |         |              |       |    |    |                    |

|               |             | 7            | 6  | 5       | 4            | 3     | 2  | 1  | 0                  |

|               | bit Symbol  | -            | -  | -       | -            | -     | -  | -  | RAM1WAI            |

|               |             |              |    |         |              |       |    |    | Т                  |

|               | Read/Write  | R            |    |         |              |       |    |    | R/W<br>1           |

|               | After reset | 0            |    |         |              |       |    |    |                    |

|               |             |              |    |         | "0" is read. |       |    |    | RAMWAIT            |

|               | Function    |              |    |         |              |       |    |    | setting            |

|               |             |              |    |         |              |       |    |    | 1:1WAIT<br>0:0WAIT |

<Bit 0><RAM1WAIT>

: Specifies the RAMWAIT.

# 3.2 Debug Interface

#### 3.2.1 Specification Overview

The TMPM322F10FG contains the SWD (Serial Wire Debug) unit as the debugging interface for connection to the ICE (In-Circuit Emulator), and the ETM (Embedded Trace Macrocell) unit for tracing and outputting internal programs. ETM outputs signals to dedicated pins (TRACEDATA[0] to [3]) through the TPIU (Trace Port Interface Unit) in the microprocessor.

For more information on SWD, ETM, and TPIU, please refer to the documents published by ARM.

Note that the TMPM322F10FG does not support connections based on the JTAG (Joint Test Action Group) Standards. Use SWD-compatible tools when connecting the TMPM322F10FG to the ICE.

#### 3.2.2 Features of SWD

SWD supports the two-pin Serial Wire Debug Port (SWCLK, SWDIO)

#### 3.2.3 Features of ETM

ETM supports four data signal pins (TRACEDATA[0]-[3]), one clock signal pin (TRACECLK).

#### 3.2.4 Pin Functions

The Trace output pins(PF0 to PF4) of debug interface pins can also be used as general-purpose ports.

After reset, the Trace output pins are configured as general-purpose ports. These pins need to be programmed as required.

The table below summarizes the debug interface pin functions and related port settings after reset.

| Pin Number | Port<br>(Bit Name) | Debug Function | Port Settings after Reset   |  |  |

|------------|--------------------|----------------|-----------------------------|--|--|

| 91         | -                  | SWDIO          | Debug pin(always Pull-Up)   |  |  |

| 92         | -                  | SWCLK          | Debug pin(always Pull-Down) |  |  |

| 93         | PF0                | TRACECLK       | general-purpose port        |  |  |

| 94         | PF1                | TRACEDATA0     | general-purpose port        |  |  |

| 95         | PF2                | TRACEDATA1     | general-purpose port        |  |  |

| 96         | PF3                | TRACEDATA2     | general-purpose port        |  |  |

| 97         | PF4                | TRACEDATA3     | general-purpose port        |  |  |

# 3.2.5 Conection with a Debug Tool

For how to connect a debug tool, refer to the method recommended by each manufacturer.

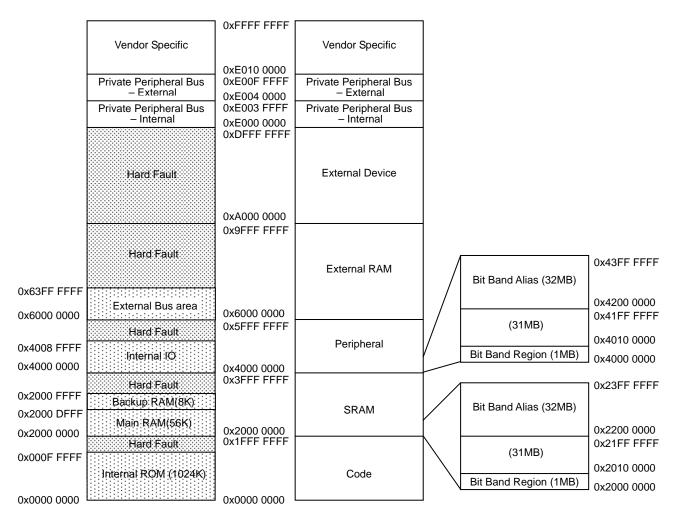

# 3.3 Memory Map

#### 3.3.1 Memory Map

The memory maps for the TMPM322F10FG is based on the ARM Cortex-M3 processor core memory map. The internal ROM, internal RAM and internal I/O of the TMPM322F10FG is mapped to the code, SRAM and peripheral regions of the Cortex-M3 respectively. The SRAM and internal I/O regions are all included in the bit-band region.

The CPU register region is the processor core's internal register region.

For more information on each region, see the "Cortex-M3 Technical Reference Manual".

Note that access to regions indicated as "Fault" causes a memory fault if memory faults are enabled or a hard fault if memory faults are disabled. Do not access the vendor-specific region.

### 3.3.2 Memory Map of TMPM322F10

Fig.3.3.1 shows the memory map of the TMPM322F10FG.

TMPM322F10FG

Cortex-M3

Fig.3.3.1 Memory Map (TMPM322F10FG)

A part of RAM(0x2000\_4000 to 0x2000\_FFFF) is set to "1WAIT" after reset is released. For performance improvement, set to "0WAIT". For detail , refer to 3.1.7 RAMWAIT.

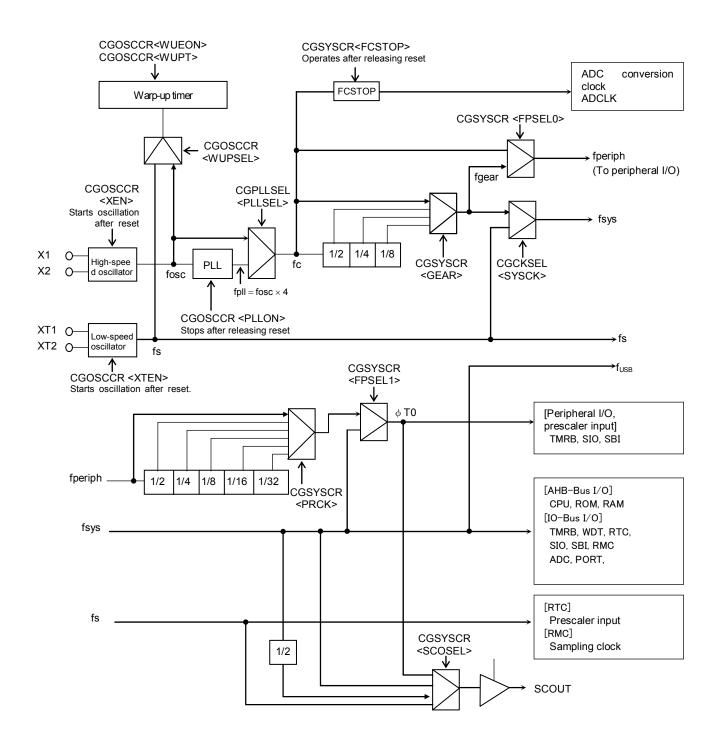

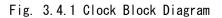

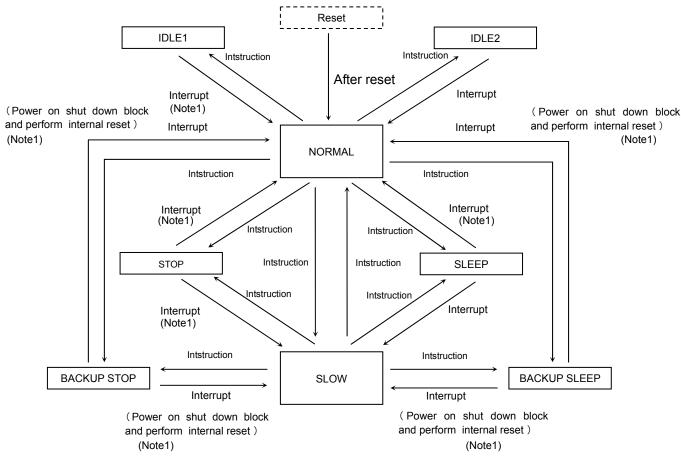

# 3.4 Clock/Mode Control

#### 3.4.1 Features

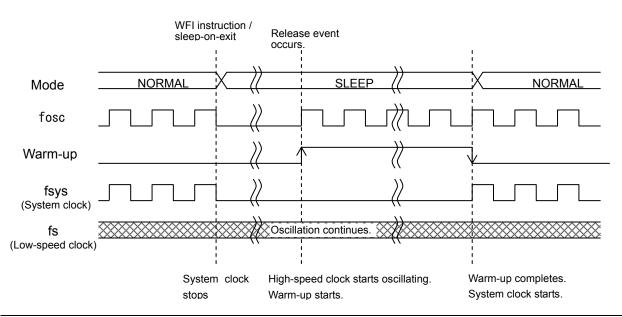

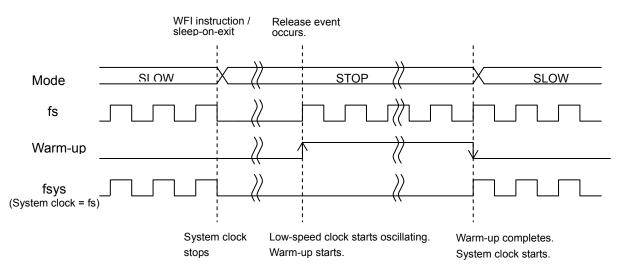

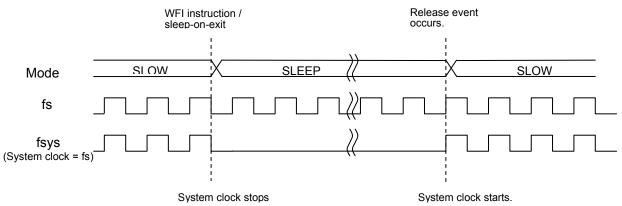

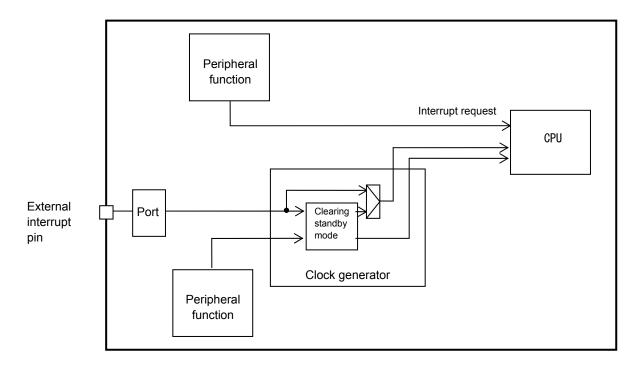

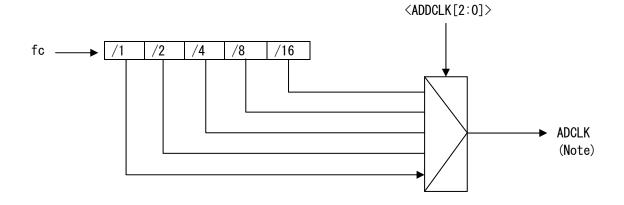

The clock/mode control block enables to select clock gear, prescaler clock and warm-up of the PLL (including clock multiplication circuit) and oscillator.

The low power consumption mode can reduce power consumption.

This chapter describes how to control clocks, clock operating modes and mode transitions.

The clock/mode control block has the following functions:

- Controls the system clock.

- Controls the prescaler clock.

- Controls the PLL multiplication circuit.

- Controls the warm-up timer.

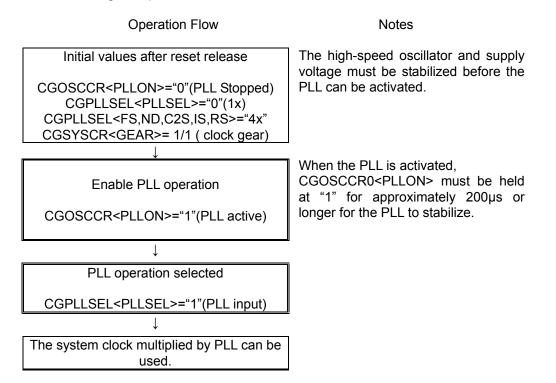

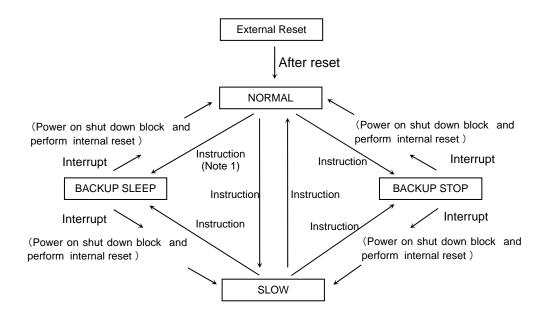

In addition to NORMAL mode, the TMPM322F10 can operate in various types of low power mode to reduce power consumption according to its usage conditions.

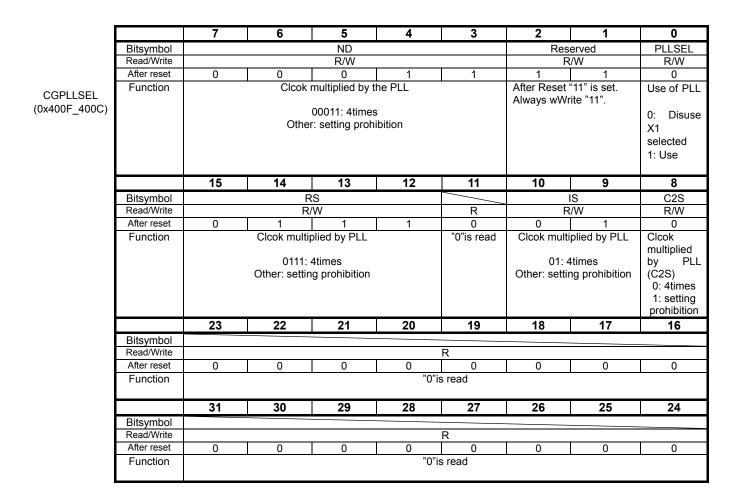

#### 3.4.2 Registers

#### 3.4.2.1 Register List

Table 3.4.1 shows registers and addresses of the clock generator.

Register name Address CGSYSCR 400F\_4000H System control register Oscillation control register 400F\_4004H CGOSCCR Standby control register 400F\_4008H CGSTBYCR PLL selection register CGPLLSEL 400F\_400CH System clock selection register CGCKSEL 400F\_4010H

Table 3.4.1 Registers of Clock Generator

#### 3.4.2.2 System Control Register

|                                                                                                                                                                     |                                                                                                                                                                     | 7            | 6             | 5            | 4            | 3            | 2                           | 1               | 0          |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|--------------|--------------|--------------|-----------------------------|-----------------|------------|--|

|                                                                                                                                                                     | Bitsymbol                                                                                                                                                           |              |               |              |              |              |                             | GEAR            |            |  |

| CGSYSCR                                                                                                                                                             | Read/Write                                                                                                                                                          |              |               | R            |              |              |                             | R/W             |            |  |

| (0x400F_4000)                                                                                                                                                       | After reset                                                                                                                                                         | 0            | 0             | 0            | 0            | 0            | 0                           | 0               | 0          |  |

|                                                                                                                                                                     | Function                                                                                                                                                            | "0" is read. |               |              |              |              | High-speed a                | clock (fc) gear |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               |              | 000: fc      | 100: fc/2    |                             |                 |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               |              |              |              | 001: reserve                | ed 101: fc/4    | 1          |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               |              |              |              | 010: reserve                |                 | 3          |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               |              |              |              | 011: reserved 111: Reserved |                 |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | 15           | 14            | 13           | 10           | 9            | 8                           |                 |            |  |

|                                                                                                                                                                     | Bitsymbol                                                                                                                                                           |              |               | FPSEL1       | 12<br>FPSEL0 | 11           |                             | PRCK            |            |  |

|                                                                                                                                                                     | Read/Write                                                                                                                                                          | F            | ٦             | R/W          | R/W          | R            |                             | R/W             |            |  |

|                                                                                                                                                                     | After reset                                                                                                                                                         | 0            | 0             | 0            | 0            | 0            | 0                           | 0               | 0          |  |

|                                                                                                                                                                     | Function                                                                                                                                                            | "0" is read. | •             | fperiph      | fperiph      | "0" is read. | Prescaler cl                | ock             |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               | select1      | select 0     |              | 000: fperiph                | /1 100: fperi   | ph/16      |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               | (Note)       |              |              | 001: fperiph                | •               | •          |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               | 0:depend     | 0: fgear     |              | 010: fperiph                | •               | •          |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               | on FPSEL0    | 1: fc        |              | 011: fperiph                |                 | erved      |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               | setting      |              |              |                             |                 |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     |              |               | 1: fs        |              |              |                             |                 |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | 23           | 22            | 21           | 20           | 19           | 18                          | 17              | 16         |  |

|                                                                                                                                                                     | Bitsymbol                                                                                                                                                           | USBHRES      |               |              | FCSTOP       |              |                             |                 | OSEL       |  |

|                                                                                                                                                                     | Read/Write                                                                                                                                                          | R/W          |               | ۲            | R/W          | I            | ۲                           | R/W             | R/W        |  |

|                                                                                                                                                                     | After reset                                                                                                                                                         | 0            | 0             | 0            | 0            | 0            | 0                           | 0               | 1          |  |

|                                                                                                                                                                     | Function                                                                                                                                                            | USB          | "0" is read.  |              | A/D          | "0" is read. |                             | SCOUT out       | put        |  |

|                                                                                                                                                                     |                                                                                                                                                                     | HOST         |               |              | converter    |              |                             | 00:fs           |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | Controller   |               |              | clock        |              |                             | 01:fsys/2       |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | RESET        |               |              |              |              |                             | 10:fsys         |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | 0:RESET      |               |              | 0: supply    |              |                             | 11:φΤ0          |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | release      |               |              | 1: stop      |              |                             |                 |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | 1:RESET      |               |              |              |              |                             |                 |            |  |

|                                                                                                                                                                     |                                                                                                                                                                     | 31           | 30            | 29           | 28           | 27           | 26                          | 25              | 24         |  |

|                                                                                                                                                                     | Bitsymbol                                                                                                                                                           |              |               |              |              |              |                             |                 |            |  |

|                                                                                                                                                                     | Read/Write                                                                                                                                                          |              |               |              |              | R            |                             |                 |            |  |

|                                                                                                                                                                     | After reset                                                                                                                                                         |              |               |              |              | 0            |                             |                 |            |  |

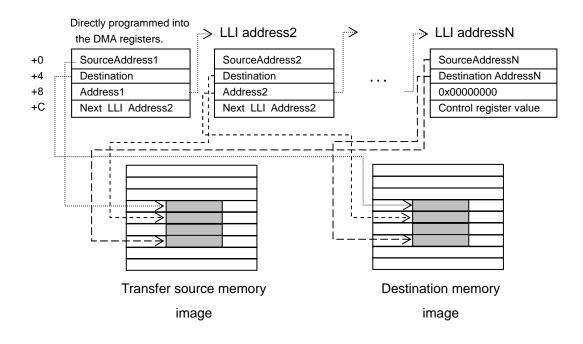

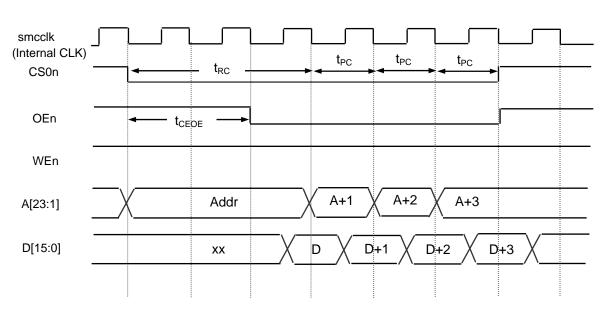

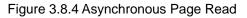

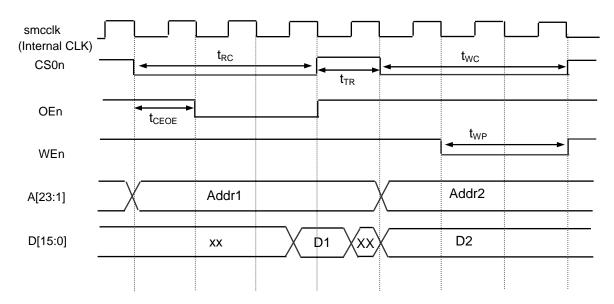

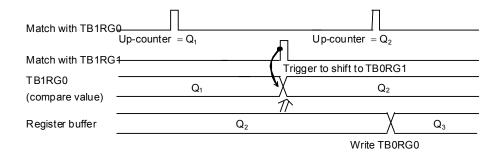

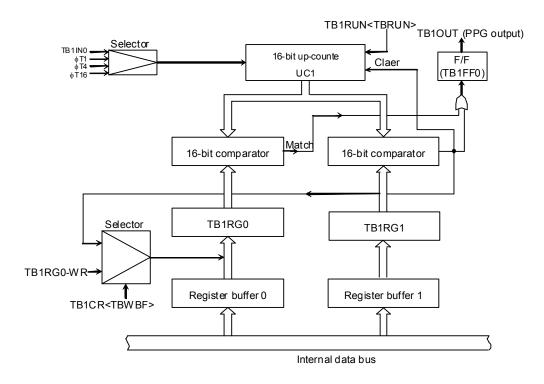

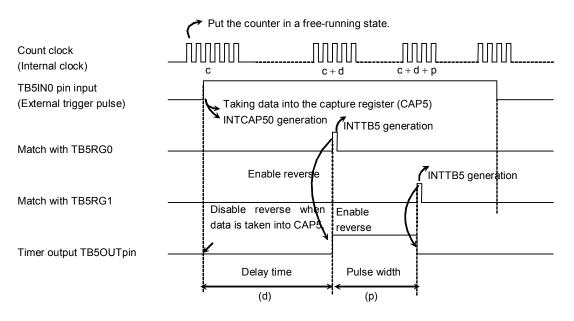

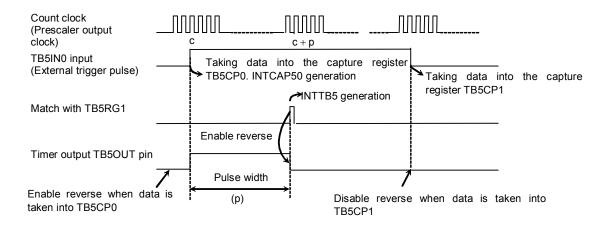

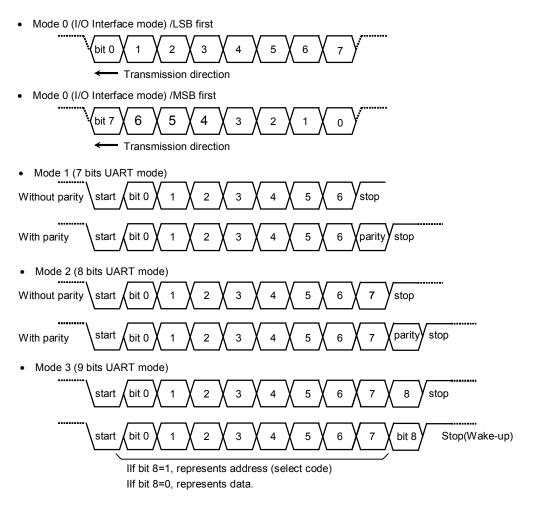

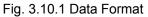

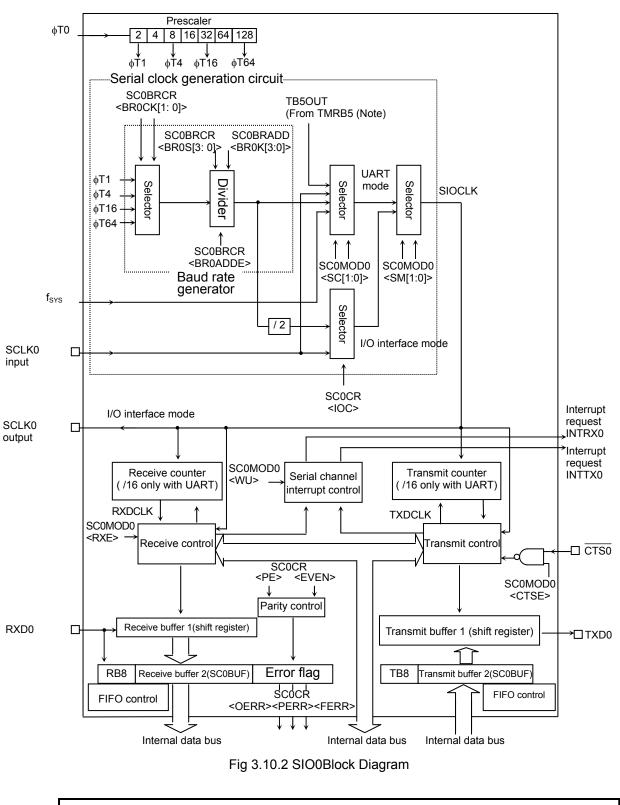

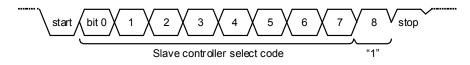

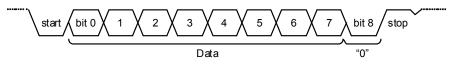

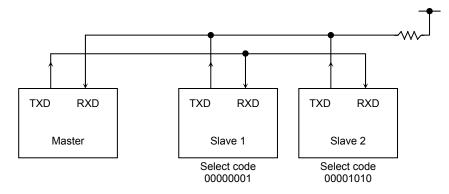

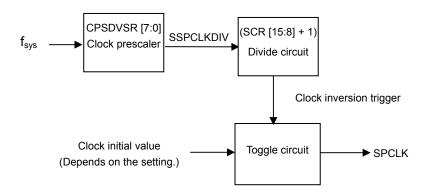

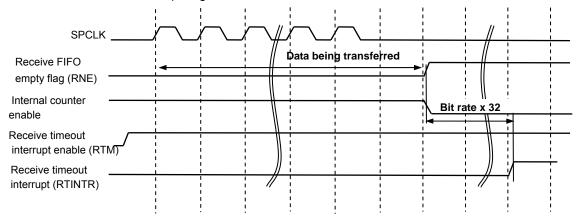

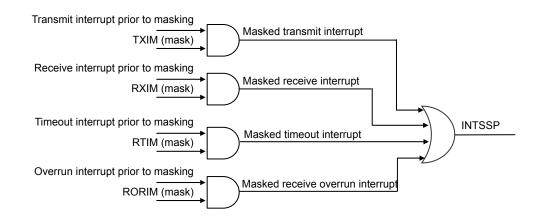

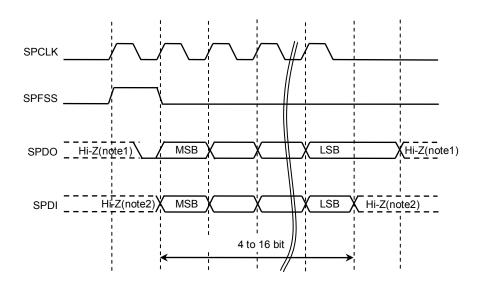

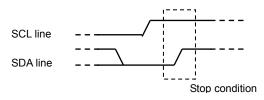

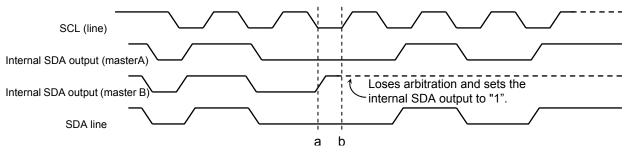

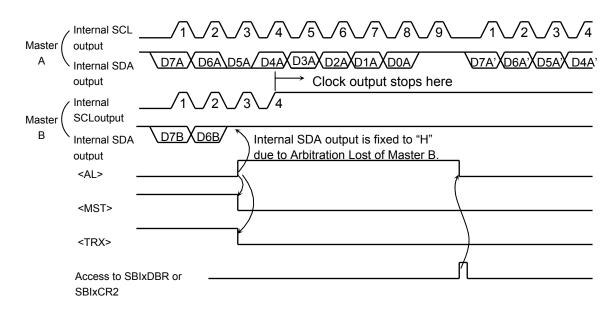

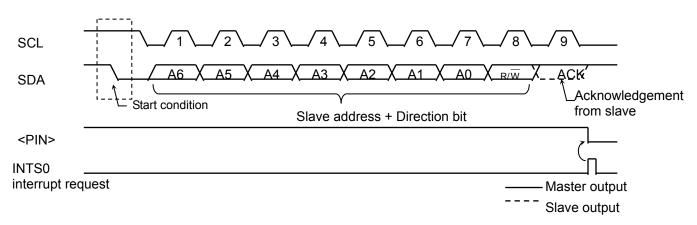

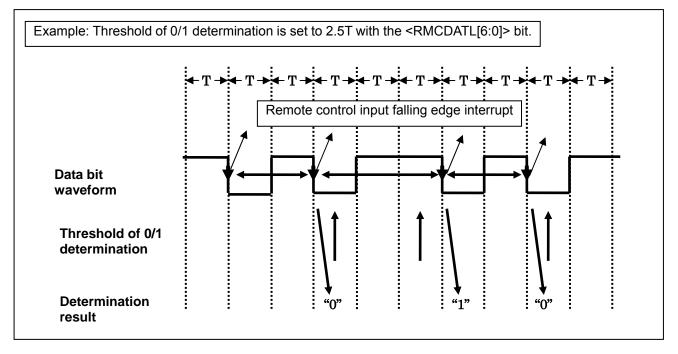

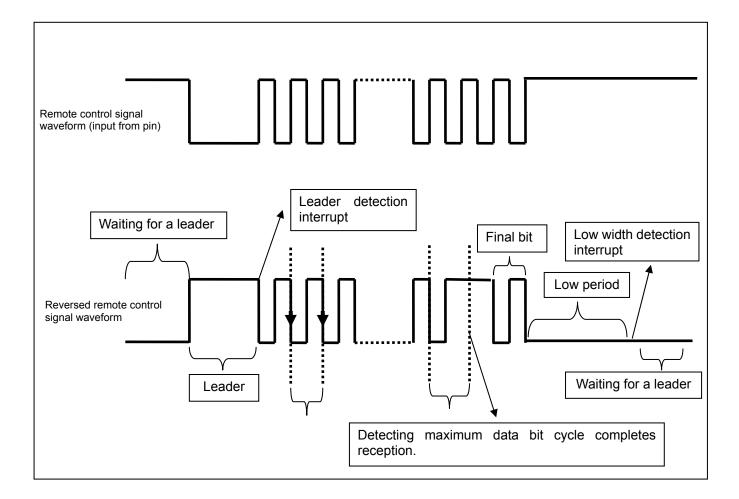

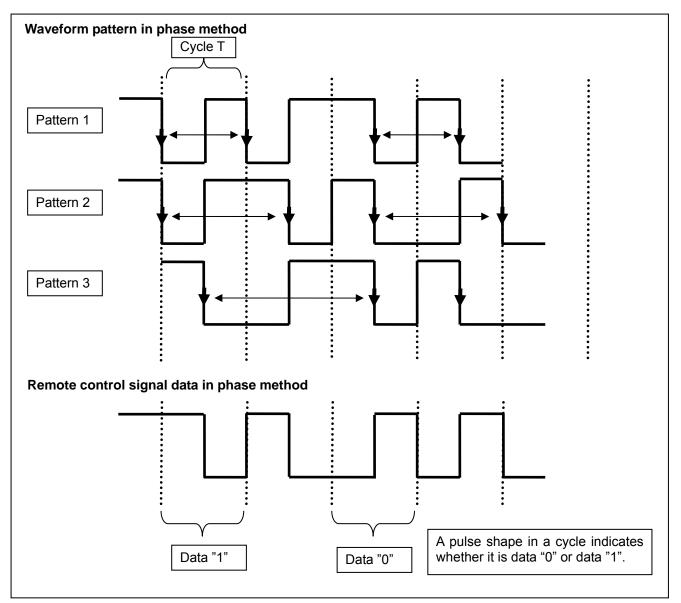

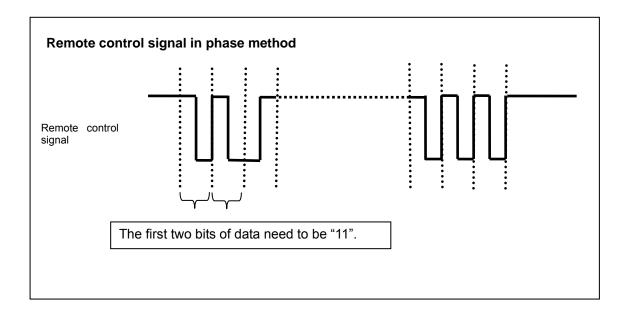

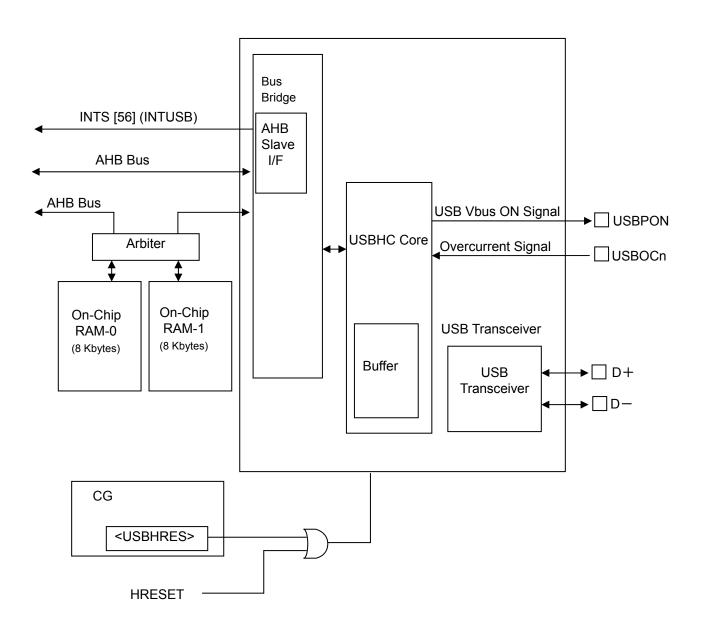

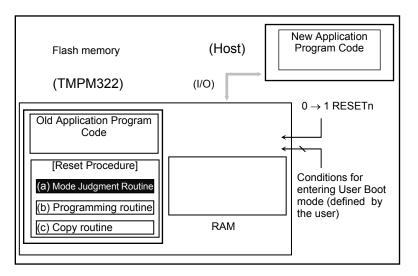

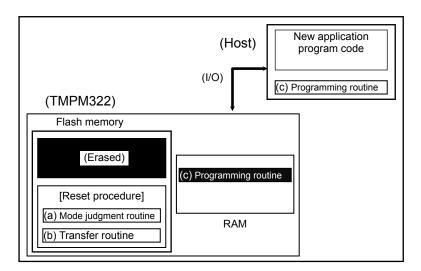

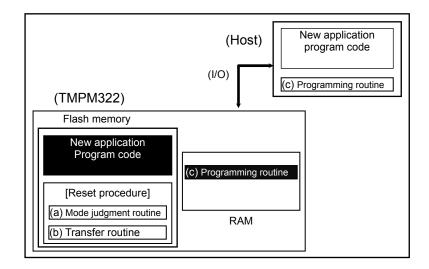

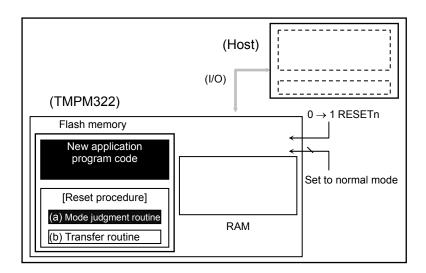

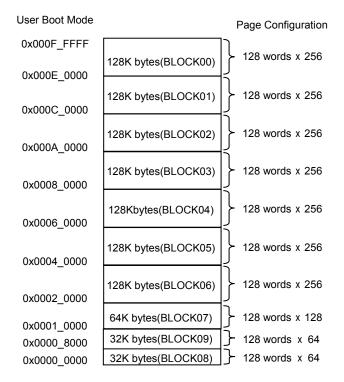

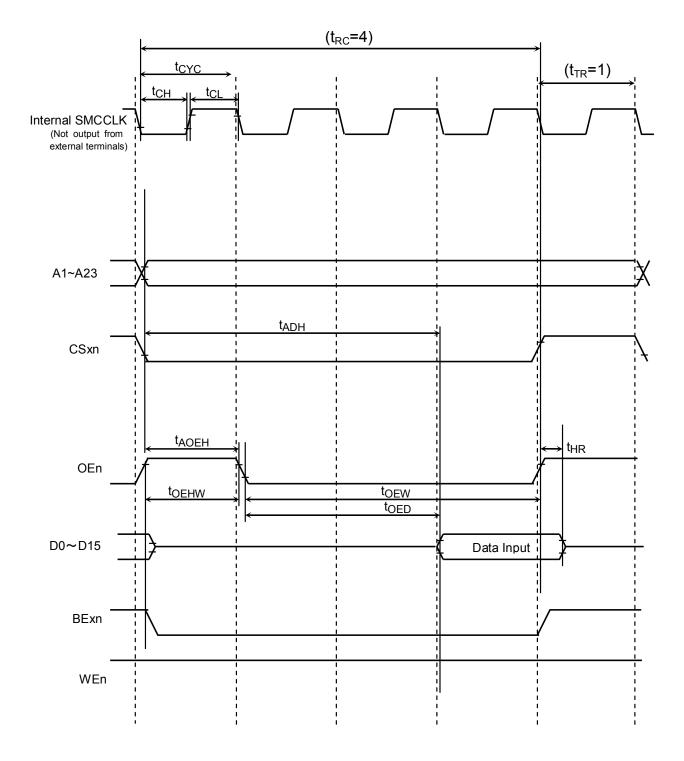

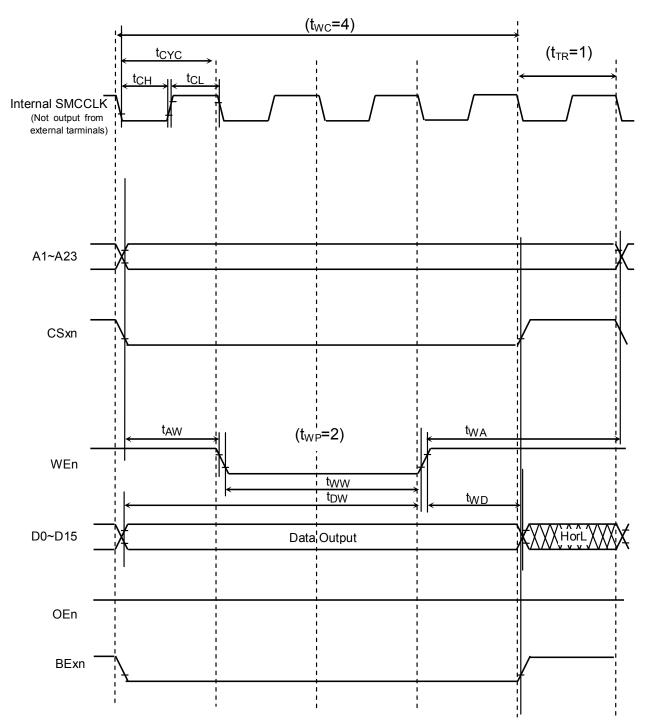

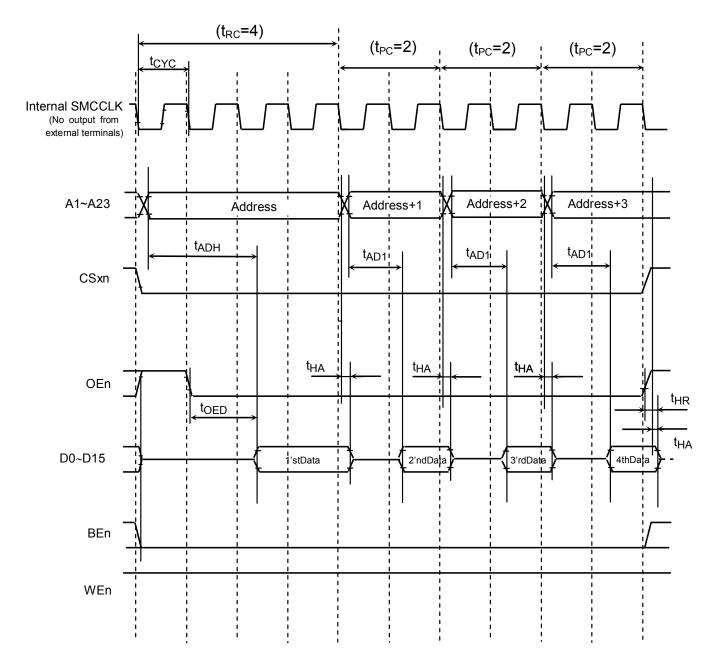

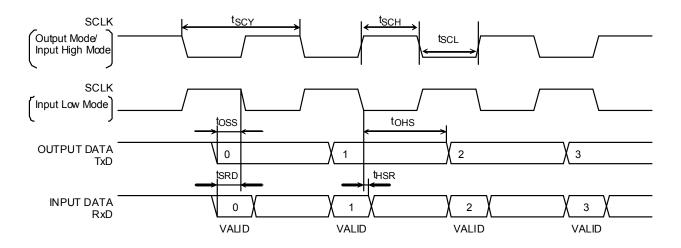

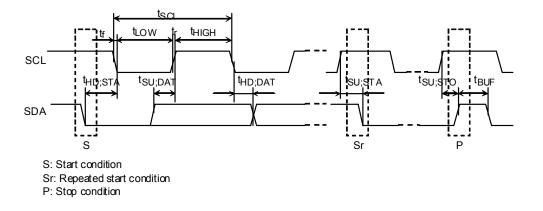

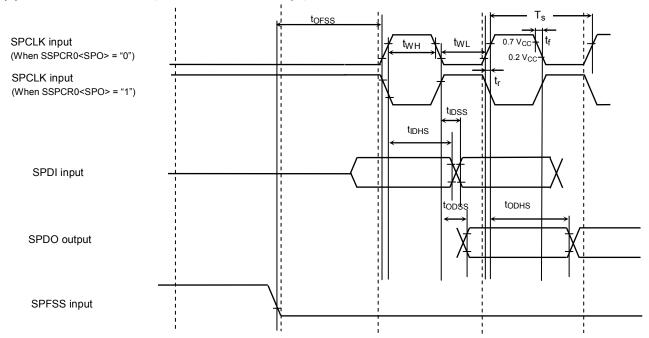

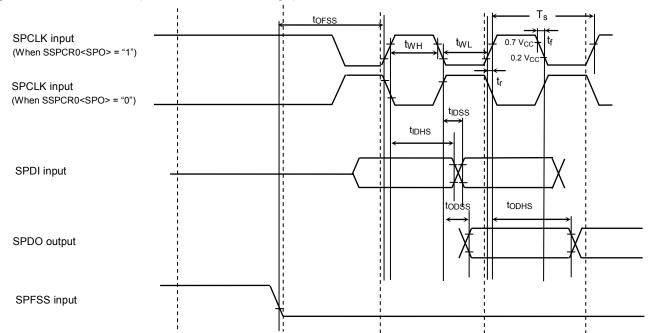

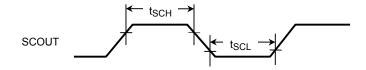

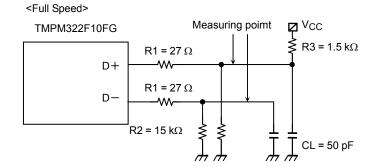

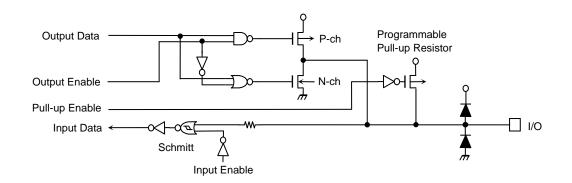

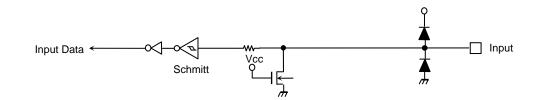

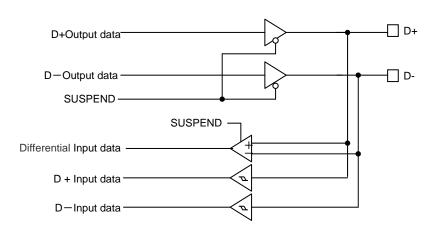

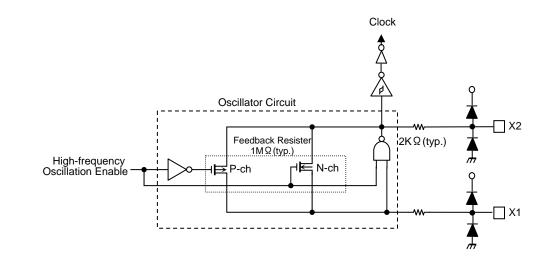

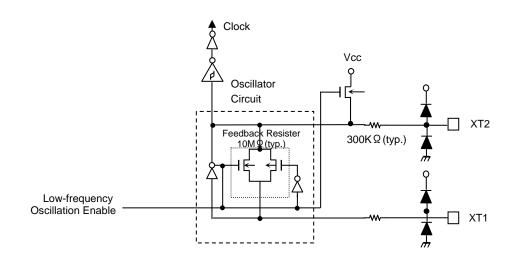

|                                                                                                                                                                     | Function                                                                                                                                                            |              |               |              | "0" is       | s read.      |                             |                 |            |  |