- Organization . . . 1048576 × 4

- Single 5-V Power Supply (±10% Tolerance)

- Performance Ranges:

|             |                     | •      |                    |                     |

|-------------|---------------------|--------|--------------------|---------------------|

|             | ACCESS              | ACCESS | ACCESS             | EDO                 |

|             | TIME                | TIME   | TIME               | CYCLE               |

|             | (t <sub>RAC</sub> ) | (tCAC) | (t <sub>AA</sub> ) | ( <sup>t</sup> HPC) |

|             | (MAX)               | (MAX)  | (MAX)              | (MIN)               |

| '44409/P-60 | 60 ns               | 15 ns  | 30 ns              | 25 ns               |

| '44409/P-70 | 70 ns               | 18 ns  | 35 ns              | 30 ns               |

| '44409/P-80 | 80 ns               | 20 ns  | 40 ns              | 35 ns               |

- Extended Data Out (EDO) Operation

- CAS-Before-RAS (CBR) Refresh

- 3-State Unlatched Output

- Low Power Dissipation

- All Inputs/Outputs and Clocks are TTL-Compatible

- Long Refresh Period

- 1 024 Cycle Refresh in 16 ns (max)

- 128 ms on Low Power, Self-Refresh Version (TMS44409P Only)

- Operating Free-Air Temperature Range 0°C to 70°C

#### description

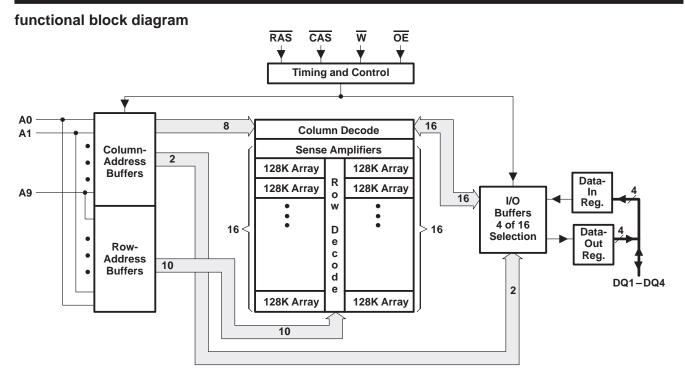

The TMS44409 is a high-speed 4194304-bit dynamic random-access memory (DRAM) organized as 1048576 words of four bits each. This device features maximum RAS access times of 60 ns, 70 ns and 80 ns. Maximum power consumption is as low as 385 mW operating and 6 mW standby. All inputs and outputs, including

clocks, are compatible with Series 74 TTL. All addresses and data-in lines are latched on chip to simplify system design. Data out is unlatched to allow greater system flexibility.

The TMS44409P is a high-speed, low-power, self-refresh version of the TMS44409 DRAM.

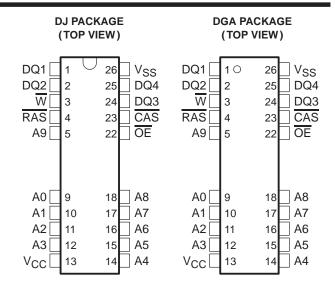

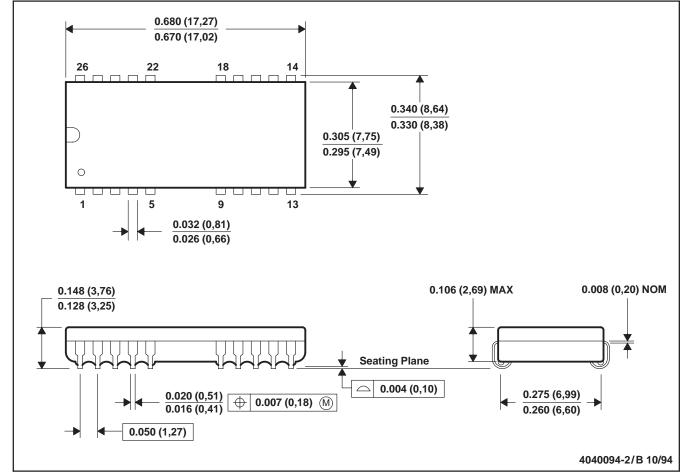

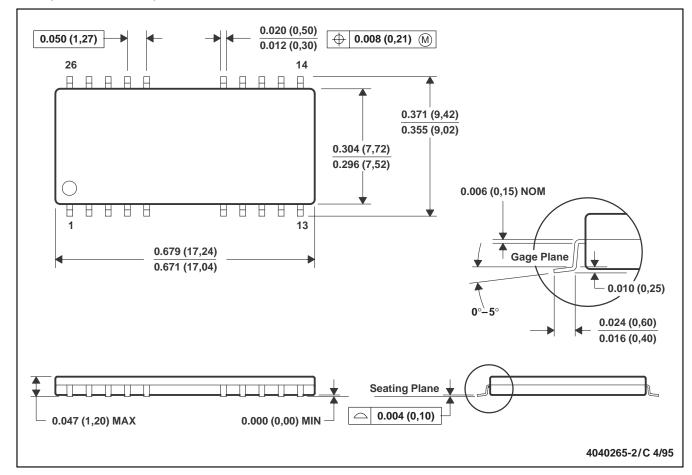

All versions of the TMS44409/P are offered in a 300-mil 20/26 J-lead plastic surface-mount SOJ package (DJ suffix) and a 20/26-lead plastic small outline package (DGA suffix). These devices are characterized for operation from 0°C to 70°C.

| PIN NOMENCLATURE |                       |  |  |  |  |  |  |

|------------------|-----------------------|--|--|--|--|--|--|

| A0-A9            | Address Inputs        |  |  |  |  |  |  |

| CAS              | Column-Address Strobe |  |  |  |  |  |  |

| DQ1 – DQ4        | Data In/Data Out      |  |  |  |  |  |  |

| OE               | Output Enable         |  |  |  |  |  |  |

| RAS              | Row-Address Strobe    |  |  |  |  |  |  |

| VCC              | 5-V Supply            |  |  |  |  |  |  |

| VSS              | Ground                |  |  |  |  |  |  |

| $\overline{W}$   | Write Enable          |  |  |  |  |  |  |

|                  |                       |  |  |  |  |  |  |

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and other specifications are subject to change without notice.

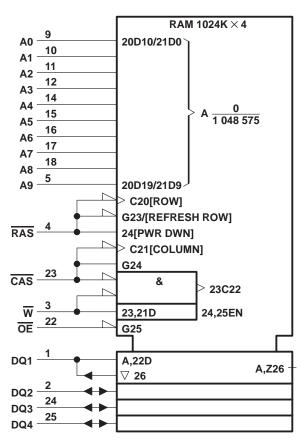

## logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

#### operation

#### extended data out

Extended data out allows for data output rates of up to 40 MHz for 60-ns devices. When keeping the same row address while selecting random column addresses, the time for row-address setup and hold and address multiplex is eliminated. The maximum number of columns that can be accessed is determined by  $t_{RASP}$ , the maximum RAS low time.

Extended data out does not place the DQs into the high-impedance state with the rising edge of  $\overline{CAS}$ . The output remains valid for the system to latch the data. After  $\overline{CAS}$  goes high, the DRAM decodes the next address.  $\overline{OE}$  and  $\overline{W}$  can be used to control the output impedance. Descriptions of  $\overline{OE}$  and  $\overline{W}$  further explain EDO operation benefit.

#### address (A0-A9)

Twenty address bits are required to decode one of 1048576 storage cell locations. Ten row-address bits are set up on A0 through A9 and latched onto the chip by the row-address strobe ( $\overline{RAS}$ ). The ten column-address bits are set up on pins A0 through A9 and latched onto the chip by the column-address strobe ( $\overline{CAS}$ ). All addresses must be stable on or before the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ .  $\overline{RAS}$  is similar to a chip-enable in that it activates the sense amplifiers as well as the row decoder.

## output enable (OE)

$\overline{OE}$  controls the impedance of the output buffers. While  $\overline{CAS}$  and  $\overline{RAS}$  are low and  $\overline{W}$  is high,  $\overline{OE}$  can be brought low or high and the DQs transition between valid data and high impedance (see Figure 7). There are two methods for placing the DQs into the high-impedance state and keeping them that way during  $\overline{CAS}$  high time. The first method is to transition  $\overline{OE}$  high before  $\overline{CAS}$  transitions high and keep  $\overline{OE}$  high for t<sub>CHO</sub> past the  $\overline{CAS}$ transition. This disables the DQs and they remain disabled, regardless of  $\overline{OE}$ , until  $\overline{CAS}$  falls again. The second method is to have  $\overline{OE}$  low as  $\overline{CAS}$  transitions high. Then  $\overline{OE}$  can pulse high for a minimum of t<sub>OEP</sub> anytime during  $\overline{CAS}$  high time, thus, disabling the DQs regardless of further transitions on  $\overline{OE}$  until  $\overline{CAS}$  falls again (see Figure 7).

SMHS563 - JULY1995

#### write enable $(\overline{W})$

The read or write mode is selected through the write-enable  $(\overline{W})$  input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The data input is disabled when the read mode is selected. When  $\overline{W}$  goes low prior to  $\overline{CAS}$  (early write), data out remains in the high-impedance state for the entire cycle, permitting a write operation independent of the state of  $\overline{OE}$ . This permits early-write operation to be completed with  $\overline{OE}$  grounded. If  $\overline{W}$  goes low in an extended-data-out read cycle, the DQs are disabled so long as  $\overline{CAS}$  is high (see Figure 8).

## data in/data out (DQ1-DQ4)

Data is written during a write or a read-modify-write cycle. Depending on the mode of operation, data is strobed in by the later falling edge of  $\overline{CAS}$  or  $\overline{W}$  with setup and hold times referenced to the latter edge. The DQs drive valid data after all access times are met and remain valid except in the cases described in the  $\overline{W}$  and  $\overline{OE}$  descriptions (above).

#### refresh

A refresh operation must be performed at least once every 16 ms to retain data. This is achieved by strobing each of the 1 024 rows (A0–A9). A normal read or write cycle refreshes all bits in each row that is selected. A RAS-only operation can be used by holding CAS at the high (inactive) level, thus conserving power as the output buffer remains in the high-impedance state. Externally generated addresses must be used for a RAS-only refresh. Hidden refresh can be performed while maintaining valid data at the output pin. This is accomplished by holding CAS at V<sub>IL</sub> after a read operation and cycling RAS after a specified precharge period, similar to a RAS-only refresh cycle.

## CAS-before-RAS (CBR) refresh

CBR refresh is utilized by bringing  $\overline{CAS}$  low earlier than  $\overline{RAS}$  (see parameter t<sub>CSR</sub>) and holding it low after  $\overline{RAS}$  falls (see parameter t<sub>CHR</sub>). For successive CBR-refresh cycles,  $\overline{CAS}$  can remain low while cycling  $\overline{RAS}$ . The external address is ignored and the refresh address is generated internally.

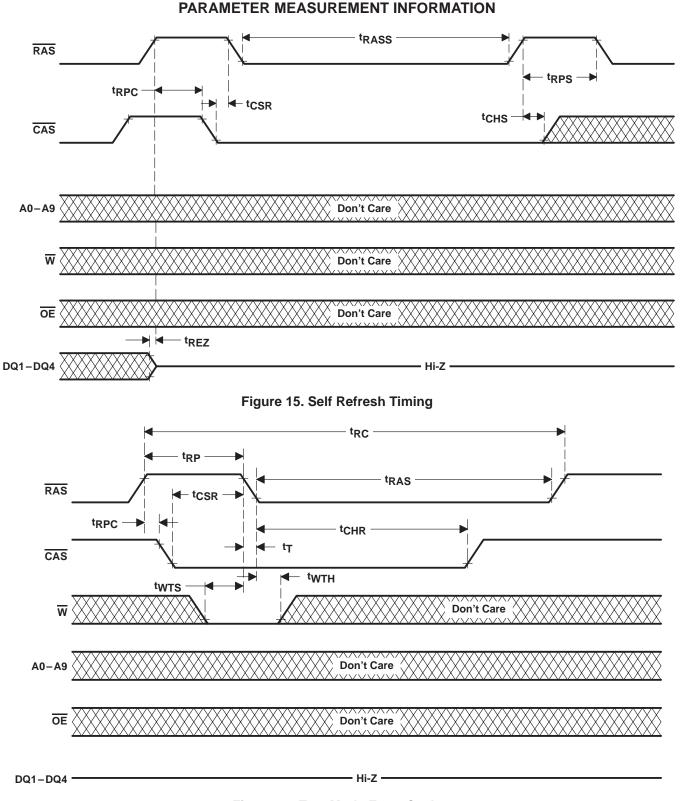

## self-refresh (TMS44409P)

The self-refresh mode is entered by dropping  $\overline{CAS}$  low prior to  $\overline{RAS}$  going low.  $\overline{CAS}$  and  $\overline{RAS}$  are both held low for a minimum of 100  $\mu$ s. The chip is then refreshed by an on-board oscillator. No external address is required because the CBR counter is used to keep track of the address. To exit the self-refresh mode, both  $\overline{RAS}$  and  $\overline{CAS}$  are brought high to satisfy t<sub>CHS</sub>. Upon exiting the self-refresh mode, a burst refresh (refresh of a full set of row addresses) must be executed before continuing with normal operation. This ensures the DRAM is fully refreshed.

#### power up

To achieve proper device operation, an initial pause of 200  $\mu s$  followed by a minimum of eight initialization cycles is required after power up to the full V<sub>CC</sub> level is achieved. These eight initialization cycles need to include at least one refresh (RAS only or CBR) cycle.

#### test mode

A design for test (DFT) mode is incorporated in the TMS44409. A CBR with  $\overline{W}$  low (WCBR) cycle is used to enter the test mode. In the test mode, data is written into and read from eight sections of the array in parallel. All data is written into the array through DQ1. Data is compared upon reading and if all bits are equal, all DQ pins go high. If any one bit is different, a DQ pin goes low. Any combination of read, write, read-write, or page-mode can be used in the test mode. The test-mode function reduces test times by enabling the 1-megabit × 4 DRAM to be tested as if it were a 512K DRAM where column address 0 is not used. A RAS-only or CBR-refresh cycle is used to exit the DFT mode.

SMHS563 - JULY1995

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Voltage range on any pin (see Note 1)                | . $-1$ V to 7 V |

|------------------------------------------------------|-----------------|

| Voltage range on V <sub>CC</sub>                     | . $-1$ V to 7 V |

| Short-circuit output current                         | 50 mA           |

| Power dissipation                                    | 1 W             |

| Operating free-air temperature range, T <sub>A</sub> | . 0°C to 70°C   |

| Storage temperature range, T <sub>stg</sub> –        | 55°C to 150°C   |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to VSS.

#### recommended operating conditions

|                |                                      | MIN | NOM | MAX | UNIT |

|----------------|--------------------------------------|-----|-----|-----|------|

| Vcc            | Supply voltage                       | 4.5 | 5   | 5.5 | V    |

| VIH            | High-level input voltage             | 2.4 |     | 6.5 | V    |

| $V_{IL}$       | Low-level input voltage (see Note 2) | - 1 |     | 0.8 | V    |

| Т <sub>А</sub> | Operating free-air temperature       | 0   |     | 70  | °C   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used for logic-voltage levels only.

SMHS563 - JULY1995

#### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                    | PARAMETER                                                       | TEST CONDITIONS                                                                                                                                                                                   |                                                                                     |         | '44409-60<br>'44409P-60 |      | '44409-70<br>'44409P-70 |      | '44409-80<br>'44409P-80 |      | UNIT |

|--------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------|-------------------------|------|-------------------------|------|-------------------------|------|------|

|                    |                                                                 |                                                                                                                                                                                                   |                                                                                     |         | MIN                     | MAX  | MIN                     | MAX  | MIN                     | MAX  |      |

| Vон                | High-level output voltage                                       | I <sub>OH</sub> = - 5 mA                                                                                                                                                                          |                                                                                     |         | 2.4                     |      | 2.4                     |      | 2.4                     |      | V    |

| Vol                | Low-level output voltage                                        | I <sub>OL</sub> = 4.2 mA                                                                                                                                                                          |                                                                                     |         |                         | 0.4  |                         | 0.4  |                         | 0.4  | V    |

| lı                 | Input current<br>(leakage)                                      | $V_{CC} = 5.5 \text{ V},  V_{I} = 0 \text{ V}$<br>All other pins = 0 V to $V_{C}$                                                                                                                 |                                                                                     |         |                         | ± 10 | ± 10                    |      |                         | ± 10 | mA   |

| IO                 | Output current<br>(leakage)                                     | $\frac{V_{CC}}{CAS} = 5.5 \text{ V}, \qquad V_{O} = 0$                                                                                                                                            | $\frac{V_{CC}}{CAS} = 5.5 \text{ V}, \qquad V_{O} = 0 \text{ V to } 6.5 \text{ V},$ |         |                         | ± 10 |                         | ± 10 |                         | ± 10 | μΑ   |

| ICC1 <sup>†</sup>  | Read- or write-cycle current (see Note 3)                       | V <sub>CC</sub> = 5.5 V, t <sub>RWC</sub> =                                                                                                                                                       | MIN                                                                                 |         |                         | 105  | 90                      |      | 80                      |      | mA   |

|                    |                                                                 | After 1 memory cycle,                                                                                                                                                                             | TTL                                                                                 |         |                         | 2    |                         | 2    |                         | 2    | mA   |

| I <sub>CC2</sub>   | Standby current                                                 | RAS and CAS high,                                                                                                                                                                                 | смоз                                                                                | '44409  |                         | 1    |                         | 1    |                         | 1    | mA   |

|                    |                                                                 | V <sub>IH</sub> = 2.4 V                                                                                                                                                                           |                                                                                     | '44409P |                         | 500  |                         | 500  |                         | 500  | μA   |

| ICC3               | Average refresh<br>current<br>(RAS only or CBR)<br>(see Note 3) |                                                                                                                                                                                                   | CAS high (RAS only);                                                                |         |                         | 105  |                         | 90   |                         | 80   | mA   |

| I <sub>CC4</sub> † | Average EDO page current (see Note 4)                           | $\frac{V_{CC}}{RAS} = 5.5 \text{ V}, \qquad \frac{t_{HPC}}{CAS} = \frac{t_{HPC}}{CAS} = \frac{t_{HPC}}{CAS}$                                                                                      |                                                                                     |         |                         | 90   |                         | 80   |                         | 70   | mA   |

| ICC6‡              | Self-refresh current                                            | CAS, RAS < 0.2 V,<br>Measured after t <sub>RASS</sub> m                                                                                                                                           | in                                                                                  |         |                         | 500  |                         | 500  |                         | 500  | μA   |

| ICC7 <sup>†</sup>  | Standby current                                                 | RAS = V <sub>IH</sub> , CAS = V<br>Data out = enabled                                                                                                                                             | / <sub>IL</sub> ,                                                                   |         |                         | 5    |                         | 5    |                         | 5    | mA   |

| ICC10 <sup>‡</sup> | Battery-backup<br>current                                       | $\begin{array}{l} t_{RC} = 125 \ \mu s,  t_{RAS} \leq \\ V_{CC} - 0.2 \ V \leq V_{IH} \leq 6.5 \\ 0 \ V \leq V_{IL} \leq 0.2 \ V, \ W \ \text{and} \\ \text{Addresses and data stab} \end{array}$ | V,<br>OE = VIH                                                                      | 1,      |                         | 500  |                         | 500  |                         | 500  | μΑ   |

<sup>†</sup> Measured with outputs open

‡TMS44409P only

NOTES: 3. Measured with a maximum of one address change while  $\overline{RAS} = V_{IL}$

4. Measured with a maximum of one address change while  $\overline{CAS} = V_{IH}$

#### capacitance over recommended ranges of supply voltage and operating free-air temperature, f = 1 MHz (see Note 5)

|                    | PARAMETER                                         | MIN | MAX | UNIT |

|--------------------|---------------------------------------------------|-----|-----|------|

| C <sub>i(A)</sub>  | Input capacitance, A0-A9                          |     | 5   | pF   |

| C <sub>i(OE)</sub> | Input capacitance, OE                             |     | 7   | pF   |

| C <sub>i(RC)</sub> | Input capacitance, CAS and RAS                    |     | 7   | pF   |

| C <sub>i(W)</sub>  | Input capacitance, $\overline{W}$                 |     | 7   | pF   |

| Co                 | Output capacitance                                |     | 7   | pF   |

| 8 Compatib         | anas massuramente era made en a sample basis anly | -   |     |      |

§ Capacitance measurements are made on a sample basis only.

NOTE 5:  $V_{CC}$  = 5 V ± 0.5 V, and the bias on pins under test is 0 V.

SMHS563 - JULY1995

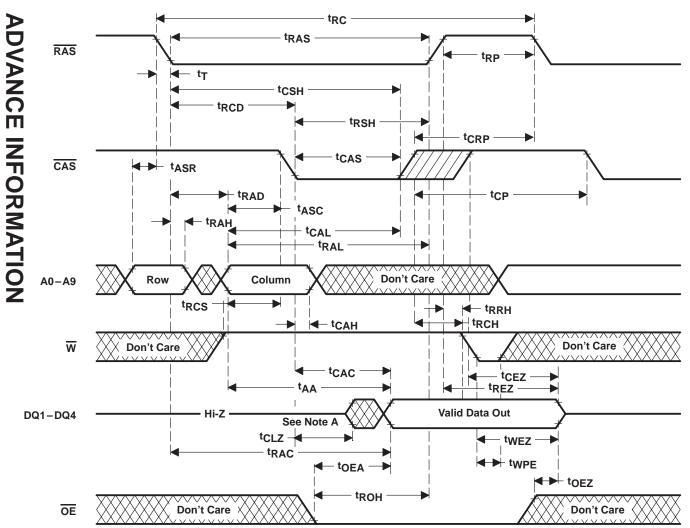

#### switching characteristics over recommended ranges of supply voltage and operating free-air temperature (see Figure 1)

| PARAMETER        |                                                                  | '44409-60<br>'44409P-60 |     | '44409-70<br>'44409P-70 |     | '44409-80<br>'44409P-80 |     | UNIT |

|------------------|------------------------------------------------------------------|-------------------------|-----|-------------------------|-----|-------------------------|-----|------|

|                  |                                                                  | MIN                     | MAX | MIN                     | MAX | MIN                     | MAX |      |

| t <sub>AA</sub>  | Access time from column address                                  |                         | 30  |                         | 35  |                         | 40  | ns   |

| <sup>t</sup> CAC | Access time from CAS low                                         |                         | 15  |                         | 18  |                         | 20  | ns   |

| <sup>t</sup> CPA | Access time from column precharge                                |                         | 35  |                         | 40  |                         | 45  | ns   |

| <sup>t</sup> RAC | Access time from RAS low                                         |                         | 60  |                         | 70  |                         | 80  | ns   |

| <sup>t</sup> OEA | Access time from OE low                                          |                         | 15  |                         | 18  |                         | 20  | ns   |

| <sup>t</sup> CLZ | CAS to output in low-impedance state                             | 0                       |     | 0                       |     | 0                       |     | ns   |

| <sup>t</sup> REZ | Output disable time, start of $\overline{RAS}$ high (see Note 6) | 3                       | 15  | 3                       | 18  | 3                       | 20  | ns   |

| <sup>t</sup> CEZ | Output disable time, start of $\overline{CAS}$ high (see Note 6) | 3                       | 15  | 3                       | 18  | 3                       | 20  | ns   |

| <sup>t</sup> OEZ | Output disable time after $\overline{OE}$ high (see Note 6)      | 3                       | 15  | 3                       | 18  | 3                       | 20  | ns   |

| <sup>t</sup> WEZ | Output disable time after $\overline{W}$ high (see Note 6)       | 3                       | 15  | 3                       | 18  | 3                       | 20  | ns   |

NOTE 6: Maximum tREZ, tCEZ, tWEZ and tOEZ are specified when the output is no longer driven.

#### EDO timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                  |                                                      | '4440<br>'4440 | 9-60<br>9P-60 | '44409-70<br>'44409P-70 |       | '44409-80<br>'44409P-80 |       | UNIT |

|------------------|------------------------------------------------------|----------------|---------------|-------------------------|-------|-------------------------|-------|------|

|                  |                                                      | MIN            | MAX           | MIN                     | MAX   | MIN                     | MAX   |      |

| <sup>t</sup> HPC | Cycle time, EDO page-mode read or write              | 25             |               | 30                      |       | 35                      |       | ns   |

| <sup>t</sup> CSH | Hold time, CAS from RAS                              | 50             |               | 55                      |       | 60                      |       | ns   |

| <sup>t</sup> CHO | Hold time, OE from CAS                               | 10             |               | 10                      |       | 10                      |       | ns   |

| <sup>t</sup> DOH | Hold time, output from CAS                           | 3              |               | 3                       |       | 3                       |       | ns   |

| tCAS             | Pulse duration, CAS                                  | 10             | 10000         | 12                      | 10000 | 15                      | 10000 | ns   |

| <sup>t</sup> WPE | Pulse duration, $\overline{W}$ (output disable only) | 5              |               | 5                       |       | 5                       |       | ns   |

| <sup>t</sup> OCH | Setup time, OE before CAS                            | 10             |               | 10                      |       | 10                      |       | ns   |

| <sup>t</sup> CP  | Precharge time, CAS                                  | 5              |               | 5                       |       | 5                       |       | ns   |

| <sup>t</sup> OEP | Precharge time, OE                                   | 5              |               | 5                       |       | 5                       |       | ns   |

#### timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                   |                                                                                         | '44409-60<br>'44409P-60 |         |     | '44409-70<br>'44409P-70 |     | '44409-80<br>'44409P-80 |    |

|-------------------|-----------------------------------------------------------------------------------------|-------------------------|---------|-----|-------------------------|-----|-------------------------|----|

|                   |                                                                                         | MIN                     | MAX     | MIN | MAX                     | MIN | MAX                     |    |

| <sup>t</sup> RC   | Cycle time, random read or write (see Note 7)                                           | 110                     |         | 130 |                         | 150 |                         | ns |

| <sup>t</sup> RWC  | Cycle time, read-write (see Note 7)                                                     | 150                     |         | 175 |                         | 200 |                         | ns |

| <sup>t</sup> PRWC | Cycle time, EDO page-mode read-write                                                    | 80                      |         | 90  |                         | 100 |                         | ns |

| t <sub>RASP</sub> | Pulse duration, page mode, RAS low, (see Note 8)                                        | 60                      | 100 000 | 70  | 100 000                 | 80  | 100 000                 | ns |

| <sup>t</sup> RAS  | Pulse duration, nonpage mode, RAS low, (see Note 8)                                     | 60                      | 10 000  | 70  | 10 000                  | 80  | 10 000                  | ns |

| <sup>t</sup> RP   | Pulse duration, RAS high (precharge)                                                    | 40                      |         | 50  |                         | 60  |                         | ns |

| tWP               | Pulse duration, W                                                                       | 10                      |         | 10  |                         | 10  |                         | ns |

| tASC              | Setup time, column address before CAS low                                               | 0                       |         | 0   |                         | 0   |                         | ns |

| <sup>t</sup> ASR  | Setup time, row address before RAS low                                                  | 0                       |         | 0   |                         | 0   |                         | ns |

| tDS               | Setup time, data before $\overline{W}$ low (see Note 9)                                 | 0                       |         | 0   |                         | 0   |                         | ns |

| <sup>t</sup> RCS  | Setup time, read before CAS low                                                         | 0                       |         | 0   |                         | 0   |                         | ns |

| <sup>t</sup> CWL  | Setup time, W low before CAS high                                                       | 10                      |         | 12  |                         | 15  |                         | ns |

| <sup>t</sup> RWL  | Setup time, W low before RAS high                                                       | 10                      |         | 12  |                         | 15  |                         | ns |

| tWCS              | Setup time, $\overline{W}$ low before $\overline{CAS}$ low (early-write operation only) | 0                       |         | 0   |                         | 0   |                         | ns |

| tWSR              | Setup time, W high (CBR refresh only)                                                   | 10                      |         | 10  |                         | 10  |                         | ns |

| <sup>t</sup> CAH  | Hold time, column address after CAS low                                                 | 10                      |         | 15  |                         | 15  |                         | ns |

| <sup>t</sup> DH   | Hold time, data after CAS low (see Note 9)                                              | 10                      |         | 15  |                         | 15  |                         | ns |

| <sup>t</sup> RAH  | Hold time, row address after RAS low                                                    | 10                      |         | 10  |                         | 10  |                         | ns |

| <sup>t</sup> RCH  | Hold time, read after CAS high (see Note 10)                                            | 0                       |         | 0   |                         | 0   |                         | ns |

| tRRH              | Hold time, read after RAS high (see Note 10)                                            | 0                       |         | 0   |                         | 0   |                         | ns |

| tWCH              | Hold time, write after CAS low (early-write operation only)                             | 10                      |         | 15  |                         | 15  |                         | ns |

| tWHR              | Hold time, $\overline{W}$ high (CBR refresh only)                                       | 10                      |         | 10  |                         | 10  |                         | ns |

| <sup>t</sup> ROH  | Hold time, RAS referenced to OE                                                         | 10                      |         | 10  |                         | 10  |                         | ns |

| tAWD              | Delay time, column address to $\overline{W}$ low (read-write operation only)            | 55                      |         | 63  |                         | 70  |                         | ns |

| <sup>t</sup> CHR  | Delay time, RAS low to CAS high (CBR refresh only)                                      | 15                      |         | 15  |                         | 20  |                         | ns |

| <sup>t</sup> CRP  | Delay time, CAS high to RAS low                                                         | 0                       |         | 0   |                         | 0   |                         | ns |

| <sup>t</sup> CSR  | Delay time, CAS low to RAS low (CBR refresh only)                                       | 5                       |         | 5   |                         | 5   |                         | ns |

| tCWD              | Delay time, $\overline{CAS}$ low to $\overline{W}$ low (read-write operation only)      | 40                      |         | 46  |                         | 50  |                         | ns |

| <sup>t</sup> OEH  | Hold time, OE command                                                                   | 15                      |         | 18  |                         | 20  |                         | ns |

| tOED              | Delay time, valid data in after OE high                                                 | 15                      |         | 18  |                         | 20  |                         | ns |

| <sup>t</sup> RAD  | Delay time, RAS low to column address                                                   | 15                      | 30      | 15  | 35                      | 15  | 40                      | ns |

| tRAL              | Delay time, column address to RAS high                                                  | 30                      |         | 35  |                         | 40  |                         | ns |

| tCAL              | Delay time, column address to CAS high                                                  | 20                      |         | 25  |                         | 30  |                         | ns |

| tRCD              | Delay time, RAS low to CAS low (see Note 11)                                            | 20                      | 45      | 20  | 52                      | 20  | 60                      | ns |

| tRPC              | Delay time, RAS high to CAS low (CBR refresh only)                                      | 0                       |         | 0   |                         | 0   |                         | ns |

NOTES: 7. All timing requirements assume  $t_T = 5$  ns.

8. In a read-write cycle,  $t_{RWD}$  and  $t_{RWL}$  must be observed.

9. Referenced to the later of CAS or W in write operations

10. The minimum value is measured when  $t_{RCD}$  is set to  $t_{RCD}$  min as a reference.

11. The minimum value is specified only to assure access time.

# timing requirements over recommended ranges of supply voltage and operating free-air temperature (continued)

|                   |                                                        |             | -    | 409-60 <sup>'</sup> 44409-70 <sup>'</sup> 44409-8<br>109P-60 <sup>'</sup> 44409P-70 <sup>'</sup> 44409P-8 |      |     | UNIT |     |    |

|-------------------|--------------------------------------------------------|-------------|------|-----------------------------------------------------------------------------------------------------------|------|-----|------|-----|----|

|                   |                                                        |             | MIN  | MAX                                                                                                       | MIN  | MAX | MIN  | MAX |    |

| <sup>t</sup> RSH  | Delay time, CAS low to RAS high                        |             | 10   |                                                                                                           | 12   |     | 15   |     | ns |

| <sup>t</sup> RWD  | Delay time, $\overline{RAS}$ low to $\overline{W}$ low |             | 85   |                                                                                                           | 98   |     | 110  |     | ns |

| t===              | Refresh time interval                                  | '44409      |      | 16                                                                                                        |      | 16  |      | 16  | ms |

| <sup>t</sup> REF  |                                                        | '44409P     |      | 128                                                                                                       |      | 128 |      | 128 | ms |

| tŢ                | Transition time                                        |             | 2    | 50                                                                                                        | 2    | 50  | 2    | 50  | ms |

| <sup>t</sup> WTH  | Hold time, write low (test mode)                       |             | 10   |                                                                                                           | 10   |     | 10   |     | ns |

| <sup>t</sup> CHS  | Hold time, CAS low after RAS high (self refresh) (TMS4 | 4409P only) | - 50 |                                                                                                           | - 50 |     | - 50 |     | ns |

| tWTS              | Setup time, write low (test mode)                      |             | 10   |                                                                                                           | 10   |     | 10   |     | ns |

| <sup>t</sup> CPS  | CAS precharge before self refresh                      |             | 0    |                                                                                                           | 0    |     | 0    |     | ns |

| t <sub>RPS</sub>  | RAS precharge after self refresh                       |             | 110  |                                                                                                           | 130  |     | 150  |     | ns |

| <sup>t</sup> RASS | Self-refresh entry from RAS low (TMS44409P only)       |             | 100  |                                                                                                           | 100  |     | 100  |     | μs |

SMHS563 - JULY1995

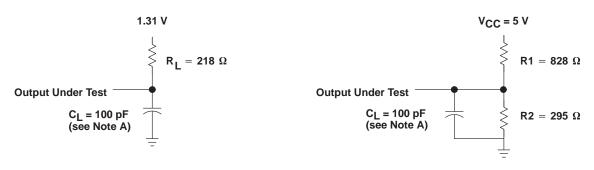

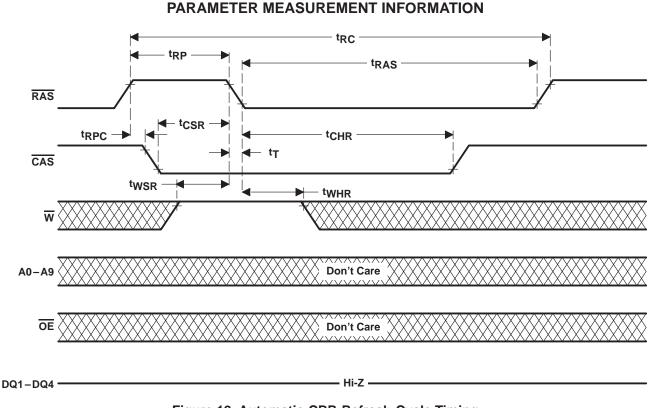

## PARAMETER MEASUREMENT INFORMATION

(a) LOAD CIRCUIT

NOTE A: CL includes probe and fixture capacitance.

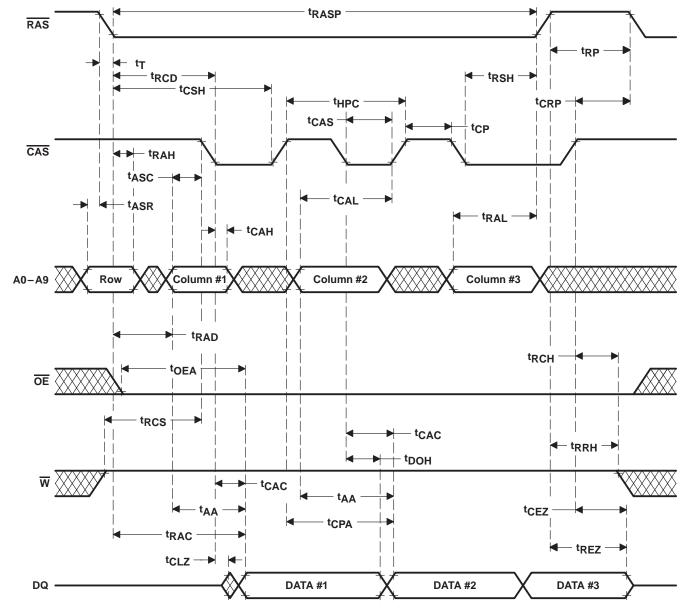

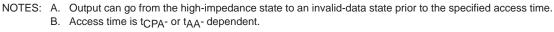

NOTE A: Output can go from the high-impedance state to an invalid-data state prior to the specified access time.

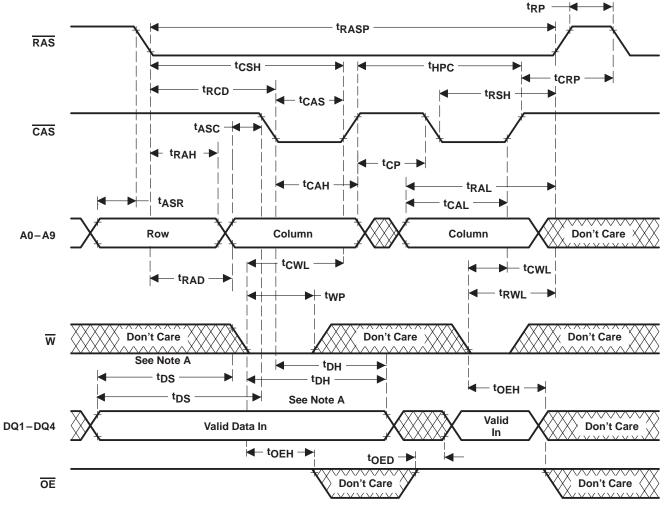

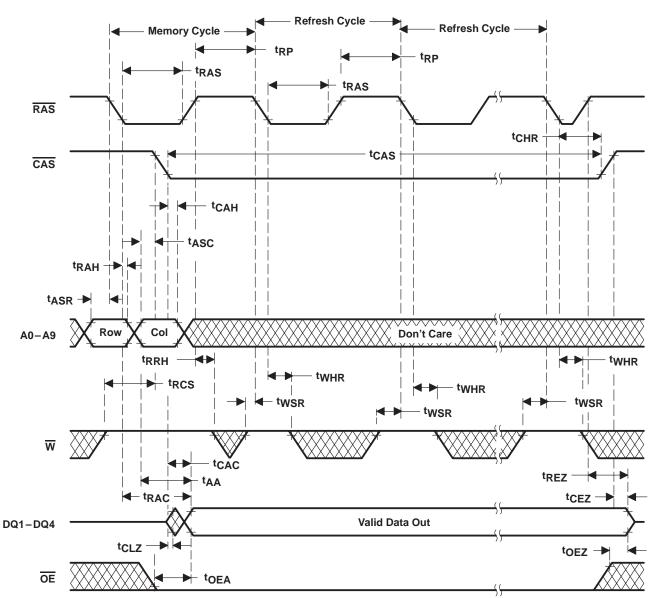

Figure 2. Read-Cycle Timing

SMHS563 - JULY1995

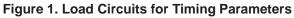

Figure 3. Early-Write-Cycle Timing

<sup>t</sup>RC tRAS RAS tRP tт <sup>t</sup>RSH <sup>t</sup>RCD tCRP tCAS <sup>t</sup>CSH CAS + tASR tCP tASC tRAL tRAH - tCAH ┢ Don't Care A0-A9 Row Column <sup>t</sup>CWL tRAD → <sup>t</sup>RWL Don't Care Don't Care W twp tDS -┢ ← t<sub>DH</sub> – DQ1-DQ4 Don't Care Valid Data Don't Care ▲ tOED <sup>t</sup>OEH OE Don't Care Don't Care

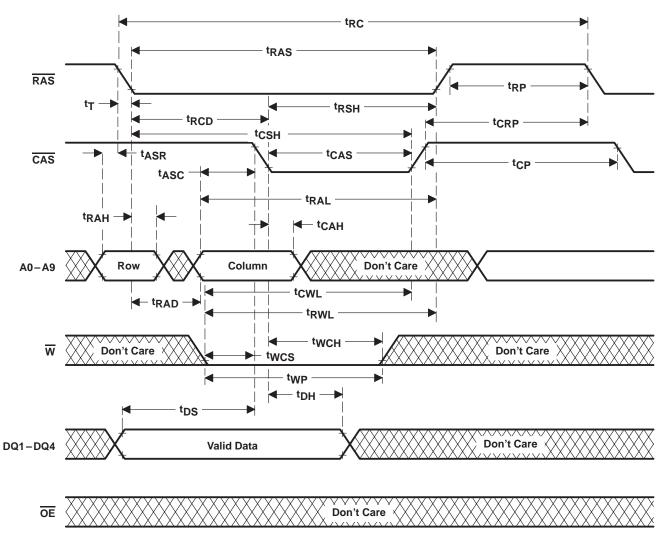

Figure 4. Write-Cycle Timing

SMHS563 - JULY1995

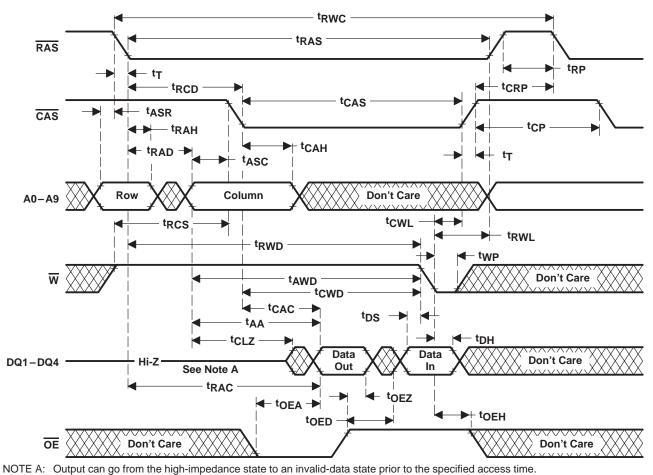

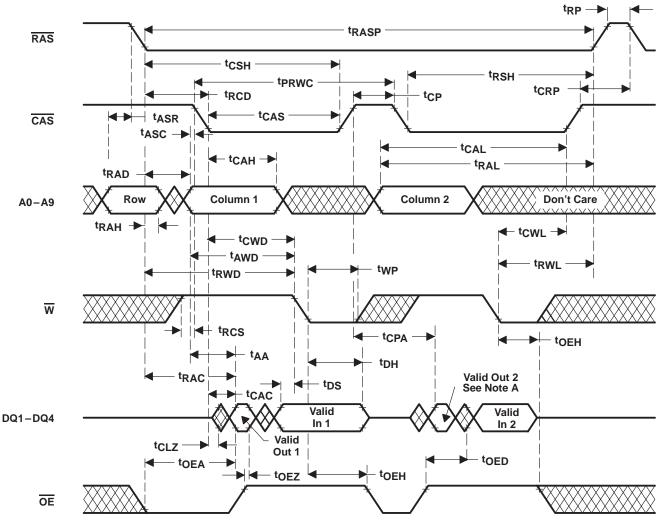

Figure 5. Read-Write-Cycle Timing

SMHS563 - JULY1995

Figure 6. Extended-Data-Out Read Cycle

SMHS563 - JULY1995

## PARAMETER MEASUREMENT INFORMATION

Figure 7. Extended-Data-Out Read-Cycle With OE Control

**ADVANCE INFORMATION**

SMHS563 - JULY1995

## PARAMETER MEASUREMENT INFORMATION

Figure 8. Extended-Data-Out Read-Cycle With W Control

XAS **RUMENTS** POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251-1443

SMHS563 - JULY1995

## PARAMETER MEASUREMENT INFORMATION

NOTES: A. Referenced to  $\overline{CAS}$  or  $\overline{W}$ , whichever occurs last.

B. A read cycle or a read-write cycle can be intermixed with write cycles as long as read and read-write timing specifications are not violated.

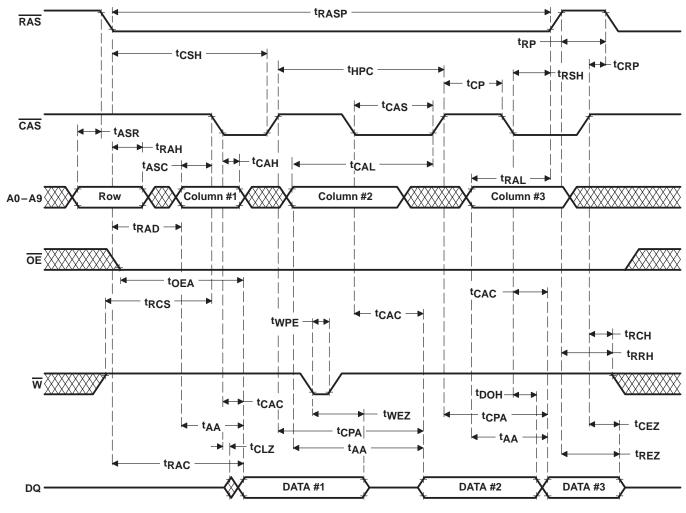

Figure 9. EDO-Write-Cycle Timing

SMHS563 - JULY1995

#### PARAMETER MEASUREMENT INFORMATION

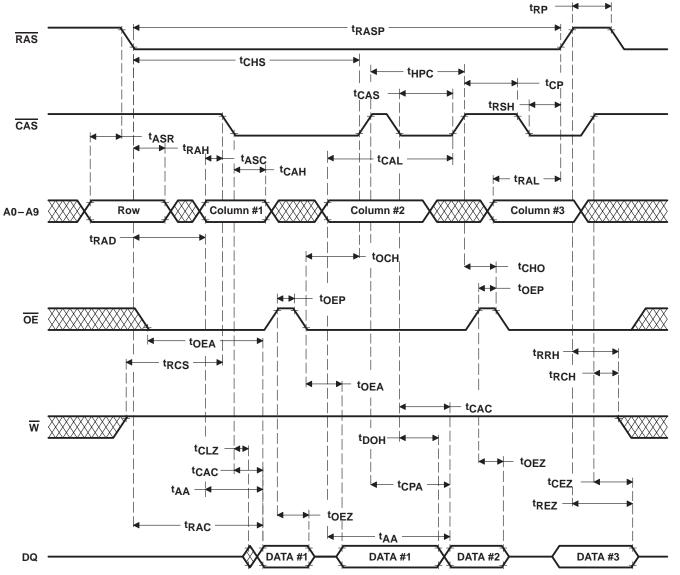

NOTES: A. Output can go from the high-impedance state to an invalid-data state prior to the specified access time.

B. A read or write cycle can be intermixed with read-write cycles as long as the read- and write-timing specifications are not violated.

Figure 10. EDO Read-Write-Cycle Timing

SMHS563 - JULY1995

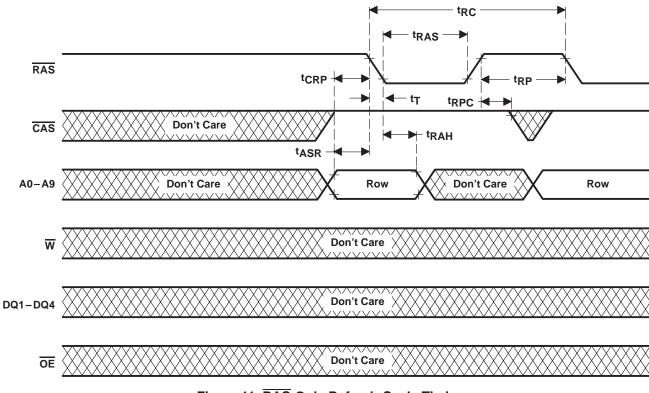

Figure 11. RAS-Only Refresh-Cycle Timing

Figure 12. Automatic-CBR-Refresh-Cycle Timing

SMHS563 - JULY1995

## PARAMETER MEASUREMENT INFORMATION

**ADVANCE INFORMATION**

Memory Cycle **Refresh Cycle** <sup>t</sup>RAS Refresh Cycle tRP t<sub>RAS</sub> tRP RAS ► tCAS CAS tCAH <sup>t</sup>ASC tRAH + tASR Don't Care A0-A9 Row Col tRRH tWHR twcs - twsr WP  $\overline{\mathsf{W}}$ tDStWCH <sup>t</sup>DH Valid Data Don't Care DQ1-DQ4 Don't Care OE

Figure 14. Hidden-Refresh Cycle (Write)

SMHS563 - JULY1995

Figure 16. Test-Mode Entry Cycle

**ADVANCE INFORMATION**

**MECHANICAL DATA**

DJ (R-PDSO-J20/26)

PLASTIC SMALL-OUTLINE J-LEAD PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Plastic body dimensions do not include mold protrusion. Maximum mold protrusion is 0.005 (0,125).

SMHS563 - JULY1995

**MECHANICAL DATA**

#### DGA (R-PDSO-G20/26)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

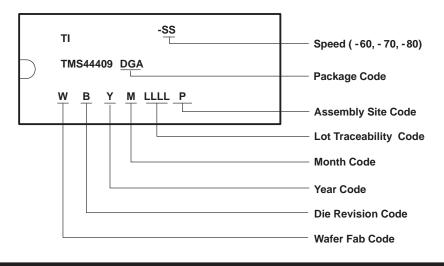

#### device symbolization (TMS44409 illustrated)

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated