8961725 0076997 0 1

.

TMS44C256, TMS44C257

-----

262,144-WORD BY 4-BIT DYNAMIC RANDOM-ACCESS MEMORIES \_

\_ \_ \_

|   | - TEXAS INSTR (ASIC/MEMORY)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25E D JUNE 1986 - REVISED MAY 1988                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ٠ | 262,144 × 4 Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | N PACKAGE T 111 22 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| • | Single 5-V Supply (10% Tolerance)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (TOP VIEW) / - 96 - 23 - 1 / 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ٠ | Performance Ranges:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | $\begin{array}{c} DQ1[1 & Q20] V_{SS} \\ DQ2[2 & 19] DQ4 \\ \hline Q20 & Q20 \\ \hline Q20 & Q20$ |

|   | ACCESS         ACCESS         ACCESS         READ           TIME         TIME         TIME         OR           te(R)         te(C)         te(CA)         WRITE           (tRAC)         (tCAC)         (tCAA)         CYCLE           (MAX)         (MAX)         (MAX)         (MAN)           TMS44C2510         100 ns         25 ns         45 ns         190 ns           TMS44C2512         120 ns         30 ns         55 ns         220 ns           TMS44C2515         150 ns         40 ns         70 ns         260 ns | WU3     18_D03     2       RASU     4     17_CAS     2       TFU     5     16_DG     2       AO     6     15_DAS     2       AO     6     16_DG     2       AO     6     16_DAS     2       A1     7     14_DA7     A       A2     8     13_DA6     Q       A3     9     12_DA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ٠ | TMS44C256 — Enhanced Page Mode<br>Operation with CAS-Before-RAS Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Vcc1 <u>10 11</u> A4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ٠ | TMS44C257 — Static Column Decode<br>Mode Operation with CAS-Before-RAS<br>Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DJ PACKAGE <sup>†</sup><br>(TOP VIEW)<br>DQ1 0 26 VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| • | Long Refresh Period<br>512-Cycle Refresh in 8 ms (Max)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DQ2 [] 2 25 ]] DQ4<br>W [] 3 24 ]] DQ3<br>RAS [] 4 23 ]] CAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ٠ | 3-State Unlatched Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ٠ | Lower Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ٠ | Texas Instruments EPIC <sup>™</sup> CMOS Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ٠ | All Inputs and Clocks Are TTL Compatible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | A0 🗍 9 18 🗋 A8<br>A1 🗍 10 17 🗋 A7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

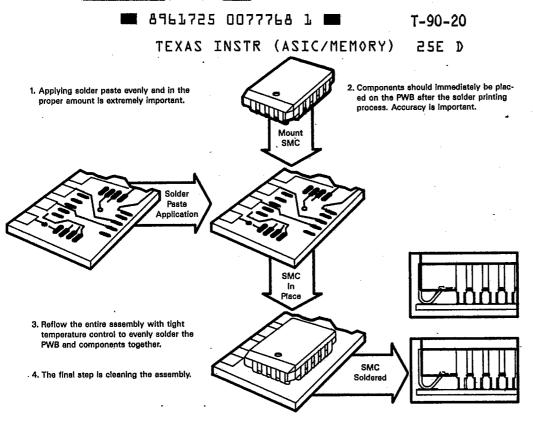

| ٠ | High-Reliability Plastic 20-Pin 300-Mil-Wide<br>DIP or 20/26-Lead Surface Mount (SOJ)<br>Package                                                                                                                                                                                                                                                                                                                                                                                                                                     | A2 11 16 A6<br>A3 12 15 A5<br>VCC 13 14 A4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

<sup>†</sup>The packages shown here are for pinout reference only, The DJ package is actually 75% of the length of the N package.

| P       | IN NOMENCLATURE       |

|---------|-----------------------|

| A0-A8   | Address Inputs        |

| CAS     | Column-Address Strobe |

| DQ1-DQ4 | Data in/Data Out      |

| G       | Data-Output Enable    |

| RAS     | Row-Address Strobe    |

| TF      | Test Function         |

| Ŵ       | Write Enable          |

| Vcc     | 5-V Supply            |

| VSS     | Ground                |

EPIC<sup>™</sup> (Enhanced Process Implanted CMOS) technology for high performance, reliability, and low power at a low cost. operation

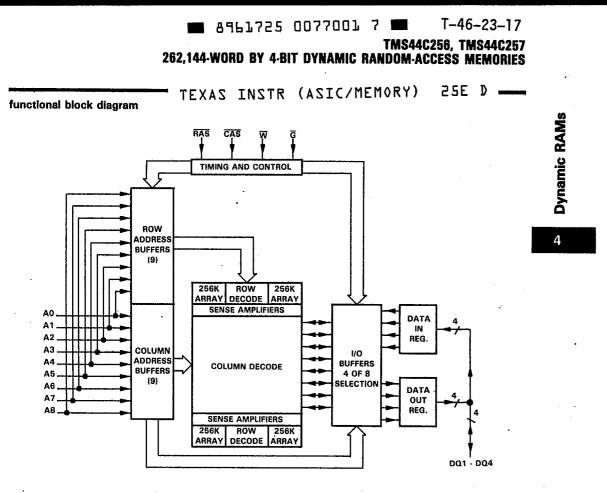

The TMS44C256 and TMS44C257 series are high-speed, 1,048,576-bit Dynamic Random-Access Memories organized as 262,144 words of four bits each. They employ state-of-the-art

**Operation of TI's Megabit CMOS DRAMs**

Can Be Controlled by TI's SN74ALS6301

and SN74ALS6302 Dynamic RAM

**Operating Free-Air Temperature . . .**

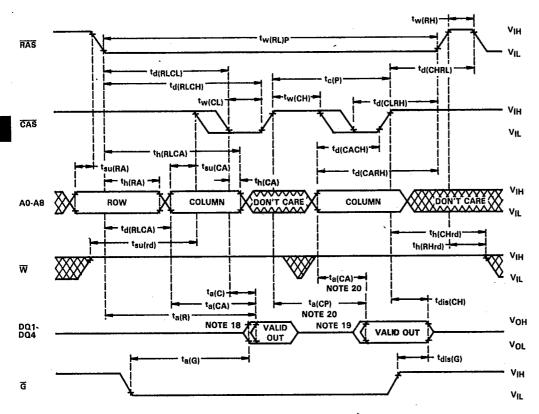

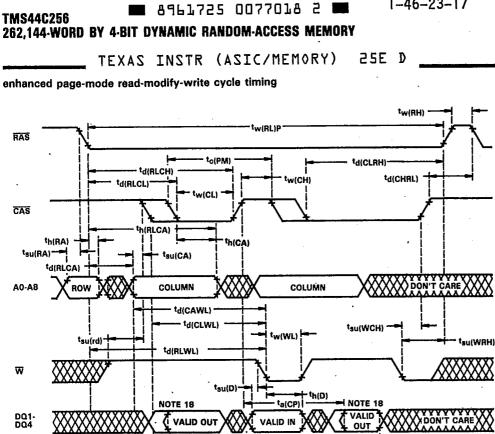

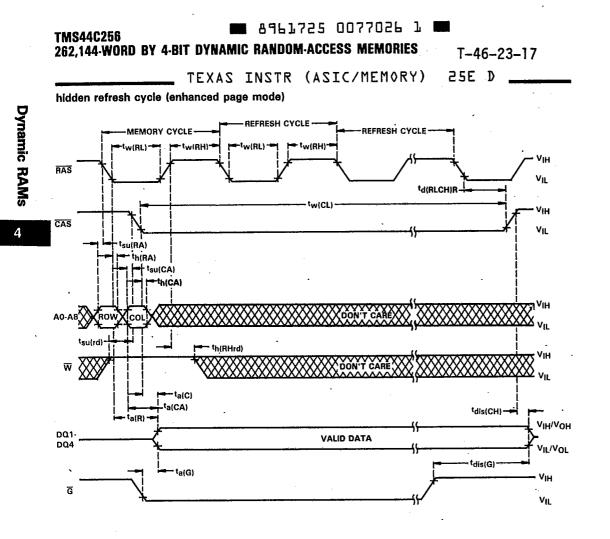

#### enhanced page mode (TMS44C256)

Page-mode operation allows faster memory access by keeping the same row address while selecting random column addresses. The time for row-address setup and hold and address multiplex is thus eliminated. The maximum number of columns that may be accessed is determined by the maximum RAS low time and EPIC is a trademark of Texas instruments incorporated,

PRODUCTION DATA documents contain information current as af publication dats. Products casform to specifications per the terms of Toxas Instruments standard warranty. Production processing dees net necessarily include testing of all perameters.

Controllers

description

0°C to 70°C

TEXAS INSTRUMENTS POST OFFICE BOX 1443 . HOUSTON, TEXAS 77001

### TMS44C256, TMS44C257 262,144-WORD BY 4-BIT DYNAMIC RANDOM-ACCESS MEMORIES

# 25E D

T-46-23-17

# TEXAS INSTR (ASIC/MEMORY)

the CAS page-mode cycle time used. With minimum CAS page cycle time, all 512 columns specified by column addresses A0 through A8 can be accessed without intervening RAS cycles.

Unlike conventional page-mode DRAMs, the column-address buffers in this device are activated on the falling edge of RAS. The buffers act as transparent or flow-through latches while CAS is high. The falling edge of CAS latches the column addresses. This feature allows the TMS44C256 to operate at a higher data bandwidth than conventional page-mode parts, since data retrieval begins as soon as column address is valid rather than when CAS transitions low. This performance improvement is referred to as "enhanced page mode." Valid column address may be presented immediately after th(RA) (row address hold time) has been satisfied, usually well in advance of the falling edge of CAS. In this case, data is obtained after ta(C) max (access time from CAS low), if ta(CA) max (access time from column address) has been satisfied. In the event that column addresses for the next page cycle are valid at the time CAS goes high, access time for the next cycle is determined by the later occurrence of ta(C) or ta(CP) (access time from rising edge of CAS).

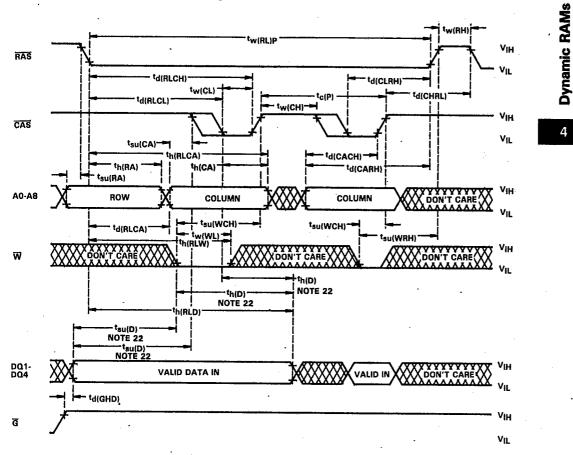

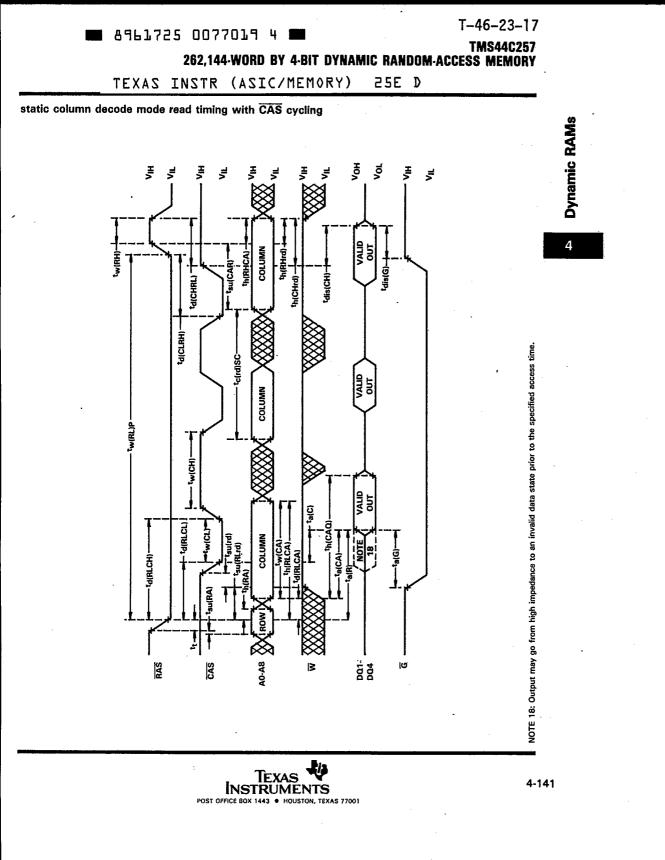

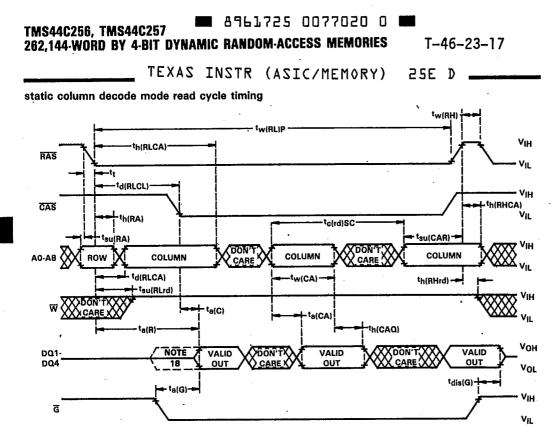

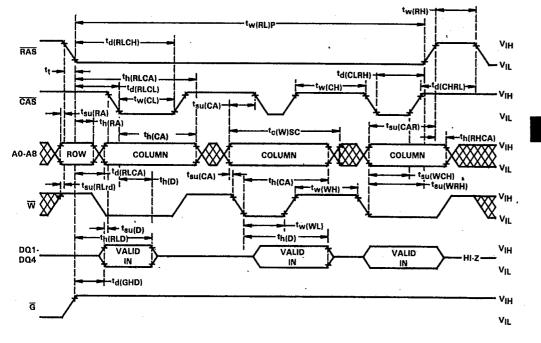

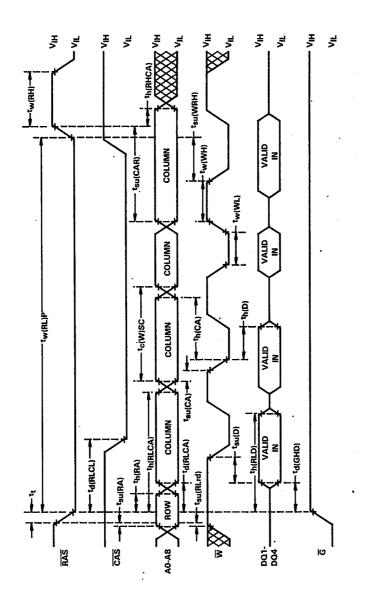

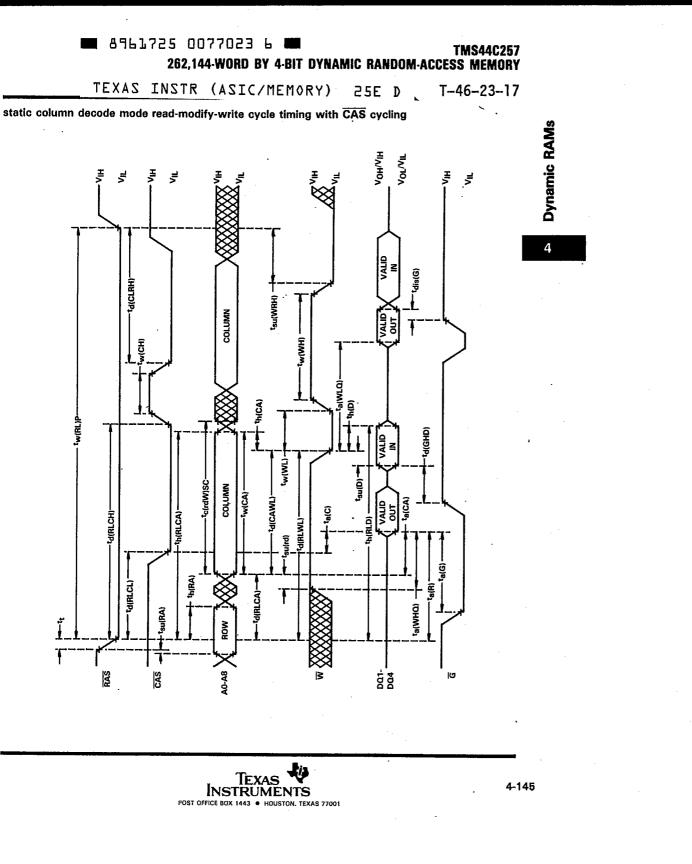

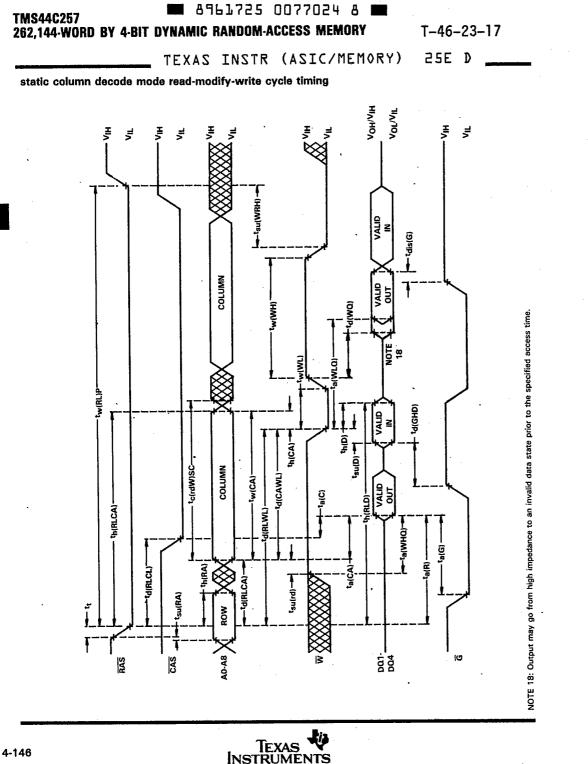

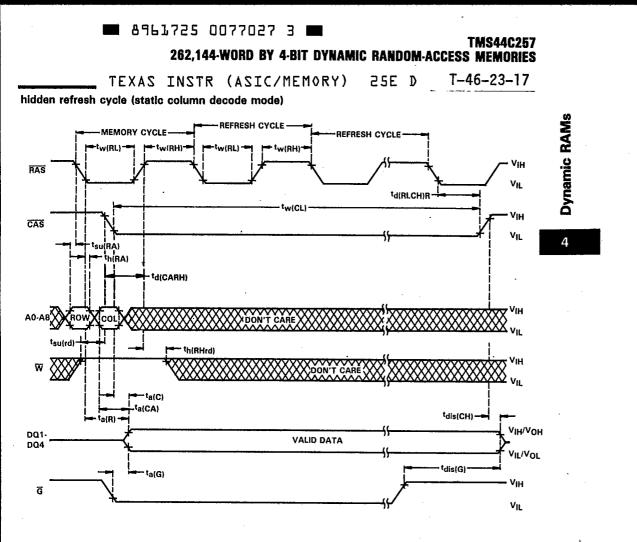

# static column decode mode (TMS44C257)

The static column decode mode of operation allows high-speed read, write, or read-modify-write by reducing the number of required signal setup, hold, and transition timings. This is achieved by first addressing the row and column in the normal manner, but after the first access maintain CAS low. Subsequently changing the column address produces valid data at the ta(CA). The first bit is accessed in the normal manner with read data coming out at  $t_{a(C)}$  time. Similarly, write or read-modify-write cycle times can be achieved with appropriate toggling of  $\overline{W}$ . The addresses are latched during the write operation, but at the completion of the internal write operation the addresses are unlatched.

#### address (A0 through A8)

Eighteen address bits are required to decode 1 of 262,144 storage cell locations. Nine row-address bits are set up on pins A0 through A8 and latched onto the chip by the row-address strobe (RAS). Then nine column-address bits are set up on pins A0 through A8 and latched onto the chip by the column-address strobe (CAS). All addresses must be stable on or before the falling edges of RAS and CAS. RAS is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder. The TMS44C256 CAS is used as a chip select activating the output buffer, as well as latching the address bits into the column-address buffers. The TMS44C257 column addresses are latched only on write cycles with the later of the  $\overline{CAS}$  or  $\overline{W}$  falling edge.

#### write enable (W)

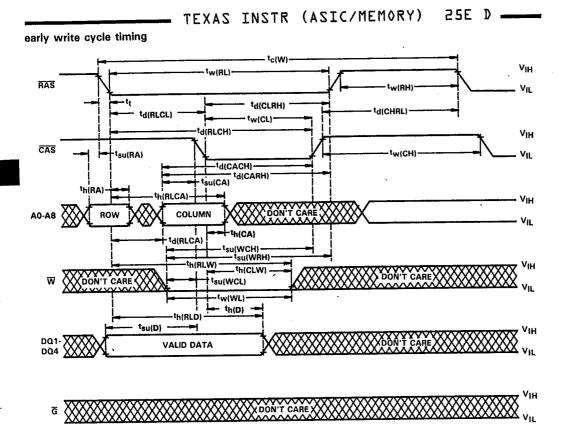

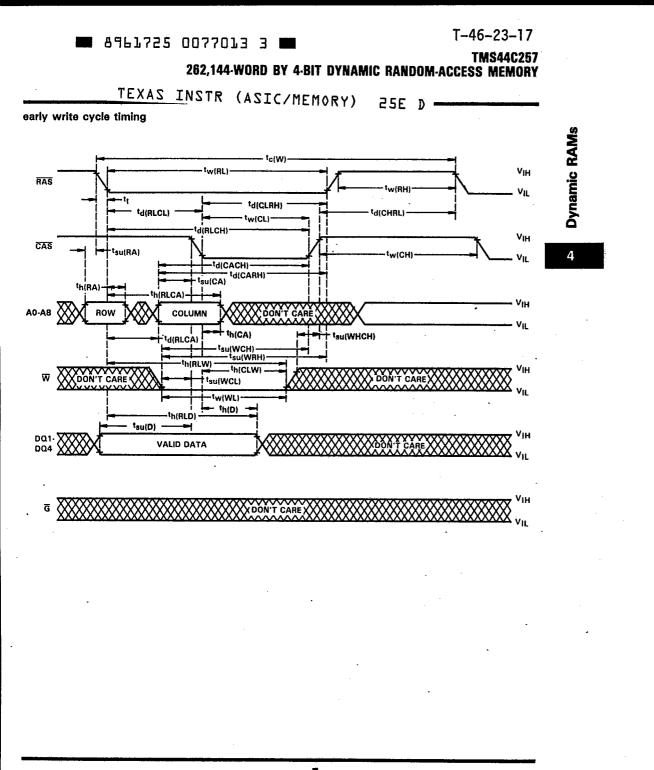

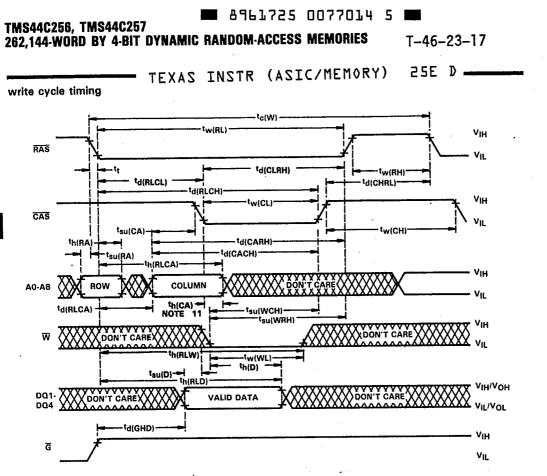

The read or write mode is selected through the write-enable (W) input. A logic high on the W input selects the read mode and a logic low selects the write mode. The write-enable terminal can be driven from standard TTL circuits without a pull-up resistor. The data input is disabled when the read mode is selected. When W goes low prior to CAS (early write), data out will remain in the high-impedance state for the entire cycle permitting a write operation with G grounded. The TMS44C257 latches the column addresses on write cycles with the later of  $\overline{CAS}$  or  $\overline{W}$  falling edge.

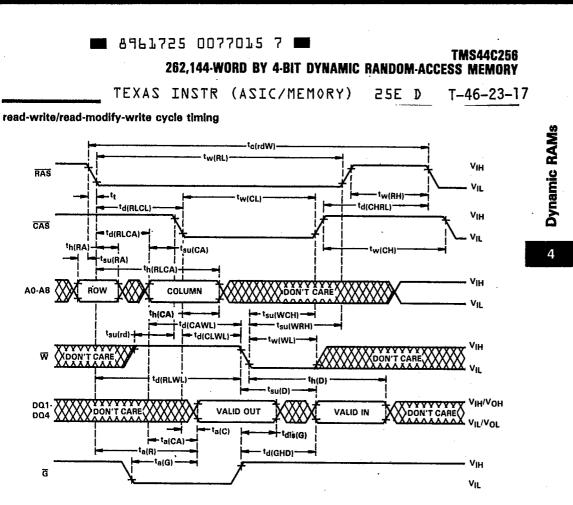

### data in (DQ1-DQ4)

Data is written during a write or read-modify-write cycle. Depending on the mode of operation, the falling edge of CAS or W strobes data into the on-chip data latch. In an early write cycle, W is brought low prior to CAS and the data is strobed in by CAS with setup and hold times referenced to this signal. In a delayed write or read-modify-write cycle,  $\overline{CAS}$  will already be low, thus the data will be strobed in by  $\overline{W}$  with setup and hold times referenced to this signal. In a delayed or read-modify-write cycle, G must be high to bring the output buffers to high impedance prior to impressing data on the I/O lines.

4-120

INSTRUMENTS POST OFFICE BOX 1443 . HOUSTON, TEXAS 77001

# 🔳 8961725 0076999 4 🔳

T-46-23-17

# TMS44C256, TMS44C257 262,144-Word by 4-bit dynamic random-access memories

### data out (DQ1-DQ4)

# TEXAS INSTR (ASIC/MEMORY) 25E D

The three-state output buffer provides direct TTL compatibility (no pull-up resistor required) with a fanout of two Series 74 TTL loads. Data out is the same polarity as data in. The output is in the high-impedance (floating) state until CAS and  $\overline{G}$  are brought low. In a read cycle the output becomes valid after the access time interval  $t_a(C)$  that begins with the negative transition of CAS as long as  $t_a(R)$  and  $\underline{f}_a(CA)$  are satisfied. The output becomes valid after the access time has elapsed and remains valid while CAS and  $\overline{G}$  are low. CAS or  $\overline{G}$  going high returns it to a high-impedance state. This is accomplished by bringing  $\overline{G}$  high prior to applying data, thus satisfying  $t_d(GHD)$ .

### output enable (G)

$\overline{G}$  controls the impedance of the output buffers. When  $\overline{G}$  is high, the buffers will remain in the high-impedance state. Bringing  $\overline{G}$  low during a normal cycle will activate the output buffers putting them in the low-impedance state. It is necessary for both  $\overline{RAS}$  and  $\overline{CAS}$  to be brought low for the output buffers to go into the low-impedance state. Once in the low-impedance state, they will remain in the low-impedance state until either  $\overline{G}$  or  $\overline{CAS}$  is brought high.

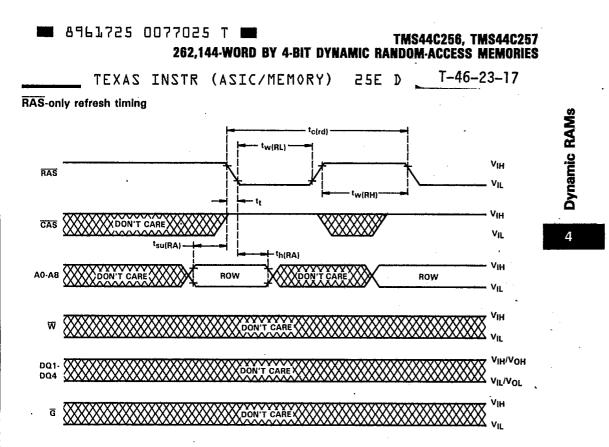

### refresh

A refresh operation must be performed at least once every eight milliseconds to retain data. This can be achieved by strobing each of the 512 rows (A0-A8). A normal read or write cycle will refresh all bits in each row that is selected. A RAS-only operation can be used by holding CAS at the high (inactive) level, thus conserving power as the output buffer remains in the high-impedance state. Externally generated addresses must be used for a RAS-only refresh. Hidden refresh may be performed while maintaining valid data at the output pin. This is accomplished by holding CAS at VIL after a read operation and cycling RAS after a specified precharge period, similar to a RAS-only refresh cycle.

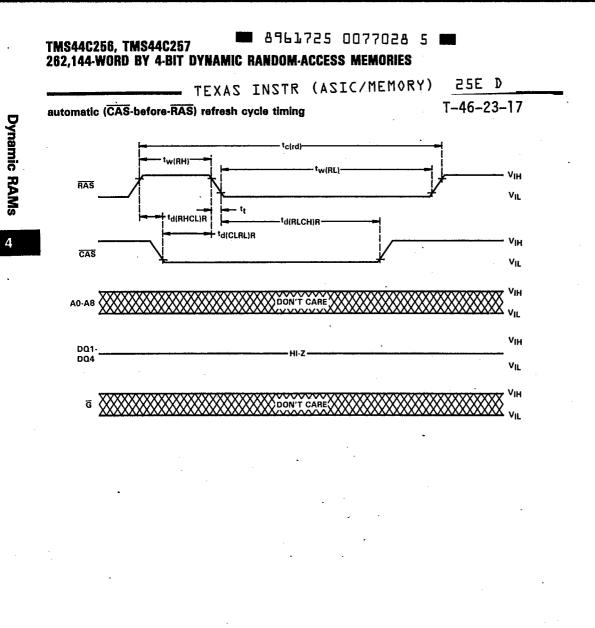

### CAS-before-RAS refresh

$\overline{CAS}$ -before- $\overline{RAS}$  refresh is utilized by bringing  $\overline{CAS}$  low earlier than  $\overline{RAS}$  [see parameter td(CLRL)R] and holding it low after  $\overline{RAS}$  falls [see parameter td(RLCH)R]. For successive  $\overline{CAS}$ -before- $\overline{RAS}$  refresh cycles,  $\overline{CAS}$  can remain low while cycling  $\overline{RAS}$ . The external address is ignored and the refresh address is generated internally. The external address is also ignored during the hidden refresh option.

### power up

To achieve proper device operation, an initial pause of 200  $\mu$ s followed by a minimum of eight initialization cycles is required after power up to the full V<sub>CC</sub> level.

### test function pin

During normal device operation, the TF pin must be either disconnected or biased at a voltage less than or equal to  $V_{CC}$ .

4-121

# 8961725 0077000 5 🛲

TMS44C256, TMS44C257 262,144 WORD BY 4-BIT DYNAMIC RANDOM ACCESS MEMORIES

T-46-23-17

25E D

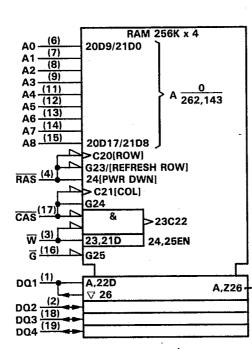

logic symbol<sup>†</sup>

TEXAS INSTR (ASIC/MEMORY)

<sup>†</sup>This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

4-122

TEXAS V INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Voltage range on any pin (see Note 1) | • | -1 V to 7 V    |

|---------------------------------------|---|----------------|

| Voltage range on VCC                  |   | 0 V to 7 V     |

| Short circuit output current          |   | 50 mA          |

| Power dissipation                     |   | <b>1</b> W     |

| Operating free-air temperature range  |   | 0°C to 70°C    |

| Storage temperature range             |   | -65°C to 150°C |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values in this data sheet are with respect to VSS.

# TMS44C256, TMS44C257 8961725 0077002 9

T-46-23-17

TEXAS INSTR (ASIC/MEMORY) 25E D -

# recommended operating conditions

|     |                                      | MIN | NOM | MAX | UNIT |

|-----|--------------------------------------|-----|-----|-----|------|

| Vcc | Supply voltage                       | 4.5 | 5   | 5.5 | V    |

| Vss | Supply voltage                       |     | 0   |     | V    |

| VIH | High-level input voltage             | 2.4 |     | 6.5 | V    |

| VIL | Low-level input voltage (see Note 2) | -1  |     | 0,8 | V    |

| TA  | Operating free-air temperature       | 0   |     | 70  | °Ĉ   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

|      |                                         | TEST                                                                                       | TMS440 | 2510 | TMS44C | 2512 | TMS44C | 2515 | UNIT |

|------|-----------------------------------------|--------------------------------------------------------------------------------------------|--------|------|--------|------|--------|------|------|

|      | PARAMETER                               | CONDITIONS                                                                                 | MIN    | MAX  | MIN    | MAX  | MIN    | MAX  | UNIT |

| VOH  | High-level output voltage               | IOH ≃ −5 mA                                                                                | 2.4    |      | 2.4    |      | 2.4    |      | V    |

| VOL  | Low-level output voltage                | I <sub>OL</sub> = 4.2 mA                                                                   |        | 0.4  |        | 0.4  |        | 0.4  | V    |

| tj   | Input current (leakage)                 | $V_{I} = 0 V \text{ to } 5.8 V,$ $V_{CC} = 5 V,$ All other pins $= 0 V \text{ to } V_{CC}$ |        | ±10  |        | ± 10 |        | ± 10 | μΑ   |

| ю    | Output current (leakage)                | $V_{O} = 0 V \text{ to } V_{CC},$ $V_{CC} = 5.5 V,$ $\overline{CAS} \text{ high}$          |        | ±10  |        | ±10  |        | ±10  | μA   |

| ICC1 | Read/write<br>cycle current             | $t_{c(rdW)} = minimum,$<br>V <sub>CC</sub> = 5.5 V                                         |        | 70   |        | 60   |        | 55   | mΑ   |

| ICC2 | Standby current                         | After 1 memory cycle,<br>RAS and CAS high,<br>VIH = 2.4 V                                  |        | 3    |        | 3    |        | 3    | mA   |

| Іссз | Average refresh current                 | t <sub>c(rdW)</sub> = minimum,<br>V <sub>CC</sub> = 5.5 V,<br>RAS cycling,<br>CAS high     |        | 65   |        | 55   |        | 50   | mA   |

| ICC4 | Average page current                    | t <sub>C(P)</sub> = minimum,<br>V <sub>CC</sub> = 5.5 V,<br>RAS low,<br>CAS cycling        |        | 45   |        | 35   |        | 30   | mA   |

| 1006 | Average static column<br>decode current | $t_{C(rdW)} = minimum,$<br>$V_{CC} = 5.5 V,$<br>RAS low,<br>CAS cycling                    |        | 45   | ,      | 35   |        | 30   | mA   |

**Dynamic RAMs**

4

# 🗰 8961725 0077003 O 📰

## T-46-23-17

ς.

# 262,144-WORD BY 4-BIT DYNAMIC RANDOM-ACCESS MEMORIES

# TEXAS INSTR (ASIC/MEMORY) 2.

0RY) 25E D 🔔

capacitance over recommended supply voltage range and operating free-air temperature range, f = 1 MHz (see Note 3)

|        | PARAMETER                             | MIN MAX | UNIT |

|--------|---------------------------------------|---------|------|

| Ci(A)  | Input capacitance, address inputs     | 6       | pF   |

| Ci(RC) | Input capacitance, strobe inputs      | 7       | pF   |

| Ci(W)  | Input capacitance, write-enable input | 7       | pF   |

| Co     | Output capacitance                    | 7       | pF   |

NOTE 3: V<sub>CC</sub> equal to 5.0 V  $\pm$  0.5 V and the bias on pins under test is 0.0 V.

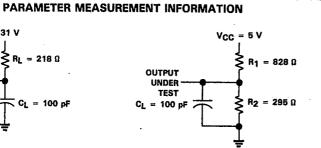

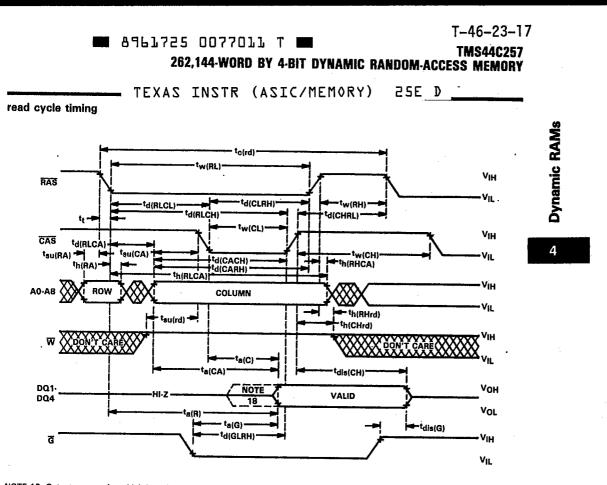

switching characteristics over recommended supply voltage range and operating free-air temperature range (see Figure 1)

|                      | PARAMETER                                                                              | ALT.             | TMS44C2 |     | TMS44C |     | TMS440 | 2515 | UNIT |

|----------------------|----------------------------------------------------------------------------------------|------------------|---------|-----|--------|-----|--------|------|------|

| _                    |                                                                                        | SYMBOL           | MIN     | MAX | MIN    | MAX | MIN    | MAX  |      |

| t <sub>a(C)</sub>    | Access time from CAS low                                                               | †CAC             |         | 25  |        | 30  |        | 40   | ns   |

| t <sub>a(CA)</sub>   | Access time from column address                                                        | †CAA             |         | 45  |        | 55  |        | 70   | ris  |

| t <sub>a(R)</sub>    | Access time from RAS low                                                               | TRAC             |         | 100 |        | 120 |        | 150  | ns   |

| t <sub>a(G)</sub>    | Access time from G low                                                                 | <sup>†</sup> GAC |         | 25  |        | 30  |        | 40   | រាន  |

| <sup>t</sup> a(CP)   | Access time from column precharge<br>(TMS44C256 only)                                  | <sup>t</sup> CAP |         | 50  |        | 60  |        | 75   | n\$  |

| <sup>t</sup> a(WHQ)  | Access time from ₩ high,<br>Static column decode mode<br>(see Note 4) (TMS44C257 only) | twra             |         | 30  | -      | 35  |        | 40   | ns   |

| t <sub>a</sub> (WLQ) | Access time from W low,<br>Static column decode mode<br>(see Note 4) (TMS44C257 only)  | tALW             |         | 95  |        | 115 |        | 120  | ns   |

| <sup>t</sup> dis(CH) | Output disable time after CAS<br>high (see Note 5)                                     | <sup>t</sup> OFF | 0       | 25  | 0      | 30  | 0      | 35   | ns   |

| <sup>t</sup> dis(G)  | Output disable time after G<br>high (see Note 5)                                       | tGOFF            | 0       | 25  | 0      | 30  | Ö      | 35   | n8   |

NOTES: 4. Read-modify-write operation only.

5. tdis(CH) and tdis(G) are specified when the output is no longer driven.

TEXAS TEXAS INSTRUMENTS POST OFFICE BOX 1443 • HOUSTON, TEXAS 77001

4-125

**Dynamic RAMs**

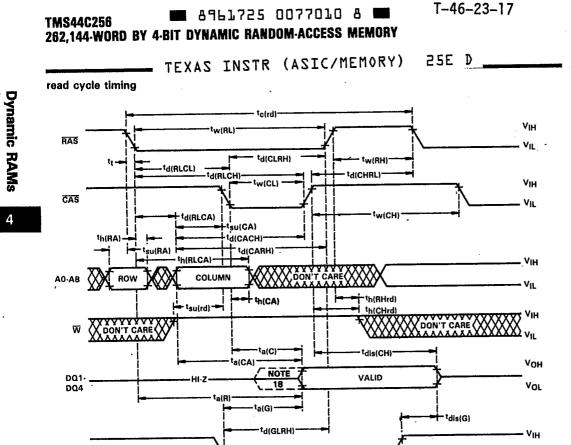

### ■ 8961725 0077004 2 TMS44C256 262,144-WORD BY 4-BIT DYNAMIC RANDOM-ACCESS MEMORY

### TEXAS INSTR (ASIC/MEMORY) 25E D

|                       |                                                         | ALT.              | TMS44 | C256-10 | TMS44 | C256-12 | TMS44    | C256-15 | UNI      |

|-----------------------|---------------------------------------------------------|-------------------|-------|---------|-------|---------|----------|---------|----------|

|                       |                                                         | SYMBOL            | MIN   | MAX     | MIN   | MAX     | MIN      | MAX     | 0.4      |

| t <sub>c(rd)</sub>    | Read cycle time (see Note 7)                            | tRC               | 190   |         | 220   |         | 260      |         | ns       |

| t <sub>c(W)</sub>     | Write cycle time                                        | twc               | 190   |         | 220   |         | 260      |         | ns       |

| t                     | Read-write/read-modify-write                            | tRWC              | 220   |         | 255   |         | 305      |         | ns       |

| t <sub>c(P)</sub>     | Page-mode read or write<br>cycle time (see Note 8)      | tPC               | 55    |         | 65    |         | 80       |         | n        |

| t <sub>c(PM)</sub>    | Page-mode read-modify-write<br>cycle time               | <sup>t</sup> PCM  | 85    |         | 100   |         | 125      |         | n        |

| tw(CH)                | Pulse duration, CAS high                                | tCP               | 10    |         | 15    |         | 25       |         | n        |

| tw(CL)                | Pulse duration, CAS low (see Note 9)                    | <sup>t</sup> CAS  | 26    | 10,000  | 30    | 10,000  | 40       | 10,000  | n        |

| tw(RH)                | Pulse duration RAS high (precharge)                     | tRP               | 80    |         | 90    |         | 100      |         | n        |

| tw(RL)                | Non-page-mode pulse duration,<br>RAS low (see Note 10)  | tRAS              | 100   | 10,000  | 120   | 10,000  | 150      | 10,000  | n        |

| t <sub>w(RL)</sub> P  | Page-mode pulse duration,<br>RAS low (see Note 10)      | <sup>t</sup> RASP | 100   | 100,000 |       | 100,000 | 150      | 100,000 | n        |

| tw(WL)                | Write pulse duration                                    | twp               | 15    |         | 20    |         | 25       |         | <u> </u> |

| t <sub>su(CA)</sub>   | Column-address setup time<br>before CAS low             | tASC              | 0     |         | 0     |         | 0        |         | n        |

| <sup>t</sup> su(RA)   | Row-address setup time<br>before RAS low                | tASR              | 0     |         | 0     |         | <u>.</u> |         | n        |

| t <sub>su(D)</sub>    | Data setup time before<br>W low (see Note 11)           | tDS               | 0     |         | 0     |         | 0        |         | n        |

| tsu(rd)               | Read setup time before<br>CAS low                       | <sup>t</sup> RCS  | 0     |         | 0     |         | 0        |         | n        |

| t <sub>su</sub> (WCL) | W-low setup time before<br>CAS low (see Note 12)        | twcs              | 0     |         | 0     |         | 0        |         | n        |

| t <sub>su</sub> (WCH) | W-low setup time before<br>CAS high                     | tCWL              | 25    |         | 30    |         | 40       |         | <b>_</b> |

| t <sub>su</sub> (WRH) | W-low setup time before<br>RAS high                     | <sup>t</sup> RWL  | 25    |         | 30    |         | 40       |         | г        |

| <sup>t</sup> h(CA)    | Column-address hold time<br>after CAS low (see Note 11) | tCAH              | 20    |         | 20    |         | 25       |         | г        |

| th(RA)                | Row-address hold time<br>after RAS low                  | tRAH              | 15    |         | 15    |         | 20       |         | r        |

Continued next page.

NOTES: 6. Timing measurements are referenced to VIL max and VIH min.

b. IIming measurements are reterenced to VIL max and VIH min.

7. All cycle times assume t<sub>t</sub> = 5 ns.

8. t<sub>c</sub>(P) > t<sub>w</sub>(CH) min + t<sub>w</sub>(CL) min + 2t<sub>t</sub>.

9. In a read-modify-write cycle, t<sub>d</sub>(CLWL) and t<sub>su</sub>(WCH) must be observed. Depending on the user's transition times, this may require additional CAS low time (t<sub>w</sub>(CL)).

10. In a read-modify-write cycle, t<sub>d</sub>(RLWL) and t<sub>su</sub>(WRH) must be observed. Depending on the user's transition times, this may require additional RAS low time (t<sub>w</sub>(RL)).

11. Later of CAS or W in write operations.

12. Early write operation on.

12. Early write operation only.

4-126

# 8961725 0077005 4 🔳

T-46-23-17

### TMS44C256 262,144-WORD BY 4-BIT DYNAMIC RANDOM-ACCESS MEMORY

TEXAS INSTR (ASIC/MEMORY)

25E D

timing requirements over recommended supply voltage range and operating free-air temperature range (continued)

|                      |                                                         | ALT,             | TMS440 | 256-10 | TMS44C | 256-12 | TMS44C | 256-15 | UNIT |

|----------------------|---------------------------------------------------------|------------------|--------|--------|--------|--------|--------|--------|------|

|                      |                                                         | SYMBOL           | MIN    | MAX    | MIN    | MAX    | MIN    | MAX    | UNIT |

| th(RLCA)             | Column-address hold time<br>after RAS low (see Note 13) | tAR              | .70    |        | 80     |        | 100    |        | ns   |

| <sup>t</sup> h(D)    | Data hold time after<br>CAS low (see Note 11)           | toh              | 20     |        | 25     |        | 30     |        | ns   |

| <sup>t</sup> h(RLD)  | Data hold time after<br>RAS low (see Note 13)           | <sup>t</sup> DHR | 70     |        | 85     |        | 110    |        | ns   |

| <sup>t</sup> h(CHrd) | Read hold time after<br>CAS high (see Note 15)          | tRCH             | 0      |        | 0      |        | 0      |        | ПŜ   |

| <sup>t</sup> h(RHrd) | Read hold time after<br>RAS high (see Note 15)          | tRRH             | 10     |        | 10     |        | 10     |        | កទ   |

| <sup>t</sup> h(CLW)  | Write hold time after<br>CAS low (see Note 12)          | twch             | 20     |        | 25     |        | 30     |        | ris  |

| <sup>t</sup> h(RLW)  | Write hold time after<br>RAS low (see Note 13)          | tWCR             | 70     |        | 85 '   |        | 100    |        | ns   |

| td(RLCH)             | Delay time, RAS low to CAS high                         | tCSH             | 100    |        | 120    |        | .150   |        | ns   |

| td(CHRL)             | ' Delay time, CAS high to<br>RAS low                    | tCRP             | 0      |        | 0      |        | 0      |        | ns   |

| td(CLRH)             | Delay time, CAS low to<br>RAS high                      | tRSH             | 25     |        | 30     |        | 40     |        | ns   |

| td(CLWL)             | Delay time, CAS low to<br>W low (see Note 4)            | tCWD             | 50     |        | 60     |        | 70     |        | ns   |

| td(RLCL)             | Delay time, RAS low to<br>CAS low (see Note 14)         | tRCD             | 25     | 75     | 25     | 90     | 30     | 110    | ns   |

| <sup>t</sup> d(RLCA) | Delay time, RAS low to column address (see Note 14)     | tRAD             | 20     | 55     | 20     | 65     | 25     | 80     | ns   |

| <sup>t</sup> d(CARH) | Delay time, column address<br>to RAS high               | tRAL             | 45     | · · ·  | 55     |        | 70     |        | ns   |

| td(CACH)             | Delay time, column address<br>to CAS high               | <sup>†</sup> CAL | 45     |        | 55     |        | 70     |        | ns   |

| td(RLWL)             | Delay time, RAS low to<br>W low (see Note 4)            | tRWD             | 100    |        | 120    |        | 150    |        | ns   |

| td(CAWL)             | Delay time, column address<br>to W low (see Note 4)     | tAWD             | 45     |        | 55     |        | 70     |        | ns   |

| d(GHD)               | Delay time, G high before<br>data at DQ                 | tGDD             | 25     |        | 30     |        | 40     |        | ns   |

| d(GLRH)              | Delay time, G low<br>to RAS high                        | tGSR             | 20     |        | 25     |        | 35     |        | ns   |

**Dynamic RAMs**

4

.

Continued next page. NOTES: 4. Read-modify-write operation only. 11. Later of CAS or W in write operations.

12. Early write operation only.

13. The minimum value is measured when  $t_d(RLCL)$  is set to  $t_d(RLCL)$  min as a reference. 14. Maximum value specified only to guarantee access time. 15. Either  $t_h(RHrd)$  or  $t_h(CHrd)$  must be satisfied for a read cycle.

ij TEXAS INSTRUMENTS POST OFFICE BOX 1443 . HOUSTON, TEXAS 77001

### TMS44C256 262,144-WORD BY 4-BIT DYNAMIC RANDOM-ACCESS MEMORY

# TEXAS INSTR (ASIC/MEMORY)

25E D

timing requirements over recommended supply voltage range and operating free-air temperature range (concluded)

|                       |                                                  | ALT.             | ALT. TM\$44C256-10 |     | TMS44C | 256-12 | TMS44C256-15 |     | UNIT |

|-----------------------|--------------------------------------------------|------------------|--------------------|-----|--------|--------|--------------|-----|------|

|                       |                                                  | SYMBOL           | MIN                | MAX | MIN    | MAX    | MIN          | MAX |      |

| <sup>t</sup> d(RLCH)R | Delay time, RAS low to<br>CAS high (see Note 16) | <sup>t</sup> CHR | 25                 |     | 25     |        | 30           |     | ns   |

| td(CLRL)R             | Delay time, CAS low to<br>RAS low (see Note 16)  | tCSR             | 10                 |     | 10     |        | 15           |     | ns   |

| td(RHCL)R             | Delay time, RAS high to<br>CAS low (see Note 16) | tRPC             | 0                  |     | 0      |        | 0            |     | ns   |

| trf                   | Refresh time interval                            | tREF             |                    | 8   |        | 8      |              | 8   | TT)S |

| t,                    | Transition time                                  | ें<br>प          | 3                  | 50  | 3      | 50     | 3            | 50  | ns   |

NOTE 16: CAS-before-RAS refresh only.

.

.

# 8961725 0077007 8 🔳

# T-46-23-17

### TMS44C257 262,144-WORD BY 4-BIT DYNAMIC RANDOM-ACCESS MEMORY

### TEXAS INSTR (ASIC/MEMORY) 25E D

timing requirements over recommended supply voltage range and operating free-air temperature range

|                       |                                                                        | ALT.               | TMS44 | TMS44C257-10 |     | C257-12                               | TMS44 | C257-15 |           |

|-----------------------|------------------------------------------------------------------------|--------------------|-------|--------------|-----|---------------------------------------|-------|---------|-----------|

|                       |                                                                        | SYMBOL             | MIN   | MAX          | MIN | MAX                                   | MIN   | MAX     | UNIT      |

| tc(rd)                | Read cycle time (see Note 7)                                           | tRC                | 190   |              | 220 |                                       | 260   |         | ns        |

| t <sub>c</sub> (W)    | Write cycle time                                                       | tWC                | 190   |              | 220 |                                       | 260   |         | ns        |

| <sup>t</sup> c(rdW)   | Read-write/read-modify-write<br>cycle time                             | tRWC               | 220   |              | 265 |                                       | 305   | -       | ns        |

| <sup>t</sup> c(rd)SC  | Static column decode mode<br>read-only cycle time                      | tSCR               | 50    |              | 60  |                                       | 90    |         | лз        |

| tc(W)SC               | Static column decode mode<br>write-only cycle time                     | tcsw               | 50    |              | 60  |                                       | 90    |         | ns        |

| <sup>t</sup> c(rdW)SC | Static column decode mode<br>read-modify-write cycle time              | <sup>t</sup> SCRDW | 100   |              | 120 |                                       | 150   |         | ns        |

| tw(CH)                | Pulse duration, CAS high                                               | tCP                | 10    |              | 15  |                                       | 25    |         | ris       |

| tw(CL)                | Pulse duration, CAS low (see Note 9)                                   | tCAS               | 20    | 10,000       | 25  | 10,000                                | 35    | 10,000  | ns        |

| tw(RH)                | Pulse duration, RAS high (precharge)                                   | tRP                | 80    |              | 90  |                                       | 100   |         | <b>N8</b> |

| tw(RL)                | Non-static column decode mode<br>pulse duration, RAS low (see Note 10) | tRAS               | 100   | 10,000       | 120 | 10,000                                | 150   | 10,000  | ńs        |

| <sup>t</sup> w(RL)P   | Static column decode mode -<br>pulse duration, RAS low (see Note 10)   | <sup>t</sup> RASP  | 100   | 100,000      | 120 | 100,000                               | 150   | 100,000 | ns        |

| tw(WL)                | Write pulse duration                                                   | twp                | 15    |              | 20  |                                       | 25    |         | ns        |

| tw(CA)                | Static column decode mode<br>column address pulse duration             | tADP               | 45    |              | 55  |                                       | 70    |         | ns        |

| <sup>t</sup> w(WH)    | Static column decode mode<br>W high pulse duration                     | tWI                | 10    |              | 15  |                                       | 25    |         | ns        |

| t <sub>su(CA)</sub>   | Column-address setup times<br>before CAS low or W low (see Note 11)    | tASC               | 0     |              | 0   |                                       | 0     |         | ns        |

| t <sub>su(RA)</sub>   | Row address setup time<br>before RAS low                               | tASR               | 0     |              | 0   |                                       | 0     |         | ns        |

| t <sub>su(D)</sub>    | Data setup time before<br>W low (see Note 11)                          | tDS                | 0     |              | 0   |                                       | 0     |         | ns        |

|                       | Read setup time before<br>CAS low                                      | tRCS               | Ö     |              | 0   | · · · · · · · · · · · · · · · · · · · | 0     |         | ns        |

| 1                     | W-low setup time before<br>CAS low (see Note 12)                       | twcs               | Q     |              | 0   |                                       | 0     |         | ns        |