- Organization . . .

1048576 x 16 Bits x 4 Banks

2097152 x 8 Bits x 4 Banks

4194304 x 4 Bits x 4 Banks

- 3.3-V Power Supply (±10% Tolerance)

- Four Banks for On-Chip Interleaving for x8/x16 (Gapless Access) Depending on Organizations

- High Bandwidth Up to 125-MHz Data Rates

- Burst Length Programmable to 1, 2, 4, 8

- Programmable Output Sequence Serial or Interleave

- Chip-Select and Clock-Enable for Enhanced-System Interfacing

- Cycle-by-Cycle DQ Bus Mask Capability

- Only x16 SDRAM Configuration Supports

Upper-/Lower-Byte Masking Control

- Programmable CAS Latency From Column Address

- Performance Ranges:

- Pipeline Architecture (Single-Cycle Architecture)

- Single Write/Read Burst

- Self-Refresh Capability (Every 16 μs)

- Low-Noise, Low-Voltage Transistor-Transistor Logic (LVTTL) Interface

- Power-Down Mode

- Compatible With JEDEC Standards

- 16K RAS-Only Refresh (Total for All Banks)

- 4K Auto Refresh (Total for All Banks)/64 ms

- Automatic Precharge and Controlled Precharge

- Burst Interruptions Supported:

- Read Interruption

- Write Interruption

- Precharge Interruption

- Support Clock-Suspend Operation (Hold Command)

- Intel PC100 Compliant (-8 and -8A parts)

|            | SYNCHF<br>CLOCK<br>TIM | CYLE  |        | S TIME<br>K TO<br>PUT | REFRESH<br>INTERVAL |

|------------|------------------------|-------|--------|-----------------------|---------------------|

|            | tCK3                   | tCK2  | tAC3   | <sup>t</sup> AC2      | <sup>t</sup> REF    |

| '664xx4-8  | 8 ns                   | 10 ns | 6 ns   | 6 ns                  | 64 ms               |

| '664xx4-8A | 8 ns                   | 15 ns | 6 ns   | 7.5 ns                | 64 ms               |

| '664xx4-10 | 10 ns                  | 15 ns | 7.5 ns | 7.5 ns                | 64 ms               |

## description

The TMS664xx4 series are 67108864-bit synchronous dynamic random-access memory (SDRAM) devices which are organized as follow:

- Four banks of 1 048 576 words with 16 bits per word

- Four banks of 2097152 words with 8 bits per word

- Four banks of 4194304 words with 4 bits per word

All inputs and outputs of the TMS664xx4 series are compatible with the LVTTL interface.

The SDRAM employs state-of-the-art technology for high-performance, reliability, and low power. All inputs and outputs are synchronized with the CLK input to simplify system design and to enhance use with high-speed microprocessors and caches.

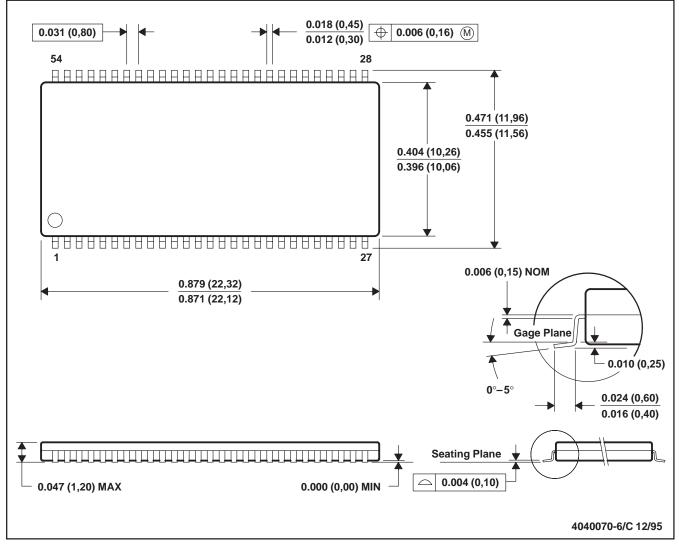

The TMS664xx4 SDRAM is available in a 400-mil, 54-pin surface-mount thin small-outline package (TSOP) (DGE suffix).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Copyright © 1998, Texas Instruments Incorporated

SMOS695A - APRIL 1998 - REVISED JULY 1998

TMS664xx4 (LVTTL) DGE PACKAGE (TOP VIEW)

|          |          |          |    | 4M x 16          |    |      |      |      |

|----------|----------|----------|----|------------------|----|------|------|------|

|          |          |          |    | 8M x 8           |    |      |      |      |

|          |          |          |    | 16M x 4          |    | _    |      |      |

| Vcc      | Vcc      | Vcc      | 1  |                  | 54 | VSS  | VSS  | VSS  |

| DQ0      | DQ0      | NC       | 2  |                  | 53 | NC   | DQ7  | DQ15 |

| VCCQ     | VCCQ     | VCCQ     | 3  |                  | 52 | VSSQ | VSSQ | VSSQ |

| DQ1      | NC       | NC       | 4  |                  | 51 | NC   | NC   | DQ14 |

| DQ2      | DQ1      | DQ0      | 5  |                  | 50 | DQ3  | DQ6  | DQ13 |

| VSSQ     | VSSQ     | VSSQ     | 6  |                  | 49 | VCCQ | VCCQ | VCCQ |

| DQ3      | NC       | NC       | 7  |                  | 48 | NC   | NC   | DQ12 |

| DQ4      | DQ2      | NC       | 8  |                  | 47 | NC   | DQ5  | DQ11 |

| Vccq     | Vccq     | VCCQ     | 9  |                  | 46 | VSSQ | VSSQ | VSSQ |

| DQ5      | NC       | NC       | 10 |                  | 45 | NC   | NC   | DQ10 |

| DQ6      | DQ3      | DQ1      | 11 | 54-Pin           | 44 | DQ2  | DQ4  | DQ9  |

| VSSQ     | VSSQ     | VSSQ     | 12 | Plastic          | 43 | VCCQ | Vccq | VCCQ |

| DQ7      | NC       | NC       | 13 | TSOP-II          | 42 | NC   | NC   | DQ8  |

| Vcc      | Vcc      | Vcc      | 14 | (Pitch = 0.8 mm) | 41 | VSS  | VSS  | VSS  |

| DQML     | NC       | NC       | 15 |                  | 40 | NC   | NC   | NC   |

| W        | W        | W        | 16 |                  | 39 | DQM  | DQM  | DQMU |

| CAS      | CAS      | CAS      | 17 |                  | 38 | CLK  | CLK  | CLK  |

| RAS      | RAS      | RAS      | 18 |                  | 37 | CKE  | CKE  | CKE  |

| CS       | CS       | CS       | 19 |                  | 36 | NC   | NC   | NC   |

| A13, BS0 | A13, BS0 | A13, BS0 | 20 |                  | 35 | A11  | A11  | A11  |

| A12, BS1 | A12, BS1 | A12, BS1 | 21 |                  | 34 | A9   | A9   | A9   |

| A10, AP  | A10, AP  | A10, AP  | 22 |                  | 33 | A8   | A8   | A8   |

| A0       | A0       | A0       | 23 |                  | 32 | A7   | A7   | A7   |

| A1       | A1       | A1       | 24 |                  | 31 | A6   | A6   | A6   |

| A2       | A2       | A2       | 25 |                  | 30 | A5   | A5   | A5   |

| A3       | A3       | A3       | 26 |                  | 29 | A4   | A4   | A4   |

| Vcc      | Vcc      | Vcc      | 27 |                  | 28 | VSS  | VSS  | VSS  |

|     | ROW<br>ADDR | COL<br>ADDR |

|-----|-------------|-------------|

| x4  | A0-A13      | A0-A9       |

| x8  | A0-A13      | A0-A8       |

| x16 | A0-A13      | A0-A7       |

A10 Auto Precharge

| BANKS | BANK-SELECT<br>ADDRESS |

|-------|------------------------|

| 4     | A13-A12                |

SMOS695A - APRIL 1998 - REVISED JULY 1998

|                                                                                                                     | PIN NOMENCLATURE                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0:13]                                                                                                             | Address Inputs      Four Banks      Column      A0 -A9 Column Addr (x4)      A0 -A8 Column Addr (x8)      A0 -A7 Column Addr (x16)      A10 Auto Precharge      A12 - A13 Bank-Select |

| _                                                                                                                   | Row<br>A0 – A11 Row Addrs<br>A12 – A13 Bank-Select                                                                                                                                    |

| W    RAS    CAS    CKE    CLK    CS    DQ[0:3]    DQ[0:7]    DQ[0:15]    DQMU/D    DQM    NC    VCCQ    VSS    VSSQ |                                                                                                                                                                                       |

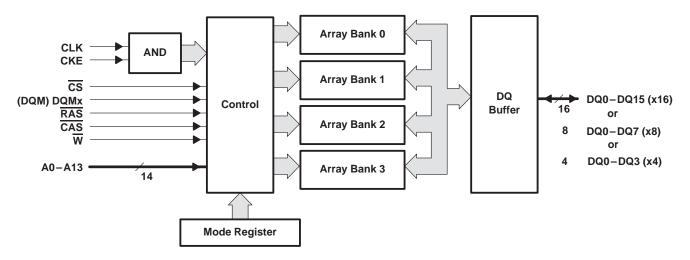

# functional block diagram (four banks)

SMOS695A - APRIL 1998 - REVISED JULY 1998

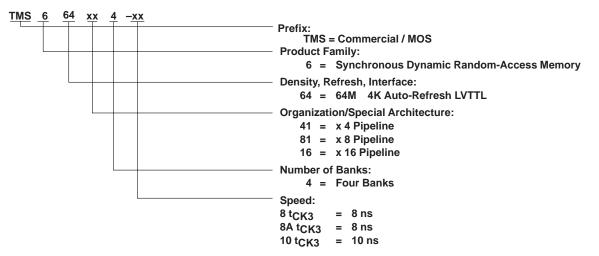

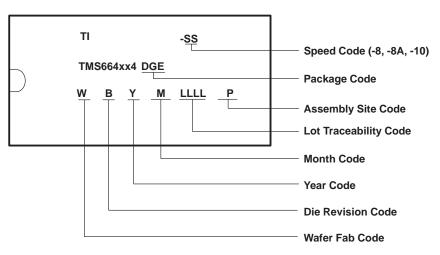

# device numbering conventions (SDRAM family nomenclature)

#### operation

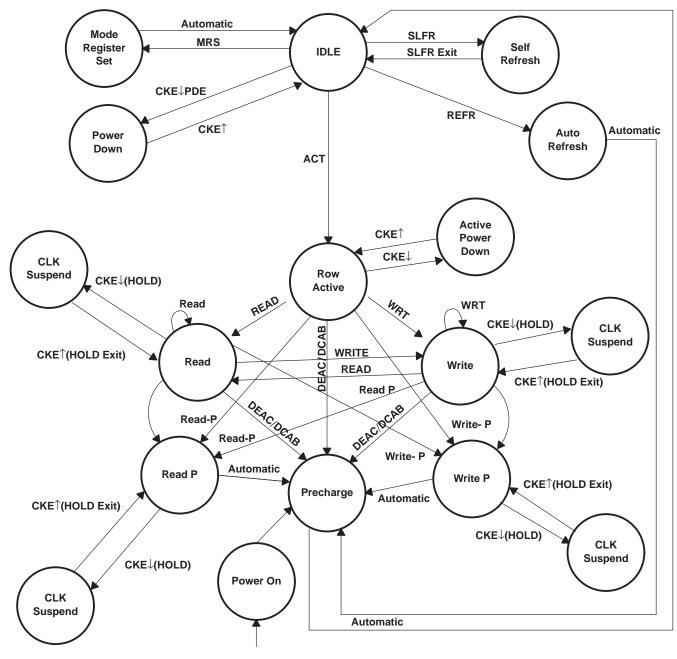

All inputs to the '664xx4 SDRAM are latched on the rising edge of the system (synchronous) clock. The outputs (DQ0-DQ3 for x4, DQ0-DQ7 for x8, and DQ0-DQ15 for x16) are also referenced to the rising edge of CLK. The '664xx4 has four banks that are accessed independently. A bank must be activated before it can be accessed (read from or written to). Refresh cycles refresh all banks alternately.

Five basic commands or functions control most operations of the '664xx4:

- Bank activate/row-address entry

- Column-address entry/write operation

- Column-address entry/read operation

- Bank deactivate

- Auto-refresh/self-refresh entry

Additionally, operations can be controlled by three methods: using chip select  $\overline{(CS)}$  to select/deselect the devices, using DQMx to enable/mask the DQ signals on a cycle-by-cycle basis, or using CKE to suspend (or gate) the CLK input. The device contains a mode register that must be programmed for proper operation.

Table 1 through Table 3 show the various operations that are available on the '664xx4. These truth tables identify the command and/or operations and their respective mnemonics. Each truth table is followed by a legend that explains the abbreviated symbols. An access operation refers to any READ (READ-P) or WRT (WRT-P) command in progress at cycle n. Access operations include the cycle upon which the READ (READ-P) or WRT (WRT-P) command is entered and all subsequent cycles through the completion of the access burst.

SMOS695A - APRIL 1998 - REVISED JULY 1998

operation (continued)

Figure 1. State Diagram

operation (continued)

| COMMAND                                                   | STATE OF<br>BANK(S) | cs | RAS | CAS | w | A13 | A12 | A11 | A10 | A9-A0                                                                                               | MNEMONIC |

|-----------------------------------------------------------|---------------------|----|-----|-----|---|-----|-----|-----|-----|-----------------------------------------------------------------------------------------------------|----------|

| Mode register set                                         | All Banks =<br>deac | L  | L   | L   | L | х   | х   | х   | х   | A9 = V, A8 = 0,<br>A7 = 0, A6 - A0 = V                                                              | MRS      |

| Bank deactivate (precharge)                               | Х                   | L  | L   | Н   | L | BS  | BS  | Х   | L   | Х                                                                                                   | DEAC     |

| Deactivate all banks                                      | Х                   | L  | L   | Н   | L | Х   | Х   | Х   | Н   | Х                                                                                                   | DCAB     |

| Bank activate/row-address entry                           | SB = deac           | L  | L   | н   | н | BS  | BS  | V   | V   | V                                                                                                   | ACTV     |

| Column-address entry/write operation                      | SB = actv           | L  | Н   | L   | L | BS  | BS  | x   | L   | A0 - A7 = V,<br>A8 - A9 = X,  for  x16<br>A0 - A8 = V,<br>A9 = X,  for  x8<br>A0 - A9 = V,  for  x4 | WRT      |

| Column-address entry/write operation with auto-deactivate | SB = actv           | L  | н   | L   | L | BS  | BS  | x   | Н   | A0 - A7 = V,<br>A8 - A9 = X,  for x16<br>A0 - A8 = V,<br>A9 = X,  for x8<br>A0 - A9 = V,  for x4    | WRT-P    |

| Column-address entry/read operation                       | SB = actv           | L  | н   | L   | н | BS  | BS  | x   | L   | A0 - A7 = V,<br>A8 - A9 = X,  for x16<br>A0 - A8 = V,<br>A9 = X,  for x8<br>A0 - A9 = V,  for x4    | READ     |

| Column-address entry/read operation with auto-deactivate  | SB = actv           | L  | н   | L   | н | BS  | BS  | x   | н   | A0 - A7 = V,<br>A8 - A9 = X, for x16<br>A0 - A8 = V,<br>A9 = X, for x8<br>A0 - A9 = V, for x4       | READ-P   |

| No operation                                              | Х                   | L  | Н   | Н   | н | Х   | Х   | Х   | Х   | Х                                                                                                   | NOOP     |

| Control-input inhibit/no operation                        | Х                   | н  | х   | х   | х | х   | х   | х   | х   | Х                                                                                                   | DESL     |

| Auto refresh§                                             | All banks=<br>deac  | L  | L   | L   | н | х   | х   | х   | х   | Х                                                                                                   | REFR     |

Table 1. Basic Command Truth Table<sup>†‡</sup>

<sup>†</sup> For execution of these commands on cycle n, CKE must satisfy requirements for one of the following:

— CKE (n-1) must be high

- t<sub>CESP</sub> from power-down exit (PDE)

- tIS and nCLE from clock-suspend (HOLD) exit

- t<sub>CESP</sub> and t<sub>RC</sub> from self-refresh (SLFR) exit.

DQMx (n) is a don't care

§ Auto-refresh or self-refresh entry requires that all banks be deactivated or be in an idle state prior to the command entry. An REFR command turns on four rows (one from each bank; therefore, 4096 REFR commands fully refresh the memory).

| Legend | u.                                          |      |   |                                     |

|--------|---------------------------------------------|------|---|-------------------------------------|

| n =    | CLK cycle number                            | actv | = | Activated                           |

| L =    | Logic low                                   | deac | = | Deactivated                         |

|        |                                             | BS   | = | Logic:                              |

|        |                                             |      |   | (A12 = 0, A13 = 0) select bank 0    |

| H =    | Logic high                                  |      |   | (A12 = 1, A13 = 0) select bank 1    |

|        |                                             |      |   | (A12 = 0, A13 = 1) select bank 2    |

|        |                                             |      |   | (A12 = 1, A13 = 1) select bank 3    |

| X =    | Don't care (either logic high or logic low) | SB   | = | Select bank by A12 – A13 at cycle n |

| V =    | Valid                                       |      |   |                                     |

SMOS695A - APRIL 1998 - REVISED JULY 1998

# operation (continued)

| COMMAND                    | STATE OF BANK(S)                    | CKE<br>(n-1) | CKE<br>(n) | CS<br>(n) | RAS<br>(n) | CAS<br>(n) | W<br>(n) | MNEMONIC |  |

|----------------------------|-------------------------------------|--------------|------------|-----------|------------|------------|----------|----------|--|

| Self-refresh entry         | All banks = deac                    | н            | L          | L         | L          | L          | H        | SLFR     |  |

| Power-down entry at n + 1‡ | All banks = no<br>access operation§ | н            | L          | х         | х          | х          | х        | PDE      |  |

| Self-refresh exit          | All banks =                         | L            | Н          | L         | Н          | Н          | Н        | —        |  |

|                            | self-refresh                        | L            | Н          | Н         | Х          | Х          | Х        | —        |  |

| Power-down exit¶           | All banks =<br>power down           | L            | н          | х         | х          | х          | х        | —        |  |

| CLK suspend at n+1         | All banks = access<br>operation§    | н            | L          | х         | х          | х          | х        | HOLD     |  |

| CLK suspend exit at n + 1  | All banks = access<br>operation§    | L            | н          | х         | х          | х          | х        | _        |  |

## Table 2. Clock-Enable (CKE) Command Truth Table<sup>†</sup>

<sup>†</sup> For execution of these commands, A0–A13 (n) and DQMx (n) are don't care entries.

<sup>‡</sup>On cycle n, the device executes the respective command (listed in Table 1). On cycle (n+1), the device enters the power-down mode.

§ A bank is no longer in an access operation one cycle after the last data-out cycle of a READ (READ-P) operation, and two cycles after the last data-in cycle of a WRT (WRT-P) operation. Neither the PDE nor the HOLD command is allowed on the cycle immediately following the last data-in cycle of a WRT (WRT-P) operation.

If setup time from CKE high to the next CLK high satisfies tCESP, the device executes the respective command (listed in Table 1). Otherwise, either the DESL or NOOP command must be applied before any other command.

Legend:

= CLK cycle number n

L = Logic low

Н = Logic high

= Don't care (either logic high or logic low) Х

deac = Deactivated

SMOS695A - APRIL 1998 - REVISED JULY 1998

# operation (continued)

## Table 3. Data/Output Mask Enable (DQM) Command Truth Table<sup>†‡</sup>

| COMMAND         | STATE OF BANK(S)                          | DQM<br>(DQML/DQMU)§<br>(n) | D0-D3 (x4)<br>D0-D7 (x8)<br>D0-D15 (x16)<br>(n) | Q0-Q3 (x4)<br>Q0-Q7 (x8)<br>Q0-Q15 (x16)<br>(n+2) | MNEMONIC |

|-----------------|-------------------------------------------|----------------------------|-------------------------------------------------|---------------------------------------------------|----------|

| —               | Any bank = deac                           | Х                          | N/A                                             | Hi-Z                                              | —        |

| _               | Any bank = actv<br>(no access operation)¶ | Х                          | N/A                                             | Hi-Z                                              | _        |

| Data-in enable  | Any bank = write                          | L                          | V                                               | N/A                                               | ENBL     |

| Data-in mask    | Any bank = write                          | Н                          | М                                               | N/A                                               | MASK     |

| Data-out enable | Any bank = read                           | L                          | N/A                                             | V                                                 | ENBL     |

| Data-out mask   | Any bank = read                           | Н                          | N/A                                             | Hi-Z                                              | MASK     |

<sup>†</sup> For execution of these commands on cycle n, one of the following must be true:

CKE (n-1) must be high

- t<sub>CESP</sub> from power-down exit (PDE)

- nCLE from clock-suspend (HOLD) exit

tcesp and tRC from self-refresh (SLFR) exit

$\pm \overline{CS}$  (n), RAS (n), CAS (n), W (n), and A0–A13 (n) are don't care entries.

§ DQM is used for x4/x8 (no byte control). DQM (n) operations correspond to D0−D7 and Q0−Q7 events. DQML/DQMU are used for x16 (for byte-control). DQML (n) operations correspond to D0−D7 and Q0−Q7 events, while DQMU (n) operations correspond to D8−D15 and Q8−Q15 events.

A bank is no longer in an access operation one cycle after the last data-out cycle of a READ (READ-P) operation, and two cycles after the last data-in cycle of a WRT (WRT-P) operation. Neither the PDE nor the HOLD command is allowed on the cycle immediately following the last data-in cycle of a WRT (WRT-P) operation.

= Activated

Deactivated

actv

deac =

Legend:

- n = CLK cycle number

- L = Logic low

- H = Logic high

- X = Don't care (either logic high or logic low)

- write = Activated and accepting data in on cycle n

read = Activated and delivering data out on cycle n + 2

- V = Valid

- M = Masked input data

- N/A = Not applicable

- Hi-Z = High impedance

#### burst sequence

All data for the '664xx4 is written or read in a *burst* fashion, that is, a single starting address is entered into the device and then the '664xx4 internally accesses a sequence of locations based on that starting address. Some of the subsequent accesses after the first one can be at preceding, as well as succeeding, column addresses depending on the starting address entered. This sequence can be programmed to follow either a serial burst or an interleave burst (see Table 4 through Table 6). The length of the burst sequence can be user-programmed to be 1, 2, 4, or 8. After a read burst is completed (as determined by the programmed burst length), the outputs are in the high-impedance state until the next read access is initiated.

|             | INTERNAL COLUMN ADDRESS A0 |     |        |     |  |  |  |  |  |  |

|-------------|----------------------------|-----|--------|-----|--|--|--|--|--|--|

|             | DECI                       | MAL | BINARY |     |  |  |  |  |  |  |

|             | START                      | 2ND | START  | 2ND |  |  |  |  |  |  |

| Serial      | 0                          | 1   | 0      | 1   |  |  |  |  |  |  |

| Senai       | 1                          | 0   | 1      | 0   |  |  |  |  |  |  |

| Interleave  | 0                          | 1   | 0      | 1   |  |  |  |  |  |  |

| IIIIeiieave | 1                          | 0   | 1      | 0   |  |  |  |  |  |  |

## Table 4. 2-Bit Burst Sequences

|              |       |     | NTERNAI | COLUM |        | S A1-A | )   |     |  |  |

|--------------|-------|-----|---------|-------|--------|--------|-----|-----|--|--|

|              |       |     | IMAL    |       | BINARY |        |     |     |  |  |

|              | START | 2ND | 3RD     | 4TH   | START  | 2ND    | 3RD | 4TH |  |  |

| Serial       | 0     | 1   | 2       | 3     | 00     | 01     | 10  | 11  |  |  |

|              | 1     | 2   | 3       | 0     | 01     | 10     | 11  | 00  |  |  |

|              | 2     | 3   | 0       | 1     | 10     | 11     | 00  | 01  |  |  |

|              | 3     | 0   | 1       | 2     | 11     | 00     | 01  | 10  |  |  |

|              | 0     | 1   | 2       | 3     | 00     | 01     | 10  | 11  |  |  |

| late de auro | 1     | 0   | 3       | 2     | 01     | 00     | 11  | 10  |  |  |

| Interleave   | 2     | 3   | 0       | 1     | 10     | 11     | 00  | 01  |  |  |

|              | 3     | 2   | 1       | 0     | 11     | 10     | 01  | 00  |  |  |

#### Table 5. 4-Bit Burst Sequences

## burst sequence (continued)

|            |       |         |     |     | I   | NTER | AL CO |     | IN ADDRESS A2-A0 |        |     |     |     |     |     |     |

|------------|-------|---------|-----|-----|-----|------|-------|-----|------------------|--------|-----|-----|-----|-----|-----|-----|

|            |       | DECIMAL |     |     |     |      |       |     |                  | BINARY |     |     |     |     |     |     |

|            | START | 2ND     | 3RD | 4TH | 5TH | 6TH  | 7TH   | 8TH | START            | 2ND    | 3RD | 4TH | 5TH | 6TH | 7TH | 8TH |

|            | 0     | 1       | 2   | 3   | 4   | 5    | 6     | 7   | 000              | 001    | 010 | 011 | 100 | 101 | 110 | 111 |

|            | 1     | 2       | 3   | 4   | 5   | 6    | 7     | 0   | 001              | 010    | 011 | 100 | 101 | 110 | 111 | 000 |

|            | 2     | 3       | 4   | 5   | 6   | 7    | 0     | 1   | 010              | 011    | 100 | 101 | 110 | 111 | 000 | 001 |

| Serial     | 3     | 4       | 5   | 6   | 7   | 0    | 1     | 2   | 011              | 100    | 101 | 110 | 111 | 000 | 001 | 010 |

| 4<br>5     | 4     | 5       | 6   | 7   | 0   | 1    | 2     | 3   | 100              | 101    | 110 | 111 | 000 | 001 | 010 | 011 |

|            | 5     | 6       | 7   | 0   | 1   | 2    | 3     | 4   | 101              | 110    | 111 | 000 | 001 | 010 | 011 | 100 |

|            | 6     | 7       | 0   | 1   | 2   | 3    | 4     | 5   | 110              | 111    | 000 | 001 | 010 | 011 | 100 | 101 |

|            | 7     | 0       | 1   | 2   | 3   | 4    | 5     | 6   | 111              | 000    | 001 | 010 | 011 | 100 | 101 | 110 |

|            | 0     | 1       | 2   | 3   | 4   | 5    | 6     | 7   | 000              | 001    | 010 | 011 | 100 | 101 | 110 | 111 |

|            | 1     | 0       | 3   | 2   | 5   | 4    | 7     | 6   | 001              | 000    | 011 | 010 | 101 | 100 | 111 | 110 |

|            | 2     | 3       | 0   | 1   | 6   | 7    | 4     | 5   | 010              | 011    | 000 | 001 | 110 | 111 | 100 | 101 |

| Interleave | 3     | 2       | 1   | 0   | 7   | 6    | 5     | 4   | 011              | 010    | 001 | 000 | 111 | 110 | 101 | 100 |

| Interleave | 4     | 5       | 6   | 7   | 0   | 1    | 2     | 3   | 100              | 101    | 110 | 111 | 000 | 001 | 010 | 011 |

|            | 5     | 4       | 7   | 6   | 1   | 0    | 3     | 2   | 101              | 100    | 111 | 110 | 001 | 000 | 011 | 010 |

|            | 6     | 7       | 4   | 5   | 2   | 3    | 0     | 1   | 110              | 111    | 100 | 101 | 010 | 011 | 000 | 001 |

|            | 7     | 6       | 5   | 4   | 3   | 2    | 1     | 0   | 111              | 110    | 101 | 100 | 011 | 010 | 001 | 000 |

#### Table 6. 8-Bit Burst Sequences

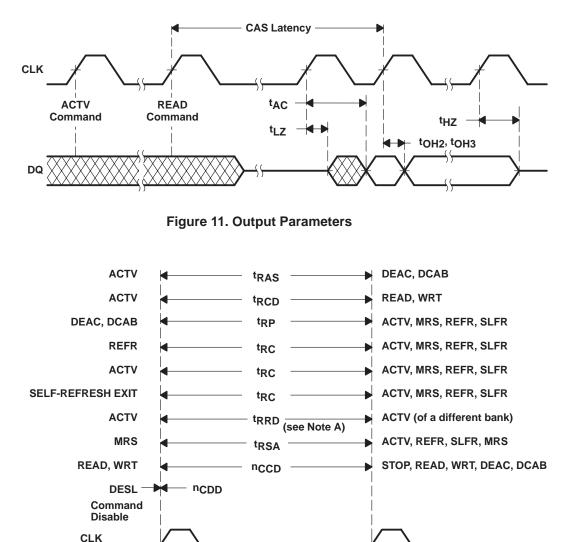

#### latency

The beginning data-output cycle of a read burst can be programmed to occur two or three CLK cycles after the READ command (see Figure 2 on how to set the mode register.) This feature allows adjustment of the '664xx4 to operate in accordance with the system's capability to latch the data output from the '664xx4. The delay between the READ command and the beginning of the output burst is known as CAS latency (also known as read latency). After the initial output cycle begins, the data burst occurs at the CLK frequency without any intervening gaps. Use of minimum CAS latencies is restricted, based on the particular maximum frequency rating of the '664xx4. Once the mode register has been set (see the section on setting the mode register), subsequent changes to the CAS latency are prohibited.

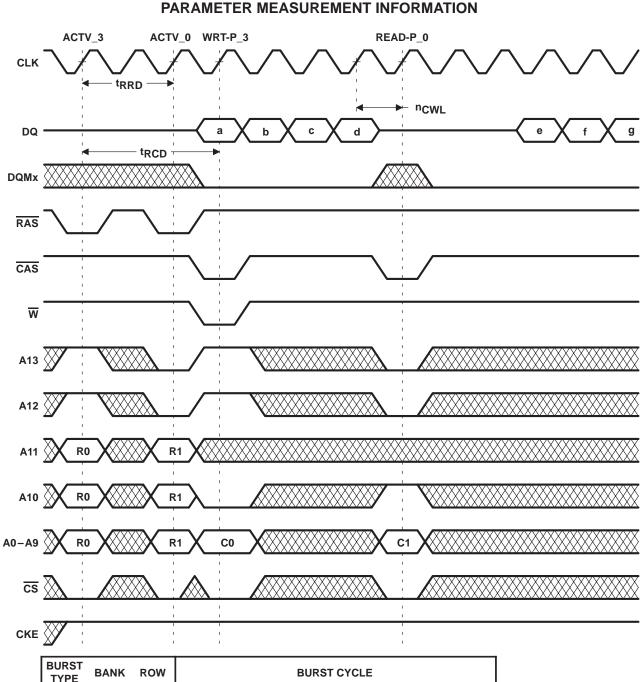

There is no latency for data-in cycles (write latency). The first data-in cycle of a write burst is entered at the same rising edge of CLK as the WRT command. The write latency is fixed and is not determined by the mode-register contents.

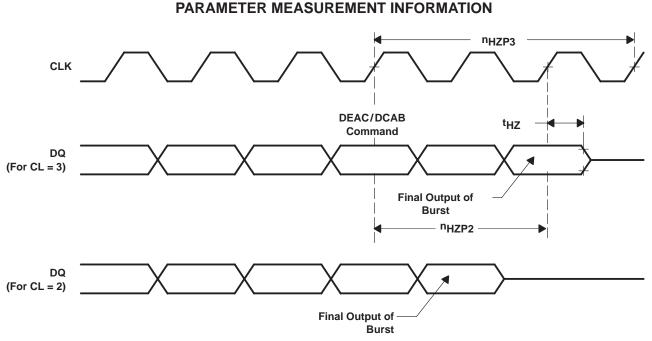

## four-bank operation

The '664xx4 contains four independent banks that can be accessed individually or in an interleaved fashion. Each bank must be activated with a row address before it can be accessed. Each bank then must be deactivated before it can be activated again with a new row address. The bank-activate/row-address-entry command (ACTV) is entered by holding RAS low, CAS high, W high, and A12–A13 valid on the rising edge of CLK. A bank can be deactivated either automatically during a READ (READ-P) or a WRT (WRT-P) command, or by using the bank-deactivate (DEAC) command. All banks can be deactivated at once by using the DCAB command (see Table 1 for a description of the bank-deactivation, and Figure 25 and Figure 26 for examples of the operation).

#### four-bank row-access operation

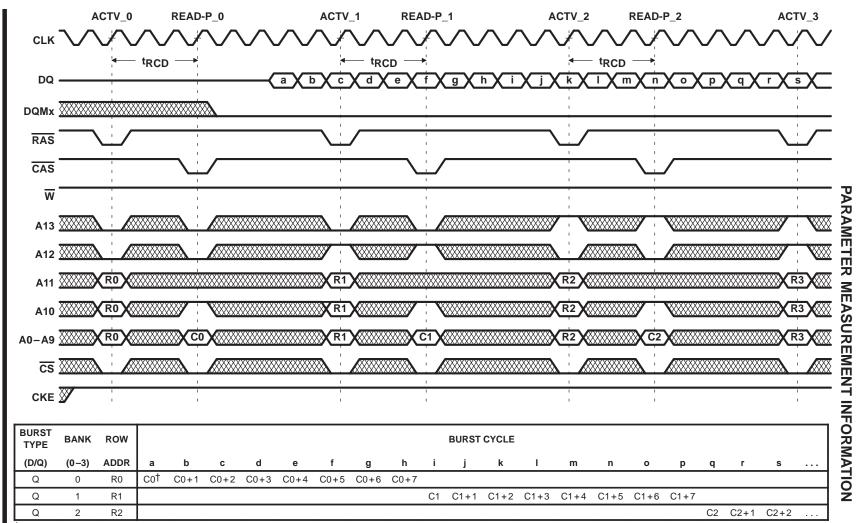

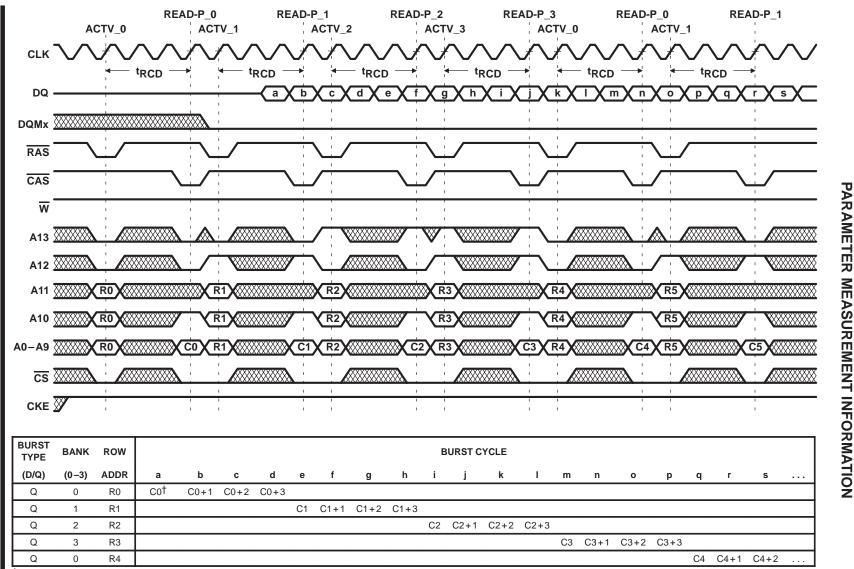

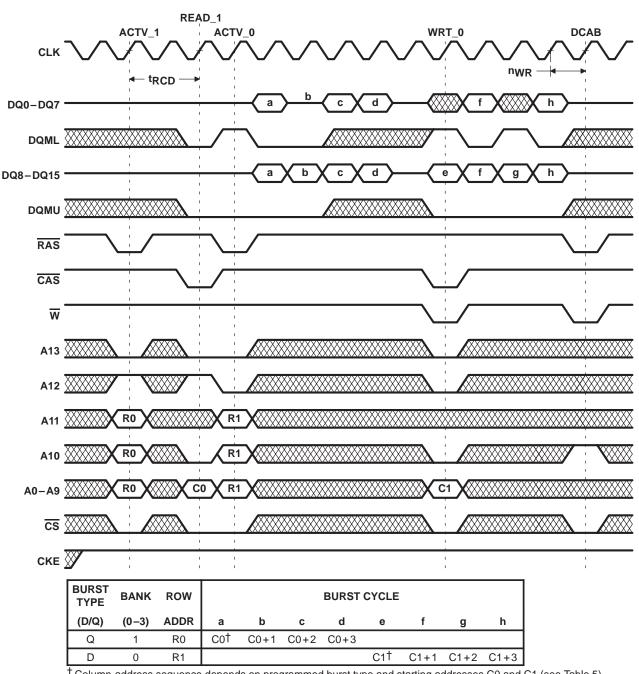

One of the features of the four-bank operation is access to information on random rows at a higher rate of operation than is possible with a standard DRAM. This is accomplished by activating one of the banks with a row address and, while the data stream is being accessed to/from that bank, activating one of the other banks with other row addresses. When the data stream to/from the first activated bank is complete, the data stream to/from the second activated bank can begin without interruption. After the second bank is activated, the first bank can be deactivated to allow the entry of a new row address for the next round of accesses or the entry of new row addresses for other banks which currently are deactivated. In this manner, operation can continue in an interleaved fashion. Figure 29A is an example of four-bank, row-interleaving, read bursts with automatic deactivate with a CAS latency of 3 and a burst length of 8. Figure 29B is an example of four-bank, row-interleaving, read bursts with automatic deactivate with a CAS latency of 4.

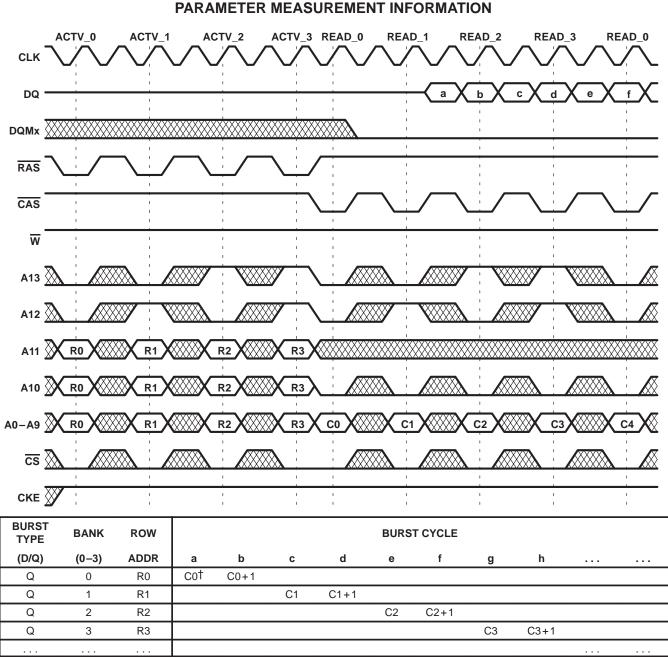

#### four-bank column-access operation

The availability of four banks allows the access of data from random starting columns between banks at a higher rate of operation. After activating each bank with a row address (ACTV command), A12–A13 for the four-bank column-access operation can be used to alternate READ or WRT commands between the banks to provide gapless accesses at the CLK frequency, provided all specified timing requirements are met. Figure 30 is an example of four-bank, column-interleaving, read bursts with a CAS latency of 3 and a burst length of 2.

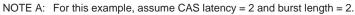

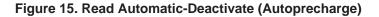

#### bank deactivation (precharge)

All banks can be deactivated simultaneously (placed in precharge) by using the DCAB command. A single bank can be deactivated by using the DEAC command. The DEAC command is entered identically to the DCAB command except that A10 must be low and A12–A13 select the bank to be precharged (see Table 1; Figure 27 and Figure 31 provide examples). A bank can also be deactivated automatically by using A10 during a READ or WRT command. If A10 is held high during the entry of a READ or WRT command, the accessed bank, selected by A12–A13, is automatically deactivated upon completion of the access burst. If A10 is held low during READ- or WRT-command entry, that bank remains active following the burst. The READ and WRT commands with automatic deactivation are denoted as READ-P and WRT-P. See Figure 29A and Figure 29B for examples.

#### chip-select

$\overline{CS}$  (chip-select) can be used to select or deselect the '664xx4 for command entries, which might be required for multiple-memory-device decoding. If  $\overline{CS}$  is held high on the rising edge of CLK (DESL command), the device does not respond to  $\overline{RAS}$ ,  $\overline{CAS}$ , or  $\overline{W}$  until the device is selected again by holding  $\overline{CS}$  low on the rising edge of CLK. Any other valid command can be entered simultaneously on the same rising CLK edge of the select operation. The device can be selected/deselected on a cycle-by-cycle basis (see Table 1 and Table 2). Using  $\overline{CS}$  does not affect an access burst that is in progress; the DESL command can restrict only  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{W}$  inputs to the '664xx4.

SMOS695A - APRIL 1998 - REVISED JULY 1998

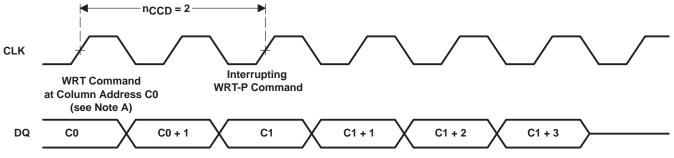

#### data/output mask

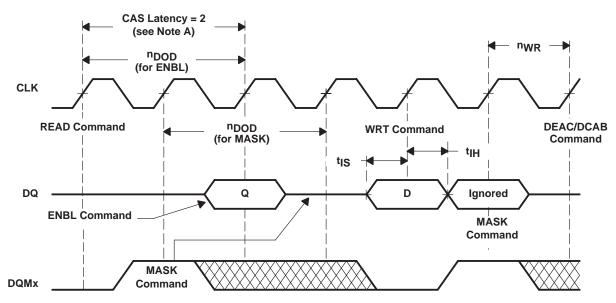

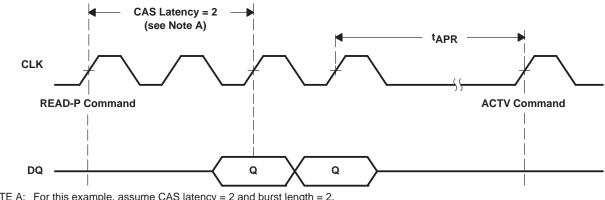

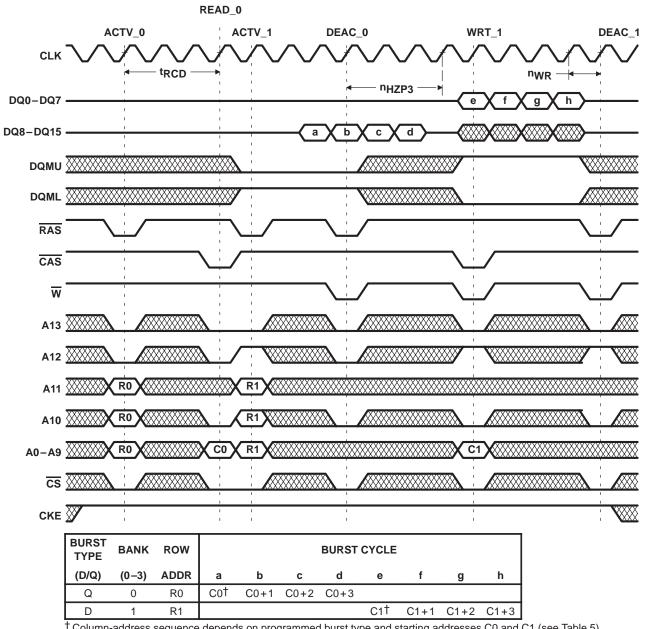

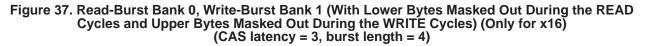

Masking of individual data cycles within a burst sequence can be accomplished by using the MASK command (see Table 3). If DQM (or DQML/DQMU of x16) is held high on the rising edge of CLK during a write burst, the incident data word (referenced to the same rising edge of CLK) on DQ0-DQ7 [or (DQ0-DQ7)/(DQ8-DQ15) of x16] is ignored. If DQM (or DQML/DQMU of x16) is held high on the rising edge of CLK for a read burst, DQ0-DQ7 [or (DQ0-DQ7)/(DQ8-DQ15) of x16], referenced to the second rising edge of CLK, are in the high-impedance state. The application of DQM (DQML/DQMU) to data-output cycles (READ burst) involves a latency of two CLK cycles, but the application of DQM to data-in cycles (WRITE burst) has no latency. The MASK command (or its opposite, the ENBL command) is performed on a cycle-by-cycle basis, allowing the user to gate any individual data cycle or cycles within either a read-burst or a write-burst sequence. Figure 14, Figure 38 and Figure 39 show examples of data/output masking.

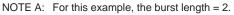

## CLK-suspend/power-down mode

For normal device operation, CKE should be held high to enable CLK. If CKE goes low during the execution of a READ (READ-P) or WRT (WRT-P) operation, the state of the DQ bus occurring at the immediate next rising edge of CLK is frozen at its current state and no further inputs are accepted until CKE is returned high. This is known as a CLK-suspend operation and its execution is denoted as a HOLD command. The device resumes operation from the point at which it was placed in suspension, beginning with the second rising edge of CLK after CKE is returned high. See Figure 42 and Figure 43 for examples.

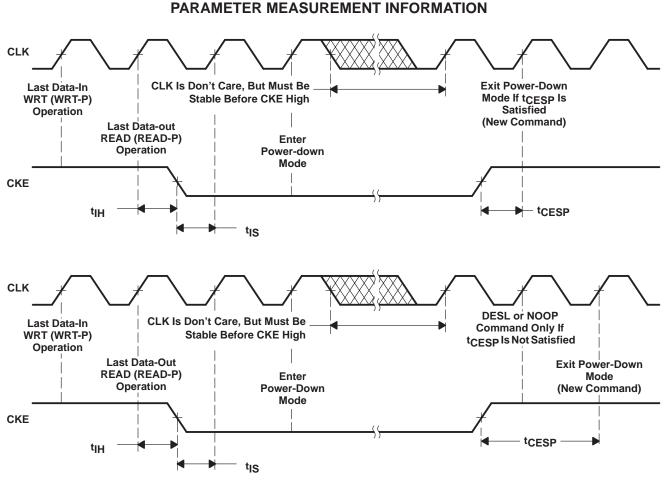

If CKE is brought low when no READ (READ-P) or WRT (WRT-P) command is in progress, the device enters power-down mode. If all banks are deactivated when power-down mode is entered, power consumption is reduced to the minimum. Power-down mode can be used during row-active or auto-refresh periods to reduce input-buffer power. After power-down mode has been entered, no further inputs are accepted until CKE returns high. To ensure that data in the device remains valid during the power-down mode, the self-refresh command (SLRF) must be executed concurrently with the power-down entry (PDE) command. When exiting power-down mode, new commands can be entered on the first CLK edge after CKE returns high, provided that the setup time (t<sub>CESP</sub>) is satisfied. Table 2 shows the command configuration for a CLK-suspend/power-down operation; Figure 18 and Figure 19 show examples of the procedure.

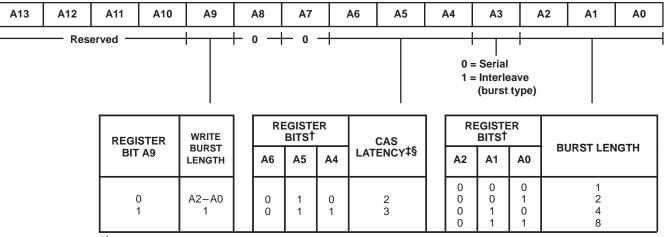

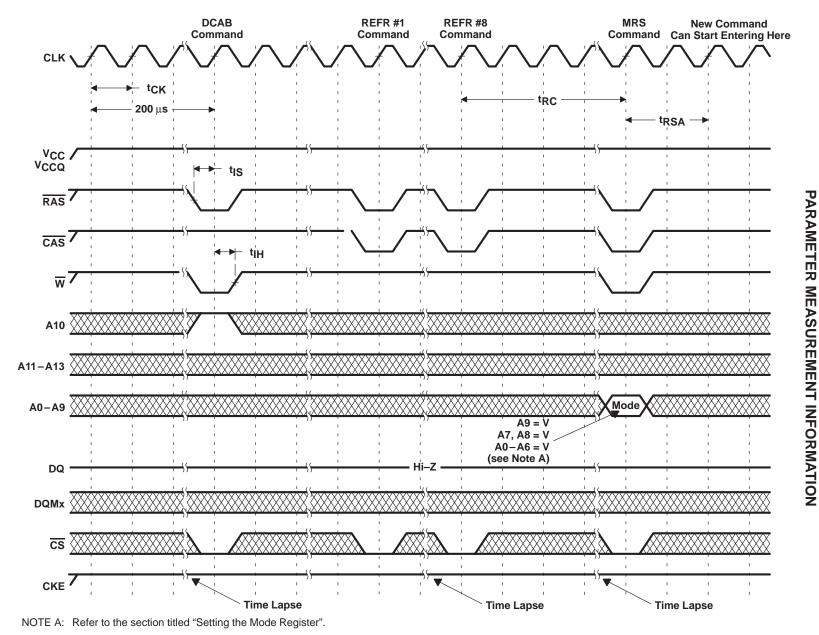

#### setting the mode register

The '664xx4 contains a mode register that must be user-programmed with the CAS latency, the burst type, and the burst length. This is accomplished by executing an MRS command with the information entered on address lines A0-A9. A logic 0 must be entered on A7 and A8, but A10-A13 are "don't care" entries for the '664xx4. When A9 = 1, the write burst length is always 1. When A9 = 0, the write burst length is defined by A2-A0. Figure 2 shows the valid combinations for a successful MRS command. Only valid addresses allow the mode register to be changed. If the addresses are not valid, the previous contents of the mode register remain unaffected. The MRS command is executed by holding RAS, CAS, and W low and the input-mode word valid on A0-A9 on the rising edge of CLK (see Table 1). The MRS command can be executed only when all banks are deactivated and may not be executed while a burst is active. See Figure 24 and Figure 35 for examples.

<sup>†</sup> All other combinations are reserved.

<sup>‡</sup>Refer to timing requirements for minimum valid read latencies based on maximum frequency rating.

§ Once the mode register has been set, subsequent changes to the CAS latency is prohibited.

#### Figure 2. Mode-Register Programming

#### refresh

The '664xx4 must be refreshed at intervals not exceeding t<sub>REF</sub> (see timing requirements) or data cannot be retained. Refresh is accomplished by performing one of the following:

- An ACTV command (RAS-only refresh) to every row in all banks

- 4096 auto-refresh (REFR) commands

- Putting the device in self-refresh mode

Regardless of the method used, refresh must be accomplished before t<sub>REF</sub> has expired. See Figure 34 for an example.

SMOS695A - APRIL 1998 - REVISED JULY 1998

#### auto refresh

Before performing an auto refresh, all banks must be deactivated (placed in precharge). To enter a REFR command, RAS and CAS must be low and W must be high during the rising edge of CLK (see Table 1). The refresh address is generated internally such that after 4096 REFR commands, all banks of the '664xx4 are refreshed. The external address and bank-select A12-A13 are ignored. The execution of a REFR command automatically deactivates all banks upon completion of the internal auto-refresh cycle. This allows consecutive REFR-only commands to be executed, if desired, without any intervening DEAC commands. The REFR commands do not necessarily have to be consecutive, but all 4096 must be completed before t<sub>RFF</sub> expires.

#### self-refresh mode

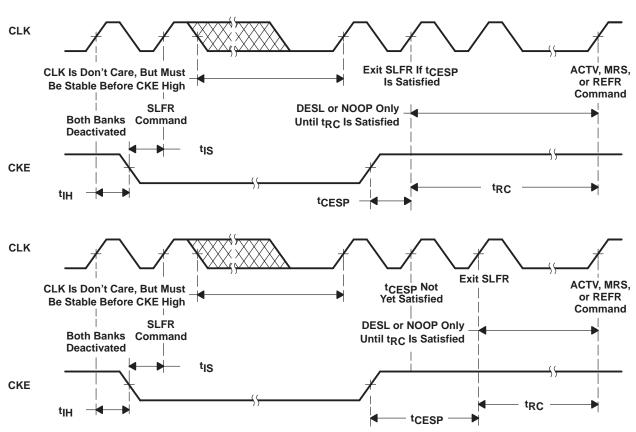

To enter self-refresh mode, all banks of the '664xx4 must be deactivated first and an SLFR command must be executed (see Table 2). The SLFR command is identical to the REFR command except that CKE is low. For proper entry of the SLFR command, CKE is brought low for the same rising edge of CLK when RAS and CAS are low and  $\overline{W}$  is high. CKE must be held low to stay in self-refresh mode. In the self-refresh mode, refreshing signals are generated internally for all banks with all external signals (except CKE) being ignored. Data can be retained by the device automatically for an indefinite period when power is maintained (consumption is reduced to a minimum). To exit self-refresh mode, CKE must be brought high. New commands are issued after t<sub>RC</sub> has expired. If CLK is made inactive during self-refresh, it must be returned to an active and stable condition before CKE is brought high to exit self-refresh mode (see Figure 19).

Prior to entering and upon exiting self-refresh mode, 4096 REFR commands are recommended before continuing with normal device operations. This ensures that the SDRAM is fully refreshed.

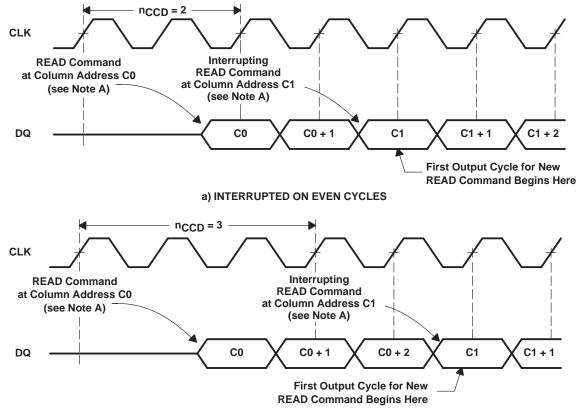

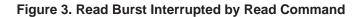

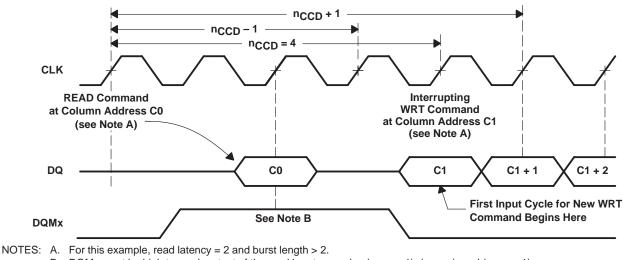

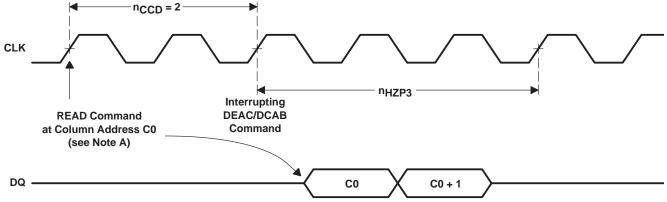

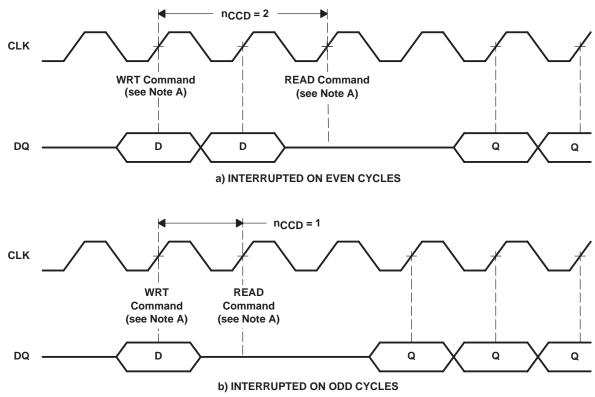

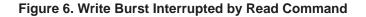

#### interrupted bursts

A read or write can be interrupted before the burst sequence is complete with no adverse effects to the operation. This is accomplished by entering certain superseding commands as listed in Table 7 and Table 8, provided that all timing requirements are met. The interruption of READ-P and WRT-P operations is not supported.

| INTERRUPTING COMMAND                                                                                                                                             | EFFECT OR NOTE ON USE DURING READ BURST                                                                                                                                                                                                                                                                         |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| READ, READ-P Current output cycles continue until the programmed latency from the superseding READ (R command is met and new output cycles begin (see Figure 3). |                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| WRT, WRT-P                                                                                                                                                       | The WRT (WRT-P) command immediately supersedes the read burst in progress. To avoid data contention, DQMx must be high before the WRT (WRT-P) command to mask output of the read burst on cycles ( $n_{CCD}-1$ ), $n_{CCD}$ , and ( $n_{CCD}+1$ ), assuming there is any output on these cycles (see Figure 4). |  |  |  |  |

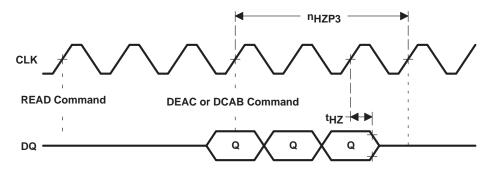

| DEAC, DCAB                                                                                                                                                       | The DQ bus is in the high-impedance state when $n_{HZP}$ cycles are satisfied or upon completion of the read burst, whichever occurs first (see Figure 5 and Figure 22).                                                                                                                                        |  |  |  |  |

#### **Table 7. Read-Burst Interruption**

SMOS695A - APRIL 1998 - REVISED JULY 1998

## interrupted bursts (continued)

b) INTERRUPTED ON ODD CYCLES

NOTE A: For this example, assume CAS latency = 2 and burst length > 2.

B. DQMx must be high to mask output of the read burst on cycles (n<sub>CCD</sub>-1), (n<sub>CCD</sub>), and (n<sub>CCD</sub>+1).

#### Figure 4. Read Burst Interrupted by Write Command

SMOS695A - APRIL 1998 - REVISED JULY 1998

# interrupted bursts (continued)

NOTE A: For this example, assume CAS latency = 3 and burst length > 2.

#### Figure 5. Read Burst Interrupted by DEAC Command

| INTERRUPTING COMMAND | EFFECT OR NOTE ON USE DURING WRITE BURST                                                                                                                                                                                |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ, READ-P         | Data that was input on the previous cycle is written and no further data inputs are accepted (see Figure 6).                                                                                                            |

| WRT, WRT-P           | The new WRT (WRT-P) command and data-in immediately supersede the write burst in progress (see Figure 7).                                                                                                               |

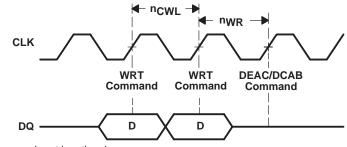

| DEAC, DCAB           | The DEAC/DCAB command immediately supersedes the write burst in progress. DQMx must be used to mask the DQ bus such that the write recovery specification ( $n_{WR}$ ) is not violated by the interrupt (see Figure 8). |

#### **Table 8. Write-Burst Interruption**

#### interrupted bursts (continued)

NOTE A: For this example, assume CAS latency = 2, burst length > 2.

NOTE A: For this example, burst length > 2.

Figure 7. Write Burst Interrupted by Write Command

SMOS695A - APRIL 1998 - REVISED JULY 1998

## interrupted bursts (continued)

NOTE A: For the purposes of this example, CAS latency = 2 and burst length > 2.

#### Figure 8. Write Burst Interrupted by DEAC/DCAB Command

#### power up

Device initialization should be performed after a power up to the full  $V_{CC}$  level. After power is established, a 200-µs interval is required (with no inputs other than CLK). After this interval, all banks of the device must be deactivated. Eight REFR commands must be performed, and the mode register must be set to complete the device initialization. See Figure 24.

SMOS695A - APRIL 1998 - REVISED JULY 1998

# absolute maximum ratings over operating ambient temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub>                     | – 0.5 V to 4.6 V                   |

|-----------------------------------------------------------|------------------------------------|

| Supply voltage range for output drivers, V <sub>CCQ</sub> | – 0.5 V to 4.6 V                   |

| Voltage range on any input pin (see Note 1)               | – 0.5 V to 4.6 V                   |

| Voltage range on any output pin (see Note 1)              | -0.5  V to V <sub>CC</sub> + 0.5 V |

| Short-circuit output current                              |                                    |

| Power dissipation                                         | 1 W                                |

| Operating ambient temperature range, T <sub>A</sub>       | 0°C to 70°C                        |

| Storage temperature range, T <sub>stg</sub>               | – 55°C to 150°C                    |

| 5                                                         |                                    |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to VSS.

#### recommended operating conditions

|                |                                    | MIN   | NOM | MAX                   | UNIT |

|----------------|------------------------------------|-------|-----|-----------------------|------|

| Vcc            | Supply voltage                     | 3     | 3.3 | 3.6                   | V    |

| VCCQ           | Supply voltage for output drivers‡ | 3     | 3.3 | 3.6                   | V    |

| VSS            | Supply voltage                     |       | 0   |                       | V    |

| VSSQ           | Supply voltage for output drivers  |       | 0   |                       | V    |

| VIH            | High-level input voltage           | 2     |     | V <sub>CC</sub> + 0.3 | V    |

| VIL            | Low-level input voltage            | - 0.3 |     | 0.8                   | V    |

| T <sub>A</sub> | Operating ambient temperature      | 0     |     | 70                    | °C   |

| +              |                                    |       |     |                       |      |

$V_{CCQ} \leq V_{CC} + 0.3 V$

SMOS695A - APRIL 1998 - REVISED JULY 1998

# electrical characteristics over recommended ranges of supply voltage and operating ambient temperature (unless otherwise noted) (see Note 2)

|                   |                                    | TEST CONDITIONS                                                                                                                               |                                                                                 | - 8 (x8/x4) |          | - 8 (x | 16)      | - 8A (x | 8/x4)    | 11511-   |

|-------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------|----------|--------|----------|---------|----------|----------|

| PARAMETER         |                                    | TEST CONDITIC                                                                                                                                 | MIN                                                                             | MAX         | MIN      | MAX    | MIN      | MAX     | UNIT     |          |

| Vон               | High-level output voltage          | I <sub>OH</sub> = -2 mA                                                                                                                       |                                                                                 |             |          | 2.4    |          | 2.4     |          | V        |

| Vol               | Low-level output voltage           | I <sub>OL</sub> = 2 mA                                                                                                                        |                                                                                 |             | 0.4      |        | 0.4      |         | 0.4      | V        |

| I                 | Input current<br>(leakage)         | $\begin{array}{l} 0 \ V \leq V_I \leq V_{CC} + 0.3 \ V, \\ \mbox{All other pins} = 0 \ V \ to \ V_{CC} \end{array}$                           |                                                                                 |             | ±10      |        | ±10      |         | ±10      | μΑ       |

| IO                | Output current<br>(leakage)        | $0 V \le V_O \le V_{CCQ}$<br>Output disabled                                                                                                  |                                                                                 |             | ±10      |        | ±10      |         | ±10      | μΑ       |

| ICC1              | Operating                          | Burst length = 1,<br>$t_{RC} \ge t_{RC} MIN$                                                                                                  | CAS latency = 2                                                                 |             | 115      |        | 125      |         | 95       | mA       |

|                   | current                            | $I_{OH}/I_{OL} = 0 \text{ mA}$<br>(see Notes 3, 4, and 5)                                                                                     | CAS latency = 3                                                                 |             | 125      |        | 135      |         | 125      | mA       |

| ICC2P             | Precharge<br>standby current       | $\begin{array}{l} \mbox{CKE} \ \leq \ \mbox{V}_{IL} \ \mbox{MAX}, \ \mbox{t}_{CK} = 15 \ \mbox{ns} \\ \mbox{(see Note 6)} \end{array}$        |                                                                                 | 1           |          | 1      |          | 1       | mA       |          |

| ICC2PS            | in power-down<br>mode              | CKE and CLK $\leq$ V <sub>IL</sub> MAX, t <sub>CF</sub> (see Note 7)                                                                          | CKE and CLK $\leq$ V <sub>IL</sub> MAX, t <sub>CK</sub> = $\infty$ (see Note 7) |             |          |        | 1        |         | 1        | mA       |

| ICC2N             | Precharge<br>standby current<br>in | $\label{eq:cke} \begin{array}{l} CKE \geq V_{IH} \; MIN,  t_{CK} = 15 \; ns \\ (see \; Note \; 6) \end{array}$                                |                                                                                 |             | 40       |        | 40       |         | 40       | mA       |

| ICC2NS            | non-power-down<br>mode             | t <sub>CK</sub> =∞ (see Note 7)                                                                                                               |                                                                                 |             | 5        |        | 5        |         | 5        | mA       |

| I <sub>CC3P</sub> | Active standby<br>current in       | $\begin{array}{l} \mbox{CKE} \ \leq \ \mbox{V}_{IL} \ \mbox{MAX}, \ \mbox{t}_{CK} = 15 \ \mbox{ns} \\ \mbox{(see Notes 3 and 6)} \end{array}$ |                                                                                 |             | 8        |        | 8        |         | 8        | mA       |

| ICC3PS            | power-down<br>mode                 | CKE and CLK $\leq$ VIL MAX, t <sub>C</sub> (see Notes 3 and 7)                                                                                | < = ∞                                                                           |             | 8        |        | 8        |         | 8        | mA       |

| ICC3N             | Active standby<br>current in       | $\begin{array}{l} \mbox{CKE} \ \geq \ \mbox{V}_{IH} \ \mbox{MIN}, \ \mbox{t}_{CK} = 15 \ \mbox{ns} \\ \mbox{(see Notes 3 and 6)} \end{array}$ |                                                                                 |             | 50       |        | 55       |         | 50       | mA       |

| ICC3NS            | non-power-down<br>mode             | $CKE \ge V_{IH} MIN, CLK \le V_{IL} M$<br>(see Notes 3 and 7)                                                                                 | MAX, t <sub>CK</sub> = ∞                                                        |             | 15       |        | 15       |         | 15       | mA       |

|                   | Durat automatic                    | Page burst, I <sub>OH</sub> /I <sub>OL</sub> = 0 mA                                                                                           | CAS latency = 2                                                                 |             | 165      |        | 165      |         | 120      | mA       |

| ICC4              | Burst current                      | All banks activated,<br>(see Notes 8, 9, and 10)                                                                                              | CAS latency = 3                                                                 |             | 225      |        | 245      |         | 165      | mA       |

| ICC5              | Auto-refresh                       | $t_{RC} \ge t_{RC} MIN$                                                                                                                       | CAS latency = 2                                                                 |             | 150      |        | 150      |         | 150      | mA       |

| ICC6              | current<br>Self-refresh<br>current | (see Notes 4 and 7)<br>CKE $\leq$ VIL MAX                                                                                                     | CAS latency = 3                                                                 |             | 150<br>1 |        | 150<br>1 |         | 150<br>1 | mA<br>mA |

NOTES: 2. All specifications apply to the device after power-up initialization. All control and address inputs must be stable and valid.

3. Only one bank is activated.

4.  $t_{RC} \ge t_{RC} MIN$

5. Control, DQ, and address inputs change state twice during  $t_{RC}$ .

6. Control, DQ, and address inputs change state once every 30 ns.

7. Control, DQ, and address inputs do not change state (stable).

8. 4-bank ping-pong, burst length = 4,  $n_{CCD}$  = 4 cycles, data pattern 0011.

9. Column address and bank address increment every 4 cycles.

10. A  $t_{CK}$  of 10 ns is used to obtain  $I_{CC4}$  for CL3 of the -8A speed grade.

SMOS695A - APRIL 1998 - REVISED JULY 1998

#### electrical characteristics over recommended ranges of supply voltage and operating ambient temperature (unless otherwise noted) (see Note 2) (continued)

|                   |                                    | TEST CONDITIONS                                                                                                                                              |                                                                                 | – 8A (x16) |            | - 10 (x8/x4) |            | - 10 (x16) |            |          |

|-------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------|------------|--------------|------------|------------|------------|----------|

| PARAMETER         |                                    | TEST CONDITIC                                                                                                                                                | MIN                                                                             | MAX        | MIN        | MAX          | MIN        | MAX        | UNIT       |          |

| Vон               | High-level output voltage          | I <sub>OH</sub> = -2 mA                                                                                                                                      |                                                                                 |            |            | 2.4          |            | 2.4        |            | V        |

| Vol               | Low-level output voltage           | I <sub>OL</sub> = 2 mA                                                                                                                                       |                                                                                 |            | 0.4        |              | 0.4        |            | 0.4        | V        |

| I                 | Input current<br>(leakage)         | $\begin{array}{l} 0 \ V \leq V_I \leq V_{CC} + 0.3 \ V, \\ \mbox{All other pins} = 0 \ V \ to \ V_{CC} \end{array}$                                          |                                                                                 |            | ±10        |              | ±10        |            | ±10        | μA       |

| IO                | Output current<br>(leakage)        | $0 V \le V_O \le V_{CCQ}$<br>Output disabled                                                                                                                 |                                                                                 |            | ±10        |              | ±10        |            | ±10        | μA       |

| ICC1              | Operating                          | Burst length = 1,<br>$t_{RC} \ge t_{RC} MIN$                                                                                                                 | CAS latency = 2                                                                 |            | 105        |              | 95         |            | 105        | mA       |

|                   | current                            | $I_{OH}/I_{OL} = 0 \text{ mA}$<br>(see Notes 3, 4, and 5)                                                                                                    | CAS latency = 3                                                                 |            | 135        |              | 105        |            | 115        | mA       |

| ICC2P             | Precharge<br>standby current       | $\begin{array}{l} \mbox{CKE} \ \leq \ \mbox{V}_{IL} \ \mbox{MAX}, \ \mbox{t}_{CK} = 15 \ \mbox{ns} \\ \mbox{(see Note 6)} \end{array}$                       |                                                                                 | 1          |            | 1            |            | 1          | mA         |          |

| ICC2PS            | in power-down<br>mode              | CKE and CLK $\leq$ V <sub>IL</sub> MAX, t <sub>CF</sub> (see Note 7)                                                                                         | CKE and CLK $\leq$ V <sub>IL</sub> MAX, t <sub>CK</sub> = $\infty$ (see Note 7) |            |            |              | 1          |            | 1          | mA       |

| ICC2N             | Precharge<br>standby current<br>in | $\label{eq:cke} \begin{array}{l} \mbox{CKE} \ \geq \ \mbox{V}_{IH} \ \mbox{MIN}, \ \mbox{t}_{CK} = 15 \ \mbox{ns} \\ \mbox{(see Note 6)} \end{array}$        |                                                                                 |            | 40         |              | 40         |            | 40         | mA       |

| ICC2NS            | non-power-down<br>mode             | t <sub>CK</sub> =∞ (see Note 7)                                                                                                                              |                                                                                 |            | 5          |              | 5          |            | 5          | mA       |

| I <sub>CC3P</sub> | Active standby current in          | $\begin{array}{l} \mbox{CKE} \ \leq \ \mbox{V}_{IL} \ \mbox{MAX}, \ \mbox{t}_{CK} = 15 \ \mbox{ns} \\ \mbox{(see Notes 3 and 6)} \end{array}$                |                                                                                 |            | 8          |              | 8          |            | 8          | mA       |

| ICC3PS            | power-down<br>mode                 | CKE and CLK $\leq$ VIL MAX, tCF (see Notes 3 and 7)                                                                                                          | < = ∞                                                                           |            | 8          |              | 8          |            | 8          | mA       |

| ICC3N             | Active standby<br>current in       | $\label{eq:cke} \begin{array}{l} \mbox{CKE} \ \geq \ \mbox{V}_{IH} \ \mbox{MIN}, \ \mbox{t}_{CK} = 15 \ \mbox{ns} \\ \mbox{(see Notes 3 and 6)} \end{array}$ |                                                                                 |            | 55         |              | 55         |            | 60         | mA       |

| ICC3NS            | non-power-down<br>mode             | $CKE \ge V_{IH} MIN, CLK \le V_{IL} N$<br>(see Notes 3 and 7)                                                                                                | MAX, t <sub>CK</sub> = ∞                                                        |            | 15         |              | 15         |            | 15         | mA       |

| ICC4              | Burst current                      | Page burst, I <sub>OH</sub> /I <sub>OL</sub> = 0 mA<br>All banks activated,                                                                                  | CAS latency = 2                                                                 |            | 140        |              | 120        |            | 140        | mA       |

|                   | Duist current                      | (see Notes 8, 9, and 10)                                                                                                                                     | CAS latency = 3                                                                 |            | 165        |              | 175        |            | 200        | mA       |

| ICC5              | Auto-refresh<br>current            | $t_{RC} \ge t_{RC} MIN$<br>(see Notes 4 and 7)                                                                                                               | CAS latency = 2<br>CAS latency = 3                                              |            | 150<br>150 |              | 150<br>150 |            | 150<br>150 | mA<br>mA |

| ICC6              | Self-refresh<br>current            | CKE ≤ V <sub>IL</sub> MAX                                                                                                                                    |                                                                                 |            | 1          |              | 2          |            | 2          | mA       |

NOTES: 2. All specifications apply to the device after power-up initialization. All control and address inputs must be stable and valid.

3. Only one bank is activated.

4.  $t_{RC} \ge t_{RC} MIN$

5. Control, DQ, and address inputs change state twice during t<sub>RC</sub>.

6. Control, DQ, and address inputs change state once every 30 ns.

7. Control, DQ, and address inputs do not change state (stable).

8. 4-bank ping-pong, burst length = 4, n<sub>CCD</sub> = 4 cycles, data pattern 0011.

9. Column address and bank address increment every 4 cycles.

10. A  $t_{CK}$  of 10 ns is used to obtain  $I_{CC4}$  for CL3 of the -8A speed grade.

SMOS695A - APRIL 1998 - REVISED JULY 1998

# capacitance over recommended ranges of supply voltage and operating ambient temperature f = 1 MHz (see Note 11)

|                    | PARAMETER                                                                    | MIN | MAX | UNIT |

|--------------------|------------------------------------------------------------------------------|-----|-----|------|

| C <sub>i(S)</sub>  | Input capacitance, CLK input                                                 | 2.5 | 4   | pF   |

| C <sub>i(AC)</sub> | Input capacitance, address and control inputs: A0–A13, CS, DQMx, RAS, CAS, W | 2.5 | 5   | pF   |

| C <sub>i(E)</sub>  | Input capacitance, CKE input                                                 |     | 5   | pF   |

| Co                 | Output capacitance                                                           | 4   | 6.5 | pF   |

NOTE 11: V<sub>CC</sub> =  $3.3 \pm 0.3$  V and bias on pins under test is 0 V.

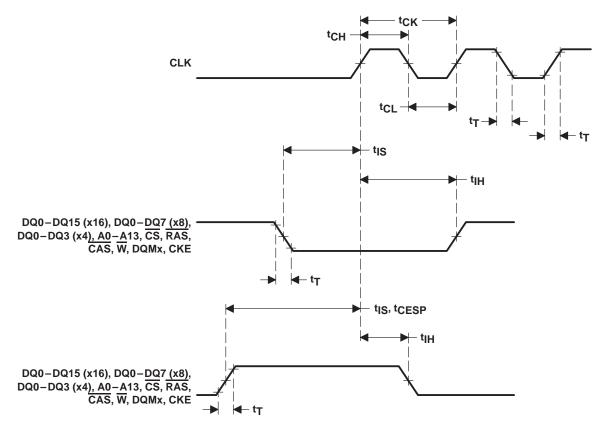

# ac timing requirements<sup>†‡</sup>

|                  |                                                                       |                       | '664 | xx4-8  | '664xx4-8A |        | '664xx4-10 |        |      |

|------------------|-----------------------------------------------------------------------|-----------------------|------|--------|------------|--------|------------|--------|------|

|                  |                                                                       |                       | MIN  | MAX    | MIN        | MAX    | MIN        | MAX    | UNIT |

| tCK2             | Cycle time, CLK                                                       | CAS latency = 2       | 10   |        | 15         |        | 15         |        | ns   |

| tCK3             | Cycle time, CLK                                                       | CAS latency = 3       | 8    |        | 8          |        | 10         |        | ns   |

| <sup>t</sup> CH  | Pulse duration, CLK high                                              |                       | 3    |        | 3          |        | 3          |        | ns   |

| tCL              | Pulse duration, CLK low                                               |                       | 3    |        | 3          |        | 3          |        | ns   |

| tAC2             | Access time, CLK high to data out (see Note 12)                       | CAS latency = 2       |      | 6      |            | 7.5    |            | 7.5    | ns   |

| tAC3             | Access time, CLK high to data out (see Note 12)                       | CAS latency = 3       |      | 6      |            | 6      |            | 7.5    | ns   |

| <sup>t</sup> OH2 | Hold time, CLK high to data out with 50-pF load                       | CAS latency = 2       | 3    |        | 3          |        | 3          |        | ns   |

| tOH3             | Hold time, CLK high to data out with 50-pF load                       | CAS latency = 3       | 3    |        | 3          |        | 3          |        | ns   |

| t <sub>LZ</sub>  | Delay time, CLK high to DQ in low-impedance                           | e state (see Note 13) | 1    |        | 1          |        | 2          |        | ns   |

| <sup>t</sup> HZ  | Delay time, CLK high to DQ in high-impedan (see Note 14)              | ce state              |      | 8      |            | 8      |            | 10     | ns   |

| tis              | Setup time, address, control, and data input                          |                       | 2    |        | 2          |        | 2          |        | ns   |

| tιΗ              | Hold time, address, control, and data input                           |                       | 1    |        | 1          |        | 1          |        | ns   |

| tCESP            | Power down/self-refresh exit time (see Note                           | 15)                   | 8    |        | 8          |        | 10         |        | ns   |

| <sup>t</sup> RAS | Delay time, ACTV command to DEAC or DC                                | AB command            | 48   | 100000 | 48         | 100000 | 50         | 100000 | ns   |

| <sup>t</sup> RC  | Delay time, ACTV, REFR, or SLFR comman<br>REFR, or SLFR command       | d to ACTV, MRS,       | 68   |        | 68         |        | 80         |        | ns   |

| <sup>t</sup> RCD | Delay time, ACTV command to READ, REAI<br>WRT-P command (see Note 16) | D-P, WRT, or          | 20   |        | 20         |        | 30         |        | ns   |

| t <sub>RP</sub>  | Delay time, DEAC or DCAB command to ACTV, MRS, REFR, or SLFR command  |                       | 20   |        | 20         |        | 30         |        | ns   |

| <sup>t</sup> RRD | Delay time, ACTV command in one bank to a the other bank              | ACTV command in       | 16   |        | 16         |        | 20         |        | ns   |

| <sup>t</sup> RSA | Delay time, MRS command to ACTV, MRS, command                         | REFR, or SLFR         | 16   |        | 16         |        | 20         |        | ns   |

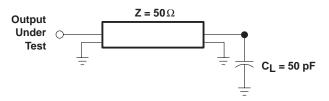

<sup>†</sup> See Parameter Measurement Information for load circuits (see Figure 9).

<sup>‡</sup>All references are made to the rising transition of CLK, unless otherwise noted.

NOTES: 12. t<sub>AC</sub> is referenced from the rising transition of CLK that precedes the data-out cycle. For example, the first data-out t<sub>AC</sub> is referenced from the rising transition of CLK that is CAS latency – one cycle after the READ command. An access time is measured at output reference level 1.5 V.

13. tLz is measured from the rising transition of CLK that is CAS latency - one cycle after the READ command.

14. tHZ MAX defines the time at which the outputs are no longer driven and is not referenced to output voltage levels.

- 15. See Figure 18 and Figure 19.

- 16. For read or write operations with automatic deactivate, tRCD must be set to satisfy minimum tRAS.

# ac timing requirements<sup>†‡</sup> (continued)

|                  |                                                                    |                    | '664x | x4-8           | '664xx            | (4-8A                 | '664xx | (4-10 | UNIT  |

|------------------|--------------------------------------------------------------------|--------------------|-------|----------------|-------------------|-----------------------|--------|-------|-------|

|                  |                                                                    |                    | MIN   | MAX            | MIN               | MAX                   | MIN    | MAX   | UNIT  |

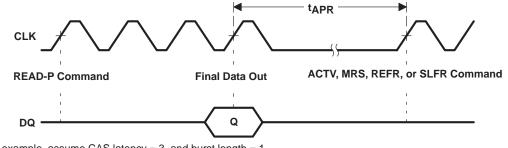

| <sup>t</sup> APR | Final data out of READ-P operation to ACTV, MRS command            | 6, SLFR, or REFR   |       | t <sub>F</sub> | RP – (CL          | –1) ∗ <sup>t</sup> Cł | <      |       | ns    |

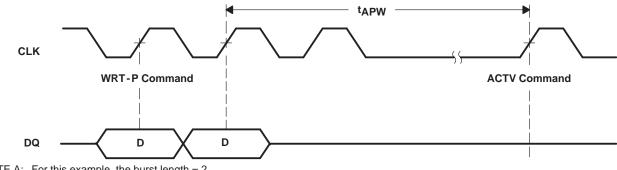

| t <sub>APW</sub> | Final data in of WRT-P operation to ACTV, MRS, S command           | SLFR, or REFR      |       |                | t <sub>RP</sub> + | 1 tCK                 |        |       | ns    |

| t <sub>T</sub>   | Transition time                                                    |                    | 1     | 5              | 1                 | 5                     | 1      | 5     | ns    |

| <sup>t</sup> REF | Refresh interval                                                   |                    |       | 64             |                   | 64                    |        | 64    | ms    |

| nWR              | Delay time, final data in of WRT operation to DEAC or DCAB command |                    | 1     |                | 1                 |                       | 1      |       | cycle |

| nCCD             | Delay time, READ or WRT command to an interru                      | pting command      | 1     |                | 1                 |                       | 1      |       | cycle |

| nCDD             | Delay time, CS low or high to input enabled or inhi                | bited              | 0     | 0              | 0                 | 0                     | 0      | 0     | cycle |

| <sup>n</sup> CLE | Delay time, CKE high or low to CLK enabled or dis                  | sabled             | 1     | 1              | 1                 | 1                     | 1      | 1     | cycle |

| nCWL             | Delay time, final data in of WRT command to REAL WRT-P command     | D, READ-P, WRT, or | 1     |                | 1                 |                       | 1      |       | cycle |

| nDID             | Delay time, ENBL or MASK command to enabled                        | or masked data in  | 0     | 0              | 0                 | 0                     | 0      | 0     | cycle |

| n <sub>DOD</sub> | Delay time, ENBL or MASK command to enabled                        | or masked data out | 2     | 2              | 2                 | 2                     | 2      | 2     | cycle |

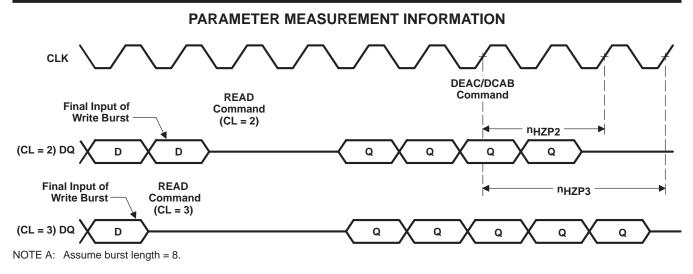

| nHZP2            | Delay time, DEAC or DCAB command to DQ in high-impedance state     | CAS latency = 2    |       | 2              |                   | 2                     |        | 2     | cycle |

| nHZP3            | Delay time, DEAC or DCAB command to DQ in high-impedance state     | CAS latency = 3    |       | 3              |                   | 3                     |        | 3     | cycle |

| nWCD             | Delay time, WRT command to first data in                           |                    | 0     | 0              | 0                 | 0                     | 0      | 0     | cycle |

<sup>†</sup> See Parameter Measurement Information for load circuits (see Figure 9).

‡ All references are made to the rising transition of CLK, unless otherwise noted.

SMOS695A - APRIL 1998 - REVISED JULY 1998

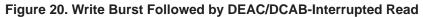

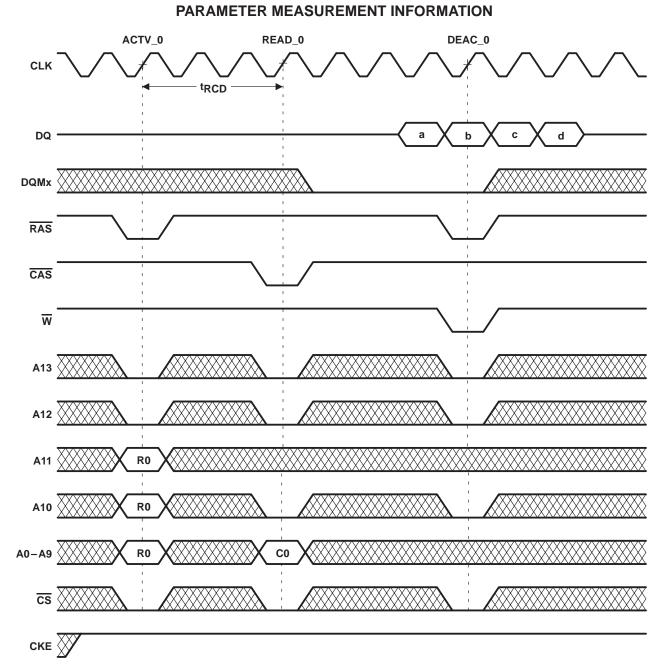

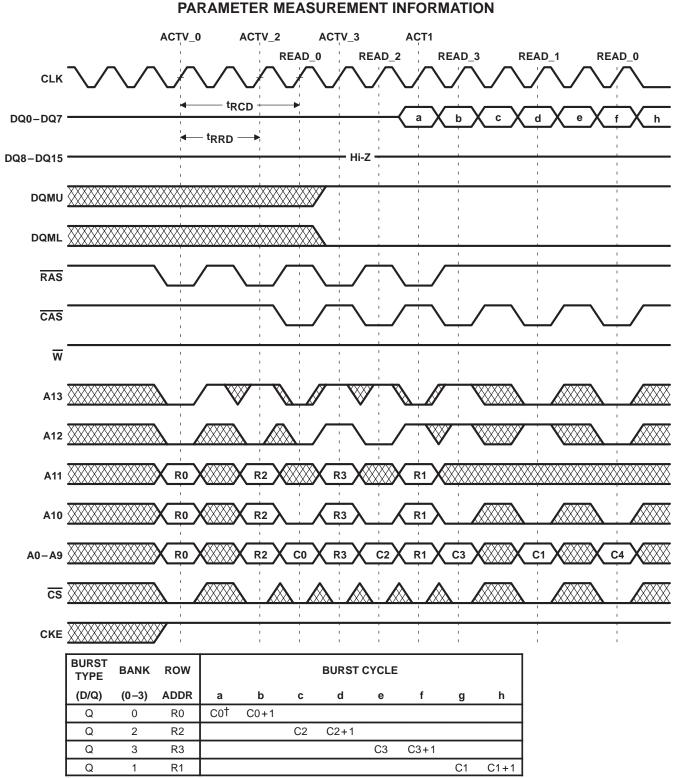

# PARAMETER MEASUREMENT INFORMATION

#### general information for ac timing measurements

The ac timing measurements are based on signal rise and fall times equal to 1 ns ( $t_T = 1$  ns) and a midpoint reference level of 1.5 V (INPUT = 2.8 V, 0 V) for LVTTL. For signal rise and fall times greater than 1 ns, the reference level should be changed to VIH MIN and VIL MAX instead of the midpoint level. All specifications referring to READ commands are valid for READ-P commands unless otherwise noted. All specifications referring to WRT commands are also valid for WRT-P commands unless otherwise noted. All specifications referring to consecutive commands are specified as consecutive commands for the same bank unless otherwise noted.

Figure 9. ac Load Circuit

# PARAMETER MEASUREMENT INFORMATION

SMOS695A - APRIL 1998 - REVISED JULY 1998

# PARAMETER MEASUREMENT INFORMATION

NOTE A: tRRD is specified for command execution in one bank to command execution in another bank.

Figure 12. Command-to-Command Parameters

NOTE A: For this example, assume CAS latency = 2, 3 and burst length > 1.

Figure 14. DQ Masking

SMOS695A - APRIL 1998 - REVISED JULY 1998

# PARAMETER MEASUREMENT INFORMATION

NOTE A: For this example, assume CAS latency = 2 and burst length = 2.

Figure 17. CLK-Suspend Operation (Assume Burst Length = 4)

Figure 18. Power-Down Operation

SMOS695A - APRIL 1998 - REVISED JULY 1998

# PARAMETER MEASUREMENT INFORMATION

NOTES: A. Assume both banks are deactivated before the execution of SLFR. B. Before/after self-refresh mode, 4K burst auto-refresh cycles are recommended to ensure that the SDRAM is fully refreshed.

Figure 19. Self-Refresh Entry/Exit

NOTE A: For this example, assume burst length = 1.

SMOS695A - APRIL 1998 - REVISED JULY 1998

# PARAMETER MEASUREMENT INFORMATION

NOTE A: For this example, assume CAS latency = 3, and burst length = 4.

NOTE A: For this example, assume CAS latency = 3, and burst length = 1.

Figure 23. Read With Auto-Deactivate

Figure 24. Power-Up Sequence

TMS664414, TMS664814, 4 194 304 BY 4-BIT/2 097 152 BY 8-BIT/1 048 576 BY 16-BIT SYNCHRONOUS DYNAMIC RANDOM-ACCESS REVISED JULY 199 TMS664164 **BY 4-BANK** 1998

6

SMOS695A - APRIL 1998 - REVISED JULY 1998

| BURST<br>TYPE | BANK  | ROW  | BURST CYCLE |        |        |        |  |  |  |  |  |

|---------------|-------|------|-------------|--------|--------|--------|--|--|--|--|--|

| (D/Q)         | (0-3) | ADDR | а           | b      | с      | d      |  |  |  |  |  |

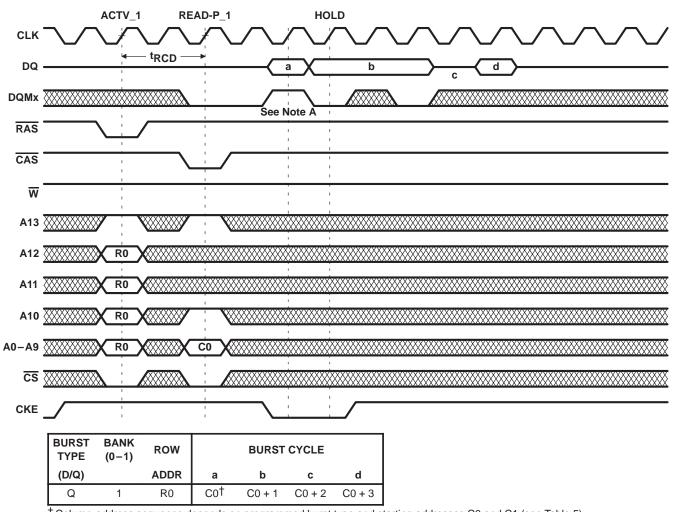

| Q             | 0     | R0   | C0†         | C0 + 1 | C0 + 2 | C0 + 3 |  |  |  |  |  |

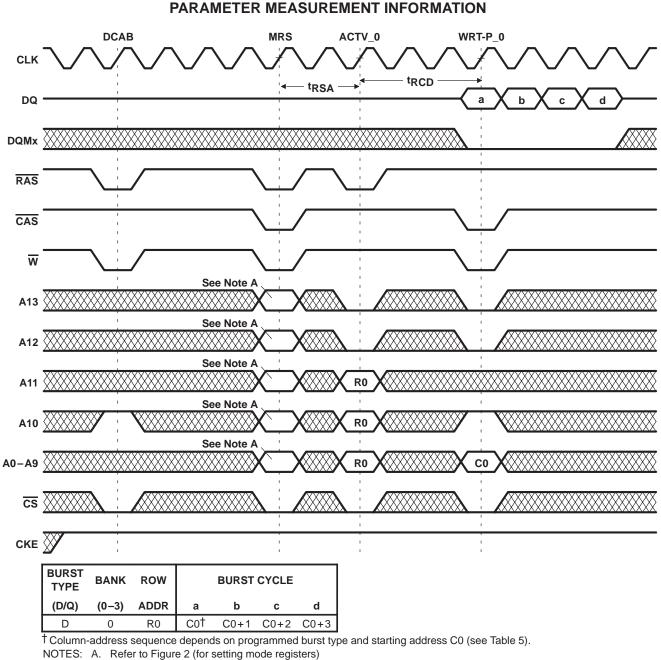

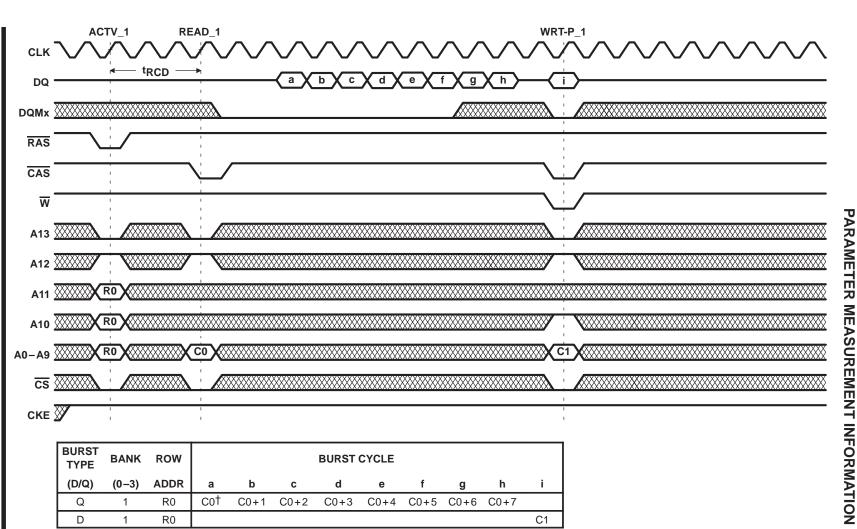

<sup>†</sup> Column-address sequence depends on programmed burst type and starting address C0 (see Table 5). NOTE A: This example illustrates minimum  $t_{RCD}$  for the '664xx4 at 125 MHz.

Figure 25. Read Burst (CAS latency = 3, burst length = 4)

ACTV\_3 WRT 3 DEAC\_3 CLK <sup>t</sup>RCD nwR DQ а b С d е g h f DQMx RAS CAS W  $\otimes$ A13  $\otimes$ A12 A11 R0 1 R0 A10 1 A0-A9 R0 C0 CS  $\diamond$ ске 淤 BURST BANK ROW **BURST CYCLE** TYPE ADDR (D/Q) (0-3)b d h а С е f g C0† C0+1 D R0 C0+2 C0+3 C0+4 C0+5 C0+6 C0+7 3

PARAMETER MEASUREMENT INFORMATION

<sup>†</sup> Column-address sequence depends on programmed burst type and starting address C0 (see Table 6). NOTE A: This example illustrates minimum t<sub>RCD</sub> and n<sub>WR</sub> for the '664xx4 at 125 MHz.

Figure 26. Write Burst (burst length = 8)

SMOS695A - APRIL 1998 - REVISED JULY 1998

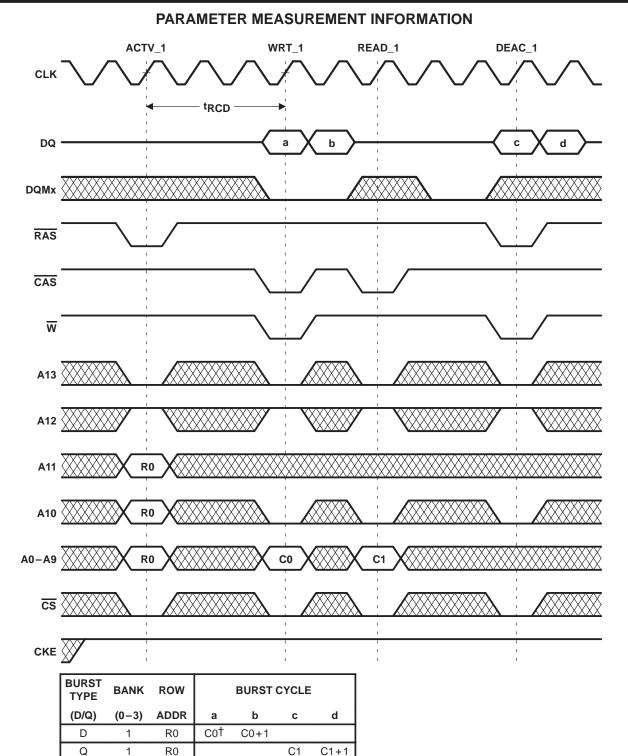

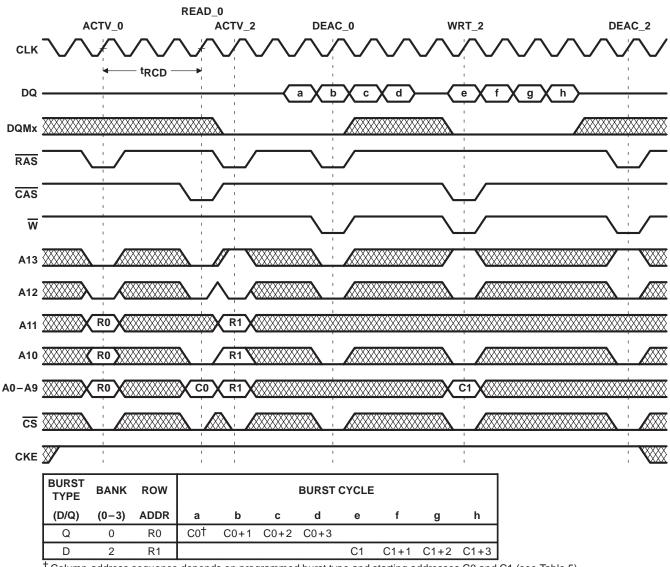

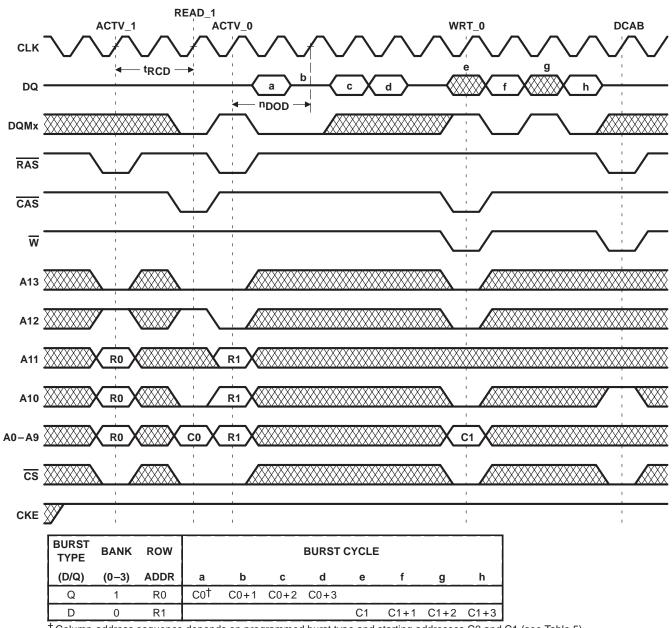

<sup>†</sup> Column-address sequence depends on programmed burst type and starting addresses C0 and C1 (see Table 4). NOTE A: This example illustrates minimum t<sub>RCD</sub> for the '664xx4 at 125 MHz.

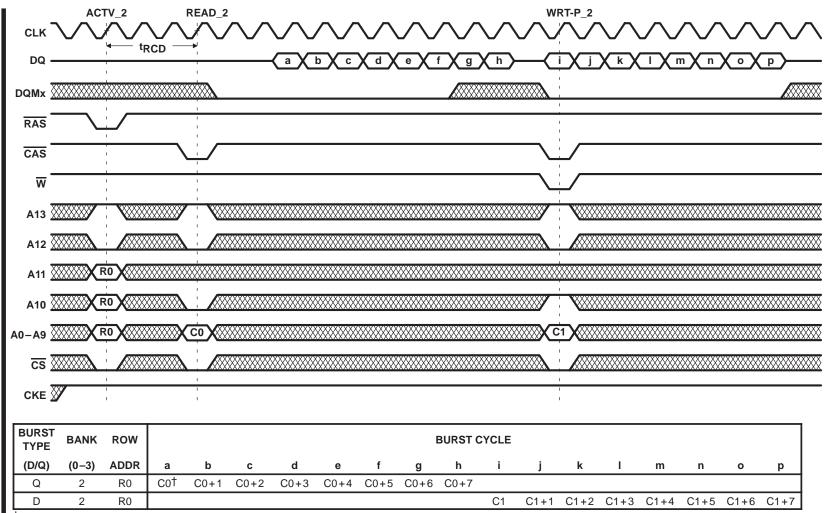

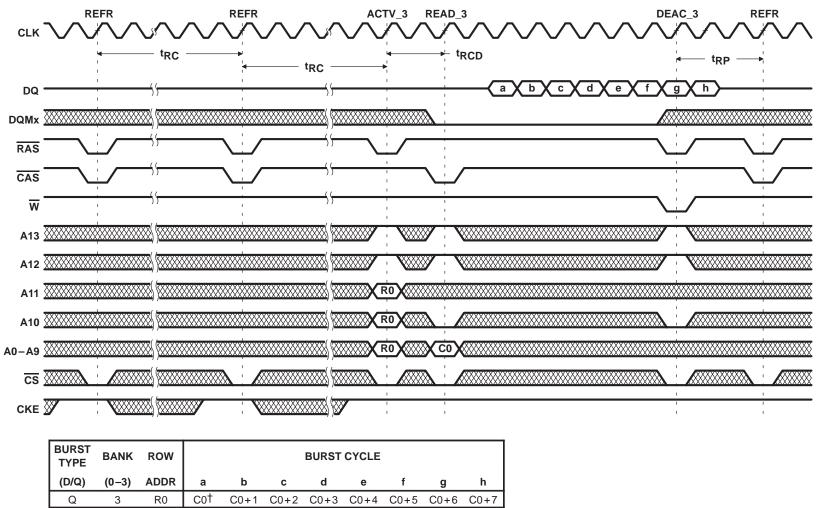

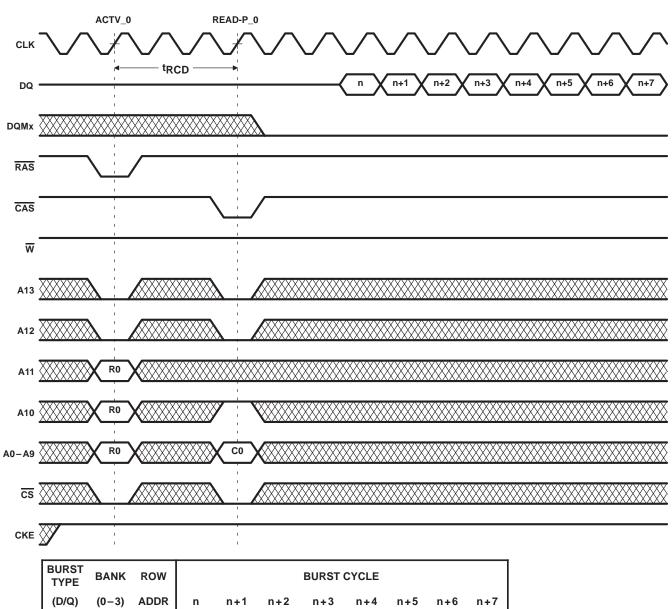

<sup>†</sup>Column-address sequence depends on programmed burst type and starting address C0 (see Table 6).

NOTE A: This example illustrates minimum  $t_{RCD}$  for the '664xx4 at 125 MHz.

Figure 28. Read-Write Burst With Automatic Deactivate (CAS latency = 3, burst length = 8)

PARAMETER MEASUREMENT INFORMATION

<sup>†</sup>Column-address sequence depends on programmed burst type and starting addresses C0, C1, and C2 (see Table 6). NOTE A: This example illustrates minimum tRCD for the '664xx4 at 125 MHz.

Figure 29. [A] Four-Bank Row-Interleaving Burst Length of 8 With Automatic Deactivate (CAS latency = 3, burst length = 8)

POST OFFICE BOX

TEXAS INSTRUMENTS DE BOX 1443 • HOUSTON, TEXAS 77251-1443

lemplate

Release

Date:

7-11-94

TMS664414, TMS664814, 194 304 BY 4-BIT/2 097 YNCHRONOUS IT/2 097 152 BY 8-BIT/1 048 576 BY 16-BIT DYNAMIC RANDOM-ACCESS MEMORIES **BY 4-BANK**

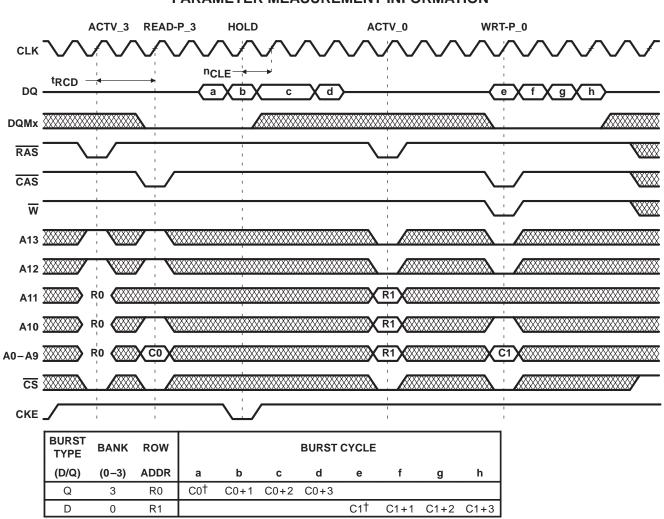

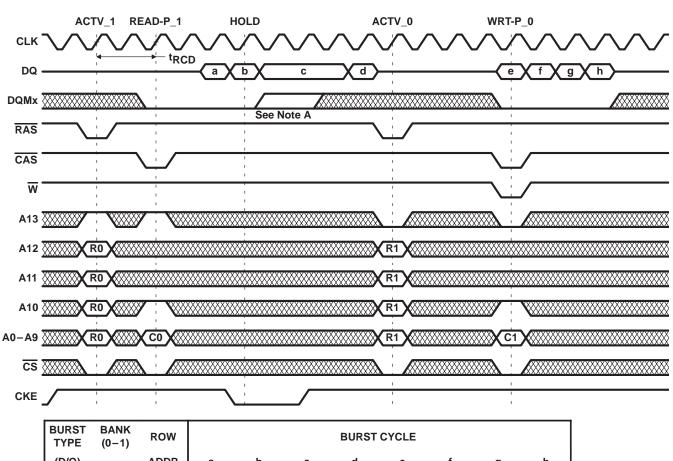

<sup>†</sup> Column-address sequence depends on programmed burst type and starting addresses C0, C1, and C2 (see Table 5). NOTE A: This example illustrates minimum t<sub>RCD</sub> for the '664xx4 at 125 MHz.

Figure 29. [B] Four-Bank Row-Interleaving Burst Length of 4 With Automatic Deactivate (CAS latency = 3, burst length = 4) (Cont'd)

POST OFFICE

77251-1443

FICE BOX 1443 • HOUSTON, TEXAS 77

SMOS695A - APRIL 1998 - REVISED JULY 1998

<sup>†</sup> Column-address sequence depends on programmed burst type and starting addresses C0, C1, and C2 (see Table 4).

Figure 30. Four-Bank Column-Interleaving Read Bursts (CAS latency = 3, burst length = 2)

SMOS695A - APRIL 1998 - REVISED JULY 1998

#### PARAMETER MEASUREMENT INFORMATION