### 990/9900 FAMILY MICROCOMPUTER COMPONENTS

- IEEE Std. 488-1975 Compatible

- Source and Acceptor Handshake

- Complete Talker and Listener Functions with Extended Addressing

- Controller and System Controller Capability

- Service Request

- Remote and Local with Lockout

- Serial and Parallel Polling

- Device Clear

- Device Trigger

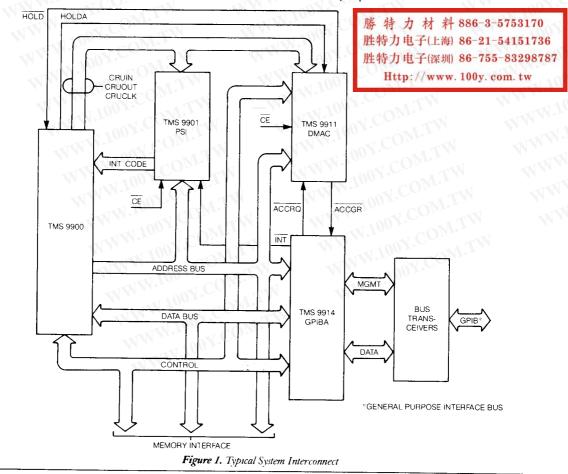

- Compatible with TMS 9911 DMA Controller

- Single +5 V Power Supply

- Interfaces directly to SN75160/1/2 Transceivers

#### DESCRIPTION

The TMS 9914 General Purpose Interface Bus Adapter is a microprocessor controlled versatile device which enables the designer to implement all of the functions or a subset described in the IEEE Std. 488-1975. Using this standard, a variety of instruments can be interconnected and remotely or automatically programmed and controlled. The TMS 9914 is fabricated with N-channel silicon-gate technology and is completely TTL compatible on all inputs and outputs including the power supply (+5 V). It needs a single phase clock (nominally 5 MHz) which may be independent of the microprocessor system clock and, therefore, it can easily be interfaced with most microprocessors. The general purpose interface bus adapter (GPIBA) performs the majority of the functions contained in IEEE STd. 488-1975 and is versatile enough to allow software implementation of those sections not directly implemented in hardware.

▶8

胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

8

### Table 1. Pin Description

| Name                    | 1/0             | Description                                                                                                                                                                                                                                                |

|-------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DI01<br>through<br>DI08 | 1/0             | DATA I/O lines: allow data transfer between the TMS 9914<br>and the IEEE 488 data bus.                                                                                                                                                                     |

| DAV                     | 1/0             | DATA VALID: Handshake Line. Sent by source device to indicate<br>to acceptors that there is valid data on the IEEE bus data lines.<br>ASSIGNED                                                                                                             |

| NRFD                    | 1/0             | NOT READY FOR DATA: Handshake Line. Sent by the acceptor<br>to the source device to indicate when it is ready for a new byte of data.                                                                                                                      |

| NDAC                    | 1/0             | DATA NOT ACCEPTED: Handshake Line. Sent by acceptor to source device to indicate when it has accepted the current byte on the data bus.                                                                                                                    |

| ATN                     | 1/0             | ATTENTION: Management Line. Sent by the controller. When ATN is asserted, the information on the data lines is interpreted as commands, sent by the controller When AT is false, the data lines carry data.                                                |

| IFC                     | 1/0             | INTERFACE CLEAR. Management Line. Sent by system controller to set the interface system, portions of which are contained in all interconnected devices in a known quiescent sta System controller assumes control. Open drain output with internal pullup. |

| REN                     | 1/0             | REMOTE ENABLE: Management Line. Sent by system controller and is used in conjunction<br>with other messages to select between two alternate sources of programming data, e.g. via<br>interface or front panel. Open drain output with internal pullup.     |

| SRQ                     | 1/0             | SERVICE REQUEST: Management Line. Issued by a device on the bus to the controller to indicate a need for service.                                                                                                                                          |

| EOI                     | 1/0             | END OR IDENTIFY: Management Line. If ATN is false, this signal is sent by the "talker" to indicate the end of a multiple byte transfer. If sent by the controller with ATN true, this w perform the parallel polling sequence.                             |

| CONTROLLER              | 0               | Bus transceiver control line. Indicates that the device is the controller.                                                                                                                                                                                 |

| ГЕ                      | 0               | TALK ENABLE: Bus transceiver control line. Indicates the direction of data transfer on the data bus.                                                                                                                                                       |

| D0 through D7           | I/O             | Data I/O lines that allow transfer of data between TMS 9914 and the microprocessor.                                                                                                                                                                        |

| RS0 through RS2         | Ι               | Address lines through which the TMS 9914 registers can be accessed by the microprocessor.                                                                                                                                                                  |

| OBIN                    | NI <sub>N</sub> | When true (high) DBIN indicates to the TMS 9914 that the microprocessor is about to read from one of its registers. When false, that the microprocessor is about to write to one of its registers.                                                         |

| WĒ                      | I               | WRITE ENABLE: indicates to the TMS 9914 that one of its registers is being written to.                                                                                                                                                                     |

| Œ                       | I               | CHIP ENABLE: selects and enables the TMS 9914 for an microprocessor data transfer.                                                                                                                                                                         |

| NT                      | 0               | INT: Open drain output. Sent to microprocessor to indicate the occurrence of an event on the bus requiring service.                                                                                                                                        |

| ACCRQ                   | 0               | ACCESS REQUEST: Signal to TMS 9911 DMA controller requesting DMA.                                                                                                                                                                                          |

NOTE: The names of the IEEE bus lines have been maintained, and are therefore negative logic signals.

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

9900 FAMILY SYSTEMS DESIGN

▶8

8-290

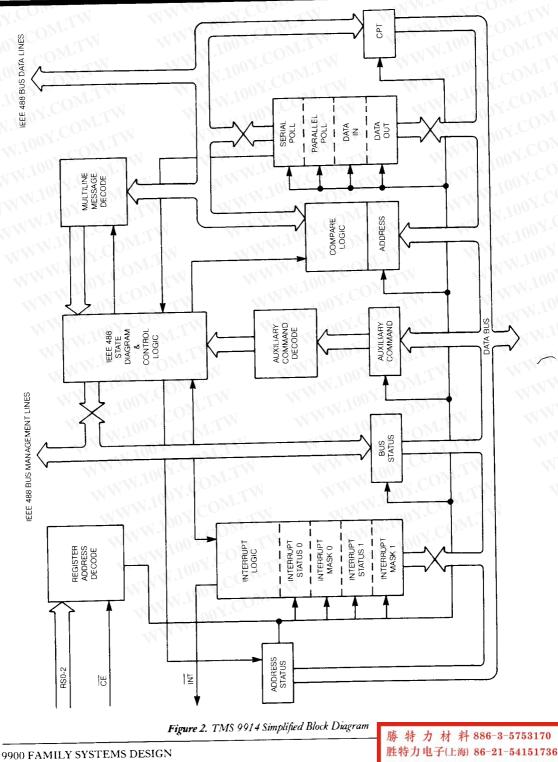

### FUNCTIONAL DESCRIPTION

The TMS 9914 interfaces to the CPU with an eight-bit bidirectional data bus, three register select lines, two DMA control lines, reset and interrupt request lines, a DBIN and a WE line.

The internal architecture of the TMS 9914 is arranged into 13 registers, there being seven WRITE and six READ registers. Some are actually address ports through which current status can be obtained. Table 2 lists these registers and their addresses. The microporcessor accesses a TMS 9914 register by supplying the correct register address in conjunction with  $\overline{WE}$  and DBIN. The  $\overline{CE}$  is used to enable the address decode.

| NAME                    | ТҮРЕ | RS2  | RS1   | RSO      | DBIN   | WE  |

|-------------------------|------|------|-------|----------|--------|-----|

| INTERRUPT STATUS 0      | N B  | 0    | 0.0   | 0        | 1 📢    | 1   |

| INTERRUPT MASK 0        | W    | 0    | 0     | 0        | 0      | 0   |

| INTERRUPT STATUS 1      | В    | 0    | 0     | COM      | 1      | NT. |

| INTERRUPT MASK 1        | W    | 0    | 0     | T.Mo     | 0      | 0   |

| ADDRESS STATUS          | B    | 0    | 1,00  | 0        | rW 1   |     |

| BUS STATUS              | B    | 0 🔨  | W 1   | V.CO     | TV1    | N1V |

| AUXILIARY COMMAND       | W W  | 0    | WW.10 | J dom    | 0      | 0   |

| ADDRESS SWITCH          | B    | 1    | 0     | 0.01     | 1      | 1   |

| ADDRESS                 | W    | 1    | 0     | 000      | 0      | 0   |

| SERIAL POLL             | W O. | 1    | 0     | 100 Y.CL | 0      | 0 < |

| COMMAND PASS<br>THROUGH | R.M. | TW 1 | 1     | 00.0     | COMITW | 1   |

| PARALLEL POLL           | W    | TVI  | 1     | 0        | 0      | 0   |

| DATA IN                 | R.   | IV   | 1VV   | hos      |        | 1   |

| DATA OUT                | WO   | W    | 1     | NN.1     | V.CC0  | 0   |

Table 2. TMS 9914 Registers and Addresses

NOTE: The Address Switch register is external to the TMS 9914

In DMA operation the TMS 9911 supplies the memory address but not the peripheral device address (i.e., RS0-2,  $\overline{CE}$ ) are not supplied). When the TMS 9914 sets  $\overline{ACCRQ}$  low true, it is either because of a byte input or a byte output, and this will happen whether or not DMA transfer will take place. If in response to  $\overline{ACCRQ}$  an  $\overline{ACCCR}$  (access granted) is received, the  $\overline{ACCRQ}$  will be reset and a DMA transfer will take place between the system memory and either the Data In or Data Out register. If the data transfer is with the microprocessor and if the microprocessor addresses either the Data In or Data Out register, the  $\overline{ACCRQ}$  line will be reset. Note that in DMA mode the sense of DBIN is inverted.

Table 3 lists the commands which are directly handled by the TMS 9914, and those which require intervention by the microprocessor for their implementation.

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

Table 3. Remote Multiple Message Coding

|                           |     | DIO8 | DIO7 | DIO6 | DIOS  | DIO4 | DI03 | DIO2  | DIOI |      | Note  |

|---------------------------|-----|------|------|------|-------|------|------|-------|------|------|-------|

| Addressed Command Group   | ACG | X    | 0    | 0    | 0     | X    | Х    | х     | X    | AC   |       |

| Device Clear              | DCL | X    | 0    | 0    | 1     | 0    | 1    | 0     | 0    | UC   |       |

| Group Execute Trigger     | GET | X    | 0    | 0    | 0     | 1    | 0    | 0     | 0    | AC   |       |

| Go To Local               | GTL | X    | 0    | 0    | 0     | 0    | 0    | 0     | 1    | AC   |       |

| Listen Address Group      | LAG | X    | 0    | 1    | X     | x    | х    | х     | x    | AD   |       |

| Local Lock Out            | LLO | X    | 0    | 0    | 1     | 0    | 0    | 0     | 1    | UC   |       |

| My Listen Address         | MLA | X    | 0    | 1    | L     | L    | L    | L     | L    | AD   | 1.1   |

| My Talk Address           | MTA | X    | 1    | 0    | Т     | T    | Т    | Т     | Т    | AD   | 2100  |

| My Secondary Address      | MSA | X    | 1    | 1    | S     | S    | S    | s     | s    | SE   | 3,4   |

| Other Secondary Address   | OSA |      |      |      |       |      |      |       |      | SE   | 4,5   |

| Other Talk Address        | OTA |      |      | 1    | FAG • | MT   | 4    |       |      | AD   | 11-   |

| Primary Command Group     | PCG |      |      |      |       |      |      |       |      |      | 6     |

| Parallel Poll Configure   | PPC | X    | 0    | 0    | 0     | 0    | 1    | 0     | 1    | AC   | 7     |

| Parallel Poll Enable      | PPE | X    | 1    | 1    | 0     | S    | Р    | Ρ     | Р    | SE 🚽 | 8,9   |

| Parallel Poll Disable     | PPD | Х    | 1    | 1    | 1     | D    | D    | D     | D    | SE   | 8, 10 |

| Parallel Poll Unconfigure | PPU | X    | 0    | 0    | 1     | 0    | 1    | 0     | 1    | UC   | 11    |

| Secondary Command Group   | SCG | X    | 1    | 1    | Х     | X    | X    | x     | X    | SE   |       |

| Selected Device Clear     | SDC | X    | 0    | 0    | 0     | 0    | 1    | 0     | 0    | AC   |       |

| Serial Poll Disable       | SPD | X    | 0    | 0    | 1     | 1    | 0    | 0     | 1    | UC   |       |

| Serial Poll Enable        | SPE | X    | 0    | 0    | 1.1   | 1    | 0    | 0     | 0    | UC   |       |

| Take Control              | TCT | Х    | 0    | 0    | 0     | 1    | 0    | 0     | 1    | AC   | 12    |

| Talk Address Group        | TAG | Х    | 1    | 0    | x     | X    | X    | x     | x    | AD   |       |

| Universal Command Group   | UCG | Х    | 0    | 0    | 1     | X    | x    | X     | X    | UC   |       |

| Unlisten                  | UNL | Х    | 0    | 1    | 1     | 1    | 1    | $C_1$ | 1    | AD   |       |

| Untalk                    | UNT | X    | 1    | 0    | 1     | 1    | 1    | 1     | 1    | AD   |       |

Symbols: AC - Addressed Command

AD - Address (Talk or Listen)

UC - Universal Command

SE - Secondary (Command or Address)

u - Logical Zero (high level on IEEE Bus; Low level within 9914).

1 - Logical One (Low level on IEEE Bus; High level within 9914).

X - Don't Care (received message)

X - Must Not Drive (transmitted)

力材料 886-3-5753170 特 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www. 100y. com. tw

## ▶8

9900 FAMILY SYSTEMS DESIGN

#### Peripheral and Interface Circuits

## TMS 9914 GENERAL PURPOSE INTERFACE BUS ADAPTER

Notes to Table 3:

- 1. L L L L L: Represents the coding for the device listen address.

- 2. T T T T T: Represents the coding for the device talk address.

- 3. S S S S S: Represents the coding for the device secondary address.

- 4. Secondary addresses will be handled via address pass through.

- 5. OSA will be handled as an invalid secondary address pass through by the MPU.

- 6.  $PCG = ACG \vee UCG \vee LAG \vee TAG$

- 7. PPC will be handled in software by the MPU via Unrecognized Address Command Group pass through.

- 8. PPE, PPD will be handled via pass through next secondary feature.

- 9. S P P P represents the sense and bit for remote configurable parallel poll.

- 10. D D D D specify don't care bits that must be sent all zeroes, but need not be decoded by receiving device.

- 11. PPU is handled via Unrecognized Universal Command Group pass through.

- TCT will be handled via Unrecognized Addressed Command Group pass through. However, in this case, the device must be in TADS before the pass through will occur.

| Interrupt          | Status Regis                 | ters o and I                                      |                        |      |             |                                              |                                   | -                                  |  |  |

|--------------------|------------------------------|---------------------------------------------------|------------------------|------|-------------|----------------------------------------------|-----------------------------------|------------------------------------|--|--|

| INT0               | INT1                         | BI                                                | BO                     | END  | SPAS        | RLC                                          | MAC                               | WITE -                             |  |  |

| GET                | UUCG                         | UACG                                              | АРТ                    | DCAS | MA          | SRQ                                          | IFC                               |                                    |  |  |

| INT0<br>INT1<br>BI | An interrup                  | ot occurred in<br>ot occurred in<br>been received | register 1             |      | GET<br>UUCG | An Undefir<br>been receiv                    | ned Univers<br>ved                | ger has occurred<br>al Command has |  |  |

| BO N               | A byte has                   | been output                                       |                        |      | UACG        |                                              |                                   | sed Command has                    |  |  |

| END                | An EOI oc                    | curred with A                                     | TN false               |      |             |                                              |                                   | t will also be set on              |  |  |

| SPAS               | Serial Poll<br>rsv set in th | Active State h<br>le Serial Poll 1<br>FE/LOCAL    | as occurre<br>register |      |             | receipt of a<br>pts feature<br>register is u | command when the<br>liary Command |                                    |  |  |

| RLC                | occurred                     | E/LOCAL                                           | change na              |      | APT         |                                              |                                   |                                    |  |  |

| MAC                |                              | change has o                                      | courred                |      | DCAS        | Device Cle                                   | ar Active St                      | tate has occurred                  |  |  |

| MAC                | Tin address                  | entange nus o                                     | 1000                   |      | MA          | My Addres                                    | ss (MLAVI                         | MTA)•SPSM                          |  |  |

|                    |                              |                                                   |                        |      | SRQ         | A Service l                                  | Request has                       | been received                      |  |  |

|                    |                              |                                                   |                        |      | IFC         |                                              | s been rece                       |                                    |  |  |

|                    |                              |                                                   |                        |      |             |                                              |                                   |                                    |  |  |

Interrupt Status Registers 0 and 1

INTO is the logical OR of each bit of Interrupt Status Register 0 ANDed with the respective bit of Interrupt Mask Register 0. INT1 is the same but applies to Interrupt Mask and Status Register 1. Reading either Interrupt Status Register will also clear it. The INT line will be cleared only when the interrupt status register which caused the interrupt is read.

Interrupt Mask Registers 0 and 1

| $\square$ | $\searrow$ | BI   | BO  | END  | IFC | RLC | MAC  |

|-----------|------------|------|-----|------|-----|-----|------|

| GET       | UUCG       | UACG | APT | DCAS | МА  | SRQ | SPAS |

The Interrupt Mask Registers 0 and 1 correspond to the Interrupt Status Registers 0 and 1 respectively, with the exception of INT0 and INT1.

Address Status Register

| LACS TACS | REM | LLO | ATN | LPAS | TPAS | LADS<br>V<br>LACS | TADS<br>V<br>TACS | ulpa |

|-----------|-----|-----|-----|------|------|-------------------|-------------------|------|

|-----------|-----|-----|-----|------|------|-------------------|-------------------|------|

9900 FAMILY SYSTEMS DESIGN

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

8-293

胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

The Address Status Register is used to convey the addressed state of the talker/listener and the remote/local and local lockout condition. This information is derived from the TMS 9914 internal logic states at the time of reading. The ulpa bit is used for dual addressing and indicates the state of the LSB of the bus at last primary addressed time.

#### **Bus Status Register**

| 1 | ATN | DAV | NDAC     | NRFD | FOI | SPO | IFC | DEN | È |

|---|-----|-----|----------|------|-----|-----|-----|-----|---|

| 1 |     |     | <u> </u> |      | LOI | ShQ | пс  | KEN | 5 |

The Bus Status Register allows the microprocessor to obtain the current status of the IEEE 488 Bus Management Lines.

勝 持 力 材 料 886-3-5753170

Auxiliary Command Register

| C/S f4 | f3 | f2 | f1 | f0 |

|--------|----|----|----|----|

|--------|----|----|----|----|

The Auxiliary Command Register allows control of additional features on chip and provides a means of inputting some of the local messages to the interface functions. Table 4 lists these messages and commands. If C/S = 1, the feature will be set and if C/S = 0, the feature will be cleared. If C/S = NA, it should be sent as zero.

### Table 4. Auxiliary Commands

| Function                     | Mnemonic | C/S | f4 | f3   | f2   | fI  | f0 |

|------------------------------|----------|-----|----|------|------|-----|----|

| Chip Reset                   | rst      | 0/1 | 0  | 0    | 0    | 0   | 0  |

| Release ACDS holdoff         | dacr     | 0/1 | 0  | 0    | 0    | 0   |    |

| Release RFD holdoff          | rhfd     | NA  | 0  | 0    | 0    | 1   | 0  |

| Holdoff on all data          | hdfa     | 0/1 | 0  | 0    | 0    | 1   | 1  |

| Holdoff on EOI only          | hdfe     | 0/1 | 0  | 0    | 01.1 | 0   | 0  |

| Set new byte available false | nbaf     | NA  | 0  | 0    | 11.  | 0   | 1  |

| Force group execute trigger  | fget     | 0/1 | 0  | 0    | 1    | TY1 | 0  |

| Return to local              | rtl      | 0/1 | 0  | 0    |      | 1   | 1  |

| Return to local immediate    | rtli     | 0   | 0  | 0    | 101  | 1   | 1  |

| Send EOI with next byte      | feoi     | NA  | 0  | 110  | 0    | 0   | 0  |

| Listen only                  | lon      | 0/1 | 0  | 1    | 0    | 0   | 1  |

| Talk only                    | ton      | 0/1 | 0  | 1    | 0.0  | 1   | 0  |

| Take control synchronously   | tcs      | NA  | 0  | VII. | 1-7  | 0   | 1  |

| Take control asynchronously  | tca      | NA  | 0  | 1    | 1.1  | 0   | 0  |

| Go to standby                | gts      | NA  | 0  | 1    | 0    | 1   | 1  |

| Request parallel poll        | rpp      | 0/1 | 0  | 1    | 1    | 1   | 0  |

| Send interface clear         | sic      | 0/1 | 0  | 1    | 1    | 1   | 1  |

| Send remote enable           | sre      | 0/1 | 1  | 0    | 0    | 0   | 0  |

| Request contol               | rqc      | NA  | 1  | 0    | 0    | 0   | 1  |

| Release control              | rlc      | NA  | 1  | 0    | 0    | 1   | 0  |

| Disable all interrupts       | dai      | 0/1 | 1  | 0    | 0    | 1   | 1  |

| Pass through next secondary  | pts      | NA  | 1  | 0    | 1    | 0   | 0  |

| Set T1 delay                 | stdl     | 0/1 | 1  | 0    | 1    | 0   | 1  |

|                              |          |     |    |      |      |     |    |

#### Peripheral and Interface Circuits

## TMS 9914 GENERAL PURPOSE INTERFACE BUS ADAPTER

| Address Re | gister |     |    | MM |    |

|------------|--------|-----|----|----|----|

| edpa       | dal    | dat | A5 | A4 | A3 |

edpaenable dual primary addressingdatdisable the talk functiondaldisable the listen functionA1 - A5primary device address

A2

The Address Switch Register corresponds to the Address Register. A power-up RESET or a rst command with C/S = 1 will leave the chip in a totally idle state. At this point, the Address Switch Register is read and the value is written into the Address Register. The reset condition is then cleared by sending rst with C/S = 0.

A1

Serial Poll Register

|    | r titu | <b>1</b> |    | 0.1 | 6.0 | 60 | 61 |

|----|--------|----------|----|-----|-----|----|----|

| S8 | rsv    | S6       | 55 | S4  | 53  | 52 | 51 |

The Serial Poll register is used to establish the status byte that is sent out when the controller conducts a serial poll. Bits 1 through 6 and 8 contain status information, while bit 7, rsv, is used to enable the SRQ line and to indicate to the controller which device(s) was responsible for making a service request.

Command Pass Through Register

| DIO8 | DIO7 | DIO6 | DIO5 | DIO4 | DIO3 | DIO2 | DIO1 |

|------|------|------|------|------|------|------|------|

| 0.00 |      |      |      |      |      |      |      |

The Command Pass Through Register is used to pass through to the microprocessor any commands or secondary addresses that are not automatically handled in the TMS 9914.

Parallel Poll Register

| PP8 | PP7 | PP6 | PP5 | PP4 | PP3 | PP2 | PP1 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|-----|-----|-----|-----|-----|-----|-----|-----|

This register contains the status bit that is output when the controller conducts a parallel poll.

Data-In Register

| DIO8 | DIO7 | DIO6 | DIO5                                  | DIO4 | DIO3 | DIO2 | DIO1 |

|------|------|------|---------------------------------------|------|------|------|------|

|      | 1    |      | · · · · · · · · · · · · · · · · · · · |      |      | -1 N |      |

The data-in register is used to move data from the interface bus when the chip is addressed as a listener. Upon receipt of a data byte, the chip will hold NRFD true until the microprocessor reads the data-in register, when NRFD will be set false automatically.

Data-Out Register

| DIO8 | DIO7 | DIO6 | DIO5 | DIO4 | DIO3 | DIO2 | DIO1 |

|------|------|------|------|------|------|------|------|

| L    |      |      | 1    |      |      |      |      |

The data-out register is used to move data from the TMS 9914 onto the IEEE std 488-1975 data bus.

After sending a byte out on the bus, the device can take part in a new handshake only after a new byte is placed in the data-out register, when it will be able to send DAV true again.

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## NAT9914

Pin compatible with TI TMS9914A Software compatible with NEC µPD7210 or TI TMS9914A controller chips Low power consumption Meets all IEEE 488.2 requirements Bus line monitoring Preferred implementation of requesting service Will not send messages when there are no Listeners Performs all IEEE 488.1 interface functions Programmable data transfer rate (T1 delays of 350 ns, 500 ns, 1.1 µs, and 2 µs) Automatic EOS and/or NL message detection Direct memory access (DMA) Automatically processes IEEE 488 commands and reads undefined commands

TTL-compatible CMOS device Programmable clock rate up to 20 MHz Reduces driver overhead Does not lose a data byte if ATN is asserted while transmitting data

INSTRUMENTS®

0391671 CP01111 K9441

> BUY ONLINE! ni.com/store

## Description

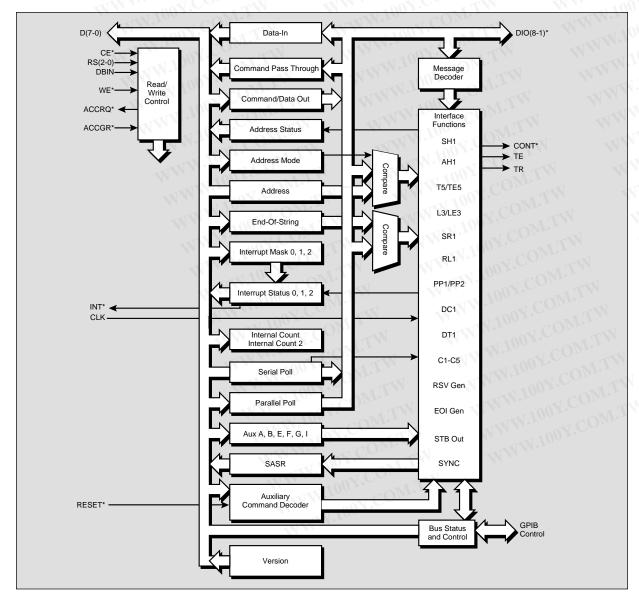

The NAT9914 IEEE 488.2 controller chip can perform all the interface functions defined by that the IEEE Standard 488.1-1987, and also meets the additional requirements and recommendations of the IEEE Standard 488.2-1987. Connected between the processor and the IEEE 488 bus, the NAT9914 provides high-level management of the IEEE 488 bus, significantly increases the throughput of driver software, and simplifies both the hardware and software design. The NAT9914 performs complete IEEE 488 Talker, Listener, and Controller functions. In addition to its numerous improvements, the NAT9914 is also completely pin compatible with the TI TMS 9914A and software compatible with the NEC µPD7210 and TI TMS9914A controller chips.

# **IEEE 488.2 Overview**

The IEEE 488.2 standard removes the ambiguities of IEEE 488.1 by standardizing the way instruments and controllers operate. It defines data formats, status reporting, error handling, and common configuration commands to which all IEEE 488.2 instruments must respond in a precise manner. It also defines a set of controller requirements. The benefits of IEEE 488.2 for the test system developer are reduced development time and cost because systems are more compatible and reliable. The NAT9914 brings the full power of IEEE 488.2 to the design engineer along with numerous other design and performance benefits, while retaining the 40-pin and 44-pin hardware configurations of the TI TMS 9914A.

## General

The NAT9914 manages the IEEE 488 bus. You program the IEEE 488 bus by writing control words into the appropriate registers. CPU-readable status registers supply operational feedback. The NAT9914 mode determines the function of these registers. On power up or reset, the NAT9914 registers resemble the TMS9914A register set with additional registers that supply extra functionality and IEEE 488.2 compatibility. In this mode, the NAT9914 is completely pin compatible with the TI TMS9914A. If you enable the 7210 mode, the registers resemble the NEC µPD7210 register set with additional registers that supply extra functionality and IEEE 488.2 compatibility. This mode is not pin compatible with the NECµPD7210. Figure 3 shows the key components of the NAT9914.

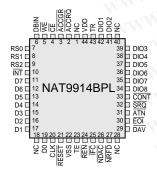

Figure 1. NAT9914BPD **Pin Configuration**

Figure 2. NAT9914BPL Pin Configuration

# **Pin Identification**

| Pin N       | lumber      |           | 1                     | COM.                                                  |

|-------------|-------------|-----------|-----------------------|-------------------------------------------------------|

| PLCC        | DIP         | Mnemonic  | Туре                  | Description                                           |

| 11, 12, 13, | 10, 11, 12, | D(7-0)    | I/0 <sup>†</sup>      | Bidirectional 3-state data bus transfers              |

| 14, 15, 16, | 13, 14, 15, | N.100     | 0M.,                  | commands, data, and status between the                |

| 17, 19      | 16, 17      | 100Y.C    | A.                    | NAT9914 and the CPU.                                  |

|             | NV.         | W.L.      | 10m                   | D0 is the most significant bit.                       |

| 4           | 3           | CE*       | CON                   | Chip Enable gives access to the register              |

|             | W           | 1004      |                       | selected by a read or write operation, and the        |

|             | 1           | WW.L      | CO.                   | register selects RS(2-0).                             |

| 6           | 5           | DBIN      |                       | With the Data Bus Input, you can place the            |

| VT.         |             | 10        | ay.                   | contents of the register selected by RS(2-0) and      |

|             | M           | WWW.L     | J.C                   | $CE^*$ onto the data bus D(7-0). The polarity of      |

|             |             | I.V.      | 002.                  | DBIN is reversed for DMA operation.                   |

| 5           | 4           | WE*       |                       | The Write input latches the contents of the data      |

| COM.        | 4           | VVL       |                       | bus D(7-0) into the register selected by RS(2-0).     |

| 3           | 2           | ACCGR*    |                       | The Access Grant signal selects the DIR or            |

| S.COM       | 2           | ACCON     | 1.00                  |                                                       |

| 2           | 1. F        |           | 0                     | CDOR for the current read or write cycle.             |

| 2           | WL.IN       | ACCRQ*    | U                     | The Access Request output asserts to request a        |

|             | 10          | 01.14     | It                    | DMA Acknowledge cycle.                                |

| 20          | 18          | CLK       | It 1                  | The CLK input can be up to 20 MHz.                    |

| 21          | 19          | RESET*    | ľ                     | Asserting the RESET* input places the NAT9914         |

| 10          | COM         |           |                       | in an initial, idle state.                            |

| 10          | 9           | INT*      | 0                     | The Interrupt output asserts when one of the          |

|             | . I and .   | (00)      | 10.1                  | unmasked interrupt conditions is true. The NAT9914    |

|             | V.COm       | W         | WW                    | does not drive INT* high. The INT* pin must be        |

|             | Moo         |           |                       | pulled up by an external resistor.                    |

| 9, 8, 7     | 8, 7, 6     | RS(2-0)   | - T                   | The Register Selects determine which register to      |

|             |             | W         | -                     | access during a read or write operation.              |

| 25          | 23          | IFC*      | I/0 <sup>†,††</sup>   | Bidirectional control line initializes the IEEE 488   |

|             | 100Y.CC     | WTIE      | (00)                  | interface functions.                                  |

| 24          | 22          | REN*      | I/O⁺                  | Bidirectional control line selects either remote or   |

|             | N.1001.     | .M.       | (00)                  | local control of devices.                             |

| 31          | 28          | ATN*      | I/0 <sup>†</sup>      | Bidirectional control line indicates whether data     |

|             | W.100       | COM       |                       | on the DIO lines is an interface or device-           |

|             | X 100 1     | . Mon     |                       | dependent message.                                    |

| 32          | 29          | SRQ*      | I/0 <sup>†</sup>      | Bidirectional control line requests service from      |

|             | WW.100      | COM.      | IN                    | the controller.                                       |

| 34, 35, 36, | 31, 32, 33, | DIO(8-1)* | I/0 <sup>+</sup>      | 8-bit bidirectional IEEE 488 data bus                 |

| 37, 38, 39, | 34, 35, 36  | NY.CO     | WT                    | WW 100Y.COLL                                          |

| 41, 42      | 37, 38      | CON       |                       | WWW.LCOM.                                             |

| 29          | 26          | DAV*      | I/0 <sup>†</sup>      | Handshake line indicates that the data on the         |

|             | NW          | ANY.CO.   | 17.5                  | DIO(8-1)* lines is valid.                             |

| 27          | 25          | NRFD*     | I/0 <sup>†</sup>      | Handshake line indicates that the device is ready     |

|             |             | N 1001.   | M                     | for data.                                             |

| 26          | 24          | NDAC*     | I/0 <sup>†</sup>      | Handshake line indicates the completion of a          |

| 20          | - 4         | 1.D/10    |                       | message reception.                                    |

| 30          | 27          | EOI*      | I/0 <sup>†</sup>      | Bidirectional control line indicates the last byte of |

| 50          | 21          | LUI       |                       | a data message or executes a parallel poll.           |

| 23          | 21          | TE        | <b>O</b> <sup>†</sup> | Talk Enable controls the direction of the IEEE 488    |

| 23          | 21          | IC        | 0                     |                                                       |

|             |             |           |                       | data transceiver.                                     |

料 886-3-5753170

胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

勝

力 材

特

### 2 National Instruments -

Tel: (512) 794-0100 • Fax: (512) 683-9300 • info@ni.com • ni.com/gpib

# W.100Y.COM.TW **IEEE 488.2 Controller Chip** WWW.I

| Pin Nu          | mber   | Wr.      |                 | COMP.                                                            | MW.10 N COM.                                        |

|-----------------|--------|----------|-----------------|------------------------------------------------------------------|-----------------------------------------------------|

| PLCC            | DIP    | Mnemonic | Туре            | Description                                                      | W.1001. COM.1                                       |

| 43              | 39     | TR       | 0†              | Trigger asserts when one of the trigger conditions is satisfied. | WWW.100Y.COM.TW                                     |

| 33              | 30     | CONT*    | 0,              | Controller asserts when the NAT9914 is<br>Controller-In-Charge.  | 勝 特 力 材 料 886-3-5753170<br>胜特力电子(上海) 86-21-54151736 |

| 44              | 40     | VDD      | <1 <b>-</b>     | Power pin – +5 V (±5%)                                           |                                                     |

| 22              | 20     | VSS      | <u> </u>        | Ground pin – 0 V                                                 | 胜特力电子(深圳) 86-755-8329878                            |

| 1, 18,<br>28,40 | NV2.10 | NC       | 17 <del>1</del> | No connect                                                       | Http://www.100y.com.tw                              |

<sup>†</sup> The pin contains an internal pull-up resistor of 25 to 100 k $\Omega$ .

\* Active low.

<sup> $\pi$ </sup> In controller applications where the CLK signal frequency is > 8 MHz, IFC\* should be pulled up with a 4.7 k $\Omega$  resistor.

Figure 3. NAT9914 Block Diagram

# 9914 Mode Registers

In 9914 mode, the NAT9914 registers consist of all the TI TMS9914A registers and two types of additional registers – newly defined registers and paged-in registers. The NAT9914 maps the newly defined registers into the unused portion of the 9914 address space. Each paged-in register appears at offset 2 immediately after you issue an auxiliary page-in command, and it remains there until you page another register into the same space or you issue a reset. The table below lists all the registers in the 9914 register set. See the NAT9914 Reference Manual available at **ni.com** for more information.

## 9914 Register Set

| Register                        | Page In | <b>N</b> B | RS(2-0 | )  | WE* | DBIN                   | CE* | ACCGR*     |

|---------------------------------|---------|------------|--------|----|-----|------------------------|-----|------------|

| Interrupt Status 0              | U       | 0          | 0      | 0  | 1   | 1                      | 0   | 1          |

| Interrupt Mask 0                | U       | 0          | 0      | 0  | 0   | 0                      | 0   | 1          |

| Interrupt Status 1              | U       | 0          | 0      | 1  | 1   | 01                     | 0   | <u>⊸</u> 1 |

| Interrupt Mask 1                | U       | 0          | 0      | 10 | 0   | 0                      | 0   | 1          |

| Address Status                  | U       | 0          | 1      | 0  | 17  | $\mathbb{C}1^{\times}$ | 0   | 1          |

| Interrupt Mask 2 <sup>+</sup>   | Р       | 0          | 1      | 0  | 0   | 0                      | 0   | 1          |

| End-of-String <sup>+</sup>      | Р       | 0          | 1      | 0  | 0   | 0                      | 0   | . 1        |

| Bus Control                     | Р       | 0          | 1      | 0  | 0   | 0                      | 0   | 1          |

| Accessory                       | Р       | 0          | 1      | 0  | 0   | 0                      | 0   | 1          |

| Bus Status                      | U       | 0          | 1      | 1  | 11  | 01                     | 0   | 11         |

| Auxiliary Command               | U       | 0          | 1      | 1  | 0   | 0                      | 0   | 1          |

| Interrupt Status 2 <sup>+</sup> | Р       | 1          | 0      | 0  | 1.  | 1                      | 0   | 04         |

| Address                         | U       | 1          | 0      | 0  | 0   | 0                      | 0   | _1\        |

| Serial Poll Status <sup>+</sup> | Р       | 1          | 0      | 1  | 1   | 1                      | 0   | 1          |

| Serial Poll Mode                | U       | 1          | 0      | 1  | 0   | 0                      | 0   | CD         |

| Command Pass Thru               | U       | 1          | 1      | 0  | 1   | 11                     | 0   | 1          |

| Parallel Poll                   | U       | 1          | 1      | 0  | 0   | 0                      | 0   | 1          |

| Data-In                         | U       | 1          | 1      | 1  | 1   | 11                     | 0   | ~1C        |

| Data-In                         | U       | Х          | Х      | Х  | Х   | 0                      | Х   | 0          |

| Command/Data Out                | U       | 1          | 1      | 1  | 0   | 0                      | 0   | 01         |

| Command/Data Out                | U       | Х          | Х      | Х  | 0   | . <b>1</b> N           | X   | 0          |

The " symbol denotes features (such as registers and auxiliary commands) that are not available in the TMS9914A

Notes for the PAGE-IN column:

- U = Page-in auxiliary commands do not affect the register offset.

- P = The register offset is valid only after a page-in auxiliary command.

# 7210 Mode Registers

The NAT9914 registers include all the NEC  $\mu$ PD7210 registers plus two types of additional registers – extra auxiliary registers and paged-in registers. You write the extra auxiliary registers the same as standard  $\mu$ PD7210 auxiliary registers. On issuing an auxiliary page-in command, the paged-in registers appear at the same offsets as existing  $\mu$ PD7210 registers. At the end of the next CPU access, the chip pages out the paged-in registers. The following table lists all the registers in the 7210 mode register set. See the NAT9914 Reference Manual available at **ni.com** for more information.

## 7210 Register Set

| Register                            | PAGE-IN |    | A(2-0 | ) | WE* | DBIN | CE* | ACCGR |

|-------------------------------------|---------|----|-------|---|-----|------|-----|-------|

| Data-In                             | U       | 0  | 0     | 0 | 1   | 1    | 0   | 1     |

| Data-In                             | X       | Х  | Х     | Х | Х   | 0    | X   | 0     |

| Command/Data Out                    | U       | 0  | 0     | 0 | 0   | 0    | 0   | 1     |

| Command/Data Out                    | X       | Х  | Х     | Х | 0   | 1    | X   | 0     |

| Interrupt Status 1                  | U.      | 0  | 0     | 1 | 1   | 1    | 0   | 1     |

| Interrupt Mask 1                    | U       | 0  | 0     | 1 | 0   | 0    | 0   | 1     |

| Interrupt Status 2                  | U       | 0  | 1     | 0 | 1   | 1    | 0   | 1     |

| Interrupt Mask 2                    | U       | 0  | 1     | 0 | 0   | 0    | 0   | 1     |

| Serial Poll Status                  | N       | 0  | 1     | 1 | 1   | 1    | 0   |       |

| Serial Poll Mode                    | N.V     | 0  | 1     | 1 | 0   | 0    | 0   | 1     |

| Version                             | Р       | 0  | 1     | 1 | 1   | 1    | 0   | 1     |

| Internal Counter 2                  | Р       | 0  | 1     | 9 | 0   | 0    | 0   | 1     |

| Address Status                      | U       | 1  | 0     | 0 | 1   | 1    | 0   | 1     |

| Address Mode                        | U       | 1  | 0     | 0 | 0   | 0    | 0   | 1     |

| Command Pass Through                | N       | 1  | 0     | 1 | 1   | 1    | 0   | 1     |

| Auxiliary Mode                      | U       |    | 0     | 1 | 0   | 0    | 0   | 1     |

| Source/Acceptor Status <sup>+</sup> | Р       | 1  | 0     | 1 | 1   | 13   | 0   | 1     |

| Address 0                           | N       | 1  | 1     | 0 | 1.1 | 1    | 0   | 1     |

| Address                             | Ν       | 1  | 1     | 0 | 0   | 0    | 0   | 1     |

| Interrupt Status 0 <sup>+</sup>     | Р       | 1  | 1     | 0 | 1   | 1    | 0   | 1     |

| Interrupt Mask 0 <sup>+</sup>       | Р       | 1  | 1     | 0 | 0   | 0    | 0   | 1     |

| Address 1                           | N       | 1  | 1     | 1 | 1   | 10   | 0   | 1     |

| End-Of-String                       | N       | 1  | 1     | 1 | 0   | 0    | 0   | 1     |

| Bus Status <sup>+</sup>             | Р       | -1 | 1     | 1 | 1   | V.C  | 0   | 1     |

| Bus Control <sup>+</sup>            | Р       | 1  | 1     | 1 | 0   | 0    | 0   | 1     |

he " symbol denotes features (such as registers and auxiliary commands) that are not available in the TMS9914A.

Notes for the PAGE-IN column:

U = The page-in auxiliary command does not affect

the register.

- N = The register offset is always valid except for immediately after a page-in auxiliary command.

- P = The register is valid only immediately after a page-in auxiliary command.

## **Preliminary DC Characteristics**

$T_A 0$  to 70 °C;  $V_{CC} = 5 V \pm 5\%$

| WWW.                  | N.C.            | Lim   | its             |      | Test                    |

|-----------------------|-----------------|-------|-----------------|------|-------------------------|

| Parameter             | Symbol          | Min   | Max             | Unit | Condition               |

| Voltage input low     | VIL             | -0.5  | +0.8            | V    | ALC: NO                 |

| Voltage input high    | VIII            | +2.0  | V <sub>CC</sub> | V    | - WWW.                  |

| Voltage output low    | V <sub>OL</sub> | 0     | 0.4             | V    | -                       |

| Voltage output high   | V <sub>OH</sub> | +2.4  | VCC             | V    |                         |

| Input/output          | - N             | -10   | +10             | μA   | without                 |

| Leakage current       |                 | N.C.  | The             |      | internal pull-up        |

| Input/output          | TV-             | -200  | +200            | μA   | with internal           |

| Leakage current       |                 | 01.   | Mo              |      | pull-up                 |

| Supply current        | <u> </u>        | 00-X- | 45              | mA   | - 11                    |

| Output current low    |                 |       | CON             |      |                         |

| All pins except ACCRQ | I <sub>OL</sub> | 2     |                 | mA   | 0.4 V @ I <sub>OL</sub> |

| ACCRQ                 |                 | 4     | 1 G-9 '         | mA   | 0.4 V @ I <sub>OL</sub> |

| Input current low     | I <sub>IL</sub> | N.100 | - 0.5           | mA   | -                       |

| Supply voltage        | V <sub>DD</sub> | 4.75  | 5.25            | V    | 72                      |

| 11.5 0                                                           | 00                     |      | V    |      |           |

|------------------------------------------------------------------|------------------------|------|------|------|-----------|

| <b>Capacitance</b><br>F <sub>A</sub> 0 to 70 °C; V <sub>CC</sub> | <sub>2</sub> = 5 V ±5% |      |      |      |           |

|                                                                  |                        | Lir  | nits |      | Test      |

| Parameter                                                        | Symbol 🔨               | Min  | Max  | Unit | Condition |

| Input<br>capacitance                                             | C <sub>IN</sub>        | NAN  | 10   | pF   | WT.M      |

| Output<br>capacitance                                            | C <sub>OUT</sub>       | 1-11 | 10   | pF   | OM.TW     |

| I/O capacitance                                                  | C <sub>I/O</sub>       | 21   | 10   | pF   | -ONE TY   |

## Absolute Maximum Ratings

| Property                                   | Range                                                     |

|--------------------------------------------|-----------------------------------------------------------|

| Supply voltage, V <sub>DD</sub>            | -0.5 to +7.0 V                                            |

| Input voltage, V <sub>I</sub>              | -0.5 to V <sub>DD</sub> +0.5 V                            |

| Operating temperature, T <sub>OPB</sub>    | 0 to +70° C                                               |

| Storage temperature, T <sub>STG</sub>      | -40 to +125° C                                            |

| Comment: Exposing the device to stresses a | above those listed could cause permanent damage. The      |

|                                            | onditions outside the limits described in the operational |

## **AC Characteristics**

$T_A 0$  to 70 °C;  $V_{CC} = 5 V \pm 5\%$

| A 00                                                                        |                 |     |      |      |           |  |  |  |

|-----------------------------------------------------------------------------|-----------------|-----|------|------|-----------|--|--|--|

| N.COM                                                                       |                 | Lin | nits |      | Test      |  |  |  |

| Parameter                                                                   | Symbol          | Min | Max  | Unit | Condition |  |  |  |

| Address hold from CE, WE, and DBIN                                          | t <sub>AH</sub> | 0   | N 7. | ns   | 0.7       |  |  |  |

| Address setup to $\overline{\text{CE}}$ , $\overline{\text{WE}}$ , and DBIN | t <sub>AS</sub> | 0   | WTX- | ns   | C to      |  |  |  |

| Data float from CE or DBIN                                                  | t <sub>DF</sub> | -   | 20   | ns   | 002       |  |  |  |

| Data delay from DBIN↓                                                       | t <sub>DR</sub> | -   | 75   | ns   | ACCGR=0   |  |  |  |

| ACCRQ unassertion                                                           | t <sub>DU</sub> | -   | 20   | ns   |           |  |  |  |

| Data delay from $\overline{CE}\downarrow$                                   | t <sub>BD</sub> | -   | 80   | ns   | ACCGR=1   |  |  |  |

| CE recovery width                                                           | t <sub>RR</sub> | 80  |      | ns   |           |  |  |  |

| CE pulse width                                                              | t <sub>BW</sub> | 80  | -    | ns   | N.100     |  |  |  |

| Data hold from WET                                                          | t <sub>WH</sub> | 0   | -    | ns   | -710      |  |  |  |

| Data setup to WE↑                                                           | tws             | 60  | -    | ns   | Mr.       |  |  |  |

### Notes:

•  $t_{AH}$  is the hold time from  $\overline{WE}\uparrow$  or  $\overline{CE}\uparrow$  whichever is earlier.

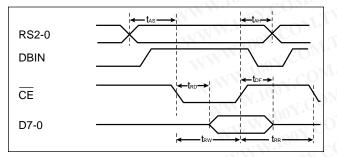

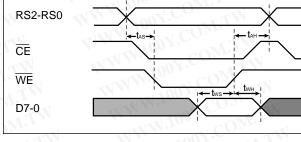

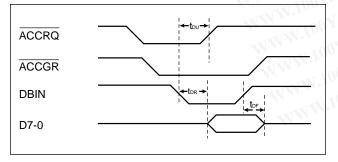

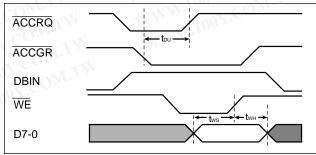

# **Timing Waveforms**

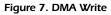

Figure 5. DMA Read

Figure 6. CPU Write

<sup>•</sup>  $t_{\text{AS}}$  is the setup time to  $\overline{\text{CE}}{\downarrow}~~\text{or}~\overline{\text{WE}}{\downarrow}~~\text{whichever}$  is later.

# WWW.100Y.COM.TW 100Y.COM.TW **IEEE 488.2 Controller Chip**

## **Source Handshake**

| WW 100X.                                                      |                 | Limit | s (ns) | Test               |

|---------------------------------------------------------------|-----------------|-------|--------|--------------------|

| Parameter                                                     | Symbol          | Min   | Max    | Condition          |

| NDAC↑ to DAV↑                                                 | t <sub>ND</sub> | NF.   | 40     | -                  |

| $\overline{NDAC}$ to $\overline{INT}$ or $\overline{ACCRQ}$   | t <sub>NI</sub> | × .   | 40     | INT(DOIE Bit=1)    |

| WWW                                                           | N.C.            | 92.   | Wn     | ACCGR (DMAO Bit=1) |

| WE ↑ to DAV↓                                                  | t <sub>WD</sub> | 2000  | 2180   | 2 µs T1, 5MHz      |

| WE ↑ to DAV↓                                                  | t <sub>WD</sub> | 1200  | 1380   | 1.1 µs T1, 5MHz    |

| WE ↑ to DAV↓                                                  | t <sub>WD</sub> | 600   | 780    | 500 ns T1, 5MHz    |

| $\overline{WE} \uparrow \text{to } \overline{DAV} \downarrow$ | t <sub>WD</sub> | 400   | 580    | 350 ns T1, 5MHz    |

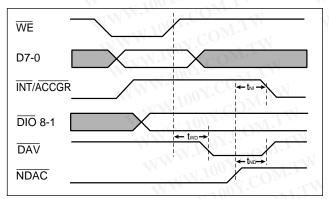

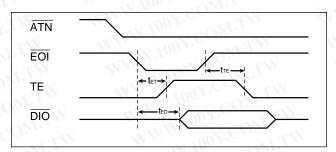

### Figure 8. Source Handshake Timing

### **Acceptor Handshake**

|                                                                                                               |                 | Limits (ns) |       | Test                                   |

|---------------------------------------------------------------------------------------------------------------|-----------------|-------------|-------|----------------------------------------|

| Parameter                                                                                                     | Symbol          | Min         | Max   | Condition                              |

| DAV↓ to NDAC↑                                                                                                 | t <sub>DD</sub> |             | 35+3T | 1.100 1.                               |

| DAV↑ to NDAC↓                                                                                                 | t <sub>DF</sub> |             | 25    | 1001.001                               |

| $\overline{\text{DAV}}\downarrow$ to $\overline{\text{INT}}\downarrow$ or $\overline{\text{ACCRQ}}\downarrow$ | t <sub>DI</sub> |             | 50+2T | INT(DIIE Bit=1),<br>ACCGR (DMAI Bit=1) |

| $\overline{DAV}\downarrow$ to $\overline{NRFD}\downarrow$                                                     | t <sub>DR</sub> |             | 20    | 1007.0                                 |

| DBIN↑ to NRFD↑                                                                                                | t <sub>NR</sub> |             | 35    | Read of DIR, not in Holdoff state      |

Note: T = one clock period

Figure 9. Acceptor Handshake Timing

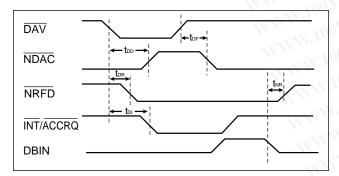

| Parameter                                                               | Symbol          | Limits (ns) |     | Test                       |

|-------------------------------------------------------------------------|-----------------|-------------|-----|----------------------------|

|                                                                         |                 | Min         | Max | Condition                  |

| ATN ↑ to NRFD↓                                                          | t <sub>AF</sub> | N           | 35  | Acceptor handshake holdoff |

| $\overline{\text{ATN}}\downarrow$ to $\overline{\text{NDAC}}\downarrow$ | t <sub>AN</sub> | <           | 35  | $AIDS \rightarrow ANRS$    |

| $\overline{\text{ATN}}\downarrow$ to $\overline{\text{TE}}\downarrow$   | t <sub>AT</sub> |             | 30  | $TACS \to TADS$            |

## **Parallel Poll**

| WW                                                             | N.2 01          | Limit | s (ns) | Test                    |

|----------------------------------------------------------------|-----------------|-------|--------|-------------------------|

| Parameter                                                      | Symbol          | Min   | Max    | Condition               |

| $\overline{EOI}\downarrow$ to $\overline{DIO}\downarrow$ valid | t <sub>ED</sub> | J     | 90     | $PPSS \rightarrow PPAS$ |

| EOI↓ to TE↑                                                    | t <sub>ET</sub> |       | 30     | $PPSS \rightarrow PPAS$ |

| $\overline{EOI}$ to $\overline{TE}\downarrow$                  | t <sub>TE</sub> | -1    | 30     | $PPAS \to PPSS$         |

W.100Y.COM. Figure 11. Parallel Poll Response Timing WWW.100Y.COM.TW

# 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

勝特力材料 886-3-5753170

勝特力材料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

# **IEEE 488.2 Controller Chip**

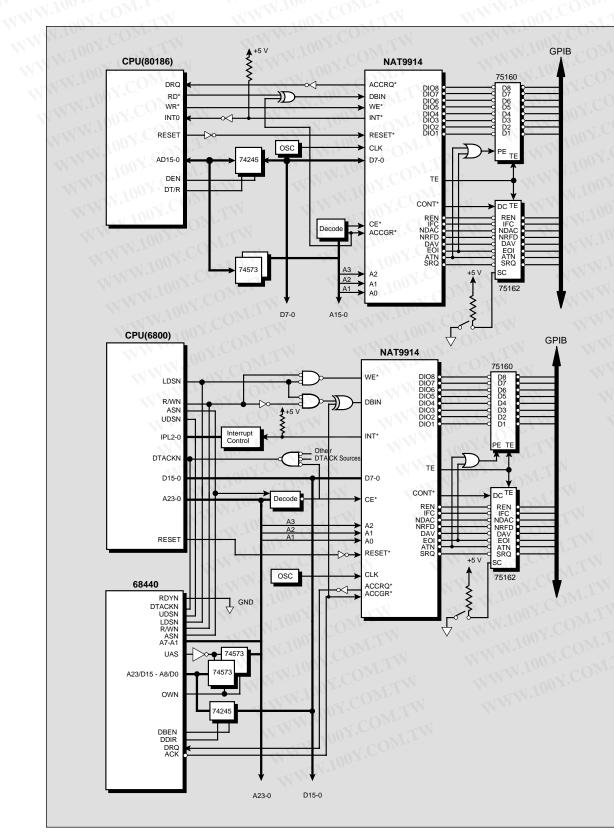

Figure 12. Typical CPU Systems with NAT9914

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

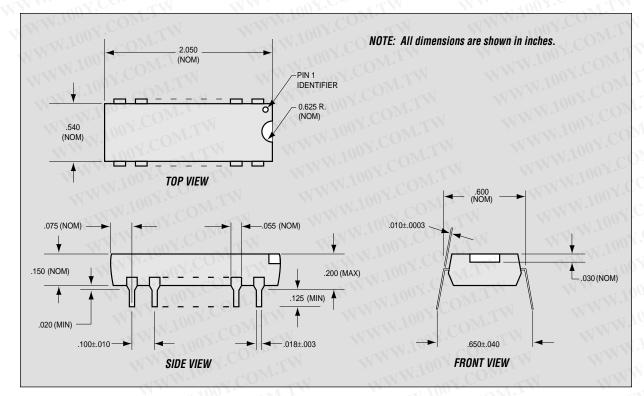

Figure 13. Mechanical Data 40-Pin Plastic DIP

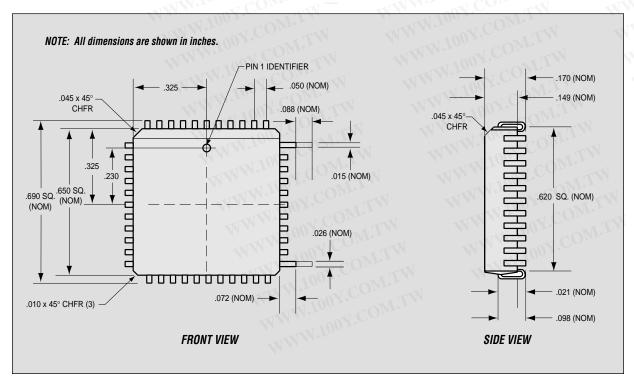

Figure 14. Mechanical Data 44-Pin PLCC

C

В

d

Ρ

e

D

勝 特 力 材 料 886-3-5753170 胜特力电子(上海) 86-21-54151736 胜特力电子(深圳) 86-755-83298787 Http://www.100y.com.tw

## **Ordering Information**

NAT9914BPD NAT9914BPL

### Part Number Legend

a b NAT 9914

- a. Family name NAT = 8-bit GPIB Talker/Listener/Controller interface

- Device number 9914 = TI TMS9914A pin-compatible part

- c. Revision

- d. Package material -P = plastic

- e. Package type D = Dual Inline Package (DIP) L = Plastic Leaded Chip Carrier (PLCC)

NAT9914 Programmer Reference Manual.....visit ni.com

## **Technical Support**

National Instruments strives to provide you with quality technical assistance worldwide. We currently offer electronic technical support along with our technical support centers staffed by Applications Engineers.

Access information from our Web site at **ni.com** Our FTP site is dedicated to 24-hour support, with a collection of files and documents to answer your questions. Log on to our Internet host at ftp.ni.com You can fax questions to our Applications Engineers anytime at (800) 328-2203 or (512) 683-5678. Or, you can call from 8:00 a.m. to 6:00 p.m. (central time) at (512) 795-8248. Internationally, contact your local office. National Instruments sponsors a wide variety of group activities, such as user group meetings at trade shows and at large industrial sites. Our users also receive our quarterly *Instrumentation Newsletter*<sup>®</sup> and *AutomationView*<sup>®</sup> newsletter to get the latest information on new products, product updates, application tips, and current events. In addition, sign up for *NI News*, our electronic news service at **ni.com/news**

## Warranty

All National Instruments data acquisition, computer-based instrument, VXIbus, and MXI°bus products are covered by a oneyear warranty. GPIB hardware products are covered by a two-year warranty from the date of shipment. The warranty covers board failures, components, cables, connectors, and switches, but does not cover faults caused by misuse. The owner may return a failed assembly to National Instruments for repair during the warranty period. Extended warranties are available at an additional charge.

Information furnished by National Instruments is believed to be accurate and reliable. National Instruments reserves the right to change product specifications without notice.

## Seminars/Training

Free and fee-paid seminars are presented several times a year in cities around the world. Comprehensive, fee-paid training courses are available at National Instruments offices or at customer sites. Call for training schedules.

## ni.com/gpib (512) 794-0100

U.S. Corporate Headquarters - Fax: (512) 683-9300 - info@ni.com

Branch Offices: Australia 03 9879 5166 • Austria 0662 45 79 90 0 • Belgium 02 757 00 20 • Brazil 55 000 811 947 8791 • Canada 905 785 0085 China 0755 3904939 • Denmark 45 76 26 00 • Finland 09 725 725 11 • France 01 48 14 24 24 • Germany 089 741 31 30 • Greece 30 1 42 96 427 Hong Kong 2645 3186 • India 91805275406 • Israel 03 6120092 • Italy 02 413091 • Japan 03 5472 2970 • Korea 02 596 7456 • Mexico 001 800 010 0793 Netherlands 0348 433466 • New Zealand 09 914 0488 • Norway 32 27 73 00 • Poland 0 22 528 94 06 • Portugal 351 1 726 9011 • Singapore 2265886 Spain 91 640 0085 • Sweden 08 587 895 00 • Switzerland 056 200 51 51 • Taiwan 02 2528 7227 • U.K. 01635 523545 • Venezuela 800 1 4466