# **TMU3132MS**

## **USB Full Speed Controller**

## **Data Sheet**

tenx reserves the right to change or discontinue the manual and online documentation to this product herein to improve reliability, function or design without further notice. tenx does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. tenx products are not designed, intended, or authorized for use in life support appliances, devices, or systems. If Buyer purchases or uses tenx products for any such unintended or unauthorized application, Buyer shall indemnify and hold tenx and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that tenx was negligent regarding the design or manufacture of the part.

Preliminary

tenx technology inc. Rev 1.2, 2012/02/06

## AMENDMENT HISTORY

| Version | Date      | Description                                                                                                              |  |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------|--|

| V1.0    | Nov, 2011 | New release                                                                                                              |  |

| V1.1    | Jan, 2012 | Add Ordering Information table                                                                                           |  |

| V1.2    | Feb, 2012 | <ol> <li>Add PDIP/SOP 20/18Pin</li> <li>Revise Application figure.</li> <li>Modify Ordering Information table</li> </ol> |  |

## CONTENTS

| AMENDMENT HISTORY                            | 2  |

|----------------------------------------------|----|

| GENERAL DESCRIPTION                          | 4  |

| FEATURES                                     | 4  |

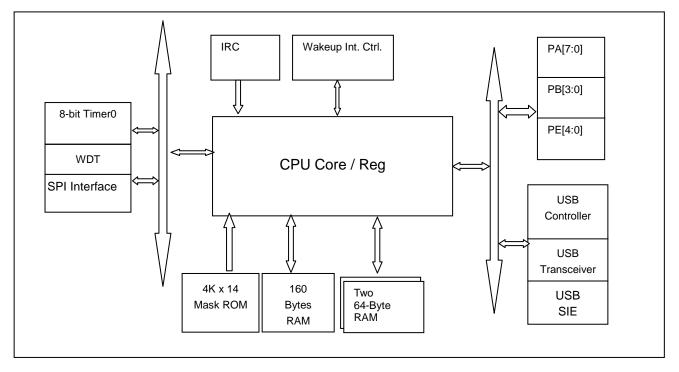

| Functional Block Diagram                     | 5  |

| PIN DESCRIPTION                              | 5  |

| PACKAGE                                      |    |

| Functional Description                       | 7  |

| 1. CPU Core                                  |    |

| 1.1 Clock Scheme and Instruction Cycle       | 7  |

| 1.2 CPU Clock Control Register               | 7  |

| 1.3 Programming Counter (PC) and Stack       | 7  |

| 1.4 ALU and Working (W) Register             |    |

| 1.5 Addressing Mode                          | 8  |

| 1.6 Instruction Set                          | 9  |

| 2. Control Registers                         | 22 |

| F-Plane                                      | 22 |

| R-Plane                                      | 24 |

| 3. USB Engine                                | 26 |

| 3.1 USB Device Address                       | 26 |

| 3.2 Endpoint 0 Receive (SET0/OUT0)           | 26 |

| 3.3 Endpoint 0 Transmit (TX0)                | 27 |

| 3.4 Endpoint 1/2 Transmit (TX1/2)            | 27 |

| 3.5 Endpoint 3 Transmit (TX3)                | 27 |

| 3.6 USB Endpoint 4 Receive (RC4)             | 27 |

| 3.7 USB Control and Status                   | 28 |

| 3.8 Suspend and Resume                       | 28 |

| 3.9 Interrupt Vector                         |    |

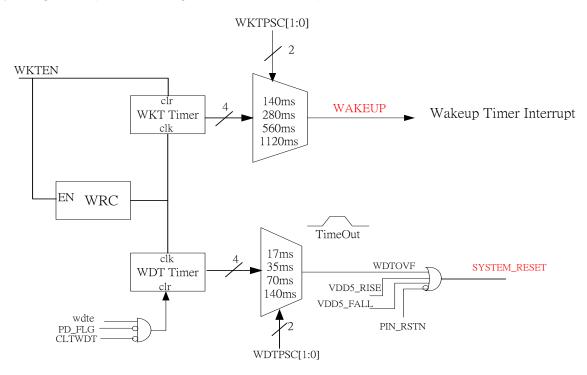

| 4. Wakeup Timer and Watch Dog Timer          | 29 |

| 5. Timer                                     | -  |

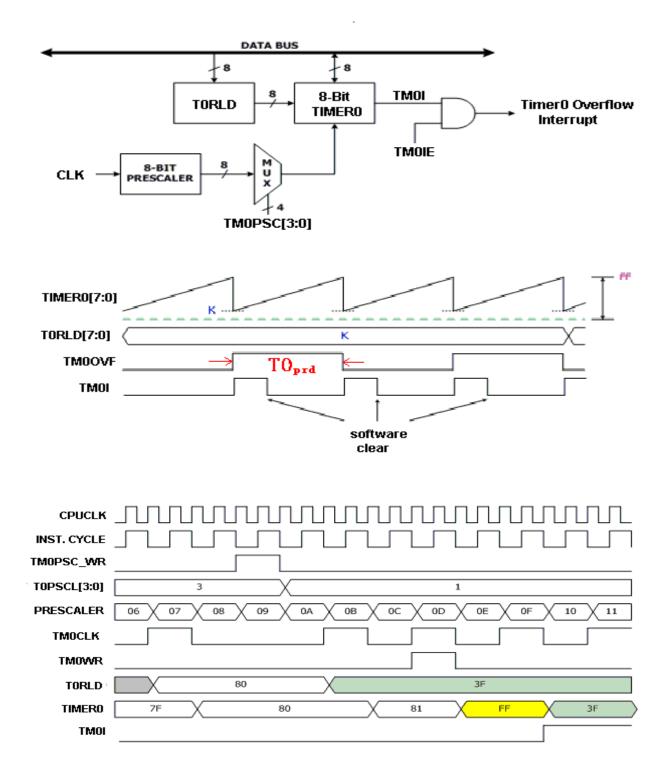

| 5.1 Timer0: 8-bit Timer with Pre-scale (PSC) |    |

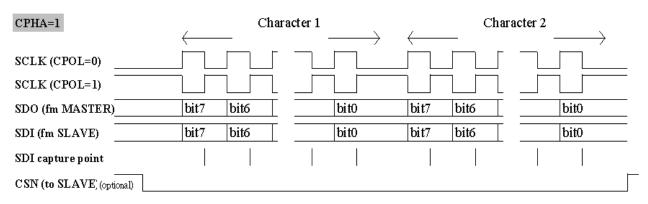

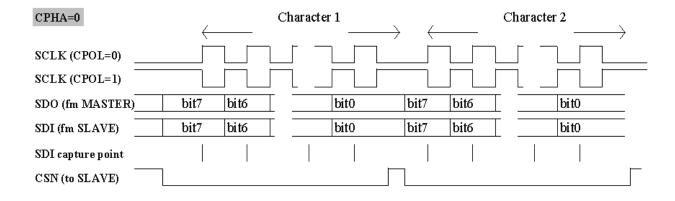

| 6. SPI (Serial Peripheral Interface)         |    |

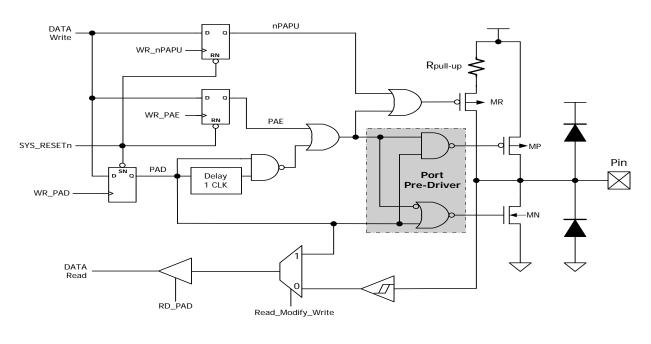

| 7. I/O Port                                  |    |

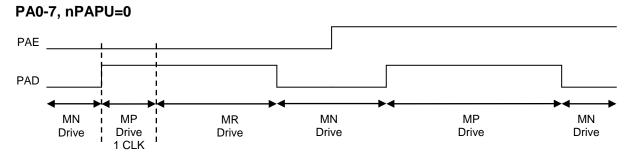

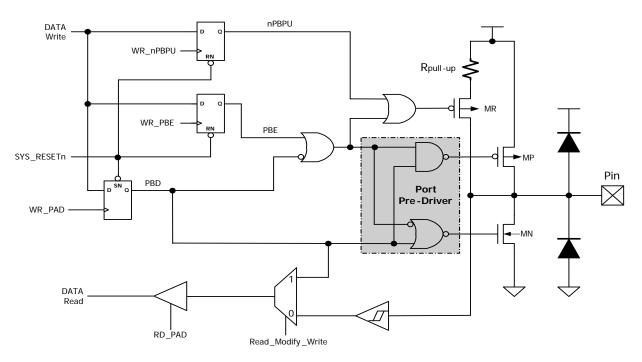

| 7.1 PA0-7                                    |    |

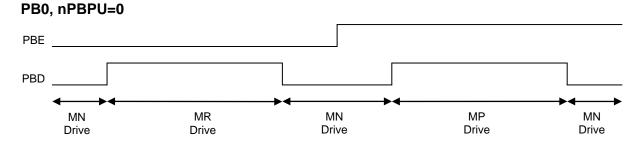

| 7.2 PB0                                      |    |

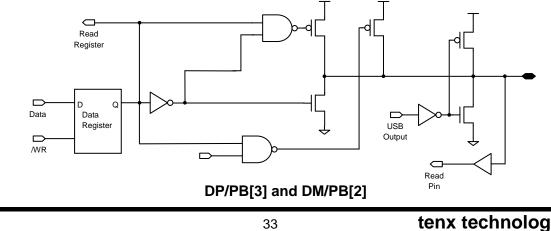

| 7.3 PB3 (DP) and PB2 (DM)                    |    |

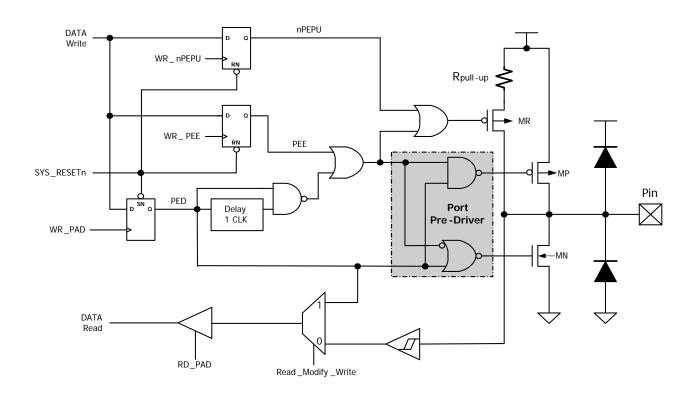

| 7.4 PE0-4                                    |    |

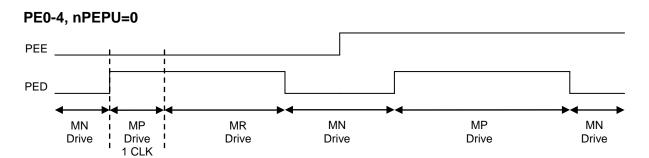

| 8. Application                               |    |

| 9. Electrical Characteristics                |    |

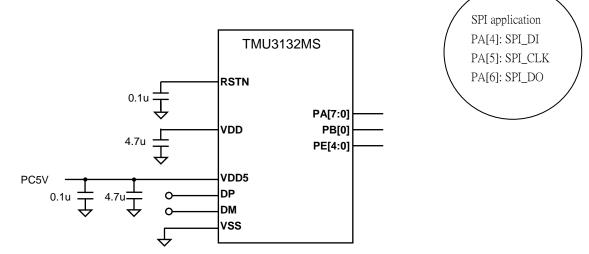

| 10. Package Information                      |    |

| Ordering Information                         | 38 |

#### **GENERAL DESCRIPTION**

The TMU3132MS is a 2T RISC tailored to the USB 2.0 full speed general purpose IC. It contains 4K \* 14 Mask ROM. The Internal RC Oscillator is 48 MHz +/- 0.25% for USB mode and 12 MHz clock output for the RF 2.4G module. The USB DMA channel allows data transfer between USB RAM with SPI interface which supports mode 0/1/2/3 master up to 6 Mbps clock rate. The TMU3132MS also supports suspend mode, wake-up and watchdog timer. The data memory is internal 160 bytes of RAM in F-plane and two 64 bytes in R-plane. The TMU3132MS USB MCU is suited for USB mouse and wireless 2.4G dongle device.

## FEATURES

- Operation Frequency

- Internal 48 MHz RC oscillator +/- 0.25% accuracy for USB with no extra component.

- On-Chip Memory

- 4k x 14 internal Mask ROM.

- Internal 160 Bytes RAM at F-plane and two 64 Bytes RAM at R-plane.

- Built-in five 8-byte USB Application FIFOs at R-plane.

- 8-bit RISC MCU

- 8-level stacks for subroutine and interrupt.

- 37 instructions.

- Two clocks per instruction except branch.

- USB interface

- Compliance with the Universal Serial Bus specification v2.0 Full Speed.

- Built-in 1.5K pull-high resistor can be set or disabled.

- Built-in USB Transceiver, 3.3V regulator.

- Support USB Suspend/Resume and Remote Wakeup function.

- Endpoint 0: Control SETUP/IN/OUT transfer (each 8 bytes).

- Endpoint 1: INTERRUPT IN transfer (8 bytes).

- Endpoint 2: INTERRUPT IN transfer (8 bytes).

- Endpoint 3: BULK-IN transfer with Ping-Pong feature (2\*64 bytes).

- Endpoint 4: BULK-OUT transfer with Ping-Pong feature (2\*64 bytes).

- Timer

- Timer0 is 8-bit with 8-bit prescaler, Counter/Reload/Interrupt function.

- Watchdog Timer clocked by built-in RC oscillator.

- Wakeup Timer clocked by built-in RC oscillator.

- Reset Controller

- Power On Reset is 2.0V.

- Watch-Dog Timer reset period can be configured at 16 ms/32 ms/64 ms/128 ms.

## **Advance Information**

- SPI interface

- Support Mode0, 1, 2, 3.

- Master only.

- Clock rate up to 6 Mbps.

- Read/Write DMA mode.

- I/O Ports

- Max. 16 GPIOs to flexible application

- Each GPIO pin supports Schmitt-trigger input, internal pull-ups and open drains output or CMOS push-pull output

- PDIP/SOP 20/18 or Die Form

- Application: USB full speed general purpose

## PIN DESCRIPTION

PIN ASSIGNMENT

| Name       | I/O | Description                                                                                      |

|------------|-----|--------------------------------------------------------------------------------------------------|

| VDD5       | Р   | PC5V Power input                                                                                 |

| VSS        | Р   | Ground                                                                                           |

| VDD        | 0   | 3.3V regulator output                                                                            |

| VPP/RSTN   | Ι   | Programming High power/Chip reset pin                                                            |

| PA[7]      | I/O | General purpose I/O (Pseudo open-drain) ;                                                        |

| PA[6]/SDO  | I/O | General purpose I/O (Pseudo open-drain) ; SPI Dout                                               |

| PA[5]/SCLK | I/O | General purpose I/O (Pseudo open-drain) ; SPI Clk                                                |

| PA[4]/SDI  | I/O | General purpose I/O (Pseudo open-drain) ; SPI Din                                                |

| PA[3]      | I/O | General purpose I/O (Pseudo open-drain)                                                          |

| PA[2]      | I/O | General purpose I/O (Pseudo open-drain)                                                          |

| PA[1]/     | I/O | General purpose I/O (Pseudo open-drain);                                                         |

| PA[0]      | I/O | General purpose I/O (Pseudo open-drain);                                                         |

| DP/PB[3]   | I/O | USB positive signal/General purpose I/O                                                          |

| DM/PB[2]   | I/O | USB negative signal/General purpose I/O                                                          |

| PB[0]      | I/O | General purpose I/O (open-drain)                                                                 |

| PE[4:0]    | I/O | General purpose I/O (Pseudo open-drain) ;<br>PE[3] can configured as clock output (6 MHz/12 MHz) |

.I/O voltage is fixed 3.3V, unless otherwise specified.

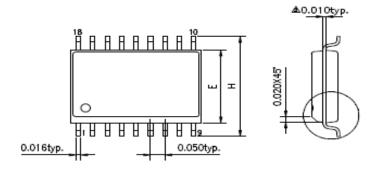

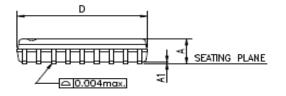

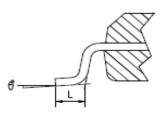

## PACKAGE

| PA0 [ 1<br>PA1 ] 2<br>PA2 ] 3<br>PA3 ] 4<br>PE1 ] 5<br>PE2 ] 6<br>VSS ] 7<br>VDD ] 8<br>VPP ] 9<br>PE3 ] 10 | TNU3132<br>20Pin | 20 PA4<br>19 PA5<br>18 PA6<br>17 PA7<br>16 PE0<br>15 PE4<br>14 DP/PB3<br>13 DN/PB2<br>12 VDD5<br>11 N.C. | PA0 [ 1<br>PA1 [ 2<br>PA2 [ 3<br>PA3 [ 4<br>PE1 [ 5<br>PE2 [ 6<br>VSS [ 7<br>VDD [ 8<br>VPP [ 9<br>PE3 [ 10 | TNU3132<br>20Pin | 20   PA4<br>19   PA5<br>18   PA6<br>17   PA7<br>16   PB0<br>15   PE0<br>14   PE4<br>13   DP/PB3<br>12   DM/PB2<br>11   VDD5 |

|-------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------|

| PA0 []<br>PA1 [] 2<br>PA2 [] 3<br>PA3 [] 4<br>PE2 [] 5<br>VSS [] 6<br>VDD [] 7<br>VPP [] 8<br>PE3 [] 9      | TWU3132<br>18Pin | 18 PA4<br>17 PA5<br>16 PA6<br>15 PA7<br>14 PE4<br>13 DP/PB3<br>12 DM/PB2<br>11 VDD5<br>10 N.C.           |                                                                                                             |                  |                                                                                                                             |

### **Functional Description**

#### 1. CPU Core

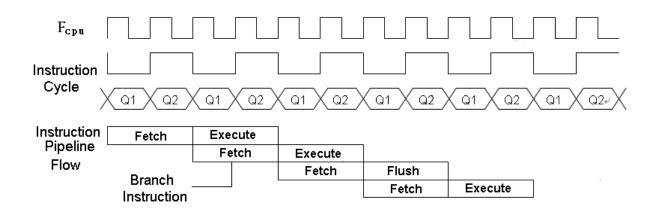

#### **<u>1.1</u>** Clock Scheme and Instruction Cycle

TMU3132MS has only one chip clock sources as following:  $F_{rc}$ : Internal RC oscillator 24 MHz clock

$F_{rc}$  can be synchronized by USB signals and popup to 48 MHz clock ( $F_{48m}$ ) for USB module.  $F_{rc}$  can be divided to 12 MHz clock as CPU clock. The CPU clock is internally divided by two to generate Q1 state and Q2 state for each instruction cycle. The Programming Counter (PC) is updated at Q1 and the instruction is fetched from program ROM and latched into the instruction register in Q2. It is then decoded and executed during the following Q1-Q2 cycle. Branch instructions take two cycles since the fetch instruction is 'flushed' from the pipeline, while the new instruction is being fetched and then executed.

#### 1.2 CPU Clock Control Register

CPU clock speed selection: The CPU clock source is Internal RC and it will be divided to 12 MHz, 6 MHz, 3 MHz or 1.5 MHz by firmware setting.

R07 [1:0] is used to select the different speed

R07 [1:0] =0 select 12 MHz

R07 [1:0] =1 select 6 MHz

R07 [1:0] =2 select 3 MHz

R07 [1:0] =3 select 1.5 MHz

#### **<u>1.3</u>** Programming Counter (PC) and Stack

The Programming Counter is 12-bit wide capable of addressing a 4K x 14 program ROM. As a program instruction is executed, the PC will contain the address of the next program instruction to be executed. The PC value is normally increased by one except the followings. The Reset Vector (000h) and the Interrupt Vectors (from 001h to 00dh) are provided for PC initialization and Interrupt. For CALL/GOTO instructions, PC loads the lower 11 bits address from instruction word. For RET/RETI/RETLW instructions, PC retrieves its content from the top level

STACK. For the other instructions updating PC [7:0], the PC [11:8] keeps unchanged. The STACK is 12-bit wide and 8-level in depth. The CALL instruction and Hardware interrupt will push STACK level in order. While the RET/RETI/RETLW instruction pops the STACK level in order.

#### 1.4 ALU and Working (W) Register

The ALU is 8-bit wide and capable of addition, subtraction, shift and logical operations. In twooperand instructions, typically one operand is the W register, which is an 8-bit non-addressable register used for ALU operations. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either W register or a file register. Depending on the instruction executed, the ALU may affect the values of Carry (C), Digit Carry (DC), and Zero (Z) Flags in the STATUS register. The C and DC flags operate as a /Borrow and /Digit Borrow, respectively, in subtraction.

Note: /Borrow represents inverted of Borrow register. /Digit Borrow represents inverted of Digit Borrow register.

#### 1.5 Addressing Mode

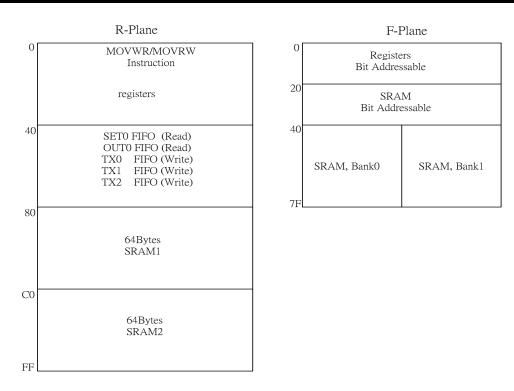

There are two Data Memory Planes in CPU, R-Plane and F-Plane. The lower locations of F-Plane are reserved for the SFR. Above the SFR is General Purpose Data Memory, implemented as static RAM. F-Plane can be addressed directly or indirectly. Indirect Addressing is made by INDF register. The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a pointer). The first half of F-Plane is bit-addressable, while the second half of F-Plane is not bitaddressable. R-plane can be indirect accessed via RSR register.

- 1. 4K x 14 Mask ROM.

- 2.160-byte SRAM (F-plane) is addressed from 0x20 to 0x7F. The lower 32-byte (0x20 ~ 0x3f) is bit addressable. The higher address (0x40 ~ 0x7F) is separated to two banks which can be selected by setting register F03[5]. F03[5]=0 is used to select Bank0, F03[5]=1 is used to select Bank1.

- 3. Two 64-bytes RAM (R-plane).

- 4. Five 8-byte USB FIFOs are allocated in R-plane.

Example: Initial value: [F30h]=12h MOVLW 30h ;W=30h MOVWF FSR MOVFW INDF ;W=12h CLRW MOVWF INDF ;[F30h]=00h INCF FSR,F ;FSR=31h

#### 1.6 Instruction Set

Each instruction is a 14-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands, which further specify the operation of the instruction. The instructions can be categorized as byte-oriented, bit-oriented and literal operations list in the following table.

For byte-oriented instructions, "f" or "r" represents the address designator and "d" represents the destination designator. The address designator is used to specify which address in Program memory is to be used by the instruction. The destination designator specifies where the result of the operation is to be placed. If "d" is "0", the result is placed in the W register. If "d" is "1", the result is placed in the address specified in the instruction.

For bit-oriented instructions, "b" represents a bit field designator, which selects the number of the bit affected by the operation, while "f" represents the address designator. For literal operations, "k" represents the literal or constant value.

| Field / Legend | Description                                                        |

|----------------|--------------------------------------------------------------------|

| f              | F-Plane Register File Address                                      |

| r              | R-Plane Register File Address                                      |

| b              | Bit Address                                                        |

| k              | Literal. Constant data or label                                    |

| d              | Destination selection field, 0: Working register, 1: Register file |

| W              | Working Register                                                   |

| Z              | Zero Flag                                                          |

| С              | Carry Flag                                                         |

| DC             | Decimal Carry Flag                                                 |

| PC             | Program Counter                                                    |

| TOS            | Top Of Stack                                                       |

## **Preliminary**

tenx technology inc.

| Field / Legend | Description                           |

|----------------|---------------------------------------|

| GIE            | Global Interrupt Enable Flag (i-Flag) |

| []             | Option Field                          |

| ()             | Contents                              |

|                | Bit Field                             |

| В              | Before                                |

| А              | After                                 |

| ←              | Assign direction                      |

| Mnemo  | nic                                    | Op Code           | Cycle        | Flag Affect | Description                      |

|--------|----------------------------------------|-------------------|--------------|-------------|----------------------------------|

|        |                                        | Byte-Oriented I   | ile Register | Instruction | 1                                |

| ADDWF  | f,d                                    | 00 0111 dfff ffff | 1            | C,DC,Z      | Add W to f                       |

| ANDWF  | f,d                                    | 00 0101 dfff ffff | 1            | Z           | AND W to f                       |

| CLRF   | f                                      | 00 0001 1fff ffff | 1            | Z           | Clear f                          |

| CLRW   |                                        | 00 0001 0100 0000 | 1            | Z           | Clear W                          |

| COMF   | f,d                                    | 00 1001 dfff ffff | 1            | Z           | Invert F bit by bit              |

| DECF   | f,d                                    | 00 0011 dfff ffff | 1            | Z           | Decrement of f                   |

| DECFSZ | f,d                                    | 00 1011 dfff ffff | 1 or 2       | -           | Decrease f, skip if zero         |

| Mnemo  | nic                                    | Op Code           | Cycle        | Flag Affect | Description                      |

|        |                                        | Byte-Oriented I   | ile Register | Instruction |                                  |

| INCF   | f,d                                    | 00 1010 dfff ffff | 1            | Z           | Increment of f                   |

| INCFSZ | f,d                                    | 00 1111 dfff ffff | 1 or 2       | -           | Increase f, skip if zero         |

| IORWF  | f,d                                    | 00 0100 dfff ffff | 1            | Z           | OR W to f                        |

| MOVFW  | f                                      | 00 1000 Offf ffff | 1            | -           | Move f to W                      |

| MOVWF  | f                                      | 00 0000 1fff ffff | 1            | -           | Move W to f                      |

| MOVRW  | r                                      | 01 1111 rrrr rrrr | 1            | -           | Move r to W                      |

| MOVWR  | r                                      | 01 1110 rrrr rrrr | 1            | -           | Move W to r                      |

| RLF    | f,d                                    | 00 1101 dfff ffff | 1            | С           | F rotate to left                 |

| RRF    | f,d                                    | 00 1100 dfff ffff | 1            | С           | F rotate to right                |

| SUBWF  | f,d                                    | 00 0010 dfff ffff | 1            | C,DC,Z      | Substrate W from f               |

| SWAPF  | f,d                                    | 00 1110 dfff ffff | 1            | -           | Swap high and low<br>nibble of f |

| TESTZ  | f,d                                    | 00 1000 dfff ffff | 1            | Z           | Test f if zero                   |

| XORWF  | f,d                                    | 00 0110 dfff ffff | 1            | Z           | XOR W to f                       |

|        | Bit-Oriented File Register Instruction |                   |              |             |                                  |

| BCF    | f,b                                    | 01 000b bbff ffff | 1            | -           | Bit clear f                      |

| BSF    | f,b                                    | 01 001b bbff ffff | 1            | -           | Bit set f                        |

| BTFSC  | f,b                                    | 01 010b bbff ffff | 1 or 2       | -           | Bit test f, skip if clear        |

| BTFSS  | f,b                                    | 01 011b bbff ffff | 1 or 2       | -           | Bit test f, skip if set          |

## tenx technology inc.

| Mnemo  | nic                             | Op Code           | Cycle | Flag Affect | Description              |  |

|--------|---------------------------------|-------------------|-------|-------------|--------------------------|--|

|        | Literal and Control Instruction |                   |       |             |                          |  |

| ADDLW  | k                               | 01 1100 kkkk kkkk | 1     | C,DC,Z      | Add literal to W         |  |

| ANDLW  | k                               | 01 1011 kkkk kkkk | 1     | Z           | AND literal to W         |  |

| XORLW  | K                               | 01 1101 kkkk kkkk | 1     | Z           | XOR literal to W         |  |

| CALL   | k                               | 10 kkkk kkkk kkkk | 2     | -           | Subroutine call          |  |

| CLRWDT |                                 | 01 1110 0000 0011 | 1     | -           | Clear watchdog timer     |  |

| GOTO   | k                               | 11 kkkk kkkk kkkk | 2     | -           | Unconditional branch     |  |

| IORLW  | k                               | 01 1010 kkkk kkkk | 1     | Z           | OR literal to W          |  |

| MOVLW  | k                               | 01 1001 kkkk kkkk | 1     | -           | Move literal to W        |  |

| NOP    |                                 | 00 0000 0000 0000 | 1     | -           | No operation             |  |

| RET    |                                 | 00 0000 0100 0000 | 2     | -           | Return from CALL         |  |

| RETI   |                                 | 00 0000 0110 0000 | 2     | -           | Return from interrupt    |  |

| RETLW  | k                               | 01 1000 kkkk kkkk | 2     | -           | Return with literal to W |  |

| SLEEP  |                                 | 01 1110 0000 0011 | 1     | -           | Power down               |  |

| ADDLW           | Add Literal "k" and                                                                                               | W            |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------|--------------|--|

| Syntax          | ADDLW k                                                                                                           |              |  |

| Operands        | k : 00h ~ FFh                                                                                                     |              |  |

| Operation       | (W) ← (W) + k                                                                                                     |              |  |

| Status Affected | Č, DC, Ž                                                                                                          |              |  |

| OP-Code         | 01 1100 kkkk kkkk                                                                                                 |              |  |

| Description     | The contents of the W register are added to the eight-bit literal 'k' and the result is placed in the W register. |              |  |

| Cycle           | 1                                                                                                                 |              |  |

| Example         | ADDLW 0x15                                                                                                        | B : W = 0x10 |  |

| •               |                                                                                                                   | A : W = 0x25 |  |

| ADDWF           | Add W and "f"                                                                                                                                                      |                               |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|

| Syntax          | ADDWF f [,d]                                                                                                                                                       |                               |  |

| Operands        | f : 00h ~ 7Fh d : 0, 1                                                                                                                                             |                               |  |

| Operation       | (Destination) $\leftarrow$ (W) + (f)                                                                                                                               |                               |  |

| Status Affected | Č, DC, Z                                                                                                                                                           |                               |  |

| OP-Code         | 00 0111 dfff ffff                                                                                                                                                  |                               |  |

| Description     | Add the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |                               |  |

| Cycle           | 1                                                                                                                                                                  | -                             |  |

| Example         | ADDWF FSR, 0                                                                                                                                                       | B : W = 0x17, FSR = 0xC2      |  |

|                 |                                                                                                                                                                    | A : W = $0xD9$ , FSR = $0xC2$ |  |

| ANDLW           | Logical AND Liter                                                     | al "k" with W   |  |

|-----------------|-----------------------------------------------------------------------|-----------------|--|

| Syntax          | ANDLW k                                                               |                 |  |

| Operands        | k : 00h ~ FFh                                                         |                 |  |

| Operation       | (W) ← (W) 'AND' k                                                     |                 |  |

| Status Affected | Ž                                                                     |                 |  |

| OP-Code         | 01 1011 kkkk kkkk                                                     |                 |  |

| Description     | The contents of W register are AND'ed with the eight-bit literal 'k'. |                 |  |

|                 | The result is placed in                                               | the W register. |  |

| Cycle           | 1                                                                     | -               |  |

| Example         | ANDLW 0x5F                                                            | B : W = 0xA3    |  |

| -               |                                                                       | A : W = 0x03    |  |

| ANDWF           | AND W with "f"                                                                                                                                     |                                                      |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|

| Syntax          | ANDWF f [,d]                                                                                                                                       |                                                      |  |

| Operands        | f:00h~7Fh d:0,1                                                                                                                                    |                                                      |  |

| Operation       | (Destination) $\leftarrow$ (W) 'A                                                                                                                  | ND' (f)                                              |  |

| Status Affected | Z                                                                                                                                                  |                                                      |  |

| OP-Code         | 00 0101 dfff ffff                                                                                                                                  |                                                      |  |

| Description     | AND the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |                                                      |  |

| Cycle           | 1                                                                                                                                                  | -                                                    |  |

| Example         | ANDWF FSR, 1                                                                                                                                       | B : W = 0x17, FSR = 0xC2<br>A : W = 0x17, FSR = 0x02 |  |

| BCF             | Clear "b" bit of "f"                |                                            |

|-----------------|-------------------------------------|--------------------------------------------|

| Syntax          | BCF f [,b]                          |                                            |

| Operands        | f:00h~3Fh b:0~7                     |                                            |

| Operation       | (f.b) ← 0                           |                                            |

| Status Affected | -                                   |                                            |

| OP-Code         | 01 000b bbff ffff                   |                                            |

| Description     | Bit 'b' in register 'f' is cleared. |                                            |

| Cycle           |                                     |                                            |

| Example         | BCF FLAG_REG, 7                     | B : FLAG_REG = 0xC7<br>A : FLAG REG = 0x47 |

|                 |                                     | A . 1 EAO_REO = 0.47                       |

|                 |                                     |                                            |

| BSF             | Set "b" bit of "f"                  |                                            |

| Syntax          | BSF f [,b]                          |                                            |

| Operands        | f:00h~3Fh b:0~7                     |                                            |

| Operation       | (f.b) ← 0                           |                                            |

| Status Affected | -                                   |                                            |

| OP-Code         | 01 001b bbff ffff                   |                                            |

| Description     | Bit 'b' in register 'f' is set.     |                                            |

| Cycle           |                                     |                                            |

| Example         | BSF FLAG_REG, 7                     | $B : FLAG_REG = 0x0A$                      |

|                 |                                     | A : FLAG_REG = 0x8A                        |

|                 |                                     |                                            |

| BTFSC           | Test "b" bit of "f", skip           | if clear(0)                                |

| Syntax          | BTFSC f [,b]                        |                                            |

| Operands        | f:00h~3Fh b:0~7                     |                                            |

| Operation       | Skip next instruction if (f.b) = 0  | )                                          |

| Statue Affected |                                     |                                            |

| Skip next instruction if $(f.b) =$ | 0                                                                                                                                                                                           |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                  |                                                                                                                                                                                             |

| 01 010b bbff ffff                  |                                                                                                                                                                                             |

| 5                                  | en the next instruction is executed. If bit 'b'<br>ext instruction is discarded, and a NOP is<br>s a 2nd cycle instruction.                                                                 |

| 1 or 2                             |                                                                                                                                                                                             |

| LABEL1 BTFSC FLAG, 1               | B : PC = LABEL1                                                                                                                                                                             |

| TRUE GOTO SUB1<br>FALSE            | A : if FLAG.1 = 0, PC = FALSE<br>if FLAG.1 = 1, PC = TRUE                                                                                                                                   |

|                                    | -<br>01 010b bbff ffff<br>If bit 'b' in register 'f' is '1', the<br>in register 'f' is '0', then the m<br>executed instead, making this<br>1 or 2<br>LABEL1 BTFSC FLAG, 1<br>TRUE GOTO SUB1 |

| BTFSS           | Test "b" bit of "f", skip if set(1)                                                                                                                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax          | BTFSS f [,b]                                                                                                                                                                                                             |

| Operands        | f:00h~3Fh b:0~7                                                                                                                                                                                                          |

| Operation       | Skip next instruction if $(f.b) = 1$                                                                                                                                                                                     |

| Status Affected | -                                                                                                                                                                                                                        |

| OP-Code         | 01 011b bbff ffff                                                                                                                                                                                                        |

| Description     | If bit 'b' in register 'f' is '0', then the next instruction is executed. If bit 'b' in register 'f' is '1', then the next instruction is discarded, and a NOP is executed instead, making this a 2nd cycle instruction. |

| Cycle           | 1 or 2                                                                                                                                                                                                                   |

| Example         | LABEL1BTFSSFLAG, 1B : PC = LABEL1TRUEGOTO SUB1A : if FLAG.1 = 0, PC = TRUEFALSEif FLAG.1 = 1, PC = FALSE                                                                                                                 |

| CALL            | Call subroutine "k"                                                                                           |                                    |

|-----------------|---------------------------------------------------------------------------------------------------------------|------------------------------------|

| Syntax          | CALL k                                                                                                        |                                    |

| Operands        | k : 00h ~ FFFh                                                                                                |                                    |

| Operation       | Operation: TOS $\leftarrow$ (PC)+ 1, PC.11~0 $\leftarrow$                                                     | k                                  |

| Status Affected | -                                                                                                             |                                    |

| OP-Code         | 10 kkkk kkkk kkkk                                                                                             |                                    |

| Description     | Call Subroutine. First, return address (P<br>The 12-bit immediate address is loaded<br>two-cycle instruction. | <i>,</i> ,                         |

| Cycle           | 2                                                                                                             |                                    |

| Example         |                                                                                                               | = LABEL1<br>= SUB1, TOS = LABEL1+1 |

| CLRF                 | Clear "f"                                                      |                                                   |

|----------------------|----------------------------------------------------------------|---------------------------------------------------|

| Syntax               | CLRF f                                                         |                                                   |

| Operands             | f : 00h ~ 7Fh                                                  |                                                   |

| Operation            | (f) ← 00h, Z ← 1                                               |                                                   |

| Status Affected      | Ž                                                              |                                                   |

| OP-Code              | 00 0001 1fff ffff                                              |                                                   |

| Description<br>Cycle | The contents of register 'f' are cleared and the Z bit is set. |                                                   |

| Example              | CLRF FLAG_REG                                                  | B : FLAG_REG = 0x5A<br>A : FLAG_REG = 0x00, Z = 1 |

| CLRW            | Clear W                  |                        |

|-----------------|--------------------------|------------------------|

| Syntax          | CLRW                     |                        |

| Operands        | -                        |                        |

| Operation       | (W) ← 00h, Z ← 1         |                        |

| Status Affected | Z                        |                        |

| OP-Code         | 00 0001 0100 0000        |                        |

| Description     | W register is cleared an | d Zero bit (Z) is set. |

| Cycle           | 1                        | ( )                    |

| Example         | CLRW                     | B : W = 0x5A           |

| •               |                          | A : W = 0x00, Z = 1    |

| CLRWDT               | Clear Watchdog                                           | Timer                                         |

|----------------------|----------------------------------------------------------|-----------------------------------------------|

| Syntax               | CLRWDT                                                   |                                               |

| Operation            | -                                                        |                                               |

| Operation            | WDTE← 00h                                                |                                               |

| Status Affected      | -                                                        |                                               |

| OP-Code              | 01 1110 0000 0100                                        |                                               |

| Description<br>Cycle | CLRWDT instruction enables and reset the Watchdog Timer. |                                               |

| Example              | CLRWDT                                                   | B : WDT counter = ?<br>A : WDT counter = 0x00 |

| COMF                         | Complement "f"                                                                                                                                                                                                                                                                                            |                                                   |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| Syntax                       | COMF f [,d]                                                                                                                                                                                                                                                                                               |                                                   |  |

| Operands                     | f : 00h ~ 7Fh, d : 0, 1                                                                                                                                                                                                                                                                                   |                                                   |  |

| Operation                    | $(destination) \leftarrow (f)$                                                                                                                                                                                                                                                                            |                                                   |  |

| Status Affected              | Z                                                                                                                                                                                                                                                                                                         |                                                   |  |

| OP-Code                      | 00 1001 dfff ffff                                                                                                                                                                                                                                                                                         | complemented If (d) is 0, the result              |  |

| Description<br>Cycle         | The contents of register 'f' are complemented. If 'd' is 0, the result is stored in W. If 'd' is 1, the result is stored back in register 'f'.                                                                                                                                                            |                                                   |  |

| Example                      | COMF REG1,0                                                                                                                                                                                                                                                                                               | B : REG1 = 0x13<br>A : REG1 = 0x13, W = 0xEC      |  |

| DECF                         | Decrement "f"                                                                                                                                                                                                                                                                                             |                                                   |  |

| Syntax                       | DECF f [,d]                                                                                                                                                                                                                                                                                               |                                                   |  |

| Operands                     | f : 00h ~ 7Fh, d : 0, 1                                                                                                                                                                                                                                                                                   |                                                   |  |

| Operation                    | (destination) $\leftarrow$ (f) - 1                                                                                                                                                                                                                                                                        |                                                   |  |

| Status Affected<br>OP-Code   | Z<br>00 0011 dfff ffff                                                                                                                                                                                                                                                                                    |                                                   |  |

| Description                  |                                                                                                                                                                                                                                                                                                           | 0, the result is stored in the W register. If 'd' |  |

| Description                  | is 1, the result is stored back i                                                                                                                                                                                                                                                                         |                                                   |  |

| Cycle                        | 1                                                                                                                                                                                                                                                                                                         |                                                   |  |

| Example                      | DECF CNT, 1                                                                                                                                                                                                                                                                                               | B : CNT = 0x01, Z = 0                             |  |

|                              |                                                                                                                                                                                                                                                                                                           | A : CNT = 0x00, Z = 1                             |  |

|                              |                                                                                                                                                                                                                                                                                                           |                                                   |  |

| DECFSZ                       | Decrement "f", skip if 0                                                                                                                                                                                                                                                                                  | )                                                 |  |

| Syntax                       | DECFSZ f [,d]                                                                                                                                                                                                                                                                                             |                                                   |  |

| Operands                     |                                                                                                                                                                                                                                                                                                           | f : 00h ~ 7Fh, d : 0, 1                           |  |

| Operation                    | (destination) $\leftarrow$ (f) - 1, skip ne Z                                                                                                                                                                                                                                                             | xt instruction if result is 0                     |  |

| Status Affected<br>OP-Code   | 2<br>00 1011 dfff ffff                                                                                                                                                                                                                                                                                    |                                                   |  |

| Description                  | The contents of register 'f' are decremented. If 'd' is 0, the result is place<br>in the W register. If 'd' is 1, the result is placed back in register 'f'. If the<br>result is 1, the next instruction is executed. If the result is 0, then a NC<br>executed instead, making it a 2 cycle instruction. |                                                   |  |

| Cycle                        | 1 or 2<br>LABEL1 DECFSZ CNT, 1                                                                                                                                                                                                                                                                            | B : PC = LABEL1                                   |  |

| Example                      | GOTO LOOP                                                                                                                                                                                                                                                                                                 | A : CNT = CNT - 1                                 |  |

|                              | CONTINUE                                                                                                                                                                                                                                                                                                  | if $CNT = 0$ , $PC = CONTNUE$                     |  |

|                              |                                                                                                                                                                                                                                                                                                           | If CNT ≠0, PC = LABEL1 +1                         |  |

|                              |                                                                                                                                                                                                                                                                                                           |                                                   |  |

| GOTO                         | Unconditional Branch                                                                                                                                                                                                                                                                                      |                                                   |  |

| Syntax                       |                                                                                                                                                                                                                                                                                                           |                                                   |  |

| Operands                     | k : 00h ~ FFFh                                                                                                                                                                                                                                                                                            |                                                   |  |

| Operation<br>Status Affected | PC.11~0 ← k<br>-                                                                                                                                                                                                                                                                                          |                                                   |  |

| OP-Code                      | -<br>11 kkkk kkkk kkkk                                                                                                                                                                                                                                                                                    |                                                   |  |

| Description                  |                                                                                                                                                                                                                                                                                                           | nch. The 12-bit immediate value is loaded         |  |

| F                            | into PC bits <11:0>. GOTO is                                                                                                                                                                                                                                                                              |                                                   |  |

| Cycle                        | 2                                                                                                                                                                                                                                                                                                         |                                                   |  |

| Example                      | LABEL1 GOTO SUB1                                                                                                                                                                                                                                                                                          | B : PC = LABEL1                                   |  |

|                              | GOTO LOOP                                                                                                                                                                                                                                                                                                 | A : PC = SUB1                                     |  |

|                              |                                                                                                                                                                                                                                                                                                           |                                                   |  |

|                       | Increment "f"                      |                                                         |

|-----------------------|------------------------------------|---------------------------------------------------------|

| Syntax                | INCF f [,d]                        |                                                         |

| Operands              | f : 00h ~ 7Fh                      |                                                         |

| Operation             | (destination) $\leftarrow$ (f) + 1 |                                                         |

| Status Affected       | Z                                  |                                                         |

| OP-Code               | 00 1010 dfff ffff                  |                                                         |

| Description           | The contents of registe            | er 'f' are incremented. If 'd' is 0, the result is pla  |

|                       | in the W register. If 'd'          | is 1, the result is placed back in register 'f'.        |

| Cycle                 | 1                                  |                                                         |

| Example               | INCF CNT, 1                        | B: CNT = 0xFF, Z = 0                                    |

|                       |                                    | A : CNT = 0x00, Z = 1                                   |

| INCFSZ                | Incromont "f" SI                   | kin if 0                                                |

| Syntax                | Increment "f", SI                  |                                                         |

| •                     | f : 00h ~ 7Fh, d : 0, 1            |                                                         |

| Operands<br>Operation |                                    | skip payt instruction if result is 0                    |

| Status Affected       | $(uesumanon) \leftarrow (i) + i$   | , skip next instruction if result is 0                  |

| OP-Code               | -<br>00 1111 dfff ffff             |                                                         |

| Description           |                                    | er 'f' are incremented. If 'd' is 0, the result is pla  |

| Description           |                                    | is 1, the result is placed back in register 'f'. If the |

|                       |                                    | struction is executed. If the result is 0, a NOP is     |

|                       | -                                  | king it a 2 cycle instruction.                          |

| Cycle                 | 1 or 2                             |                                                         |

| Example               | LABEL1 INCFSZ CN                   | IT, 1 B : PC = LABEL1                                   |

| Example               | GOTO LOC                           |                                                         |

|                       | CONTINUE                           |                                                         |

|                       | 00111102                           | If CNT $\neq 0$ , PC = LABEL1 +1                        |

|                       |                                    |                                                         |

| IORLW                 | Inclusive OR Lite                  | ral with W                                              |

| Syntax                |                                    |                                                         |

| Operands              | k : 00h ~ FFh                      |                                                         |

| Operation             | $(W) \leftarrow (W) OR k$          |                                                         |

| Status Affected       | Z                                  |                                                         |

| OP-Code               |                                    |                                                         |

| Description           |                                    | register are OR'ed with the eight-bit literal 'k'.      |

|                       | The result is placed in            |                                                         |

|                       | 1                                  | -                                                       |

| Cycle                 |                                    |                                                         |

| Cycle<br>Example      | IORLW 0x35                         | B:W=0x9A                                                |

| IORWF           | Inclusive OR W with "f"                                                                                                                                     |                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Syntax          | IORWF f[,d]                                                                                                                                                 |                                                                   |

| Operands        | k : 00h ~ FFh                                                                                                                                               |                                                                   |

| Operation       | (destination) $\leftarrow$ (W) OR                                                                                                                           | (f)                                                               |

| Status Affected | Z                                                                                                                                                           |                                                                   |

| OP-Code         | 00 0100 dfff ffff                                                                                                                                           |                                                                   |

| Description     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |                                                                   |

| Cycle           | 1                                                                                                                                                           |                                                                   |

| Example         | IORWF RESULT, 0                                                                                                                                             | B : RESULT = 0x13, W = 0x91<br>A : RESULT = 0x13, W = 0x93, Z = 0 |

| MOVFW                                              | Move "f" to W                                    |                                                                                |

|----------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------|

| Syntax                                             | MOVFW f                                          |                                                                                |

| Operands                                           | f : 00h ~ 7Fh                                    |                                                                                |

| Operation                                          | (W) ← (f)Status                                  |                                                                                |

| Affected                                           | -                                                |                                                                                |

| OP-Code                                            | 00 1000 Offf ffff                                |                                                                                |

| Description                                        | The contents of register                         | f are moved to W.                                                              |

| register. Cycle                                    | 1                                                |                                                                                |

| Example                                            | MOVFW REG1                                       | B : REG1 = 0x4F, W = ?                                                         |

|                                                    |                                                  | A : REG1 = 0x4F, W = 0x4F                                                      |

|                                                    |                                                  |                                                                                |

| MOVLW                                              | Move Literal to W                                |                                                                                |

| Syntax                                             | MOVLW k                                          |                                                                                |

| Operands                                           | k : 00h ~ FFh                                    |                                                                                |

| Operation                                          | (W)                                              |                                                                                |

| Status Affected                                    | -                                                |                                                                                |

| OP-Code                                            | 01 1001 kkkk kkkk                                |                                                                                |

| Description                                        |                                                  | loaded into W register. The don't cares                                        |

|                                                    | will assemble as 0's.                            | <b>C</b>                                                                       |

| Cycle                                              | 1                                                |                                                                                |

| Example                                            | MOVLW 0x5A                                       | B : W = ?                                                                      |

| •                                                  |                                                  | A : W = 0x5A                                                                   |

|                                                    |                                                  |                                                                                |

| MOVWF                                              | Move W to "f"                                    |                                                                                |

| Syntax                                             | MOVWF f                                          |                                                                                |

| Operands                                           | f : 00h ~ 7Fh                                    |                                                                                |

| Operation                                          | (f) ← (W)                                        |                                                                                |

| Status Affected                                    | -                                                |                                                                                |

| OP-Code                                            | 00 0000 1fff ffff                                |                                                                                |

| Description                                        | Move data from W regis                           | ter to register 'f'.                                                           |

| Cycle                                              | 1                                                | -                                                                              |

| Example                                            | MOVWF REG1                                       | B : REG1 = 0xFF, W = 0x4F                                                      |

|                                                    |                                                  | A : REG1 = 0x4F, W = 0x4F                                                      |

|                                                    |                                                  |                                                                                |

| MOVWR                                              | Move W to "r"                                    |                                                                                |

| Syntax                                             | MOVWR r                                          |                                                                                |

| Operands                                           | r : 00h ~ FFh                                    |                                                                                |

| Operation                                          |                                                  |                                                                                |

|                                                    | (r) ← (W)                                        |                                                                                |

|                                                    |                                                  |                                                                                |

| Status Affected                                    | -                                                |                                                                                |

| Status Affected<br>OP-Code                         | -<br>01 1110 rrrr rrrr<br>Move date from W regio | tor to register 'r'                                                            |

| Status Affected<br>OP-Code<br>Description          | Move data from W regis                           | ter to register 'r'.                                                           |

| Status Affected<br>OP-Code<br>Description<br>Cycle | Move data from W regis<br>1                      | -                                                                              |

| Status Affected<br>OP-Code<br>Description          | Move data from W regis                           | ter to register 'r'.<br>B : REG1 = 0xFF, W = 0x4F<br>A : REG1 = 0x4F, W = 0x4F |

| MOVRW                  | Move "r" to W                            |                                                                                            |

|------------------------|------------------------------------------|--------------------------------------------------------------------------------------------|

| Syntax                 | MOVRW r                                  |                                                                                            |

| Operands               | r : 20h ~ FFh                            |                                                                                            |

| Operation              | (W) ← (r)                                |                                                                                            |

| Status Affected        | -                                        |                                                                                            |

| OP-Code                | 01 1111 rrrr rrrr                        |                                                                                            |

| Description            | Move data from register 'r               | to W register.                                                                             |

| Cycle                  |                                          |                                                                                            |

| Example                | MOVRW REG1                               | B : REG1 = 0x4F, W = ?<br>A : REG1 = 0x4F, W = 0x4F                                        |

| NOP                    | No Operation                             |                                                                                            |

| Syntax                 | NOP                                      |                                                                                            |

| Operands               | -                                        |                                                                                            |