# TP44400NM – 360mΩ, 650V GaN HEMT With Integrated Driver and Protection

### 1.0 Features

- 650V enhancement mode HEMT with integrated driver

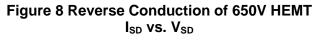

- 360mΩ R<sub>DSON</sub>

- 5V PWM input

- UVLO protection

- Zero reverse recovery

- Low quiescent current driver

- Adjustable turn-on slew rate

- Dv/Dt immunity both with/without driver-supply

- Low propagation delay for up to 2MHz operation

TP44400NM (Top view) (Bottom View)

**Figure 1 Device Image** (22pin 5×7×0.85 mm QFN Package)

#### RoHS/REACH/Halogen Free Compliance

## 2.0 Topologies and Applications

- As switching FETs in singles, or in pairs as half-bridges

- AC-DC, DC-DC, DC-AC converters

- PFC applications (totem pole and standard)

- High frequency LLC converters

- Mobile chargers and laptop adapters

- LED and motor drives

- Server power supplies

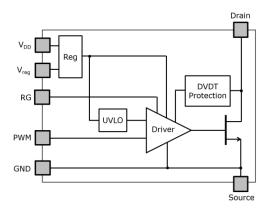

# 3.0 Description

The TP44400NM is a 360m $\Omega$ , 650V GaN HEMT device with integrated driver circuit. The monolithic integration of driver minimizes inductance in the gate loop enabling safe and clean switching even at high-voltage high-frequency operations. This device makes the applications more efficient/reliable, and also reduces the size of the magnetic components dramatically. UVLO function of the device turns-off the HEMT in case V<sub>DD</sub> voltage droops below its threshold voltage. A proprietary dv/dt protection circuit protects the HEMT from drain-dvdt induced false turn-on even in the absence of V<sub>DD</sub> supply. An external resistance between V<sub>reg</sub> and RG allows control of drain voltage slew rate for best EMI performance.

Figure 2 Functional Block Diagram

# 4.0 Ordering Information

### Table 1 Ordering Information

| Base Part<br>Number | Package Type            | Form          | Qty  | Reel<br>Diameter | Reel<br>Width | Orderable<br>Part Number |

|---------------------|-------------------------|---------------|------|------------------|---------------|--------------------------|

| TP44400NM           | 22 Pin 5×7×0.8mm<br>QFN | Tape and Reel | 1000 | 13" (330mm)      | 18mm          | TP44400NMTRPBF           |

| Evaluation Board    |                         |               |      |                  |               | TP44400NM-EVB            |

|                     |                         |               |      |                  |               |                          |

Revision 1.4 - 2021-04-29

Page 1 of 16

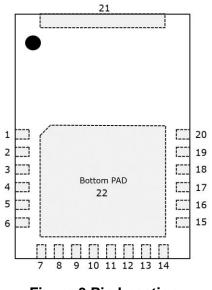

# **5.0 Pin Definition**

Figure 3 Pin Location (Package Top View)

### Table 2 Pin Definition

| Pin Number    | Pin Name         | Pin Type | Description                                                              |  |  |  |  |  |

|---------------|------------------|----------|--------------------------------------------------------------------------|--|--|--|--|--|

| 4 7 00        | NO               |          | No connect. Pins 8–20 can be connected to GND for better PCB             |  |  |  |  |  |

| 1, 7–20       | NC               |          | layout. Pin 1 and Pin 7 should be left open.                             |  |  |  |  |  |

| 2             | V <sub>DD</sub>  | LV-PWR   | VDD supply for driver. Connect 7.5V with a bypass capacitor of           |  |  |  |  |  |

| 2             | VDD              | LV-PVK   | 100nF.                                                                   |  |  |  |  |  |

| 3             | V <sub>reg</sub> | AO       | Internally generated supply. Connect a bypass capacitor of 10nF.         |  |  |  |  |  |

| 4             | RG               | AI       | Connect a suitable resistor between RG and $V_{reg}$ for controlling the |  |  |  |  |  |

| 4             |                  |          | drain voltage slew rate during the turn on.                              |  |  |  |  |  |

| 5             | PWM              | DI       | PWM input                                                                |  |  |  |  |  |

| C             | 6 GND            | GND      | Ground pin of the driver (internally Kelvin connected to the source      |  |  |  |  |  |

| o             |                  |          | of the 650V GaN HEMT)                                                    |  |  |  |  |  |

| 21            | Drain            | HV-PWR   | Drain of 650V GaN HEMT                                                   |  |  |  |  |  |

| 22 (Back Pad) | Source           |          | Source of 650V GaN HEMT                                                  |  |  |  |  |  |

**Abbreviations:** NC = not connected; LV-PWR = low-voltage power; AO = analog output; AI = analog input; DI = digital input; GND = ground; HV-PWR = high-voltage power

**Note:** The backside Source pad of the package must be connected directly or through multiple vias to the thermal plane of the PCB to ensure proper thermal management.

# 6.0 Absolute Maximum Ratings

### Table 3 Absolute Maximum Ratings <sup>[1]</sup> @T<sub>J</sub>=+25°C Unless Otherwise Specified

| Parameter                                                          | Symbol                | Value         | Unit |  |  |  |  |

|--------------------------------------------------------------------|-----------------------|---------------|------|--|--|--|--|

| Electrical Ratings                                                 |                       |               |      |  |  |  |  |

| Drain to Source Voltage of GaN HEMT                                | V <sub>DS</sub>       | 650           | V    |  |  |  |  |

| Transient Drain to Source Voltage [2]                              | VTDS                  | 750           | V    |  |  |  |  |

| Continuous Drain Current (at Tc = 100 °C)                          | IDS                   | 4.5           | A    |  |  |  |  |

| Pulsed Drain Current (at $T_J = 25^{\circ}C$ ) <sup>[3]</sup>      | DSpulse               | 7.5           | A    |  |  |  |  |

| Pulsed Drain Current (at $T_J = 125^{\circ}C$ ) <sup>[3]</sup>     | DSpulse               | 5.5           | A    |  |  |  |  |

| Drain to Source Voltage Slew Rate                                  | (dv/dt) <sub>DS</sub> | 200           | V/ns |  |  |  |  |

| V <sub>DD</sub> Supply Voltage                                     | V <sub>DD</sub>       | 8.0           | V    |  |  |  |  |

| Input PWM Voltage                                                  | V <sub>PWM</sub>      | 6.5           | V    |  |  |  |  |

| Transient Input PWM Voltage                                        | VPWM(Transient)       | 9.0           | V    |  |  |  |  |

| Storage Temperature Range                                          | T <sub>st</sub>       | −55 to +150   | °C   |  |  |  |  |

| Operating Temperature Range                                        | T <sub>op</sub>       | −55 to +150   | °C   |  |  |  |  |

| Maximum Junction Temperature                                       | TJ                    | +150          | °C   |  |  |  |  |

| Thermal Ra                                                         | tings                 |               |      |  |  |  |  |

| Thermal Resistance (junction-to-case) <sup>[4]</sup> – Bottom side | Rejc                  | 2.5           | °C/W |  |  |  |  |

| Thermal Resistance (junction-to-ambient) <sup>[4]</sup>            | Reja                  | 45            | °C/W |  |  |  |  |

| Soldering Temperature                                              | TSOLD                 | 260           | °C   |  |  |  |  |

| ESD Ratings                                                        |                       |               |      |  |  |  |  |

| Human Body Model (HBM) per JS-001-2017                             | Level 1C              | 1000 to <2000 | V    |  |  |  |  |

| Charged Device Model (CDM) per JS-002-2014                         | Level C3              | ≥1000         | V    |  |  |  |  |

| Moisture Ra                                                        | ating                 |               |      |  |  |  |  |

| Moisture Sensitivity Level (per J-STD-020D.1)                      | MSL                   | 1             | -    |  |  |  |  |

#### Note:

- [1] These are stress ratings. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Exceeding one or a combination of the absolute maximum ratings may cause permanent and irreversible damages to the device and/or to the surrounding circuit.

- [2] For duration < 1ms, provided to indicate robustness and not recommended for normal operation.

- [3] For duration < 10us, followed by sufficient time for the device to cool off.

- [4] As measured on DUT soldered on 2 oz Cu (FR4) PCB of size 1 square inch.

# 7.0 Recommended Operating Conditions

### Table 4 Recommended Operating Conditions <sup>[1][2]</sup> @T<sub>J</sub>=+25°C, Unless Otherwise Specified

| Parameter                                | Symbol            | Min | Nominal | Max  | Unit |

|------------------------------------------|-------------------|-----|---------|------|------|

| VDD Supply Voltage                       | V <sub>DD</sub>   | 7.0 | 7.5     | 8.0  | V    |

| Input PWM Voltage                        | V <sub>PWM</sub>  | 0   |         | 6.0  | V    |

| Drain Slew-Rate Control Resistor         | Rg                | 0   |         | 300  | Ω    |

| Bypass capacitor at V <sub>DD</sub> pin  | C <sub>VDD</sub>  |     | 100     |      | nF   |

| Bypass Capacitor at V <sub>reg</sub> pin | C <sub>Vreg</sub> |     | 10      |      | nF   |

| Operating Case Temperature               | Tc                | -40 |         | +125 | °C   |

#### Note:

[1] Operating for extended periods of time at conditions beyond the recommended range might affect device reliability.

[2] All voltages are with respect to GND pin which is internally Kelvin connected to Source pin.

# 8.0 Electrical Specifications

## Table 5 Electrical Specifications <sup>[1]</sup> $@T_J=+25^{\circ}C$ , $V_{DD} = +7.5V$ , Rg = 0 $\Omega$ , Unless Otherwise Specified

| Parameter                         | Description                                     | Condition                                                                             | Minimum | Typical                                                                                                                                                                                        | Maximum | Unit  |  |  |

|-----------------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|--|--|

| 650V GaN HEMT                     |                                                 |                                                                                       |         |                                                                                                                                                                                                |         |       |  |  |

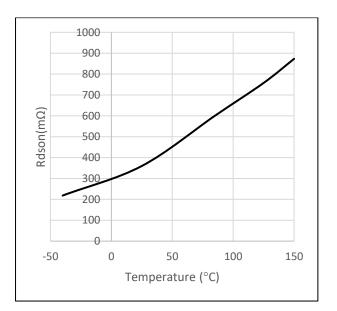

| R <sub>DSON</sub>                 | Drain to source                                 | I <sub>DS</sub> =0.5A DC                                                              |         | 360                                                                                                                                                                                            |         | mΩ    |  |  |

| NDSON                             | resistance                                      | I <sub>DS</sub> =0.5A DC, T <sub>J</sub> =+150°C                                      |         | 880                                                                                                                                                                                            |         | 11152 |  |  |

|                                   | Drain to source                                 | V <sub>DS</sub> =650V, V <sub>PWM</sub> =0                                            |         | 0.1                                                                                                                                                                                            |         |       |  |  |

| IDSS                              | leakage current                                 | V <sub>DS</sub> =650V, V <sub>РWM</sub> =0,<br>Tj=+150°С                              |         | 10.0                                                                                                                                                                                           |         | μA    |  |  |

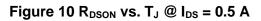

|                                   | Output                                          | V <sub>DS</sub> =100V, V <sub>PWM</sub> =0V                                           |         | 360         880         0.1         10.0         22         8         4.4         8         0         2.5         4.0         7.5         2.0         3.1         6.0         4.65         4.5 |         |       |  |  |

| Coss                              | capacitance                                     | VDS=400V, VPWM=0V                                                                     |         |                                                                                                                                                                                                |         | pF    |  |  |

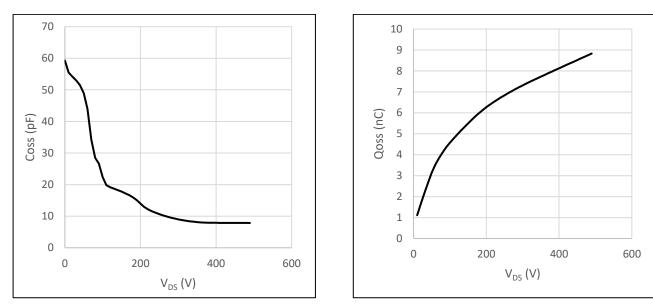

| -                                 |                                                 | V <sub>DS</sub> =100V                                                                 |         | -                                                                                                                                                                                              |         | _     |  |  |

| Qoss                              | Output charge                                   | V <sub>DS</sub> =400V                                                                 |         |                                                                                                                                                                                                |         | nC    |  |  |

| Q <sub>RR</sub>                   | Reverse recovery charge                         |                                                                                       |         | 0                                                                                                                                                                                              |         | nC    |  |  |

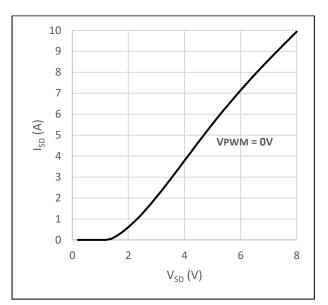

|                                   | Reverse                                         | I <sub>SD</sub> =1A, V <sub>PWM</sub> =0V                                             |         | 2.5                                                                                                                                                                                            |         | V     |  |  |

| V <sub>SD</sub>                   | conduction voltage                              | I <sub>SD</sub> =3.5A, V <sub>PWM</sub> =0V                                           |         | 4.0                                                                                                                                                                                            |         |       |  |  |

|                                   |                                                 | Driver                                                                                |         |                                                                                                                                                                                                |         |       |  |  |

| V <sub>DD</sub>                   | Supply voltage                                  |                                                                                       | 7.0     | 7.5                                                                                                                                                                                            | 8       | V     |  |  |

| Ιq                                | Quiescent current<br>from VDD                   | V <sub>DS</sub> open, V <sub>PWM</sub> =0                                             |         | 2.0                                                                                                                                                                                            |         | mA    |  |  |

| $I_{sw0}$                         | Switching current from V <sub>DD</sub>          | V <sub>DS</sub> open,<br>V <sub>PWM</sub> switching at 50%<br>duty cycle, 1 MHz freq. |         | 3.1                                                                                                                                                                                            |         | mA    |  |  |

| V <sub>reg</sub>                  | Regulated voltage                               | V <sub>DS</sub> open, V <sub>PWM</sub> =0                                             |         | 6.0                                                                                                                                                                                            |         | V     |  |  |

| $V_{\text{DD}\_\text{UVLO-High}}$ | UVLO threshold<br>while VDD rising              | $V_{DD}$ =0V to 7.5V                                                                  |         | 4.65                                                                                                                                                                                           |         | V     |  |  |

| VDD_UVLO-Low                      | UVLO threshold<br>while V <sub>DD</sub> falling | V <sub>DD</sub> =7.5V to 0V                                                           |         | 4.5                                                                                                                                                                                            |         | V     |  |  |

| UVLO <sub>hyst</sub>              | UVLO hysteresis                                 |                                                                                       |         | 0.15                                                                                                                                                                                           |         | V     |  |  |

| Vін                   | PWM input<br>voltage to turn on       |                                                                           |              |           | 3.0 | V    |  |

|-----------------------|---------------------------------------|---------------------------------------------------------------------------|--------------|-----------|-----|------|--|

| VIL                   | PWM input<br>voltage to turn off      |                                                                           | 0.7          |           |     | V    |  |

|                       | · · · · · · · · · · · · · · · · · · · | DVDT Immunity                                                             |              |           |     | •    |  |

| (dv/dt) <sub>DS</sub> | Max drain-source<br>dv/dt             | $V_{DD} = 0V$ to $8V$                                                     |              |           | 200 | V/ns |  |

|                       | Switching Time                        | $\mathbb{D}$ R <sub>G</sub> = 0 $\Omega$ , I <sub>DS</sub> = 2A (Refer to | Figure 5 and | Figure 6) |     |      |  |

|                       | Die e time                            | V <sub>DS</sub> =400V                                                     |              | 15        |     |      |  |

| tr                    | Rise time                             | V <sub>DS</sub> =400V, T <sub>J</sub> =+150°C                             |              | 15        |     | ns   |  |

|                       | E all Cara                            | V <sub>DS</sub> =400V                                                     |              | 4         |     |      |  |

| t <sub>f</sub>        | Fall time                             | V <sub>DS</sub> =400V, T <sub>J</sub> =+150°C                             |              | 7         |     | ns   |  |

|                       | Turn-on                               | V <sub>DS</sub> =400V,                                                    |              | 13        |     |      |  |

| <b>t</b> prop-on      | propagation delay                     | V <sub>DS</sub> =400V, T <sub>J</sub> =+150°C                             |              | 15        |     | ns   |  |

|                       | Turn-off                              | V <sub>DS</sub> =400V,                                                    |              | 19        |     |      |  |

| tprop-off             | propagation delay                     | V <sub>DS</sub> =400V, T <sub>J</sub> =+150°C                             |              | 23        |     | ns   |  |

### Note:

[1] All voltages are with respect to GND pin which is internally Kelvin connected to Source pin.

# 9.0 Detailed Description of Functions

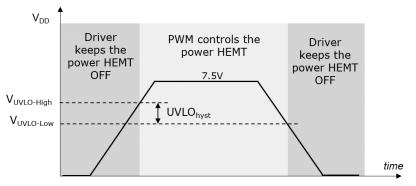

### 9.1 UVLO Function

UVLO (Under Voltage Lock Out) block controls the driver functionality. When the  $V_{DD}$  voltage is relatively low, such as during the startup, the 650V GaN HEMT might turn on unintentionally due to the ramping of the driver supply. Hence, for  $V_{DD}$  below UVLO threshold, this functionality allows the driver to keep the HEMT off and the PWM signal is ignored. As the  $V_{DD}$  voltage reaches within the region where the driver functions properly as shown in Figure 4, then the UVLO releases the control, and the driver turns on and off the device according to the PWM input applied to the driver. However, for the safe operation of the HEMT, the minimum value of  $V_{DD}$  must be within the range given in the recommended operating conditions.

Figure 4 UVLO Functionality Diagram

# 9.2 DvDt Immunity Function

Large dv/dt at the drain pin is normal during the operation of converter. Such dv/dt may arise due to the usual switching actions, or due to the first-time hook-up of the converter system to the main supply of the power-stage. A positive dv/dt on the drain (with respect to the gate/source) will try to turn on the HEMT device through the parasitic gate to drain capacitance  $C_{GD}$ . This parasitic turn-on, also known as Miller turn-on or false turn-on, is highly undesirable, and might even cause catastrophic amount of shoot-through or crowbar current.

Usually, the driver is able to keep the HEMT off in the face of such dv/dt events, but for this to work properly, the driver requires its own supply to be up and steady. However, in many cases, the driver supply, which is derived from the main supply, may not be present at the first-time hookup of the main supply, which will lead to the HEMT device getting parasitically turn on.

The DvDt immunity function of TP44400NM device is a proprietary design which keeps the HEMT immune to such dv/dt induced turn-ons irrespective of whether  $V_{DD}$  supply is present or not. Also, this function works irrespective of usage of the device either on the low-side or the high-side.

# 9.3 Adjustable Turn-On Slew Rate Function

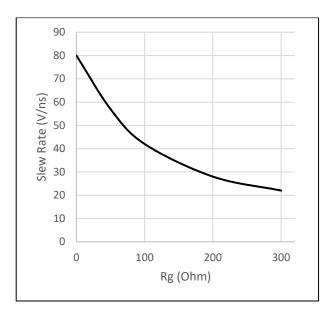

An adjustable slew-rate of the drain voltage during turn-on is a useful feature which helps control EMI and limits the magnitude of ringing on the switch node in a converter. For this feature, TP44400NM uses an external resistor Rg of user selectable value between the pins RG and V<sub>reg</sub> as shown in Figure 5. A typical plot of slew rate versus Rg value has been shown in Figure 15. It shall be noted that the switching-time numbers given in Table 5 are for the default value of Rg = 0  $\Omega$ .

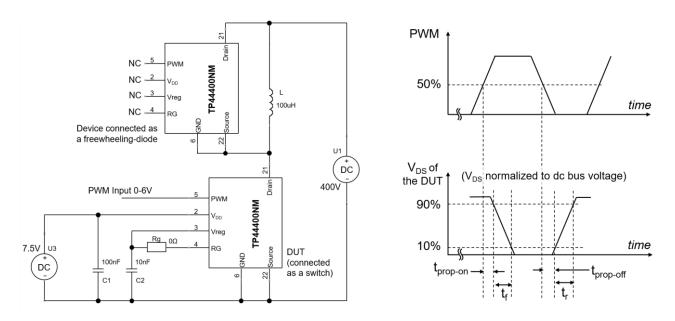

# **10.0 Switching Time Measurement Information**

The switching time is measured using the test circuit shown in Figure 5, two TP44400NM devices have been used. The low-side TP44400NM is the switching device, and it is connected to a 7.5V DC supply for its driver to operate properly. A resistor of 0  $\Omega$  is connected between R<sub>G</sub> and V<sub>reg</sub>. The high-side TP44400NM is used as a freewheeling/clamp-diode in the reverse direction. Its terminals 2–4 have been kept open for simplicity.

The junction point of the drain of the low-side and the source of the high-side forms the switching node, and this is connected to a 400V DC bus supply with an inductive load.

When the PWM input pin of the low-side TP44400NM is supplied with a 5V pulse, the HEMT device turns on and its drain to source voltage ( $V_{DS}$ ) goes down as shown in Figure 6. During this time, the inductor current starts to increase. When the PWM signal goes low, the HEMT device turns off, and hence,  $V_{DS}$  starts to increase with the slew rate depending on the values of the inductor current and the switch-node

capacitance. The drain to source voltage  $V_{DS}$  gets clamped to the DC bus voltage because of the clamp diode, and the diode will conduct till the inductor current reaches zero.

The rise and fall times, and the propagation delays of PWM are defined as shown in Figure 6. The propagation delay to turn on the device is defined as the time from 50% of PWM rising edge to  $V_{DS}$  falling by 10% of the DC bus voltage at the given current. Similarly, propagation delay to turn off is defined as the time from 50% of PWM falling edge to  $V_{DS}$  rising by 10% of its bus voltage at the given current.

The rise time  $t_r$  is defined as the time it takes  $V_{DS}$  to go from 10% to 90% of the bus voltage during rising edge at the given drain current, while the fall time  $t_f$  is defined as the time it takes  $V_{DS}$  to drop from 90% to 10% of the bus voltage during the falling edge at the given drain current.

Figure 5 Switching Time Measurement Circuit

Figure 6 Switching Time Waveform and Definition of Parameters

# **11.0 Typical Characteristics**

**Conditions:**  $@T_J = +25^{\circ}C$ ,  $V_{DD} = +7.5V$ , Rg = 0 $\Omega$ , unless otherwise specified.

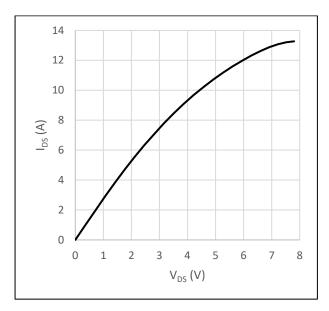

Figure 7 Forward Conduction of 650V HEMT  $I_{\text{DS}}$  vs.  $V_{\text{DS}}$

Figure 9 R<sub>DSON</sub> vs. I<sub>DS</sub>

Figure 11 Coss vs. VDs

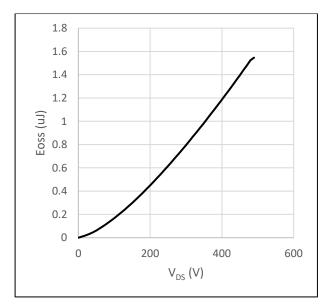

Figure 13 Eoss vs. VDs

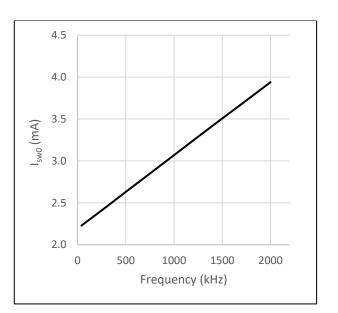

Figure 14 Driver Supply Current I<sub>sw0</sub> vs. PWM Frequency under Open Drain Condition @50% duty cycle

# Figure 15 Drain Slew-Rate Variation vs. Rg Resistor at Turn-On Transition <sup>[1]</sup>

### Note:

[1] The measurement setup is as per Figure 5 and Figure 6. The slew-rate corresponds to the region where  $V_{DS}$  drops from 90% to 10% of the bus voltage during its falling edge transition, and the value of  $I_{DS}$  at the transition edge is 1.5A.

# **12.0 Application Information**

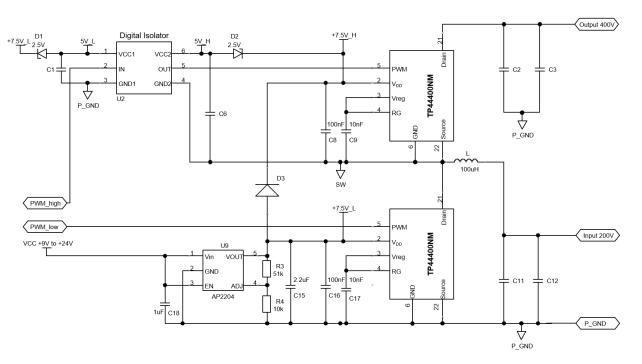

The TP44400NM can be used in a half bridge configuration as shown in Figure 16 for a generic buck or boost converter application. Two chips with integrated driver are used to create a half bridge. The module requires proper driver bias supplies for its operation.

A regulated 7.5V supply is used for the low-side module, while a bootstrap configuration is used to generate the boot voltage for the high-side module. The high-side module can also be supplied with a regulated 7.5V supply derived from an isolated DC-DC converter (not shown here).

The PWM input signal to the low-side module can be directly fed from the PWM output of a controller or a microcontroller (sitting on the low-side device ground) with PWM voltage level not exceeding 6.0V, while the PWM for the high-side module can be supplied through a digital isolator as shown in the figure. The digital isolator shall have sufficient immunity against the expected high dv/dt rates of the switching node. The bias supplies for the primary and the secondary sides of the digital isolator can be derived from the 7.5V supplies available on the two sides using either low cost LDO (not shown here) or Zener diodes as shown in the figure.

Although, in Figure 16, the RG pin is shorted to the pin Vreg, one can also use a non-zero valued gate resistor between these pins to control the turn-on switching time.

Figure 16 Boost Converter Application Circuit

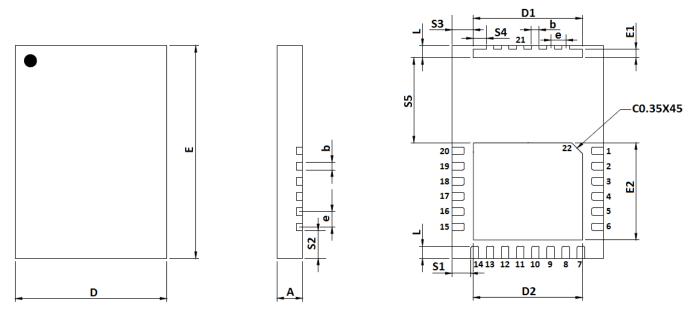

# **13.0 Device Package Information**

# Figure 17 Device Package Drawing

(All dimensions are in mm)

| Table 6 Device Package Dimensions |       |           |  |  |  |  |  |  |

|-----------------------------------|-------|-----------|--|--|--|--|--|--|

| Dimension                         | Value | Tolerance |  |  |  |  |  |  |

| Dimension<br>(mm) | Value<br>(mm) | Tolerance<br>(mm) | Dimension<br>(mm) | Value<br>(mm) | Tolerance<br>(mm) |

|-------------------|---------------|-------------------|-------------------|---------------|-------------------|

| A                 | 0.80          | ±0.05             | E2                | 3.20          | ±0.05             |

| b                 | 0.25          | +0.05/-0.07       | L                 | 0.40          | ±0.05             |

| D                 | 5.00 BSC      | ±0.05             | S1                | 0.625         | ±0.05             |

| D1                | 3.60          | ±0.05             | S2                | 0.91          | ±0.05             |

| D2                | 3.60          | ±0.05             | S3                | 0.70          | ±0.05             |

| е                 | 0.50 BSC      | ±0.05             | S4                | 0.425         | ±0.05             |

| E                 | 7.00 BSC      | ±0.05             | S5                | 2.80          | ±0.05             |

| E1                | 0.28          | ±0.05             | -                 | -             | -                 |

**Note:** Lead finish: Pure Sn without underlayer; Thickness: 7.5µm ~ 20µm (Typical 10µm ~ 12µm)

### Attention:

Please refer to application notes TN-001 and TN-002 at http://www.tagoretech.com for PCB and soldering related guidelines.

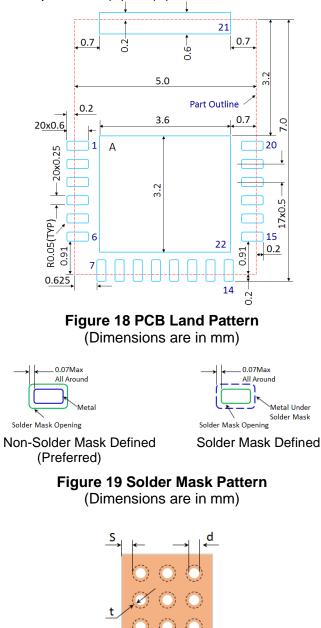

# 14.0 PCB Land Design

### **Guidelines:**

- [1] A 4-layer PCB is recommended.

- [2] Via diameter is recommended to be 0.3mm to prevent solder wicking inside the vias.

- [3] Thermal vias shall only be placed on pad A.

- [4] The maximum via number for pad A is  $6(X) \times 5(Y) = 30$  units.

#### **Figure 20 Thermal Via Pattern**

(Recommended Values: S≥0.15mm; Y≥0.20mm; d=0.3mm; Plating Thickness t=25µm or 50µm)

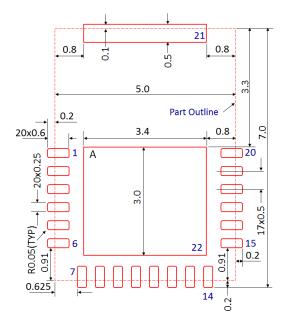

# 15.0 PCB Stencil Design

#### **Guidelines:**

- [1] Laser-cut, stainless steel stencil is recommended with electro-polished trapezoidal walls to improve the paste release.

- [2] Stencil thickness is recommended to be 125µm.

Figure 21 Stencil Openings (Dimensions are in mm)

Figure 22 Stencil Openings (Shall Not Cover Via Areas if Possible) (Dimensions are in mm)

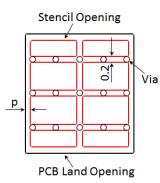

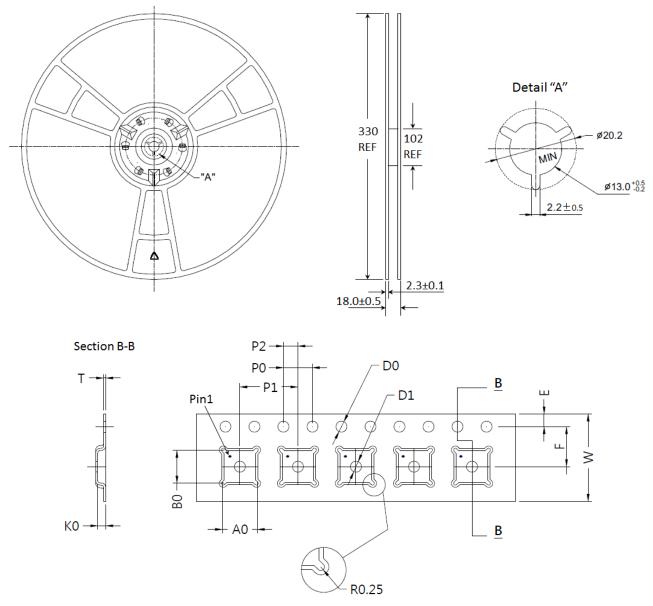

# 16.0 Tape and Reel Information

Figure 23 Tape and Reel Drawing

| Dimension (mm) | Value (mm) | Tolerance (mm) | Dimension (mm) | Value (mm) | Tolerance (mm) |  |  |  |

|----------------|------------|----------------|----------------|------------|----------------|--|--|--|

| A0             | 5.35       | ±0.10          | K0             | 1.10       | ±0.10          |  |  |  |

| B0             | 7.35       | ±0.10          | P0             | 4.00       | ±0.10          |  |  |  |

| D0             | 1.50       | +0.10/-0.00    | P1             | 8.00       | ±0.10          |  |  |  |

| D1             | 1.50       | +0.10/-0.00    | P2             | 2.00       | ±0.05          |  |  |  |

| E              | 1.75       | ±0.10          | Т              | 0.30       | ±0.05          |  |  |  |

| F              | 5.50       | ±0.05          | W              | 12.00      | ±0.30          |  |  |  |

#### Table 7 Tape and Reel Dimensions

Edition Revision 1.4 - 2021-04-29

### Published by

Tagore Technology Inc. 5 East College Drive, Suite 200 Arlington Heights, IL 60004, USA

©2021 All Rights Reserved

#### Legal Disclaimer

The information provided in this document shall in no event be regarded as a guarantee of conditions or characteristics. Tagore Technology assumes no responsibility for the consequences of the use of this information, nor for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of Tagore Technology. The specifications mentioned in this document are subject to change without notice.

#### For Further Information

For further information on technology, delivery terms and conditions and prices, please contact Tagore Technology: support@tagoretech.com.