# National Semiconductor

## TP5116A, TP5116A-1, TP5156A, TP5156A-1 Monolithic CODECs

## **General Description**

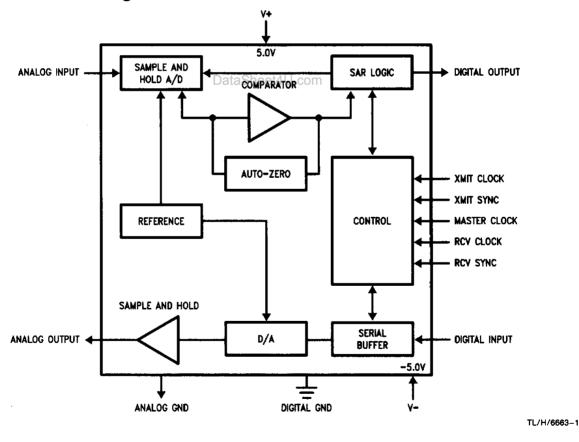

The TP5116A and TP5156A are monolithic PCM CODECs implemented with double-poly CMOS technology. The TP5116A is intended for  $\mu$ -law applications and the TP5156A is for A-law applications.

Each device contains separate D/A and A/D circuitry, all necessary sample and hold capacitors, and internal autozero circuits. Each device also contains a precision internal voltage reference, eliminating the need for an external reference. There are no internal connections to pins 15 or 16, making them directly interchangeable with CODECs using external reference components.

All devices are intended to be used with the TP3040 monolithic PCM filter which provides the input anti-aliasing function for the encoder, smooths the output of the decoder and corrects for the sin x/x distortion introduced by the decoder sample and hold output.

#### **Features**

- TP5116A--µ-law coding (sign plus magnitude format)

- TP5156A—A-law coding

- Synchronous or asynchronous operation

- Precision voltage reference on-chip

- Internal sample-and-hold capacitors

- Internal auto-zero circuit

- Low operation power—40 mW typical

- ±5V operation

- TTL compatible digital interface

## **Simplified Block Diagram**

DataShe

1-202

www.DataSheet4U.com

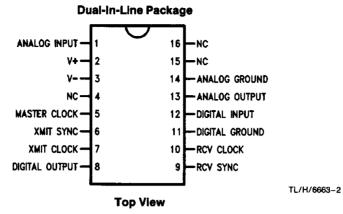

## **Connection Diagram**

Order Number TP5116AJ or TP5156AJ See NS Package Number J16A

## **Description of Pin Functions**

|      | Symbol         | Function                                                                                                                                                                                                   | Symbol         | Function                                                                                                                       |

|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

|      | ANALOG INPUT   | ANALOG INPUT to the encoder. This signal will be sampled at the beginning of the encoder time slot and the resulting PCM code will be shifted out during                                                   | RCV SYNC       | Decoder frame sync pulse. Normally oc-<br>curring at an 8 kHz rate, this pulse is<br>nominally eight RCV CLOCK cycles<br>wide. |

|      |                | the subsequent encode time slot.                                                                                                                                                                           | RCV CLOCK      | Receive bit clock input used to shift in                                                                                       |

|      | <b>V</b> +     | 5V(±5%) Power Supply.                                                                                                                                                                                      |                | the PCM data on DIGITAL INPUT. May                                                                                             |

|      | V-             | -5V(±5%) Power Supply.                                                                                                                                                                                     |                | operate from 64 kHz to 2.048 MHz. May<br>be asynchronous with XMIT CLOCK.                                                      |

|      | NC             | Unused.                                                                                                                                                                                                    | DIGITAL GROUND | •                                                                                                                              |

|      | MASTER CLOCK   | MASTER CLOCK input used to operate the internal encode and decode se-                                                                                                                                      | DIGITAL GROUND | All digital levels referenced to the DIGI-<br>TAL GROUND pin.                                                                  |

|      |                | quencers. Should be 1.536 MHz, 1.544 MHz or 2.048 MHz.                                                                                                                                                     | DIGITAL INPUT  | Serial PCM data input to the decoder.<br>During the decoder time slot, PCM data                                                |

| et4U | .○XMIT SYNC    | Encoder frame sync pulse. Normally ocDataSI curring at an 8 kHz rate, this pulse is nominally eight XMIT CLOCK cycles                                                                                      | neet4U.com     | is shifted into DIGITAL INPUT, most sig-<br>nificant bit first, on the rising edge of<br>RCV CLOCK.                            |

|      |                | wide.                                                                                                                                                                                                      | ANALOG OUTPUT  | ANALOG OUTPUT from the decoder.                                                                                                |

|      | XMIT CLOCK     | Transmit bit clock input used to shift out<br>the PCM data on DIGITAL OUTPUT.<br>May operate from 64 kHz to 2.048 MHz.                                                                                     |                | The decoder sample and hold amplifier is updated approximately 15 $\mu$ s after the end of the decode time slot.               |

|      |                | May be asynchronous with RCV                                                                                                                                                                               | ANALOG         |                                                                                                                                |

|      |                | CLOCK.                                                                                                                                                                                                     | GROUND         | All analog signals are referenced to the                                                                                       |

|      | DIGITAL OUTPUT | Serial PCM TRI-STATE output from encoder. During the encoder time slot, the PCM code for the previous sample of ANALOG INPUT is shifted out, most significant bit first, on the rising edge of XMIT CLOCK. |                | ANALOG GROUND pin.                                                                                                             |

DataShe

1

#### **ENCODING FORMAT AT DIGITAL OUTPUT**

|                               |    | <u>.</u> | Sig | TP51<br>n + M |   | ıde |   |   | TP5156A<br>A-Law<br>(Includes Even Bit Inversion) |   |   |   |   | on) |   |   |

|-------------------------------|----|----------|-----|---------------|---|-----|---|---|---------------------------------------------------|---|---|---|---|-----|---|---|

| V <sub>IN</sub> = +Full-Scale | 1  | 1        | 1   | 1             | 1 | 1   | 1 | 1 | 1                                                 | 0 | 1 | 0 | 1 | 0   | 1 | 0 |

|                               | [1 | 0        | 0   | 0             | 0 | 0   | 0 | 0 | 1                                                 | 1 | 0 | 1 | 0 | 1   | 0 | 1 |

| $V_{IN} = 0V$                 | lo | 0        | 0   | 0             | 0 | 0   | 0 | 0 | 0                                                 | 1 | 0 | 1 | 0 | 1   | 0 | 1 |

| $V_{IN} = -Full-Scale$        | 0  | 1        | 1   | 1             | 1 | 1   | 1 | 1 | 0                                                 | 0 | 1 | 0 | 1 | 0   | 1 | 0 |

## **Functional Description**

Approximately 4  $\mu s$  after the rising edge of the XMIT SYNC pulse, the voltage present on the ANALOG INPUT is sampled and the process of encoding that sample into a PCM code is begun. Simultaneously, the 8-bit PCM code corresponding to the previous sample is shifted out of the DIGITAL OUTPUT, MSB first, on the rising edge of the next eight cycles of the XMIT CLOCK. When XMIT SYNC (which is normally eight XMIT CLOCK cycles long) goes low, the TRISTATE DIGITAL OUTPUT is returned to the high impedance state. On the TP5116A, the PCM code is in a  $\mu$ -law sign plus magnitude format. The TP5156A uses the standard A-law coding.

An 8-bit PCM code is shifted into DIGITAL INPUT on the rising edge of the first eight RCV CLOCK pulses after RCV SYNC goes high. RCV SYNC is nominally eight RCV CLOCK cycles wide. Approximately 15  $\mu s$  after RCV SYNC goes low, the ANALOG OUTPUT is updated to the voltage corresponding to the PCM input code.

All encoding and decoding operations are run from the MASTER CLOCK. MASTER CLOCK should be in the range of 1.536 MHz to 2.048 MHz and must be synchronous with XMIT CLOCK. The XMIT and RCV CLOCK may vary from 64 kHz to 2.048 MHz.

#### **ENCODING DELAY**

The encoding process begins immediately at the beginning of the encode time slot and is concluded no later than 18 time slots later. In normal applications, the PCM data is not shifted out until the next time slot 125  $\mu$ s later, resulting in an encoding delay of 125  $\mu$ s. In some applications it is possible to operate the CODEC at a higher frame rate to reduce this delay. With a 2.048 MHz MASTER CLOCK, the FS rate could be increased to 15 kHz, reducing the delay from 125  $\mu$ s to 67  $\mu$ s.

#### **DECODING DELAY**

The decoding process begins immediately after the end of the decoder time slot. The output of the decoder sample and hold amplifier is updated 28 MASTER CLOCK cycles later. The decoding delay is therefore approximately 28 clock cycles plus one half of a frame time or, 81  $\mu s$  for a 1.544 MHz system with an 8 kHz frame rate or, 76  $\mu s$  for a 2.048 MHz system with an 8 kHz frame rate. Again, for some applications the frame rate could be increased to reduce this delay.

et4U.com

DataSheet4U.com

DataShe

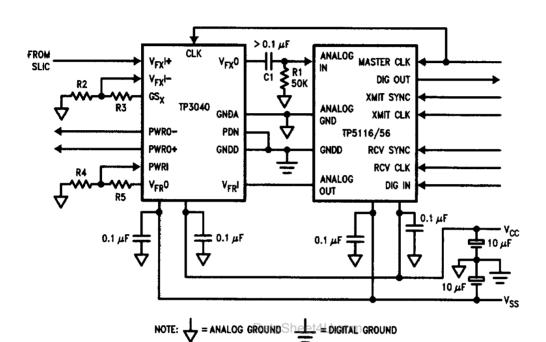

## **Typical Application**

A typical application of these CODECs used in conjunction with the TP3040 PCM filter is shown below. The values of resistor R1 and DC blocking capacitor C1, are non-critical. The capacitor value should exceed 0.1  $\mu\text{F},$  R1 should be less than 50 k $\Omega$ , and the product R1×C1 should exceed 4 ms.

$$\begin{aligned} \text{XMIT GAIN} &= 20 \times \log \left( \frac{\text{R3} + \text{R2}}{\text{R2}} \right) + 3 \, \text{dB} \\ \text{RCV GAIN} &= 20 \times \log \left( \frac{\text{R4}}{\text{R4} + \text{R5}} \right) \end{aligned}$$

The power supply decoupling capacitors should be 0.1  $\mu$ F. In order to take advantage of the excellent noise performance of these CODECs, care must be taken in board layout to prevent coupling of digital noise into the sensitive analog lines. For card insertion into a hot connector, care should be taken to insure that GNDA and GNDD are contacted prior to V<sub>CC</sub> and V<sub>BB</sub>.

TL/H/6663-5

DataShe

et4U.com

et4U.com

## Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

**Operating Temperature** Storage Temperature

-25°C to +125°C

-65°C to +150°C

-7V

Lead Temperature

$V^- - 0.3V$  to  $V^+ + 0.3V$

Input or Output

GNDD - 0.3V to  $V^+ + 0.3V$

(Solderdip 10 sec.)

Voltage at Any Analog

Voltage at Any Digital

Input or Output

300°C

taShe

ESD rating to be determined.

## DC Electrical Characteristics

V+ with Respect to DIGITAL GROUND

V - with Respect to DIGITAL GROUND

Unless otherwise noted  $T_A=0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ ,  $V^+=5.0V~\pm5\%$ ,  $V^-=-5.0V~\pm5\%$ . Typical characteristics are specified at  $V^+=5.0V, V^-=-5.0V$  and  $T_A=25^{\circ}\text{C}$ . All digital signals are referenced to DIGITAL GROUND. All analog signals are referenced to ANALOG GROUND. Limits printed in bold characters are guaranteed for V+ = 5.0V  $\pm$ 5%, V- = -5.0V  $\pm$ 5%; T<sub>A</sub> = 0°C to 70°C by correlation with 100% electrical testing at T<sub>A</sub> = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization.

| Symbol           | Parameter                            | Conditions                                                                       | Min  | Тур      | Max     | Units                                 |

|------------------|--------------------------------------|----------------------------------------------------------------------------------|------|----------|---------|---------------------------------------|

| IGITAL INTER     | RFACE                                |                                                                                  |      |          |         | · · · · · · · · · · · · · · · · · · · |

| l <sub>l</sub>   | Input Current                        | 0V <v<sub>IN<v+< td=""><td>-10</td><td></td><td>10</td><td>μΑ</td></v+<></v<sub> | -10  |          | 10      | μΑ                                    |

| V <sub>IL</sub>  | Input Low Voltage                    |                                                                                  | 1 .  | <u> </u> | 0.6     | V                                     |

| V <sub>IH</sub>  | Input High Voltage                   |                                                                                  | 2.2  |          | <u></u> | V                                     |

| V <sub>OL</sub>  | Output Low Voltage                   | I <sub>OL</sub> = 3.2 mA                                                         |      |          | 0.4     | V                                     |

| Voн              | Output High Voltage                  | I <sub>OH</sub> = 6 mA                                                           | 2.4  |          |         | V                                     |

| NALOG INTE       | RFACE                                |                                                                                  |      |          |         |                                       |

| ZI               | Analog Input Impedance when Sampling | Resistance in Series with<br>Approximately 70 pF                                 | 2    |          |         | kΩ                                    |

| Z <sub>O</sub>   | Output Impedance at Analog<br>Output |                                                                                  |      | 10       | 20      | Ω                                     |

| IN               | Analog Input Bias Current            | V <sub>IN</sub> = 0V                                                             | -0.1 |          | 0.1     | μΑ                                    |

| R1 × C1          | DC Blocking Time Constant            |                                                                                  | 4.0  |          |         | ms                                    |

| C1               | DC Blocking Capacitor                | DataSheet4U.com                                                                  | 0.1  |          |         | μF                                    |

| R1               | Input Bias Resistor                  |                                                                                  |      | L        | 50      | kΩ                                    |

| OWER DISSI       | PATION                               |                                                                                  |      |          |         |                                       |

| I <sub>CC1</sub> | Operating Current, V <sub>CC</sub>   |                                                                                  |      | 3.5      | 8.0     | mA                                    |

| I <sub>BB1</sub> | Operating Current, V <sub>BB</sub>   |                                                                                  |      | 3.5      | 8.0     | mA                                    |

### **AC Electrical Characteristics**

Unless otherwise noted,  $T_A = 25^{\circ}\text{C}$ ,  $V^+ = 5.0\text{V}$ ,  $V^- = -5.0\text{V}$ . The analog input is a 0 dBm0, 1.02 kHz sine wave. The DIGITAL INPUT is a PCM bit stream generated by passing a 0 dBm0, 1.02 kHz sine wave through an ideal encoder. All output levels are sin x/x corrected, limits printed in bold characters are guaranteed for V<sup>+</sup> = 5.0V  $\pm$ 5%, V<sup>-</sup> = -5.0V  $\pm$ 5%; T<sub>A</sub> = 0°C to 70°C by correlation with 100% electrical testing at TA = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization.

| Symbol           | Parameter                                           | Conditions                                                                                                                                                                                                                                                                                                             | Min              | Тур | Max            | Units    |

|------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|----------------|----------|

|                  | Absolute Level                                      | The nominal 0 dBm0 levels for the TP5116A is 1.227 Vrms and 1.231 Vrms for the TP5156A. The resulting nominal overload level is 2.5V peak for all devices. All gain measurements for the encode and decode portions of the devices are based on these nominal levels after the necessary sin x/x corrections are made. |                  |     |                |          |

| G <sub>RA</sub>  | Receive Gain, Absolute                              | $T_A = 25^{\circ}C$ , $V^+ = 5V$ , $V^- = -5V$<br>TP5116A, TP5156A<br>TP5116A-1, TP5156A-1                                                                                                                                                                                                                             | -0.125<br>-0.175 |     | 0.125<br>0.175 | dB<br>dB |

| G <sub>RAT</sub> | Absolute Receive Gain<br>Variation with Temperature | $T_A = 0$ °C to $70$ °C                                                                                                                                                                                                                                                                                                | -0.05            |     | 0.05           | dB       |

1-206

www.DataSheet4U.com

DataShe

## **AC Electrical Characteristics** (Continued)

Unless otherwise noted,  $T_A = 25^{\circ}\text{C}$ ,  $V^+ = 5.0\text{V}$ ,  $V^- = -5.0\text{V}$ . The analog input is a 0 dBm0, 1.02 kHz sine wave. The DIGITAL INPUT is a PCM bit stream generated by passing a 0 dBm0, 1.02 kHz sine wave through an ideal encoder. All output levels are sin x/x corrected. Limits printed in bold characters are guaranteed for  $V^+ = 5.0\text{V} \pm 5\%$ ,  $V^- = -5.0\text{V} \pm 5\%$ ;  $T_A = 0^{\circ}\text{C}$  to 70°C by correlation with 100% electrical testing at  $T_A = 25^{\circ}\text{C}$ . All other limits are assured by correlation with other production tests and/or product design and characterization.

| Symbol            | Parameter                                              | Conditions                                                                                                                                          | Min                                    | Тур | Max                        | Units                |

|-------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|----------------------------|----------------------|

| G <sub>RAV</sub>  | Absolute Receive Gain<br>Variation with Supply Voltage | $V^{+} = 5V \pm 5\%, V^{-} = -5V \pm 5\%$                                                                                                           | -0.07                                  |     | 0.07                       | dВ                   |

| G <sub>XA</sub>   | Transmit Gain, Absolute                                | $T_A = 25^{\circ}\text{C}, V^+ = 5\text{V}, V^- = -5\text{V}$<br>TP5116A, TP5156A<br>TP5116A-1, TP5156A-1                                           | -0.125<br>-0.175                       |     | 0.125<br>0.175             | dB                   |

| G <sub>XAT</sub>  | Absolute Transmit Gain Variation with Temperature      | $T_A = 0$ °C to 70°C                                                                                                                                | -0.05                                  |     | 0.05                       | dB                   |

| G <sub>XAV</sub>  | Absolute Transmit Gain Variation with Supply Voltage   | $V^{+} = 5V \pm 5\%, V^{-} = -5V \pm 5\%$                                                                                                           | -0.07                                  |     | 0.07                       | dB                   |

| G <sub>RAL</sub>  | Absolute Receive Gain<br>Variation with Level          | CCITT Method 2 Relative to - 10 dBm0 0 dBm0 to 3 dBm0 - 40 dBm0 to 0 dBm0 - 50 dBm0 to - 40 dBm0 - 55 dBm0 to - 50 dBm0                             | 0.3<br>0.2<br>0.4<br>1.0               |     | 0.3<br>0.2<br>0.4<br>1.0   | dB<br>dB<br>dB<br>dB |

| G <sub>XAL</sub>  | Absolute Transmit Gain<br>Variation with Level         | CCITT Method 2 Relative to - 10 dBm0 0 dBm0 to 3 dBm0 40 dBm0 to 0 dBm0 50 dBm0 to 40 dBm0 TP5116A, TP5156A TP5116A-1, TP5156A-1 55 dBm0 to 50 dBm0 | -0.3<br>-0.2<br>-0.4<br>-0.475<br>-1.0 |     | 0.3<br>0.2<br>0.4<br>0.475 | dB<br>dB<br>dB<br>dB |

| STD <sub>R</sub>  | Receive Signal to Distortion<br>Ratio                  | Sinusoidal Test Method Input<br>Level<br>- 30 dBm0 to 0 dBm0<br>- 40 dBm0<br>- 45 dBm0 DataSheet4U.com                                              | 35<br>29<br>25                         |     |                            | dBC<br>dBC<br>dBC    |

| STD <sub>X</sub>  | Transmit Signal to Distortion<br>Ratio                 | Sinusoidal Test Method Input<br>Level<br>-30 dBm0 to 0 dBm0<br>-40 dBm0<br>-45 dBm0                                                                 | 35<br>29<br>25                         |     |                            | dBC<br>dBC<br>dBC    |

| N <sub>R</sub>    | Receive Idle Channel Noise                             | D <sub>R</sub> = Idle Code                                                                                                                          |                                        |     | 8                          | dBrnC0               |

| N <sub>X</sub>    | Transmit Idle Channel Noise                            | TP5116A, $VF_X = 0V$<br>TP5156A, $VF_X = 0V$                                                                                                        |                                        |     | 13<br>66                   | dBrnC0<br>dBm0p      |

| PPSRX             | Positive Power Supply Rejection, Transmit              | Input Level = 0V, $V_{CC}$ = 5.0 $V_{DC}$<br>+300 mVrms, f = 1.02 kHz                                                                               | 50                                     |     |                            | dB                   |

| PPSRR             | Positive Power Supply<br>Rejection, Receive            | $D_R = Idle Code$<br>$V_{CC} = 5.0 V_{DC} + 300 \text{ mVrms},$<br>f = 1.02  kHz                                                                    | 40                                     |     |                            | dB                   |

| NPSRX             | Negative Power Supply<br>Rejection, Transmit           | Input Level = 0V, $V_{BB} = -5.0 V_{DC}$<br>+ 300 mVrms, f = 1.02 kHz                                                                               | 50                                     |     |                            | dB                   |

| NPSR <sub>R</sub> | Negative Power Supply<br>Rejection, Receive            | $D_{R} = $ Steady PCM Code,<br>$V_{BB} = -5.0 V_{DC} + 300 \text{ mVrms},$<br>f = 1.02  kHz                                                         | 45                                     |     |                            | dВ                   |

| CT <sub>XR</sub>  | Transmit to Receive Crosstalk                          | D <sub>R</sub> = Steady PCM Code                                                                                                                    |                                        |     | -75                        | dB                   |

| CT <sub>RX</sub>  | Receive to Transmit Crosswalk                          | Transmit Input Level = 0V<br>TP5116A<br>TP5156A                                                                                                     |                                        |     | -70<br>-65<br>(Note 2)     | dB<br>dB             |

Note 1: Measured by extrapolation from the distortion test result at  $-50\ \mathrm{dBm0}$  level.

1-207

www.DataSheet4U.com

et4L

Note 2: Theoretical worst-case for a perfectly zeroed encoder with alternating sign bit, due to the decoding law.

et4U.com

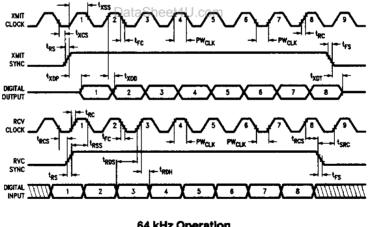

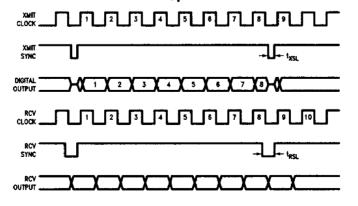

Timing Specifications Unless otherwise noted,  $T_A = 0^{\circ}C$  to  $70^{\circ}C$ ,  $V^+ - +5V \pm 5\%$ ,  $V^- = -5V \pm 5\%$ . All digital signals are referenced to DIGITAL GROUND and are measured at  $V_{IH}$  and  $V_{IL}$  as indicated in the Timing Waveforms. Limits printed in bold characters are guaranteed for  $V^+ = 5.0V \pm 5\%$ ,  $V^- = -5.0V \pm 5\%$ ;  $T_A = 0^{\circ}C$  to  $70^{\circ}C$  by correlation with 100% electrical testing at TA = 25°C. All other limits are assured by correlation with other production tests and/or product design and characterization. All timing specifications measured at  $V_{OH}=2.0V$  and  $V_{OL}=0.7V$ .

| Symbol                              | Parameter                     | Conditions                    | Min   | Тур   | Max | Units    |

|-------------------------------------|-------------------------------|-------------------------------|-------|-------|-----|----------|

| F <sub>M</sub>                      | MASTER CLOCK Frequency        |                               | 1.5   | 2.048 | 2.1 | MHz      |

| F <sub>X</sub> , F <sub>R</sub>     | XMIT, RCV CLOCK Frequency     |                               | 0.064 | 2.048 | 2.1 | MHz      |

| PW <sub>CLK</sub>                   | Clock Pulse Width             | MASTER, XMIT, RCV CLOCKS      | 150   |       |     | ns       |

| t <sub>RC</sub> , t <sub>FC</sub>   | Clock Rise and Fall Time      | MASTER, XMIT, RCV CLOCKS      |       |       | 50  | ns       |

| t <sub>RS</sub> , t <sub>FS</sub>   | Sync Pulse Rise and Fall Time | RCV, XMIT, SYNC               |       |       | 50  | ns       |

| t <sub>RCS</sub> , t <sub>XCS</sub> | Clock to Sync Delay           | RCV, XMIT                     | 0     |       |     | ns       |

| txss                                | XMIT SYNC Set-Up Time         |                               | 150   |       |     | ns       |

| txDD                                | XMIT Data Delay               | Load = 100 pF + 2 LSTTL Loads |       |       | 200 | ns       |

| t <sub>XDP</sub>                    | XMIT Data Present             | Load = 100 pF + 2 LSTTL Loads |       |       | 200 | ns       |

| txdt                                | XMIT Data TRI-STATE®          |                               |       |       | 150 | ns       |

| tsrc                                | RCV CLOCK to RCV SYNC Delay   |                               | 0     |       |     | ns       |

| t <sub>RDS</sub>                    | RCV Data Set-Up Time          |                               | 0     |       |     | ns       |

| t <sub>RSS</sub>                    | RCV SYNC Set-Up Time          |                               | 150   |       |     | ns       |

| t <sub>RDH</sub>                    | RCV Data Hold Time            |                               | 100   |       |     | ns       |

| txsL                                | XMIT SYNC Low Time            | 64 kHz Operation              | 300   |       |     | ns       |

| t <sub>RSL</sub>                    | RCV SYNC Low Time             | 64 kHz Operation              | 17    |       |     | (Note 3) |

Note 3: RCV SYNC must remain low for at least 17 cycles of MASTER CLOCK, each frame.

## **Timing Waveforms**

#### 72 kHz or Greater Operation

64 kHz Operation

TL/H/6663-4

TL/H/6663~3

1-208

www.DataSheet4U.com DataSheet4U.com