## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### Features

- 4-Channel 12-Bit Voltage Output DAC

- Positive and Negative Output Range: -5 V, -2.5 V, 2.5 V, 5 V

- High Output Capability: 60 mA

- 4-Channel 12-Bit Current Output DAC

- 200-mA Output Range

- 12-Bit ADC

- 4 External Inputs

- VDAC Current Monitor

- Internal Reference

- 2.5 V

- Serial Interfaces

- 4 Wire SPI

- I<sup>2</sup>C with 4 Slave Addresses

- Temperature Range: -40°C to +125°C

- Package: Wafer-Level CSP

### Applications

- High-Speed Optical Module

### Description

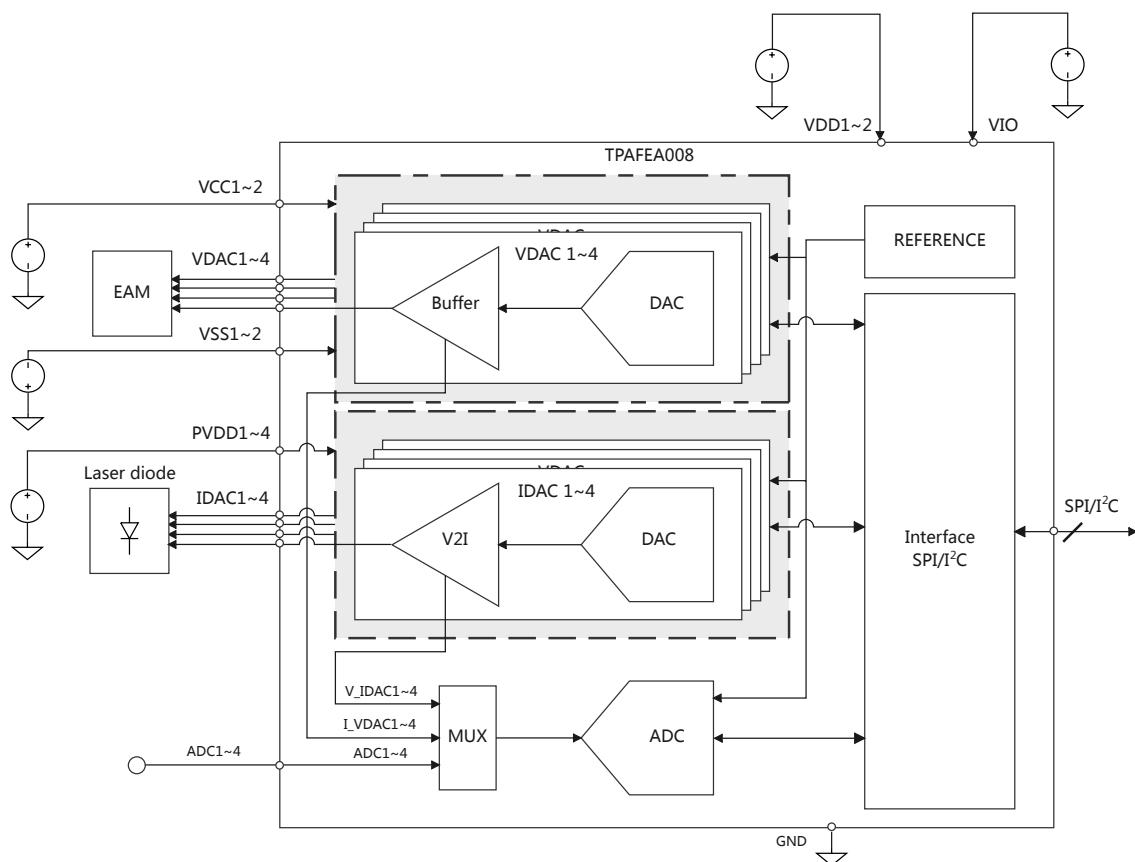

The TPAFEA008 is an integrated product with 4-ch negative/positive output VDAC and 4-ch IDAC, which is optimized for the optical module with 4-channel EML (Electro-absorption Modulated Laser).

The VDAC in TPAFEA008 supports both negative and positive output ranges, and the current capability is large enough to bias EAM (Electro-Absorption Modulator).

The IDAC in TPAFEA008 can support large output current range, and the output voltage range is also large enough to support different laser diodes.

The TPAFEA008 includes a 12bit ADC, with 4 input pins. Also, it incorporates internal alarm functions for ADC, so it can be used for RSSI (Received Signal Strength Indicator) and LOS (Loss of Signal) detection.

The VDAC output current and IDAC output voltage can be monitored by an integrated 12-bit ADC, so it is convenient for customers to monitor the loading status, without external components.

The TPAFEA008 is featured with small size, high integration, wide supply range, and operating temperature range, which make the device an excellent choice for 4-ch EML optical modules.

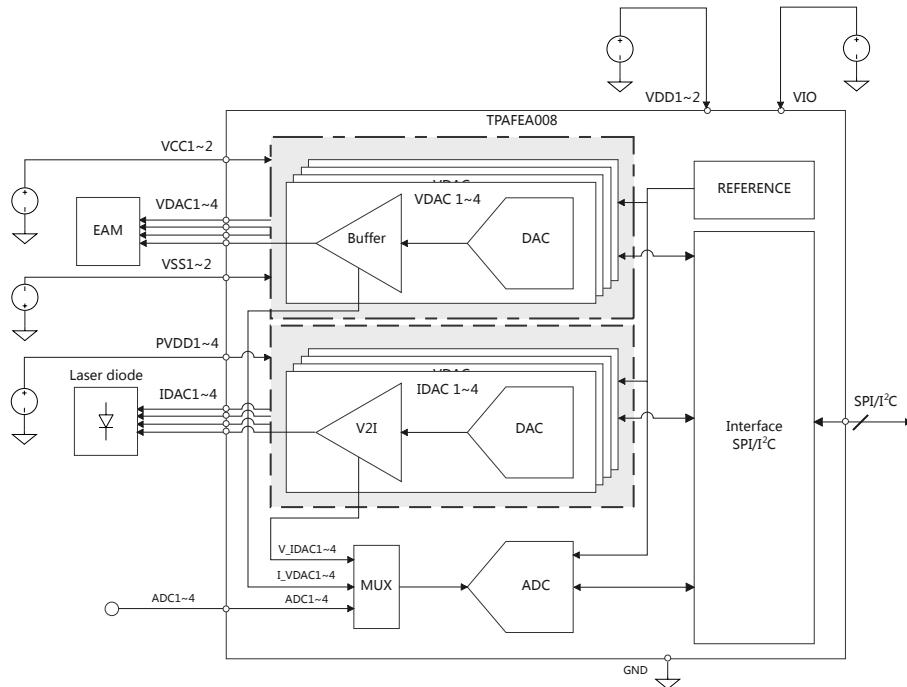

### Typical Application Circuit

---

**4-Channel EML Monitor and Controller with Positive/Negative

Voltage and Current DAC****Table of Contents**

|                                               |           |

|-----------------------------------------------|-----------|

| <b>Features.....</b>                          | <b>1</b>  |

| <b>Applications.....</b>                      | <b>1</b>  |

| <b>Description.....</b>                       | <b>1</b>  |

| <b>Typical Application Circuit.....</b>       | <b>1</b>  |

| <b>Product Family Table.....</b>              | <b>3</b>  |

| <b>Revision History.....</b>                  | <b>3</b>  |

| <b>Pin Configuration and Functions.....</b>   | <b>4</b>  |

| <b>Specifications.....</b>                    | <b>7</b>  |

| Absolute Maximum Ratings <sup>(1)</sup> ..... | 7         |

| ESD, Electrostatic Discharge Protection.....  | 7         |

| Recommended Operating Conditions.....         | 7         |

| Thermal Information.....                      | 7         |

| Electrical Characteristics.....               | 8         |

| Timing Requirements.....                      | 15        |

| Timing Diagrams.....                          | 16        |

| Typical Performance Characteristics.....      | 17        |

| <b>Detailed Description.....</b>              | <b>18</b> |

| Overview.....                                 | 18        |

| Functional Block Diagram.....                 | 18        |

| Feature Description.....                      | 18        |

| Serial Interface.....                         | 19        |

| Register Table.....                           | 21        |

| <b>Application and Implementation.....</b>    | <b>35</b> |

| Application Information .....                 | 35        |

| <b>Layout.....</b>                            | <b>36</b> |

| Layout Guideline.....                         | 36        |

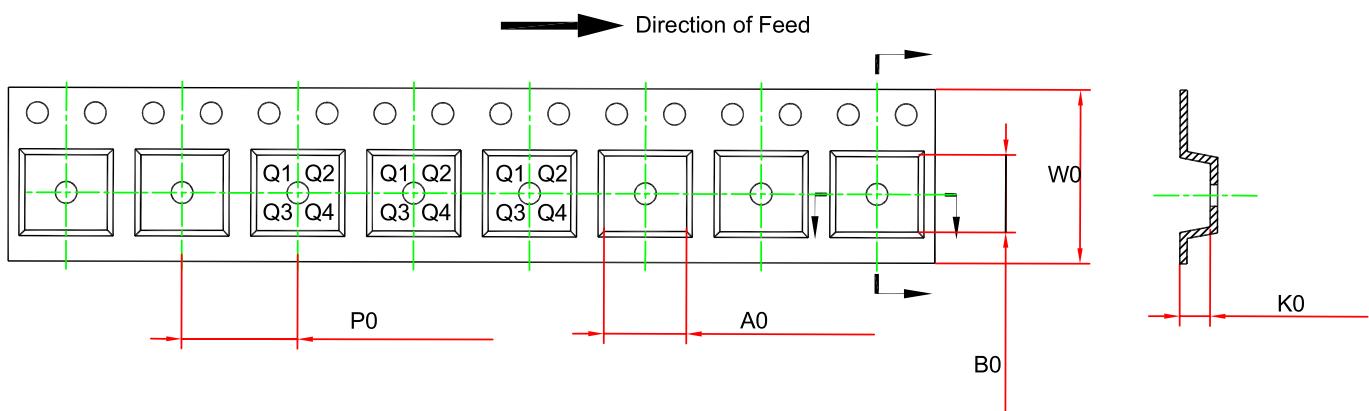

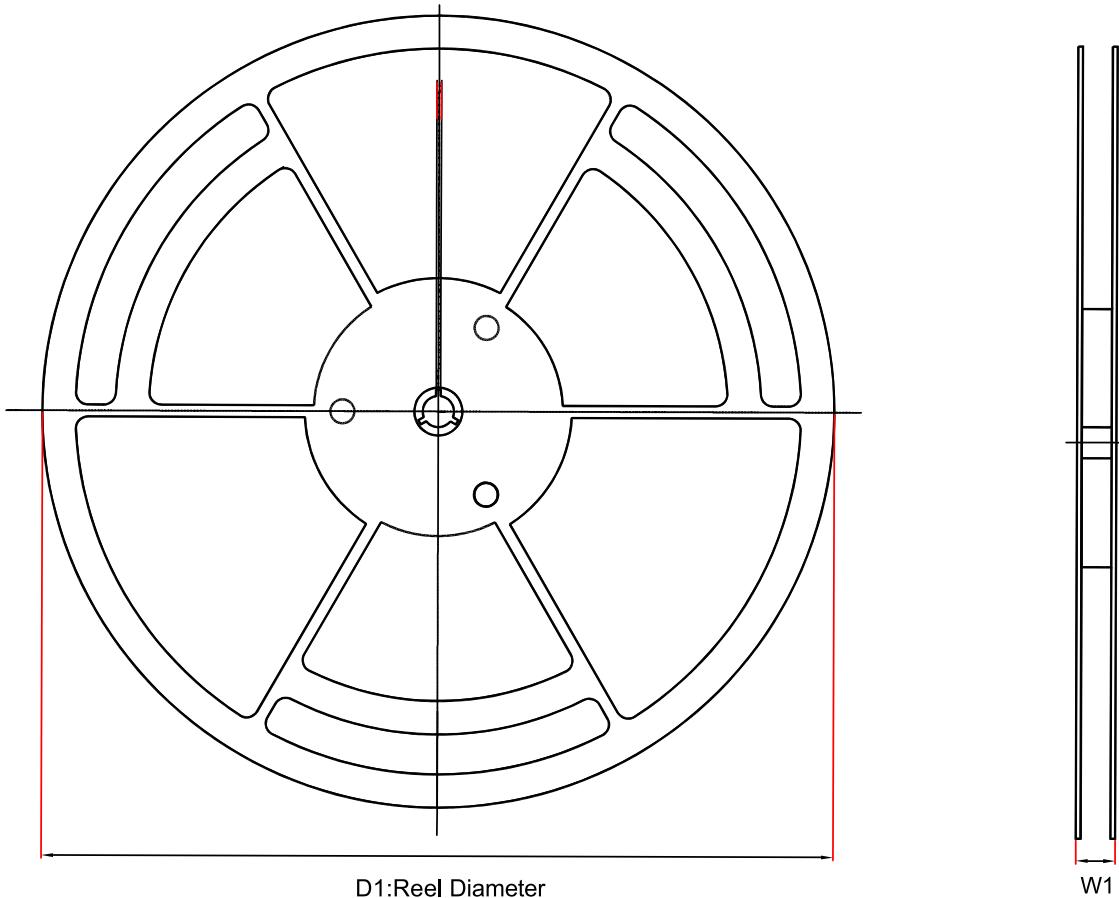

| <b>Tape and Reel Information.....</b>         | <b>37</b> |

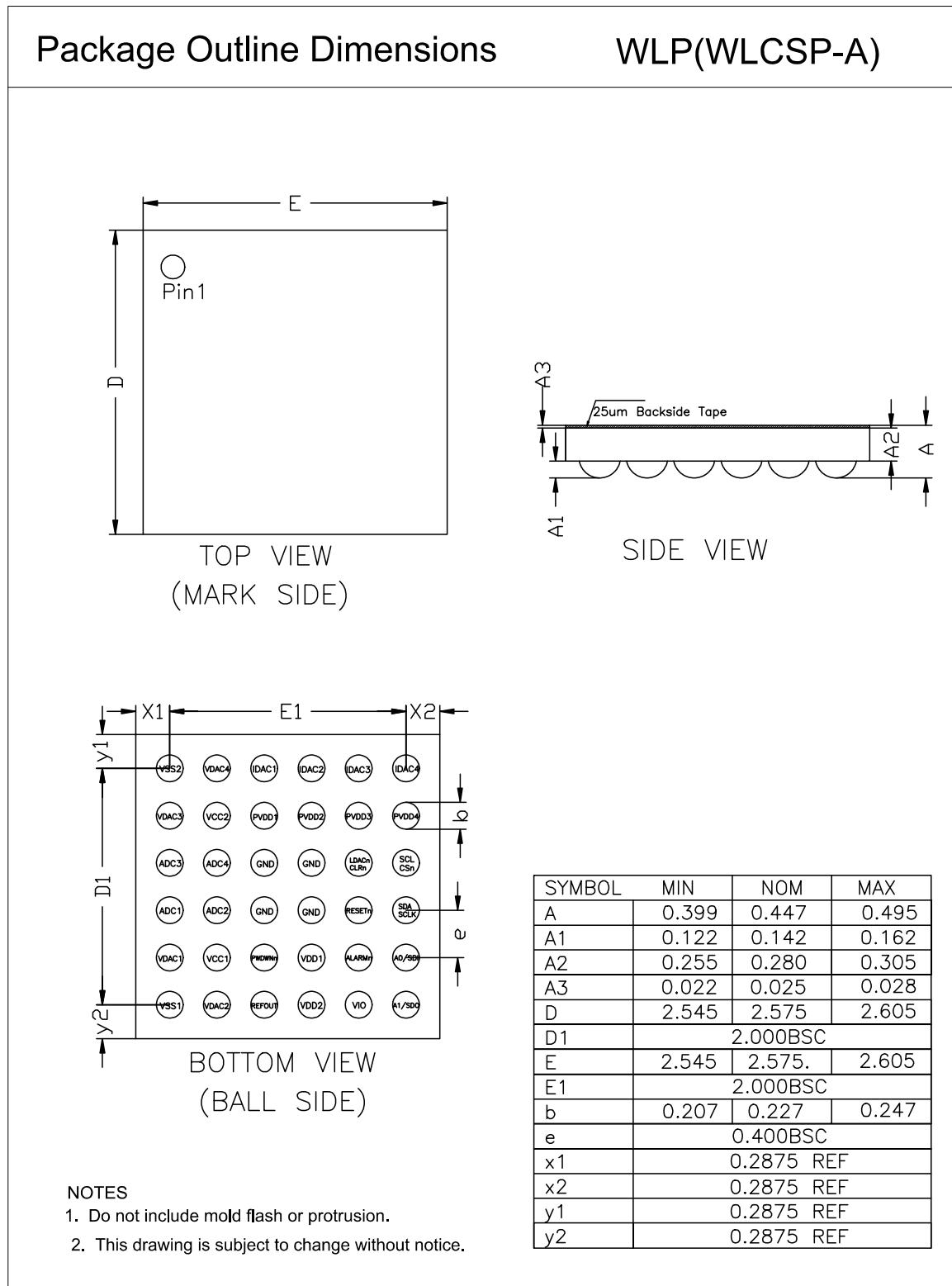

| <b>Package Outline Dimensions.....</b>        | <b>38</b> |

| WLCSP.....                                    | 38        |

| <b>Order Information.....</b>                 | <b>39</b> |

| <b>IMPORTANT NOTICE AND DISCLAIMER.....</b>   | <b>40</b> |

TPA008

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### Product Family Table

| Order Number | VDAC Channel | IDAC Channel | ADC Channel | Package |

|--------------|--------------|--------------|-------------|---------|

| TPA008-WLPR  | 4            | 4            | 4           | WLCSP   |

### Revision History

| Date       | Revision | Notes                                                                                             |

|------------|----------|---------------------------------------------------------------------------------------------------|

| 2023-06-05 | Rev.A.0  | Released version.                                                                                 |

| 2023-08-18 | Rev.A.1  | Updated the output compliance voltage range and application information, and corrected unit typo. |

| 2024-07-12 | Rev.A.2  | Updated the minimum operating voltage of VDAC.                                                    |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

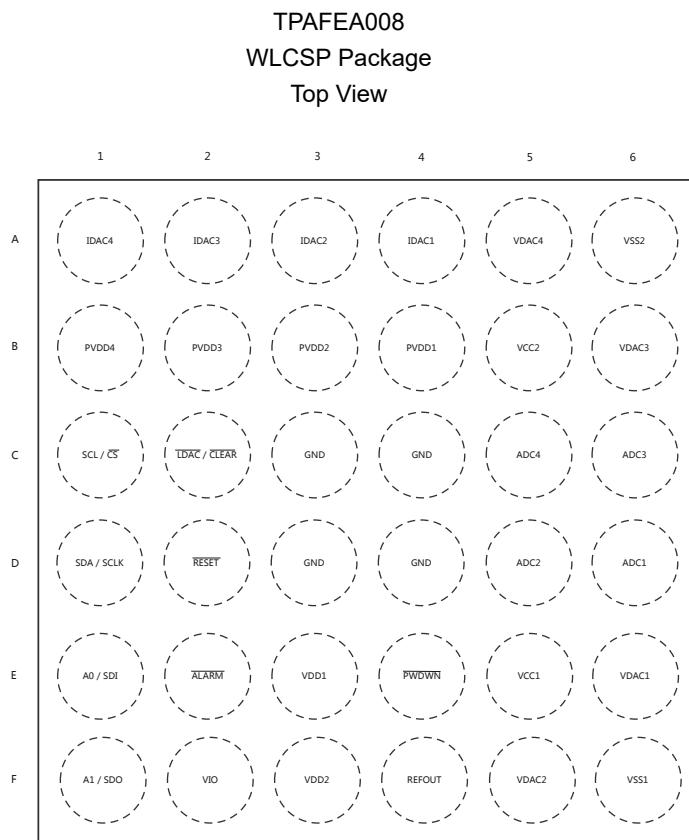

### Pin Configuration and Functions

**Table 1. Pin Functions: TPAFEA008**

| Pin |       | I/O    | Description                                                                                               |

|-----|-------|--------|-----------------------------------------------------------------------------------------------------------|

| No. | Name  |        |                                                                                                           |

| A1  | IDAC4 | Output | IDAC4 output.                                                                                             |

| A2  | IDAC3 | Output | IDAC3 output.                                                                                             |

| A3  | IDAC2 | Output | IDAC2 output.                                                                                             |

| A4  | IDAC1 | Output | IDAC1 output.                                                                                             |

| A5  | VDAC4 | Output | VDAC4 output.                                                                                             |

| A6  | VSS2  | Power  | VDAC3~4 output buffers negative analog power supply. Must be tied to the same potential as VSS1.          |

| B1  | PVDD4 | Power  | IDAC4 output buffer analog power supply.                                                                  |

| B2  | PVDD3 | Power  | IDAC3 output buffer analog power supply.                                                                  |

| B3  | PVDD2 | Power  | IDAC2 output buffer analog power supply.                                                                  |

| B4  | PVDD1 | Power  | IDAC1 output buffer analog power supply.                                                                  |

| B5  | VCC2  | Power  | VDAC3~4 output buffers positive analog power supply. This pin must be tied to the same potential as VCC1. |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

| Pin |           | I/O          | Description                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name      |              |                                                                                                                                                                                                                                                                                                                                              |

| B6  | VDAC3     | Output       | VDAC3 output.                                                                                                                                                                                                                                                                                                                                |

| C1  | SCL/ CS   | Input        | I <sup>2</sup> C: Clock input.                                                                                                                                                                                                                                                                                                               |

|     |           |              | SPI: Active-low serial data enable. This input is the frame synchronization signal for the serial data. When the signal goes low, this pin enables the serial interface input shift register.                                                                                                                                                |

| C2  | LDAC/ CLR | Input        | Active-low DAC synchronization signal. A high-to-low transition on the LDAC pin simultaneously updates the outputs of the IDACs and VDACs that are configured in synchronous mode. Alternatively, this pin can be configured as an active-low DAC clear signal to load the clear code for the IDACs or VDACs configured for a clear control. |

| C3  | GND       | Ground       | Ground reference point for all circuitry on the device.                                                                                                                                                                                                                                                                                      |

| C4  | GND       | Ground       | Ground reference point for all circuitry on the device.                                                                                                                                                                                                                                                                                      |

| C5  | ADC4      | Input        | ADC4 analog input.                                                                                                                                                                                                                                                                                                                           |

| C6  | ADC3      | Input        | ADC3 analog input.                                                                                                                                                                                                                                                                                                                           |

| D1  | SDA/SCLK  | Input/Output | I <sup>2</sup> C: Bidirectional data line. SPI: Clock input.                                                                                                                                                                                                                                                                                 |

| D2  | RESET     | Input        | Active low reset input. Logic low on this pin initiates a reset event.                                                                                                                                                                                                                                                                       |

| D3  | GND       | Ground       | Ground reference point for all circuitry on the device.                                                                                                                                                                                                                                                                                      |

| D4  | GND       | Ground       | Ground reference point for all circuitry on the device.                                                                                                                                                                                                                                                                                      |

| D5  | ADC2      | Input        | ADC2 analog input.                                                                                                                                                                                                                                                                                                                           |

| D6  | ADC1      | Input        | ADC1 analog input.                                                                                                                                                                                                                                                                                                                           |

| E1  | A0/SDI    | Input        | I <sup>2</sup> C: Slave address selector. SPI: Data input.                                                                                                                                                                                                                                                                                   |

|     |           |              | Data are clocked into the input shift register on each falling edge of the SCLK pin.                                                                                                                                                                                                                                                         |

| E2  | ALARM     | Output       | Alarm output. This pin is an open-drain, active-low output by default but can also be configured as a push-pull output or as an active-high output.                                                                                                                                                                                          |

| E3  | VDD1      | Power        | Analog supply voltage. This pin must be tied to the same potential as VDD2. And it should be powered up before VCC1/2 or PVDD1/2/3/4.                                                                                                                                                                                                        |

| E4  | PWDWN     | Input        | Active low DAC power-down input. This pin is used to power down the IDACs or VDACs configured for power-down control.                                                                                                                                                                                                                        |

| E5  | VCC1      | Power        | VDAC1~2 output buffers positive analog power supply. This pin must be tied to the same potential as VCC2.                                                                                                                                                                                                                                    |

| E6  | VDAC1     | Output       | VDAC1 output.                                                                                                                                                                                                                                                                                                                                |

| F1  | A1/SDO    | Input/Output | I <sup>2</sup> C: Slave address selector. SPI: Data output.                                                                                                                                                                                                                                                                                  |

|     |           |              | Data are clocked out of the input shift register on either rising or falling edges of the SCLK pin as specified by the FSDO bit.                                                                                                                                                                                                             |

**4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC**

| Pin |        | I/O    | Description                                                                                                                           |

|-----|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name   |        |                                                                                                                                       |

| F2  | VIO    | Power  | IO supply voltage. This pin sets the I/O operating voltage for the device.                                                            |

| F3  | VDD2   | Power  | Analog supply voltage. This pin must be tied to the same potential as VDD1. And it should be powered up before VCC1/2 or PVDD1/2/3/4. |

| F4  | REFOUT | Output | Internal reference output voltage pin.                                                                                                |

| F5  | VDAC2  | Output | VDAC2 output.                                                                                                                         |

| F6  | VSS1   | Power  | VDAC1~2 output buffers negative analog power supply. This pin must be tied to the same potential as VSS2.                             |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### Specifications

#### Absolute Maximum Ratings (1)

| Parameter                 | Min  | Max       | Unit |

|---------------------------|------|-----------|------|

| VDD to GND                | -0.3 | 6         | V    |

| Digital IO to GND         | -0.3 | VDD + 0.3 | V    |

| Analog IO to GND          | -0.3 | VDD + 0.3 |      |

| PVDD to GND               | -0.3 | VDD + 0.3 |      |

| VCC to VSS                | -0.3 | 6         |      |

| Operating Temperature     | -40  | 125       | °C   |

| Storage Temperature, Tstg |      | 6         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

#### ESD, Electrostatic Discharge Protection

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| HBM    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | 2             | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | 1             | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### Recommended Operating Conditions

| Parameter           |                                            | Min  | Typ | Max     | Unit |

|---------------------|--------------------------------------------|------|-----|---------|------|

| VDD[1,2]            | Analog Supply Voltage                      | 3    | 3.3 | 3.6     | V    |

| VIO                 | Digital IO Supply Voltage                  | 1.65 |     | 3.6     | V    |

| PVDD[1:4]           | IDAC Output Buffer Supply Voltage          | 1.5  |     | VDD-0.5 | V    |

| VCC[1,2] (1)        | VDAC Output Buffer Positive Supply Voltage | 2.5  |     | 5.5     | V    |

| VSS[1,2] (2)        | VDAC Output Buffer Negative Supply Voltage | -5.5 |     | -2.5    | V    |

| VCC[1,2] – VSS[1,2] | VDAC Output Buffer Supply Voltage          | 2.5  |     | 5.5     | V    |

| TA                  | Operating Ambient Temperature              | -40  |     | 125     | °C   |

(1) V<sub>CC[1,2]</sub> must be connected to GND when VDACS are configured for negative output voltage range operation.

(2) V<sub>SS[1,2]</sub> must be connected to GND when VDACS are configured for positive output voltage range operation.

#### Thermal Information

| Package Type | θ <sub>JA</sub> | θ <sub>Jc</sub> | Unit |

|--------------|-----------------|-----------------|------|

| WLCSP        | 57              | 0.3             | °C/W |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### Electrical Characteristics

All minimum/maximum specifications at  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$  and all typical specifications at  $T_J = 25^\circ\text{C}$ ,  $V_{DD[1,2]} = 3.0\text{ V}$  to  $3.6\text{ V}$ ,  $V_{IO} = 1.65\text{ V}$  to  $3.6\text{ V}$ ,  $PV_{DD[1,4]} = 1.5\text{ V}$  to  $V_{DD}-0.5\text{ V}$ , positive output ranges:  $V_{CC[1,2]} = 3.0\text{ V}$  to  $5.5\text{ V}$ ,  $V_{SS[1,2]} = \text{GND}$ , negative output ranges:  $V_{SS[1,2]} = -5.5\text{ V}$  to  $-3.0\text{ V}$ ,  $V_{CC[1,2]} = \text{GND}$ , and DAC outputs unloaded, unless otherwise noted.

| Parameter                              | Test Conditions                                                               | Min                        | Typ      | Max       | Unit |                       |

|----------------------------------------|-------------------------------------------------------------------------------|----------------------------|----------|-----------|------|-----------------------|

| <b>VDAC Characteristics</b>            |                                                                               |                            |          |           |      |                       |

|                                        | Resolution                                                                    | 12                         |          |           | Bits |                       |

|                                        | Full-Scale Output Voltage Range                                               | -2.5                       |          | 0         | V    |                       |

|                                        |                                                                               | -5.0                       |          | 0         | V    |                       |

|                                        |                                                                               | 0                          |          | 2.5       | V    |                       |

|                                        |                                                                               | 0                          |          | 5         | V    |                       |

| DNL                                    | Differential Nonlinearity                                                     | Specified 12-bit monotonic | -1       | $\pm 0.5$ | 1    | LSB                   |

| INL                                    | Integral Nonlinearity                                                         |                            | -4       | $\pm 2$   | 4    | LSB                   |

| TUE                                    | Total Unadjusted Error                                                        | Positive output Ranges     | -0.7     | $\pm 0.2$ | 0.7  | %FSR                  |

| OE                                     | Offset Error                                                                  | Positive output ranges     | -12      | $\pm 2$   | 12   | mV                    |

|                                        |                                                                               | Negative output ranges     | -12      | $\pm 2$   | 12   | mV                    |

|                                        | Offset Error Temperature Drift                                                | Positive output ranges     |          | $\pm 5$   |      | ppm/ $^\circ\text{C}$ |

|                                        |                                                                               | Negative output ranges     |          | $\pm 5$   |      | ppm/ $^\circ\text{C}$ |

| GE                                     | Gain Error                                                                    | Positive output ranges     | -0.5     | $\pm 0.1$ | 0.5  | %FSR                  |

|                                        |                                                                               | Negative output ranges     | -0.5     | $\pm 0.1$ | 0.5  | %FSR                  |

| ZSE                                    | Gain Error Temperature Drift                                                  | Positive output ranges     |          | $\pm 20$  |      | ppm/ $^\circ\text{C}$ |

|                                        |                                                                               | Negative output ranges     |          | $\pm 20$  |      | ppm/ $^\circ\text{C}$ |

|                                        | Zero-Scale Error                                                              | Positive output ranges     | 0        | 2         | 12   | mV                    |

|                                        |                                                                               | Negative output ranges     | -12      | -2        | 0    | mV                    |

| FSE                                    | Zero-Scale Error Temperature Drift                                            | Positive output ranges     |          | $\pm 20$  |      | ppm/ $^\circ\text{C}$ |

|                                        |                                                                               | Negative output ranges     |          | $\pm 20$  |      | ppm/ $^\circ\text{C}$ |

| CL                                     | Capacitive Load Stability <sup>(1)</sup>                                      | Positive output ranges     | -0.6     | $\pm 0.2$ | 0.6  | %FSR                  |

|                                        |                                                                               | Negative output ranges     | -0.6     | $\pm 0.2$ | 0.6  | %FSR                  |

|                                        | Full-Scale Error Temperature Drift                                            | Positive output ranges     |          | $\pm 20$  |      | ppm/ $^\circ\text{C}$ |

|                                        |                                                                               | Negative output ranges     |          | $\pm 20$  |      | ppm/ $^\circ\text{C}$ |

| RL                                     | Capacitive Load Stability <sup>(1)</sup>                                      | VDAC_CAP_LOAD=0            | 0        |           | 100  | nF                    |

|                                        |                                                                               | VDAC_CAP_LOAD=1            | 100      |           |      | nF                    |

| Output Voltage Headroom <sup>(2)</sup> | To $V_{CC[1,2]}$ , $I_{OUT} = 60\text{ mA}$ , $\Delta V_{OUT} < 5\text{ mV}$  |                            | 0.5      |           | V    |                       |

| Output Voltage Footroom <sup>(2)</sup> | To $V_{SS[1,2]}$ , $I_{OUT} = -60\text{ mA}$ , $\Delta V_{OUT} < 5\text{ mV}$ |                            | 0.5      |           | V    |                       |

| Short Circuit Current <sup>(2)</sup>   |                                                                               |                            | $\pm 75$ |           | mA   |                       |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

| Parameter |                                     | Test Conditions                                                                                                                     | Min | Typ | Max | Unit   |

|-----------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

|           | DC Small Signal Output Impedance    | Midscale code                                                                                                                       |     | 0.1 |     | Ω      |

| Ten       | Output Voltage Enable Settling Time | $R_L = 2 \text{ k}\Omega$ , $C_L = 200 \text{ pF}$ , Disable to 1/2 scale settling to $\pm 1 \text{ LSB}$                           |     | 150 |     | μs     |

| Tst       | Output Voltage Settling Time        | $R_L = 2 \text{ k}\Omega$ , $C_L = 200 \text{ pF}$ , 1/4 to 3/4 scale settling to $\pm 1 \text{ LSB}$<br>$V_{DAC\_SETTING[1:0]}=00$ |     | 30  |     | μs     |

|           | Slew Rate                           | 1/4 to 3/4 scale transition, 10% to 90%                                                                                             |     | 0.3 |     | V/μs   |

| Vn        | Output Noise                        | 0.1 Hz to 10 Hz, midscale code                                                                                                      |     | 150 |     | μVpp   |

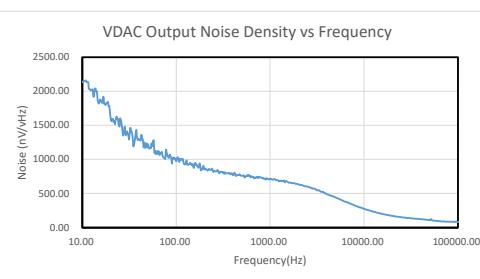

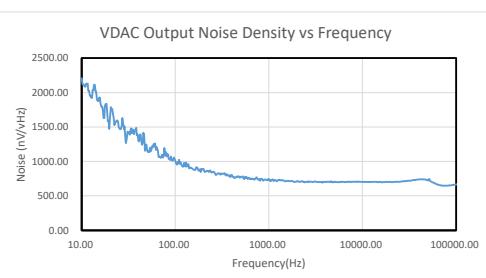

|           | Output Noise Density                | 1 kHz, midscale code                                                                                                                |     | 700 |     | nV/√Hz |

| PSRRac    | AC PSRR                             | Midscale code, frequency = 1M Hz, amplitude = 100 mV PP superimposed on VDD                                                         |     | 80  |     | dB     |

|           |                                     | Midscale code, frequency = 1M Hz, amplitude = 100 mV PP superimposed on $V_{CC[1,2]}$                                               |     | 80  |     | dB     |

|           |                                     | Midscale code, frequency = 1M Hz, amplitude = 100 mV PP superimposed on $V_{SS[1,2]}$                                               |     | 80  |     | dB     |

| PSRRdc    | DC PSRR                             | Midscale code, ±10% variation on all supplies                                                                                       |     | 0.3 |     | mV/V   |

|           | Code Change Glitch Impulse          | 1 LSB change around major carrier                                                                                                   |     | 1   |     | nV-s   |

|           | Code Change Glitch Amplitude        | 1 LSB change around major carrier                                                                                                   |     | 1   |     | mV     |

|           | Channel-to-Channel DC Crosstalk     | Measured DAC output at midscale, all other DAC outputs at full-scale                                                                |     | 100 |     | μV     |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

All minimum/maximum specifications at  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$  and all typical specifications at  $T_J = 25^\circ\text{C}$ ,  $V_{DD[1:2]} = 3.0\text{ V}$  to  $3.6\text{ V}$ ,  $V_{IO} = 1.65\text{ V}$  to  $3.6\text{ V}$ ,  $PV_{DD[1:4]} = 1.5\text{ V}$  to  $V_{DD} - 0.5\text{ V}$ , positive output ranges:  $V_{CC[1:2]} = 3.0\text{ V}$  to  $5.5\text{ V}$ ,  $V_{SS[1:2]} = \text{GND}$ , negative output ranges:  $V_{SS[1:2]} = -5.5\text{ V}$  to  $-3.0\text{ V}$ ,  $V_{CC[1:2]} = \text{GND}$ , and DAC outputs unloaded, unless otherwise noted.

| Parameter                   | Test Conditions                     | Min                                                                      | Typ  | Max        | Unit                         |

|-----------------------------|-------------------------------------|--------------------------------------------------------------------------|------|------------|------------------------------|

| <b>IDAC Characteristics</b> |                                     |                                                                          |      |            |                              |

|                             | Resolution                          | 12                                                                       | 12   | 12         | Bits                         |

|                             | Full scale output current range     | 0                                                                        |      | 200        | mA                           |

| DNL                         | Differential nonlinearity           | Specified 12-bit monotonic                                               | -1   | $\pm 0.5$  | 1                            |

| INL                         | Integral nonlinearity               |                                                                          | -3   | $\pm 1$    | 3                            |

| TUE                         | Total unadjusted error              |                                                                          | -1.5 | $\pm 0.05$ | 1.5                          |

|                             | Offset error                        |                                                                          | -1   | $\pm 0.5$  | 1                            |

|                             | Offset error temperature drift      |                                                                          |      | $\pm 10$   | $\text{ppm}/^\circ\text{C}$  |

|                             | Gain error                          |                                                                          | -1   | $\pm 0.05$ | 1                            |

|                             | Gain error temperature drift        |                                                                          |      | $\pm 20$   | $\text{ppm}/^\circ\text{C}$  |

|                             | Zero-scale error                    | 0                                                                        | 0.5  | 1          | mA                           |

|                             | Zero-scale error temperature drift  |                                                                          |      | $\pm 5$    | $\text{ppm}/^\circ\text{C}$  |

|                             | Full-scale error                    |                                                                          | -1   | $\pm 0.05$ | 1                            |

|                             | Full-scale error temperature drift  |                                                                          |      | $\pm 20$   | $\text{ppm}/^\circ\text{C}$  |

|                             | Output compliance voltage           |                                                                          |      |            | $PV_{DD} - 0.3$ V            |

|                             | Pull down resistance <sup>(2)</sup> |                                                                          | 2    |            | $\text{k}\Omega$             |

|                             | Output current settling time        | 1/4 to 3/4 scale settling to $\pm 1$ LSB                                 | 30   |            | $\mu\text{s}$                |

|                             | Slew rate                           | 1/4 to 3/4 scale transition, 10% to 90%                                  |      | 8          | $\text{mA}/\mu\text{s}$      |

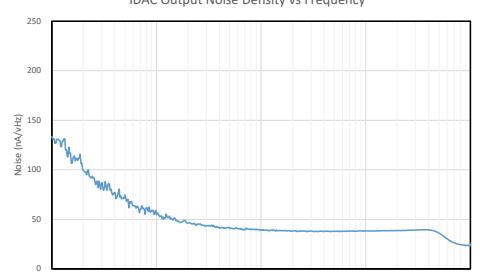

|                             | Output noise                        | 0.1 Hz to 10 Hz, midscale code (no ref)                                  |      | 2          | $\mu\text{ARMS}$             |

|                             | Output noise density                | 1 kHz, midscale code (no ref)                                            | 50   |            | $\text{nA}/\sqrt{\text{Hz}}$ |

| AC PSRR                     |                                     | Midscale code, frequency = 1M, amplitude = 20 mV PP superimposed on VDD  |      | 1000       | $\mu\text{A}/\text{V}$       |

|                             |                                     | Midscale code, frequency = 1M, amplitude = 20 mV PP superimposed on PVDD |      | 1000       | $\mu\text{A}/\text{V}$       |

|                             | DC PSRR                             | Midscale code, $\pm 10\%$ variation on all supplies                      | 80   |            | $\text{dB}$                  |

|                             | Code change glitch impulse          | 1 LSB change around major carrier                                        | 500  |            | $\text{pA}\cdot\text{s}$     |

|                             | Code change glitch amplitude        | 1 LSB change around major carrier                                        | 200  |            | $\mu\text{A}$                |

|                             | Channel-to-channel DC crosstalk     | Measured DAC output at midscale, all other DAC outputs at full-scale     | 100  |            | $\mu\text{A}$                |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

All minimum/maximum specifications at  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$  and all typical specifications at  $T_J = 25^\circ\text{C}$ ,  $V_{DD} [1,2] = 3.0\text{ V}$  to  $3.6\text{ V}$ ,  $V_{IO} = 1.65\text{ V}$  to  $3.6\text{ V}$ ,  $PV_{DD} [1:4] = 1.5\text{ V}$  to  $V_{DD}-0.5\text{ V}$ , positive output ranges:  $V_{CC} [1,2] = 3.0\text{ V}$  to  $5.5\text{ V}$ ,  $V_{SS} [1,2] = \text{GND}$ , negative output ranges:  $V_{SS} [1,2] = -5.5\text{ V}$  to  $-3.0\text{ V}$ ,  $V_{CC} [1,2] = \text{GND}$ , and DAC outputs unloaded, unless otherwise noted.

| Parameter                            | Test Conditions                            | Min                                              | Typ                 | Max                 | Unit                      |

|--------------------------------------|--------------------------------------------|--------------------------------------------------|---------------------|---------------------|---------------------------|

| <b>ADC Characteristics</b>           |                                            |                                                  |                     |                     |                           |

|                                      | Resolution                                 |                                                  | 12                  |                     | Bits                      |

|                                      | Full scale input voltage range             | 0                                                | 5                   |                     | V                         |

| $D_{NL}$                             | Differential nonlinearity                  | Specified 12-bit monotonic                       | -1.5                | $\pm 0.5$           | 3.5 LSB                   |

| $I_{NL}$                             | Integral nonlinearity                      |                                                  | -4                  | $\pm 1$             | 4 LSB                     |

|                                      | Offset error                               | After calibration                                | -6                  | $\pm 1$             | 6 LSB                     |

|                                      | Offset error match                         |                                                  |                     | $\pm 1$             | LSB                       |

|                                      | Gain error                                 |                                                  | -0.5                | $\pm 0.05$          | 0.5 %FSR                  |

|                                      | Gain error match                           |                                                  |                     | $\pm 1$             | LSB                       |

|                                      | Input capacitance                          |                                                  | 12                  |                     | pF                        |

|                                      | Input bias current                         | ADC not converting                               | 1                   |                     | $\mu\text{A}$             |

|                                      | Conversion time                            |                                                  | 0.7                 |                     | $\mu\text{s}$             |

|                                      | Acquisition time                           |                                                  | 0.3                 |                     | $\mu\text{s}$             |

|                                      | Conversion rate                            |                                                  |                     | 1                   | MSPS                      |

| <b>Sensors Characteristics</b>       |                                            |                                                  |                     |                     |                           |

|                                      | VDAC current sense gain error              |                                                  | -0.8                |                     | 0.8 %FSR                  |

|                                      | VDAC current sense offset error            | Positive output ranges                           | -0.5                | $\pm 0.1$           | 0.5 %FSR                  |

|                                      |                                            | Negative output ranges                           | -0.5                | $\pm 0.1$           | 0.5 %FSR                  |

|                                      | VDAC current sense accuracy                |                                                  |                     | $\pm 1$             | %FSR                      |

|                                      | Thermal alarm accuracy                     | $T_J = -40^\circ\text{C}$ to $150^\circ\text{C}$ |                     | $\pm 5$             | $^\circ\text{C}$          |

| <b>Reference Characteristics</b>     |                                            |                                                  |                     |                     |                           |

| $V_{REFOUT}$                         | Internal reference voltage                 | $T_A = 25^\circ\text{C}$                         | 2.492               | 2.5                 | 2.508 V                   |

|                                      | Internal reference temperature coefficient | $T_J = -40^\circ\text{C}$ to $105^\circ\text{C}$ |                     | 25                  |                           |

|                                      | Internal reference impedance               |                                                  |                     | 0.5                 | $\Omega$                  |

|                                      | Internal reference output noise            | 0.1 Hz to 10 Hz                                  |                     | 20                  | $\mu\text{V}$ PP          |

|                                      | Internal reference noise density           |                                                  |                     | 200                 | $\text{nV}/\text{sqrtHz}$ |

|                                      | Internal reference load current            |                                                  |                     | $\pm 10$            | mA                        |

|                                      | Internal reference load cap                |                                                  | 100                 |                     | nF                        |

| <b>Digital Input Characteristics</b> |                                            |                                                  |                     |                     |                           |

| $V_{IH}$                             | High-level input voltage                   |                                                  | $0.7 \times V_{IO}$ |                     | V                         |

| $V_{IL}$                             | Low-level input voltage                    |                                                  |                     | $0.3 \times V_{IO}$ | V                         |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

| Parameter                             |                                         | Test Conditions                            | Min            | Typ | Max | Unit |

|---------------------------------------|-----------------------------------------|--------------------------------------------|----------------|-----|-----|------|

|                                       | Input current                           |                                            |                | 1   |     | µA   |

|                                       | Input pin capacitance                   |                                            |                | 8   |     | pF   |

| <b>Digital Output Characteristics</b> |                                         |                                            |                |     |     |      |

| $V_{OH}$                              | High-level output voltage               | $I_{SOURCE} = 0.2 \text{ mA}$              | $V_{IO} - 0.4$ |     |     | V    |

| $V_{OL}$                              | Low-level output voltage                | $I_{SINK} = 0.2 \text{ mA}$                |                |     | 0.4 | V    |

|                                       | Output pin capacitance                  |                                            |                | 8   |     | pF   |

| $V_{OL}$                              | Open-drain low-level output voltage     | $I_{SINK} = 2 \text{ mA}$                  |                |     | 0.4 | V    |

| <b>Supply Monitor Characteristics</b> |                                         |                                            |                |     |     |      |

| $V_{CC}$ to $V_{SSTH}$                | $V_{CC}$ to $V_{SS}$ threshold detector | $V_{CC}$ to $V_{SS}$ supply failure detect |                | 2   |     | V    |

| $V_{DDTH}$                            | $V_{DD}$ threshold detector             | $V_{DD}$ supply failure detect             |                | 2   |     | V    |

| $PV_{DDTH}$                           | $PV_{DD}$ threshold detector            | $PV_{DD}$ supply failure detect            |                | 1.3 |     | V    |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

All minimum/maximum specifications at  $T_J = -40^\circ\text{C}$  to  $+125^\circ\text{C}$  and all typical specifications at  $T_J = 25^\circ\text{C}$ ,  $V_{DD[1,2]} = 3.0\text{ V}$  to  $3.6\text{ V}$ ,  $V_{IO} = 1.65\text{ V}$  to  $3.6\text{ V}$ ,  $PV_{DD[1:4]} = 1.5\text{ V}$  to  $V_{DD} - 0.5\text{ V}$ , positive output ranges:  $V_{CC[1,2]} = 3.0\text{ V}$  to  $5.5\text{ V}$ ,  $V_{SS[1,2]} = \text{GND}$ , negative output ranges:  $V_{SS[1,2]} = -5.5\text{ V}$  to  $-3.0\text{ V}$ ,  $V_{CC[1,2]} = \text{GND}$ , and DAC outputs unloaded, unless otherwise noted.

| Parameter                                |                                     | Test Conditions                                                                                                                                  | Min  | Typ   | Max  | Unit          |

|------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|---------------|

| <b>Power Consumption Characteristics</b> |                                     |                                                                                                                                                  |      |       |      |               |

| $I_{VDD}$                                | $V_{DD}$ supply current             | No DAC load, VDACs in positive range at midscale code, IDACs at zero-scale, ADC at the fastest auto conversion rate, and static serial interface |      | 7     | 9    | mA            |

| $I_{VCC[1,2]}$                           | $V_{CC}$ supply current per channel |                                                                                                                                                  |      | 2     | 3.5  | mA            |

| $I_{PVDD}$                               | $PVDD$ supply current               |                                                                                                                                                  |      | 0.1   | 0.15 | mA            |

| $I_{VIO}$                                | $V_{IO}$ supply current             |                                                                                                                                                  |      | 1     | 10   | $\mu\text{A}$ |

| $I_{VDD}$                                | $V_{DD}$ supply current             | No DAC load, VDACs in negative range at midscale code, IDACs at zero-scale, ADC at the fastest auto conversion rate, and static serial interface |      | 7     | 9    | mA            |

| $I_{VSS}$                                | $V_{SS}$ supply current             |                                                                                                                                                  |      | 2     | 3.5  | mA            |

| $I_{PVDD}$                               | $PVDD$ supply current               |                                                                                                                                                  |      | 0.1   | 0.15 | mA            |

| $I_{VIO}$                                | $V_{IO}$ supply current             |                                                                                                                                                  |      | 1     | 10   | $\mu\text{A}$ |

| $I_{VDD}$                                | $V_{DD}$ supply current             | ALL DACs in Power-down mode, VDACs in positive range                                                                                             |      | 2.1   | 3    | mA            |

| $I_{VCC}$                                | $V_{CC}$ supply current             |                                                                                                                                                  |      | 0.06  | 1    | mA            |

| $I_{PVDD}$                               | $PVDD$ supply current               |                                                                                                                                                  |      | 0.005 | 0.01 | mA            |

| $I_{VIO}$                                | $V_{IO}$ supply current             |                                                                                                                                                  |      | 1     | 10   | $\mu\text{A}$ |

| $I_{VDD}$                                | $V_{DD}$ supply current             | ALL DACs in Power-down mode, VDACs in negative range                                                                                             |      | 2.6   | 3    | mA            |

| $I_{VSS}$                                | $V_{SS}$ supply current             |                                                                                                                                                  | -0.7 | -0.5  |      | mA            |

| $I_{PVDD}$                               | $PVDD$ supply current               |                                                                                                                                                  |      | 0.005 | 0.01 | mA            |

| $I_{VIO}$                                | $V_{IO}$ supply current             |                                                                                                                                                  |      | 1     | 10   | $\mu\text{A}$ |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

All minimum/maximum specifications at  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and all typical specifications at  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD[1,2]} = 3.0\text{ V}$  to  $3.6\text{ V}$ ,  $V_{IO} = 1.65\text{ V}$  to  $3.6\text{ V}$ ,  $PV_{DD[1,4]} = 1.5\text{ V}$  to  $V_{DD}-0.5\text{ V}$ , positive output ranges:  $V_{CC[1,2]} = 3.0\text{ V}$  to  $5.5\text{ V}$ ,  $V_{SS[1,2]} = \text{GND}$ , negative output ranges:  $V_{SS[1,2]} = -5.5\text{ V}$  to  $-3.0\text{ V}$ ,  $V_{CC[1,2]} = \text{GND}$ , and DAC outputs unloaded, unless otherwise noted.

| Parameter                    | Test Conditions               | Min                                                                           | Typ | Max | Unit          |

|------------------------------|-------------------------------|-------------------------------------------------------------------------------|-----|-----|---------------|

| <b>Reset Characteristics</b> |                               |                                                                               |     |     |               |

| $t_{AMCRDY}$                 | Device ready wait time        | Time for valid serial interface access, measured from reset event             |     | 100 | $\mu\text{s}$ |

| $t_{RESET}$                  | RESET pulse width             |                                                                               | 20  |     | ns            |

| <b>DAC Characteristics</b>   |                               |                                                                               |     |     |               |

|                              | IDAC power-down response time | Measured from alarm condition, DAC outputs unloaded                           | 100 |     | ns            |

| $t_{DACPWD}$                 | VDAC power-down response time |                                                                               | 0.5 |     | $\mu\text{s}$ |

|                              | VDAC clear response time      | Measured from CLEAR trigger, DAC outputs unloaded                             | 150 |     | ns            |

| $t_{DACCCLR}$                | IDAC clear response time      |                                                                               | 2   |     | $\mu\text{s}$ |

| $t_{CLRWDTH}$                | CLEAR pulse width             |                                                                               | 20  |     | ns            |

| $t_{LDACWDT H}$              | LDAC pulse width              |                                                                               | 20  |     | ns            |

| <b>ADC Characteristics</b>   |                               |                                                                               |     |     |               |

| $t_{ADCWAIT}$                | ADC wait time                 | Time from when the ADC enters IDLE state to when the ADC is ready for trigger |     | 2   | $\mu\text{s}$ |

| $t_{ALMOUT}$                 | ALARM response time           | Measured from analog input out-of-range alarm condition                       |     | 20  | $\mu\text{s}$ |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

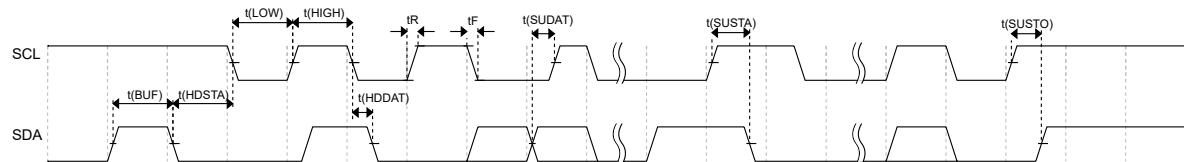

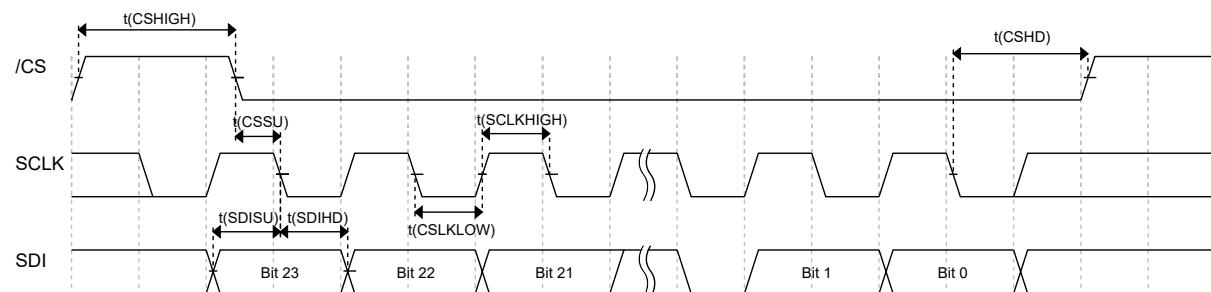

### Timing Requirements

All minimum/maximum specifications at  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and all typical specifications at  $T_J = 25^{\circ}\text{C}$ ,  $V_{DD[1:2]} = 3.0\text{ V}$  to  $5.5\text{ V}$ ,  $V_{IO} = 1.65\text{ V}$  to  $5.5\text{ V}$ ,  $PV_{DD[1:4]} = 1.3\text{ V}$  to  $5.5\text{ V}$ , positive output ranges:  $V_{CC[1:2]} = 3.0\text{ V}$  to  $5.5\text{ V}$ ,  $V_{SS[1:2]} = \text{GND}$ , negative output ranges:  $V_{SS[1:2]} = -5.5\text{ V}$  to  $-3.0\text{ V}$ ,  $V_{CC[1:2]} = \text{GND}$ , and DAC outputs unloaded, unless otherwise noted.

| Parameter                                 | Min                                                                                       | Typ | Max  | Unit |

|-------------------------------------------|-------------------------------------------------------------------------------------------|-----|------|------|

| <b>I<sup>2</sup>C Timing Requirements</b> |                                                                                           |     |      |      |

| $f_{(\text{SCL})}$                        | I <sup>2</sup> C Clock Frequency                                                          | 10  | 400  | kHz  |

| $t_{(\text{LOW})}$                        | SCL Clock Low Period                                                                      | 1.3 |      | μs   |

| $t_{(\text{HIGH})}$                       | SCL Clock High Period                                                                     | 0.6 |      | μs   |

| $t_{(\text{HDSTA})}$                      | Hold time after repeated start condition. After this period, the first clock is generated | 0.6 |      | μs   |

| $t_{(\text{SUSTA})}$                      | Repeated Start Condition Setup Time                                                       | 0.6 |      | μs   |

| $t_{(\text{SUSTO})}$                      | Stop Condition Setup Time                                                                 | 0.6 |      | μs   |

| $t_{(\text{BUF})}$                        | Bus Free Time between Stop and Start Condition                                            | 1.3 |      | μs   |

| $t_{(\text{SUDAT})}$                      | Data Setup Time                                                                           | 100 |      | ns   |

| $t_{(\text{HDDAT})}$                      | Data Hold Time                                                                            | 0   | 900  | ns   |

| $t_{F,SDA}$                               | Data Fall Time                                                                            | 20  | 300  | ns   |

| $t_{F,SCL}$                               | Clock Fall Time                                                                           |     | 300  | ns   |

| $t_{R,SCL}$                               | Clock Rise Time                                                                           |     | 300  | ns   |

| $t_{R,SCL100}$                            | Rise Time for SCL $\leq 100\text{ kHz}$                                                   |     | 1000 | ns   |

|                                           | SCL and SDA Timeout                                                                       | 20  | 30   | ms   |

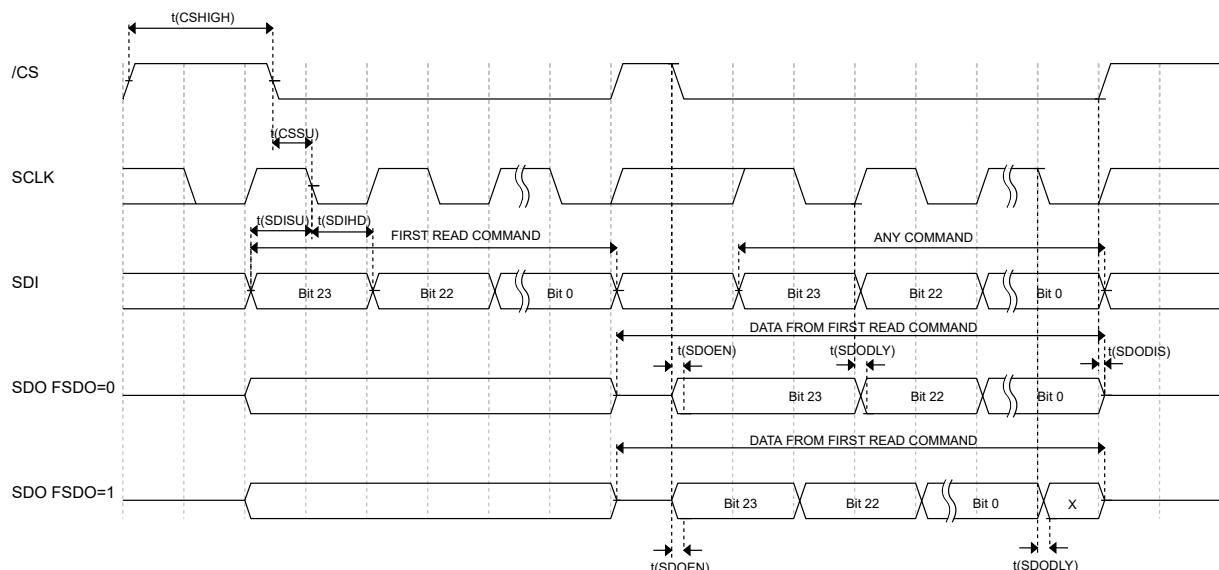

| <b>SPI Timing Requirements</b>            |                                                                                           |     |      |      |

| $f_{(\text{SCLK})}$                       | SCLK Frequency                                                                            |     | 20   | MHz  |

| $t_{(\text{SCLKHIGH})}$                   | SCLK High Time                                                                            | 23  |      | ns   |

| $t_{(\text{SCLKLOW})}$                    | SCLK Low Time                                                                             | 23  |      | ns   |

| $t_{(\text{SDISU})}$                      | SDI Setup Time                                                                            | 7   |      | ns   |

| $t_{(\text{SDIH})}$                       | SDI Hold Dime                                                                             | 7   |      | ns   |

| $t_{(\text{SDOTOZ})}$                     | SDO Driven to Tri-State                                                                   | 0   | 15   | ns   |

| $t_{(\text{SDOTOD})}$                     | SDO Tri-state to Driven                                                                   | 0   | 18   | ns   |

| $t_{(\text{SDODLY})}$                     | SDO Output Delay                                                                          | 0   | 30   | ns   |

| $t_{(\text{CSSU})}$                       | CS Setup Time                                                                             | 10  |      | ns   |

| $t_{(\text{CSHD})}$                       | CS Hold Time                                                                              | 20  |      | ns   |

| $t_{(\text{CSHIGH})}$                     | CS High Time                                                                              | 20  |      | ns   |

(1) Values based on design and characterization.

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### Timing Diagrams

**Figure 1. I<sup>2</sup>C Timing Diagram**

**Figure 2. SPI Write Timing Diagram**

**Figure 3. SPI Read Timing Diagram**

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

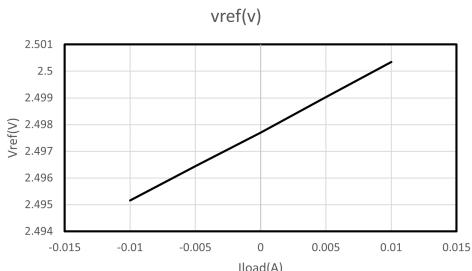

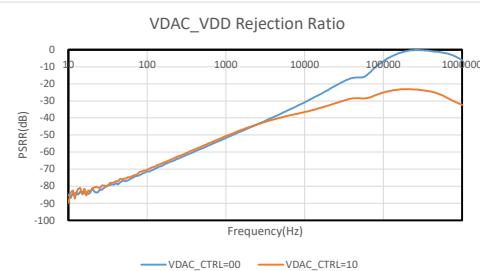

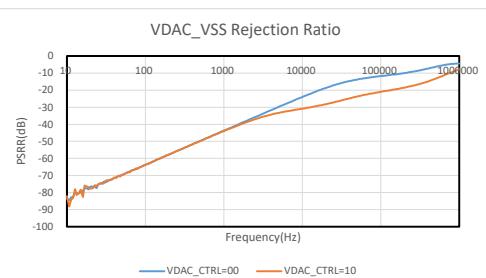

### Typical Performance Characteristics

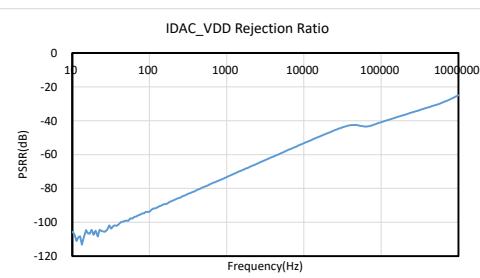

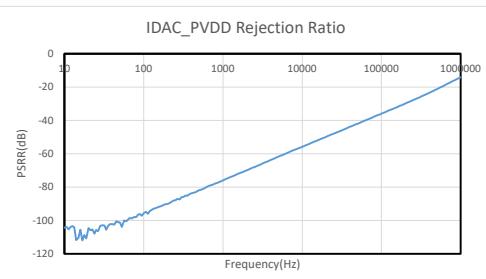

All test condition:  $V_{DD[1,2]} = 5$  V,  $V_{IO} = 3.3$  V,  $PV_{DD[1:4]} = 3$  V, positive output ranges:  $V_{CC[1,2]} = 3.0$  V to 5.5 V,  $V_{SS[1,2]} = GND$ , negative output ranges:  $V_{SS[1,2]} = -5$  V,  $V_{CC[1,2]} = GND$ , unless otherwise noted.

**Figure 4. VREF VS Load Current**

**Figure 5. VDAC Rejection versus VDD**

**Figure 6. VDAC Rejection versus VSS**

**Figure 7. IDAC Rejection versus VDD**

**Figure 8. IDAC Rejection versus PVDD**

**Figure 9. VDAC Noise with Cload=1**

**Figure 10. VDAC Noise with Cload=0**

**Figure 11. IDAC Noise at 200mA**

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### Detailed Description

#### Overview

The TPAFEA008 is an integrated product with 4-channel negative/positive output VDAC and 4-channel IDAC, which is optimized for the optical module with 4-channel EML (Electro-absorption Modulated Laser).

#### Functional Block Diagram

Figure 12. Functional Block Diagram

### Feature Description

#### IDAC

The device has 4-ch IDACs.

For larger output current requirement, two or more IDAC outputs can be connected.

IDAC full range is 200 mA.

$$I_{DAC} = \frac{IDAC_{CODE}}{2^{12}} \times FSR \quad (1)$$

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### VDAC

The device has 4-ch VDACs which support negative or positive output range.

VDAC output current could be monitored by ADC. The full range can be configured to be 60 mA or 30 mA.

For positive output, FSR can be selected as 2.5/5 V, and VDAC equation is as followings:

$$V_{DAC} = \frac{VDAC_{CODE}}{2^{12}} \times FSR \quad (2)$$

For negative output, FSR can be selected as -2.5/-5 V, and VDAC equation is as followings:

$$V_{DAC} = \frac{VDAC_{CODE} - 2^{12}}{2^{12}} \times FSR \quad (3)$$

### ADC

The ADC has 4 pins to monitor external signals and can monitor the output voltage of IDAC as well as the output current of VDAC.

For external ADC input, ADC equation is as followings, and ADC range is 2.5 V or 5 V according to register setting:

$$ADC_{CODE} = \frac{ADC_{input}}{ADC_{RANGE}} \times 2^{12} \quad (4)$$

For output voltage of IDAC, ADC equation is as followings, and ADC range is 2.5 V:

$$V_{IDAC} = \frac{ADC_{CODE}}{2^{12}} \times ADC_{RANGE} \quad (5)$$

For output current of VDAC, ADC equation is as followings:

In 30 mA range:

$$I_{VDAC} = \frac{2.5}{83.31} \times \frac{ADC_{CODE}}{2^{12}} \quad (6)$$

In 60 mA range:

$$I_{VDAC} = \frac{2.5}{41.66} \times \frac{ADC_{CODE}}{2^{12}} \quad (7)$$

### Internal Reference

The device has an internal 2.5-V reference.

### Alarm Function

The device has several alarm functions, including ADC alarm, overtemperature alarm, etc.

### Serial Interface

The TPA08A008 supports either I<sup>2</sup>C-compatible two-wire bus, or an SPI-compatible bus. The device detects between an SPI-compatible or I<sup>2</sup>C -compatible master at startup, and automatically configures the interface accordingly. Protocol change during normal operation should be prevented.

The TPA08A008 has 3 pages of registers. Address 0x01 is used to select the different pages in both SPI and I<sup>2</sup>C configurations. The page for that register must first be selected to read and write. by writing the 5-bit representation of the page number (PAGE<sub>[4:0]</sub>) to address 0x01. The page value is held until a new page address is programmed.

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

Addresses 0x00 to 0x2F on each page are global registers, thus enabling access to these bits regardless of the page configuration.

### I<sup>2</sup>C Interface

In I<sup>2</sup>C mode, the device works as a slave device. The device supports the transmission protocol for fast mode. All data bytes are transmitted MSB first.

### I<sup>2</sup>C Bus Overview

In I<sup>2</sup>C protocol, the device that initiates the transfer is called a master, and the devices controlled by the master are slaves.

### I<sup>2</sup>C Address

The device has 4 slave addresses, which are selected by connecting the A0 and A1 pins to the VIO or GND.

**Table 2. I<sup>2</sup>C Slave Address**

| A1 | A0 | Address <sub>[A6:A0]</sub> |

|----|----|----------------------------|

| 0  | 0  | 1000000                    |

| 0  | 1  | 1000001                    |

| 1  | 0  | 1000010                    |

| 1  | 1  | 1000011                    |

### I<sup>2</sup>C Read and Write Operation

General I<sup>2</sup>C read and write operations are supported by the device.

In the write operation, the value for the address register is the first byte transferred after the slave address byte with the R/W bit low.

In the read operation, the last value stored in the address register by a write operation is used to determine which register is read.

Reads can be repeated on the same register, and there is no need to continually send the address registerBytes.

A not-acknowledge command should be sent by master to terminate read operations at the end of the last byte to be read. At the last byte that is read from slave, the master should leave the SDA line high during the acknowledge time.

Block access functionality is provided by the device for large read and write sets. By setting the block access bit ( bit 7 of register address byte ) high, block access is enabled for multibyte transfers. The device reads and writes the subsequent memory locations until the transaction is terminated by the STOP condition.

### I<sup>2</sup>C Timeout Function

If either SCL or SDA are held low for 25 ms (typical) between a START and STOP condition, the device resets the serial interface, releases the bus, and waits for a START condition.

To avoid activating the time-out function, make sure to maintain SCL operating frequency of at least 1 kHz.

### I<sup>2</sup>C General-Call Reset

The device acknowledges the general-call address 00h (0000 0000b) and responds to the second byte. If the second byte is 06h (0000 0110b), the device executes a software reset.

### SPI interface

In SPI mode, the device is controlled through a four-wire serial interface.

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

### SPI Bus Overview

A serial interface access cycle is initiated by asserting the CS pin low and is 24 bits long. The access cycle ends when the CS pin is asserted high, so the CS pin must stay low for at least 24 SCLK falling edges.

The communication is ignored if the access cycle contains less than the minimum clock edges. The last 24 bits are used by the device if the access cycle contains more than the minimum clock edges.

When CS is high, the SCLK and SDI signals are blocked and the SDO pin is in a Hi-Z state.

SDI data are clocked in on SCLK falling edges.

Data are clocked out on the SDO pin on SCLK rising or falling edges, according to the FSDO bit setting.

## Register Table

### Global Register Page

There are 3 pages for TPAFEA008 register,. 1st is Global register page, 2nd is DAC register page and 3rd is ADC register page. DAC and ADC register pages are selected by PAGE\_SEL bit.

In DAC register page, configuration registers can be set to select different range and output channels, while the followings are DAC data registers.

In ADC register page, configuration registers can be set to select different input channels, while the followings are ADC data registers.

| Address | RegName        | Width | Bit     | FieldName   | R/W | ResetValue | Description                                                                                           |

|---------|----------------|-------|---------|-------------|-----|------------|-------------------------------------------------------------------------------------------------------|

| 0x00    | NOP            | 16    | [15:0]  | NOP         | WO  | 0          | no operation register.<br>Always read 0;                                                              |

| 0x01    | PAGE           | 16    | [15:2]  | RESERVED    | RO  | 0          | reserved                                                                                              |

|         |                |       | [1:0]   | PAGE_SEL    | RW  | 0          | 0: DAC page sel;<br>1: ADC page sel;                                                                  |

| 0x02    | CHIP_ID        | 16    | [15:0]  | CHIP_ID     | RO  | 16'hA008   | CHIP_ID                                                                                               |

| 0x03    | CHIP_VER       | 16    | [15:4]  | RESERVED    | RO  | 0          | reserved                                                                                              |

|         |                |       | [3:0]   | VERSION_ID  | RO  | 0          | VERSION ID                                                                                            |

| 0x04    | SW_RST         | 16    | [15:8]  | RESERVED    | RO  | 0          | reserved                                                                                              |

|         |                |       | [7:0]   | SW_RST      | RW  | 0          | Writing 0xA5 to this register causes a power-on-reset.                                                |

| 0x08    | ALARM_ST<br>S0 | 16    | [15:12] | RESERVED    | RO  | 0          | reserved                                                                                              |

|         |                |       | [11:8]  | ADC_ALR     | RO  | 0          | 0 = corresponding ADC channel is in the normal range<br>1 = corresponding ADC channel is out-of-range |

|         |                |       | [7:4]   | IDAC_ALR    | RO  | 0          |                                                                                                       |

|         |                |       | [3:0]   | VDAC_ALR    | RO  | 0          |                                                                                                       |

| 0x09    | ALARM_ST<br>S1 | 16    | [15:8]  | RESERVED    | RO  | 0          | reserved                                                                                              |

|         |                |       | [7]     | OTP_ERR_ALR | RO  | 0          | 1: idac temperature is over 150°C<br>0: idac temperature is under 150°C                               |

**4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC**

| Address | RegName | Width | Bit     | FieldName     | R/W | ResetValue | Description                                                                                                       |

|---------|---------|-------|---------|---------------|-----|------------|-------------------------------------------------------------------------------------------------------------------|

| 0x0A    | GLB_STS | 16    | [6]     | OTP_WARN_ALR  | RO  | 0          | 1: idac temperature is over 105°C<br>0: idac temperature is under 105°C                                           |

|         |         |       | [5]     | VCC2_VSS2_ALR | RO  | 0          | 1: Voltage range from VSS to VCC is smaller than the threshold<br>0: Voltage range from VSS to VCC is normal      |

|         |         |       | [4]     | VCC1_VSS1_ALR | RO  | 0          | 1: PVDD-n is no less than the PVDD threshold voltage<br>0: PVDD-n is less than the PVDD threshold voltage         |

|         |         |       | [3]     | PVDD4_ALR     | RO  | 0          | 1: PVDD-n is less than the PVDD threshold voltage                                                                 |

|         |         |       | [2]     | PVDD3_ALR     | RO  | 0          | 1: PVDD-n is less than the PVDD threshold voltage                                                                 |

|         |         |       | [1]     | PVDD2_ALR     | RO  | 0          | 1: PVDD-n is less than the PVDD threshold voltage                                                                 |

|         |         |       | [0]     | PVDD1_ALR     | RO  | 0          | 1: PVDD-n is less than the PVDD threshold voltage                                                                 |

|         |         |       | [15:12] | RESERVED      | RO  | 0          | reserved                                                                                                          |

|         |         |       | [11:8]  | VDAC_SC       | RO  | 0          | 0 = The corresponding vdac has no short circuit detected<br>1 = The corresponding vdac has short circuit detected |

|         |         |       | [7]     | ADC_BUSY      | RO  | 0          | 0 = ADC is not working; 1 = ADC is working                                                                        |

|         |         |       | [6]     | RESERVED      | RO  | 0          | reserved                                                                                                          |

|         |         |       | [5]     | VCC_VSS_GALR  | RO  | 0          | 1: at least one vcc_vss has alarm event<br>0: no vcc_vss alarm event happened                                     |

|         |         |       | [4]     | PVDD_GALR     | RO  | 0          | 1: at least one pvdd has alarm event<br>0: no pvdd alarm event happened                                           |

|         |         |       | [3]     | VDAC_GALR     | RO  | 0          | 1: at least one vdac has alarm event<br>0: no vdac alarm event happened                                           |

|         |         |       | [2]     | IDAC_GALR     | RO  | 0          | 1: at least one idac has alarm event<br>0: no idac alarm event happened                                           |

|         |         |       | [1]     | ADC_GLAR      | RO  | 0          | 1: at least one adc external channel has alarm event                                                              |

## 4-Channel EML Monitor and Controller with Positive/Negative Voltage and Current DAC

| Address | RegName | Width | Bit    | FieldName       | R/W | ResetValue | Description                                                                                                                                                                                                                 |

|---------|---------|-------|--------|-----------------|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |         |       |        |                 |     |            | 0: no adc external channel alarm event happened                                                                                                                                                                             |