### **Features**

18-bit SAR ADC without Zero Latency

Throughput Speed: 300 KSPS

Unipolar, Differential Analog Input

– -VREF to VREF

External VREF

2.5 V to VDD

High Linearity

DNL: ±0.6 LSB Typical

- INL: ±2 LSB Typical

THD: -110 dB Typical at 1 kHz

· High Dynamic Range and Noise Performance

- SNR: 96 dB Typical at 1 kHz

Dynamic Range: 96 dB Typical at 1 kHz

· Serial Interface:

SPI Compatible

· Daisy-Chain is Supported

• Wide Operating Temperature Range:

— −40°C to +125°C

Package: MSOP10

### **Applications**

- Data Acquisitions

- Instruments

- · Industry Measurement and Control

- Medical Equipment

- Automatic Test Equipment

### **Description**

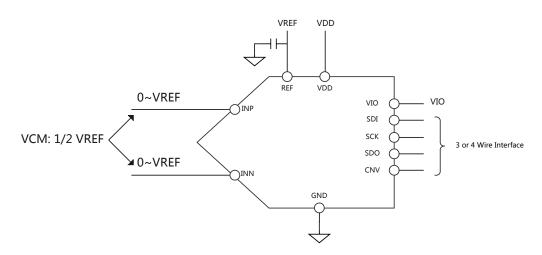

The TPC5180 is an 18-bit analog-to-digital converter (ADC). The device supports unipolar, differential input, and the input range -VREF ~VREF with a common mode voltage of VREF/2.

The device operates with a 2.5 V to VDD external reference.

The device offers an SPI-compatible interface and supports daisy-chain operation for multiple device applications.

The devices also offer an optional busy indicator bit, which can be used to synchronize with the host.

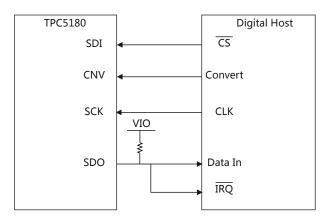

### **Typical Application Circuit**

www.3peak.com 1 / 22 BA20231001A0

## **Table of Contents**

| Features                                | 1  |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Product Family Table                    | 3  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Specifications                          | 5  |

| Absolute Maximum Ratings <sup>(1)</sup> | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Recommended Operating Conditions        | 5  |

| Thermal Information                     | 5  |

| Electrical Characteristics              | 6  |

| Timing Requirements <sup>(1)</sup>      | 8  |

| Typical Performance Characteristics     | 9  |

| Detailed Description                    | 10 |

| Overview                                | 10 |

| Functional Block Diagram                | 10 |

| Feature Description                     | 11 |

| Tape and Reel Information               | 19 |

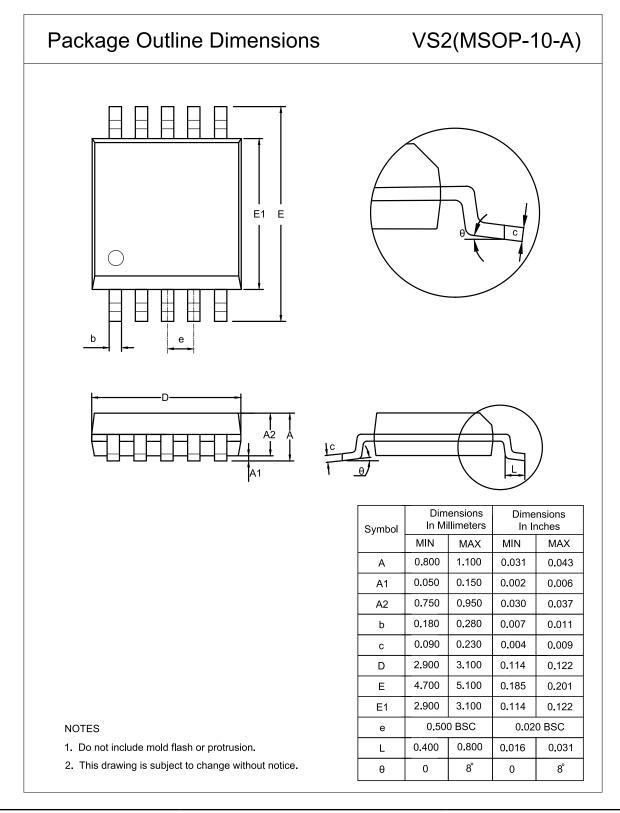

| Package Outline Dimensions              | 20 |

| MSOP10                                  | 20 |

| Order Information                       | 21 |

| IMPORTANT NOTICE AND DISCLAIMER         | 22 |

# **Product Family Table**

| Order Number | Resolution | Input Range                      | Throughput Speed | Package |

|--------------|------------|----------------------------------|------------------|---------|

| TPC5180-VS2R | 18         | -VREF~VREF<br>Fully Differential | 300K SPS         | MSOP10  |

| TPC5160-VS2R | 16         | -VREF~VREF<br>Fully Differential | 600K SPS         | MSOP10  |

| TPC5161-VS2R | 16         | 0~VREF<br>Pseudo Differential    | 600K SPS         | MSOP10  |

# **Revision History**

| Date       | Revision | Notes            |

|------------|----------|------------------|

| 2023-09-26 | Rev.A.0  | Initial release. |

www.3peak.com 3 / 22 BA20231001A0

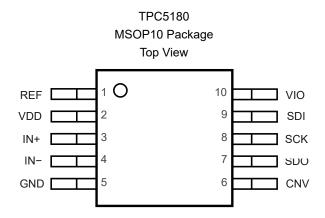

# **Pin Configuration and Functions**

Table 1. Pin Functions: TPC5180

| Р   | in   | 1/0                                                            | De contesti e c                                                                                                                                                                                                    |

|-----|------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Name | I/O                                                            | Description                                                                                                                                                                                                        |

| 1   | REF  | 1                                                              | Reference voltage.                                                                                                                                                                                                 |

| 2   | VDD  | 0                                                              | Power supply.                                                                                                                                                                                                      |

| 3   | IN+  | 0                                                              | Positive analog Input.                                                                                                                                                                                             |

| 4   | IN-  | I                                                              | Negative analog Input.                                                                                                                                                                                             |

| 5   | GND  | – Power Ground.                                                |                                                                                                                                                                                                                    |

| 6   | CNV  |                                                                | Conversion input. It initiates the conversions of the device and selects the interface mode together with SDI.  1. Chain mode: SDI is low during CNV rising edge.  2. CS mode: SDI is high during CNV rising edge. |

| 7   | SDO  |                                                                | Serial Data output.                                                                                                                                                                                                |

| 8   | SCK  | Serial Data clock.                                             |                                                                                                                                                                                                                    |

| 9   | SDI  | Serial Data input. It selects the serial mode together with CN |                                                                                                                                                                                                                    |

| 10  | VIO  |                                                                | Digital interface power.                                                                                                                                                                                           |

www.3peak.com 4 / 22 BA20231001A0

### **Specifications**

### Absolute Maximum Ratings (1)

|                     | Parameter                           | Min  | Max       | Unit |

|---------------------|-------------------------------------|------|-----------|------|

| A mala m V (alta ma | IN+, IN- to GND                     | -0.3 | VDD + 0.3 | V    |

| Analog Voltage      | VREF to GND                         | -0.3 | VDD + 0.3 | ٧    |

| Dinital Malkana     | Digital Inputs to GND               | -0.3 | VIO + 0.3 | V    |

| Digital Voltage     | Digital Outputs to GND              | -0.3 | VIO + 0.3 | V    |

| 0 1 1/ 11           | VDD to GND                          | -0.3 | 6         | V    |

| Supply Voltage      | VIO to GND                          | -0.3 | VDD+0.3   | V    |

| TJ                  | Maximum Junction Temperature        | -40  | 150       | °C   |

| T <sub>A</sub>      | Operating Temperature Range         | -40  | 125       | °C   |

| T <sub>STG</sub>    | Storage Temperature Range           |      | 150       | °C   |

| TL                  | Lead Temperature (Soldering 10 sec) |      | 260       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum Level | Unit |

|--------|--------------------------|----------------------------|---------------|------|

| НВМ    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 (1) | 2             | kV   |

| CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 (2) | 1.5           | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

| Parameter        | Min  | Тур | Max | Unit |

|------------------|------|-----|-----|------|

| VDD              | 4.5  | 5   | 5.5 | V    |

| V <sub>REF</sub> | 3    | 5   | VDD | V    |

| VIO              | 1.71 | 3.3 | VDD | V    |

#### **Thermal Information**

| Package Type | θυΑ | θυς | Unit |

|--------------|-----|-----|------|

| MSOP10       | 125 | 48  | °C/W |

www.3peak.com 5 / 22 BA20231001A0

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **Electrical Characteristics**

All test conditions: VDD = 5 V, VIO = 1.71 V to 5 V,  $T_A = -40^{\circ}$ C to +125°C, unless otherwise noted.

| Parameter                                 | Test conditions                            |             | Min          | Тур   | Max          | Unit   |

|-------------------------------------------|--------------------------------------------|-------------|--------------|-------|--------------|--------|

| AC Accuracy <sup>(1)</sup>                |                                            |             |              |       |              |        |

| CND                                       | fin _ 4 kl l=                              | REF = 5 V   | 93           | 96    |              | dB     |

| SNR                                       | fin = 1 kHz                                | REF = 3 V   |              | 92    |              | dB     |

| OINAB                                     | c 4111                                     | REF = 5 V   |              | 95    |              | dB     |

| SINAD                                     | fin = 1 kHz                                | REF = 3 V   |              | 91.5  |              | dB     |

| D                                         | £ 4 1.1 1                                  | REF = 5 V   |              | 96    |              | dB     |

| Dynamic Range                             | fin = 1 kHz                                | REF = 3 V   |              | 92    |              | dB     |

| THD                                       | fin = 1 kHz                                | REF = 5 V   |              | -110  |              | dB     |

| SFDR                                      | fin = 1 kHz                                | REF = 5 V   |              | -108  |              | dB     |

| DC Accuracy                               |                                            |             |              |       |              |        |

| Resolution                                | NO missing code                            |             | 18           |       |              | Bits   |

| D. II                                     | REF = 5 V                                  |             | -0.99        | ±0.6  | 1.1          |        |

| DNL                                       | REF = 3 V                                  |             |              | ±0.6  |              | LSB    |

|                                           | REF = 5 V                                  |             | -8           | ±2    | 8            | 1.00   |

| INL                                       | REF = 3 V                                  |             |              | ±2    |              | LSB    |

| Gain Error                                | REF = 5 V                                  |             | -36          | ±16   | 36           | LSB    |

| Gain Error Drift                          |                                            |             |              | ±0.35 |              | ppm/°C |

| Zero Code Error                           | REF = 5 V                                  |             | -18          | ±1.5  | 18           | LSB    |

| Zero Code Error Drift                     |                                            |             |              | ±0.35 |              | ppm/°C |

| Power Supply Sensitivity                  | AVDD +/-5%                                 |             |              | 70    |              | dB     |

| Analog Input                              |                                            |             |              |       |              |        |

| Voltage Range                             | IN+ - IN-                                  |             | -VREF        |       | VREF         | V      |

| Common Mode Input<br>Range <sup>(1)</sup> |                                            |             | VREF/2 – 0.1 |       | VREF/2 + 0.1 |        |

| 0 ( 1 1)// 11                             | IN+                                        |             | -0.1         |       | VREF+0.1     | V      |

| Operating Input Voltage                   | IN-                                        |             | -0.1         |       | VREF+0.1     | V      |

| Analog Input CMRR                         | fin = 10 kHz                               |             |              | 84    |              | dB     |

| Leakage Current at 25°C                   |                                            |             |              | 1     |              | nA     |

| Input Capacitance                         |                                            |             |              | 33    |              | pF     |

| Throughput                                |                                            |             |              |       |              |        |

| 0                                         | VIO ≥ 2.3 V up to 89<br>above 85°C up to 1 |             | 0            | 0.3   |              | MHz    |

| Conversion Rate                           | VIO ≥ 1.71 V, VIO ≤ 125°C                  | 3.3 V up to |              | 0.3   |              | MHz    |

| Acquisition Time                          |                                            |             |              | 1.7   |              | us     |

www.3peak.com 6 / 22 BA20231001A0

| Parameter                                    | Test con                 | ditions                    | Min            | Тур                 | Max             | Unit |

|----------------------------------------------|--------------------------|----------------------------|----------------|---------------------|-----------------|------|

| Conversion time                              |                          |                            |                | 1.63                |                 | us   |

| Transient Response                           |                          |                            |                | 1.7                 |                 | us   |

| Reference                                    |                          |                            |                |                     |                 |      |

| REFERENCE                                    |                          |                            | 2.5            |                     | VDD             | V    |

| Voltage Range                                |                          |                            | 2.5            |                     | VDD             | V    |

| REFERENCE                                    | 300 KSPS,                |                            |                | 130                 |                 | uA   |

| Load Current                                 | REF = 5 V                |                            |                |                     |                 | G, ( |

| Sampling Dynamics                            |                          |                            |                |                     |                 |      |

| -3dB BW                                      |                          |                            |                | 20                  |                 | MHz  |

| Aperture Delay                               |                          |                            |                | 4                   |                 | ns   |

| Digital Input                                |                          | _                          |                |                     |                 |      |

| V <sub>IH</sub>                              | VIO > 3 V                |                            | 0.7*VIO        |                     |                 | V    |

| V <sub>IL</sub>                              | VIO > 3 V                |                            |                |                     | 0.3*VIO         | V    |

| VIH                                          | VIO <= 3 V               |                            | 0.7*VIO        |                     |                 | V    |

| V <sub>IL</sub>                              | VIO <= 3 V               |                            |                |                     | 0.3*VIO         | V    |

| Іін                                          | input current            |                            | -1             |                     | 1               | uA   |

| I <sub>IL</sub>                              | input current            |                            | -1             |                     | 1               | uA   |

| Digital Output                               |                          |                            |                |                     |                 |      |

| Data Format                                  |                          |                            | Seria          | al 18bit straight b | inary           |      |

| Dinalina Dalay                               |                          |                            | Conversion res | sults available im  | mediately after |      |

| Pipeline Delay                               |                          |                            | со             | mpleted convers     | ion             |      |

| V <sub>он</sub>                              | output logic high        | current source<br>= 500 uA | VIO-0.2        |                     |                 | V    |

|                                              | voltage                  |                            |                |                     |                 |      |

| V <sub>OL</sub>                              | output logic low voltage | current sink<br>= 500 uA   |                |                     | 0.2             | V    |

| Power Supply                                 |                          |                            |                |                     |                 |      |

| V <sub>DD</sub>                              |                          |                            | 4.5            |                     | 5.5             | V    |

| V <sub>IO</sub>                              |                          |                            | 1.8            |                     | VDD             | V    |

| Standby Current                              |                          |                            |                | 3200                |                 | uA   |

| V 0 (()                                      | operating                | fs = 1 kHz                 |                | 3                   |                 | mA   |

| V <sub>DD</sub> Current ( I <sub>VDD</sub> ) | operating                | fs = 300 kHz               |                | 3.5                 |                 | mA   |

<sup>(1)</sup> Parameters are provided by lab bench test and design simulation.

www.3peak.com 7 / 22 BA20231001A0

## Timing Requirements (1)

All test conditions: at  $V_{DD}$  = 5 V,  $V_{IO}$  = 1.71 V to 5 V,  $T_A$ = -40°C to +125°C,  $C_{load}$  = 20 pF, unless otherwise noted.

|                      | Parameter                                                                | Min  | Тур  | Max  | Unit |

|----------------------|--------------------------------------------------------------------------|------|------|------|------|

| t <sub>CONV</sub>    | Conversion Time: CNV Rising Edge to Data Available                       | 1540 | 1620 | 1700 | ns   |

| t <sub>ACQ</sub>     | Acquisition Time                                                         | 1630 |      |      | ns   |

| tcyc                 | Time between Conversions                                                 | 3330 |      |      | ns   |

| t <sub>CNVH</sub>    | CNV Pulse Width (CS Mode)                                                | 9    |      |      | ns   |

| t <sub>SCK</sub>     | SCK Period (CS Mode)                                                     |      |      |      | ns   |

|                      | VIO above 4.5 V                                                          | 16   |      |      | ns   |

|                      | VIO above 3.3 V                                                          | 17   |      |      | ns   |

|                      | VIO above 1.7 V                                                          | 25   |      |      | ns   |

| tsck                 | SCK Period (Chain Mode)                                                  |      |      |      | ns   |

|                      | VIO above 4.5 V                                                          | 16   |      |      | ns   |

|                      | VIO above 3.3 V                                                          | 17   |      |      | ns   |

|                      | VIO above 1.7 V                                                          | 25   |      |      | ns   |

| t <sub>SCKL</sub>    | SCK Low Time                                                             | 5    |      |      | ns   |

| tsckh                | SCK High Time                                                            | 5    |      |      | ns   |

| t <sub>HSDO</sub>    | SCK Falling Edge to Data Remains Valid                                   | 3.5  |      |      | ns   |

| t <sub>DSDO</sub>    | SCK Falling Edge to Data Valid Delay                                     |      |      |      |      |

|                      | VIO above 4.5 V                                                          |      |      | 14   | ns   |

|                      | VIO above 3.3 V                                                          |      |      | 15   | ns   |

|                      | VIO above 1.7 V                                                          |      |      | 23   | ns   |

| t <sub>EN</sub>      | CNV or SDI Low to SDO D15 MSB Valid (CS Mode)                            |      |      |      |      |

|                      | VIO above 4.5 V                                                          |      |      | 12   |      |

|                      | VIO above 3.3 V                                                          |      |      | 13   | ns   |

|                      | VIO above 1.7 V                                                          |      |      | 21   | ns   |

| t <sub>DIS</sub>     | CNV or SDI High or Last SCK Falling Edge to SDO High Impedance (CS Mode) |      |      | 10   | ns   |

| tssdicnv             | SDI Valid Setup Time from CNV Rising Edge                                | 8    |      |      | ns   |

| t <sub>HSDICNV</sub> | SDI Valid Hold Time from CNV Rising Edge (CS Mode)                       | 0    |      |      |      |

| thsdicnv             | SDI Valid Hold Time from CNV Rising Edge (Chain Mode)                    | 0    |      |      | ns   |

| tssckcnv             | SDI Valid Hold Time from CNV Rising Edge (Chain Mode)                    | 8    |      |      | ns   |

| t <sub>HSCKCNV</sub> | SCK Valid Setup Time from CNV Rising Edge (Chain Mode)                   | 0.5  |      |      | ns   |

| tssdisck             | SCK Valid Hold Time from CNV Rising Edge (Chain Mode)                    | 0    |      |      | ns   |

| t <sub>HSDISCK</sub> | SDI Valid Setup Time from SCK Falling Edge (Chain Mode)                  | 0.5  |      |      | ns   |

| t <sub>DSDOSDI</sub> | SDI Valid Hold Time from SCK Falling Edge (Chain Mode)                   |      |      | 9    | ns   |

<sup>(1)</sup> Parameters are provided by design simulation.

www.3peak.com 8 / 22 BA20231001A0

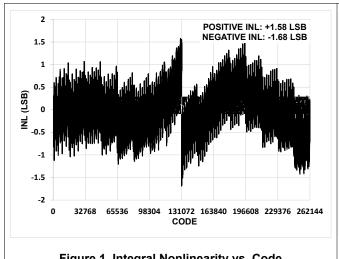

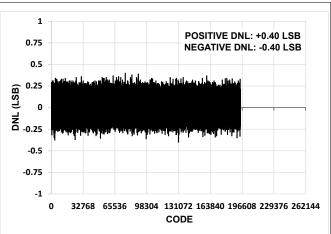

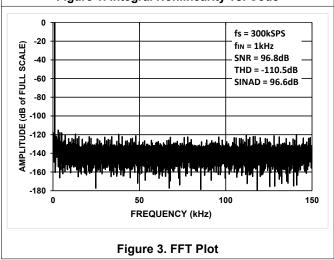

### **Typical Performance Characteristics**

All test condition: VDD = 5.0 V, VREF = 5.0 V , VIO= 3.3 V ,  $T_A$  =  $+25^{\circ}\text{C}$ , unless otherwise noted.

Figure 1. Integral Nonlinearity vs. Code

9/22 BA20231001A0 www.3peak.com

### **Detailed Description**

#### Overview

TPC5180 is an 18-bit successive approximation register (SAR) ADC. The device is capable to convert analog input into digital output without latency or pipeline delay, so it is ideal for multiple channel applications.

When a conversion is initiated, the analog input is sampled on internal capacitor, and then converted based on charge redistribution with the internal clock. During conversion, the input is disconnected from the internal capacitor.

After conversion, the device reconnects the sampling capacitors to input pins, and enters acquisition phase.

### **Functional Block Diagram**

Figure 4. TPC5180 Block Diagram

www.3peak.com 10 / 22 BA20231001A0

#### **Feature Description**

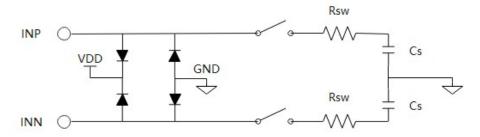

#### **Analog Input**

The following is the equivalent input sampling circuit. The sampling switch is represented by a resistance in series with the ideal switch. The electrostatic discharge (ESD) protection diodes from both analog inputs are also shown in the figure.

Figure 5. Equivalent Input Sampling Circuit

#### Reference

The device operates with an external reference voltage. During the conversion process, internal capacitors are switched onto the reference terminal, and a dynamic charge is required. The switching frequency is proportional to the internal conversion clock frequency. A reference driver circuit is required to support the dynamic charge so that the noise and linearity performance of the device is not degraded.

#### **ADC Transfer Function**

The device is a unipolar, differential input device, and the output is in twos complement format. The transfer equation is shown in the following table:

| Description                 | Analog Input  | Digital output Code (Hex) |

|-----------------------------|---------------|---------------------------|

| Full scale range            | 2*VREF        | -                         |

| Least Significant Bit (LSB) | 2*VREF/262144 | -                         |

| Positive full scale         | VREF – 1 LSB  | 7FFF                      |

| Midscale                    | 0 V           | 0000                      |

| Midscale – 1 LSB            | 0 – 1LSB      | FFFF                      |

| Negative full scale         | -VREF         | 8000                      |

#### **Device Function Modes**

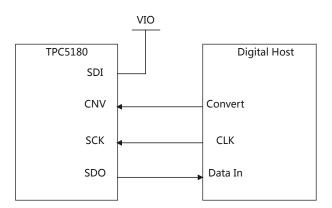

The device offers  $\overline{\text{CS}}$  mode and Daisy-chain mode for interfacing with the host.

The mode in which the device operates depends on the SDI level when the CNV rising edge occurs. The device operates in  $\overline{\text{CS}}$  mode if SDI is high at the CNV rising edge. If SDI is low at the CNV rising edge, or if SDI and CNV are connected, the device operates in daisy-chain mode.

In  $\overline{\text{CS}}$  mode, the device is compatible with SPI hosts. This interface can use a 3-wire or 4-wire interface. The 3-wire interface, using the CNV, SCK, and SDO signals, minimizes the wiring connections and is useful for isolation applications. The 4-wire interface, using the SDI, CNV, SCK, and SDO signals, allows the user to sample the analog input independent of the serial interface timing, and is useful to control an individual device while having multiple similar devices on board.

www.3peak.com 11 / 22 BA20231001A0

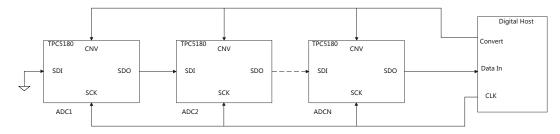

In daisy-chain mode, multiple devices can be cascaded on a single data line similar to a shift register. This mode is useful to reduce component count and signal traces on the board.

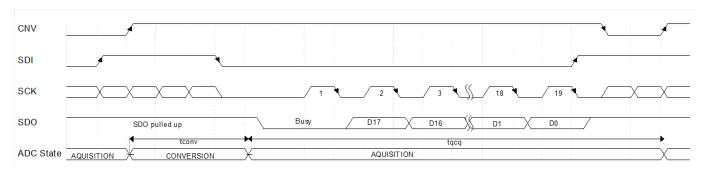

In both modes, the device can either operate with or without a busy indicator, where the busy indicator is a bit preceding the output data bits that can be used to interrupt the digital host and trigger the data transfer.

#### **CS** Mode

The device operates in  $\overline{CS}$  mode if SDI is high at the CNV rising edge. There are four different interface options available in this mode: 3-wire  $\overline{CS}$  mode without a busy indicator, 3-wire  $\overline{CS}$  mode with a busy indicator, 4-wire  $\overline{CS}$  mode with a busy indicator.

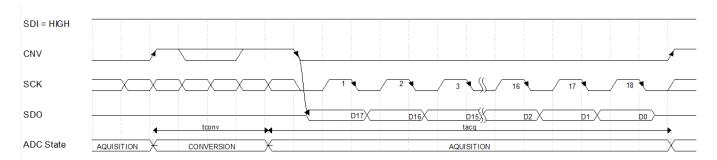

#### 3-wire CS Mode without Busy Indicator

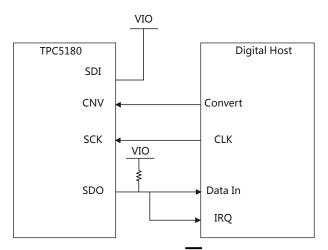

This mode is useful when a single ADC is connected to an SPI-compatible digital host.

In this mode, SDI can be connected to VIO. A CNV rising edge samples the input signal, causes the device to enter a conversion phase, and SDO is forced to 3-state. Conversion is done with an internal clock and continues regardless of the state of CNV. So CNV can be pulled low then to select other devices on the board.

However, CNV must return and hold high before the conversion time elapses. A high level on CNV at the end of the conversion ensures the device does not generate a busy indicator.

Figure 6. Connection Diagram: 3-Wire CS Mode without Busy Indicator

Figure 7. Timing Diagram: 3-Wire CS Mode without Busy Indicator

On the CNV falling edge, SDO comes out of 3-state and the device outputs the MSB of the data at first, and then low data bits on subsequent SCK falling edges.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and the SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 18th SCK falling edge or when CNV goes high, whichever occurs first.

www.3peak.com 12 / 22 BA20231001A0

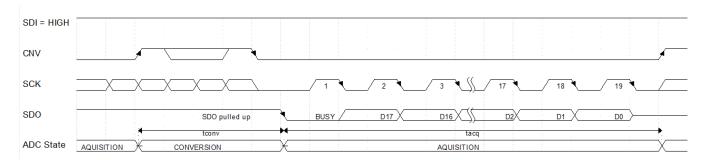

#### 3-wire CS Mode with a Busy Indicator

This mode is useful when a single ADC is connected to an SPI-compatible digital host and an interrupt-driven data transfer is required.

In this mode, SDI can be connected to VIO. A CNV rising edge samples the input signal, causes the device to enter a conversion phase, and SDO is forced to 3-state.

Conversion is done with an internal clock and continues regardless of the state of CNV. So CNV can be pulled low then to select other devices on the board.

A pull-up resistor on the SDO pin ensures that  $\overline{\text{CS}}$  pin of digital host is held high when SDO is in 3-state.

However, CNV must be pulled low before conversion time elapses. A low level of CNV at the end of conversion ensures the device generates a busy indicator.

Figure 8. Connection Diagram: 3-Wire CS Mode with a Busy Indicator

Figure 9. Timing Diagram: 3-Wire CS Mode with a Busy Indicator

When the conversion completes, the device enters an acquisition state. SDO comes out of 3-state, and outputs a busy indicator bit (low level). This feature provides a high-to-low transition on the  $\overline{CS}$  pin of the digital host.

Then the data bits are clocked out on the subsequent SCLK falling edges, MSB first.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 17th SCK falling edge or when CNV goes high, whichever occurs first.

www.3peak.com 13 / 22 BA20231001A0

#### 4-wire CS Mode without Busy Indicator

This mode is useful when one or more ADCs are connected to an SPI-compatible digital host. The following is the connection diagram of the two ADCs.

In this mode, SDI is controlled by the digital host and functions as  $\overline{\text{CS}}$ .

Figure 10. Connection Diagram: Two ADCs with 4-Wire CS Mode without Busy Indicator

Figure 11. Timing Diagram: Two ADCs with 4-Wire CS Mode without Busy Indicator

When SDI is high, a CNV rising edge samples the input signal, causes the device to enter a conversion phase, and forces SDO to 3-state.

In this mode, CNV must be held high from the start of the conversion until all data bits are read.

Conversion is done with the internal clock regardless of the state of SDI. So SDI (functioning as  $\overline{CS}$ ) can be pulled low to select other devices on the board.

However, SDI must return and hold high before the conversion time elapses. A high level on SDI at the end of the conversion ensures the device does not generate a busy indicator.

On the SDI falling edge, SDO comes out of 3-state and the device outputs the MSB of the data at first, and then low data bits on subsequent SCK falling edges.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and the SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 18th SCK falling edge or when SDI goes high, whichever occurs first.

When multiple devices are connected together on the same data bus, the SDI of the second device (functioning as  $\overline{\text{CS}}$  for the second device) can go low after the first device data are read, and the SDO of the first device is in 3-state.

Care must be taken so that CNV and SDO of the devices are not low together during the read cycle.

www.3peak.com 14 / 22 BA20231001A0

### 4-Wire CS Mode with Busy Indicator

This mode is most useful when a single ADC is connected to a digital host and an interrupt-driven data transfer is desired.

In this mode, SDI is controlled by the digital host and functions as  $\overline{\text{CS}}$ .

A pull-up resistor on SDO pin ensures that  $\overline{CS}$  pin of digital host is held high when SDO is in 3-state.

When SDI is high, a CNV rising edge samples the input signal, causes the device to enter a conversion phase, and forces SDO to 3-state.

In this mode, CNV must be held high from the start of the conversion until all data bits are read.

Conversion is done with the internal clock regardless of the state of SDI. So SDI (functioning as  $\overline{CS}$ ) can be pulled low to select other devices on the board.

However, CNV must be pulled low before conversion time elapses. A low level of CNV at the end of conversion ensures the device generates a busy indicator.

Figure 12. Connection Diagram: 4-wire CS Mode with a Busy Indicator

Figure 13. Timing Diagram: 4-Wire CS Mode with a Busy Indicator

When the conversion completed, the device enters an acquisition state. SDO comes out of 3-state, and outputs a busy indicator bit (low level). This feature provides a high-to-low transition on the  $\overline{\text{CS}}$  pin of the digital host.

Then the data bits are clocked out on the subsequent SCLK falling edges, MSB first.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and the SCK falling edge allows a faster reading rate if there is an acceptable hold time.

SDO goes to 3-state after the 17th SCK falling edge or when SDI goes high, whichever occurs first.

Care must be taken so that CNV and SDO of the devices are not low together during the read cycle.

www.3peak.com 15 / 22 BA20231001A0

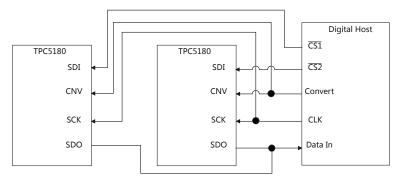

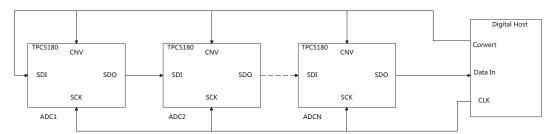

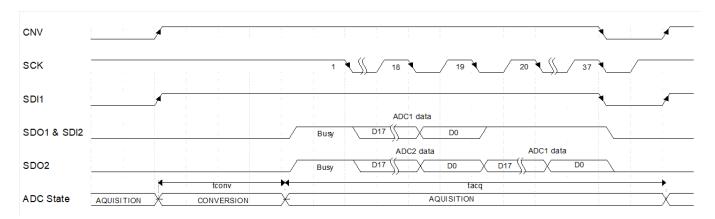

#### **Daisy-Chain Mode**

Daisy-chain mode is selected if SDI is low at CNV rising edge or if SDI and CNV are connected.

#### **Daisy-Chain Mode without Busy Indicator**

This mode is useful in applications where the digital host has limited interfacing capability with multiple ADCs. In this mode, the CNV pins of all ADCs in the chain are connected and are controlled by a single pin of the digital host. The SCK pins are also connected and controlled by a single pin of the digital host.

Figure 14. Connection Diagram: Daisy-Chain Mode without Busy Indicator

Figure 15. Timing Diagram: Daisy-Chain Mode without Busy Indicator

The SDO pin is driven low when SDI and CNV are both low.

A CNV rising edge with SDI low selects daisy-chain mode, samples the analog input, and causes the device to enter a conversion phase.

In this mode, CNV must remain high from the start of the conversion until all data bits are read. When started, the conversion continues with the internal clock, regardless of the state of SCK.

However, SCK must be low at the CNV rising edge so that the device does not generate a busy indicator at the end of the conversion.

At the end of conversion, every ADC in the chain outputs the MSB bit of the conversion result on its own SDO pin. The internal shift register of each ADC latches the data available on its SDI pin and shifts out the next bit of data on its SDO pin on every subsequent SCK falling edge.

Therefore, the digital host receives the data of ADC N at first (MSB first), followed by the data of ADC N–1, and so on. A total of 18 x N SCK falling edges are required to capture the outputs of all N devices in the chain.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

www.3peak.com 16 / 22 BA20231001A0

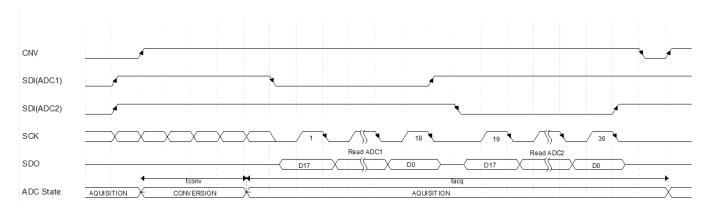

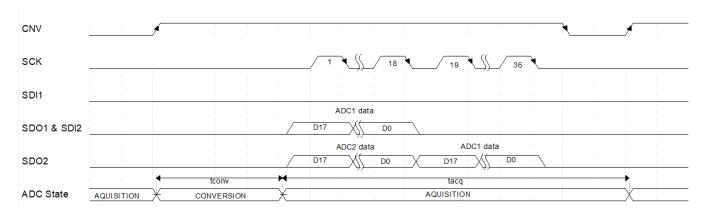

#### Daisy-Chain Mode with a Busy Indicator

This mode is useful in applications where the digital host has limited interfacing capability with multiple ADCs, and an interrupt-driven data transfer is desired.

In this mode, the CNV pins of all ADCs in the chain are connected and are controlled by a single pin of the digital host. The SCK pins are also connected and controlled by a single pin of the digital host.

Figure 16. Connection Diagram: Daisy-Chain Mode with Busy Indicator

Figure 17. Timing Diagram: Daisy-Chain Mode with Busy Indicator

The SDO pin is driven low when SDI and CNV are both low.

A CNV rising edge with SDI low selects daisy-chain mode, samples the analog input, and causes the device to enter a conversion phase.

In this mode, CNV must remain high from the start of the conversion until all data bits are read. When started, the conversion continues with internal clock, regardless of the state of SCK.

However, SCK must be high at the CNV rising edge so that the device generates a busy indicator at the end of the conversion.

At the end of conversion, every ADC in the chain forces its SDO pin high, providing a low-to-high transition on the  $\overline{\rm IRQ}$  pin of the digital host. The internal shift register of each ADC latches the data available on its SDI pin and shifts out the next bit of data on its SDO pin on every subsequent SCK falling edge. Therefore, the digital host receives the interrupt signal followed by the data of ADC N (MSB first), and then the data of

ADC N-1, and so on. A total of (18 × N) + 1 SCK falling edges are required to capture the outputs of all N devices in the chain. The busy indicator bits of ADC 1 to ADC N-1 do not propagate to the next device in the chain.

The data is valid on both SCK edges. The rising edge can be used to capture the data, and SCK falling edge allows a faster reading rate if there is an acceptable hold time.

#### **Power Supply Sequence**

The recommended power supply sequence is listed below:

www.3peak.com 17 / 22 BA20231001A0

- Power-up: VDD → VIO → REF → Analog Input. It should be noticed that REF and analog input must be applied after VDD. However, the device is insensitive to VDD and VIO sequence, which means VIO could be applied before VDD. Besides, it's high-Z status for digital input pins without VDD and VIO applied and digital signal on these pins even would not cause issue even if VDD and VIO are gone.

- 2. Power-down: Analog Input  $\rightarrow$  REF  $\rightarrow$  VIO  $\rightarrow$  VDD.

www.3peak.com 18 / 22 BA20231001A0

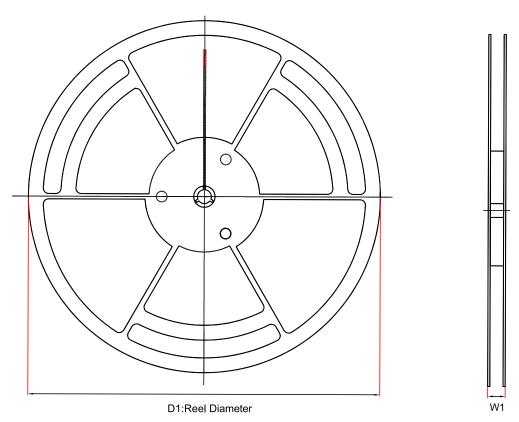

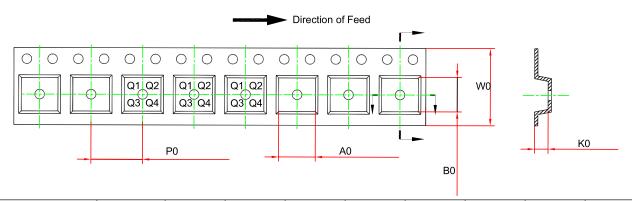

# **Tape and Reel Information**

| Order Number | Package | D1 (mm) | W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P0 (mm) | W0 (mm) | Pin1<br>Quadrant |

|--------------|---------|---------|---------|---------|---------|---------|---------|---------|------------------|

| TPC5180-VS2R | MSOP10  | 330     | 17.6    | 5.2     | 3.3     | 1.5     | 8       | 12      | Q1               |

www.3peak.com 19 / 22 BA20231001A0

## **Package Outline Dimensions**

### MSOP10

### **Order Information**

| Order Number | Operating Temperature<br>Range | Package | Marking Information | MSL  | Transport Media, Quantity | Eco Plan |

|--------------|--------------------------------|---------|---------------------|------|---------------------------|----------|

| TPC5180-VS2R | -40 to 125°C                   | MSOP10  | 5180                | MSL1 | Tape and Reel, 3000       | Green    |

**Green**: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

www.3peak.com 21 / 22 BA20231001A0

#### IMPORTANT NOTICE AND DISCLAIMER

Copyright<sup>©</sup> 3PEAK 2012-2023. All rights reserved.

**Trademarks.** Any of the 思瑞浦 or 3PEAK trade names, trademarks, graphic marks, and domain names contained in this document /material are the property of 3PEAK. You may NOT reproduce, modify, publish, transmit or distribute any Trademark without the prior written consent of 3PEAK.

**Performance Information.** Performance tests or performance range contained in this document/material are either results of design simulation or actual tests conducted under designated testing environment. Any variation in testing environment or simulation environment, including but not limited to testing method, testing process or testing temperature, may affect actual performance of the product.

**Disclaimer.** 3PEAK provides technical and reliability data (including data sheets), design resources (including reference designs), application or other design recommendations, networking tools, security information and other resources "As Is". 3PEAK makes no warranty as to the absence of defects, and makes no warranties of any kind, express or implied, including without limitation, implied warranties as to merchantability, fitness for a particular purpose or non-infringement of any third-party's intellectual property rights. Unless otherwise specified in writing, products supplied by 3PEAK are not designed to be used in any life-threatening scenarios, including critical medical applications, automotive safety-critical systems, aviation, aerospace, or any situations where failure could result in bodily harm, loss of life, or significant property damage. 3PEAK disclaims all liability for any such unauthorized use.

www.3peak.com 22 / 22 BA20231001A0