Order

Now

**TPS40422**

SLUSAQ4F-OCTOBER 2011-REVISED JANUARY 2017

# TPS40422 Dual-Output or Two-Phase Synchronous Buck Controller with PMBus™ Interface

## 1 Features

- Single Supply Operation: 4.5 V to 20 V

- Output Voltage from 0.6 V to 5.6 V

- Dual-output or Two-Phase Synchronous Buck

Controller

- PMBus™ Interface Capability

- Margining Up or Down with 2-mV Step

- Programmable Fault Limit and Response

- Output Voltage, Output Current Monitoring

- External Temperature Monitoring with 2N3904 Transistor

- Programmable UVLO ON and OFF Thresholds

- Programmable Soft-start Time and Turn-On and Turn-Off Delay

- On-Chip Non-volatile Memory (NVM) to Store Custom Configurations

- 180° Out-of-Phase to Reduce Input Ripple

- 600-mV Reference Voltage with ±0.5% Accuracy from 0°C to 85°C

- Inductor DCR Current Sensing

- Programmable Switching Frequency: 200 kHz to 1 MHz

- Voltage Mode Control with Input Feed Forward

- Current Sharing for Multiphase Operation

- Supports Pre-biased Output

- Differential Remote Sensing

- External SYNC

- BPEXT Pin Boosts Efficiency by Supporting External Bias Power Switch Over

- OC, OV, UV, and OT Fault Protection

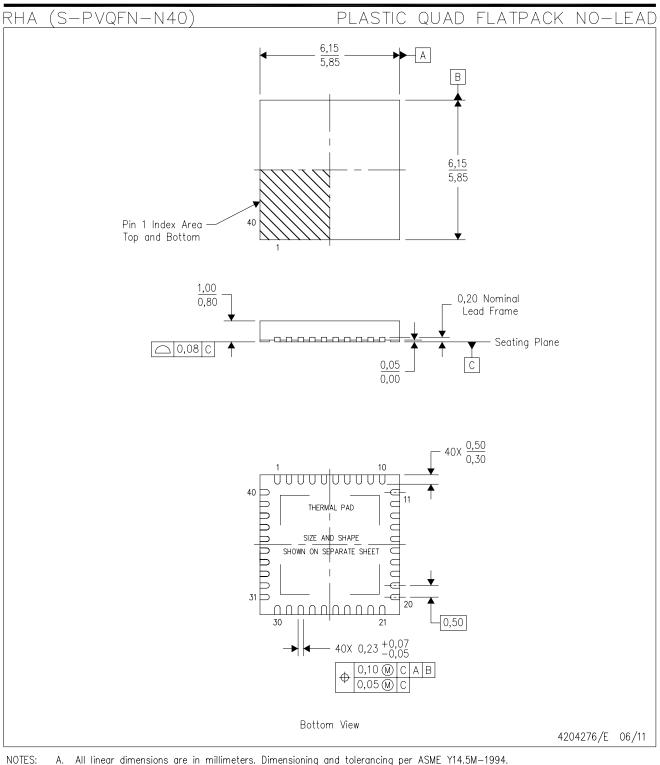

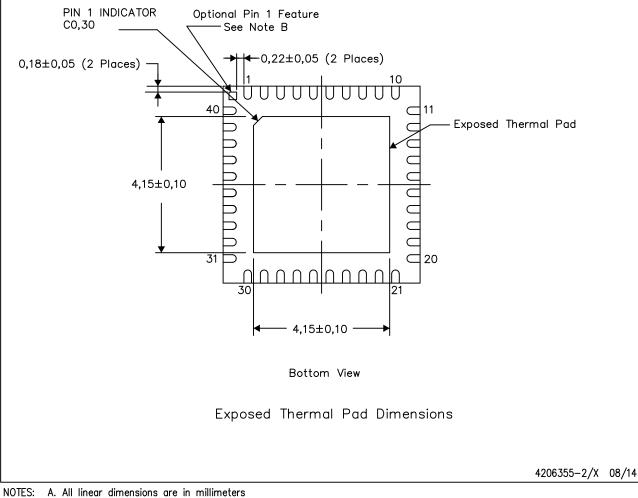

- 40-Pin, 6 mm × 6 mm VQFN Package with 0.5mm Pitch

- 40-Pin, 5 mm × 5 mm WQFN Package with 0.4mm Pitch

# 2 Applications

- Multiple Rail Systems

- Telecom Base Station

- Switcher/Router Networking

- Server and Storage System

## 3 Description

The TPS40422 is a dual-output PMBus protocol, synchronous buck controller. It can be configured also for a single, two-phase output.

The wide input range supports 5-V and 12-V intermediate buses. The accurate reference voltage satisfies the need of precision voltage to the modern ASICs and potentially reduces the output capacitance. Voltage mode control reduces noise sensitivity and also ensures low duty ratio conversion.

Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TDC 40422   | VQFN (40) | 6.00 mm × 6.00 mm |

| TPS40422    | WQFN (40) | 5.00 mm × 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

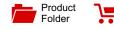

## **Simplified Application**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

Texas Instruments

www.ti.com

Page

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Des  | cription (continued) 3             |

| 6 | Pin  | Configuration and Functions 4      |

| 7 | Spe  | cifications6                       |

|   | 7.1  | Absolute Maximum Ratings 6         |

|   | 7.2  | ESD Ratings 6                      |

|   | 7.3  | Recommended Operating Conditions 6 |

|   | 7.4  | Electrical Characteristics7        |

|   | 7.5  | Typical Characteristics 11         |

| 8 | Deta | ailed Description 12               |

|   | 8.1  | Overview 12                        |

|   | 8.2  | Functional Block Diagram 13        |

|   | 8.3  | Feature Description 14             |

|   | 8.4  | Device Functional Modes 23         |

|   |      |                                    |

|    | 8.5  | Programming                              | <mark>26</mark> |

|----|------|------------------------------------------|-----------------|

|    | 8.6  | Register Maps                            | 27              |

| 9  | Арр  | lications and Implementation             | <mark>51</mark> |

|    | 9.1  | Application Information                  | <mark>51</mark> |

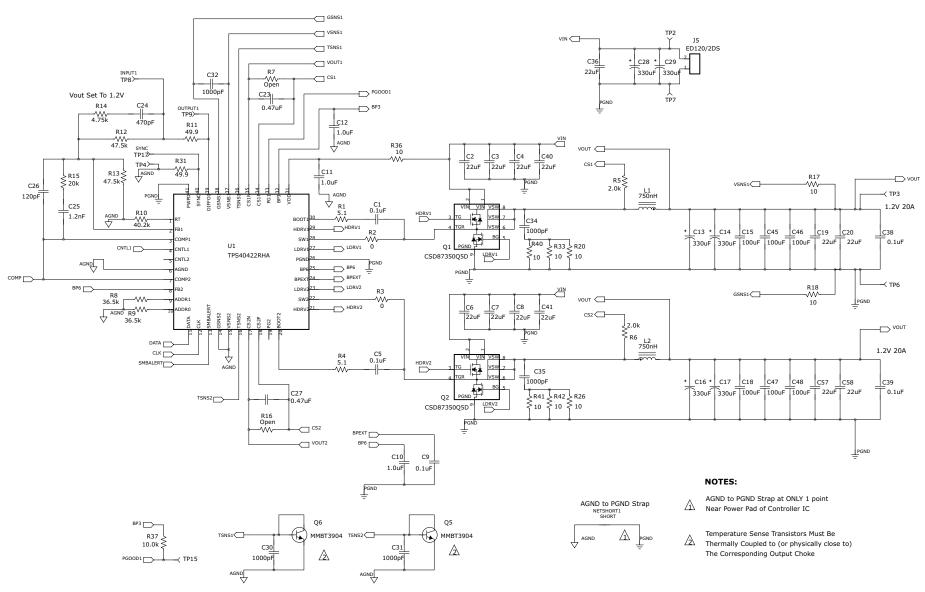

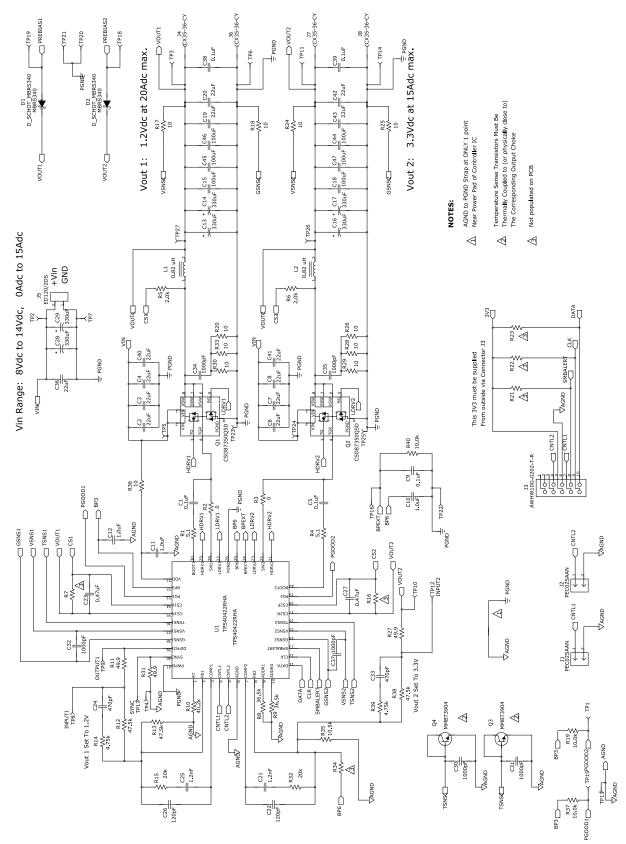

|    | 9.2  | Typical Application                      | 51              |

| 10 | Pow  | ver Supply Recommendations               | <mark>60</mark> |

| 11 | Lay  | out                                      | 61              |

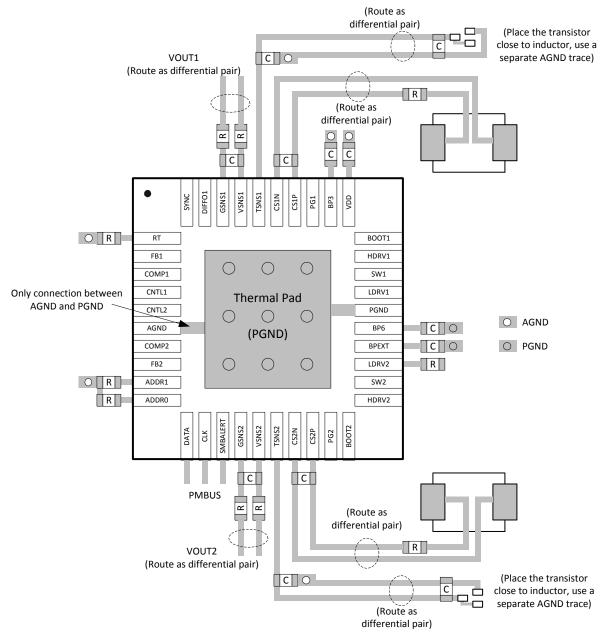

|    | 11.1 | Layout Guidelines                        | <mark>61</mark> |

|    | 11.2 | Layout Example                           | <mark>62</mark> |

| 12 | Dev  | ice and Documentation Support            | <mark>63</mark> |

|    | 12.1 | Device Support                           | <mark>63</mark> |

|    | 12.2 | Community Resources                      | <mark>63</mark> |

|    | 12.3 | Trademarks                               | <mark>63</mark> |

|    | 12.4 | Electrostatic Discharge Caution          | <mark>63</mark> |

|    | 12.5 | Glossary                                 | <mark>63</mark> |

| 13 |      | hanical, Packaging, and Orderable mation | 63              |

## **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | hanges from Revision E (September 2016) to Revision F | Page |

|----|-------------------------------------------------------|------|

| •  | Added WQFN package to Device Information table        | 1    |

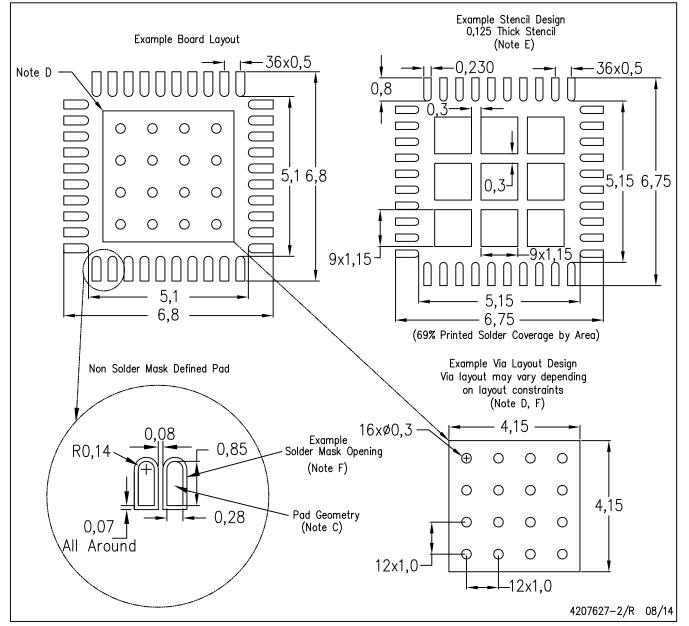

| •  | Added WQFN package drawing                            | 4    |

|    |                                                       |      |

## Changes from Revision D (August 2014) to Revision E

| • | Added pins (CS1N, CS2N, CS1P, CS2P, GSNS1, and GSNS2) to <i>Input voltage range</i> specification in Absolute Maximum Ratings table | (  |

|---|-------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Updated VSNSx connection description in Table 1                                                                                     | 2; |

| • | Updated VSNS2 connection description in Table 2                                                                                     | 2! |

| • | Corrected Equation 23                                                                                                               | 54 |

| • | Clarified Table 9                                                                                                                   | 5! |

## Changes from Revision C (August 2012) to Revision D

Page

| • | Added Handling Ratings table, Feature Description section, Device Functional Modes section, Application and<br>Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation<br>Support section, and Mechanical, Packaging, and Orderable Information section | 1    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Corrected Simplified Application                                                                                                                                                                                                                                                                       | 1    |

| • | Updated FB2 description in table                                                                                                                                                                                                                                                                       | 5    |

| • | Changed maximum input voltage range for VDD from "20 V" to "22 V" in Absolute Maximum Ratings table                                                                                                                                                                                                    | 6    |

| • | Corrected maximum input voltage range for CLK, DATA, and SYNC to "5.5 V" in Absolute Maximum Ratings table                                                                                                                                                                                             | 6    |

| • | Corrected maximum input voltage range for CNTL1, CNTL2 to "7 V" in Absolute Maximum Ratings table                                                                                                                                                                                                      | 6    |

| • | Corrected maximum output voltage range for SMBALRT in Absolute Maximum Ratings table                                                                                                                                                                                                                   | 6    |

| • | Updated specifications in PMBus INTERFACE section of Electrical Characteristics table                                                                                                                                                                                                                  | . 10 |

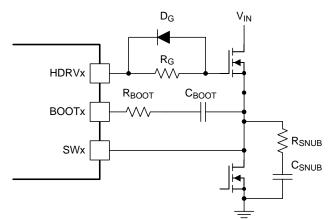

| • | Added Switching Node and BOOT Voltage section                                                                                                                                                                                                                                                          | . 19 |

| • | Changed section title from User Data and Adjustable Anti-Cross Conduction Delay to User Data                                                                                                                                                                                                           | . 22 |

| • | Updated User Data section                                                                                                                                                                                                                                                                              | 22   |

| • | Added Adjustable Anti-Cross Conduction Delay section                                                                                                                                                                                                                                                   | . 22 |

| • | Added Table 4                                                                                                                                                                                                                                                                                          | 28   |

## 5 Description (continued)

Using the PMBus protocol, the device margining function, reference voltage, fault limit, UVLO threshold, soft-start time, turn-on delay, and turn-off delay can be programmed.

In addition, an accurate measurement system is implemented to monitor the output voltages, currents and temperatures for each channel.

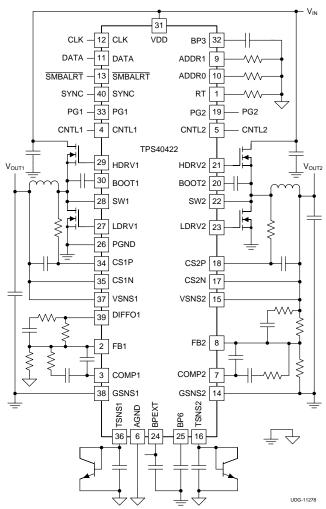

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN   | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                    |  |

|-------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADDR0 | 10  | I   | Low-order address pin for PMBus address configuration. One of eight resistor values must be connected from this pin to AGND to select the low-order octal digit in the PMBus address.                                                                          |  |

| ADDR1 | 9   | I   | High-order address pin for PMBus address configuration. One of eight resistor values must be connected from this pin to AGND to select the high-order octal digit in the PMBus address.                                                                        |  |

| AGND  | 6   | _   | Low-noise ground connection to the controller. Connections should be arranged so that power level currents do not flow through the AGND path.                                                                                                                  |  |

| BOOT1 | 30  | I   | Bootstrapped supply for the high-side FET driver for channel 1 (CH1). Connect a capacitor (100 nF typical) from BOOT1 to SW1 pin.                                                                                                                              |  |

| BOOT2 | 20  | I   | Bootstrapped supply for the high-side FET driver for channel 2 (CH2). Connect a capacitor (100 nF typical) from BOOT2 to SW2 pin.                                                                                                                              |  |

| BP3   | 32  | 0   | Output bypass for the internal 3.3-V regulator. Connect a 100 nF or larger capacitor from this pin to AGND. The maximum suggested capacitor value is 10 $\mu$ F.                                                                                               |  |

| BP6   | 25  | 0   | tput bypass for the internal 6.5-V regulator. Connect a low ESR, 1 $\mu$ F or larger ceramic capacitor m this pin to PGND. The maximum suggested capacitor value is 10 $\mu$ F.                                                                                |  |

| BPEXT | 24  | I   | xternal voltage input for BP6 switchover function. If the BPEXT function is not used, connect this pin to GND via a 10-kΩ resistor. Otherwise connect a 100-nF or larger capacitor from this pin to PGND. The naximum suggested capacitor value is 10 $\mu$ F. |  |

| CLK   | 12  | I   | ock input for the PMBus interface. Pull up to 3.3 V with a resistor.                                                                                                                                                                                           |  |

| CNTL1 | 4   | I   | Logic level input which controls startup and shutdown of CH1, determined by PMBus options. When floating, the pin is pulled up to BP6 by an internal 6-µA current source.                                                                                      |  |

| CNTL2 | 5   | I   | Logic level input which controls startup and shutdown of CH2, determined by PMBus options. When floating, the pin is pulled up to BP6 by an internal 6-µA current source.                                                                                      |  |

| COMP1 | 3   | 0   | Output of the error amplifier for CH1 and connection node for loop feedback components.                                                                                                                                                                        |  |

| COMP2 | 7   | 0   | Output of the error amplifier for CH2 and connection node for loop feedback components. For two-phase peration, use COMP1 for loop feedback and connect COMP1 to COMP2.                                                                                        |  |

| CS1N  | 35  | I   | Negative terminal of current sense amplifier for CH1.                                                                                                                                                                                                          |  |

| CS2N  | 17  | I   | Negative terminal of current sense amplifier for CH2.                                                                                                                                                                                                          |  |

Copyright © 2011–2017, Texas Instruments Incorporated

## Pin Functions (continued)

| PIN     | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                             |  |  |  |

|---------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CS1P    | 34  | I   | Positive terminal of current sense amplifier for CH1.                                                                                                                                                                                                                                                   |  |  |  |

| CS2P    | 18  | I   | Positive terminal of current sense amplifier for CH2.                                                                                                                                                                                                                                                   |  |  |  |

| DATA    | 11  | I/O | Data input/output for the PMBus interface. Pull up to 3.3 V with a resistor.                                                                                                                                                                                                                            |  |  |  |

| DIFFO1  | 39  | 0   | Output of the differential remote sense amplifier for CH1.                                                                                                                                                                                                                                              |  |  |  |

| FB1     | 2   | I   | verting input of the error amplifier for CH1. Connect a voltage divider to FB1 between DIFFO1 and GND to program the output voltage for CH1.                                                                                                                                                            |  |  |  |

| FB2     | 8   | I   | Inverting input of the error amplifier for CH2. Connect a voltage divider to FB2 between VOUT2 and GND to program the output for CH2. For two-phase operation, use FB1 to program the output voltage and connect FB2 to BP6 before applying voltage to VDD.                                             |  |  |  |

| GSNS1   | 38  | I   | Negative terminal of the differential remote sense amplifier for CH1.                                                                                                                                                                                                                                   |  |  |  |

| GSNS2   | 14  | I   | Negative terminal of the differential remote sense amplifier for CH2.                                                                                                                                                                                                                                   |  |  |  |

| HDRV1   | 29  | 0   | Bootstrapped gate drive output for the high-side N-channel MOSFET for CH1.                                                                                                                                                                                                                              |  |  |  |

| HDRV2   | 21  | 0   | Bootstrapped gate drive output for the high-side N-channel MOSFET for CH2.                                                                                                                                                                                                                              |  |  |  |

| LDRV1   | 27  | 0   | Gate drive output for the low side synchronous rectifier N-channel MOSFET for CH1.                                                                                                                                                                                                                      |  |  |  |

| LDRV2   | 23  | 0   | Gate drive output for the low-side synchronous rectifier N-channel MOSFET for CH2.                                                                                                                                                                                                                      |  |  |  |

| PGND    | 26  | _   | Power GND.                                                                                                                                                                                                                                                                                              |  |  |  |

| PG1     | 33  | 0   | Open drain power good indicator for CH1 output voltage.                                                                                                                                                                                                                                                 |  |  |  |

| PG2     | 19  | 0   | Open drain power good indicator for CH2 output voltage.                                                                                                                                                                                                                                                 |  |  |  |

| RT      | 1   | I   | Frequency programming pin. Connect a resistor from this pin to AGND to set the oscillator frequency.                                                                                                                                                                                                    |  |  |  |

| SMBALRT | 13  | 0   | Alert output for the PMBus interface. Pull up to 3.3 V with a resistor.                                                                                                                                                                                                                                 |  |  |  |

| SW1     | 28  | I   | Return of the high-side gate driver for CH1. Connect to the switched node for CH1.                                                                                                                                                                                                                      |  |  |  |

| SW2     | 22  | I   | Return of the high-side gate driver for CH2. Connect to the switched node for CH2.                                                                                                                                                                                                                      |  |  |  |

| SYNC    | 40  | I   | Logic level input for external clock synchronization. When an external clock is applied to this pin, the controller oscillator is synchronized to the external clock and the switching frequency is one half of the external clock frequency. When an external clock is not used, tie this pin to AGND. |  |  |  |

| TSNS1   | 36  | I   | External temperature sense input for CH1.                                                                                                                                                                                                                                                               |  |  |  |

| TSNS2   | 16  | I   | External temperature sense input for CH2.                                                                                                                                                                                                                                                               |  |  |  |

| VDD     | 31  | I   | Power input to the controller. Connect a low ESR, 100 nF or larger ceramic capacitor from this pin to AGND.                                                                                                                                                                                             |  |  |  |

| VSNS1   | 37  | Ι   | Positive terminal of the differential remote sense amplifier for CH1.                                                                                                                                                                                                                                   |  |  |  |

| VSNS2   | 15  | I   | Positive terminal of the differential remote sense amplifier for CH2.                                                                                                                                                                                                                                   |  |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                     |                                                                                   | MIN  | MAX | UNIT |  |

|-------------------------------------|-----------------------------------------------------------------------------------|------|-----|------|--|

|                                     | VDD                                                                               | -0.3 | 22  |      |  |

|                                     | BOOT1, BOOT2, HDRV1, HDRV2                                                        | -0.3 | 30  |      |  |

| Input voltage range <sup>(2)</sup>  | BOOT1 - SW1, BOOT2 - SW2                                                          | -0.3 | 7   | V    |  |

| input voltage range                 | CLK, DATA, SYNC                                                                   | -0.3 | 5.5 | ·    |  |

|                                     | BPEXT, CNTL1, CNTL2, CS1N, CS2N, CS1P, CS2P, FB1, FB2, GSNS1, GSNS2, VSNS1, VSNS2 | -0.3 | 7   |      |  |

|                                     | BP6, COMP1, COMP2, DIFFO1, LDRV1, LDRV2, PG1, PG2                                 | -0.3 | 7   |      |  |

| Output voltage range $(3)$          | SMBALRT                                                                           | -0.3 | 5.5 | V    |  |

| Output voltage range <sup>(3)</sup> | SW1, SW2                                                                          | -1   | 30  | v    |  |

|                                     | ADDR0, ADDR1, BP3, RT, TSNS1, TSNS2                                               | -0.3 | 3.6 |      |  |

| Operating junction tempera          | ature, T <sub>J</sub>                                                             | -40  | 150 | °C   |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground pin unless otherwise noted.

(3) Voltage values are with respect to the SW pin.

## 7.2 ESD Ratings

|                    |                         |                                                                                          | MIN | MAX | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-----|-----|------|

| T <sub>stg</sub>   | Storage temperature ran | ge                                                                                       | -55 | 155 | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | 2   |     | 1.1/ |

|                    |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | 1.5 |     | kV   |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|     |                                | MIN | MAX | UNIT |

|-----|--------------------------------|-----|-----|------|

| VDD | Input operating voltage        | 4.5 | 20  | V    |

| TJ  | Operating junction temperature | -40 | 125 | °C   |

## 7.4 Electrical Characteristics

$T_J = -40^{\circ}C$  to 125°C,  $V_{IN} = V_{DD} = 12$  V,  $f_{SW} = 500$  kHz, all parameters at zero power dissipation (unless otherwise noted)

|                            | PARAMETER                                            | TEST CONDITIONS                                                                             | MIN     | TYP                   | MAX   | UNIT |

|----------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------|---------|-----------------------|-------|------|

| INPUT SUPPL                | Y                                                    | I                                                                                           |         |                       |       |      |

| V <sub>VDD</sub>           | Input supply voltage range                           |                                                                                             | 4.5     |                       | 20    | V    |

|                            |                                                      | Switching, no driver load                                                                   | ·       | 18                    | 25    |      |

| I <sub>VDD</sub>           | Input operating current                              | Not switching                                                                               |         | 15                    | 20    | mA   |

| UVLO                       |                                                      |                                                                                             | ·       |                       |       |      |

| V <sub>IN(on)</sub>        | Input turn on voltage <sup>(1)</sup>                 | Default settings                                                                            |         | 4.25                  |       | V    |

| V <sub>IN(off)</sub>       | Input turn off voltage <sup>(1)</sup>                | Default settings                                                                            |         | 4                     |       | V    |

| V <sub>INON(rng)</sub>     | Programmable range for turn on voltage               |                                                                                             | 4.25    |                       | 16    | V    |

| VINOFF(rng)                | Programmable range for turn off voltage              |                                                                                             | 4       |                       | 15.75 | V    |

| VINONOFF(acc)              | Turn on and turn off voltage accuracy <sup>(2)</sup> | 4.5 V $\leq$ V <sub>VDD</sub> $\leq$ 20 V, all VIN_ON and VIN_OFF settings                  | -5%     |                       | 5%    |      |

| ERROR AMPL                 | IFIER                                                |                                                                                             | · · · · |                       |       |      |

|                            |                                                      | 0°C ≤ T <sub>J</sub> ≤ 85°C                                                                 | 597     | 600                   | 603   |      |

| V <sub>FB</sub>            | Feedback pin voltage                                 | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$                                                   | 594     | 600                   | 606   | mV   |

| A <sub>OL</sub>            | Open-loop gain <sup>(2)</sup>                        |                                                                                             | 80      |                       |       | dB   |

| G <sub>BWP</sub>           | Gain bandwidth product <sup>(2)</sup>                |                                                                                             | · · · · | 24                    |       | MHz  |

| I <sub>FB</sub>            | FB pin bias current (out of pin)                     | V <sub>FB</sub> = 0.6 V                                                                     |         |                       | 50    | nA   |

| 10                         | Sourcing                                             | V <sub>FB</sub> = 0 V                                                                       | 1       | 3                     |       |      |

| ICOMP                      | Sinking                                              | V <sub>FB</sub> = 1 V                                                                       | 3       | 9                     |       | mA   |

| BP6 REGULAT                | FOR                                                  |                                                                                             | · · ·   |                       |       |      |

| .,                         | Output voltage                                       | I <sub>BP6</sub> = 10 mA                                                                    | 6.2     | 6.5                   | 6.8   | V    |

| V <sub>BP6</sub>           | Dropout voltage                                      | $V_{VIN} - V_{BP6}, V_{VDD} = 4.5 \text{ V}, I_{BP6} = 25 \text{ mA}$                       | · · ·   | 70                    | 120   | mV   |

| I <sub>BP6</sub>           | Output current                                       | V <sub>VDD</sub> = 12 V                                                                     | 120     |                       |       | mA   |

| V <sub>BP6UV</sub>         | Regulator UVLO voltage <sup>(2)</sup>                |                                                                                             | 3.3     | 3.55                  | 3.8   | V    |

| V <sub>BP6UV(hyst)</sub>   | Regulator UVLO voltage hysteresis <sup>(2)</sup>     |                                                                                             | 230     | 255                   | 270   | mV   |

| BPEXT                      |                                                      |                                                                                             | · · · · |                       |       |      |

| V <sub>BPEXT(swover)</sub> | BPEXT switch-over voltage                            |                                                                                             | 4.5     | 4.6                   |       | V    |

| V <sub>hys(swover)</sub>   | BPEXT switch-over hysteresis                         |                                                                                             | 100     |                       | 200   | mV   |

| V <sub>BPEXT(do)</sub>     | BPEXT dropout voltage                                | V <sub>BPEXT</sub> -V <sub>BP6</sub> , V <sub>BPEXT</sub> = 4.8 V, I <sub>BP6</sub> = 25 mA | · · · · |                       | 100   | mV   |

| BOOTSTRAP                  |                                                      |                                                                                             | · · · · |                       |       |      |

| V <sub>BOOT(drop)</sub>    | Bootstrap voltage drop                               | I <sub>BOOT</sub> = 5 mA                                                                    |         | 0.7                   | 1.0   | V    |

| BP3 REGULAT                | FOR                                                  |                                                                                             | · · · · |                       |       |      |

| V <sub>BP3</sub>           | Output voltage                                       | $V_{VDD} = 4.5 \text{ V}, \text{ I}_{BP3} \le 5 \text{ mA}$                                 | 3.1     | 3.3                   | 3.5   | V    |

| OSCILLATOR                 |                                                      |                                                                                             | ·       |                       |       |      |

|                            | Adjustment range                                     |                                                                                             | 100     |                       | 1000  | kHz  |

| f <sub>SW</sub>            | Switching frequency                                  | R <sub>RT</sub> = 40 kΩ                                                                     | 450     | 500                   | 550   | kHz  |

| V <sub>RMP</sub>           | Ramp peak-to-peak <sup>(2)</sup>                     |                                                                                             | · · · · | V <sub>VDD</sub> /8.2 |       | V    |

| V <sub>VLY</sub>           | Valley voltage <sup>(2)</sup>                        |                                                                                             | 0.7     | 0.8                   | 1.0   | V    |

Hysteresis of at least 150 mV is specified by design.

Specified by design. Not production tested.

## **Electrical Characteristics (continued)**

$T_J = -40^{\circ}C$  to 125°C,  $V_{IN} = V_{DD} = 12$  V,  $f_{SW} = 500$  kHz, all parameters at zero power dissipation (unless otherwise noted)

|                                              | PARAMETER                                                             | TEST CONDITIONS                                                                           | MIN                   | TYP   | MAX                   | UNIT |  |

|----------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------|-------|-----------------------|------|--|

| SYNCHRONIZ                                   | ATION                                                                 |                                                                                           |                       |       |                       |      |  |

| V <sub>SYNCH</sub>                           | SYNC high-level threshold                                             |                                                                                           | 2.0                   |       |                       | V    |  |

| V <sub>SYNCL</sub>                           | SYNC low level threshold                                              |                                                                                           |                       |       | 0.8                   | V    |  |

| t <sub>SYNC</sub>                            | Minimum SYNC pulse width                                              |                                                                                           |                       |       | 100                   | ns   |  |

| f <sub>SYNC(max)</sub>                       | Maximum SYNC frequency <sup>(3)</sup>                                 |                                                                                           | 2000                  |       |                       | kHz  |  |

| f <sub>SYNC(min)</sub>                       | Minimum SYNC frequency <sup>(3)</sup>                                 |                                                                                           |                       |       | 200                   |      |  |

|                                              | SYNC frequency range (increase from nominal oscillator frequency)     |                                                                                           | -20%                  |       | 20%                   |      |  |

| PWM                                          |                                                                       | J                                                                                         |                       |       |                       |      |  |

| t <sub>OFF(min)</sub>                        | Minimum off time                                                      |                                                                                           | 90                    | 100   |                       | ns   |  |

| t <sub>ON(min)</sub>                         | Minimum on pulse <sup>(2)</sup>                                       |                                                                                           |                       | 90    | 130                   | ns   |  |

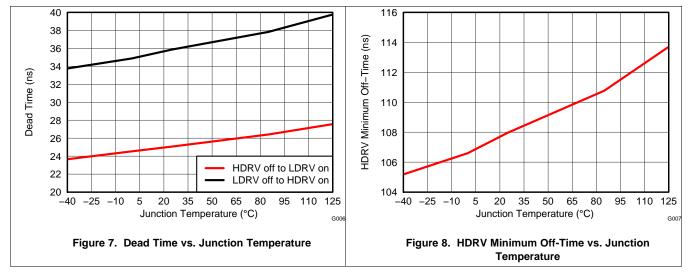

|                                              | · · · · · · · · · · · · · · · · · · ·                                 | HDRV off to LDRV on                                                                       | 15                    | 30    | 45                    |      |  |

| t <sub>DEAD</sub>                            | Output driver dead time                                               | LDRV off to HDRV on                                                                       | 15                    | 30    | 45                    | ns   |  |

| SOFT START                                   |                                                                       |                                                                                           |                       |       |                       |      |  |

|                                              | Soft-start time                                                       | Factory default settings                                                                  | 2.4                   | 2.7   | 3.0                   | ms   |  |

| t <sub>SS</sub>                              | Accuracy over range <sup>(2)</sup>                                    | 600 µs ≤ t <sub>SS</sub> ≤ 9 ms                                                           | -15%                  |       | 15%                   |      |  |

| t <sub>ON(delay)</sub>                       | Turn-on delay time <sup>(4)</sup>                                     | Factory default settings                                                                  |                       | 0     |                       | ms   |  |

| t <sub>OFF(delay)</sub>                      | Turn-off delay time                                                   | Factory default settings                                                                  |                       | 0     |                       | ms   |  |

|                                              | ISE AMPLIFIER                                                         |                                                                                           | - ı                   |       |                       |      |  |

|                                              |                                                                       | $(V_{SNS1} - G_{SNS1}) = 0.6 V$                                                           | -5                    |       | 5                     |      |  |

| V <sub>DIFFO(err)</sub>                      | Error voltage from DIFFO1 to (V <sub>SNS1</sub> - G <sub>SNS1</sub> ) | (V <sub>SNS1</sub> -G <sub>SNS1</sub> ) = 1.2 V                                           | -8                    |       | 8                     | mV   |  |

|                                              |                                                                       | $(V_{SNS1} - G_{SNS1}) = 3.0 V$                                                           | -17                   |       | 17                    |      |  |

| BW                                           | Closed-loop bandwidth <sup>(2)</sup>                                  |                                                                                           | 2                     |       |                       | MHz  |  |

| V <sub>DIFFO(max)</sub>                      | Maximum DIFFOx output voltage                                         |                                                                                           | V <sub>BP6</sub> -0.2 |       |                       | V    |  |

| Birro(max)                                   | Sourcing                                                              |                                                                                           | 1                     |       |                       |      |  |

| IDIFFO                                       | Sinking                                                               |                                                                                           | 1                     |       |                       | mA   |  |

| DRIVERS                                      |                                                                       |                                                                                           |                       |       |                       |      |  |

| R <sub>HS(up)</sub>                          | High-side driver pull-up resistance                                   | $(V_{BOOT} - V_{SW}) = 6.5 \text{ V}, \text{ I}_{HS} = -40 \text{ mA}$                    | 0.8                   | 1.5   | 2.5                   |      |  |

| R <sub>HS(dn)</sub>                          | High-side driver pull-down resistance                                 | $(V_{BOOT} - V_{SW}) = 6.5 \text{ V}, \text{ I}_{HS} = 40 \text{ mA}$                     | 0.5                   | 1.0   | 1.5                   |      |  |

| R <sub>LS(up)</sub>                          | Low-side driver pull-up resistance                                    | $I_{LS} = -40 \text{ mA}$                                                                 | 0.8                   | 1.5   | 2.5                   | Ω    |  |

| R <sub>LS(dn)</sub>                          | Low-side driver pull-down resistance                                  | $I_{LS} = 40 \text{ mA}$                                                                  | 0.35                  | 0.70  | 1.40                  |      |  |

| t <sub>HS(rise)</sub>                        | High-side driver rise time <sup>(2)</sup>                             | $C_{\text{LOAD}} = 5 \text{ nF}$                                                          |                       | 15    |                       |      |  |

| t <sub>HS(fall)</sub>                        | High-side driver fall time <sup>(2)</sup>                             | $C_{LOAD} = 5 \text{ nF}$                                                                 |                       | 10    |                       |      |  |

|                                              | Low-side driver rise time <sup>(2)</sup>                              | $C_{LOAD} = 5 \text{ nF}$                                                                 |                       | 12    |                       | ns   |  |

| t <sub>LS(rise)</sub>                        | Low-side driver fall time <sup>(2)</sup>                              | $C_{LOAD} = 5 \text{ nF}$                                                                 |                       | 10    |                       |      |  |

| t <sub>LS(fall)</sub>                        | NSING AMPLIFIER                                                       |                                                                                           |                       | 10    |                       |      |  |

|                                              | Differential input voltage range                                      | V <sub>CSxP</sub> -V <sub>CSxN</sub>                                                      | -60                   |       | 60                    | mV   |  |

| V <sub>CS(rng)</sub><br>V <sub>CS(cmr)</sub> | Input common-mode range                                               | *CSXP *CSXN                                                                               | 0                     |       | V <sub>BP6</sub> –0.2 | V    |  |

|                                              | Input offset voltage                                                  | $V_{CSxP} = V_{CSxN} = 0 V$                                                               | -3                    |       | v <sub>BP6</sub> 0.2  | mV   |  |

| V <sub>CS(os)</sub>                          | · ·                                                                   | VCSXP - VCSXN - U V                                                                       | -5                    | 15.00 | 3                     | V/V  |  |

| A <sub>CS</sub>                              | Current sensing gain                                                  | $(V_{CSxP}-V_{CSxN}) = 20 \text{ mV}$                                                     | 270                   |       | 220                   |      |  |

| V <sub>CS(out)</sub>                         | Amplfier output<br>Closed-loop bandwidth <sup>(2)</sup>               | $(v_{CSxP} - v_{CSxN}) = 20 \text{ mV}$                                                   | 270                   | 300   | 330                   | mV   |  |

| f <sub>C0</sub>                              |                                                                       |                                                                                           | 3                     | 5     |                       | MHz  |  |

| V <sub>CS(chch)</sub>                        | Amplifier output difference between CH1, CH2                          | $(V_{CS1P} - V_{CS1N}) = (V_{CS2P} - V_{CS2N}) = 20 \text{ mV},$<br>T <sub>J</sub> = 25°C | -5.00%                |       | 5.00%                 |      |  |

|                                              | · · · · · ·                                                           | $(V_{CS1P} - V_{CS1N}) = (V_{CS2P} - V_{CS2N}) = 20 \text{ mV},$<br>T <sub>1</sub> = 85°C | -6.67%                |       | 6.67%                 |      |  |

(3) When using SYNC, the switching frequency is set to one-half the SYNC frequency.

(4) The minimum turn-on delay is 50 µs, when TON\_DELAY is set to a factor of zero.

## **Electrical Characteristics (continued)**

$T_J = -40^{\circ}C$  to 125°C,  $V_{IN} = V_{DD} = 12$  V,  $f_{SW} = 500$  kHz, all parameters at zero power dissipation (unless otherwise noted)

| -                        |                                                                      | TEST CONDITIONS                                                 | MIN         | TYP               | MAX    | UNIT   |

|--------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------|-------------|-------------------|--------|--------|

| CURRENT LI               | МІТ                                                                  |                                                                 |             |                   |        |        |

| t <sub>OFF(oc)</sub>     | Off-time between restart attempts                                    | Hiccup mode                                                     |             | 7×t <sub>SS</sub> |        | ms     |

|                          |                                                                      | Factory default settings                                        |             | 0.488             |        | _      |

| DCR                      | Inductor DCR current sensing calibration value                       | Programmable range                                              | 0.240       | 1                 | 15.500 | mΩ     |

|                          |                                                                      | Factory default settings                                        | · · · · · · | 30                |        |        |

| I <sub>OC(flt)</sub>     | Output current overcurrent fault threshold                           | Programmable range                                              | 3           |                   | 50     | A      |

|                          |                                                                      | Factory default settings                                        |             | 27                |        |        |

| I <sub>OC(warn)</sub>    | Output current overcurrent warning threshold                         | Programmable range                                              | 2           |                   | 49     | A      |

| I <sub>OC(tc)</sub>      | Output current fault/warning temperature coefficient <sup>(2)</sup>  |                                                                 | 3900        | 4000              | 4100   | ppm/°C |

| I <sub>OC(acc)</sub>     | Output warning and fault accuracy                                    | (V <sub>CSxP</sub> -V <sub>CSxN</sub> ) = 30 mV                 | -15%        |                   | 15%    |        |

| PGOOD                    |                                                                      |                                                                 |             |                   |        |        |

| V <sub>FBPGH</sub>       | FB PGOOD high threshold                                              | Factory default settings                                        |             | 675               |        | mV     |

| V <sub>FBPGL</sub>       | FB PGOOD low threshold                                               | Factory default settings                                        |             | 525               |        | mV     |

|                          |                                                                      | $4.5 \text{ V} \le \text{V}_{\text{VDD}} \le 20 \text{ V},$     |             |                   |        |        |

| V <sub>PG(acc)</sub>     | PGOOD accuracy over range                                            | $468 \text{ mV} \le \text{V}_{\text{PGOOD}} \le 675 \text{ mV}$ | -4%         |                   | 4%     |        |

| V <sub>pg(hyst)</sub>    | FB PGOOD hysteresis voltage                                          |                                                                 |             | 25                | 40     | mV     |

| R <sub>PGOOD</sub>       | PGOOD pulldown resistance                                            | $V_{FB} = 0$ , $I_{PGOOD} = 5$ mA                               |             | 40                | 70     | Ω      |

| I <sub>PGOOD(lk)</sub>   | PGOOD pin leakage current                                            | No fault, V <sub>PGOOD</sub> = 5 V                              |             |                   | 20     | μΑ     |

| OUTPUT OVE               | ERVOLTAGE/UNDERVOLTAGE                                               | L                                                               |             |                   |        |        |

| V <sub>FBOV</sub>        | FB pin over voltage threshold                                        | Factory default settings                                        |             | 700               |        | mV     |

| V <sub>FBUV</sub>        | FB pin under voltage threshold                                       | Factory default settings                                        |             | 500               |        | mV     |

| V <sub>UVOV(acc)</sub>   | FB UV/OV accuracy over range                                         | $4.5 \text{ V} \leq \text{V}_{\text{VDD}} \leq 20 \text{ V}$    | -4%         |                   | 4%     |        |

|                          | TAGE TRIMMING AND MARGINING                                          |                                                                 |             |                   |        |        |

| V <sub>FBTM(step)</sub>  | Resolution of FB steps with trim and margin                          |                                                                 |             | 2                 |        | mV     |

| t <sub>FBTM(step)</sub>  | Transition time per trim or margin step                              | After soft-start time                                           |             | 30                |        | μs     |

| V <sub>FBTM(max)</sub>   | Maximum FB voltage with trim and/or margin                           |                                                                 |             | 660               |        | mV     |

| T D T WI(IIIdX)          | Minimum FB voltage with trim or margin only                          |                                                                 |             | 480               |        |        |

| V <sub>FBTM(min)</sub>   | Minimum FB voltage range with trim and margin combined               |                                                                 |             | 420               |        | mV     |

| V <sub>FBMH</sub>        | Margin high FB pin voltage                                           | Factory default settings                                        |             | 660               |        | mV     |

| V <sub>FBML</sub>        | Margin low FB pin voltage                                            | Factory default settings                                        |             | 540               |        | mV     |

|                          | RE SENSE AND THERMAL SHUTDOWN                                        |                                                                 | <u>.</u>    |                   |        |        |

| T <sub>SD</sub>          | Junction thermal shutdown temperature <sup>(2)</sup>                 |                                                                 | 135         | 145               | 155    | °C     |

| T <sub>HYST</sub>        | Thermal shutdown hysteresis <sup>(2)</sup>                           |                                                                 | 15          | 20                | 25     | °C     |

| I <sub>TSNS(ratio)</sub> | Ratio of bias current flowing out of TSNS pin,<br>state 2 to state 1 |                                                                 | 9.7         | 10.0              | 10.3   |        |

| I <sub>TSNS</sub>        | State 1 current out of TSNSx pin <sup>(2)</sup>                      |                                                                 |             | 10                |        | μA     |

| I <sub>TSNS</sub>        | State 2 current out of TSNSx pin <sup>(2)</sup>                      |                                                                 | · · · ·     | 100               |        | μA     |

| V <sub>TSNS</sub>        | Voltage range on TSNSx pin <sup>(2)</sup>                            |                                                                 | 0           |                   | 1.00   | V      |

| T <sub>SNS(acc)</sub>    | External temperature sense accuracy <sup>(2)</sup>                   | 0°C ≤ T <sub>J</sub> ≤ 125°C                                    |             |                   | 5      | °C     |

| T <sub>OT(flt)</sub>     | Overtemperature fault limit <sup>(2)</sup>                           | Factory default settings                                        |             | 145               | 5      | °C     |

| · 01(III)                | OT fault limit range <sup>(2)</sup>                                  |                                                                 | 120         | 110               | 165    | °C     |

| Terr                     | Overtemperature warning limit <sup>(2)</sup>                         | Factory default settings                                        | 120         | 125               | 103    | °C     |

| T <sub>OT(warn)</sub>    | OT warning limit range <sup>(2)</sup>                                | י מסוטיץ עבומטוג שבונוויעש                                      | 100         | 120               | 140    | °C     |

| т                        |                                                                      |                                                                 | 100         | F                 | 140    |        |

| T <sub>OT(step)</sub>    | OT fault/warning step                                                |                                                                 |             | 5                 | ~~~    | 0°     |

| T <sub>OT(hys)</sub>     | OT fault/warning hysteresis <sup>(2)</sup>                           |                                                                 | 15          | 20                | 25     | °C     |

## **Electrical Characteristics (continued)**

$T_J = -40^{\circ}C$  to 125°C,  $V_{IN} = V_{DD} = 12$  V,  $f_{SW} = 500$  kHz, all parameters at zero power dissipation (unless otherwise noted)

|                        | PARAMETER                                                   | TEST CONDITIONS                                                                                   | MIN     | TYP   | MAX   | UNIT |

|------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------|-------|-------|------|

| MEASUREME              | ENT SYSTEM                                                  |                                                                                                   |         |       |       |      |

| M <sub>VOUT(rng)</sub> | Output voltage measurement range (5)                        |                                                                                                   | 0.5     |       | 5.8   | V    |

| M <sub>VOUT(acc)</sub> | Output voltage measurement accuracy                         | V <sub>OUT</sub> = 1.0 V                                                                          | -2.0%   |       | 2.0%  |      |

| . ,                    |                                                             | $V_{CSxP}$ - $V_{CSxN}$ , 0.2440 mΩ ≤ IOUT_CAL_GAIN ≤ 0.5795 mΩ                                   | 0       |       | 24    |      |

| M <sub>IOUT(rng)</sub> | Output current measurement signal range <sup>(5)</sup>      | $V_{CSxP}$ - $V_{CSxN}$ , 0.5796 mΩ ≤ IOUT_CAL_GAIN ≤ 1.1285 mΩ                                   | 0       |       | 40    | mV   |

|                        |                                                             | $V_{CSxP}$ - $V_{CSxN}$ , 1.1286 mΩ ≤ IOUT_CAL_GAIN ≤ 15.5 mΩ                                     | 0       |       | 60    |      |

| M <sub>IOUT(acc)</sub> | Output current measurement accuracy                         | $I_{OUT} \ge 20$ A, DCR = 0.5 m $\Omega$                                                          | -1.0    |       | 1.0   | А    |

| PMBus ADD              | RESSING                                                     |                                                                                                   |         |       |       |      |

| I <sub>ADD</sub>       | Address pin bias current                                    |                                                                                                   | 9.24    | 10.50 | 11.76 | μA   |

| PMBus INTE             | RFACE                                                       |                                                                                                   |         |       |       |      |

| V <sub>IH</sub>        | Input high voltage, CLK, DATA, CNTLx                        |                                                                                                   | 2.1     |       |       | V    |

| V <sub>IL</sub>        | Input low voltage, CLK, DATA, CNTLx                         |                                                                                                   |         |       | 0.8   | V    |

| I <sub>IH</sub>        | Input high level current, CLK, DATA                         |                                                                                                   | -10     |       | 10    | μA   |

| IIL                    | Input low level current, CLK, DATA                          |                                                                                                   | -10     |       | 10    | mA   |

| ICTNL                  | CNTL pin pull-up current                                    |                                                                                                   | · · ·   | 6     |       | μA   |

| V <sub>OL</sub>        | Low-level output voltage, DATA, (5)                         | $4.5 \text{ V} \le \text{V}_{\text{VDD}} \le 20 \text{ V}, \text{ I}_{\text{OUT}} = 4 \text{ mA}$ | · · ·   |       | 0.4   | V    |

| I <sub>OH</sub>        | High-level output open-drain leakage current, DATA, SMBALRT | V <sub>OUT</sub> = 5.5 V                                                                          | 0       |       | 10    | μA   |

| C <sub>OUT</sub>       | Output capacitance, CLK, DATA <sup>(5)</sup>                |                                                                                                   | · · ·   |       | 1     | pF   |

| F <sub>PMB</sub>       | PMBus operating frequency range <sup>(5)</sup>              | Slave mode                                                                                        | 10      |       | 400   | kHz  |

| t <sub>BUF</sub>       | Bus free time between START and STOP <sup>(5)</sup>         |                                                                                                   | 1.3     |       |       | μs   |

| t <sub>HD:STA</sub>    | Hold time after repeated START <sup>(5)</sup>               |                                                                                                   | 0.6     |       |       | μs   |

| t <sub>SU:STA</sub>    | Repeated START setup time <sup>(5)</sup>                    |                                                                                                   | 0.6     |       |       | μs   |

| t <sub>SU:STO</sub>    | STOP setup time <sup>(5)</sup>                              |                                                                                                   | 0.6     |       |       | μs   |

|                        | 5                                                           | Receive mode                                                                                      | 0       |       |       |      |

| t <sub>HD:DAT</sub>    | Data hold time <sup>(5)</sup>                               | Transmit mode                                                                                     | 300     |       |       | ns   |

| t <sub>SU:DAT</sub>    | Data setup time <sup>(5)</sup>                              |                                                                                                   | 100     |       |       | ns   |

| t <sub>TIMEOUT</sub>   | Error signal/detect <sup>(5)</sup>                          |                                                                                                   | 25      |       | 35    | ms   |

| t <sub>LOW:MEXT</sub>  | Cumulative clock low master extend time <sup>(5)</sup>      |                                                                                                   |         |       | 10    | ms   |

| t <sub>LOW:SEXT</sub>  | Cumulative clock low slave extend time <sup>(5)</sup>       |                                                                                                   |         |       | 25    | μs   |

| t <sub>LOW</sub>       | Clock low time <sup>(5)</sup>                               |                                                                                                   | 1.3     |       |       | μs   |

| t <sub>HIGH</sub>      | Clock high time <sup>(5)</sup>                              |                                                                                                   | 0.6     |       |       | μs   |

| t <sub>FALL</sub>      | CLK/DATA fall time <sup>(5)</sup>                           |                                                                                                   | · · · · |       | 300   | ns   |

| t <sub>RISE</sub>      | CLK/DATA rise time <sup>(5)</sup>                           |                                                                                                   |         |       | 300   | ns   |

(5) Specified by design. Not production tested.

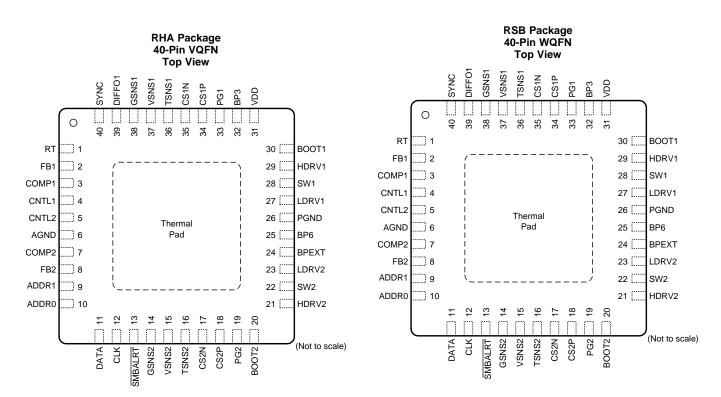

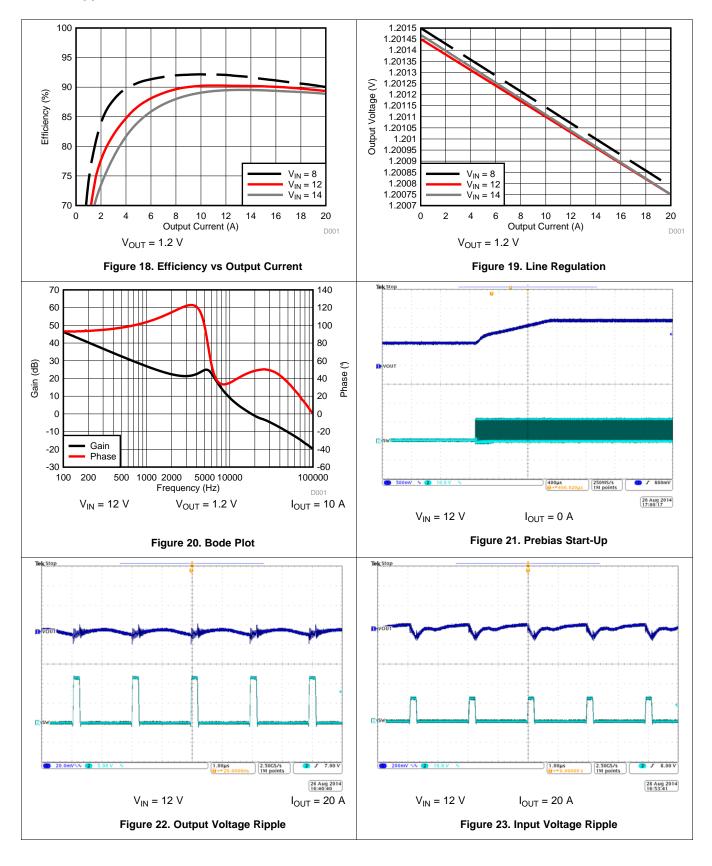

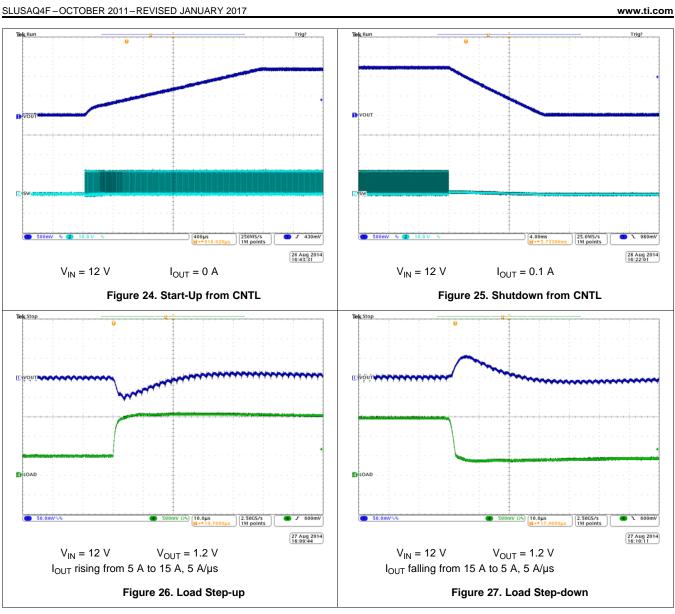

## 7.5 Typical Characteristics

TPS40422 SLUSAQ4F-OCTOBER 2011-REVISED JANUARY 2017

www.ti.com

## **Typical Characteristics (continued)**

## 8 Detailed Description

## 8.1 Overview

The device is a flexible synchronous buck controller. It can be used as a dual-output controller, or as a twophase single-output controller. It operates with a wide input range from 4.5 V to 20 V and generates accurate regulated output as low as 600 mV.

In dual output mode, voltage mode control with input feed-forward architecture is implemented. With this architecture, the benefits are less noise sensitivity, no control instability issues for small DCR applications, and a smaller minimum controllable on-time, often desired for high conversion ratio applications.

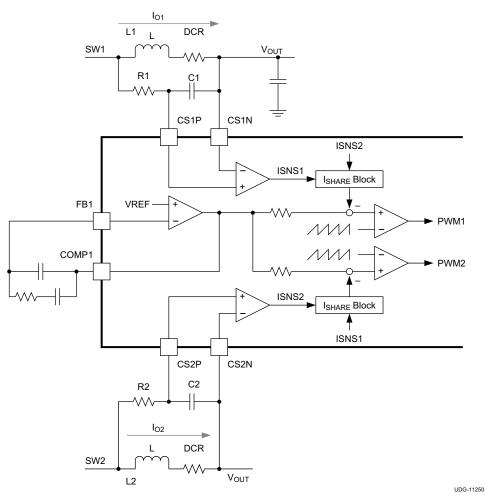

In two-phase single-output mode, a current-sharing loop is implemented to ensure a balance of current between phases. Because the induced error current signal to the loop is much smaller when compared to the PWM ramp amplitude, the control loop is modeled as voltage mode with input feed-forward.

## DESIGN NOTE

To operate the device in two-phase mode, tie the FB2 pin to the BP6 pin and tie the COMP1 pin to the COMP2 pin. These connections must be made before applying voltage to the VDD pin.

(See the *Two-Phase Mode Operation* section for more information)

TPS40422 SLUSAQ4F – OCTOBER 2011 – REVISED JANUARY 2017

### www.ti.com

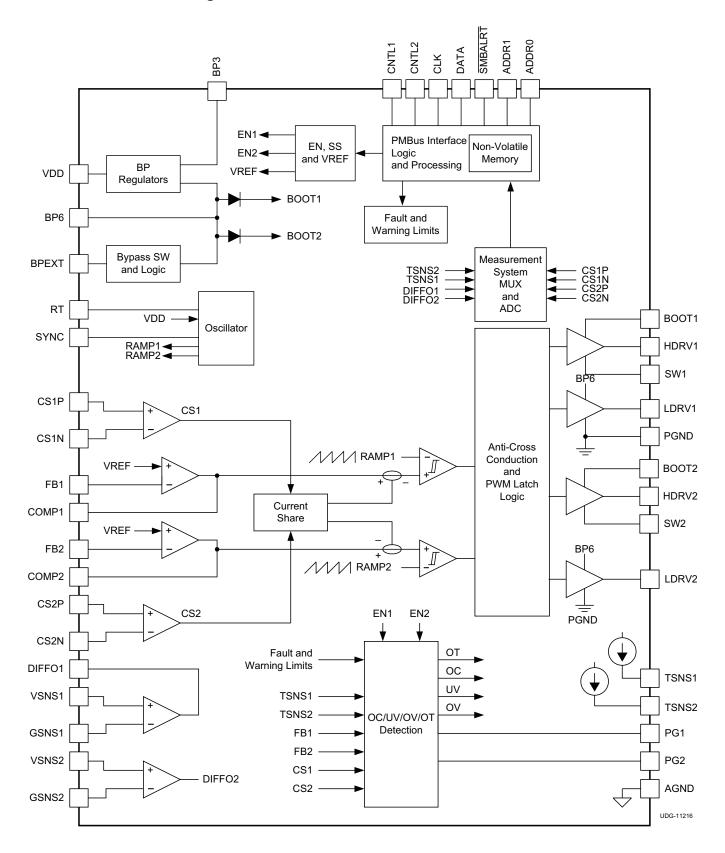

## 8.2 Functional Block Diagram

## 8.3 Feature Description

### 8.3.1 PMBus Interface Protocol General Description

Timing and electrical characteristics of the PMBus protocol can be found in the PMB Power Management Protocol Specification, Part 1, revision 1.1 available at http://pmbus.org. The device supports both the 100 kHz and 400 kHz bus timing requirements. The device does not stretch pulses on the PMBus interface when communicating with the master device.

Communication over the PMBus interface can either support the Packet Error Checking (PEC) scheme or not. If the master supplies CLK pulses for the PEC byte, it is used. If the CLK pulses are not present before a STOP, the PEC is not used.

The device supports a subset of the commands in the PMBus 1.1 specification. Most controller parameters can be programmed using the PMBus interface and stored as defaults for later use. All commands that require data input or output use the linear format. The exponent of the data words is fixed at a reasonable value for the command and altering the exponent is not supported. Direct format data input or output is not supported by the device. See the *Supported Commands* section for specific details.

The device also supports the SMBALERT response protocol. The SMBALERT response protocol is a mechanism by which a slave (the device) can alert the bus master that it wants to talk. The master processes this event and simultaneously accesses all slaves on the bus (that support the protocol) through the alert response address. Only the slave that caused the alert acknowledges this request. The host performs a modified receive byte operation to get the slave's address. At this point, the master can use the PMBus status commands to query the slave that caused the alert. For more information on the SMBus alert response protocol, see the System Management Bus (SMBus) specification.

The device uses non-volatile memory to store configuration settings and scale factors. However, the device does not automatically save the programmed settings into this non-volatile memory. The STORE\_USER\_ALL command must be used to commit the current settings to non-volatile memory as device defaults. The detailed description of each setting notes if it is able to be stored in non-volatile memory.

#### 8.3.2 Voltage Reference

The 600-mV bandgap cell connects internally to the non-inverting input of the error amplifier. The device trims the reference voltage by using the error amplifier in a unity gain configuration to remove amplifier offset from the final regulation voltage. The 0.5-% tolerance on the reference voltage allows the user to design a very accurate power supply.

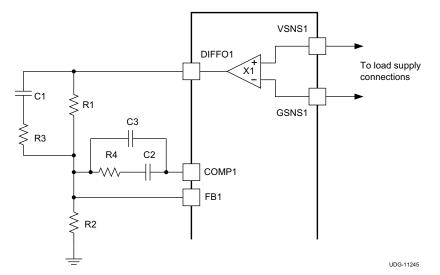

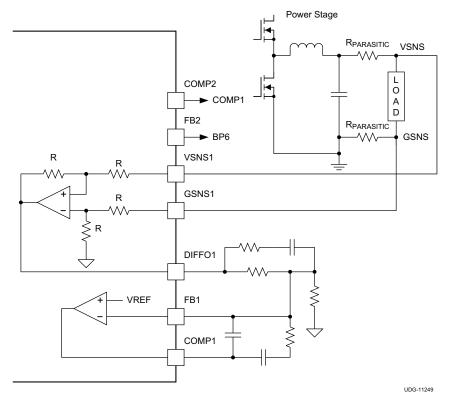

## 8.3.3 Output Voltage

The device sets the output voltage in a way that is very similar to a traditional analog controller by using a voltage divider from the output to the FB (feedback) pin. The output voltage must be divided down to the nominal reference voltage of 600 mV. Figure 9 shows the typical connections for the controller. The device senses the voltage at the load by using the unity gain differential voltage sense amplifier. This functionality provides better load regulation for output voltages lower than 5-V nominal (see the *Electrical Characteristics* table for the maximum output voltage specification for the differential sense amplifier). For output voltages above this level, connect the output voltage directly to the junction of R1 and C1, leave DIFFO1 open, and do not connect the VSNS1 pin to the output voltage. The differential amplifier may also be used elsewhere in the overall system as a voltage buffer, provided the electrical specifications are not exceeded.

## Feature Description (continued)

Figure 9. Setting the Output Voltage

The components shown in Figure 9 that determine the nominal output voltage are R1 and R2. In most cases, choose a value for R to ensure the feedback compensation values (R3, R4, C1, C2 and C3) come close to readily available standard values. A value for R2 is then calculated in Equation 1.

$$R2 = V_{FB} \times \left(\frac{R1}{\left(V_{OUT} - V_{FB}\right)}\right)$$

where

- V<sub>FB</sub> is the feedback voltage

- V<sub>OUT</sub> is the desired output voltage

- R1 and R2 are in the same unit

(1)

## DESIGN NOTE

There is no DIFFO2 pin. In dual-output mode, VSNS2 and GSNS2 are connected to the load for channel 2 and the device uses the DIFFO2 signal internally to provide voltage monitoring. Connect the output directly to the junction of R1 and C1 for channel 2 to set the output voltage and for feedback.

The DIFFO1 pin operates at voltages up to ( $V_{BP6}$ –0.2 V). If the voltage between the VSNS1 and GSNS1 pins is higher than ( $V_{BP6}$ –0.2 V) during any condition, the output voltage moves out of regulation because the DIFFO1 voltage is limited by BP6. To prevent this from happening, the BP6 voltage must be pre-biased before the PWM turns on, and ( $V_{BP6}$ –0.2 V) must remain higher than the voltage between the VSNS1 and GSNS1 pins until the PWM turns off.

The feedback voltage can be changed to a value between -30% and +10% from the nominal 600 mV using PMBus commands. This adjustment allows the output voltage to vary by the same percentage. See the *Supported PMBus Commands* section for more details.

## 8.3.4 Voltage Feed Forward

The device uses input-voltage feed-forward topology that maintains a constant power stage gain when the input voltage varies. It also provides for very good response to input voltage transient disturbances. The constant power stage gain of the controller greatly simplifies feedback loop design because loop characteristics remain constant as the input voltage changes, unlike a buck converter without voltage feed-forward topology. For modeling purposes, the gain from the COMP pin to the average voltage at the input of the L-C filter is 8.2 V/V.

Copyright © 2011–2017, Texas Instruments Incorporated

**NSTRUMENTS**

FXAS

## Feature Description (continued)

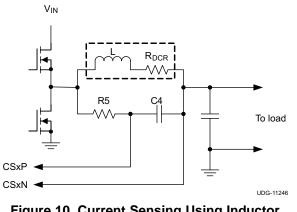

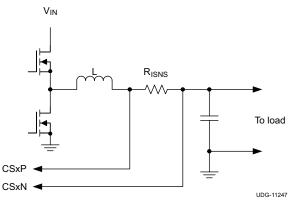

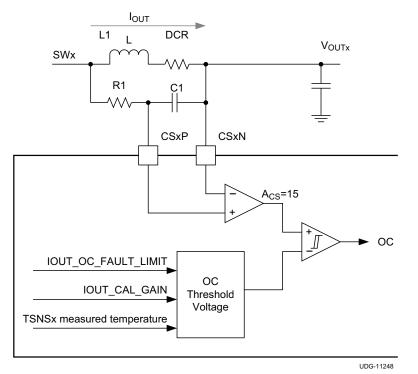

## 8.3.5 Current Sensing

The device uses a differential current-sense scheme to sense the output current. The sense element can be either the series resistance of the power stage filter inductor or a separate current sense resistor. When using the inductor series resistance as in Figure 10, a filter must be used to remove the large AC component of voltage across the inductor and leave only the component of the voltage that appears across the resistance of the R-C filter should be equal to or greater than the time constant of the inductor itself. If the time constants are equal, the voltage appearing across C4 is the current in the inductor multiplied the inductor resistance. The voltage across C4 perfectly reflects the inductor ripple current. Therefore, there is no need to have a shorter R-C time constant.