TPS51427A

www.ti.com

SLUS843B-MAY 2008-REVISED SEPTEMBER 2008

# DUAL D-CAP™ SYNCHRONOUS STEP-DOWN CONTROLLER FOR NOTEBOOK POWER RAILS

# FEATURES

- Fixed-Frequency Emulated On-Time Control; Frequency Selectable from Three Options

- D-CAP<sup>™</sup> Mode Enables Fast Transient Response Less than 100 ns

- Advanced Ramp Compensation Allows Low

Output Ripple with Minimal Jitter

- Selectable PWM-Only/OOA™/Auto-Skip Modes

- Wide Input Voltage Range: 5.5 V to 28 V

- Dual Fixed or Adjustable SMPS:

- 0.7 V to 5.9 V (Channel1)

- 0.5 V to 2.5 V (Channel2)

- Fixed 3.3-V/5-V, or Adjustable Output 0.7-V to 4.5-V LDO; Capable of Sourcing 100 mA

- Fixed 3.3-VREF Output Capable of Sourcing 10 mA

- Temperature Compensated Low-Side R<sub>DS(on)</sub> Current Sensing

- Adaptive Gate Drivers with Integrated Boost

Switch

- Bootstrap Charge Auto Refresh

- Integrated Soft Start, Tracking Soft Stop

- Independent PGOOD and EN for Each Channel

- OOB Function Disabled. Refer to TPS51427 for OOB-Enabled Device

# **APPLICATIONS**

- Notebook I/O and System Bus Rails

- Graphics Application

- PDAs and Mobile Communication Devices

# DESCRIPTION

The TPS51427A is a dual synchronous step-down controller designed for notebook and mobile communications applications. This device is part of a low-cost suite of notebook power bus regulators that enables system designs with low external component counts. The TPS51427A includes two pulse-width-modulation (PWM) controllers, SMPS1 and SMPS2. The output of SMPS1 can be adjusted from 0.7 V to 5.9 V, while the output of SMPS2 can be adjusted from 0.5 V to 2.5 V. This device also features a low-dropout (LDO) regulator that provides a 5-V/3.3-V output, or adjustable from 0.7-V to 4.5-V output via LDOREFIN. The fixed-frequency emulated adaptive on-time control supports seamless operation between PWM mode under heavy load conditions and reduced frequency operation at light loads for high-efficiency down to the milliampere range. An integrated boost switch enhances the high-side MOSFET to further improve efficiency. The main control loop is the D-CAP™ mode that is optimized for low equivalent series resistance (ESR) output capacitors such as POSCAP or SP-CAP. Advanced ramp compensation minimizes jitter without degrading line and load regulation. R<sub>DS(on)</sub> current sensing methods offers maximum cost saving.

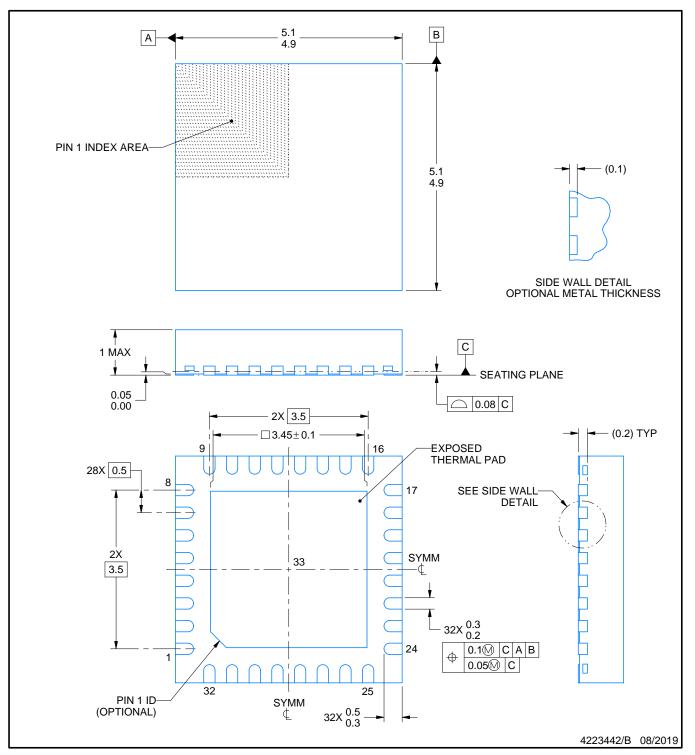

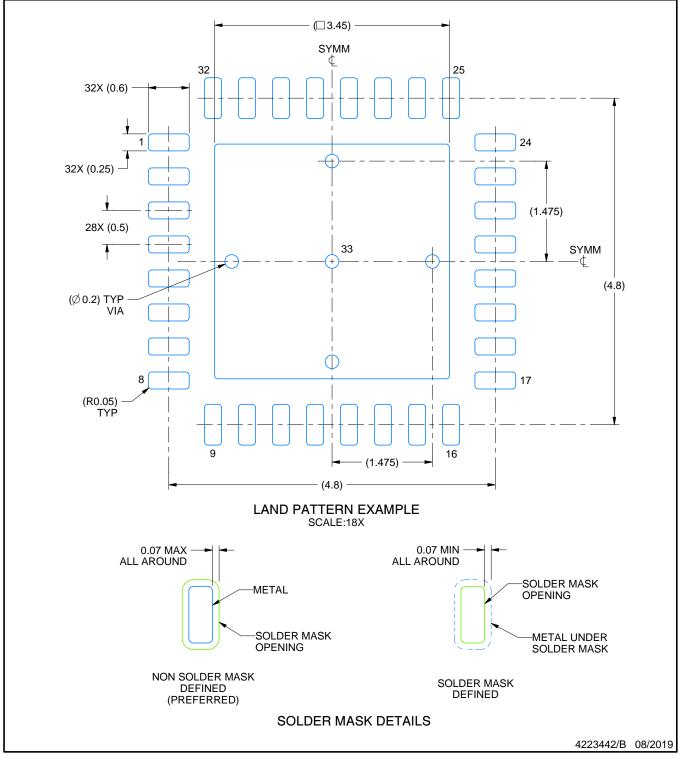

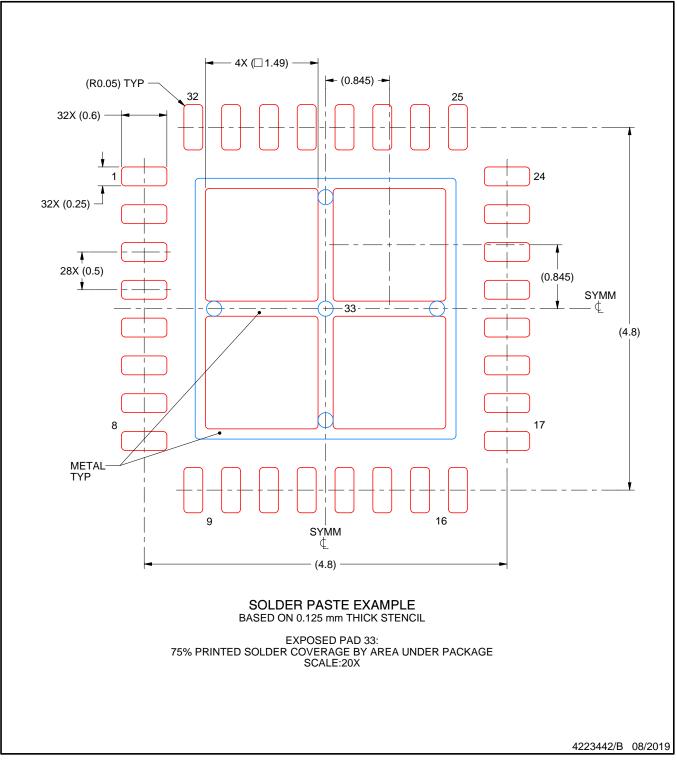

The TPS51427A supports supply input voltages that range from 5.5 V to 28 V. It is available in the 32-pin, 5-mm  $\times$  5-mm QFN package (Green, RoHscompliant, and Pb-free). The device is specified from -40°C to +85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

D-CAP, OOA are trademarks of Texas Instruments. All other trademarks are the property of their respective owners.

**EXAS**

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION<sup>(1)</sup>

| T <sub>A</sub> | PACKAGE                                          | ORDERABLE<br>PART NO. | TRANSPORT MEDIA | QUANTITY | ECO STATUS <sup>(2)</sup> |

|----------------|--------------------------------------------------|-----------------------|-----------------|----------|---------------------------|

|                | 40°C to +85°C Plastic Quad Flatpack (32-pin QFN) | TPS51427ARHBT         |                 | 250      | Green                     |

| –40°C to +85°C |                                                  | TPS51427ARHBR         | Tape and Reel   | 3000     | (RoHs and No<br>Sb/Br)    |

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) Eco-Status information: Additional details including specific material content can be accessed at www.ti.com/leadfree GREEN: Ti defines Green to mean Lead (Pb)-Free and in addition, uses less package materials that do not contain halogens, including bromine (Br), or antimony (Sb) above 0.1% of total product weight.

N/A: Not yet available Lead (Pb)-Free; for estimated conversion dates, go to www.ti.com/leadfree.

**Pb-FREE:** Ti defines Lead (Pb)-Free to mean RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and, if designed to be soldered, suitable for use in specified lead-free soldering processes.

#### SLUS843B-MAY 2008-REVISED SEPTEMBER 2008

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range; all voltages are with respect to GND (unless otherwise noted).

|                                        | PARAMETER                                                                          | VALUE                  | UNIT |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------|------------------------|------|--|--|--|

| 5V voltage range                       | V5DRV, V5FILT                                                                      | -0.3 to 7              |      |  |  |  |

|                                        | VIN, ENLDO                                                                         | -0.3 to 30             |      |  |  |  |

|                                        | VBST1, VBST2                                                                       | -0.3 to 37             |      |  |  |  |

| Input voltage range <sup>(2)</sup>     | VBST1, VBST2 (w.r.t. LLx)                                                          | -0.3 to 7              | V    |  |  |  |

| input voltage range                    | EN1, EN2, VOUT1, VOUT2, VFB1, REFIN2, TRIP1, TRIP2, SKIPSEL, TONSEL, VSW, LDOREFIN | -0.3 to 7              |      |  |  |  |

|                                        | TRIP1, TRIP2                                                                       | -0.3 to (V5FILT + 0.3) |      |  |  |  |

|                                        | DRVH1, DRVH2                                                                       | -2 to 37               |      |  |  |  |

|                                        | DRVH1, DRVH2 (w.r.t. LLx)                                                          | -0.3 to 7              |      |  |  |  |

| Output voltage<br>range <sup>(2)</sup> | LL1, LL2                                                                           | -2 to 30               | V    |  |  |  |

| lange                                  | DRVL1, DRVL2, VREF2, PGOOD1, PGOOD2, LDO, VREF3                                    | -0.3 to 7              |      |  |  |  |

|                                        | PGND                                                                               | -0.3 to 0.3            |      |  |  |  |

| T <sub>stg</sub> Storage tempera       | T <sub>stg</sub> Storage temperature range -55 to +150                             |                        |      |  |  |  |

| T <sub>J</sub> Junction tempe          | rature range                                                                       | +150                   | °C   |  |  |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal unless otherwise noted.

## DISSIPATION RATINGS<sup>(1)</sup>

| PACKAGE        | T <sub>A</sub> < +25°C | DERATING FACTOR              | T <sub>A</sub> = +85°C |

|----------------|------------------------|------------------------------|------------------------|

|                | POWER RATING           | ABOVE T <sub>A</sub> = +25°C | POWER RATING           |

| 32Ld 5 × 5 QFN | 2.320 W                | 23.2 mW/°C                   | 0.93 W                 |

(1) Dissipation ratings are calculated based on the usage of nine standard thermal vias and thermal pad soldered on the PCB. If thermal pad is not soldered to the PCB, the junction-to-ambient thermal resistance is 88.6°C/W.

# **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range (unless otherwise noted).

|                              |                                                                                   | MIN  | TYP | MAX | UNIT |

|------------------------------|-----------------------------------------------------------------------------------|------|-----|-----|------|

| Supply input voltage range   | V5DRV, V5FILT                                                                     | 4.5  |     | 5.5 | V    |

| Input voltage range          | VBST1, VBST2                                                                      | -0.1 |     | 34  |      |

|                              | VBST1, VBST2 (with regard to LLx)                                                 | -0.1 |     | 5.5 |      |

|                              | EN1, EN2, VOUT1, VFB1, REFIN2, TRIP1, TRIP2, SKIPSEL, TONSEL, ENLDO,VSW, LDOREFIN | -0.1 |     | 5.5 |      |

|                              | VOUT2                                                                             | -0.1 |     | 3.7 |      |

| Output voltage range         | DRVH1, DRVH2                                                                      | -0.8 |     | 34  | V    |

|                              | DRVH1, DRVH2 (w.r.t. LLx)                                                         | -0.1 |     | 5.5 |      |

|                              | LL1, LL2                                                                          | -0.8 |     | 28  |      |

|                              | DRVL1, DRVL2, VREF2, PGOOD1, PGOOD2, LDO, VREF3                                   | -0.1 |     | 5.5 |      |

|                              | PGND                                                                              | -0.1 |     | 0.1 |      |

| Operating free-air temperatu | ire, T <sub>A</sub>                                                               | -40  |     | +85 | °C   |

## Texas Instruments

www.ti.com

# **ELECTRICAL CHARACTERISTICS**

Over recommended free-air temperature range,  $V_{V5DRV} = 5 \text{ V}$ ,  $V_{VIN} = 12 \text{ V}$  (unless otherwise noted).

| PARAMETER                               | TEST CONDITIONS                                                                                                                                                                                                             | MIN              | TYP    | MAX              | UNIT |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|------------------|------|

| INPUT SUPPLIES                          |                                                                                                                                                                                                                             |                  |        |                  |      |

| VIN Input Voltage Range                 | LDO in regulation                                                                                                                                                                                                           | 5.5              |        | 28               | V    |

| VIN Operating Supply Current            | LDO switched over to VSW, 4.5-V to 5.5-V SMPS                                                                                                                                                                               |                  | 5      | 10               | μA   |

| VIN Standby Current                     | 5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V, T <sub>A</sub> = +25°C, no load, EN_LDO = 5 V, EN1 = EN2 = VSW = 0 V                                                                                                             |                  | 115    | 150              | μΑ   |

| VIN Shutdown Current                    | 5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V, T <sub>A</sub> = +25°C, no load, EN_LDO = EN1 = EN2 = VSW = 0 V                                                                                                                  |                  | 12     | 20               | μΑ   |

| Quiescent Power Consumption             | $\label{eq:transformation} \begin{array}{l} T_A = +25^\circ C, \mbox{ no load, EN_LDO} = EN1 = EN2 = REFIN2 \\ = 5 \mbox{ V, VFB1} = SKIPSEL = 0 \mbox{ V, VOUT1} = VSW = 5.3 \mbox{ V, VOUT2} = 3.5 \mbox{ V} \end{array}$ |                  | 5      | 7                | mW   |

| PWM CONTROLLERS                         | · · · ·                                                                                                                                                                                                                     |                  |        |                  |      |

|                                         | 5-V Preset output: 5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V,<br>VFB1 = 0 V, SKIPSEL = 5 V                                                                                                                                  | 4.975<br>(–1.5%) | 5.05   | 5.125<br>(+1.5%) |      |

| VOUT1 Output Voltage Accuracy           | 1.5-V Preset output: 5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V,<br>VFB1 = 5V, SKIPSEL = 5V                                                                                                                                  | 1.482<br>(–1.2%) | 1.50   | 1.518<br>(+1.2%) | V    |

|                                         | Adjustable feedback output,<br>5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V, SKIPSEL = 5 V                                                                                                                                     | 0.693<br>(–1%)   | 0.70   | 0.707<br>(+1%)   |      |

| VOUT1 Voltage Adjust Range              |                                                                                                                                                                                                                             | 0.707            |        | 5.900            | V    |

|                                         | 5-V Preset output                                                                                                                                                                                                           |                  |        | 0.20             | V    |

| VFB1 Threshold Voltage                  | 1.5-V Preset output                                                                                                                                                                                                         | 3.90             |        |                  | V    |

| VFB1 Input Current                      | VFB1 = 0.8 V                                                                                                                                                                                                                | -0.20            |        | 0.20             | μA   |

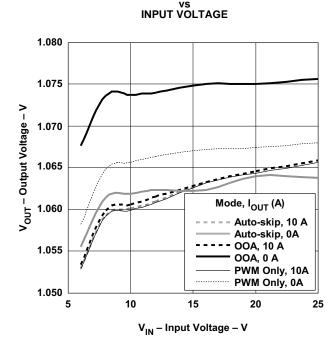

|                                         | 3.3-V Preset output: REFIN2 = 5 V, 5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V, SKIPSEL = 5 V                                                                                                                                 | 3.285<br>(–1.4%) | 3.33   | 3.375<br>(+1.4%) |      |

| VOUT2 Output Voltage Accuracy           | 1.05-V Preset output: REFIN2 = 3.3 V,<br>5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V, SKIPSEL= 5 V                                                                                                                            | 1.038<br>(-1.2%) | 1.05   | 1.062<br>(+1.2%) | V    |

|                                         | Tracking output: REFIN2 = 1.0 V, 5.5 V $\leq$ V <sub>VIN</sub> $\leq$ 28 V, SKIPSEL = 5 V                                                                                                                                   | 0.99<br>(-1%)    | 1.00   | 1.01<br>(+1%)    |      |

| REFIN2 Voltage Adjust Range             |                                                                                                                                                                                                                             | 0.50             |        | 2.50             | V    |

| REFIN2 Input Current                    | $0.5 \text{ V} \le \text{V}_{\text{VREFIN2}} \le 2.5 \text{ V}$                                                                                                                                                             | -0.2             |        | 0.2              | μA   |

|                                         | 1.05-V Preset output                                                                                                                                                                                                        | 3.00             |        | 3.45             |      |

| REFIN2 Threshold Voltage                | 3.3-V Preset output                                                                                                                                                                                                         | 3.90             |        |                  | V    |

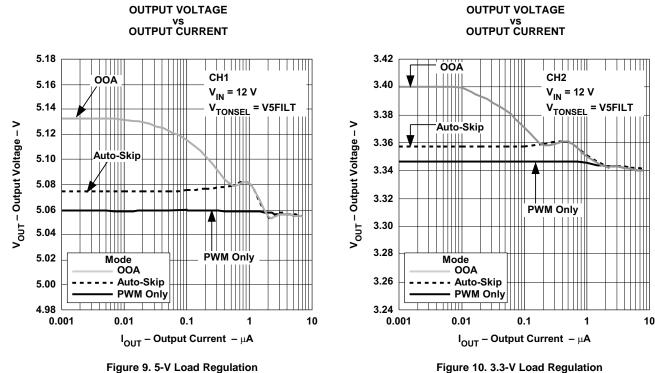

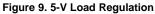

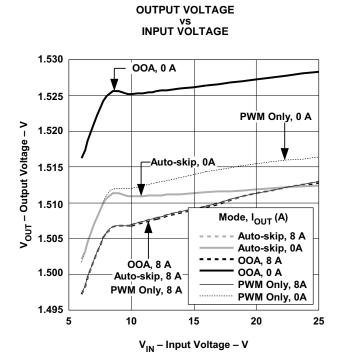

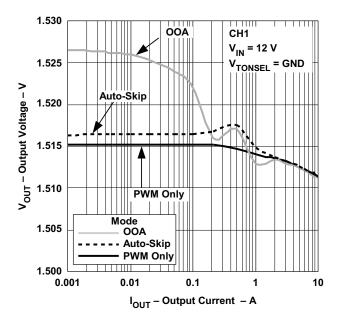

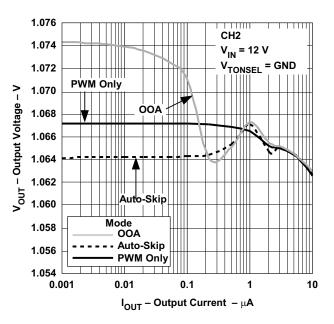

|                                         | Either SMPS, SKIPSEL = 5 V, 0 A to 5 $A^{(1)}$                                                                                                                                                                              |                  | -0.10% |                  |      |

| DC Load Regulation                      | Either SMPS, SKIPSEL = 2 V, 0 A to 5 A <sup>(1)</sup>                                                                                                                                                                       |                  | -2.20% |                  |      |

|                                         | Either SMPS, SKIPSEL = GND, 0 A to 5 A <sup>(1)</sup>                                                                                                                                                                       |                  | -0.50% |                  |      |

| Line Regulation                         | Either SMPS, 5.5 V < VIN < 28 V <sup>(1)</sup>                                                                                                                                                                              |                  | 0.005  |                  | %/V  |

| Channel1 On-Time                        | TONSEL = 0 V, 2 V, or OPEN (400 kHz),<br>VOUT1 = 5.05 V                                                                                                                                                                     | 895              | 1052   | 1209             | ns   |

|                                         | TONSEL = 5 V (200 kHz), VOUT1 = 5.05 V                                                                                                                                                                                      | 1895             | 2105   | 2315             |      |

|                                         | TONSEL = 0 V (500 kHz), VOUT2 = 3.33 V                                                                                                                                                                                      | 475              | 555    | 635              |      |

| Channel2 On-Time                        | TONSEL = 2 V, OPEN, or 5 V (300 kHz),<br>VOUT2 = 3.33 V                                                                                                                                                                     | 833              | 925    | 1017             | ns   |

| Minimum Off-Time                        |                                                                                                                                                                                                                             | 300              | 400    | 500              | ns   |

| Soft Start Ramp Time                    | Zero to full limit                                                                                                                                                                                                          |                  | 1.8    |                  | ms   |

| VOUT1, VOUT2 Discharge On<br>Resistance | EN1 = EN2 = 0 V, VOUT1 = VOUT2 = 0.5 V                                                                                                                                                                                      |                  | 17     | 35               | Ω    |

| OOA Operating Frequency                 | SKIPSEL = 2 V or OPEN                                                                                                                                                                                                       | 22               | 30     |                  | kHz  |

(1) Ensured by design. Not production tested.

www.ti.com

# ELECTRICAL CHARACTERISTICS (continued)

Over recommended free-air temperature range,  $V_{V5DRV} = 5 \text{ V}$ ,  $V_{VIN} = 12 \text{ V}$  (unless otherwise noted).

| PARAMETER                                        | TEST CONDITIONS                                                           | MIN              | TYP             | MAX              | UNIT |  |

|--------------------------------------------------|---------------------------------------------------------------------------|------------------|-----------------|------------------|------|--|

| LINEAR REGULATOR (LDO)                           |                                                                           |                  |                 |                  |      |  |

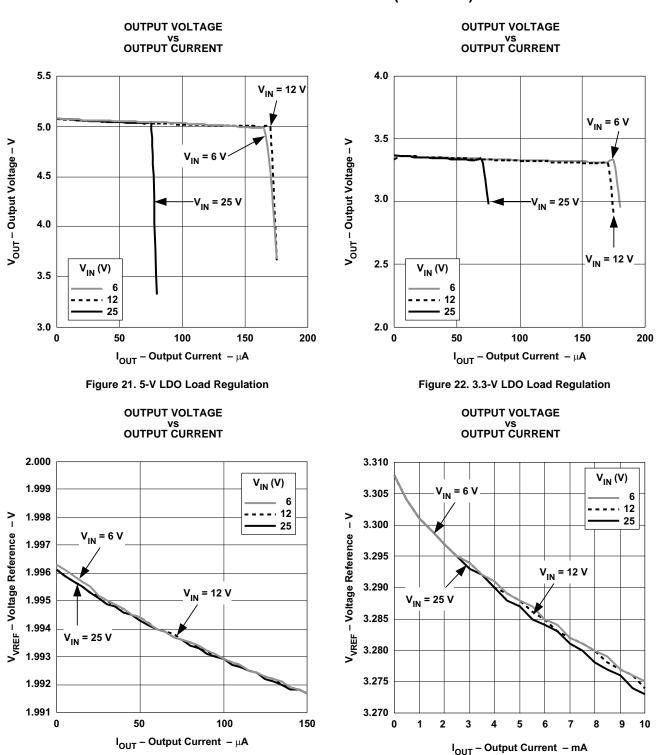

|                                                  | LDOREFIN = VSW = 0 V, 0 < I <sub>LDO</sub> < 10 0mA,<br>6 V< VIN< 28 V    | 4.94<br>(-1.7%)  | 5.025           | 5.11<br>(+1.7%)  |      |  |

| LDO Output Voltage                               | LDOREFIN = 5 V, VSW = 0 V, 0 < $\rm I_{LDO}$ < 100 mA, 5.5 V < VIN < 28 V | 3.28<br>(–1.5%)  | 3.33            | 3.38<br>(+1.5%)  | V    |  |

|                                                  | LDOREFIN = 0.5 V, VSW = 0 V, 0 < $I_{LDO}$ < 50 mA, 5.5V < VIN < 28 V     | 0.98<br>(–2%)    | 1.00            | 1.02<br>(+2%)    |      |  |

| LDOREFIN Input Range                             | VLDO = 2 × VLDOREFIN                                                      | 0.35             |                 | 2.25             | V    |  |

| LDOREFIN Leakage Current                         | VLDOREFIN = 0 V or 5 V                                                    | -0.5             |                 | 0.5              | μΑ   |  |

| LDOREFIN Threshold Voltage                       | Fixed LDO = 5 V                                                           |                  |                 | 0.15             | V    |  |

| LOOREFIN THreshold voltage                       | Fixed LDO = 3.3 V                                                         | 3.90             |                 |                  | v    |  |

| LDO Output Current                               | VSW = GND , VIN = 5.5 V to 28 V                                           |                  |                 | 100              | mA   |  |

| LDO Output Current During<br>Switchover to 5 V   | VSW = 5 V , VIN = 5.5 V to 28 V, LDOREFIN = 0 V                           |                  | 340             | 500              | mA   |  |

| LDO Output Current During<br>Switchover to 3.3 V | VSW = 3.3 V , VIN = 5.5 V to 28 V, LDOREFIN = 5 V                         |                  | 330             | 500              | mA   |  |

| LDO Short-Circuit Current                        | VSW = LDO = 0 V                                                           | 140              | 180             | 220              | mA   |  |

| LDO 5-V Switchover Threshold                     | Rising edge of VSW, LDOREFIN = 0 V                                        | 4.63<br>(92.6%)  | 4.78<br>(95.6%) | 4.93<br>(98.6%)  | V    |  |

|                                                  | Hysteresis                                                                |                  | 0.20            |                  |      |  |

| LDO 3.3-V Switchover Threshold                   | Rising edge of VSW, LDOREFIN = 5 V                                        | 3.05<br>(92.5%)  | 3.15<br>(95.5%) | 3.25<br>(98.5%)  | V    |  |

|                                                  | Hysteresis                                                                |                  | 0.150           |                  |      |  |

| LDO Switchover Switch On Resistance              | LDO to VSW, VSW = 5 V, ILDO = 100 mA                                      |                  | 0.7             | 1.5              | Ω    |  |

| LDO Switchover Delay                             | Turning on                                                                |                  | 3.96            |                  | ms   |  |

| LDO Undervoltage Lockout                         | Falling edge of V5FILT                                                    | 3.80             | 3.93            | 4.10             | V    |  |

| Threshold                                        | Rising edge of V5FILT                                                     | 4.20             | 4.37            | 4.50             | V    |  |

| VIN POR Threshold                                | Falling edge of VIN                                                       |                  | 1.8             |                  | V    |  |

| VIN FOR Threshold                                | Rising edge of VIN                                                        |                  | 2.1             |                  | V    |  |

| Thermal-Shutdown Threshold                       | Hysteresis = +10°C <sup>(2)</sup>                                         |                  | +140            |                  | °C   |  |

| 3.3V ALWAYS-ON LINEAR REGU                       | JLATOR (VREF3)                                                            |                  |                 | <u>.</u>         |      |  |

|                                                  | No external load, $V_{VSW}$ > 4.5 V                                       | 3.250<br>(–1.5%) | 3.300           | 3.350<br>(+1.5%) | V    |  |

| VREF3 Output Voltage                             | No external load, V <sub>VSW</sub> < 4.0 V                                | 3.220<br>(–2.4%) | 3.300           | 3.380<br>(+2.4%) | 30   |  |

| VREF3 Load Regulation                            | 0 mA < I <sub>LOAD</sub> < 10 mA                                          |                  |                 | 60               | mV   |  |

| VREF3 Current Limit                              | VREF3 = GND                                                               |                  | 15              | 20               | mA   |  |

| VREF3 Undervoltage Lockout                       | Falling edge of VREF3                                                     |                  | 2.96            |                  |      |  |

| Threshold                                        | Hysteresis                                                                |                  | 0.17            |                  | V    |  |

(2) Ensured by design. Not production tested.

# **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended free-air temperature range,  $V_{V5DRV}$  = 5 V,  $V_{VIN}$  = 12 V (unless otherwise noted).

| PARAMETER                               | TEST CONDITIONS                                                              | MIN               | TYP    | MAX               | UNIT |

|-----------------------------------------|------------------------------------------------------------------------------|-------------------|--------|-------------------|------|

| REFERENCE (REF)                         |                                                                              |                   |        | <u>i</u>          |      |

| VREF2 Output Voltage                    | I <sub>VREF2</sub>   = 0 μA                                                  | 1.98<br>(–1%)     | 2.00   | 2.02<br>(+1%)     | V    |

| VNET 2 Oulput Voltage                   | I <sub>VREF2</sub>   < 50 μΑ                                                 | 1.975<br>(–1.25%) | 2.00   | 2.025<br>(+1.25%) | v    |

| VREF2 Sink Current                      | VREF2 in regulation                                                          | 50                |        |                   | μΑ   |

| VREF2 Undervoltage Lockout              | Falling edge of VREF2                                                        | 1.575             | 1.700  | 1.825             | V    |

| Threshold                               | Hysteresis                                                                   |                   | 0.1    |                   | v    |

| OUT1 FAULT DETECTION                    |                                                                              |                   |        |                   |      |

| Overvoltage Trip Threshold              | VFB1 with respect to nominal regulation point                                | +12.5%            | +15%   | +17.5%            |      |

| Overvoltage Fault Propagation<br>Delay  | VFB1 delay with 50-mV overdrive                                              |                   | 10     |                   | μs   |

| Undervoltage Trip Threshold             | VFB1 with respect to nominal output voltage                                  | -35%              | -30%   | -25%              |      |

| Undervoltage Fault Propagation<br>Delay |                                                                              | 0.8               | 1      | 1.2               | ms   |

| Undervoltage Fault Enable Delay         | From ENx signal                                                              | 10                | 20     | 30                | ms   |

| PGOOD1 Lower Trip Threshold             | VFB1 with respect to nominal output, falling edge, typical hysteresis = 5%   | -12.5%            | -10%   | -7.5%             |      |

| PGOOD1 Low Propagation Delay            | Falling edge, 50-mV overdrive                                                |                   | 10     |                   | μs   |

| PGOOD1 High Propagation Delay           | Rising edge, 50-mV overdrive                                                 | 0.8               | 1.0    | 1.2               | ms   |

| PGOOD1 Output Low Voltage               | PGOOD1 Low impedance, I <sub>SINK</sub> = 4 mA                               |                   | 0.4    | 0.8               | V    |

| PGOOD1 Leakage Current                  | PGOOD1 High impedance, forced to 5.5 V                                       |                   |        | 1                 | μA   |

| OUT2 FAULT DETECTION                    |                                                                              | - <u>r</u>        |        |                   |      |

| Overvoltage Trip Threshold              | REFIN2 with respect to nominal regulation point                              | +12.5%            | +15.0% | +17.5%            |      |

| Overvoltage Fault Propagation<br>Delay  | REFIN2 delay with 50-mV overdrive                                            |                   | 10     |                   | μs   |

| Undervoltage Trip Threshold             | REFIN2 with respect to nominal output voltage                                | -35%              | -30%   | -25%              |      |

| Undervoltage Fault Propagation<br>Delay |                                                                              | 0.8               | 1      | 1.2               | ms   |

| Undervoltage Fault Enable Delay         | From ENx signal                                                              | 10                | 20     | 30                | ms   |

| PGOOD2 Lower Trip Threshold             | REFIN2 with respect to nominal output, falling edge, typical hysteresis = 5% | -12.5%            | -10%   | -7.5%             |      |

| PGOOD2 Low Propagation Delay            | Falling edge, 50-mV overdrive                                                |                   | 10     |                   | μs   |

| PGOOD2 High Propagation Delay           | Rising edge, 50-mV overdrive                                                 | 0.8               | 1.0    | 1.2               | ms   |

| PGOOD2 Output Low Voltage               | PGOOD2 Low impedance, I <sub>SINK</sub> = 4 mA                               |                   | 0.4    | 0.8               | V    |

| PGOOD2 Leakage Current                  | PGOOD2 High impedance, forced to 5.5 V                                       |                   |        | 1                 | μA   |

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended free-air temperature range,  $V_{V5DRV}$  = 5 V,  $V_{VIN}$  = 12 V (unless otherwise noted).

| PARAMETER                                   | TEST CONDITIONS                                                      | MIN            | ТҮР   | MAX            | UNIT   |

|---------------------------------------------|----------------------------------------------------------------------|----------------|-------|----------------|--------|

| CURRENT LIMIT                               | ·                                                                    |                |       |                |        |

| TRIPx Adjustment Range                      |                                                                      | 0.2            |       | 2.0            | V      |

| TRIPx Source Current                        | 0.2 V < V <sub>TRIPx</sub> < 2 V, T <sub>A</sub> = +25°C             | 4.75<br>(–5%)  | 5     | 5.25<br>(+5%)  | μA     |

| TRIPx Current Temperature                   | Coefficient on the basis of $T_A = +25^{\circ}C^{(3)}$               |                | 2900  |                | ppm/°C |

|                                             | GND – LLx, V <sub>TRIPx</sub> = 0.2 V                                | 13<br>(–35%)   | 20    | 27<br>(+35%)   |        |

| Current-Limit Threshold (Positive,          | GND – LLx, V <sub>TRIPx</sub> = 0.5 V                                | 42.5<br>(–15%) | 50    | 57.5<br>(+15%) | mV     |

| Adjustable)                                 | GND – LLx, V <sub>TRIPx</sub> = 1 V                                  | 93<br>(–7%)    | 100   | 107<br>(+7%)   | ΠV     |

|                                             | GND – LLx, V <sub>TRIPx</sub> = 2 V                                  | 190<br>(–5%)   | 200   | 210<br>(+5%)   |        |

| Current-Limit Threshold (Positive, Default) | $V_{TRIPx}$ = 5.0 V, GND – LLx (no temperature compensation)         | 93<br>(–7%)    | 100   | 107<br>(+7%)   | mV     |

| Fixed 100-mV OCL TRIPx                      | High threshold                                                       | 3.0            | 3.2   | 3.3            | V      |

| Threshold Voltage                           | Hysteresis                                                           | 40             | 70    | 100            | mV     |

| Current Limit Threshold (Negative)          | With respect to valley current limit threshold,<br>SKIPSEL = 5 V     |                | -100% |                |        |

| Zero-Crossing Current Limit<br>Threshold    | SKIPSEL = 0 V, 2 V, or OPEN, GND – LLx                               | -3.5           | 0     | 3.5            | mV     |

| GATE DRIVERS                                |                                                                      |                |       |                |        |

| DRVHx Gate-Driver                           | Source, VBSTx-DRVHx = 0.1 V                                          |                | 1.0   | 3.6            | Ω      |

| On-Resistance                               | Sink, DRVHx-LLx = 0.1 V                                              |                | 0.8   | 2.6            | 12     |

| DRVLx Gate-Driver On-Resistance             | Source, V5DRV-DRVLx = 0.1 V                                          |                | 1.2   | 4.0            | Ω      |

| Drvex Gale-Driver On-Resistance             | Sink, DRVLx-PGND = 0.1 V                                             |                | 0.6   | 1.5            | 32     |

| DRVHx Gate-Driver Source<br>Current         | VBSTx-LLx = 5 V, DRVHx = 2.0 $V^{(3)}$                               |                | 1.8   |                | А      |

| DRVHx Gate-Driver Sink Current              | VBSTx-LLx = 5 V, DRVHx = 2.0 $V^{(3)}$                               |                | 1.6   |                | А      |

| DRVLx Gate-Driver Source<br>Current         | V5DRV-PGND = 5 V, DRVLx = 2.0 $V^{(3)}$                              |                | 1.4   |                | А      |

| DRVLx Gate-Driver Sink Current              | V5DRV-PGND = 5 V, DRVLx = $2.0 V^{(3)}$                              |                | 2.6   |                | А      |

| Dead Time                                   | DRVHx low (DRVHx = 1 V) to DRVLx high (DRVLx = 4 V), LLx = $-0.05$ V | 20             | 30    | 50             | ns     |

|                                             | DRVLx low (DRVLx = 1 V) to DRVHx high (DRVHx = 4 V), LLx = $-0.05$ V | 25             | 40    | 60             | ns     |

| Internal BST_ Switch<br>On-Resistance       | $I_{VBSTx}$ = 10 mA, V5DRV = 5 V, $T_A$ = +25°C                      |                | 10    |                | Ω      |

| VBSTx Leakage Current                       | V <sub>VBSTx</sub> = 35 V, LLx = 28 V                                |                | 0.01  | 2.0            | μA     |

(3) Ensured by design. Not production tested.

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended free-air temperature range,  $V_{V5DRV}$  = 5 V,  $V_{VIN}$  = 12 V (unless otherwise noted).

| PARAMETER                     | TEST CONDITIONS           | MIN  | TYP  | MAX  | UNIT |  |

|-------------------------------|---------------------------|------|------|------|------|--|

| INPUTS AND OUTPUTS            |                           |      |      | i    |      |  |

|                               | High level                | 2.9  |      |      |      |  |

| TONSEL Input Logic Levels     | Float level               | 1.85 |      | 2.25 | V    |  |

|                               | Low level                 |      |      | 0.45 |      |  |

|                               | High threshold (PWM Only) | 2.9  |      |      |      |  |

| SKIPSEL Input Logic Levels    | Float level (OOA)         | 1.85 |      | 2.25 | V    |  |

|                               | Low level (Auto Skip)     |      |      | 0.45 |      |  |

| SKIPSEL, TONSEL Input Current | SKIPSEL = TONSEL = 0 V    | 2.5  | 4.0  | 5.5  | μΑ   |  |

|                               | SMPS On level             | 2.9  |      |      |      |  |

| EN1, EN2 Input Logic Levels   | Delay start level         | 1.85 |      | 2.25 | V    |  |

|                               | SMPS Off level            |      |      | 0.45 |      |  |

| EN1, EN2 Leakage Current      | EN1 = EN2 = 0 V           | -0.1 |      | 0.1  | μΑ   |  |

|                               | Rising edge               | 1.3  | 1.65 | 1.9  | V    |  |

| EN_LDO Input Logic Levels     | Hysteresis                |      | 0.6  |      | V    |  |

|                               | EN_LDO = 0 V              | 0.7  | 1.0  | 1.3  | ^    |  |

| EN_LDO Input Current          | EN_LDO = 30 V             | -0.1 | 0    | 0.1  | μA   |  |

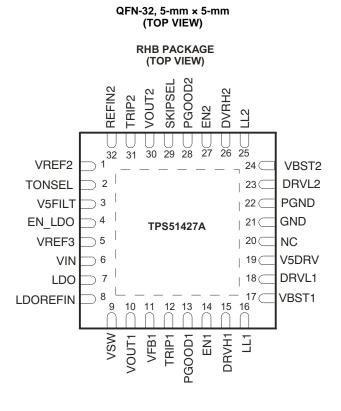

# **DEVICE INFORMATION**

#### **TERMINAL FUNCTIONS**

| TERMIN   | TERMINAL |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|----------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO.      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| DRVH1    | 15       | 0   | High-side N-Channel FET driver outputs. LL referenced floating drivers. The gate drive voltage is defined by the voltage across                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| DRVH2    | 26       |     | VBST to LL node bootstrap capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| DRVL1    | 18       | 0   | Synchronous low-side MOSFET driver outputs. Ground referenced drivers. The gate drive voltage is defined by V5DRV voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| DRVL2    | 23       | 0   | Synchronous low-side MOSFET anver outputs. Ground referenced anvers. The gate anve voltage is defined by voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| EN1      | 14       |     | Channel enable pins. If EN1 is connected to VREF2, Channel1 starts after Channel2 reaches regulation (delay start). If EN2 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| EN2      | 27       | '   | connected to VREF2, Channel2 starts after Chanel1 reaches regulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| EN_LDO   | 4        | I   | LDO Enable Input. The LDO is enabled if EN_LDO is within logic high level and disabled if EN_LDO is less than the logic low level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| GND      | 21       | I   | Analog ground for both channels and LDO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| LL1      | 16       | 1/0 | Phase node connections for high-side drivers. These connections also serve as inputs to current comparators for R <sub>DS(on)</sub> sensing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| LL2      | 25       | 1/0 | and input voltage monitor for on-time control circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| LDO      | 7        | 0   | Linear regulator output. The LDO regulator can provide a total of 100-mA external loads. The LDO regulates at 5 V If LDOREFIN is connected to GND. When the LDO is set at 5 V and VSW is within a 5-V switchover threshold, the internal regulator shuts down and the LDO output pin connects to VSW through a 0.7- $\Omega$ switch. The LDO regulates at 3.3 V if LDOREFIN is connected to V5FILT. When the LDO is set at 3.3 V and VSW is within a 3.3-V switchover threshold, the internal regulator shuts down and the LDO output pin connects to VSW through a 0.7- $\Omega$ switch. Bypass the LDO output with a minimum of 4.7- $\mu$ F ceramic capacitance. |  |  |  |  |

| LDOREFIN | 8        | I   | LDO Reference Input. Connect LDOREFIN to GND for fixed 5-V operation. Connect LDOREFIN to V5FILT for fixed 3.3-V operation. LDOREFIN can be used to program LDO output voltage from 0.7 V to 4.5 V. LDO output is twice the voltage of LDOREFIN. There is no switchover in adjustable mode.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| PGND     | 22       | I   | Ground pin for drivers and LS synchronous FET source terminals. This pin is also the input to zero crossing comparator and overcurrent comparator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| PGOOD1   | 13       | _   | Channel1/Channel2 power-good open-drain output. PGOOD1/PGOOD2 is low when the Channel1/Channel2 output voltage is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| PGOOD2   | 28       | 0   | 10% less than the normal regulation point, at onset of OVP events, or during soft start. PGOOD1/PGOOD2 is high impedance when the output is in regulation and the soft-start circuit has terminated. PGOOD1/PGOOD2 is low in shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

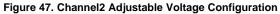

| REFIN2   | 32       | I   | Output voltage control for Channel2. Connect REFIN2 to V5FILT for fixed 3.3-V operation. Connect REFIN2 to VREF3 for fixed 1.05-V operation. REFIN2 can be used to program Channel2 output voltage from 0.5 V to 2.5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| NC       | 20       | -   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| SKIPSEL  | 29       | I   | Low-noise mode control. Connect SKIPSEL to GND for Auto Skip mode operation or to V5FILT for PWM mode (fixed frequency). Connect to VREF2 or leave floating for OOA <sup>™</sup> mode operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

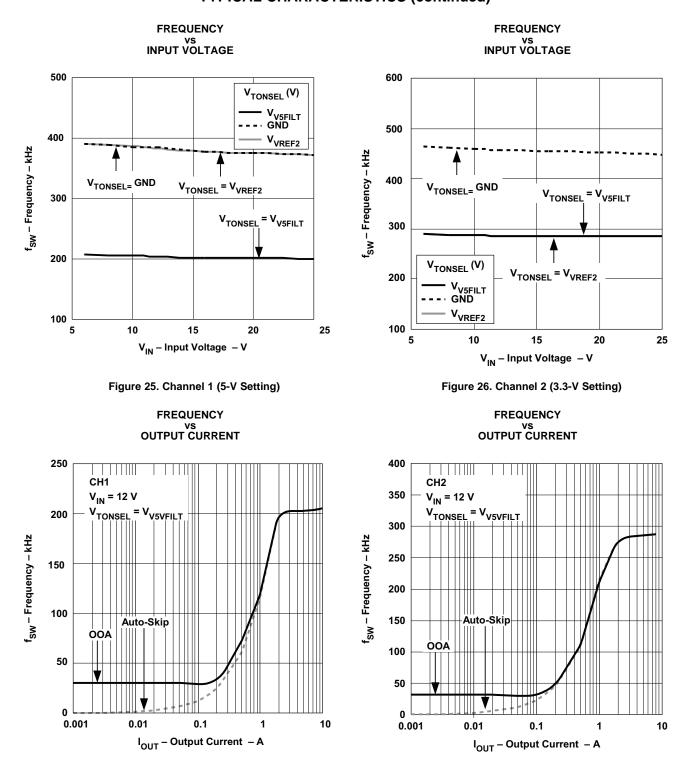

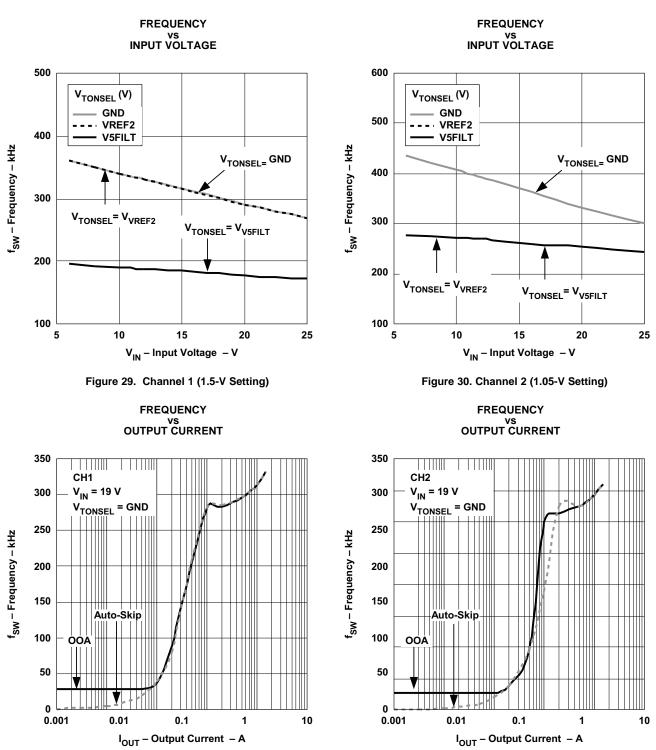

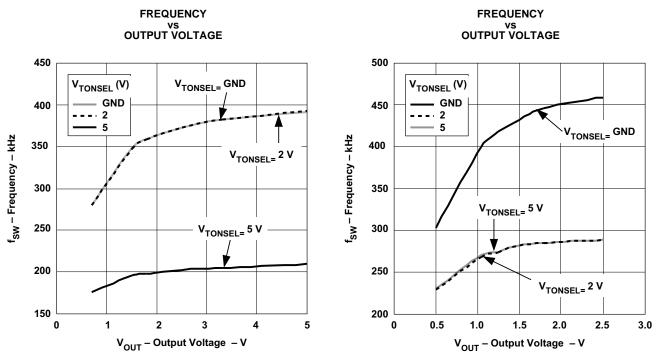

| TONSEL   | 2        | I   | Frequency select input. Connect to GND for 400-kHz/500-kHz operation. Connect to VREF2 (or leave open) for 400-kHz/300-kHz operation. Connect to V5FILT for 200-kHz/300-kHz operation (5-V/3.3-V SMPS switching frequencies, respectively).                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TRIP1    | 12       | 1   | Querourset trip point act input. Sourcing surrent is 5 u.A. at DT with 2000 ppm //C tomperature coefficient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| TRIP2    | 31       | '   | Overcurrent trip point set input. Sourcing current is 5 µA at RT with 2900 ppm/°C temperature coefficient.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| V5DRV    | 19       | I   | Supply voltage for the low-side MOSFET driver DRVL1/DRVL2. Connect a 5-V power source to the V5DRV pin (bypass with 4.7-µF MLCC capacitor to PGND if necessary).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| V5FILT   | 3        | - I | 5-V analog supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

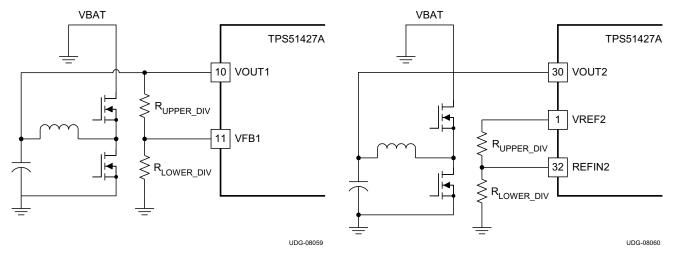

| VFB1     | 11       | I   | Channel1 feedback input. Connect VFB1 to GND for fixed 5-V operation. Connect VFB1 to V5FILT for fixed 1.5-V operation. Connect VFB1 to a resistive voltage divider from OUT1 to GND to adjust the output from 0.7 V to 5.9 V.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| VBST1    | 17       |     | Supply input for high-side MOSFET driver (bootstrap terminal). Connect a capacitor from this pin to the respective LL terminals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| VBST2    | 24       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| VIN      | 6        | I   | Power supply input. VIN supplies power to the linear regulators. The linear regulators are powered by Channel1 if VOUT1 is set greater than 5 V and VSW is tied to VOUT1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| VOUT1    | 10       | 0   | Output connections to SMPS. These terminals serve two functions: on-time adjustment and output discharge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| VOUT2    | 30       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| VREF2    | 1        | 0   | 2-V reference output. Bypass to GND with a 0.1- $\mu$ F capacitor. VREF2 can source up to 50 $\mu$ A for external loads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| VREF3    | 5        | 0   | 3.3-V reference output. VREF3 can source up to 10 mA for external loads. Bypass to GND with a 1- $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| VSW      | 9        | I   | VSW is the switchover source voltage for the LDO when LDOREFIN is connected to GND or V5FILT. Connect VSW to 5 V if LDOREFIN is tied GND. Connect VSW to 3.3 V if LDOREFIN is tied to V5FILT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

www.ti.com

NC = No connection.

#### SLUS843B-MAY 2008-REVISED SEPTEMBER 2008

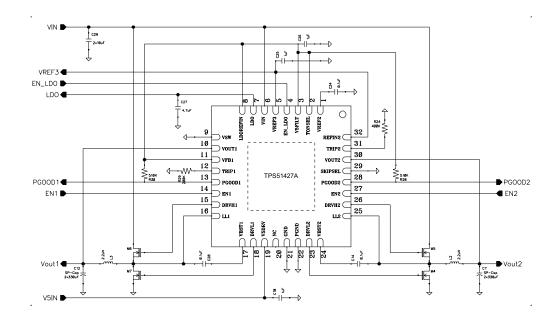

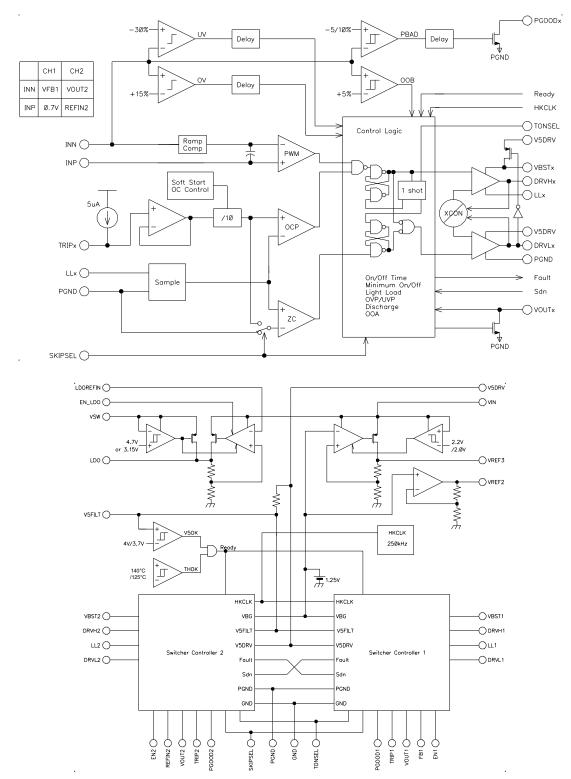

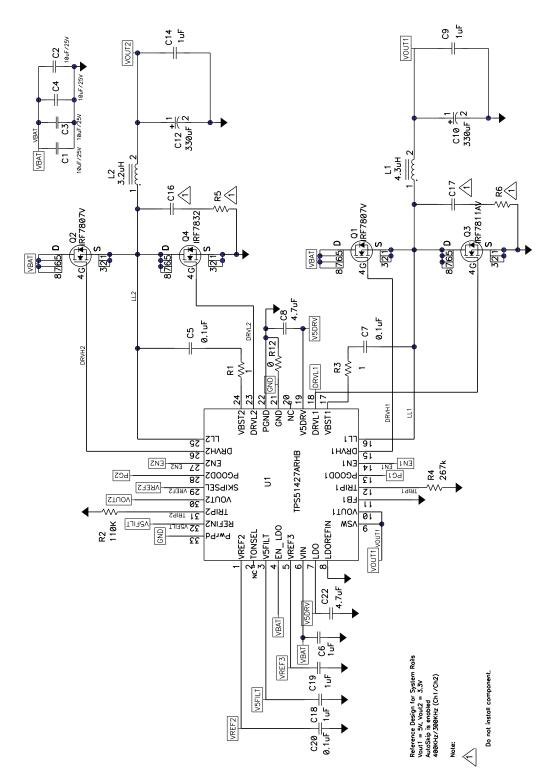

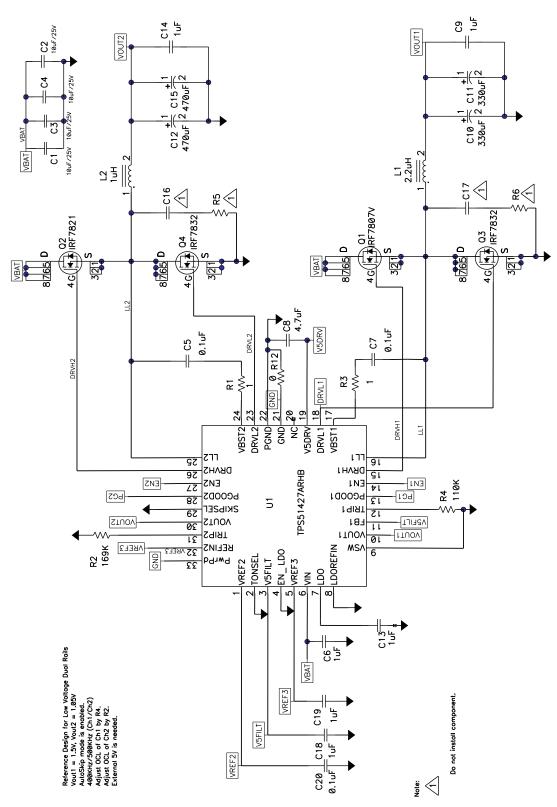

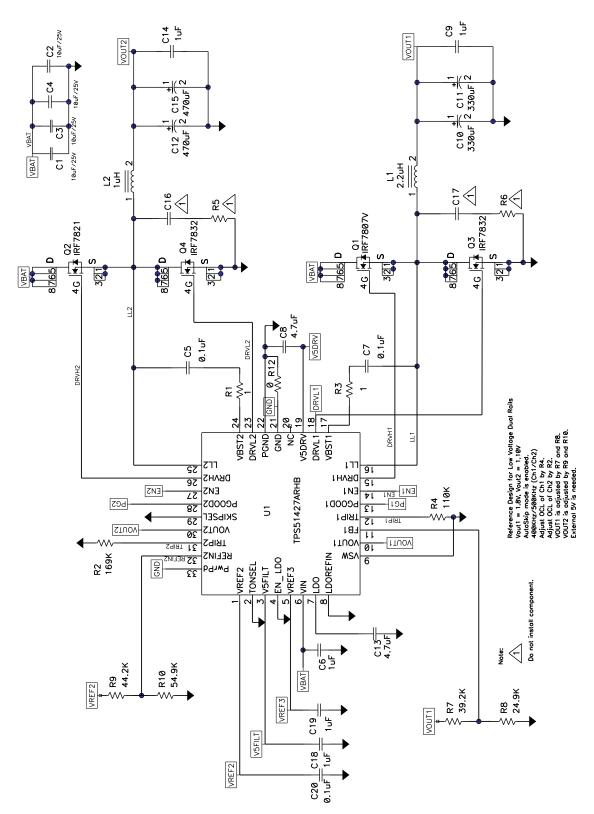

# FUNCTIONAL BLOCK DIAGRAMS

# DETAILED DESCRIPTION

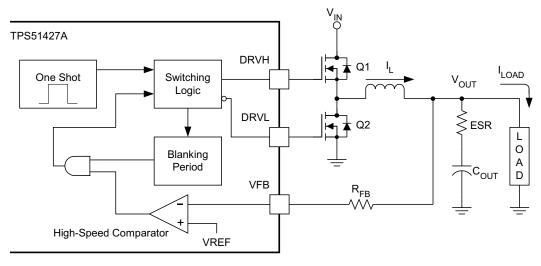

## **BASIC PWM OPERATION**

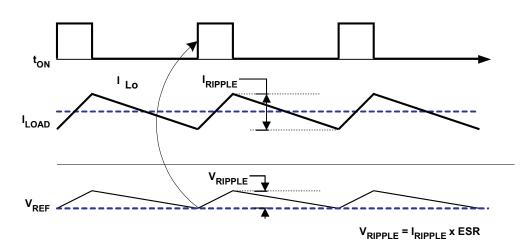

The main control loop of the TPS51427A is designed as an adaptive on-time pulse width modulation (PWM) controller. It supports a proprietary D-CAP<sup>™</sup> mode that uses internal compensation circuitry and is suitable for a minimal external component count configuration when an appropriate amount of ESR at the output capacitor(s) is allowed. D-CAP mode can also enable stable operation when using capacitors with low ESR, such as specialty polymer capacitors.

The basic operation of D-CAP mode can be described in this way: At the beginning of each cycle, the synchronous high-side MOSFET turns on or goes to an *ON* state. This MOSFET turns off, or returns to an *OFF* state, after an internal one-shot timer expires. The one-shot timer is determined by VIN and VOUT and keeps the frequency fairly constant over the input voltage range under steady-state conditions; it is an adaptive on-time control or *fixed-frequency emulated* on-time control. The MOSFET turns on again when the following two conditions occur:

- Feedback information, monitored at the VFB1/VOUT2 voltage, indicates insufficient output voltage; and

- the inductor current information indicates that current is below the overcurrent limit.

Operating in this manner, the controller regulates the output voltage. The synchronous low-side or the *rectifying* MOSFET is turned on each OFF state to keep the conduction loss minimum.

# LIGHT LOAD CONDITIONS

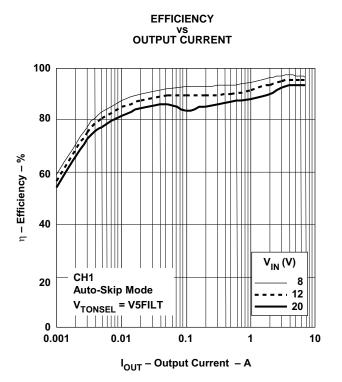

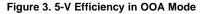

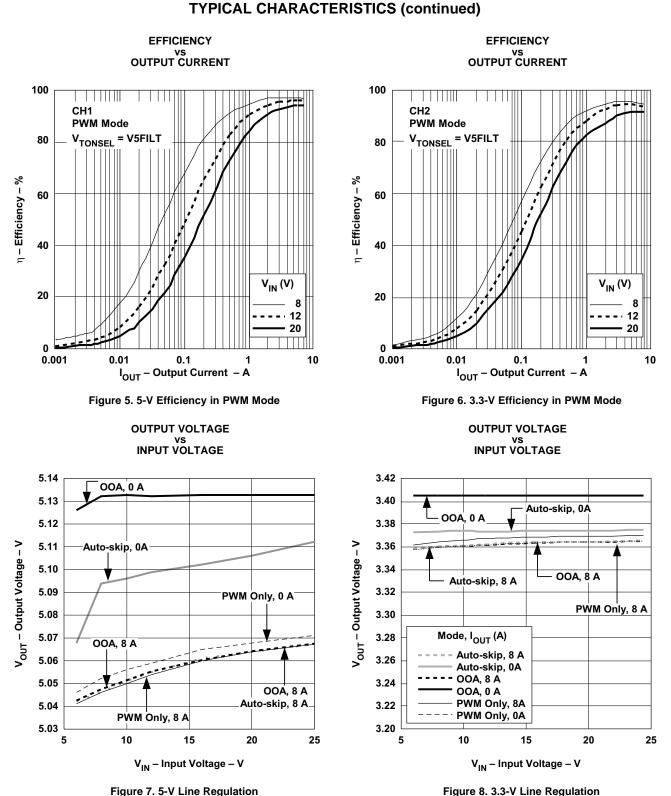

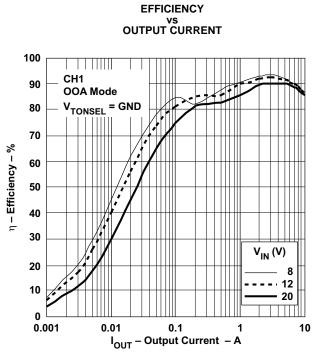

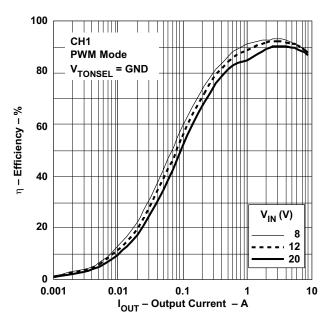

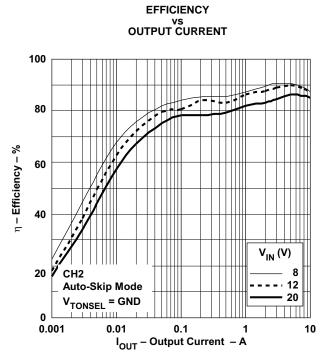

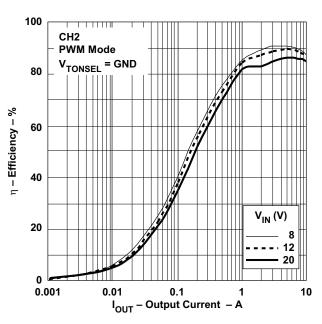

The TPS51427A supports three selectable operating modes: PWM-only, Out-Of-Audio (OOA™), and Auto-Skip.

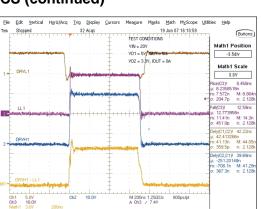

If the SKIPSEL pin is connected to GND, Auto-Skip mode is selected. This mode enables a seamless transition to the reduced frequency operation under light load conditions so that high efficiency is maintained over a wide range of load current. This frequency reduction is achieved smoothly and without an increase in V<sub>OUT</sub> ripple or load regulation.

Auto-Skip operation can be described in this way: As the output current decreases from a heavy load condition, the inductor current is also reduced. Eventually, the inductor current reaches the point that its *valley* equals zero current; that is, the boundary between continuous conduction and discontinuous conduction modes. The rectifying MOSFET turns off when this zero inductor current is detected. Because the output voltage remains higher than the reference voltage at this point, both high-side and low-side MOSFETs are turned off and wait for the next cycle. As the load current decreases further, the converter runs in discontinuous conduction mode and takes longer to discharge the output capacitor below the reference voltage. Note that the *ON* time remains the same as that in the heavy load condition. On the other hand, when the output current increases from a light load to a heavy load, the switching frequency increases to the preset value as the inductor current reaches the continuous conduction limit. The transition load point to the light load operation  $I_{OUT(LL)}$  (that is, the threshold between continuous conduction and discontinuous conduction mode) can be calculated as shown in Equation 1:

$$I_{OUT(LL)} = \left(\frac{1}{2 \times L \times f_{SW}}\right) \times \left(\frac{\left(V_{VIN} - V_{VOUT}\right) \times V_{VOUT}}{V_{VIN}}\right)$$

(1)

Where  $f_{SW}$  is the PWM switching frequency. Switching frequency versus output current under a light load condition is a function of L,  $f_{SW}$ ,  $V_{IN}$ , and  $V_{OUT}$ , but decreases at a near-proportional rate to the output current from the  $I_{OUT(LL)}$  threshold. For example, the frequency is approximately 60 kHz at  $I_{OUT(LL)}/5$  if the PWM switching frequency is 300 kHz.

PWM-only mode is selected if the SKIPSEL pin is connected to 5 V. The rectifying MOSFET does not turn off when the inductor current reaches zero. The converter runs in forced continuous conduction mode over the entire load range. System designers may want to use this mode to avoid certain frequencies under light load conditions but do so at the cost of lower efficiency. However, keep in mind that the output has the capability to both source and sink current in this mode. If the output terminal is connected to a voltage source that is higher than the regulator target value, the converter sinks current from the output and boosts the charge into the input capacitors. This operation may cause an unexpected high voltage at VIN and may damage the power FETs.

If SKIPSEL pin is connected to VREF2 or left floating, OOA mode operation is selected.

SLUS843B-MAY 2008-REVISED SEPTEMBER 2008

#### Table 1. SKIPSEL Operating Modes

| SKIPSEL        | GND       | FLOAT/VREF2 | V5IN     |

|----------------|-----------|-------------|----------|

| Operating Mode | Auto Skip | OOA™        | PWM Only |

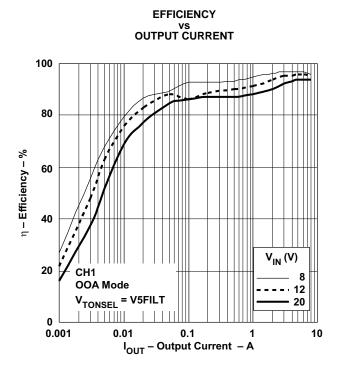

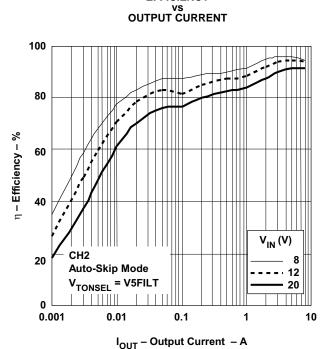

## OUT-OF-AUDIO (OOA™) OPERATION

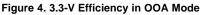

If out-of-audio (OOA) operation is enabled, the switching frequency of the channel remains higher than the audible frequency under any load condition, at a minimum of 22 kHz to minimize the audible noise in the system. The TPS51427A automatically reduces switching frequencies under light load conditions. The OOA control circuit monitors the switching period and forces the high-side MOSFET to turn on if the switching frequency goes below the 22-kHz threshold.

The high-side MOSFET turns on even if the output voltage is higher than the target value; therefore, the output voltage tends to be higher when operating in OOA mode. The OOA control circuit detects the overvoltage condition and prevents the voltage from rising by re-modulating the device on time. The overvoltage condition is detected by the VFB1/VOUT2 voltages.

The inductor current ripple (peak-to-peak) should be less than two-thirds of the OCL setting for the OOA circuit to work properly at a 0-A load. To keep the OOA mode loop stable, the output voltage ripple cannot be too large. If OOA mode operation is desired, the recommended output ripple voltage cannot be more than 1% of the target dc voltage.

### RAMP COMPENSATION

The TPS51427A employs an advanced ramp compensation technique in D-CAP mode to optimize jitter performance. An internal ramp signal is added to the reference voltage to virtually increase the slope of the VFB1/VOUT2 down ramp, which the PWM comparator uses to determine the turn-on timing.

## LOW-SIDE DRIVER

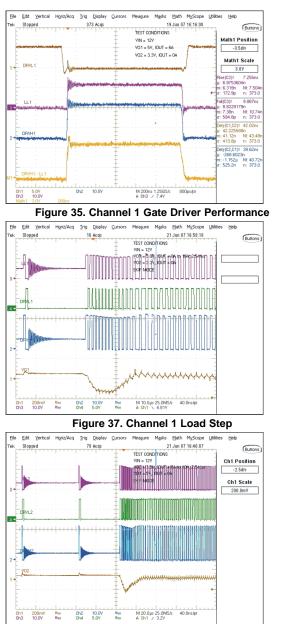

The low-side driver is designed to drive high-current, low  $R_{DS(on)}$ , N-channel MOSFET(s). The drive capability is represented by its internal resistance: 1.2  $\Omega$  for V5DRV to DRVLx and 0.6  $\Omega$  for DRVLx to PGND. A dead time to prevent shoot-through is generated internally between the two transistors, with the top MOSFET off and bottom MOSFET on, and then with the bottom MOSFET off and the top MOSFET on. A 5-V bias voltage is delivered from the V5DRV supply. The instantaneous drive current is supplied by an input capacitor connected between V5DRV and GND. The average drive current is equal to the gate charge at  $V_{GS}$  = 5 V times the switching frequency.

### HIGH-SIDE DRIVER

The high-side driver is also designed to drive high-current, low  $R_{DS(on)}$ , N-channel MOSFET(s). When configured as a floating driver, a 5-V bias voltage is delivered from the V5DRV supply. The average drive current is also calculated by the gate charge at  $V_{GS} = 5$  V times the switching frequency. The instantaneous drive current is supplied by the floating capacitor between the VBSTx and LLx pins. The drive capability is represented by its internal resistance: 1.0  $\Omega$  for VBSTx to DRVHx and 0.8  $\Omega$  for DRVHx to LLx.

### **BOOSTRAP CHARGE AUTO REFRESH**

Boost undervoltage protection is activated during the device *ON* time when the voltage difference between DRVH and LL becomes less than 1.8 V. Upon detection of the undervoltage condition, the high-side gate driver immediately turns off and the low-side gate driver turns on after the deadtime expires for the minimum off time in an attempt to recharge the boost capacitor.

### PWM FREQUENCY AND ADAPTIVE ON-TIME CONTROL

The TPS51427A employs an adaptive on-time control scheme and does not have a dedicated onboard oscillator. However, the device runs with pseudo-constant frequency by feed-forwarding the input voltage and output voltage into the on-time one-shot timer. The frequencies are set by the TONSEL terminal connection as Table 2 shows. The on-time is controlled: it is inversely proportional to the input voltage and proportional to the output voltage, so that the duty ratio maintains technically as VOUT/VIN with the same cycle time. Although the TPS51427A does not use VIN directly, the input voltage is monitored at the LLx pin during the *ON* state.

Copyright © 2008, Texas Instruments Incorporated

|                    | 1       | -              |         |

|--------------------|---------|----------------|---------|

| TONSEL             | GND     | VREF2 or Float | V5FILT  |

| Channel1 Frequency | 400 kHz | 400 kHz        | 200 kHz |

| Channel2 Frequency | 500 kHz | 300 kHz        | 300 kHz |

#### Table 2. TONSEL Terminal Connection Options

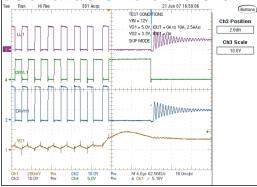

## ENABLE AND SOFT START

TPS51427A has an internal digital soft-start timer that begins to ramp up to the maximum allowed current limit during device startup. The soft-start ramp occurs in five steps of positive current limit; step sizes are 20%, 40%, 60%, 80%, and 100%. Smooth control of the output voltage during device startup is maintained. In addition, if tracking discharge is required, the ENx pin can be used to control the output voltage discharge smoothly. At the beginning of the soft-start period, the rectifying MOSFET maintains an off state until the top MOSFET turns on at least once. This architecture prevents a high negative current from flowing back from the output capacitor in the event of an output capacitor pre-charged condition.

If EN1 is connected to VREF2, Channel1 starts up after the Channel2 reaches regulation (delay start). If EN2 is connected to VREF2, Channel2 starts up after the Channel1 reaches regulation (delay start).

When both ENx are low and ENLDO is low, the TPS51427A enters a shutdown state and consumes less than  $15 \,\mu$ A.

## POWER-GOOD

The TPS51427A has a power-good output (PGOODx) for each switching channel. The power-good function activates after the soft start finishes. If the output voltage reaches within  $\pm$ 95% of the target value, internal comparators detect a power-good state and the power-good signal goes high after a 1-ms internal delay. If the output voltage falls below 90% of the target value, the power-good signal goes low after a 10- $\mu$ s internal delay.

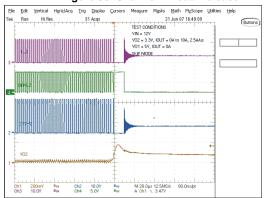

### **OUTPUT SHUTDOWN AND DISCHARGE CONTROL**

The TPS51427A discharges the output when ENx is low, or when the controller is shut down by the circuit protection functions (OVP, UVP, UVLO, and thermal shutdown). The TPS51427A discharges the outputs using an internal,  $17-\Omega$  MOSFET that is connected to VOUTx and PGND. The external low-side MOSFET does not turn on during the output discharge operation to avoid the possibility of causing a negative voltage at the output. The output discharge time constant is a function of the output capacitance and the resistance of the internal discharge MOSFET. This discharge ensures that on device restart, the regulated voltage always starts from 0 V. If an SMPS restarts before the discharge completes, the discharge action is terminated and switching resumes after the reference level (ramped up by an internal digital-to-analog converter, or DAC) returns to the remaining output voltage. When shutdown mode activates, the 3.3-V VREF3 remains on.

### 2-V REFERENCE (VREF2)

The 2-V reference is useful for generating auxiliary voltages. The tolerance for this reference voltage is  $\pm 1.25\%$  over a 50- $\mu$ A load and  $-40^{\circ}$ C to  $+85^{\circ}$ C ambient temperature range. This reference is enabled when ENLDO goes high, and shuts down after both switching channels are turned off and ENLDO is shut down. If this output is forcibly tied to ground, both SMPSs are turned off without a latch. Bypass the VREF2 pin to GND with a minimum 0.1- $\mu$ F ceramic capacitor.

# 3-V REFERENCE (VREF3)

The 3.3-V reference (VREF3) is accurate to  $\pm 1.5\%$  over temperature, making VREF3 useful as a precision system reference for the real-time clock (RTC) circuit in many notebook applications. VREF3 can supply up to 10 mA for external loads. Bypass VREF3 to GND with a 1- $\mu$ F capacitor. VREF3 is activated when VIN rises above 2.1 V, and remains on even when the SMPS and LDO are both shut down. VREF3 is deactivated if VIN falls below 1.8 V. In thermal shutdown conditions, VREF3 remains activate.

TPS51427A

SLUS843B-MAY 2008-REVISED SEPTEMBER 2008

## LDO

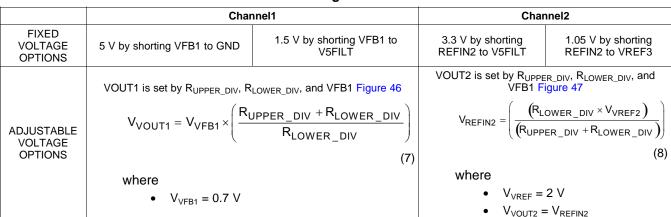

www.ti.com