# 3.8V-36V Vin, 5A, High Efficiency Synchronous Step-down DCDC Converter with Programmable Frequency

#### **FEATURES**

- Wide Input Range: 3.8V-36V

- Up to 5A Continuous Output Current

- Integrated 45mΩ High-Side and 20mΩ Low-Side Power MOSFETs

- Feedback Reference Voltage: 0.8V ±1%

- Adjustable Frequency 100KHz to 1.1MHz

- Precision Enable Threshold for Programmable Input Voltage Under-voltage Lock Out Protection (UVLO) Threshold and Hysteresis

- Minimum On-time: 100ns

- Internal Soft-start Time: 4ms

- Over-voltage and Over-Temperature Protection

- Pulse Skipping Mode (PSM) with 25uA Quiescent Current in Sleep Mode

- External Clock Synchronization

- Low Dropout Mode Operation

- Derivable Inverting Voltage Regulator

- Frequency Spread Spectrum (FSS) Modulation for EMI Reduction

- Available in an ESOP-8 Package

### **APPLICATIONS**

- Battery Pack Powered System Cordless Power Tools, Cordless Home Appliance, Drone, Aero Modeling, GPS Tracker etc.

- Cigarette Lighter Adapters, Chargers

- LCD Display

- USB Type-C Power Delivery, USB Charging

- Industrial and Medical Distributed Power Supplies

- Optical Communication and Networking System

- Automotive System

### **DESCRIPTION**

The TPS54540D is 5A synchronous buck converters with wide input voltage, ranging from 3.8V to 36V, which integrates a  $45m\Omega$  high-side MOSFET and a  $20m\Omega$ low-side MOSFET. The TPS54540D , adopting the peak current mode control, supports the Pulse Skipping Modulation (PSM) with typical 25uA low quiescent current which assists the converter on achieving high efficiency at light load or standby condition.

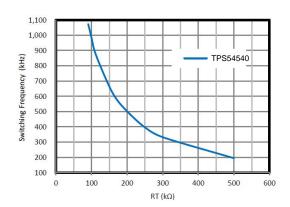

The TPS54540D features programmable switching frequency from 100 kHz to 1.1 MHz with an external resistor, which provides the flexibility to optimize either efficiency or external component size. The converter supports external clock synchronization with a frequency band from 100kHz to 1.1MHz. The TPS54540D allows power conversion from high input voltage to low output voltage with a minimum 100ns on-time of highside MOSFET, and support Low Dropout Mode Operation(LDO).

The TPS54540D is an Electromagnetic Interference (EMI) friendly buck converter with internal integration Frequency Spread Spectrum(FSS) for EMI reduction.

The TPS54540D offers cycle-by-cycle current limit and hiccup over current protection, thermal shutdown protection, output over-voltage protection and input voltage under-voltage protection. The device is available in an 8-pin thermally enhanced ESOP-8 package.

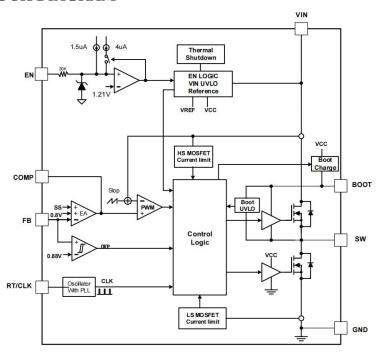

# FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

# **ELECTRICAL CHARACTERISTICS**

$V_{IN}$ =24V,  $T_J$ =-40 ~ +125°C, typical value is tested under 25°C

| SYMBOL                 | PARAMETER                                             | TEST CONDITION                                              | MIN   | TYP  | MAX   | UNIT   |

|------------------------|-------------------------------------------------------|-------------------------------------------------------------|-------|------|-------|--------|

| V <sub>IN</sub>        | Operating input voltage                               |                                                             | 3.8   |      | 36    | V      |

| 17                     | Input UVLO Threshold                                  | V <sub>IN</sub> rising                                      |       | 3.5  | 3.7   | V      |

| V <sub>IN_UVLO</sub>   | Hysteresis                                            |                                                             |       | 400  |       | mV     |

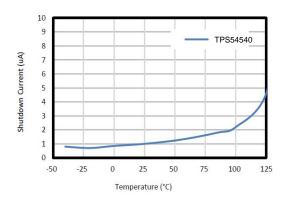

| $I_{SD}$               | Shutdown current from V <sub>IN</sub> pin             | EN=0V, no load                                              |       | 1    | 3     | μΑ     |

| $I_Q$                  | Quiescent current from V <sub>IN</sub> pin            | ENfloating, no load, $V_{BST}$ - $V_{SW}$ =5 $V$            |       | 25   |       | μΑ     |

| R <sub>DSON_H</sub>    | High-side MOSFET on-resistance                        | $V_{BST}$ - $V_{SW}$ = $5V$                                 |       | 45   |       | mΩ     |

| R <sub>DSON_L</sub>    | Low-side MOSFET on-resistance                         |                                                             |       | 20   |       | mΩ     |

| $V_{REF}$              | Reference voltage of FB                               |                                                             | 0.792 | 0.80 | 0.808 | V      |

| GEA                    | Error amplifier trans-conductance                     | $2\mu A {<} I_{COMP} {<} 2\mu A, V_{COMP} {=} 1V$           |       | 300  |       | uS     |

| I <sub>COMP_SRC</sub>  | EA maximum source current                             | $V_{FB}\!\!=\!\!V_{REF}\!\!-\!\!100mV, V_{COMP}\!\!=\!\!1V$ |       | 30   |       | μA     |

| I <sub>COMP_SNK</sub>  | EA maximum sink current                               | $V_{FB}\!\!=\!\!V_{REF}\!\!+\!\!100mV,V_{COMP}\!\!=\!\!1V$  |       | 30   |       | μA     |

| V <sub>COMP_H</sub>    | COMP high clamp                                       |                                                             |       | 3    |       | V      |

| V <sub>COMP_L</sub>    | COMP low clamp                                        |                                                             |       | 0.4  |       | V      |

| I <sub>LIM_HS</sub>    | High-side power MOSFET peak current limit threshold   |                                                             | 6.8   | 8    | 9.2   | A      |

| I <sub>LIM_LSSRC</sub> | Low-side power MOSFET souring current limit threshold |                                                             |       | 9    |       | A      |

| t <sub>HIC_W</sub>     | Over current protection hiccup wait time              |                                                             |       | 512  |       | cycles |

| $t_{\mathrm{HIC\_R}}$ | Over current protection hiccup restart time    |                                           |      | 8192 |      | cycles |

|-----------------------|------------------------------------------------|-------------------------------------------|------|------|------|--------|

| $V_{\rm EN\_H}$       | Enable high threshold                          |                                           |      | 1.18 | 1.25 | V      |

| V <sub>EN_L</sub>     | Enable low threshold                           |                                           | 1.03 | 1.1  |      | V      |

| I <sub>EN_L</sub>     | Enable pin pull-up current                     | EN=1V                                     | 1    | 1.5  | 2    | μΑ     |

| I <sub>EN_H</sub>     | Enable pin pull-up current                     | EN=1.5V                                   |      | 5.5  |      | μΑ     |

| t <sub>ss</sub>       | Internal soft start time                       |                                           |      | 4    |      | ms     |

| F <sub>RANGE_RT</sub> | Frequency range using RT mode                  |                                           | 100  |      | 1100 | KHz    |

| $F_{SW}$              | Switching frequency                            | $R_{RT}=200 \text{ k}\Omega(1\%)$         | 400  | 450  | 500  | KHz    |

| Frange_clk            | Frequency range using CLK mode                 |                                           | 100  |      | 1100 | KHz    |

| $F_{JITTER}$          | Frequency spread spectrum in percentage of Fsw |                                           |      | ±6   |      | %      |

| t <sub>ON_MIN</sub>   | Minimum on-time                                | V <sub>IN</sub> =24V                      |      | 100  |      | ns     |

| 17                    | Feedback overvoltage with respect              | V <sub>FB</sub> /V <sub>REF</sub> rising  |      | 110  |      | %      |

| $ m V_{OVP}$          | to reference voltage                           | VfB/Vref falling                          |      | 105  |      | %      |

| V <sub>BOOTUV</sub>   | BOOT-SW UVLO threshold                         | V <sub>BST</sub> -V <sub>SW</sub> rising  |      | 2.36 |      | V      |

|                       | Hysteresis                                     | V <sub>BST</sub> -V <sub>SW</sub> falling |      | 300  |      | mV     |

| т                     | Thermal shutdown threshold                     | T <sub>J</sub> rising                     |      | 170  |      | °C     |

| $T_{SD}$              | Hysteresis                                     |                                           |      | 25   |      | °C     |

# **ABSOLUTE MAXIMUM RATINGS**

| DESCRIPTION                                   | VALUE              | UNIT |

|-----------------------------------------------|--------------------|------|

| $V_{\mathrm{IN}}$ , $V_{\mathrm{EN}}$         | 38                 | V    |

| $ m V_{BOOT}$                                 | 44                 | V    |

| $ m V_{SW}$                                   | 38                 | V    |

| $ m V_{FB},  m V_{COMP},  m V_{RT/CLK}$       | 6                  | V    |

| $ m V_{BOOT}	ext{-}V_{SW}$                    | 6                  | V    |

| Operating junction temperature T <sub>J</sub> | -40 ~ +150         | °C   |

| Storage temperature T <sub>S</sub>            | <b>-</b> 65 ∼ +150 | °C   |

# RECOMMENDED OPERATING CONDITIONS

| DESCRIPTION                                   | VALUE      | UNIT |

|-----------------------------------------------|------------|------|

| Input voltage range $V_{\rm IN}$              | 3.8~36     | V    |

| Output voltage range VOUT                     | 0.8~35     | V    |

| Operating junction temperature T <sub>J</sub> | -40 ~ +125 | °C   |

# ESD RATINGS

| DESCRIPTION                                       | VALUE     | UNIT |  |

|---------------------------------------------------|-----------|------|--|

| Human Body Model(HBM), ANSI-JEDEC-JS-001-2014     | -2~+2     | KV   |  |

| Charged Device Model(CDM), ANSI-JEDEC-JS-002-2014 | -0.5~+0.5 | KV   |  |

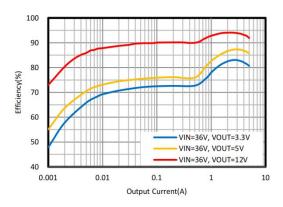

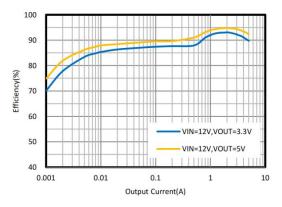

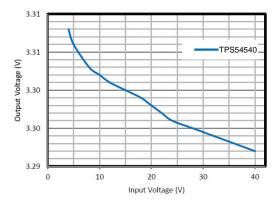

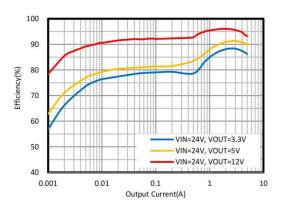

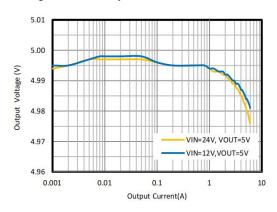

### TYPICAL CHARACTERISTICS

Figure 2. Efficiency vs Load Current, Vin=36V

Figure 4. Efficiency vs Load Current, Vin=12V

Figure 6. Line Regulation  $V_{OUT}$ =3.3V,  $I_{LOAD}$ =5A

Figure 3. Efficiency vs Load Current, Vin=24V

Figure 5. Load Regulation (Vout=5V)

Figure 7.Clock Frequency vs RT/CLK Resistor

Figure 8. Shutdown Current vs Temperature

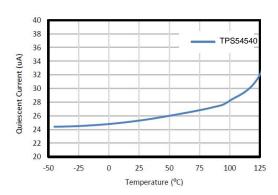

Figure 9. Quiescent Current vs Temperature

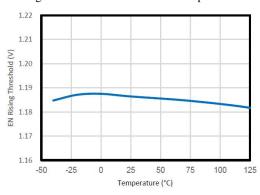

Figure 10. EN Threshold vs Temperature

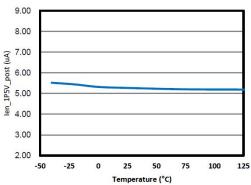

Figure 11. EN Pull-up Current vs Temperature

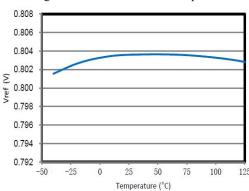

Figure 12. Reference Voltage vs Temperature

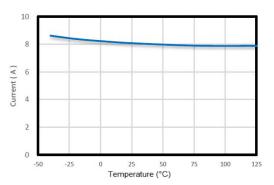

Figure 13. Peak Current Limit vs Temperature

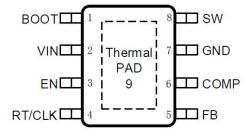

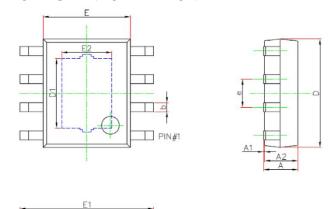

### PIN CONFIGURATION

Figure 14. 8-Lead Plastic E-SOP

| NO.    | NAME         | PIN FUNCTION                                                                                            |  |

|--------|--------------|---------------------------------------------------------------------------------------------------------|--|

|        |              | Power supply bias for high-side power MOSFET gate driver. Connect a 0.1uF capacitor from BOOT           |  |

| 1 BOOT |              | pin to SW pin. Bootstrap capacitor is charged when low-side power MOSFET is on or SW voltage is         |  |

|        |              | low.                                                                                                    |  |

| 2      | VIN          | Input supply voltage. Connect a local bypass capacitor from VIN pin to GND pin. Path from VIN           |  |

|        | VIIV         | pin to high frequency bypass capacitor and GND must be as short as possible.                            |  |

|        |              | Enable pin to the regulator with internal pull-up current source. Pull below 1.1V to                    |  |

| 3      | EN           | disable the converter. Float or connect to VIN to enable the converter. The tap of resistor divider     |  |

|        |              | from VIN to GND connecting EN pin can adjust the input voltage lockout threshold.                       |  |

|        |              | Set the 20internal oscillator clock frequency or synchronize to an external clock.                      |  |

|        | RT/CLK       | Connect a resistor from this pin to ground to set switching frequency. An external clock can be input   |  |

| 4      |              | directly to the RT/CLK pin. The internal oscillator synchronizes to the external clock frequency with   |  |

|        |              | PLL. If detected clocking edges stops, the operation mode automatically returns to resistor             |  |

|        |              | programmed frequency.                                                                                   |  |

|        |              | Inverting input of the trans-conductance error amplifier. The tap of external feedback resistor divider |  |

| 5      | FB           | from the output to GND sets the output voltage. The device regulates                                    |  |

|        |              | FB voltage to the internal reference value of 0.8V typical.                                             |  |

| 6      | COMP         | Error amplifier output. Connect to frequency loop compensation network.                                 |  |

| 7      | GND          | Ground.                                                                                                 |  |

| 8      | SW           | Regulator switching output. Connect SW to an external power inductor.                                   |  |

| 9      | Thermal Pad  | Heat dissipation path of die. Electrically connection to GND pin. Must be connected to ground plane     |  |

| 7      | Thermai i au | on PCB for proper operation and optimized thermal performance.                                          |  |

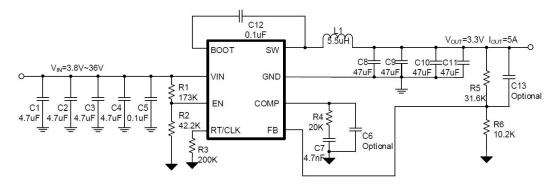

# **TYPICAL APPLICATION**

Figure 15. TPS54540D Design Example: 3.3V/3.5A Output, Switching frequency 500KHz

Output Voltage:

$$V_{OUT} = 0.8 \bullet \frac{R_5 + R_6}{R_6}$$

**Switching Frequency:**

$$f_{SW}(kHz) = \frac{100000}{R_3(k \Omega)}$$

### **Under Voltage Lock-Out:**

$$\begin{split} V_{rise} &= 1.18 \times \left(1 + \frac{R_1}{R_2}\right) - 1.5uA \times R_1 \\ V_{fall} &= 1.10 \times \left(1 + \frac{R_1}{R_2}\right) - 5.5uA \times R_1 \end{split}$$

Compensation Values for Typical Output Voltage/Capacitor Combinations at fsw=500KHz:

| Vout | L1    | COUT   | R4    | C7     | C6              |

|------|-------|--------|-------|--------|-----------------|

| 1.8V | 3.3uH | 4*47uF | 12.1K | 6.8nF  | 100pF(optional) |

| 2.5V | 4.7uH | 4*47uF | 16.9K | 4.7nF  | 68pF (optional) |

| 3.3V | 5.5uH | 4*47uF | 20K   | 4.7 nF | 47pF (optional) |

| 5V   | 7.8uH | 4*47uF | 34K   | 3.3nF  | 22pF (optional) |

| 12V  | 10uH  | 4*47uF | 54.9K | 1nF    | 220pF           |

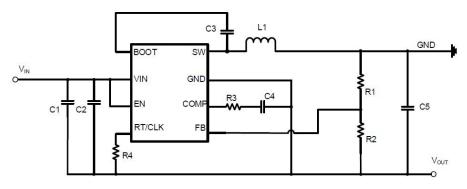

# **Inverting Power application**

The TPS54540D can be used to convert a positive input voltage to a negative output voltage. Typical applications are amplifiers requiring a negative power supply.

Figure 16.TPS54540D Inverting Power Supply

## **PACKAGE INFORMATION**

| Symbol   | Dimensions | Dimensions in Millimeters |  |  |

|----------|------------|---------------------------|--|--|

| Syllibol | Min.       | Max.                      |  |  |

| Α        | 1.300      | 1.700                     |  |  |

| A1       | 0.000      | 0.100                     |  |  |

| A2       | 1.350      | 1.550                     |  |  |

| b        | 0.330      | 0.510                     |  |  |

| С        | 0.170      | 0.250                     |  |  |

| D        | 4.700      | 5.100                     |  |  |

| D1       | 3.050      | 3.250                     |  |  |

| E        | 3.800      | 4.000                     |  |  |

| E1       | 5.800      | 6.200                     |  |  |

| E2       | 2.160      | 2.360                     |  |  |

| е        | 1.270(BSC) |                           |  |  |

|          |            |                           |  |  |

| L        | 0.400      | 1.270                     |  |  |

| θ        | 0°         | 8°                        |  |  |

Figure 17. Package Outline Dimensions Of TPS54540D