SLVSCA6C - OCTOBER 2013-REVISED OCTOBER 2017

TPS65311-Q1

# TPS65311-Q1 High-Voltage Power-Management IC for Automotive Applications

## **Features**

- **Qualified for Automotive Applications**

- AEC-Q100 Test Guidance With the Following Results:

- Device Temperature Grade 1: -40°C to +125°C Ambient Operating Temperature

- Device HBM ESD Classification Level H1B

- Device CDM ESD Classification Level C4B

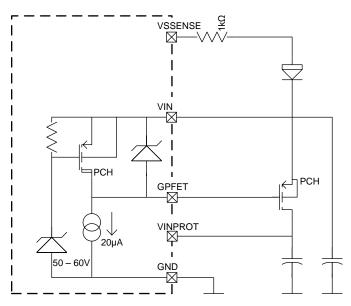

- Input Voltage Range: 4 V to 40 V, Transients up to 60 V; 80 V When Using External PMOS-FET

- Single-Output Synchronous-Buck Controller

- Peak Gate-Drive Current 0.6 A

- 490-kHz Fixed Switching Frequency

- Pseudo Random Frequency-Hopping Spread Spectrum or Triangular Mode

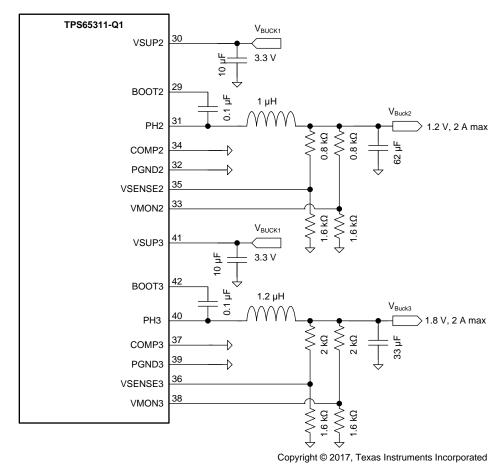

- **Dual-Synchronous Buck Converter**

- Designed for Output Currents up to 2 A

- Out of Phase Switching

- Switching Frequency: 2.45 MHz

- Adjustable 350-mA Linear Regulator

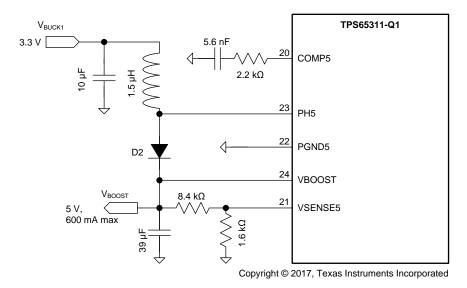

- Adjustable Asynchronous-Boost Converter

- 1-A Integrated Switch

- Switching Frequency: 2.45 MHz

- Soft-Start Feature for All Regulator Outputs

- Independent Voltage Monitoring

- Undervoltage (UV) Detection and Overvoltage (OV) Protection

- Short Circuit, Overcurrent, and Thermal Protection on all supply output rails

- Serial-Peripheral Interface (SPI) for Control and Diagnostic

- Integrated Window Watchdog (WD)

- Reference Voltage Output

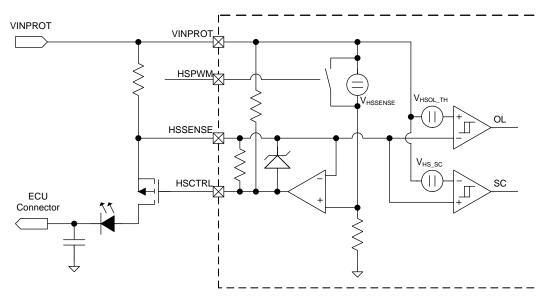

- High-Side (HS) Driver for Use with External PMOS-FET for driving an LED

- Input for External Temperature Sensor for Shutdown at  $T_A < -40$ °C

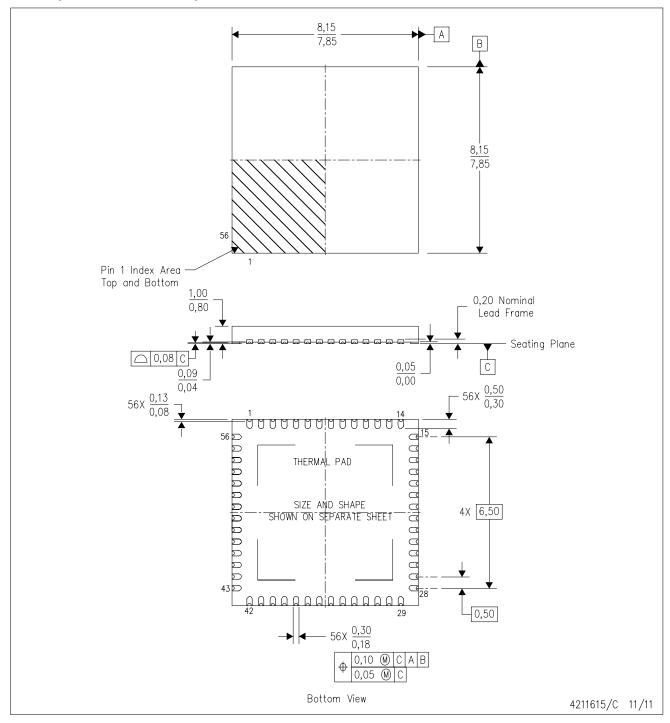

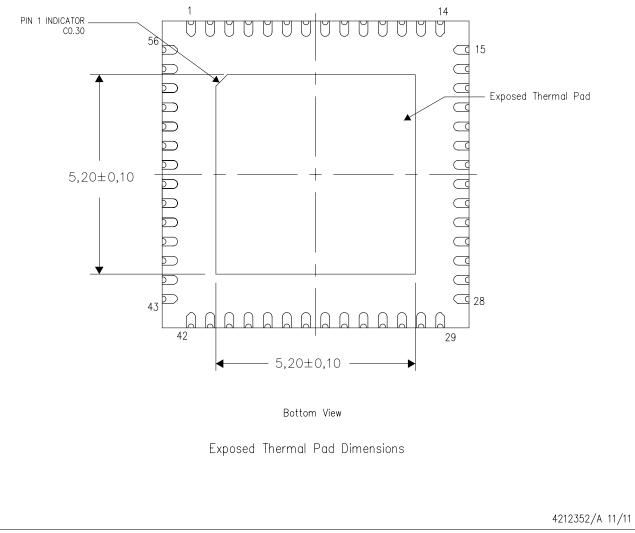

- Thermally Enhanced Packages With Exposed Thermal Pad

- 56-Pin VQFN (RVJ) or 56-Pin VQFNP (RWE)

## 2 Applications

- Multi-Rail DC Power Distribution Systems

- Safety-Relevant Automotive Applications

- Advanced Driver Assistance Systems

## 3 Description

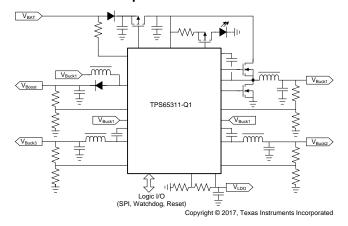

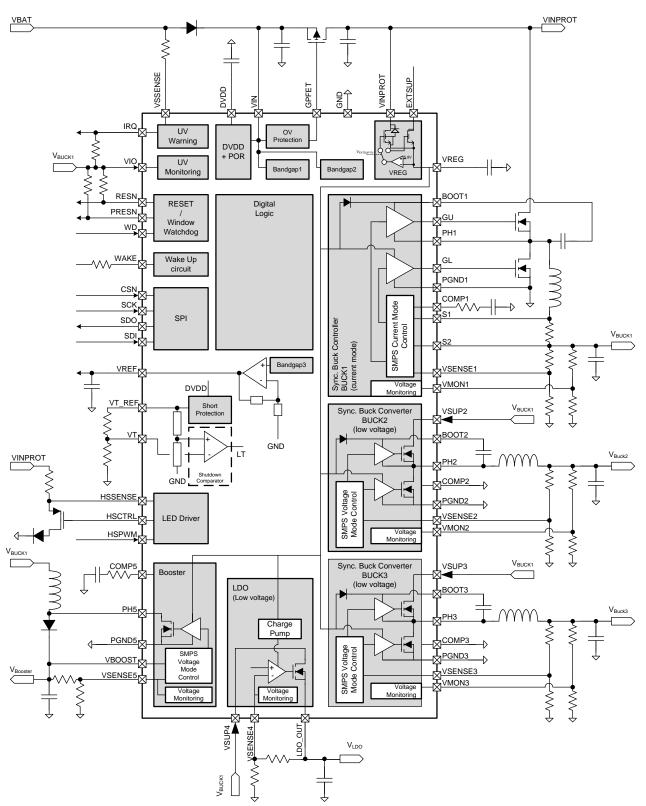

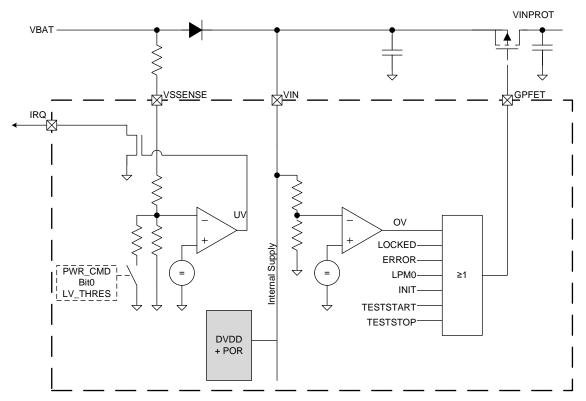

The TPS65311-Q1 device is a power-management IC (PMIC), meeting the requirements of digital-signalprocessor (DSP) controlled-automotive systems (for example, advanced driver-assistance systems). With the integration of commonly used supply rails and features, the TPS65311-Q1 device significantly reduces board space and system costs.

The device is capable of providing stable output voltages to the application, including a typical 5-V CAN-supply, from a varying input power supply (such as an automotive car battery) from 4 V to 40 V. The device includes one synchronous buck controller as a pre-regulator that offers flexible output power to the application. For post-regulation, the device includes two synchronous buck and one asynchronous boost converter, working at a switching frequency of 2.45 MHz to allow for a smaller inductor which requires less board space. The two buck converters also offer internal loop compensation which eliminates the need for external compensation components. Furthermore, the device includes a low-noise linear regulator.

#### Device Information<sup>(1)</sup>

| DEVICE NAME | PACKAGE    | BODY SIZE         |

|-------------|------------|-------------------|

| TD065344 O4 | VQFN (56)  | 8.00 mm × 8.00 mm |

| TPS65311-Q1 | VQFNP (56) | 8.00 mm × 8.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

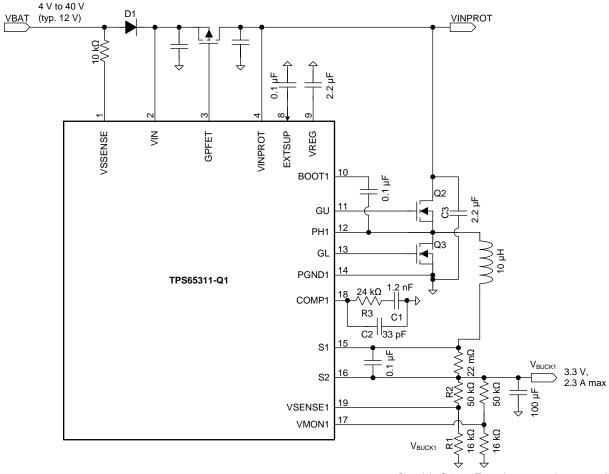

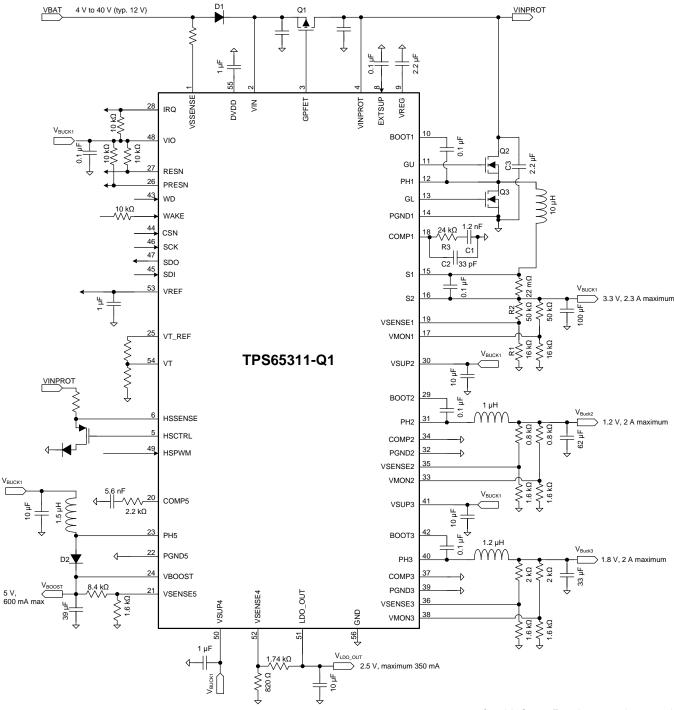

### Simplified Schematic

### **Table of Contents**

| 1 | Features 1                                                                |    | 8.4 Device Functional Modes                          | . 30               |

|---|---------------------------------------------------------------------------|----|------------------------------------------------------|--------------------|

| 2 | Applications 1                                                            |    | 8.5 Programming                                      | . 34               |

| 3 | Description 1                                                             |    | 8.6 Register Map                                     | . 35               |

| 4 | Revision History2                                                         | 9  | Application and Implementation                       | 41                 |

| 5 | Description (continued)4                                                  |    | 9.1 Application Information                          | . 41               |

| 6 | Pin Configuration and Functions 4                                         |    | 9.2 Typical Applications                             | . 41               |

| 7 | _                                                                         | 10 | Power Supply Recommendations                         | 51                 |

| ′ | Specifications         7           7.1 Absolute Maximum Ratings         7 | 11 | Layout                                               | 53                 |

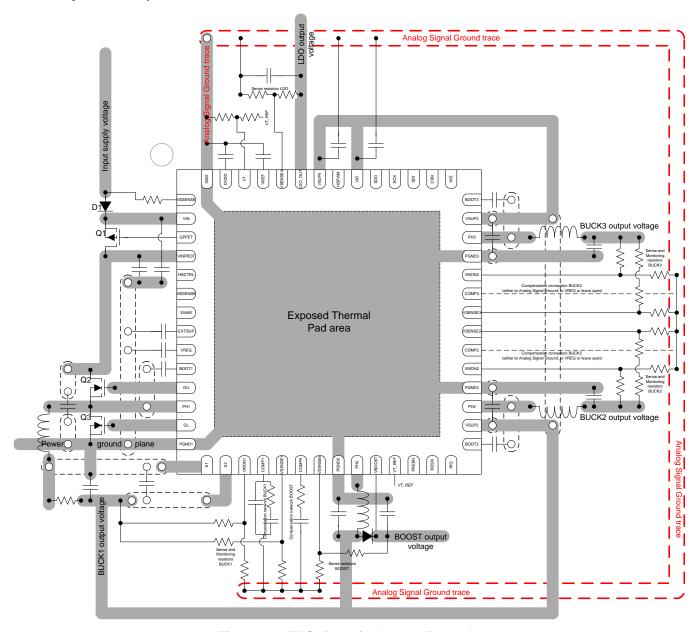

|   | 7.2 ESD Ratings8                                                          |    | 11.1 Layout Guidelines                               | . 53               |

|   | 7.3 Recommended Operating Conditions                                      |    | 11.2 Layout Example                                  | . 54               |

|   | 7.4 Thermal Information                                                   | 12 | Device and Documentation Support                     | 55                 |

|   | 7.5 Electrical Characteristics                                            |    | 12.1 Documentation Support                           | . 55               |

|   | 7.6 Timing Requirements                                                   |    | 12.2 Receiving Notification of Documentation Updates | 5 <mark>5</mark> 5 |

|   | 7.7 Switching Characteristics                                             |    | 12.3 Community Resources                             | . 55               |

|   | 7.8 Typical Characteristics                                               |    | 12.4 Trademarks                                      | . 55               |

| 8 | Detailed Description                                                      |    | 12.5 Electrostatic Discharge Caution                 | . 55               |

| U | 8.1 Overview                                                              |    | 12.6 Glossary                                        |                    |

|   | 8.2 Functional Block Diagram                                              | 13 | Mechanical, Packaging, and Orderable                 |                    |

|   | 8.3 Feature Description21                                                 |    | Information                                          | 55                 |

|   |                                                                           |    |                                                      |                    |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| hanges from Revision B (April 2014) to Revision C                                                                     | Page       |

|-----------------------------------------------------------------------------------------------------------------------|------------|

| Added the VQFNP (RWE) package option to the data sheet                                                                | 1          |

| Added pin descriptions for the S1 and S2 pins in the Pin Functions table                                              | 5          |

| Deleted the lead temperature (soldering, 10 sec), 260°C parameter from the Absolute Maximum Ratin                     | ngs table8 |

| Changed the Handling Ratings table to ESD Ratings and moved storage temperature back to the Abs Maximum Ratings table |            |

| Changed all the thermal values for the RWE package in the <i>Thermal Information</i> table                            | 8          |

| Added the Receiving Notification of Documentation Updates and Community Resources sections                            | 55         |

| hanges from Revision A (October 2013) to Revision B                                                                   | Page       |

| Changed CDM ESD Classification Level from C3B to C4B in the Features list and ESD ratings                             | 1          |

| Added device number to document title                                                                                 | 1          |

| Added Device Information table to first page and Table of Contents to second page. Moved Revision assecond page also  |            |

Moved the pin diagram and function table to before the electrical specifications and change it to the Pin

Submit Documentation Feedback

Copyright © 2013–2017, Texas Instruments Incorporated

| •  | Added test condition for I <sub>OUT</sub> = 350 mA, T <sub>J</sub> = 150°C to the V <sub>Dropout</sub> parameter in the <i>ELECTRICAL CHARACTERISTICS</i> table                                                                                    | 10               |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| •  | Changed the min value for the V <sub>HSSC HY</sub> parameter from 1.5 to 1 and deleted the typ (2.5) and max (3.5) values                                                                                                                          | 10               |

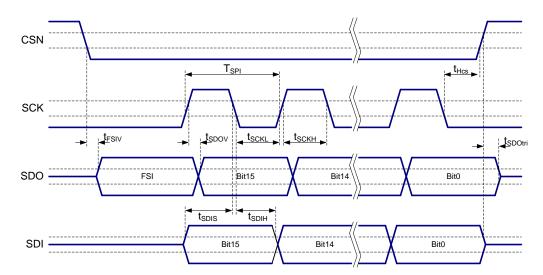

| •  | Moved all timing specifications from the <i>Electrical Characteristics</i> table into the <i>Timing Requirements</i> table and added figure references to the timing diagram                                                                       |                  |

| •  | Changed the max value for the t <sub>VSSENSE_BLK</sub> parameter from 20 to 35                                                                                                                                                                     | 13               |

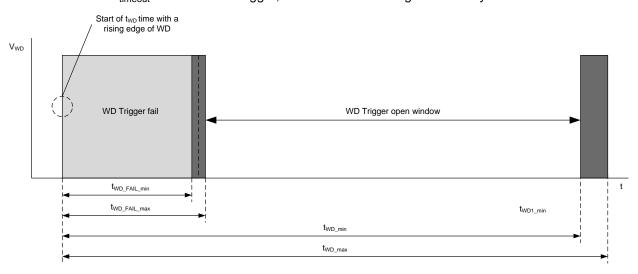

| •  | Changed the MAX value for the WD filter time parameter from 0.5 µs to 1.2 µs in the <i>Timing Requirements</i> table                                                                                                                               |                  |

| •  | Changed the min value for the t <sub>GL-BLK</sub> parameter from 10 to 5                                                                                                                                                                           | 14               |

| •  | Moved all switching characteristics out of the <i>Electrical Characteristics</i> and into the new <i>Switching Characteristics</i> table                                                                                                           | 15               |

| •  | Moved all but the first paragraph of the Description into the new Overview section in the Detailed Description section                                                                                                                             | າ 19             |

| •  | Moved the block diagram into the Detailed Description section                                                                                                                                                                                      | 20               |

| •  | Deleted the Operating Modes table and Normal Mode PWM Operation section title for Buck Controller (BUCK1)                                                                                                                                          | 21               |

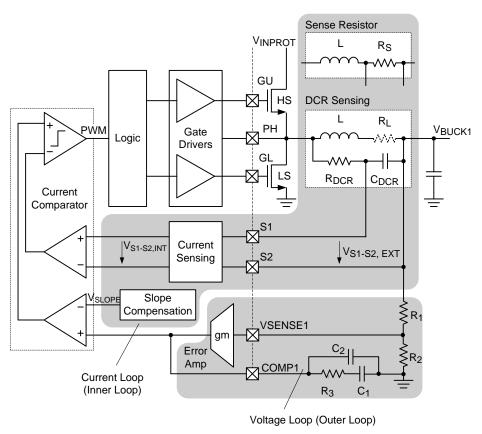

| •  | Changed the resistor name for the resistor next to C <sub>1</sub> from R <sub>1</sub> to R <sub>3</sub> and added R <sub>1</sub> and R <sub>2</sub> to the <i>Detailed Block Diagram of Buck 1 Controller</i> image                                | 21               |

| •  | Moved the component selection portion of the Synchronous Buck Converters BUCK2 and BUCK3 section into the Typical Applications section                                                                                                             | <mark>2</mark> 2 |

| •  | Moved the component selection portion of the BOOST Converter section into the Typical Applications section                                                                                                                                         | 22               |

| •  | Changed the voltage value that EXTSUP is connected to from 4.6 to 4.8 in the Gate Driver Supply section                                                                                                                                            | 23               |

| •  | Moved the SPI section into a Programming section                                                                                                                                                                                                   | 34               |

| •  | Added the Design Parameters tables for each of the Typical Application sections                                                                                                                                                                    | 42               |

| •  | Added the Adjusting the Output Voltage for the BUCK1 Controller section to the Buck Controller (BUCK1) application section                                                                                                                         | 42               |

| •  | Moved the component selection portion of the Buck Controller (BUCK1) section into the Typical Applications section                                                                                                                                 | 42               |

| •  | Changed R1 to R3 in the Compensation of the Buck Controller section                                                                                                                                                                                | 43               |

| •  | Added the Adjusting the Output Voltage for the BUCK2 and BUCK3 Converter to the Detailed Design Procedure in the Synchronous Buck Converters BUCK2 and BUCK3 section                                                                               | 45               |

| •  | Changed the inductance, capacitance and FLC values from 3.3 $\mu$ H, 20 $\mu$ F, and 12.9 kHz to 1.5 $\mu$ H, 39 $\mu$ F, and 13.7 kHz (respectively) in the <i>For example:</i> section of the <i>Compensation of the BOOST</i> Converter section |                  |

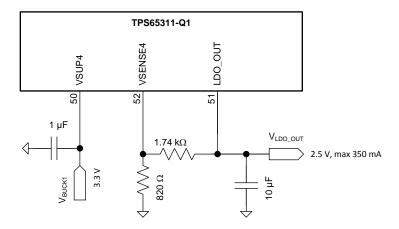

| •  | Added the Linear Regulator application section                                                                                                                                                                                                     | <mark>50</mark>  |

| •  | Added the Device and Documentation Support and Mechanical, Packaging, and Orderable Information sections. The Device and Documentation Support now includes the electrostatic discharge caution, trademark information,                            |                  |

|    | and a link to the TI Glossary                                                                                                                                                                                                                      | 55               |

| Ch | nanges from Original (October 2013) to Revision A                                                                                                                                                                                                  | Page             |

| •  | Changed document status from Product Preview to Production Data                                                                                                                                                                                    | 1                |

| •  | Deleted both min values (-44°C and -55°C) for T <sub>J</sub> in the RECOMMENDED OPERATING CONDITIONS table                                                                                                                                         | 8                |

| •  | Changed both max values for T <sub>J</sub> from 150°C to 125°C in the <i>RECOMMENDED OPERATING CONDITIONS</i> table                                                                                                                                | 8                |

| •  | Changed condition statement of ELECTRICAL CHARACTERISTICS table from $T_J$ temperature range to $T_{J(max)} = 125$                                                                                                                                 | 5°C . 9          |

| •  | Changed one test condition for the $V_{Droupout}$ parameter in the <i>ELECTRICAL CHARACTERISTICS</i> table from $T_J = 150^{\circ}\text{C}$ to $T_J = 125^{\circ}\text{C}$                                                                         | 10               |

| •  | Deleted the T <sub>J</sub> temperature range from SHUTDOWN COMPARATOR subheader row in the <i>ELECTRICAL CHARACTERISTICS</i> table                                                                                                                 | 11               |

| •  | Changed one test condition for the $I_{VT\_leak}$ parameter in the <i>ELECTRICAL CHARACTERISTICS</i> table from $T_J = -20^{\circ}\text{C}$ to $150^{\circ}\text{C}$ to $T_J = -20^{\circ}\text{C}$ to $125^{\circ}\text{C}$                       | 11               |

| •  | Changed the $T_J$ temperature range to $T_{J(max)}$ = 125°C for the INTERNAL VOLTAGE REGULATORS subheader row in the <i>ELECTRICAL CHARACTERISTICS</i> table                                                                                       |                  |

Copyright © 2013–2017, Texas Instruments Incorporated

## 5 Description (continued)

To help support system safety, the device includes voltage monitoring on all supply rails and a window-watchdog to monitor the MCU and DSP. Other features include a high-side driver which drives a warning-lamp LED, a reference voltage which is used as ADC reference in the MCU, DSP, and a shutdown comparator which, in combination with external NTC-resistor, switches off the device at too-low ambient temperature.

## 6 Pin Configuration and Functions

## **Pin Functions**

| PI    | N   | TYPE <sup>(1)</sup> | PULLUP OR | DESCRIPTION                                                                                                        |  |  |

|-------|-----|---------------------|-----------|--------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | NO. | TYPE                | PULLDOWN  | DESCRIPTION                                                                                                        |  |  |

| BOOT1 | 10  | I                   | _         | The capacitor on this pin acts as the voltage supply for the BUCK1 high-side MOSFET gate-drive circuitry.          |  |  |

| BOOT2 | 29  | I                   | _         | The capacitor on this pin acts as the voltage supply for the BUCK2 high-side MOSFET gate drive circuitry.          |  |  |

| воотз | 42  | I                   | _         | The capacitor on this pin act as the voltage supply for the BUCK3 high-side MOSFET gate drive circuitry.           |  |  |

| COMP1 | 18  | 0                   | _         | Error amplifier output for the switching controller. External compensation network is connected to this pin.       |  |  |

| COMP2 | 34  | I                   | _         | Compensation selection for the BUCK2 switching converter                                                           |  |  |

| COMP3 | 37  | I                   | _         | Compensation selection for the BUCK3 switching converter.                                                          |  |  |

| COMP5 | 20  | 0                   | _         | Error amplifier output for the boost switching controller. External compensation network is connected to this pin. |  |  |

| CSN   | 44  | I                   | Pullup    | SPI – Chip select                                                                                                  |  |  |

(1) Description of pin type: I = Input; O = Output; OD = Open-drain output

# Pin Functions (continued)

| PIN(1) PULLUP OR |     |                     |          |                                                                                                                                                                             |  |  |

|------------------|-----|---------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME             | NO. | TYPE <sup>(1)</sup> | PULLDOWN | DESCRIPTION                                                                                                                                                                 |  |  |

| DVDD             | 55  | 0                   | _        | Internal DVDD output for decoupling                                                                                                                                         |  |  |

| EXTSUP           | 8   | I                   | _        | Optional LV input for gate driver supply                                                                                                                                    |  |  |

| GL               | 13  | 0                   | _        | Gate driver – low-side FET                                                                                                                                                  |  |  |

| GND              | 56  | 0                   | _        | Analog GND, digital GND and substrate connection                                                                                                                            |  |  |

| GPFET            | 3   | 0                   | _        | Gate driver external protection PMOS FET.                                                                                                                                   |  |  |

| GU               | 11  | 0                   | _        | Gate driver – high-side FET                                                                                                                                                 |  |  |

| HSCTRL           | 5   | 0                   | _        | High-side gate driver output                                                                                                                                                |  |  |

| HSPWM            | 49  | I                   | Pulldown | High side and LED PWM input                                                                                                                                                 |  |  |

| HSSENSE          | 6   | I                   | _        | Sense input high side and LED                                                                                                                                               |  |  |

| IRQ              | 28  | OD                  | _        | Low battery interrupt output in operating mode                                                                                                                              |  |  |

| LDO_OUT          | 51  | 0                   | _        | Linear regulated output (connect a low ESR ceramic output capacitor to this pin)                                                                                            |  |  |

| PGND1            | 14  | 0                   | _        | Ground for low-side FET driver                                                                                                                                              |  |  |

| PGND2            | 32  | 0                   | _        | Power ground of synchronous converter BUCK2                                                                                                                                 |  |  |

| PGND3            | 39  | 0                   | _        | Power ground of synchronous converter BUCK3                                                                                                                                 |  |  |

| PGND5            | 22  | 0                   | _        | Power ground boost converter                                                                                                                                                |  |  |

| PH1              | 12  | 0                   | _        | Switching node - BUCK1 (floating ground for high-side FET driver)                                                                                                           |  |  |

| PH2              | 31  | 0                   | _        | Switching node BUCK2                                                                                                                                                        |  |  |

| PH3              | 40  | 0                   | _        | Switching node BUCK3                                                                                                                                                        |  |  |

| PH5              | 23  | 0                   | _        | Switching node boost                                                                                                                                                        |  |  |

| PRESN            | 26  | OD                  | _        | Peripherals reset                                                                                                                                                           |  |  |

| RESN             | 27  | OD                  | _        | System reset                                                                                                                                                                |  |  |

| S1               | 15  | I                   | _        | Differential current sense input for BUCK1                                                                                                                                  |  |  |

| S2               | 16  | I                   | Pulldown | · · · · · · · · · · · · · · · · · · ·                                                                                                                                       |  |  |

| SCK              | 46  | I                   | Pulldown | SPI – Clock                                                                                                                                                                 |  |  |

| SDI              | 45  | I                   | Pulldown | SPI – Master out, slave in                                                                                                                                                  |  |  |

| SDO              | 47  | 0                   | _        | SPI – Master in, slave out - push-pull output supplied by VIO                                                                                                               |  |  |

| VBOOST           | 24  | I                   | _        | Booster output voltage                                                                                                                                                      |  |  |

| VIN              | 2   | 1                   | _        | Unprotected supply input for the base functionality and band-gap 1. Supplied blocks are: RESET, WD, wake, SPI, temp sensing, voltage monitoring and the logic block.        |  |  |

| VINPROT          | 4   | I                   | _        | Main input supply (gate drivers and bandgap2)                                                                                                                               |  |  |

| VIO              | 48  | 1                   | _        | Supply input for the digital interface to the MCU. Voltage on this input is monitored. If VIO falls below UV threshold a reset is generated and the part enters error mode. |  |  |

| VMON1            | 17  | I                   | _        | Input for the independent voltage monitor at BUCK1                                                                                                                          |  |  |

| VMON2            | 33  | I                   | _        | Input for the independent voltage monitor at BUCK2                                                                                                                          |  |  |

| VMON3            | 38  | I                   | _        | Input for the independent voltage monitor at BUCK3                                                                                                                          |  |  |

| VREF             | 53  | 0                   | _        | Accurate reference voltage output for peripherals on the system (for example, ADC)                                                                                          |  |  |

| VREG             | 9   | 0                   | _        | Internal regulator for gate driver supply (decoupling) and VREF                                                                                                             |  |  |

| VSENSE1          | 19  | I                   | _        | Input for externally sensed voltage of the output using a resistor divider network from their respective output line to ground.                                             |  |  |

| VSENSE2          | 35  | I                   | _        | Input for externally sensed voltage of the output using a resistor divider network from their respective output line to ground                                              |  |  |

| VSENSE3          | 36  | 1                   | _        | Input for externally sensed voltage of the output using a resistor divider network from their respective output line to ground                                              |  |  |

| VSENSE4          | 52  | 1                   | _        | Input for externally sensed voltage of the output using a resistor divider network from their respective output line to ground.                                             |  |  |

| VSENSE5          | 21  | I                   | _        | Input for externally sensed voltage of the boost output using a resistor divider network from their respective output line to ground.                                       |  |  |

| VSSENSE          | 1   | I                   | _        | Input to monitor the battery line for undervoltage conditions. UV is indicated by the IRQ pin.                                                                              |  |  |

| VSUP2            | 30  | ı                   | _        | Input voltage supply for switch mode regulator BUCK2                                                                                                                        |  |  |

| VSUP3            | 41  | I                   | _        | Input voltage supply for switch mode regulator BUCK3                                                                                                                        |  |  |

| VSUP4            | 50  | ı                   | _        | Input voltage supply for linear regulator LDO                                                                                                                               |  |  |

|                  | 1   | 1                   | 1        | ,                                                                                                                                                                           |  |  |

# Pin Functions (continued)

| PII    | PIN |                     | PULLUP OR | DESCRIPTION                                                                                                                                                                                                         |

|--------|-----|---------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | TYPE <sup>(1)</sup> | PULLDOWN  | DESCRIPTION                                                                                                                                                                                                         |

| VT     | 54  | I                   | _         | Input for the comparator with shutdown functionality. This input can be used to sense an external NTC resistor to shutdown the IC in case the ambient temperature is too high or too low. Tie to GND if not in use. |

| VT_REF | 25  | 0                   | _         | Shutdown comparator reference output. Internally connected to DVDD, current-limited. When not in use can be connected to DVDD or left open.                                                                         |

| WAKE   | 7   | I                   | Pulldown  | Wake up input                                                                                                                                                                                                       |

| WD     | 43  | I                   | Pulldown  | Watchdog input. WD is the trigger input coming from the MCU.                                                                                                                                                        |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                     |                               | MIN                               | MAX                                        | UNIT |  |

|---------------------|-------------------------------|-----------------------------------|--------------------------------------------|------|--|

|                     | VIN                           | -0.3                              | 80                                         |      |  |

|                     | VINPROT                       | -0.3                              | 60                                         |      |  |

|                     | VSUP2, 3 (BUCK2 and 3)        | -0.3                              | 20                                         |      |  |

| Supply inputs       | VSUP4 (Linear Regulator)      | -0.3                              | 20                                         | V    |  |

|                     | VBOOST                        | -0.3                              | 20                                         |      |  |

|                     | EXTSUP                        | -0.3                              | 13                                         |      |  |

|                     | VIO                           | -0.3                              | 5.5                                        |      |  |

|                     | PH1                           | –1<br>–2 for 100 ns               | 60                                         |      |  |

|                     | VSENSE1                       | -0.3                              | 20                                         |      |  |

|                     | COMP1                         | -0.3                              | 20                                         |      |  |

| Buck controller     | GU-PH1, GL-PGND1, BOOT1-PH1   | -0.3                              | 8                                          | V    |  |

|                     | S1, S2                        | -0.3                              | 20                                         |      |  |

|                     | S1-S2                         | -2                                | 2                                          |      |  |

|                     | BOOT1                         | -0.3                              | 68                                         |      |  |

|                     | VMON1                         | -0.3                              | 20                                         |      |  |

|                     | BOOT2, BOOT3                  | -1                                | 20                                         |      |  |

|                     | PH2, PH3                      | -1 <sup>(2)</sup><br>-2 for 10 ns | 20 <sup>(2)</sup>                          |      |  |

| Buck controller     | VSENSE2, VSENSE3              | -0.3                              | 20                                         | V    |  |

|                     | COMP2, COMP3                  | -0.3                              | 20                                         |      |  |

|                     | VMON2, VMON3                  | -0.3                              | 20                                         |      |  |

|                     | BOOTx – PHx                   | -0.3                              | 8                                          |      |  |

| Parameters.         | LDO_OUT                       | -0.3                              | 8                                          | V    |  |

| Linear regulator    | VSENSE4                       | -0.3                              | 20                                         | V    |  |

|                     | VSENSE5                       | -0.3                              | 20                                         |      |  |

| Boost converter     | PH5                           | -0.3                              | 20                                         | V    |  |

|                     | COMP5                         | -0.3                              | 20                                         |      |  |

| Divital interfere   | CSN, SCK, SDO, SDI, WD, HSPWM | -0.3                              | 5.5                                        | V    |  |

| Digital interface   | RESN, PRESN, IRQ              | -0.3                              | 20                                         | V    |  |

| Wake input          | WAKE                          | -1 <sup>(3)</sup>                 | 60                                         | V    |  |

| Protection FET      | GPFET                         | -0.3                              | 80                                         | \/   |  |

| FIOLECTION FET      | VIN – GPFET                   | -0.3                              | 20                                         | V    |  |

| Battery sense input | VSSENSE                       | -1 <sup>(3)</sup>                 | 60<br>Transients up to 80 V <sup>(4)</sup> | V    |  |

| Tomporature consc   | VT                            | -0.3                              | 5.5                                        | \/   |  |

| Temperature sense   | VT_REF                        | -0.3                              | 20                                         | V    |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> Maximum 3.5 A

<sup>(3)</sup>  $I_{max} = 100 \text{ mA}$

<sup>(4)</sup> Internally clamped to 60-V, 20-kΩ external resistor required, current into pin limited to 1 mA.

## **Absolute Maximum Ratings (continued)**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                          |                                             | MIN  | MAX | UNIT |

|--------------------------|---------------------------------------------|------|-----|------|

| Reference voltage        | VREF                                        | -0.3 | 5.5 | V    |

|                          | HSSENSE                                     | -0.3 | 60  |      |

| High-side and LED driver | HSCTRL                                      | -0.3 | 60  | V    |

|                          | VINPROT-HSSENSE, VINPROT-HSCTRL             | -0.3 | 20  |      |

| Driver supply decoupling | VREG                                        | -0.3 | 8   | V    |

| Supply decoupling        | DVDD                                        | -0.3 | 3.6 | V    |

|                          | Junction temperature range, T <sub>J</sub>  | -55  | 150 |      |

| Temperature ratings      | Operating temperature range, T <sub>A</sub> | -55  | 125 | °C   |

|                          | Storage temperature, T <sub>stg</sub>       | -55  | 165 |      |

## 7.2 ESD Ratings

|                    |               |                                                                  |                                                 | VALUE | UNIT |

|--------------------|---------------|------------------------------------------------------------------|-------------------------------------------------|-------|------|

|                    |               | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup>          |                                                 | ±1000 |      |

|                    | Flactrostatio | ectrostatic charged Charged-device model (CDM), per AEC Q100-011 | VT pin                                          | ±150  |      |

| V <sub>(ESD)</sub> | discharge     |                                                                  | Corner pins (1, 14, 15, 28, 29, 42, 43, and 56) | ±750  | V    |

|                    |               |                                                                  | All other pins                                  | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                       |                                                                      | MIN | NOM | MAX | UNIT |  |

|----------------|-------------------------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|--|

|                | Supply voltage at VIN, VINPROT, VS                    | Supply voltage at VIN, VINPROT, VSSENSE                              |     |     | 40  | V    |  |

|                | T <sub>A</sub> Operating free air temperature         | All electrical characteristics in specification                      | -40 |     | 125 |      |  |

| T <sub>A</sub> |                                                       | Shutdown comparator and internal voltage regulators in specification | -55 |     | 125 | °C   |  |

|                | T <sub>J</sub> Operating virtual junction temperature | All electrical characteristics in specification                      |     |     | 150 |      |  |

| $T_{J}$        |                                                       | Shutdown comparator and internal voltage regulators in specification |     |     | 150 | °C   |  |

### 7.4 Thermal Information

|                      |                                              | TPS65       |            |      |

|----------------------|----------------------------------------------|-------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RWE (VQFNP) | RVJ (VQFN) | UNIT |

|                      |                                              | 56 PINS     | 56 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 22.1        | 22.3       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 9.6         | 9.8        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.2         | 6.3        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.1         | 0.1        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.2         | 6.2        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.4         | 0.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: TPS65311-Q1

### 7.5 Electrical Characteristics

VIN = VINPROT 4.8 V to 40 V, VSUPx = 3 V to 5.5 V, EXTSUP = 0 V,  $T_{J(max)}$  = 150°C, unless otherwise noted

|                               | PARAMETER                                                        | TEST CONDITIONS                                                                                                                                                                                                               | MIN  | TYP   | MAX  | UNIT |

|-------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| INPUT VOLTAG                  | E-CURRENT CONSUMPTION                                            |                                                                                                                                                                                                                               |      |       |      |      |

| V <sub>IN</sub>               | Device operating range                                           | Buck regulator operating range, Voltage on VIN and VINPROT pins                                                                                                                                                               | 4    |       | 50   | ٧    |

| .,                            | Davis an aread through and                                       | Falling VIN                                                                                                                                                                                                                   | 3.5  | 3.6   | 3.8  | V    |

| $V_{POR}$                     | Power-on reset threshold                                         | Rising VIN                                                                                                                                                                                                                    | 3.9  | 4.2   | 4.3  | V    |

| V <sub>POR_hyst</sub>         | Power-on reset hysteresis on VIN                                 |                                                                                                                                                                                                                               | 0.47 | 0.6   | 0.73 | V    |

| I <sub>LPM0</sub>             | LPM0 current consumption <sup>(1)(2)</sup>                       | All off, wake active, V <sub>IN</sub> = 13 V<br>Total current into VSSENSE, VIN and VINPROT                                                                                                                                   |      |       | 44   | μА   |

| I <sub>LPM0</sub>             | LPM0 current (commercial vehicle application) consumption (3)(2) | All off, wake active, V <sub>IN</sub> = 24.5 V<br>Total current into VSSENSE, VIN and VINPROT                                                                                                                                 |      |       | 60   | μΑ   |

| I <sub>ACTIVE1</sub>          | ACTIVE total current consumption <sup>(1)(4)</sup>               | $\begin{array}{l} \text{BUCK1} = \text{on, V}_{\text{IN}} = \text{13 V, EXTSUP} = \text{0 V,} \\ \text{Q}_{\text{g}} \text{ of BUCK1 FETs} = \text{15 nC.} \\ \text{Total current into VSSENSE, VIN and VINPROT} \end{array}$ |      | 32    |      | mA   |

| I <sub>ACTIVE123</sub>        | ACTIVE total current consumption <sup>(1)(4)</sup>               | $\begin{array}{l} \text{BUCK1/2/3} = \text{on, V}_{\text{IN}} = 13 \text{ V}, \\ \text{Q}_{\text{g}} \text{ of BUCK1 FETs} = 15 \text{ nC}. \\ \text{Total current into VSSENSE, VIN and VINPROT} \end{array}$                |      | 40    |      | mA   |

| I <sub>ACTIVE1235</sub>       | ACTIVE current consumption (1)(4)                                | BUCK1/2/3, LDO, BOOST, high-side switch = on, $V_{IN}$ = 13 V, $Q_g$ of BUCK1 FETs = 15 nC. EXTSUP = 5 V from BOOST Total current into VSSENSE, VIN and VINPROT                                                               |      | 31    |      | mA   |

| I <sub>ACTIVE1235_noEXT</sub> | ACTIVE current consumption (1)(4)                                | BUCK1/2/3, LDO, BOOST, high-side switch = on, $V_{IN}$ = 13 V, $Q_g$ of BUCK1 FETs = 15 nC, EXTSUP = open Total current into VSENSE, VIN and VINPROT                                                                          |      | 53    |      | mA   |

| BUCK CONTRO                   | DLLER (BUCK1)                                                    |                                                                                                                                                                                                                               |      |       |      |      |

| V <sub>BUCK1</sub>            | Adjustable output voltage range                                  |                                                                                                                                                                                                                               | 3    |       | 11   | V    |

| V <sub>Sense1_NRM</sub>       | Internal reference voltage in operating mode                     | VSENSE1 pin, load = 0 mA,<br>Internal REF = 0.8 V                                                                                                                                                                             | -1%  |       | 1%   |      |

| V                             | VS1-2 for forward OC in CCM                                      | Maximum sense voltage VSENSE1 = 0.75 V (low duty cycle)                                                                                                                                                                       | 60   | 75    | 90   | mV   |

| V <sub>S1-2</sub>             | VS1-2 for forward OC III CCM                                     | Minimum sense voltage VSENSE 1 = 1 V (negative current limit)                                                                                                                                                                 | -65  | -37.5 | -23  | IIIV |

| A <sub>CS</sub>               | Current sense voltage gain                                       | ΔVCOMP1 / Δ (VS1 - VS2)                                                                                                                                                                                                       | 4    | 8     | 12   | V/V  |

| I <sub>Gpeak</sub>            | Gate driver peak current                                         | VREG = 5.8 V                                                                                                                                                                                                                  |      | 0.6   |      | Α    |

| R <sub>DSON_DRIVER</sub>      | Source and sink driver                                           | I <sub>G</sub> current for external MOSFET = 200 mA,<br>VREG = 5.8 V, V <sub>BOOT1-PH1</sub> = 5.8 V                                                                                                                          |      | 5     | 10   | Ω    |

| V <sub>DIO1</sub>             | Bootstrap diode forward voltage                                  | I <sub>BOOT1</sub> = -200 mA, VREG-BOOT1                                                                                                                                                                                      | 0.8  |       | 1.1  | ٧    |

| ERROR AMPLI                   | FIER (OTA) FOR BUCK CONTROLL                                     | ERS AND BOOST CONVERTER                                                                                                                                                                                                       |      |       |      |      |

| gm <sub>EA</sub>              | Forward transconductance                                         | COMP1/2/3/5 = 0.8 V; source/sink = 5 μA,<br>Test in feedback loop                                                                                                                                                             |      | 0.9   |      | mS   |

| A <sub>EA</sub>               | Error amplifier DC gain                                          |                                                                                                                                                                                                                               | 60   |       |      | dB   |

|                               | S BUCK CONVERTER BUCK2 AND                                       | BUCK3 (BUCK2/3)                                                                                                                                                                                                               |      |       | "    |      |

| VSUP2/3                       | Supply voltage                                                   |                                                                                                                                                                                                                               | 3    |       | 11   | V    |

| V <sub>BUCK2/3</sub>          | Regulated output voltage range                                   | $I_{load} = 02 \text{ A}$<br>VSUPx = $V_{BUCK2/3} + I_{load} \times 0.2 \Omega$                                                                                                                                               | 0.8  |       | 5.5  | V    |

| R <sub>DSON-HS</sub>          | R <sub>DSON</sub> high-side switch                               | V <sub>BOOTx -PHx</sub> = 5.8 V                                                                                                                                                                                               |      |       | 0.20 | Ω    |

| R <sub>DSON-LS</sub>          | R <sub>DSON</sub> low-side switch                                | VREG = 5.8 V                                                                                                                                                                                                                  |      |       | 0.20 | Ω    |

| I <sub>HS-Limit</sub>         | High-side switch current-limit                                   | Static current limit test. In application L > 1 µH at I <sub>HS-Limit</sub> and I <sub>LS-Limit</sub> to limit dl / dt                                                                                                        | 2.5  | 2.9   | 3.3  | А    |

| I <sub>LS-Limit</sub>         | Low-side switch current-limit                                    | Static current limit test. In application L > 1 µH at I <sub>HS-Limit</sub> and I <sub>LS-Limit</sub> to limit dl / dt                                                                                                        | 2    | 2.5   | 3    | Α    |

<sup>(1)</sup>  $T_A = 25^{\circ}C$

<sup>(2)</sup> Quiescent Current Specification does not include the current flow through the external feedback resistor divider. Quiescent Current is non-switching current, measured with no load on the output with VBAT = 13 V.

<sup>(3)</sup>  $T_A = 130^{\circ}C$

<sup>(4)</sup> Total current consumption measured on EVM includes switching losses.

VIN = VINPROT 4.8 V to 40 V, VSUPx = 3 V to 5.5 V, EXTSUP = 0 V,  $T_{J(max)}$  = 150°C, unless otherwise noted

|                            | PARAMETER                                                                 | TEST CONDITION                                                                                                    | IS                                               | MIN        | TYP      | MAX           | UNIT                                           |

|----------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------|----------|---------------|------------------------------------------------|

| VSUP <sub>Lkg</sub>        | VSUP leakage current                                                      | VSUP = 10 V for high side, controll $T_J = 100$ °C                                                                | er disabled,                                     |            | 1        | 2             | μΑ                                             |

| V <sub>Sense2/3</sub>      | Feedback voltage                                                          | With respect to the 800-mV interna                                                                                | l reference                                      | -1%        |          | 1%            |                                                |

| COMP2/3 <sub>HTH</sub>     | COMP2/3 Input threshold low                                               |                                                                                                                   |                                                  | 0.9        |          | 1.5           | V                                              |

| COMP2/3 <sub>LTH</sub>     | COMP2/3 Input threshold high                                              |                                                                                                                   |                                                  | VREG – 1.2 |          | VREG –<br>0.3 | V                                              |

| R <sub>TIEOFF COMP23</sub> | COMP2/3 internal tie-off                                                  | BUCK2/3 enabled. Resistor to VRE each                                                                             | G and GND,                                       | 70         | 100      | 130           | kΩ                                             |

| V <sub>DIO2 3</sub>        | Bootstrap diode forward voltage                                           | $I_{BOOT1} = -200 \text{ mA}, VREG-BOOT2,$                                                                        | VREG-BOOT3                                       |            | 1.1      | 1.2           | V                                              |

| BOOST CONVE                | ERTER                                                                     |                                                                                                                   |                                                  |            |          |               |                                                |

| V <sub>Boost</sub>         | Boost adjustable output voltage range                                     | Using 3.3-V input voltage, leak_swi                                                                               | itch ≤ 1 A                                       | 4.5        |          | 15            | V                                              |

| $V_{Boost}$                | Boost adjustable output voltage range                                     | Using 3.3-V input voltage $I_{loadmax} = I_{peak\_switch} = 0.3 A$                                                | 20 mA,                                           | 15         |          | 18.5          | V                                              |

| R <sub>DS-ON_BOOST</sub>   | Internal switch on-resistance                                             | VREG = 5.8 V                                                                                                      |                                                  |            | 0.3      | 0.5           | Ω                                              |

| V <sub>Sense5</sub>        | Feedback voltage                                                          | With respect to the 800-mV interna                                                                                | l reference                                      | -1%        |          | 1%            |                                                |

| I <sub>CLBOOST</sub>       | Internal switch current-limit                                             |                                                                                                                   |                                                  | 1          |          | 1.5           | Α                                              |

| LINEAR REGUL               | LATOR LDO                                                                 |                                                                                                                   |                                                  |            |          |               |                                                |

| VSUP4                      | Device operating range for LDO                                            | Recommended operating range                                                                                       |                                                  | 3          |          | 7             | V                                              |

| $V_{LDO}$                  | Regulated output range                                                    | I <sub>OUT</sub> = 1 mA to 350 mA                                                                                 |                                                  | 0.8        |          | 5.25          | V                                              |

| $V_{RefLDO}$               | DC output voltage tolerance at VSENSE4                                    | VSENSE4 = $0.8 \text{ V}$ (regulated at inte VSUP4 = $3 \text{ V}$ to $7 \text{ V}$ , $I_{OUT} = 1 \text{ mA to}$ | -2%                                              |            | 2%       |               |                                                |

| $V_{\text{step1}}$         | Load step 1                                                               | VSENSE4 = 0.8 V (regulated at intellout = 1 mA to 101 mA, $C_{LDO}$ = 6 to 50 $\mu$ F, $t_{rise}$ = 1 $\mu$ s     |                                                  |            |          |               |                                                |

| V <sub>Sense4</sub>        | Feedback voltage                                                          | With respect to the 800-mV interna                                                                                | -1%                                              |            | 1%       |               |                                                |

|                            |                                                                           | I <sub>OUT</sub> = 350 mA, T <sub>J</sub> = 25°C                                                                  | I <sub>OUT</sub> = 350 mA, T <sub>J</sub> = 25°C |            |          |               |                                                |

| $V_{Dropout}$              | Drop out voltage                                                          | I <sub>OUT</sub> = 350 mA, T <sub>J</sub> = 125°C                                                                 |                                                  |            | 156      | 180           | mV                                             |

|                            |                                                                           | I <sub>OUT</sub> = 350 mA, T <sub>J</sub> = 150°C                                                                 |                                                  |            | 275      | 335           |                                                |

| I <sub>OUT</sub>           | Output current                                                            | V <sub>OUT</sub> in regulation                                                                                    |                                                  | -350       |          | -1            | mA                                             |

| I <sub>LDO-CL</sub>        | Output current limit                                                      | V <sub>OUT</sub> = 0 V, VSUP4 = 3 V to 7 V                                                                        |                                                  | -1000      |          | -400          | mA                                             |

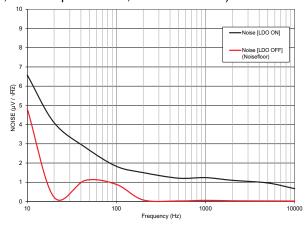

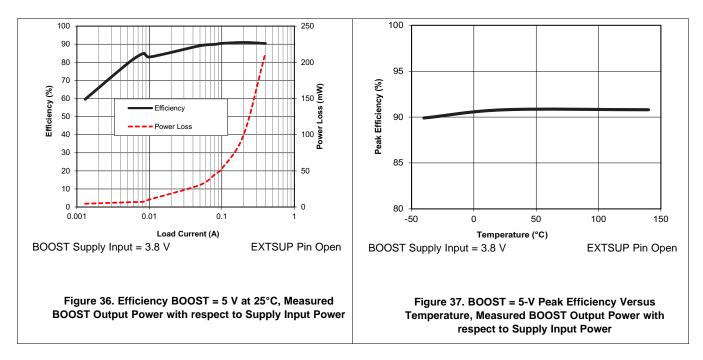

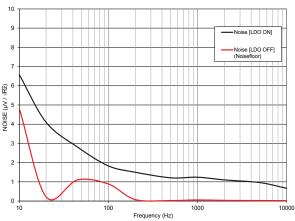

|                            |                                                                           |                                                                                                                   | Freq = 100 Hz                                    |            | 60       |               |                                                |

| $PSRR_{LDO}$               | Power supply ripple rejection                                             | $V_{ripple} = 0.5 V_{PP}, I_{OUT} = 300 \text{ mA},$<br>$C_{LDO} = 10 \mu\text{F}$                                | Freq = 4 kHz                                     |            | 50       |               | dB                                             |

|                            |                                                                           | Ομο = 10 μι                                                                                                       | Freq = 150 kHz                                   |            | 25       |               |                                                |

| LDOns <sub>10-100</sub>    | Output noise 10 Hz - 100 Hz                                               | 10-μF output capacitance, $V_{LDO} = 2$                                                                           | 2.5 V                                            |            |          | 20            | μV/√(Hz)                                       |

| LDOns <sub>100-1k</sub>    | Output noise 100 Hz - 10 kHz                                              | 10-μF output capacitance, $V_{LDO} = 2$                                                                           | 2.5 V                                            |            |          | 6             | μV/√(Hz)                                       |

| C <sub>LDO</sub>           | Output capacitor                                                          | Ceramic capacitor with ESR range, 100 m $\Omega$                                                                  | $C_{LDO\_ESR} = 0$ to                            | 6          |          | 50            | μF                                             |

| LED AND HIGH               | I-SIDE SWITCH CONTROL                                                     |                                                                                                                   |                                                  |            |          |               |                                                |

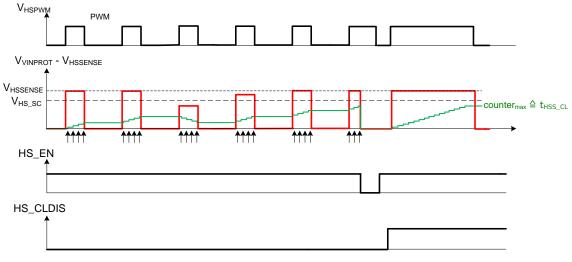

| V <sub>HSSENSE</sub>       | Current sense voltage                                                     | VINPROT – HSSENSE, high-side s<br>limit                                                                           | switch in current                                | 370        | 400      | 430           | mV                                             |

| VCM <sub>HSSENSE</sub>     | Common mode range for current sensing                                     | See VINPROT                                                                                                       |                                                  | 4          |          | 60            | V                                              |

| $V_{HSOL\_TH}$             | VINPROT – HSSENSE open load threshold                                     | Ramping negative Ramping positive                                                                                 |                                                  | 5<br>26    | 20<br>38 | 35<br>50      | mV                                             |

|                            |                                                                           | 1 31                                                                                                              |                                                  | 10         | 18       | 28            | mV                                             |

| Vuent HV                   | Open load hysteresis                                                      |                                                                                                                   |                                                  |            |          | -9            |                                                |

| V <sub>HSOL_HY</sub>       | Open load hysteresis                                                      | Ramping positive                                                                                                  |                                                  | 88%        | 92.5%    | 96%           | VHSSENISE                                      |

| V <sub>HSOL_HY</sub>       | Open load hysteresis  VINPROT – HSSENSE load short detection threshold    | Ramping positive  Ramping negative from load short of                                                             | condition                                        | 88%<br>87  | 92.5%    | 96%<br>93     | V <sub>HSSENSE</sub> % of V <sub>HSSENSE</sub> |

|                            | VINPROT – HSSENSE load short                                              | . 5.                                                                                                              | condition                                        |            |          |               |                                                |

| V <sub>HS SC</sub>         | VINPROT – HSSENSE load short detection threshold  VINPROT – HSSENSE short | . 5.                                                                                                              | condition                                        | 87         |          |               | % of V <sub>HSSENSE</sub> % of                 |

Submit Documentation Feedback

Copyright © 2013–2017, Texas Instruments Incorporated

VIN = VINPROT 4.8 V to 40 V, VSUPx = 3 V to 5.5 V, EXTSUP = 0 V,  $T_{J(max)} = 150 ^{\circ}\text{C}$ , unless otherwise noted

|                          | PARAMETER                                                               | TEST CONDITIONS                                                                                                 | MIN  | TYP          | MAX  | UNIT     |

|--------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|--------------|------|----------|

| $V_{OS\_HS}$             | Overshoot during turn-on                                                | V <sub>OS_HS</sub> = VINPROT - HSSENSE                                                                          |      |              | 400  | mV       |

| I <sub>CL_HSCTRL</sub>   | HSCTRL current-limit                                                    |                                                                                                                 | 2    | 4.1          | 5    | mA       |

| R <sub>PU_HSCTRL</sub>   |                                                                         | Between VINPROT and HSCTRL                                                                                      | 70   | 100          | 130  |          |

| R <sub>PU_HSCTRL</sub> - | Internal pullup resistors                                               | Between HSCTRL and HSSENSE                                                                                      | 70   | 100          | 130  | kΩ       |

| V <sub>I_high</sub>      | High level input voltage                                                | HSPWM, VIO = 3.3 V                                                                                              | 2    |              |      | V        |

| $V_{I\_low}$             | Low level input voltage                                                 | HSPWM, VIO = 3.3 V                                                                                              |      |              | 0.8  | V        |

| V <sub>I_hys</sub>       | Input voltage hysteresis                                                | HSPWM, VIO = 3.3 V                                                                                              | 150  |              | 500  | mV       |

| R <sub>SENSE</sub>       | External sense resistor                                                 | Design info, no device parameter                                                                                | 1.5  |              | 50   | Ω        |

| C <sub>GS</sub>          | External MOSFET gate source capacitance                                 |                                                                                                                 | 100  |              | 2000 | pF       |

| $C_{GD}$                 | External MOSFET gate drain capacitance                                  |                                                                                                                 |      |              | 500  | pF       |

| REFERENCE \              | /OLTAGE                                                                 | 1                                                                                                               |      |              |      |          |

| V <sub>REF</sub>         | Reference voltage                                                       |                                                                                                                 |      | 3.3          |      | V        |

| V <sub>REF-tol</sub>     | Reference voltage tolerance                                             | I <sub>VREF</sub> = 5 mA                                                                                        | -1%  |              | 1%   |          |

| I <sub>REFCL</sub>       | Reference voltage current-limit                                         |                                                                                                                 | 10   |              | 25   | mA       |

| C <sub>VREF</sub>        | Capacitive load                                                         |                                                                                                                 | 0.6  |              | 5    | μF       |

| REFns <sub>10-100</sub>  | Output noise 10 Hz–100 Hz                                               | 2.2 μF output capacitance, I <sub>VREF</sub> = 5 mA                                                             |      |              | 20   | μV/√(Hz) |

| REFns <sub>100-1k</sub>  | Output noise 100 Hz–10 kHz                                              | 2.2 µF output capacitance, I <sub>VREF</sub> = 5 mA                                                             |      |              | 6    | μV/√(Hz) |

|                          |                                                                         | Threshold, V <sub>REF</sub> falling                                                                             | 2.91 | 3.07         | 3.12 | V        |

| V <sub>REF_OK</sub>      | Reference voltage OK threshold                                          | Hysteresis                                                                                                      | 14   | 70           | 140  | mV       |

| SHUTDOWN C               | OMPARATOR                                                               |                                                                                                                 |      |              |      |          |

|                          | Chutdown comparator reference                                           | $I_{VT\_REF}$ = 20 μA. Measured as drop voltage with respect to VDVDD                                           | 10   | 17           | 500  |          |