• **Complete Power Supply for Cellular PW PACKAGE** (TOP VIEW) Handsets 28 🗌 V<sub>CC</sub> Three Low-Dropout Regulators (LDOs) with RESET 10 100-mV Dropout VCP [ 2 ПРЬ 27 GND CP 3 Г 26 GND Less Than 1 µA Supply Current in CP  $\Pi 4$ 25 **ON** Shutdown Typ Π5 EN CP 24 CL • 250-ms Microprocessor Reset Output 6 23 VL GND [ 10-mA Charge-Pump Driver Configurable EN Π7 22 REF For Inverted or Doubled Output ON 8 21 Separate Enables for LDOs and Charge 9 20 🗌 VB VA Pump CA 10 19 CB 1.185-V Reference PA [ 11 18 ON REM 12 17 GND [ GND 28-Pin TSSOP Package EN\_A 13 16 EN\_B 14 15 PB Vcc L

# description

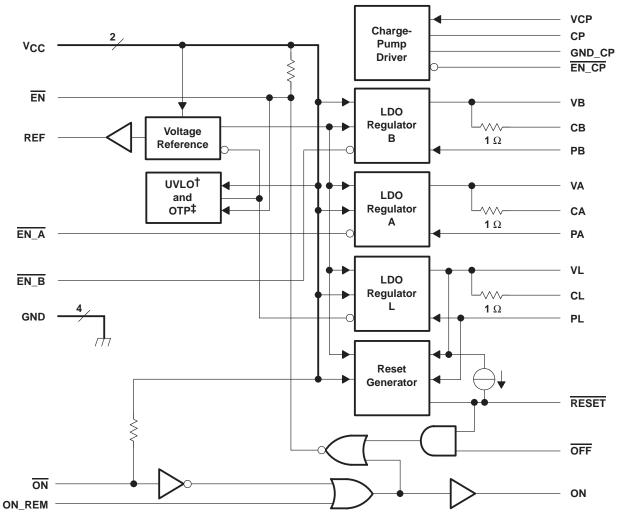

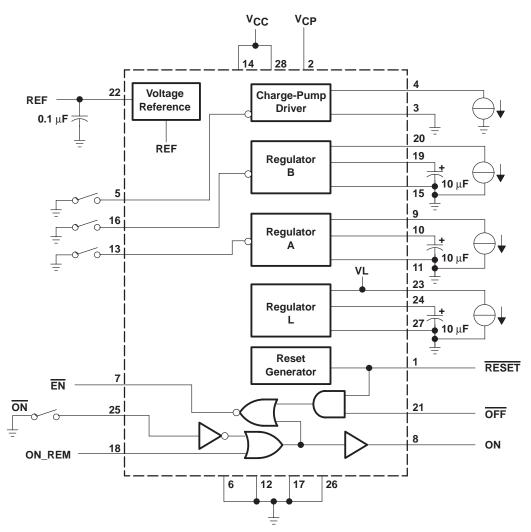

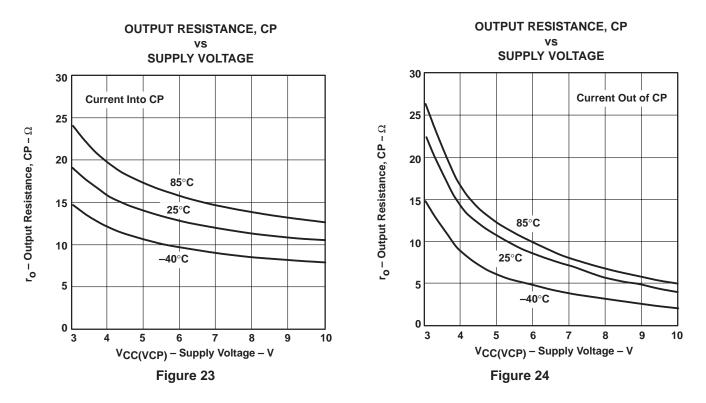

The TPS9110 incorporates a complete power supply system for a cellular subscriber terminal that uses battery packs with three or four NiMH/NiCd cells or a single lithium-ion cell. The device includes three low-dropout linear regulators rated for 3.3 V or 3 V at 100 mA each, a charge-pump driver, and logic that includes a 250-ms reset, on/off control, and processor interface. Regulators A and B and the charge-pump driver have separate enables allowing circuitry to be powered up or down as necessary to conserve battery power. Regulators VL, VA, and VB, and the charge pump driver are active as soon as UVLO and OTP are valid and ON is toggled low.

The TPS9110 operates over a free-air temperature range of –40°C to 85°C and is supplied in a 28-pin TSSOP package.

| Т             | PACKAGED DEVICE | CHIP FORM |

|---------------|-----------------|-----------|

| 'A            | TSSOP (PW)      | (Y)       |

| -40°C to 85°C | TPS9110IPWLE    | TPS9110Y  |

AVAILABLE OPTIONS

The PW package is only available left-end taped and reeled.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1997, Texas Instruments Incorporated

# functional block diagram

<sup>†</sup> UVLO - Undervoltage lockout <sup>‡</sup>OTP - Overtemperature protection

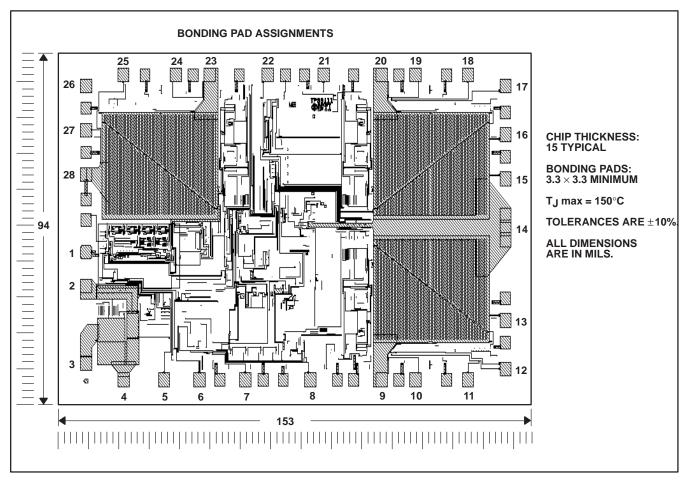

# **TPS9110Y** chip information

These chips, when properly assembled, display characteristics similar to those of the TPS9110. Thermal compression or ultrasonic bonding may be used on the doped aluminum bonding pads. The chips may be mounted with conductive epoxy or a gold-silicon preform.

# **Terminal Functions**

| TERMI  | NAL              | 1/0 | DECODIDITION                                                                                                                           |

|--------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO.              | I/O | DESCRIPTION                                                                                                                            |

| CA     | 10               |     | Regulator A filter capacitor connection                                                                                                |

| EN_A   | 13               | Ι   | Regulator A enable input. A logic low on EN_A turns on regulator A.                                                                    |

| PA     | 11               | Ι   | Program A. PA provides programming input for regulator A.                                                                              |

| VA     | 9                | 0   | Regulator A output voltage                                                                                                             |

| СВ     | 19               |     | Regulator B filter capacitor connection                                                                                                |

| EN_B   | 16               | Ι   | Regulator B enable input. A logic low on EN_B turns on regulator B.                                                                    |

| PB     | 15               | Ι   | Program B. PB provides programming input for regulator B.                                                                              |

| VB     | 20               | 0   | Regulator B output voltage                                                                                                             |

| CL     | 24               |     | Regulator L filter capacitor connection                                                                                                |

| PL     | 27               | Ι   | Program L. PL provides voltage programming input for regulator L.                                                                      |

| VL     | 23               | 0   | Regulator L output voltage                                                                                                             |

| GND    | 6, 12,<br>17, 26 |     | Ground. GND terminals should be externally connected to ground to ensure proper functionality.                                         |

| REF    | 22               | 0   | 1.185-V reference output. Decouple REF with an external 0.01- $\mu$ F to 0.1- $\mu$ F capacitor to ground.                             |

| VCC    | 14, 28           |     | Supply voltage input. $V_{CC}$ terminals are not connected internally and must be externally connected to ensure proper functionality. |

| CP     | 4                | 0   | Charge pump driver output                                                                                                              |

| EN_CP  | 5                | Ι   | Charge pump driver enable input. Logic low on EN_CP turns on the charge pump.                                                          |

| GND_CP | 3                |     | Charge pump driver ground                                                                                                              |

| VCP    | 2                |     | Charge pump driver supply voltage                                                                                                      |

| EN     | 7                | I/O | Enable signal input/output. A logic low on EN enables the TPS9110.                                                                     |

| OFF    | 21               | Ι   | Off-signal input. A logic low on OFF turns off the TPS9110.                                                                            |

| ON     | 8                | 0   | On-signal output. ON is the logical inversion of ON.                                                                                   |

| ON     | 25               | Ι   | On signal. A logic low on ON enables the TPS9110.                                                                                      |

| ON_REM | 18               | Ι   | Remote on. A logic high on ON_REM enables the TPS9110.                                                                                 |

| RESET  | 1                | 0   | Microprocessor reset output. RESET is a logic low for 250 ms at power-up.                                                              |

#### detailed description

#### voltage reference

The regulators and reset generator utilize an internal 1.185-V band-gap voltage reference. The reference is also buffered and brought out on REF for external use; REF can source a maximum of 2 mA. A 0.01- $\mu$ F to 0.1- $\mu$ F capacitor must be connected between REF and ground.

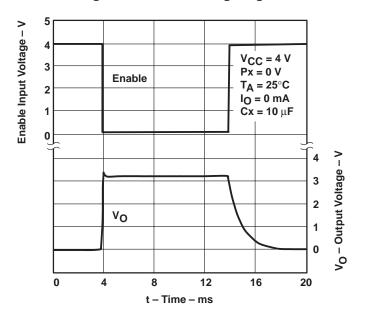

#### LDO regulators

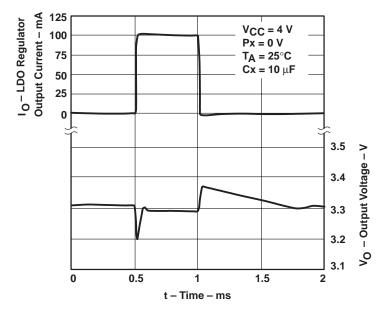

The TPS9110 includes three low-dropout regulators, implemented with 1- $\Omega$  PMOS series-pass transistors, with quiescent supply currents of 100  $\mu$ A. Each of the regulators can supply up to 100 mA of continuous output current. The 1- $\Omega$  PMOS series-pass transistor achieves the dropout voltage of 100 mV at the maximum-rated output current. Each regulator output voltage can be independently programmed to either 3.3 V or 3 V using its programming control input PL, PA or PB (Px). A logic low on Px sets the output voltage of the regulator to 3.3 V; a logic high sets it to 3 V.

Each LDO contains a current limit circuit. When the current demand on the regulator exceeds the current limit, the output voltage drops in proportion to the excess current. When the excess load current is removed, the output voltage returns to regulation. Exceeding the current limit on VL can disable the TPS9110. If enough current demand is placed on VL, the output voltage drops below the reset threshold voltage causing RESET to go low, effectively unlatching the enable.

VL is intended to be the primary supply voltage for the microprocessor and other system logic functions. VA and VB can power low-noise analog circuits and/or implement system power management. The enable terminals  $\overline{EN}_{A}$  and  $\overline{EN}_{B}$  are utilized to power down circuitry when it is not required.  $\overline{EN}_{A}$  and  $\overline{EN}_{B}$  are TTL-compatible inputs with 10-µA active current-source pullups. A logic low enables the respective regulator while a logic high pulls the regulator output voltage to ground and reduces the regulator quiescent current to leakage levels.

Stability of the LDOs is ensured by the addition of compensation terminals CL, CA, and CB, which connect to the output of the regulator through an internal  $1-\Omega$  resistor. This compensation scheme allows for capacitors with equivalent series resistance (ESR) of up to  $15 \Omega$ , eliminating the need for expensive, low-ESR capacitors.

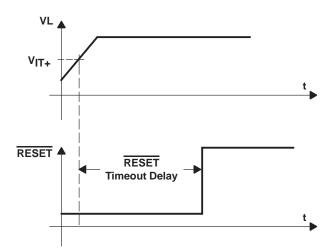

#### reset generator

RESET is a microprocessor reset signal that goes to logic low at power-up, or whenever VL drops below 2.93 V (2.6 V for 3-V applications), and remains in that state for 250 ms after VL exceeds the RESET threshold (see Figure 5). The open-drain output has a  $30-\mu$ A pullup that eliminates the need for an external pullup resistor and still allows it to be connected with other open-drain or open-collector signals. RESET is valid for supply voltages as low as 1.5 V.

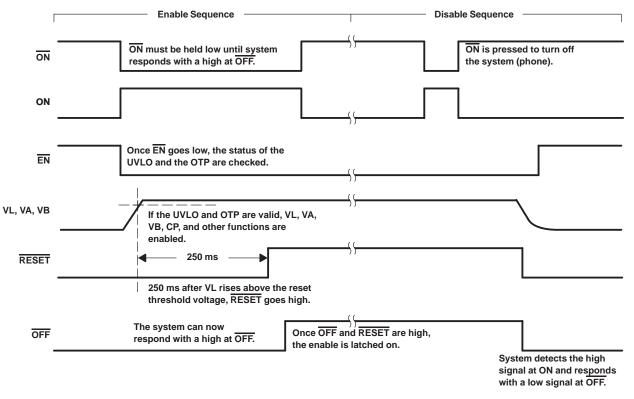

#### ON, OFF, ON, ON\_REM and EN functions

The  $\overline{ON}$  input is intended to be the main enable for the TPS9110 and should be connected to ground through a pushbutton switch. Once the switch is pressed, internal logic pulls  $\overline{EN}$  low.  $\overline{EN}$  is designed to sink 3.2 mA and can be used as a pulldown to enable other functions on the TPS9110 or other system circuitry. When  $\overline{EN}$  is pulled low, the TPS9110 checks to make sure the supply voltage is above the undervoltage lockout (UVLO) threshold voltage and the die temperature is below 160°C. If both of these conditions are met, the reference circuitry, regulator L, reset generator, and other support circuitry are enabled. When  $\overline{EEET}$  goes high, the system can respond with a logic high on  $\overline{OFF}$ , which latches the TPS9110 on, and the  $\overline{ON}$  pushbutton can then be released.

The TPS9110 is disabled in a similar manner. If the  $\overline{ON}$  pushbutton is pressed while the TPS9110 is enabled, ON responds with a logic high. Once this logic high is detected, the system can respond with a logic low on  $\overline{OFF}$ , disabling the TPS9110 and reducing supply currents to 1  $\mu$ A (see Figure 1).

# ON, OFF, ON, ON\_REM and EN functions (continued)

ON\_REM can be used in the same manner as  $\overline{ON}$  in enabling or disabling the TPS9110. The signal is provided as a system interface to increase the flexibility of the system. EN can also be used as an input wired-OR open collector/drain to enable the TPS9110; however, it does not produce a logic signal on ON and, therefore, cannot be used in the disable sequence described above. It is not recommended that EN be used as the primary enable signal for the TPS9110.

Figure 1. Recommended Enable and Disable Sequence

# undervoltage lockout (UVLO)

UVLO prevents operation of the functions in the TPS9110 until the supply voltage exceeds the threshold voltage, eliminating abnormal power-up conditions internally and externally, and providing an orderly turn-on.

# overtemperature shutdown

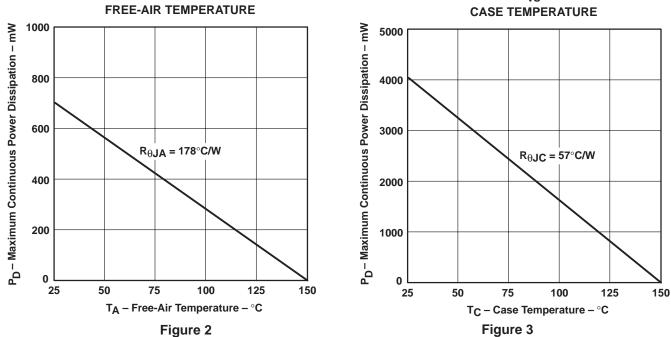

When the die temperature exceeds 160°C, the thermal protection circuit shuts off the TPS9110. When the die temperature drops below 150°C, the device can be restarted with the ON input.

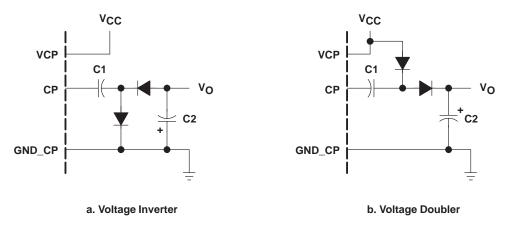

# charge pump driver

An unregulated inverting or doubler charge pump is implemented by connecting a network of two capacitors and two diodes to CP (see Figure 26). In the inverting configuration, the charge pump can power a liquid-crystal display (LCD) or provide gate bias for a GaAs power amplifier. A 5-V supply for flash-memory programming or powering the subscriber identity module (SIM) European applications can be achieved using the doubler configuration and an external LDO. A logic-low input to the charge-pump enable, EN\_CP, turns on the oscillator and driver; a logic high turns them off. The charge pump driver can be turned on as soon as UVLO and OTP are valid and  $\overline{ON}$  is toggled low.  $\overline{EN_CP}$  has an 10-µA internal pullup.

| $\mathbf{\tilde{\mathbf{v}}}$ |     |      | •   | - | -  |    |   |     |   |

|-------------------------------|-----|------|-----|---|----|----|---|-----|---|

| SL                            | VS1 | 64 - | - A | U | Gι | JS | Τ | 199 | 7 |

| DISSIPATION RATING TABLE 1 – Free-Air Temperature |                                                                                                                                                                                                          |           |                                       |        |  |  |  |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|--------|--|--|--|

| PACKAGE                                           | $\label{eq:tau} \begin{array}{ll} T_{A} \leq 25^{\circ} C & \mbox{DERATING FACTOR} & T_{A} = 70^{\circ} C \\ \mbox{POWER RATING} & \mbox{ABOVE } T_{A} = 25^{\circ} C & \mbox{POWER RATING} \end{array}$ |           | T <sub>A</sub> = 85°C<br>POWER RATING |        |  |  |  |

| PW                                                | 700 mW                                                                                                                                                                                                   | 5.6 mW/°C | 448 mW                                | 364 mW |  |  |  |

| DISSIPATION RATING TABLE 2 – Case Temperature |                                       |                                                |                                       |                                       |  |  |  |

|-----------------------------------------------|---------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|--|--|--|

| PACKAGE                                       | T <sub>C</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>C</sub> = 25°C | T <sub>C</sub> = 70°C<br>POWER RATING | T <sub>C</sub> = 85°C<br>POWER RATING |  |  |  |

| PW                                            | 4025 mW                               | 32.2 mW/°C                                     | 2576 mW                               | 2093 mW                               |  |  |  |

# MAXIMUM CONTINUOUS POWER DISSIPATION

# MAXIMUM CONTINUOUS POWER DISSIPATION

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†‡</sup>

| Supply voltage range, V <sub>CC</sub> , VCP                          | 0.3 V to 12 V                                       |

|----------------------------------------------------------------------|-----------------------------------------------------|

| Input voltage range at OFF                                           | $\dots \dots \dots \dots \dots -0.3$ V to 7 V       |

| Input voltage range at PL, PA, PB, EN, EN_A, EN_B, ON, ON_REM, EN_CP | $\dots \dots \dots \dots -0.3$ V to V <sub>CC</sub> |

| Continuous total power dissipation                                   | See Dissipation Rating Tables                       |

| Peak output current                                                  | Internally limited                                  |

| Operating free-air temperature range, T <sub>A</sub>                 | 40°C to 85°C                                        |

| Storage temperature range, T <sub>stg</sub>                          | 65°C to 150°C                                       |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds         |                                                     |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

‡ All voltages are with respect to GND.

SLVS164 - AUGUST 1997

### recommended operating conditions

|                                                                | MIN | MAX | UNIT |

|----------------------------------------------------------------|-----|-----|------|

| Supply voltage, V <sub>CC</sub> , VCP                          | 3   | 10  | V    |

| Input voltage, OFF                                             | 0   | 5   | V    |

| Input voltage at PL, PA, PB, EN, EN_A, EN_B, ON, ON_REM, EN_CP | 0   | VCC | V    |

| Reference output current                                       | 0   | 2   | mA   |

| Continuous regulator output current                            | 0   | 100 | mA   |

| Operating free-air temperature                                 | -40 | 85  | °C   |

electrical characteristics over recommended operating free-air temperature range,  $V_{CC} = VCP = 4 V$ , Px = 0 V,  $I_{O(Vx)} = 35 mA$ ,  $\overline{OFF} = VL$ ,  $\overline{ON}$  open,  $ON_REM = 0 V$ ,  $Cx = 10 \mu F$  (unless otherwise noted)

#### voltage reference (REF)

| PARAMETER      | TEST CONDITIONS <sup>†</sup>                        |                                | MIN   | TYP MAX | UNIT |

|----------------|-----------------------------------------------------|--------------------------------|-------|---------|------|

| Output voltage | T <sub>A</sub> = 25°C,                              | I <sup>O</sup> = 0             |       | 1.185   | V    |

| Output voltage | $4 \text{ V} \leq \text{V}_{CC} \leq 10 \text{ V},$ | $0 \le I_{O} \le 2 \text{ mA}$ | 1.161 | 1.209   | V    |

† Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effect must be taken into account separately.

#### LDO regulators

| PARAMETER                          | TEST CONDITION                                                                                  | ist                             | MIN  | TYP | MAX  | UNIT |

|------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------|------|-----|------|------|

|                                    | $T_A = 25^{\circ}C$                                                                             |                                 | 3.25 | 3.3 | 3.35 | V    |

|                                    | $0 \le I_{O(Vx)} \le 100 \text{ mA},  3.5 \text{ V} \le 100 \text{ mA}$                         | $\leq V_{CC} \leq 10 \text{ V}$ | 3.2  |     | 3.4  | V    |

| Output voltage at VA, VB, VL (Vx)  | $Px = V_{CC}, 	 T_A = 25$                                                                       | 5°C                             | 2.95 | 3   | 3.05 | V    |

| ropout voltage                     | $ \begin{array}{l} Px = V_{CC,} & 0 \leq I_{O}(\\ 3.2 \ V \leq V_{CC} \leq 10 \ V \end{array} $ | Vx) ≤ 100 mA,                   | 2.9  |     | 3.10 | V    |

| Dropout voltage                    | $I_{O(Vx)} = 100 \text{ mA},  V_{CC} =$                                                         | 3.2 V                           |      | 100 | 200  | mV   |

| Load regulation                    | $I_{O(Vx)} = 0$ mA to 100 mA                                                                    |                                 |      | 30  |      | mV   |

| Line regulation                    | $I_{O(Vx)} = 100 \text{ mA},  V_{CC} =$                                                         | 3.5 V to 10 V                   |      | 10  |      | mV   |

| Ripple rejection                   | f = 120 Hz                                                                                      |                                 |      | 60  |      | dB   |

| Quiescent current (each regulator) |                                                                                                 |                                 |      | 100 |      | μΑ   |

† Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effect must be taken into account separately.

#### charge pump driver

| PARAMETER         | MIN | TYP | MAX | UNIT |

|-------------------|-----|-----|-----|------|

| Frequency         | 50  | 100 | 150 | kHz  |

| Duty cycle        |     | 50% |     |      |

| Output resistance |     | 15  | 30  | Ω    |

SLVS164 - AUGUST 1997

#### RESET

| PARAMETER                 | TEST COND                                                                                                                   | ITIONS <sup>†</sup>     | MIN   | TYP  | MAX   | UNIT |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|-------|------|-------|------|

| Input threshold voltage   | VL voltage decreasin                                                                                                        | g                       | 2.871 | 2.93 | 2.989 | V    |

| Input threshold voltage   | VL voltage decreasin                                                                                                        | g, PL = V <sub>CC</sub> | 2.548 | 2.6  | 2.652 | V    |

| Timeout delay at RESET    | See Figure 5                                                                                                                |                         | 125   | 250  | 375   | ms   |

| High-level output voltage | I <sub>O</sub> = -40 μA                                                                                                     |                         | 2.4   |      |       | V    |

|                           | I <sub>O</sub> = 1 mA,                                                                                                      | V <sub>CC</sub> = 1.5 V |       |      | 0.4   | V    |

| Low-level output voltage  | VL voltage decreasing, PL = V <sub>CC</sub> 2.548 2.6 2.652   See Figure 5 125 250 375 $I_O = -40 \ \mu A$ 2.4 10 1.5 V 0.4 | 0.4                     |       |      |       |      |

| Hysteresis                |                                                                                                                             |                         |       | 40   |       | mV   |

<sup>†</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effect must be taken into account separately.

#### logic inputs at EN\_A, EN\_B

| PARAMETER                | MIN | TYP | MAX | UNIT |

|--------------------------|-----|-----|-----|------|

| High-level input voltage | 2   |     |     | V    |

| Low-level input voltage  |     |     | 0.8 | V    |

| Input current            | -20 | -10 | 1   | μΑ   |

# logic inputs at PL, PA, PB, OFF, ON\_REM

| PARAMETER                | MIN | MAX | UNIT |

|--------------------------|-----|-----|------|

| High-level input voltage | 2   |     | V    |

| Low-level input voltage  |     | 0.8 | V    |

| Input current            | -1  | 1   | μΑ   |

# logic inputs at ON‡

| PARAMETER                | MIN | MAX | UNIT |

|--------------------------|-----|-----|------|

| High-level input voltage | 2   |     | V    |

| Low-level input voltage  |     | 0.8 | V    |

| Input current            | -20 | 1   | μΑ   |

<sup>‡</sup> High and low level voltages are dependent on V<sub>CC</sub> (see Figure 17).

# logic inputs at EN<sup>‡</sup>

| PARAMETER                 | TEST CONDITIONS                              | MIN | MAX | UNIT |

|---------------------------|----------------------------------------------|-----|-----|------|

| High-level input voltage  |                                              | 2.4 |     | V    |

| Low-level input voltage   |                                              |     | 0.8 | V    |

| High-level output voltage | $I_{O} = -50 \ \mu A$ OFF = 0                | 2.4 |     | V    |

| Low-level output voltage  | $I_{O} = 3.2 \text{ mA},  \overline{ON} = 0$ |     | 0.4 | V    |

<sup> $\ddagger$ </sup> High and low-level input voltages are dependent on V<sub>CC</sub> (see Figure 18).

#### logic outputs at ON

| PARAMETER                 | TEST CONDITIONS     | MIN | MAX | UNIT |

|---------------------------|---------------------|-----|-----|------|

| High-level output voltage | 1-mA source current | 2.4 |     | V    |

| Low-level output voltage  | 1-mA sink current   |     | 0.4 | V    |

#### overtemperature shutdown

| PARAMETER              | MIN | TYP | MAX | UNIT |

|------------------------|-----|-----|-----|------|

| Temperature threshold  |     | 160 |     | °C   |

| Temperature hysteresis |     | 10  |     | °C   |

SLVS164 – AUGUST 1997

#### undervoltage lockout (UVLO)

| PARAMETER         | TEST CONDITIONS            | MIN  | TYP | MAX  | UNIT |

|-------------------|----------------------------|------|-----|------|------|

| Threshold voltage | V <sub>CC</sub> increasing | 1.80 |     | 2.52 | V    |

| Hysteresis        |                            |      | 50  |      | mV   |

#### supply current

| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------|-----------------|-----|-----|-----|------|

| Shutdown  | OFF = 0 V       |     | 0.5 | 10  | μΑ   |

| Operating | EN_CP = VCP     |     | 0.7 | 1   | mA   |

# <u>TPS9110Y</u> electrical characteristics, $T_J = 25^{\circ}C$ , $V_{CC} = VCP = 4 V$ , Px = 0 V, $I_{O(Vx)} = 35 \text{ mA}$ , $\overline{OFF} = VL$ , ON open, ON\_REM = 0 V, $Cx = 10 \ \mu\text{F}$ (unless otherwise noted)

#### voltage reference (REF)

| PARAMETER      | TEST CONDITIONS <sup>†</sup> | MIN TYP | MAX | UNIT |

|----------------|------------------------------|---------|-----|------|

| Output voltage | I <sub>O</sub> = 0           | 1.185   |     | V    |

<sup>†</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; the thermal effect must be taken into account separately.

#### LDO regulators

| PARAMETER                          | TEST CONDITIONS <sup>†</sup>                                          | MIN  | TYP | MAX  | UNIT |

|------------------------------------|-----------------------------------------------------------------------|------|-----|------|------|

| Output voltage at VA, VB, VL (Vx)  | $P_X = V_{CC}$                                                        | 2.95 | 3   | 3.05 | V    |

| Dropout voltage                    | $I_{O(Vx)} = 100 \text{ mA}, V_{CC} = 3.2 \text{ V}$                  |      | 100 |      | mV   |

| Load regulation                    | $I_{O(Vx)} = 0$ mA to 100 mA                                          |      | 30  |      | mV   |

| Line regulation                    | $I_{O(Vx)} = 100 \text{ mA}, V_{CC} = 3.5 \text{ V to } 10 \text{ V}$ |      | 10  |      | mV   |

| Ripple rejection                   | f = 120 Hz                                                            |      | 60  |      | dB   |

| Quiescent current (each regulator) |                                                                       |      | 100 |      | μΑ   |

<sup>†</sup> Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effect must be taken into account separately.

#### charge-pump driver

| PARAMETER         | MIN | TYP | MAX | UNIT |

|-------------------|-----|-----|-----|------|

| Frequency         |     | 100 |     | kHz  |

| Duty cycle        |     | 50% |     |      |

| Output resistance |     | 15  |     | Ω    |

#### RESET

| PARAMETER         | TEST CONDITIONS <sup>†</sup>         | MIN | TYP  | MAX | UNIT |

|-------------------|--------------------------------------|-----|------|-----|------|

| Threshold voltage | VL voltage decreasing                |     | 2.93 |     | V    |

| Theshold voltage  | VL voltage decreasing, $PL = V_{CC}$ |     | 2.6  |     | v    |

| Delay             | See Figure 5                         |     | 250  |     | ms   |

| Hysteresis        |                                      |     | 40   |     | mV   |

† Pulse-testing techniques are used to maintain virtual junction temperature as close as possible to ambient temperature; thermal effect must be taken into account separately.

Figure 4. Test Circuit

# PARAMETER MEASUREMENT INFORMATION

Figure 5. RESET Timing Diagram

Figure 6. LDO-Regulator Output-Voltage Rise Time and Fall Time

# PARAMETER MEASUREMENT INFORMATION

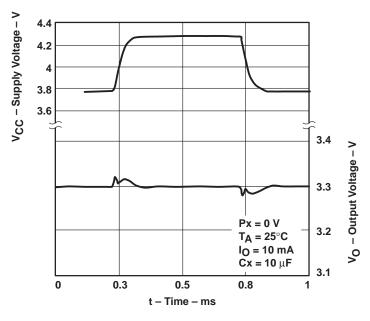

Figure 7. LDO-Regulator Load Transient, 1 mA to 100 mA Pulsed Load

Figure 8. LDO-Regulator Line Transient

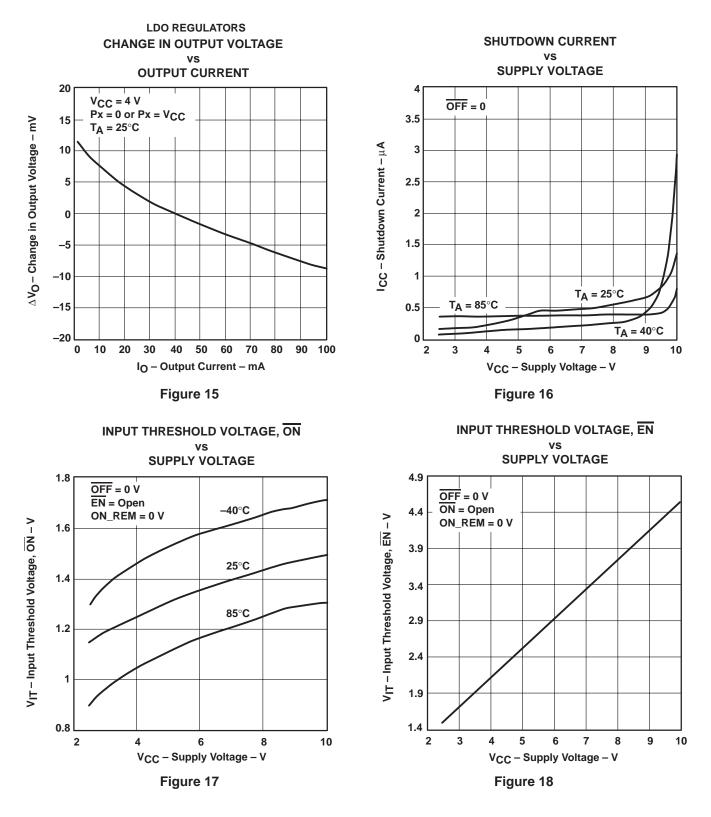

# TYPICAL CHARACTERISTICS

|     |                                 |                         | FIGURE |

|-----|---------------------------------|-------------------------|--------|

| ICC | Quiescent current               | vs Supply voltage       | 9      |

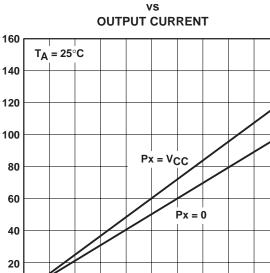

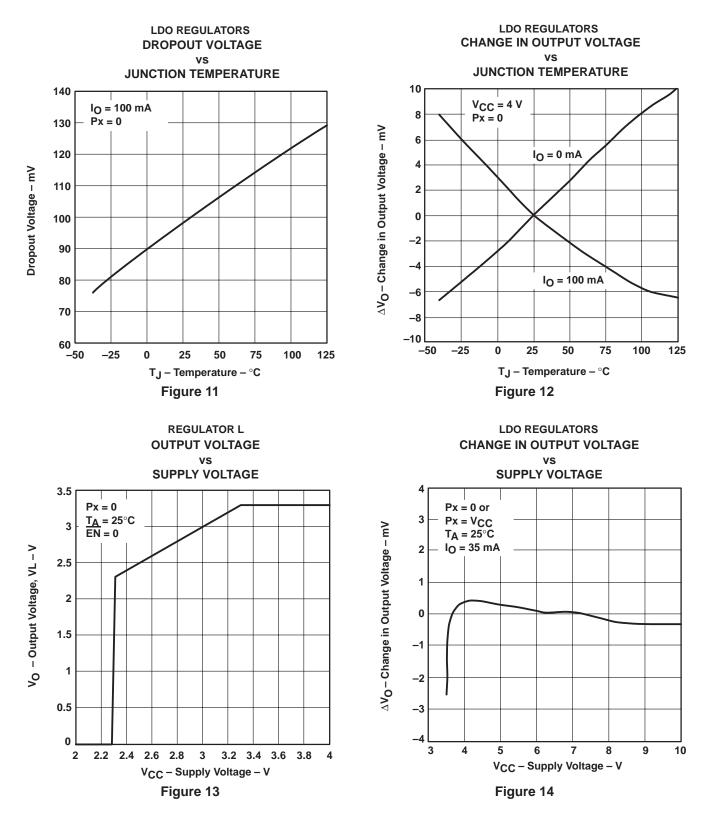

|     | Dropoutvoltago                  | vs Output current       | 10     |

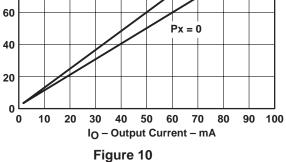

|     | Dropout voltage                 | vs Junction temperature | 11     |

| ΔVO | Change in output voltage        | vs Junction temperature | 12     |

| Vo  | Output voltage, VL              | vs Supply voltage       | 13     |

| ΔVO | Change in output voltage        | vs Supply voltage       | 14     |

| ΔVO | Change in output voltage        | vs Output current       | 15     |

| lcc | Shutdown current                | vs Supply voltage       | 16     |

|     | Input threshold voltage, ON     | vs Supply voltage       | 17     |

|     | Input threshold voltage, EN     | vs Supply voltage       | 18     |

|     | Input threshold voltage, ON_REM | vs Supply voltage       | 19     |

|     | Ripple rejection                | vs Frequency            | 20     |

|     | Output spectral noise density   | vs Frequency            | 21     |

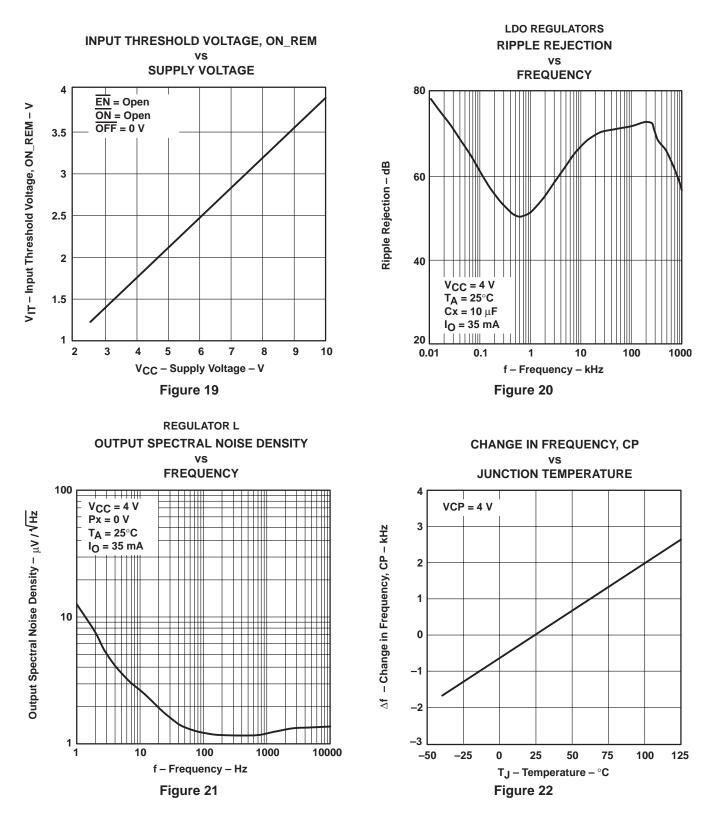

|     | Change in frequency, CP         | vs Junction temperature | 22     |

| rO  | Output resistance into CP       | vs Supply voltage       | 23     |

| rO  | Output resistance out of CP     | vs Supply voltage       | 24     |

Dropout Voltage – mV

# **Table of Graphs**

# QUIESCENT CURRENT VS SUPPLY VOLTAGE $P_{X} = 0$ $I_{O} = 0$ 0.9 0.8 0.8 0.7 0.6 $-40^{\circ}C$ $25^{\circ}C$ 0.6

7

V<sub>CC</sub> – Supply Voltage – V

6

Figure 9

8

LDO REGULATORS DROPOUT VOLTAGE

10

9

I<sub>CC</sub>- Quiescent Current - mA

0.5

3

4

5

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

# **TYPICAL CHARACTERISTICS**

# TYPICAL CHARACTERISTICS

# THERMAL INFORMATION

Using thermal resistance, junction-to-ambient ( $R_{\theta JA}$ ), maximum power dissipation can be calculated with the equation:

$$P_{D(max)} = \frac{T_{J(max)} - T_{A}}{R_{\theta JA}}$$

Where  $T_{J(max)}$  is the maximum allowable junction temperature or 150°C.

This limit should then be applied to the internal power dissipation of the TPS9110. The equation for calculating total internal power dissipation of the TPS9110 is:

$$\mathsf{P}_{\mathsf{D}(\mathsf{max})} = \sum_{\mathsf{x}} (\mathsf{V}_{\mathsf{I}} - \mathsf{V}_{\mathsf{X}}) \times \mathsf{I}_{\mathsf{X}} + \mathsf{V}_{\mathsf{I}} \times \mathsf{I}_{\mathsf{Q}}$$

Many system-dependent issues such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power dissipation limits of a given component.

Three basic approaches for enhancing thermal performance are:

- Improving the power dissipation capability of the PWB design

- Improving the thermal coupling of the component to the PWB

- Introducing airflow in the system

#### **APPLICATION INFORMATION**

Figure 25. Typical Application

# LDOs (VL, VA, VB) output capacitors

A 10- $\mu$ F capacitor must be tied to Cx (CL, CA, or CB). The Cx terminal is connected internally to the output of the LDO through a 1- $\Omega$  resistor. The stability of LDOs is dependent on the ESR of the output filter capacitor. Most LDOs are designed to be stable over a narrow range of ESR with lower limits and upper limits, thus limiting the type of capacitor that can be used. With the use of the internal 1- $\Omega$  resistor, the lower ESR limit of the capacitor is eliminated, permitting the upper limit to be raised. Therefore, almost any tantalum or ceramic capacitor can be used, provided the ESR does not exceed 15  $\Omega$  over operating temperature range.

**APPLICATION INFORMATION**

# charge pump design

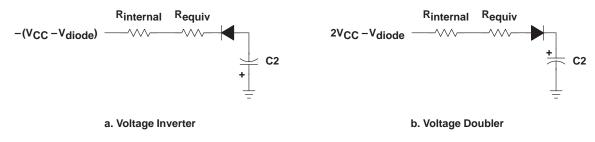

Figure 26. Charge-Pump Configurations

The charge-pump terminal can drive either a voltage inverter or a voltage doubler. In either case only two capacitors and two signal diodes are needed. The output voltage is unregulated and a regulator may be added if needed.

The charge transfer of C1 is:

$\Delta q = C1 \times (VCC - VO)$

This occurs f times a second and the charge transfer per unit time (current) is:

$I = f \times C1 \times (V_{CC} - V_{O})$

Rewriting this equation in the form of I = V/R gives:

$$I = \frac{V_{CC} - V_{O}}{\frac{1}{f \times C1}}$$

where  $\frac{1}{f \times C1}$  is an equivalent resistor.

An equivalent circuit can now be drawn taking the diodes into account.

# **APPLICATION INFORMATION**

### charge-pump design (continued)

The output voltage for the doubler is then:

$V_{O} = 2 \times V_{CC} - 2 \times V_{diode} - I_{O} \times R_{total}$

and the output voltage for the inverter is:

$$V_{O} = -(V_{CC} - 2 \times V_{diode}) + I_{O} \times R_{total}$$

To determine the size of C1 use:

$$C = \frac{I}{f \times \Delta V}$$

where f = 100,000 and  $\Delta V$  = ripple voltage.

For an output current of 10 mA calculate:

$$C1 = \frac{0.01 \text{ A}}{100 \text{ kHz} \times 0.1 \text{ V}_{ripple}} = 1 \mu F$$

Because of losses caused by diode switching and ESR, the calculated capacitance should be multiplied by 1.5 to 2. A  $2-\mu$ F capacitance should drive a 10-mA voltage doubler or inverter.

SEV3104 - A06031 1997

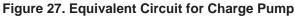

**MECHANICAL DATA**

# PW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated