# High-Efficiency Transmit Controller for Wireless Power Systems

#### POWER MANAGEMENT

#### **Features**

- Supports portable wireless charging applications

- Wireless power systems up to 5W

- Integrated controller and FLASH for communications and control

- · High precision data converter

- Low external component count

- Product is lead-free, Halogen Free, RoHS / WEEE compliant

### **Applications**

- Low-power wireless chargers for:

- Smart Watches

- Wearables

- Toys

- Portable Lighting

- o Medical Devices

# **Description**

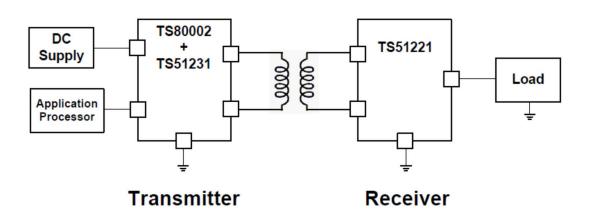

The TS80002 is a power transmitter communications and control unit for wireless charging applications. The TS80002 can support systems up to 5W and proprietary applications.

The TS80002 performs the necessary coding of protocol to send commands to the transmitter to adjust the power level accordingly.

### **Specifications**

- RISC-based controller core with flash and SRAM memory

- 10-bit A/D converter

- Two 16-bit timers, advanced control and general purpose

- 8-bit timer

- Auto-wakeup and watchdog timers

- 4 configurable general purpose IOs

- I2C interface

- 20 pin 3x3 QFN

# **Typical Application Circuit-**

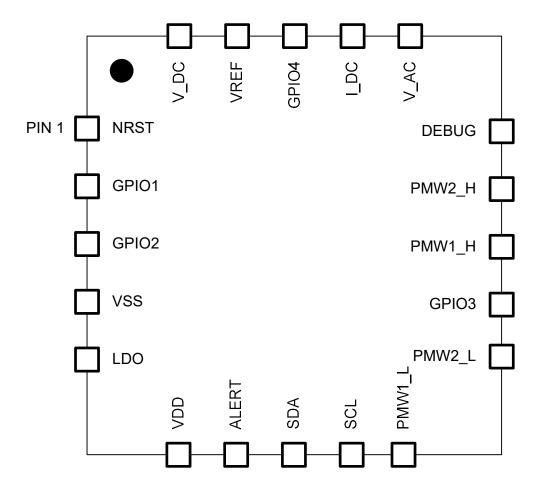

# Pinout (Top View)

# **Pin Description**

| QFN Pin # | Pin Symbol | Function         | Description                   |

|-----------|------------|------------------|-------------------------------|

| 1         | NRST       | Reset            | Reset input                   |

| 2         | GPIO1      | GPIO             | GPIO 1                        |

| 3         | GPIO2      | GPIO             | GPIO 2                        |

| 4         | VSS        | Power GND        | Power GND                     |

| 5         | LDO        | Filter           | Internal LDO filter capacitor |

| 6         | VDD        | Input power      | Input power supply            |

| 7         | ALERT      | I2C Alert        | I2C Alert signal              |

| 8         | SDA        | I2C Serial Data  | I2C Serial Data               |

| 9         | SCL        | I2C Serial Clock | I2C Serial Clock              |

| 10        | PWM1_L     | PWM output       | PWM1 low-side control         |

| 11        | PWM2_L     | PWM output       | PWM2 low-side control         |

| 12        | GPIO3      | GPIO             | GPIO 3                        |

| 13        | PWM1_H     | PWM              | PWM1 high-side control        |

| 14        | PWM2_H     | PWM              | PWM2 high-side control        |

| 15        | DEBUG      | Debug            | Debug interface               |

| 16        | V_AC       | Analog GPIO      | AC voltage measurement        |

| 17        | I_DC       | Analog GPIO      | DC current measurement        |

| 18        | GPIO4      | GPIO             | GPIO 4                        |

| 19        | VREF       | Analog GPIO      | Voltage reference input       |

| 20        | V_DC       | Analog GPIO      | DC voltage measurement        |

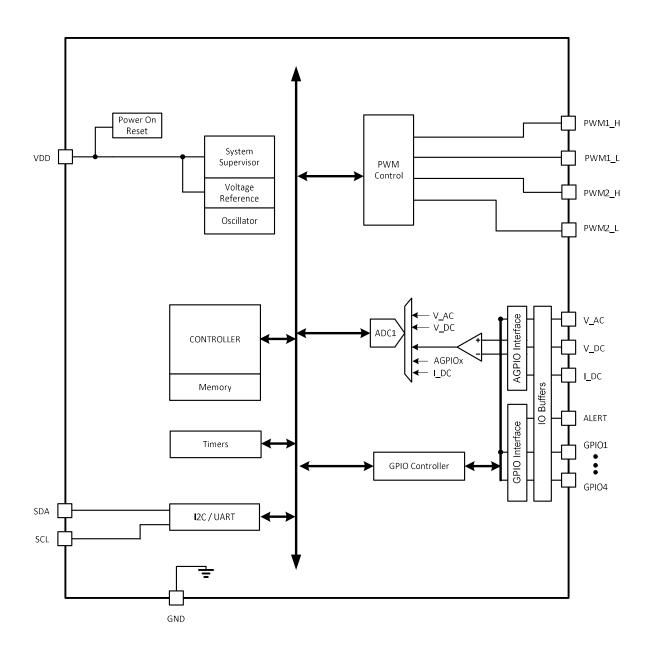

# **Functional Block Diagram**

# **Absolute Maximum Ratings**

Over operating free-air temperature range unless otherwise noted (1, 2, 3)

| Parameter                                                                                                            | Min       | Max       | Unit |

|----------------------------------------------------------------------------------------------------------------------|-----------|-----------|------|

| VDD, VSS                                                                                                             | -0.3      | 6.5       | V    |

| GPIO1, GPIO2, VSS, VDD, ALERT, SDA, SCL, PWM1_L, PWM2_L, GPIO3, PWM1_H, PWM2_H, DEBUG, V_AC, I_DC, GPIO4, VREF, V_DC | VSS - 0.3 | 6.5       | V    |

| NRST, LDO                                                                                                            | VSS - 0.3 | VDD + 0.3 | V    |

| Operating Junction Temperature Range, T <sub>J</sub>                                                                 | -40       | 125       | °C   |

| Storage Temperature Range, T <sub>STG</sub>                                                                          | -65       | 150       | °C   |

| Electrostatic Discharge – Human Body Model                                                                           |           | ±2k       | V    |

| IR reflow temperature (soldering, 10 seconds)                                                                        |           | 260       | °C   |

#### Notes:

- (1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximumrated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to network ground terminal.

- (3) ESD testing is performed according to the respective JESD22 JEDEC standard.

# **Recommended Operating Conditions**

| Symbol           | Parameter                      | Min  | Тур | Max | Unit |

|------------------|--------------------------------|------|-----|-----|------|

| VDD              | Input Operating Voltage        | 2.95 |     | 5.5 | V    |

| F <sub>MCU</sub> | Operating Frequency            | 0    |     | 16  | MHz  |

| VDD              | Decoupling capacitor value     |      | 1   |     | uF   |

| LDO              | Decoupling capacitor value     |      | 1   |     | uF   |

| TA               | Operating Free Air Temperature | -40  |     | 85  | °C   |

| TJ               | Operating Junction Temperature | -40  |     | 105 | °C   |

#### **Communication Interfaces**

The Applications Processor can interrogate the TS80002 using the I2C interface. The TS80002 acknowledges its I2C Slave Address only if it is powered. No ACK from the TS80002 after its slave address means that power is not applied to the TS80002.

#### I<sub>2</sub>C

#### **I2C Signal Pins**

ALERT pin (GPIO pin) - optional:

- Driven high when an event is active in the internal STATUS register

- Driven low when all the internal events are cleared

Note: The ALERT pin is provided to help with I2C communication, i.e. to signal events to the EC so the EC can interrogate the TS80002 via I2C. The use of the ALERT pin is not mandatory in the application.

#### SCL pin:

- Clock pin for the I2C interface.

- True open-drain. Needs external pull-ups.

#### SDA pin:

- Data pin for the I2C interface.

- True open-drain. Needs external pull-ups.

#### **I2C Protocol**

The TS80002 Wireless Power Receiver acts as an I2C slave peripheral to allow communication with an application microcontroller. The slave address (7 bit) is 0x49. The Embedded Controller is an I2C master and initiates every data transfer.

The TS80002 implements a set of registers available from the I2C bus. It also implements a set of API functions that receive parameters and return values using the I2C bus. Four transfer types are possible:

- Write Register

- Read Register

- Run API Function

- Read API Function Return Buffer

#### Write Register Operations

#### **Description**

| START |                                    | Start of the I2C transfer. |                                           |  |  |

|-------|------------------------------------|----------------------------|-------------------------------------------|--|--|

| M→S   | Slave Address (7 bits) 0 (1 bit)   | Slave ACK                  | Slave address + R/W bit (0x92 as 8-bit).  |  |  |

| M→S   | Register <i>n</i> address (8 bits) | Slave ACK                  | Address of the first register.            |  |  |

| M→S   | Register <i>n</i> Data (8 bits)    | Slave ACK                  | Write the first register.                 |  |  |

| M→S   | Register n+1 Data (8 bits)         | Slave ACK                  | Optionally write the following registers. |  |  |

|       |                                    |                            |                                           |  |  |

| M→S   | Register n+k Data (8 bits)         | Slave ACK                  |                                           |  |  |

| STOP  |                                    |                            | Stop of the I2C transfer.                 |  |  |

**Read Register Operations**

**Description**

| START |                                    | Start of the I2C transfer. |                                               |  |  |

|-------|------------------------------------|----------------------------|-----------------------------------------------|--|--|

| M→S   | Slave Address (7 bits) 0 (1 bit)   | Slave ACK                  | Slave address + 0 as R/W bit (0x92 as 8-bit). |  |  |

| M→S   | Register <i>n</i> address (8 bits) | Slave ACK                  | Address of the first register.                |  |  |

| START |                                    |                            | Repeated Start.                               |  |  |

| M→S   | Slave Address (7 bits) 1 (1 bit)   | Slave ACK                  | Slave address + 1 as R/W bit (0x93 as 8-bit). |  |  |

| S→M   | Register <i>n</i> Data (8 bits)    | Master ACK                 | Read the first register.                      |  |  |

| S→M   | Register n+1 Data (8 bits)         | Master ACK                 | Optionally read the following registers.      |  |  |

|       |                                    |                            |                                               |  |  |

| S→M   | Register n+k Data (8 bits)         | Master                     | The master should send a nACK after the last  |  |  |

|       | nACK                               |                            | data byte was received.                       |  |  |

| STOP  |                                    | Stop of the I2C transfer   |                                               |  |  |

# Run API Function Description

| Start |                                          |           |           | Start of the I2C transfer.                      |  |  |

|-------|------------------------------------------|-----------|-----------|-------------------------------------------------|--|--|

| M→S   | Slave Address (7 bits)                   | 0 (1 bit) | Slave ACK | Slave address + R/W bit (0x92 as 8-bit).        |  |  |

| M→S   | API number (8 bits)                      |           | Slave ACK | API number.                                     |  |  |

| M→S   | API input buffer length m (              | 8 bits)   | Slave ACK | API input buffer length. Equal to 0 if no input |  |  |

|       |                                          |           |           | buffer data is required by the API.             |  |  |

| M→S   | Input buffer data[0] (8 bits)            | )         | Slave ACK | First byte of the input buffer (optional).      |  |  |

| M→S   | Input buffer data[1] (8 bits)            |           | Slave ACK | Second byte of the input buffer (optional).     |  |  |

|       |                                          |           |           |                                                 |  |  |

| M→S   | Input buffer data[m-1] (8 bits) Slave AC |           |           | Last byte of the input buffer (optional).       |  |  |

| Stop  |                                          |           |           | Stop of the I2C transfer and execute the API    |  |  |

|       |                                          |           |           | function.                                       |  |  |

### **Read API Function Return Buffer**

# **Description**

| START |                                  | Start of the I2C transfer. |                |                                                                      |  |  |

|-------|----------------------------------|----------------------------|----------------|----------------------------------------------------------------------|--|--|

| M→S   | Slave Address (7 bits)           | 0 (1 bit)                  | Slave ACK      | Slave address + 0 as R/W bit (0x92 as 8-bit).                        |  |  |

| M→S   | API number (8 bits)              |                            | Slave ACK      | API number.                                                          |  |  |

| START |                                  |                            |                | Repeated Start.                                                      |  |  |

| M→S   | Slave Address (7 bits) 1 (1 bit) |                            | Slave ACK      | Slave address + 1 as R/nW bit (0x93 as 8-bit).                       |  |  |

| S→M   | API number (8 bits)              |                            | Master ACK     | API number for the following return buffer.                          |  |  |

| S→M   | API return buffer length n       | (8 bits)                   | Master ACK     | API return buffer length.                                            |  |  |

| S→M   | Output buffer data[0] (8 bi      | its)                       | Master ACK     | Read the first byte in the output buffer.                            |  |  |

| S→M   | Output buffer data[1] (8 bi      | its)                       | Master ACK     | Optionally read the following bytes.                                 |  |  |

|       |                                  |                            |                |                                                                      |  |  |

| S→M   | Output buffer data[n-1] (8 bits) |                            | Master<br>nACK | The master should send a nACK after the last data byte was received. |  |  |

| STOP  | STOP                             |                            |                | Stop of the I2C transfer                                             |  |  |

# **Internal Registers**

| Address   | Name              | Туре             | Description                                |

|-----------|-------------------|------------------|--------------------------------------------|

| 0x00      | BOOTFW_REV_L      | R/W              | Bootloader Firmware Revision Low Register  |

| 0x01      | BOOTFW_REV_H      | R/W              | Bootloader Firmware Revision High Register |

| 0x02      | FW_REV_L          | R/W              | Firmware Revision Low Register             |

| 0x03      | FW_REV_H          | R/W              | Firmware Revision High Register            |

| 0x04      | MODE_L            | R/W              | Operating Mode Low Register                |

| 0x05      | MODE_H            | R/W              | Operating Mode High Register               |

| 0x06      | RESET_L           | R/W              | Reset Low Register                         |

| 0x07      | RESET_H           | R/W              | Reset High Register                        |

| 0x08      | STATUS            | R                | Main Status Register                       |

| 0x09      | STATUS0           | R                | Status0 Register                           |

| 0x0A      | STATUS1           | R                | Status1 Register                           |

| 0x0B      | STATUS2           | R                | Status2 Register                           |

| 0x0C      | STATUS3           | R                | Status3 Register                           |

| 0x0D-0x7F | RESERVED. Will be | e defined later. |                                            |

#### Bootloader Firmware Revision Low Register (BOOTFW\_REV\_L)

Address: 0x00

Reset value: Minor version number of the bootloader firmware

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|---|---|---|---|---|---|---|--|

| REV_L[7:0] |   |   |   |   |   |   |   |  |

| r          | r | r | r | r | r | r | r |  |

Bits 7:0 REV\_L[7:0]: Bootloader Firmware Revision Low

These bits contain the minor version number of the bootloader firmware.

#### Bootloader Firmware Revision High Register (BOOTFW\_REV\_H)

Address: 0x01

Reset value: Major version number of the bootloader firmware

| 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---|------------|---|---|---|---|---|---|--|--|

|   | REV_H[7:0] |   |   |   |   |   |   |  |  |

| r | r          | r | r | r | r | r | r |  |  |

#### Bits 7:0 **REV\_H[7:0]**: Bootloader Firmware Revision High

These bits contain the major version number of the bootloader firmware.

### Firmware Revision Low Register (FW\_REV\_L)

Address: 0x02

Reset value: Minor version number of the user firmware

| 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---|------------|---|---|---|---|---|---|--|--|

|   | REV_L[7:0] |   |   |   |   |   |   |  |  |

| r | r          | r | r | r | r | r | r |  |  |

Bits 7:0 REV\_L[7:0]: Firmware Revision Low

These bits contain the minor version number of the user firmware.

#### Firmware Revision High Register (BOOTFW\_REV\_H)

Address: 0x03

Reset value:

Major version number of the user firmware

7

6

5

4

3

2

1

0

REV\_H[7:0]

r

r

r

r

r

r

r

Bits 7:0 **REV\_H[7:0]**: Bootloader Firmware Revision High

These bits contain the major version number of the user firmware.

#### Operating Mode Low Register (MODE\_L)

Address: 0x04

Reset value: Depends on the bootloader mode and the firmware type

7 6 5 4 3 2 1 0

Res BOOTLDR

r

Bits 7:1 Reserved

Bit 0 BOOTLDR: Bootloader mode

0: The user firmware is running

1: The controller is in bootloader mode

#### **Operating Mode High Register (MODE H)**

Address: 0x05

Reset value: Depends on the bootloader mode and the firmware type

7 6 5 4 3 2 1 0 Res

Bits 7:0 Reserved

#### Reset Low Register (RESET\_L)

Address: 0x06 Reset value: 0x00

| 7 | 6                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---|------------------|---|---|---|---|---|---|--|--|

|   | RESET_KEY_L[7:0] |   |   |   |   |   |   |  |  |

| W |                  |   |   |   |   |   |   |  |  |

#### Bits 7:0 RESET\_KEY\_L[7:0]: Reset Key

0x55: generate a system reset. Both the RESET\_L and the RESET\_H registers have to be written with the correct key to generate a reset.

Any other value: a system reset is not generated.

#### Reset High Register (RESET\_H)

Address: 0x07 Reset value: 0x00

| 7 | 6                | 5 | 4 | 3 | 2 | 1 | 0 |

|---|------------------|---|---|---|---|---|---|

|   | RESET_KEY_H[7:0] |   |   |   |   |   |   |

| W | W                | W | W | W | W | W | W |

#### Bits 7:0 **RESET\_KEY\_H[7:0]**: Reset Key

0xAA: generate a system reset. Both the RESET\_L and the RESET\_H registers have to be written with the correct key to generate a reset.

Any other value: a system reset is not generated.

#### Main Status Register (STATUS)

Address: 0x08 Reset value: 0xC0

| 7   | 6       | 5 | 4   | 3       | 2       | 1       | 0       |

|-----|---------|---|-----|---------|---------|---------|---------|

| CTS | CTS_API | Б | 100 | STATUS3 | STATUS2 | STATUS1 | STATUS0 |

| rw  | rw      |   | les | rw      | rw      | rw      | rw      |

Bit 7 CTS: Clear To Send

This bit indicates if a new command can be issued to the controller.

0: The controller is busy processing a previous command. New commands should not be sent to the controller.

1: The controller can accept a new command over the communication interface.

Bit 6 CTS\_API: Clear to Send for API

This bit indicates if a new API call can be issued to the controller.

0: The controller is busy processing a previous API call. New API calls should not be sent to the controller.

1: The controller can accept a new API call over the communication interface.

Bits 5:4 Reserved

Bit 3 STATUS3: STATUS3 Event Flag

0: No event is signaled in the STATUS3 register

1: An event is signaled in the STATUS3 register

Bit 2 STATUS2: STATUS2 Event Flag

0: No event is signaled in the STATUS2 register

1: An event is signaled in the STATUS2 register

Bit 1 STATUS1: STATUS1 Event Flag

0: No event is signaled in the STATUS1 register

1: An event is signaled in the STATUS1 register

Bit 0 STATUS0: STATUS0 Event Flag

0: No event is signaled in the STATUS0 register

1: An event is signaled in the STATUS0 register

## **API Functions**

| API Number | API Name                         | Description                                          |

|------------|----------------------------------|------------------------------------------------------|

| 0x80       | BOOTLOADER_UNLOCK_FLASH          | Allow changes to the FLASH memory                    |

| 0x81       | BOOTLOADER_WRITE_BLOCK           | Write a page into the FLASH memory                   |

| 0x82       | BOOTLOADER_CRC_CHECK             | Check the CRC of the user firmware                   |

| 0x83-0xFE  | RESERVED. Will be defined later. |                                                      |

| 0xFF       | API_ERROR                        | Value returned in the API field when a Read API      |

|            |                                  | Function Return Buffer command is issued and the API |

|            |                                  | function called previously has generated an error.   |

# Bootloader Unlock Flash (BOOTLOADER\_UNLOCK\_FLASH)

API number: 0x80

Input buffer size: TBD

Output buffer size: 1

| Buffer                | Parameter  | Length<br>(bytes) | Description |

|-----------------------|------------|-------------------|-------------|

| Input buffer          | TBD        |                   |             |

| Return data<br>buffer | ERROR_CODE | 1                 |             |

## Bootloader Write Block (BOOTLOADER\_WRITE\_BLOCK)

API number: 0x81

Input buffer size: 66

Output buffer size: 1

| Buffer             | Parameter    | Length (bytes) | Description                                     |

|--------------------|--------------|----------------|-------------------------------------------------|

| Input buffer       | Block Number | 2              | Block index. The first block has an index of 0. |

|                    | Block Data   | 64             | Data to be written to the FLASH page.           |

| Return data buffer | ERROR_CODE   | 1              |                                                 |

#### **Bootloader CRC Check (BOOTLOADER\_CRC\_CHECK)**

API number: 0x82

Input buffer size: 0

Output buffer size: 1

| Buffer                | Parameter  | Length (bytes) | Description |

|-----------------------|------------|----------------|-------------|

| Return data<br>buffer | ERROR_CODE | 1              |             |

#### **API ERROR CODES**

| Error Code | Error Code Name              | Description                                           |

|------------|------------------------------|-------------------------------------------------------|

| 0x00       | ERROR_GENERIC                | Generic error.                                        |

| 0x01       | ERROR_OK                     | Operation succeeded. This is not indicating an error. |

| 0x02       | ERROR_INVALID_CRC            | CRC error.                                            |

| 0x03       | ERROR_FLASH_UNLOCK_FAILED    | FLASH unlocking has failed.                           |

| 0x04       | ERROR_API_NOT_IMPLEMENTED    | The API number is not implemented.                    |

| 0x05       | ERROR API DATA OVERFLOW      | The API input buffer has been filled with more data   |

|            | <b>_</b>                     | than its length.                                      |

| 0x06       | ERROR_API_INVALID_PARAMETERS | At least one of the API parameters is invalid.        |

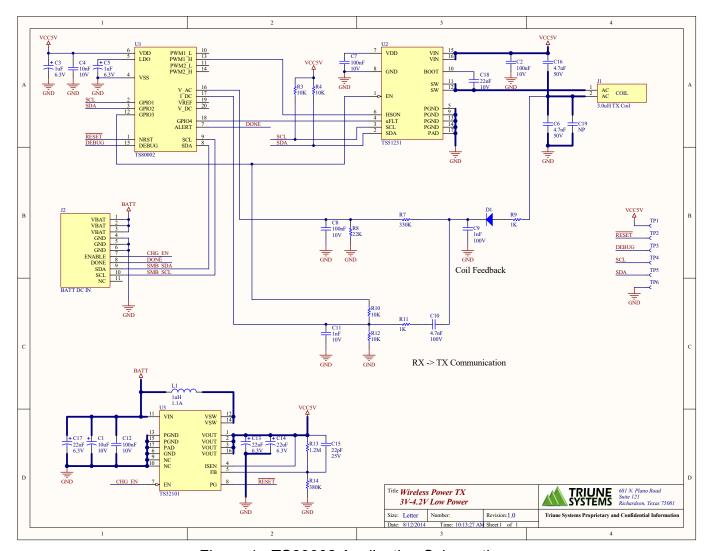

# **Application Schematic**

Figure 1: TS80002 Application Schematic

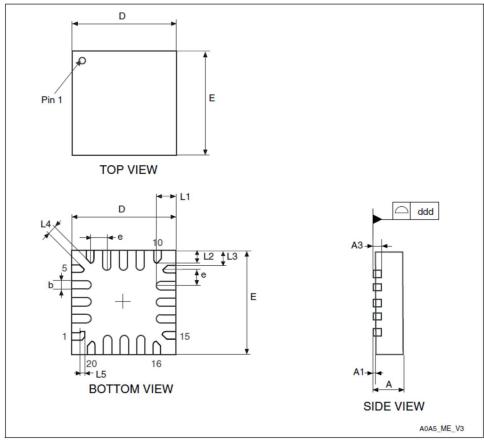

# **Package Dimensions**

20-lead ultra thin fine pitch quad flat no-lead package outline (3x3)\* \*drawing not to scale

20-lead ultra thin fine pitch quad flat no-lead package mechanical data

| Ob.al  |       | millimeters |       |                   | inches |          |

|--------|-------|-------------|-------|-------------------|--------|----------|

| Symbol | Min   | Тур         | Max   | Min               | Тур    | Max      |

| A      | 0.500 | 0.550       | 0.600 | 0.0197            | 0.0217 | 0.0236   |

| A1     | 0.000 | 0.020       | 0.050 | 0.0000            | 0.0008 | 0.0020   |

| A3     | 1#1   | 0.152       | *     | 90 <del>9</del> 7 | 0.060  | *        |

| D      | 7+0   | 3.000       | -     | 10 <del>0</del> 0 | 0.1181 | 9        |

| E      | 748   | 3.000       | e     | 1000              | 0.1181 | 9        |

| L1     | 0.500 | 0.550       | 0.600 | 0.0197            | 0.0217 | 0.0236   |

| L2     | 0.300 | 0.350       | 0.400 | 0.0118            | 0.0138 | 0.0157   |

| L3     | 123   | 0.375       | 2     |                   | 0.0148 |          |

| L4     | 123   | 0.200       | 2     |                   | 0.0079 |          |

| L5     | 120   | 0.150       | 22    |                   | 0.0059 |          |

| b      | 0.180 | 0.250       | 0.300 | 0.0071            | 0.0098 | 0.0118   |

| е      | (2)   | 0.500       | 70    | 25%               | 0.0197 | <i>5</i> |

| ddd    | (5)   | 5           | 0.050 | 3573              | -      | 0.0020   |

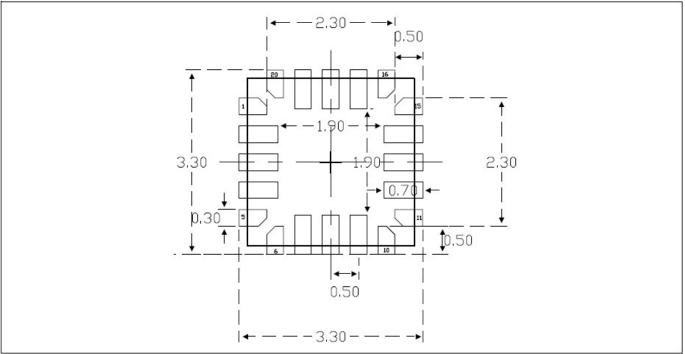

20-lead ultra thin fine pitch quad flat no-lead package recommended footprint

Dimensions are expressed in millimeters

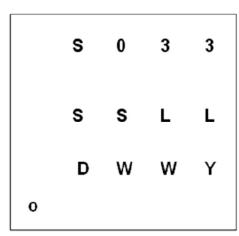

# **QFN Package (Top Marking)**

#### Legend:

| Line 1 Marking: | S033 | Internal part code       |

|-----------------|------|--------------------------|

| Line 2 Marking: | SS   | Assembly site identifier |

|                 | LL   | Lot trace code           |

| Line 3 Marking: | D    | Assembly year            |

|                 | WW   | Assembly week            |

|                 | Υ    | Additional marking       |

|                 | 0    | Pin 1 Identifier         |

## **Ordering Information**

| <b>Device Part Number</b> | Description        |

|---------------------------|--------------------|

| TS80002-QFNR              | 1W, 1MHz switching |

# **RoHS and Reach Compliance**

Semtech is fully committed to environmental quality. All Semtech materials and suppliers re fully compliant with RoHS (European Union Directive 2011/65/EU), REACH SVHC hemical Restrictions (EC 1907/2006), IPC-1752 Level 3 materials declarations, and their subsequent amendments. Semtech maintains certified laboratory reports for all product materials, from all suppliers, which show full compliance to restrictions on the following:

- Cadmium (Cd)

- Chlorofluorocarbons (CFCs)

- Chlorinate Hydrocarbons (CHCs)

- Halons (Halogen free)

- Hexavalent Chromium (CrVI)

- Hydrobromofluorocarbons (HBFCs)

- Hydrochlorofluorocarbons (HCFCs)

- Lead (Pb)

- Mercury (Hg)

- Perfluorocarbons (PFCs)

- Polybrominated biphenyls (PBB)

- Polybrominated Diphenyl Ethers (PBDEs)

#### IMPORTANT NOTICE

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2016

#### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com