Sample &

Buv

# TSC2013-Q1

SLVSC89A-JUNE 2014-REVISED JULY 2014

# TSC2013-Q1 12-Bit, Nanopower, 4-Wire Dual-Touch Screen Controller With I<sup>2</sup>C Interface

#### Features 1

- **Qualified for Automotive Applications**

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: –40°C to 125°C

- **Device HBM ESD Classification Level 2**

- Device CDM ESD Classification Level C4B

- 4-Wire Touch Screen Interface

- **Ratiometric Conversion**

- Single 1.6-V to 3.6-V Supply:

- I/OVDD 1.2 to 3.6 V

- SNSVDD: 1.6 to 3.6 V

- Preprocessing to Reduce Bus Activity

- High-Speed I<sup>2</sup>C-Compatible Interface

- Internal Detection of Screen Touch

- **Register-Based Programmable:**

- 10-Bit or 12-Bit Resolution

- Sampling Rates

- System Timing

- **Touch Pressure Measurement**

- Auto Power-Down Control

- Low Power:

- 430 µA at 1.8 V, 50 SSPS

- 320 µA at 1.6 V, 50 SSPS

- 58 µA at 1.6 V, 8.2 kSPS Eq. Rate

## 2 Applications

- Automotive Infotainment Display

- Automotive Navigation System

- Industrial User Interfaces •

- Medical Devices

- Portable Consumer Electronics

## 3 Description

The TSC2013-Q1 device is a very low-power dualtouch screen controller designed to work with powersensitive. low-cost touch-screen displays in automotive infotainment and navigation systems. It contains a complete, ultralow-power, 12-bit, analogto-digital (ADC) resistive touch-screen converter, including drivers and the control logic to measure touch pressure.

The TSC2013-Q1 device enables pinch, rotate, and zoom functionality over a standard four-wire interface. The device supports an I<sup>2</sup>C serial bus and data transmission protocol in all three defined modes: standard, fast, and high-speed. The 10 or 12-bit ADC within is easily programmable to customize system and user experience.

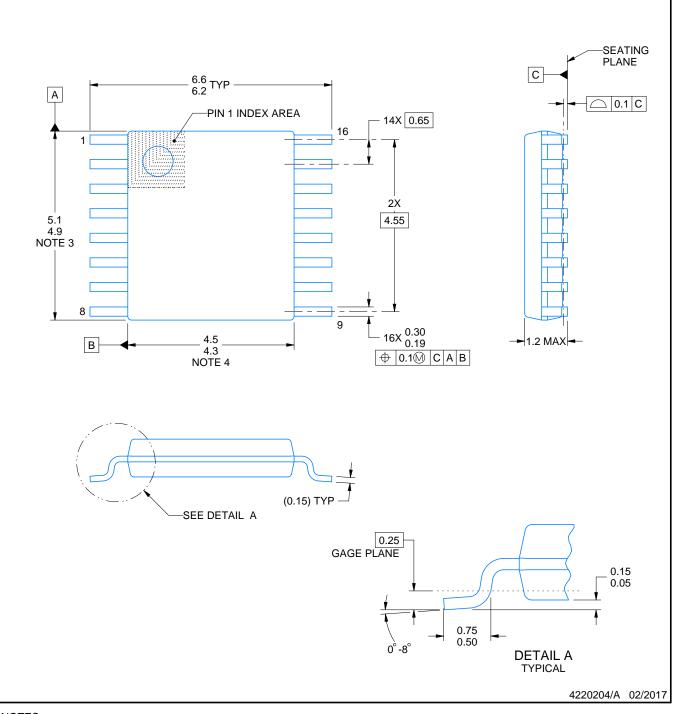

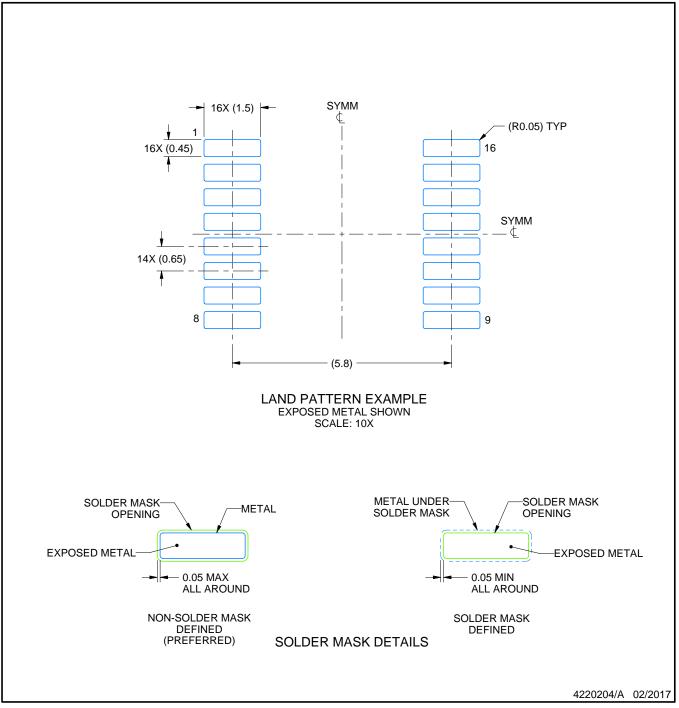

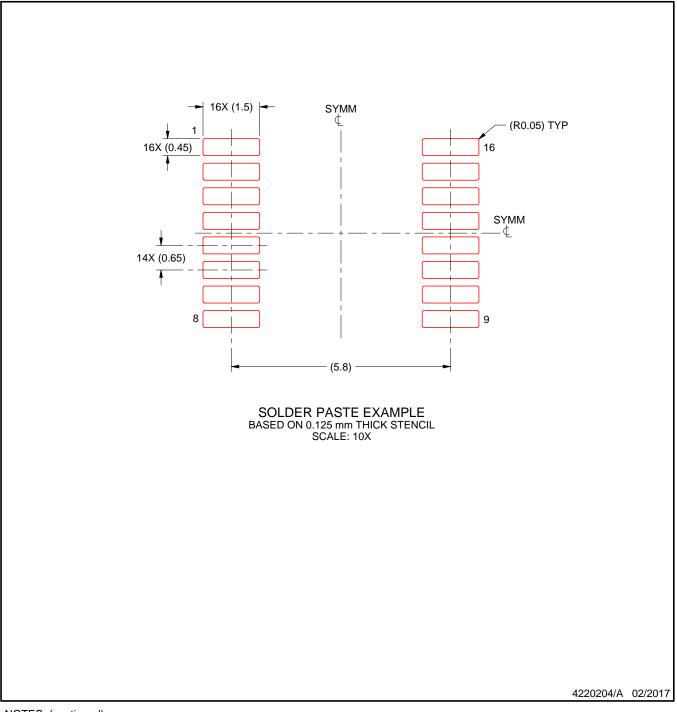

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TEC2012 01  | PVQFN (16) | 4.00 mm × 4.00 mm |

| TSC2013-Q1  | TSSOP (16) | 4.40 mm × 5.00 mm |

(1)For all available packages, see the orderable addendum at the end of the datasheet.

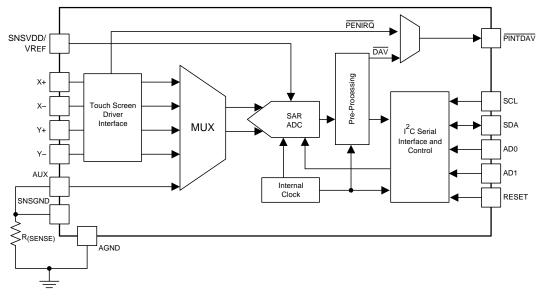

**Block Diagram**

# Table of Contents

\_

| 1 | Fea  | tures 1                                                                      |

|---|------|------------------------------------------------------------------------------|

| 2 | Арр  | lications 1                                                                  |

| 3 | Des  | cription 1                                                                   |

| 4 |      | ision History 2                                                              |

| 5 | Pin  | Configurations and Functions 3                                               |

| 6 | Spe  | cifications 4                                                                |

|   | 6.1  | Absolute Maximum Ratings 4                                                   |

|   | 6.2  | Handling Ratings 4                                                           |

|   | 6.3  | Recommended Operating Conditions 4                                           |

|   | 6.4  | Thermal Information 4                                                        |

|   | 6.5  | Electrical Characteristics 5                                                 |

|   | 6.6  | Timing Requirements — $I^2C$ Standard Mode ( $f_{(SCL)} = 100 \text{ kHz}$ ) |

|   | 6.7  | Timing Requirements — I <sup>2</sup> C Fast Mode ( $f_{(SCL)}$ = 400 kHz)7   |

|   | 6.8  | Timing Requirements — $I^2C$ High-Speed Mode<br>( $f_{(SCL)} = 1.7$ MHz)     |

|   | 6.9  | Timing Requirements — $I^2C$ High-Speed Mode<br>( $f_{(SCL)} = 3.4$ MHz)     |

|   | 6.10 | Typical Characteristics 10                                                   |

| Deta | iled Description                                                                                                                                      | 12                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

|      | -                                                                                                                                                     |                                                 |

|      |                                                                                                                                                       |                                                 |

|      | 5                                                                                                                                                     |                                                 |

| 7.3  |                                                                                                                                                       |                                                 |

| 7.4  |                                                                                                                                                       |                                                 |

| 7.5  | Programming                                                                                                                                           | 29                                              |

| 7.6  | Register Maps                                                                                                                                         | 41                                              |

| App  | lication and Implementation                                                                                                                           | 51                                              |

| 8.1  | Application Information                                                                                                                               |                                                 |

| 8.2  | Typical Application                                                                                                                                   | 52                                              |

| Pow  | er Supply Recommendations                                                                                                                             | 60                                              |

|      |                                                                                                                                                       |                                                 |

|      |                                                                                                                                                       |                                                 |

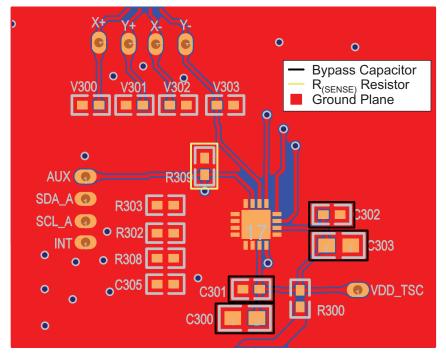

| 10.2 | Layout Example                                                                                                                                        | 61                                              |

| Dev  | ice and Documentation Support                                                                                                                         | 61                                              |

| 11.1 | Trademarks                                                                                                                                            | 61                                              |

| 11.2 | Electrostatic Discharge Caution                                                                                                                       | 61                                              |

| 11.3 | Glossary                                                                                                                                              | 61                                              |

| Mec  | hanical, Packaging, and Orderable                                                                                                                     |                                                 |

|      |                                                                                                                                                       | 61                                              |

|      | 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br><b>Appl</b><br>8.1<br>8.2<br><b>Pow</b><br>10.1<br>10.2<br><b>Dev</b><br>11.1<br>11.2<br>11.3<br><b>Mec</b> | <ul> <li>7.2 Functional Block Diagram</li></ul> |

# 4 Revision History

| CI | hanges from Original (June 2014) to Revision A                | Pag | e |

|----|---------------------------------------------------------------|-----|---|

| •  | Released full version of data sheet                           |     | 1 |

| •  | Changed device status from Product Preview to Production Data |     | 1 |

**EXAS NSTRUMENTS**

www.ti.com

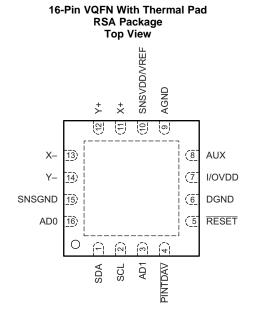

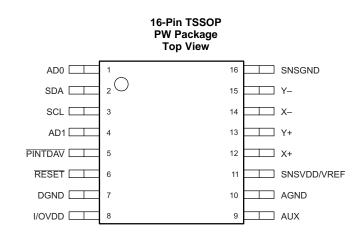

## 5 Pin Configurations and Functions

### **Pin Functions**

| PIN         |     |    | I/O | 400 | DESCRIPTION                                                                                                              |

|-------------|-----|----|-----|-----|--------------------------------------------------------------------------------------------------------------------------|

| NAME        | RSA | PW | 1/0 | ADC | DESCRIPTION                                                                                                              |

| AD0         | 16  | 1  | I   | D   | I <sup>2</sup> C bus TSC address input bit 0                                                                             |

| AD1         | 3   | 4  | I   | D   | I <sup>2</sup> C bus TSC address input bit 1                                                                             |

| AGND        | 9   | 10 | _   | _   | Analog, digital, and ESD ground <sup>(1)</sup>                                                                           |

| AUX         | 8   | 9  | _   | А   | Auxiliary channel                                                                                                        |

| DGND        | 6   | 7  | —   | _   | No internal connection. Connect this pin to analog ground for mechanical stability.                                      |

| I/OVDD      | 7   | 8  | I   | _   | Digital interface voltage                                                                                                |

| PINTDAV     | 4   | 5  | 0   | D   | Interrupt output. Data available or the pen-detect interrupt (PENIRQ), depending on setting. Pin polarity is active-low. |

| RESET       | 5   | 6  | I   | D   | External hardware reset input (active-low).                                                                              |

| SDA         | 1   | 2  | I/O | D   | Serial data I/O                                                                                                          |

| SCL         | 2   | 3  | I   | D   | Serial clock                                                                                                             |

| SNSGND      | 15  | 16 | _   | _   | Sensor driver return                                                                                                     |

| SNSVDD/VREF | 10  | 11 | I   | _   | Power supply for sensor drivers and other analog blocks                                                                  |

| X+          | 11  | 12 | _   | А   | X+ channel                                                                                                               |

| X-          | 13  | 14 |     | А   | X- channel                                                                                                               |

| Y+          | 12  | 13 | _   | А   | Y+ channel                                                                                                               |

| Y–          | 14  | 15 |     | А   | Y- channel                                                                                                               |

(1) For optimized system IEC ESD performance, contact Texas Instruments for schematic and layout reviews and suggestions.

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted).

|                                         |                                    | MIN                | МАХ                                   | UNIT |

|-----------------------------------------|------------------------------------|--------------------|---------------------------------------|------|

| Voltage                                 | Analog input X+, Y+, AUX to SNSGND | -0.4               | SNSVDD + 0.1                          | V    |

|                                         | Analog input X–, Y– to SNSGND      | -0.4               | SNSVDD + 0.1                          | V    |

| Valtaga                                 | SNSVDD to SNSGND                   | -0.3               | 5                                     | V    |

| vollage                                 | SNSVDD to AGND                     | -0.3               | 5                                     | V    |

|                                         | I/OVDD to AGND                     | -0.3               | 5                                     | V    |

| Digital input voltage to AGND           | SNSVDD to I/OVDD                   | -2.4               | 0.3                                   | V    |

| Digital input voltage to AGN            | D                                  | -0.3               | I/OVDD + 0.3                          | V    |

| Digital output voltage to AG            | ND                                 | -0.3               | I/OVDD + 0.3                          | V    |

| Power dissipation                       |                                    | (T <sub>Jmax</sub> | – T <sub>A</sub> ) / R <sub>θJA</sub> |      |

| Operating free-air temperate            | ure range, T <sub>A</sub>          | -40                | 125                                   | °C   |

| Junction temperature, T <sub>Jmax</sub> |                                    |                    | 150                                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-maximum rated conditions for extended periods may affect device reliability.

## 6.2 Handling Ratings

|                    |                                      |                                              |                                                                             | MIN   | MAX  | UNIT |

|--------------------|--------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------|-------|------|------|

| T <sub>stg</sub>   | Storage temperature range            | 2                                            |                                                                             | -65   | 150  | °C   |

| V <sub>(ESD)</sub> |                                      | Human body model (HBM), per A                | AEC Q100-002 <sup>(1)</sup>                                                 | -2000 | 2000 |      |

|                    | Electrostatic discharge              | Charged device model (CDM), per AEC Q100-011 | Corner pins (RSA: 1, 4, 5,<br>8, 9, 12, 13, and 16;<br>PW: 1, 8, 9, and 16) | -750  | 750  | V    |

|                    |                                      |                                              | Other pins                                                                  | -500  | 500  |      |

|                    | IEC contact discharge <sup>(2)</sup> | X+, X–, Y+, Y–                               |                                                                             | -15   | 15   | kV   |

|                    | IEC air discharge <sup>(2)</sup>     | X+, X–, Y+, Y–                               |                                                                             | -25   | 25   | kV   |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

(2) Test method based on IEC standard 61000-4-2. Contact Texas Instruments for test details.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         | MIN | NOM | MAX | UNIT |

|-------------------------|-----|-----|-----|------|

| Input voltage SNSVDD/VR | 1.6 | 3.3 | 3.6 | V    |

| Input voltage I/OVDD    | 1.2 | 3.3 | 3.6 | V    |

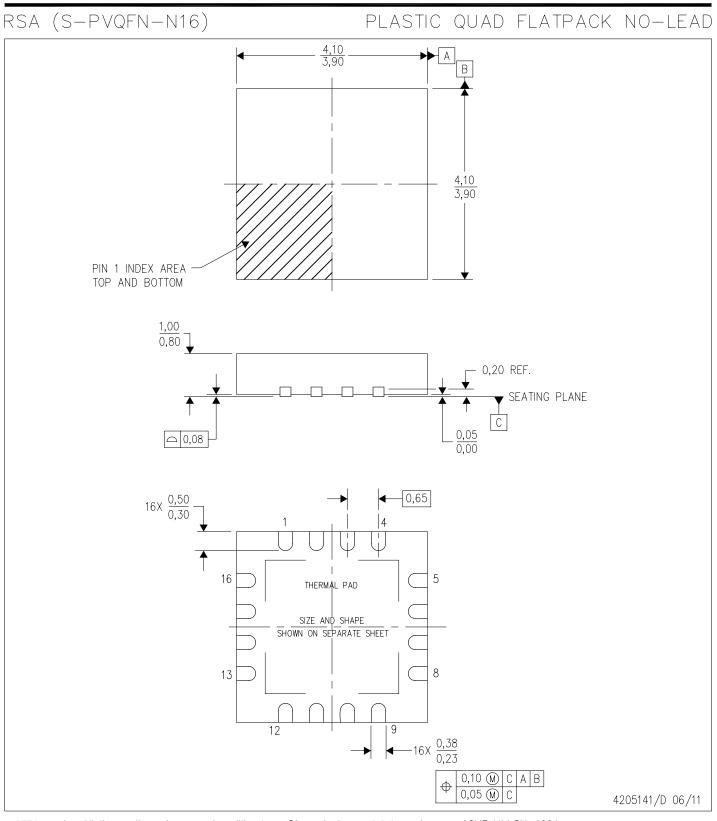

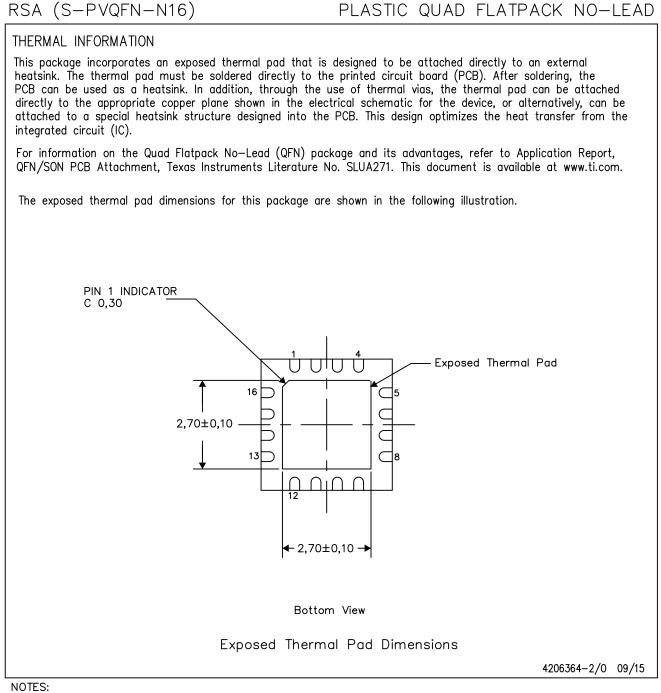

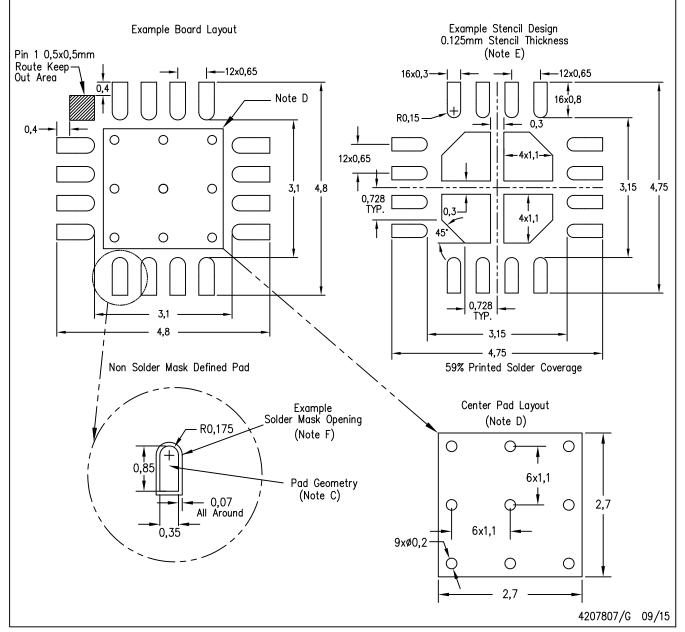

## 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | RSA     | PW      | LINUT |

|-----------------------|----------------------------------------------|---------|---------|-------|

|                       |                                              | 16 PINS | 16 PINS | UNIT  |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 33.7    | 100.9   | °C/W  |

| R <sub>0JC(top)</sub> | Junction-to-case(top) thermal resistance     | 36.7    | 36.1    | °C/W  |

| $R_{	extsf{	heta}JB}$ | Junction-to-board thermal resistance         | 10.5    | 45.7    | °C/W  |

| $\psi_{JT}$           | Junction-to-top characterization parameter   | 0.6     | 2.6     | °C/W  |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 10.5    | 45.1    | °C/W  |

| R <sub>0JC(bot)</sub> | Junction-to-case(bottom) thermal resistance  | 2.5     | —       | °C/W  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

| At $T_A = -40^{\circ}$ C to 125°C, $V_{(SNSVDD/VREF)}$ | = 1.6 V to 3.6 V, and $V_{(I/OVDD)}^{(1)}$ = 1.2 V to | $V_{(SNSVDD/VREF)}$ , unless otherwise noted. |

|--------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|

|--------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|

|                                 | PARAMETER                 |                      | TEST CONDITIONS                                                                   | MIN                            | TYP           | MAX                       | UNIT               |

|---------------------------------|---------------------------|----------------------|-----------------------------------------------------------------------------------|--------------------------------|---------------|---------------------------|--------------------|

| AUXILIA                         | RY ANALOG INPUT           |                      |                                                                                   |                                |               |                           |                    |

|                                 | Input voltage             |                      |                                                                                   | 0                              |               | V <sub>ref</sub>          | V                  |

|                                 | Input capacitance         |                      |                                                                                   |                                | 12            |                           | pF                 |

|                                 | Input leakage current     |                      | No ADC conversion                                                                 | -1                             |               | 1                         | μA                 |

|                                 | Full-scale average input  | current              | $V_{(SNSVDD/VREF)} = 1.6 \text{ V}$ , continuous AUX, $f_{(ADC)} = 2 \text{ MHz}$ |                                | 2             |                           | μA                 |

| ADC                             |                           |                      |                                                                                   |                                |               |                           |                    |

|                                 | Resolution                |                      | Programmable: 10 or 12 bits                                                       |                                |               | 12                        | Bits               |

|                                 | No missing codes          |                      | 12-bit resolution                                                                 | 11                             |               |                           | Bits               |

|                                 | Integral linearity        |                      | 12-bit resolution mode, $f_{(ADC)} = 2 \text{ MHz}$                               | -3                             | -0.5 to 0.5   | 3                         | LSB <sup>(2)</sup> |

|                                 | Differential linearity    |                      | 12-bit resolution mode, $f_{ADC} = 2MHz$                                          | -2                             | -0.5 to 0.5   | 4                         | LSB                |

|                                 | Offset error              |                      | $V_{(SNSVDD/VREF)}$ = 1.6 V, 12-bit mode, $f_{(ADC)}$ = 2 MHz, filter off         |                                | 0.2           |                           | LSB                |

|                                 | Gain error                |                      | $V_{(SNSVDD/VREF)}$ = 1.6 V, 12-bit mode, $f_{(ADC)}$ = 2 MHz, filter off         |                                | 2             |                           | LSB                |

|                                 | Data format               |                      |                                                                                   |                                | Straight bina | ary                       |                    |

| REFERE                          | NCE INPUT                 |                      |                                                                                   |                                |               |                           |                    |

|                                 | V <sub>ref</sub> range    |                      |                                                                                   | 1.6                            |               | V(SNSVDD/VREF)            | V                  |

|                                 | SNSVDD/VREF input-cu      | rrent drain          | Continuous AUX mode, $V_{(SNSVDD/VREF)} = 1.6 V$ , $f_{(ADC)} = 2 MHz$            |                                | 5             |                           | μA                 |

|                                 | Input impedance           |                      | No ADC conversion                                                                 |                                | > 100         |                           | MΩ                 |

| тоисн я                         | SENSORS                   |                      |                                                                                   |                                |               |                           |                    |

|                                 | X+ 50-kΩ pullup resistor  | , R <sub>(IRQ)</sub> |                                                                                   |                                | 52            |                           | kΩ                 |

|                                 | Quitab an register of     | Y+, X+               | $T_A = 25^{\circ}C, V_{(SNSVDD/VREF)} = 1.6 V$                                    |                                | 7             |                           | Ω                  |

|                                 | Switch on-resistance      | Y-, X-               | $T_A = 25^{\circ}C, V_{(SNSVDD/VREF)} = 1.6 V$                                    |                                | 5             |                           | Ω                  |

|                                 | Switch drivers drive curr | ent                  | 100-ms duration                                                                   |                                |               | 50                        | mA                 |

| NTERNA                          | AL OSCILLATOR             |                      |                                                                                   |                                |               |                           |                    |

|                                 |                           |                      | $V_{(SNSVDD/VREF)} = 1.6 \text{ V},  \text{T}_{\text{A}} = 25^{\circ}\text{C}$    | 3.3                            | 3.7           | 4.3                       | MHz                |

| f <sub>(OSC)</sub>              | Clock frequency           |                      | $V_{(SNSVDD/VREF)} = 3 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$             |                                | 3.8           |                           | MHz                |

|                                 | <b>E</b> 1.77             |                      | V <sub>(SNSVDD/VREF)</sub> = 1.6 V                                                |                                | -0.008        |                           | %/°C               |

|                                 | Frequency drift           |                      | V <sub>(SNSVDD/VREF)</sub> = 3 V                                                  |                                | -0.021        |                           | %/°C               |

| DIGITAL                         | INPUT/OUTPUT              |                      |                                                                                   |                                |               |                           |                    |

|                                 | Logic family              |                      |                                                                                   |                                | CMOS          |                           |                    |

| V <sub>IH</sub>                 | Input-voltage logic-level | high                 | $1.2 \text{ V} \leq \text{V}_{(VOVDD)} < 3 \text{ V}$                             | 0.7 ×<br>V <sub>(I/OVDD)</sub> |               | 3.6                       | V                  |

| V <sub>IL</sub>                 | Input-voltage logic-level | low                  | $1.2 \text{ V} \leq \text{V}_{(\text{I/OVDD})} < 3 \text{ V}$                     | -0.3                           |               | $0.2 \times V_{(I/OVDD)}$ | V                  |

| <sub>IL</sub> , I <sub>IH</sub> | Input-current logic-level | low and high         |                                                                                   | -1                             |               | 1                         | μA                 |

| Cı                              | Input-capacitance logic l | evel                 |                                                                                   |                                |               | 10                        | pF                 |

| V <sub>он</sub>                 | Output-voltage logic-leve | el high              | l <sub>OH</sub> = 100 μA                                                          | V <sub>(I/OVDD)</sub><br>- 0.2 |               | V <sub>(I/OVDD)</sub>     | V                  |

| V <sub>OL</sub>                 | Output-voltage logic-leve | el low               | I <sub>OL</sub> = -3.2 mA                                                         | 0                              |               | 0.2                       | V                  |

| lkg                             | Leakage-current logic lev | vel                  | SDA                                                                               | -1                             |               | 1                         | μA                 |

| Co                              | Output-capacitance logic  | : level              | SDA                                                                               |                                |               | 10                        | pF                 |

| POWER-                          | SUPPLY REQUIREMENT        | s                    |                                                                                   |                                |               |                           |                    |

|                                 | Power-supply voltage      |                      |                                                                                   |                                |               |                           |                    |

|                                 | SNSVDD                    |                      |                                                                                   | 1.6                            |               | 3                         | V                  |

|                                 | I/OVDD <sup>(1)</sup>     |                      |                                                                                   | 1.2                            |               | V(SNSVDD/VREF)            | V                  |

## **Electrical Characteristics (continued)**

At  $T_A = -40^{\circ}$ C to 125°C,  $V_{(SNSVDD/VREF)} = 1.6$  V to 3.6 V, and  $V_{(I/OVDD)}^{(1)} = 1.2$  V to  $V_{(SNSVDD/VREF)}$ , unless otherwise noted.

| PARAMETER                                     | TEST CONDITION                                                                                                                                                                                                                                                                      | ONS                                                                                                     | MIN | TYP  | MAX | UNIT |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|------|-----|------|

|                                               | $ \begin{array}{l} {\sf T}_{\rm A}=25^{\circ}{\rm C}, \mbox{ filter off, } {\sf M}={\sf W}=1, \mbox{ C}[3:0]=(1,0,0,0), \mbox{ RM}=1, \mbox{ CL}[1:0]=(0,1), \mbox{ cont AUX} \\ \mbox{ mode, } f_{\rm (ADC)}=2 \mbox{ MHz, without reading data} \\ \mbox{ register} \end{array} $ | $V_{(SNSVDD/VREF)} = V_{(l/OVDD)} = 1.6 V$                                                              |     | 420  | 570 | μA   |

|                                               | $T_A = 25^{\circ}C$ , filter on, M = 15, W = 7, PSM = 1,<br>C[3:0] = (0, 0, 0, 0), RM = 1, CL[1:0] = (0, 1),                                                                                                                                                                        | $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = 1.6 V$                                                              |     | 200  |     | μA   |

|                                               | <ul> <li>BTD[2:0] = (1, 0, 1), 50 SSPS, MAVEX =</li> <li>MAVEY = MAVEZ = 1, f<sub>(ADC)</sub> = 2 MHz, sensor drivers supply included<sup>(5)</sup></li> </ul>                                                                                                                      | $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = 3 V$                                                                |     | 400  |     | μA   |

|                                               | $T_A = 25^{\circ}C$ , filter off, M = W = 1, PSM = 1,                                                                                                                                                                                                                               | $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = 1.6 V$                                                              |     | 180  |     | μA   |

| Quiescent supply<br>current <sup>(3)(4)</sup> | $ \begin{array}{l} C[3:0] = (0, 0, 0, 0), RM = 1, CL[1:0] = (0, 1), \\ BTD[2:0] = (1, 0, 1), 50 SSPS, MAVEX = \\ MAVEX = MAVEZ = 1, f_{ADC} = 2 MHz, sensor \\ drivers supply included(5) \end{array} $                                                                             | $V_{(SNSVDD/VREF)} = V_{(l/OVDD)} = 3 V$                                                                |     | 370  |     | μA   |

|                                               | $T_A = 25^{\circ}C$ , filter off, M = W = 1, C[3:0] = (0, 1, 0, 1), RM = 1, CL[1:0] = (0, 1), non-cont AUX mode, $f_{(ADC)} = 2$ MHz, high-speed mode                                                                                                                               | $V_{(SNSVDD/VREF)} = V_{(VOVDD)} = 1.6 V,$<br>approximately 28 kSPS effective rate                      |     | 190  |     | μA   |

|                                               |                                                                                                                                                                                                                                                                                     | $V_{(SNSVDD/VREF)} = V_{(VOVDD)} = 3 V,$<br>approximately 28.4 kSPS<br>effective rate                   |     | 370  |     | μA   |

|                                               | $ \begin{array}{l} T_{A} = 25^{\circ}C, \mbox{ filter on, M = 7, W = 3, C[3:0] = (0, \\ 1, 0, 1), \mbox{ RM = 1, CL[1:0] = (0, 1), MAVEAUX \\ = 1, \mbox{ non-cont AUX mode, } f_{(\texttt{ADC})} = 2 \mbox{ MHz}, \\ \mbox{ high-speed mode, full speed} \end{array} $             | $V_{(SNSVDD/VREF)} = V_{(VOVDD)} = 1.6 V,$<br>approximately 10.5 kSPS<br>effective rate                 |     | 355  |     | μA   |

|                                               |                                                                                                                                                                                                                                                                                     | $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = 3 V,$<br>approximately 10.9 kSPS<br>effective rate                  |     | 655  |     | μA   |

|                                               | $T_A = 25^{\circ}C$ , filter on, M = 7, W = 3, C[3:0] = (0, 1, 0, 1), RM = 1, CL[1:0] = (0, 1), MAVEAUX                                                                                                                                                                             | V <sub>(SNSVDD/REF)</sub> = V <sub>(l/OVDD)</sub> = 1.6 V,<br>approximately 1.17 kSPS<br>effective rate |     | 36.2 |     | μA   |

|                                               | = 1, non-cont AUX mode, f <sub>(ADC)</sub> = 2 MHz,<br>high-speed mode, reduced speed (8.2-kSPS<br>equivalent rate)                                                                                                                                                                 |                                                                                                         |     | 64.9 |     | μA   |

| Power-down supply current                     | $\frac{T_A = 25^{\circ}C}{PINTDAV} = 1, V_{(SNSVDD/VREF)} = I/OVDD = V_{ref} =$                                                                                                                                                                                                     |                                                                                                         |     | 0.04 | 0.8 | μA   |

| Digital power-down supply current             | $\frac{T_A = 25^{\circ}C, \text{ not addressed, SCL} = SDA = 1, \overline{RE}}{PINTDAV} = 1, V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = V_{ref} =$                                                                                                                                          |                                                                                                         |     | 0.04 | 0.8 | μA   |

(3) Supply current from SNSVDD.

For detailed information on test condition parameter and bit settings, see the section. Touch sensor modeled by 2 k $\Omega$  for X– plane and Y– plane, and 1 k $\Omega$  for Z-plane (touch resistance). (4) (5)

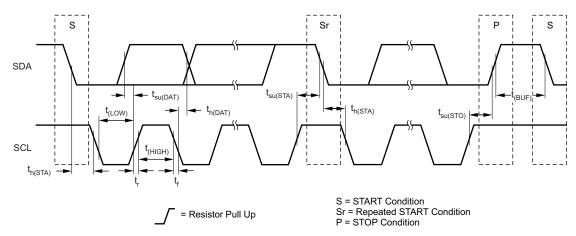

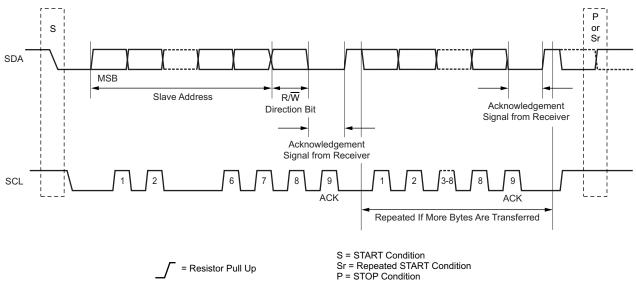

## 6.6 Timing Requirements — I<sup>2</sup>C Standard Mode ( $f_{(SCL)} = 100 \text{ kHz}$ )

All specifications typical at -40°C to 125°C,  $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = 1.6$  V to 3 V, unless otherwise noted.

|                         |                                                                         |                                                     | MIN | MAX  | UNIT |

|-------------------------|-------------------------------------------------------------------------|-----------------------------------------------------|-----|------|------|

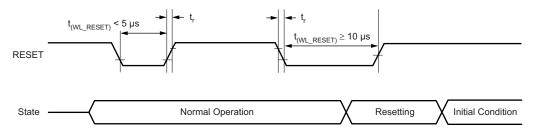

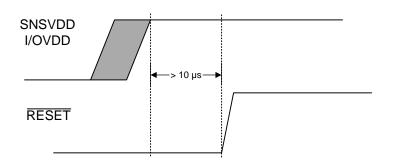

| t <sub>(WL_RESET)</sub> | Reset low time <sup>(1)</sup>                                           | See Figure 1 and Figure 37                          | 10  |      | μs   |

| $f_{(SCL)}$             | SCL clock frequency                                                     |                                                     |     | 100  | kHz  |

| t <sub>(BUF)</sub>      | Bus free time between a STOP and START condition                        |                                                     | 4.7 |      | μs   |

| t <sub>h(STA)</sub>     | Hold time for (repeated) START condition                                |                                                     | 4   |      | μs   |

| t <sub>(LOW)</sub>      | Low period of SCL clock                                                 |                                                     | 4.7 |      | μs   |

| t <sub>(HIGH)</sub>     | High period of the SCL clock                                            | See Figure 1                                        | 4   |      | μs   |

| t <sub>su(STA)</sub>    | Setup time for a repeated START condition                               |                                                     | 4.7 |      | μs   |

| t <sub>h(DAT)</sub>     | Data hold time                                                          |                                                     | 0   | 3.45 | μs   |

| t <sub>su(DAT)</sub>    | Data setup time                                                         |                                                     | 250 |      | ns   |

| t <sub>r</sub>          | Rise time of both SDA and SCL signals                                   | $C_{(b)}$ = total bus capacitance                   |     | 1000 | ns   |

| t <sub>f</sub>          | Fall time of both SDA and SCL signals                                   | See Figure 1                                        |     | 300  | ns   |

| t <sub>su(STO)</sub>    | Setup time for STOP condition                                           | See Figure 1                                        | 4   |      | μs   |

| C <sub>(b)</sub>        | Capacitive load for each bus line                                       | $C_{(b)}$ = total capacitance of one bus line in pF |     | 400  | pF   |

| t <sub>d(SP)</sub>      | Pulse duration of spikes that must be<br>suppressed by the input filter |                                                     | N/A | N/A  | ns   |

(1)  $V_{(SNSVDD/VREF)} \ge 1.6 V$

## 6.7 Timing Requirements — I<sup>2</sup>C Fast Mode ( $f_{(SCL)}$ = 400 kHz)

All specifications typical at -40°C to  $125^{\circ}C$ ,  $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = 1.6$  V to 3 V, unless otherwise noted.

|                         |                                                                         |                                                            | MIN                         | MAX | UNIT |

|-------------------------|-------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------|-----|------|

| t <sub>(WL_RESET)</sub> | Reset low time <sup>(1)</sup>                                           | See Figure 1 and Figure 37                                 | 10                          |     | μs   |

| $f_{(\rm SCL)}$         | SCL clock frequency                                                     |                                                            |                             | 400 | kHz  |

| t <sub>(BUF)</sub>      | Bus free time between a STOP and START condition                        |                                                            | 1.3                         |     | μs   |

| t <sub>h(STA)</sub>     | Hold time for (repeated) START condition                                |                                                            | 0.6                         |     | μs   |

| t <sub>(LOW)</sub>      | Low period of SCL clock                                                 |                                                            | 1.3                         |     | μs   |

| t <sub>(HIGH)</sub>     | High period of the SCL clock                                            | See Figure 1                                               | 0.6                         |     | μs   |

| t <sub>su(STA)</sub>    | Setup time for a repeated START condition                               |                                                            | 0.6                         |     | μs   |

| t <sub>h(DAT)</sub>     | Data hold time                                                          |                                                            | 0                           | 0.9 | μs   |

| t <sub>su(DAT)</sub>    | Data setup time                                                         |                                                            | 100                         |     | ns   |

| t <sub>r</sub>          | Rise time of both SDA and SCL signals                                   | $C_{(b)}$ = total bus capacitance                          | 20 + 0.1 × C <sub>(b)</sub> | 300 | ns   |

| t <sub>f</sub>          | Fall time of both SDA and SCL signals <sup>(2)</sup>                    | See Figure 1                                               | 20 + 0.1 × C <sub>(b)</sub> | 300 | ns   |

| t <sub>su(STO)</sub>    | Setup time for STOP condition                                           | See Figure 1                                               | 0.6                         |     | μs   |

| C <sub>(b)</sub>        | Capacitive load for each bus line                                       | C <sub>(b)</sub> = total capacitance of one bus line in pF |                             | 400 | pF   |

| t <sub>d(SP)</sub>      | Pulse duration of spikes that must be<br>suppressed by the input filter |                                                            | 0                           | 50  | ns   |

V<sub>(SNSVDD/VREF)</sub> ≥ 1.6 V

C<sub>(b)</sub> = the total capacitance of one bus line in pF. If using both fast-mode and Hs-mode devices, one may use faster fall times according to the *Timing Requirements* — l<sup>2</sup>C High-Speed Mode (f<sub>(SCL)</sub> = 3.4 MHz) section. Note that the TSC2013-Q1 device is an Hs-mode device and follows the table requirements listed in the *Timing Requirements* — l<sup>2</sup>C High-Speed Mode (f<sub>(SCL)</sub> = 3.4 MHz) section.

TRUMENTS

XAS

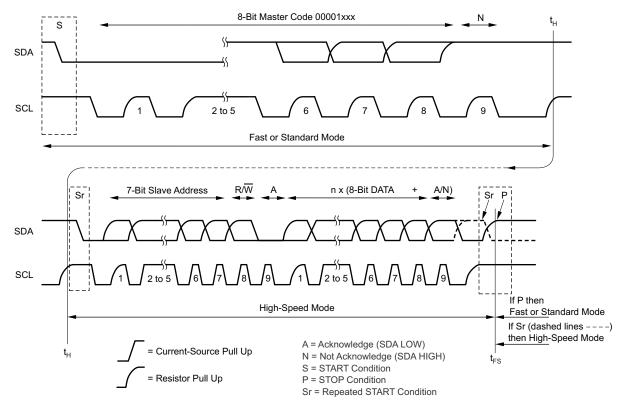

# 6.8 Timing Requirements — I<sup>2</sup>C High-Speed Mode ( $f_{(SCL)} = 1.7$ MHz)

All specifications typical at -40°C to 125°C,  $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} =$  to 3 V, unless otherwise noted.

|                      |                                                                                       |                                                     | MIN | MAX | UNIT |

|----------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|------|

| t(WL_RESET)          | Reset low time <sup>(1)</sup>                                                         | See Figure 2 and Figure 37                          | 10  |     | μs   |

| $f_{(SCL)}$          | SCL clock frequency                                                                   |                                                     |     | 1.7 | MHz  |

| t <sub>h(STA)</sub>  | Hold time of (repeated) START condition                                               |                                                     | 160 |     | ns   |

| t <sub>(LOW)</sub>   | Low period of SCL clock                                                               |                                                     | 320 |     | ns   |

| t <sub>(HIGH)</sub>  | High period of the SCL clock                                                          |                                                     | 120 |     | ns   |

| t <sub>su(STA)</sub> | Setup time for a repeated START condition                                             | See Figure 2                                        | 160 |     | ns   |

| t <sub>h(DAT)</sub>  | Data hold time                                                                        |                                                     | 0   | 150 | ns   |

| t <sub>su(DAT)</sub> | Data setup time                                                                       |                                                     | 10  |     | ns   |

| t <sub>r(CL)</sub>   | Rise time of SCL signal                                                               |                                                     | 20  | 80  | ns   |

| t <sub>r(DA)</sub>   | Rise time of SDA signal                                                               |                                                     | 20  | 160 | ns   |

| t <sub>f(CL)</sub>   | Fall time of SCL signal                                                               | $C_{(b)} = $ total bus capacitance <sup>(2)</sup>   | 20  | 80  | ns   |

| t <sub>f(DA)</sub>   | Fall time of SDA signal                                                               | Figure 2                                            | 1   | 160 | ns   |

| t <sub>r(CL1)</sub>  | Rise time of SCL signal after a repeated START condition and after an acknowledge bit |                                                     | 20  | 160 | ns   |

| t <sub>su(STO)</sub> | Setup time for STOP condition                                                         | See Figure 2                                        | 160 |     | ns   |

| C <sub>(b)</sub>     | Capacitive load for each bus line                                                     | $C_{(b)}$ = total capacitance of one bus line in pF |     | 400 | pF   |

| t <sub>d(SP)</sub>   | Pulse duration of spikes that must be<br>suppressed by the input filter               |                                                     | 0   | 10  | ns   |

(1)

$V_{(SNSVDD/VREF)} \ge 1.6 V$ For capacitive bus loads between 100 pF and 400 pF, interpolate the rise-time and fall-time values linearly. (2)

# 6.9 Timing Requirements — I<sup>2</sup>C High-Speed Mode ( $f_{(SCL)}$ = 3.4 MHz)

All specifications typical at -40°C to 125°C,  $V_{(SNSVDD/VREF)} = V_{(I/OVDD)} = 1.6 V^{(1)}$  to 3 V, unless otherwise noted.

|                         |                                                                                       |                                                     | MIN | MAX | UNIT |

|-------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|------|

| t <sub>(WL_RESET)</sub> | Reset low time <sup>(2)</sup>                                                         | See Figure 2 and Figure 37                          | 10  |     | μs   |

| $f_{(SCL)}$             | SCL clock frequency                                                                   |                                                     |     | 3.4 | MHz  |

| t <sub>h(STA)</sub>     | Hold time for (repeated) START condition                                              |                                                     | 160 |     | ns   |

| t <sub>(LOW)</sub>      | Low period of SCL clock                                                               |                                                     | 160 |     | ns   |

| t <sub>(HIGH)</sub>     | High period of the SCL clock                                                          |                                                     | 60  |     | ns   |

| t <sub>su(STA)</sub>    | Setup time for a repeated START condition                                             | See Figure 2                                        | 160 |     | ns   |

| t <sub>h(DAT)</sub>     | Data hold time                                                                        |                                                     | 0   | 70  | ns   |

| t <sub>su(DAT)</sub>    | Data setup time                                                                       |                                                     | 10  |     | ns   |

| t <sub>r(CL)</sub>      | Rise time of SCL signal                                                               |                                                     | 10  | 40  | ns   |

| t <sub>r(DA)</sub>      | Rise time of SDA signal                                                               |                                                     | 10  | 80  | ns   |

| t <sub>f(CL)</sub>      | Fall time of SCL signal                                                               | $C_{(b)}$ = total bus capacitance <sup>(3)</sup>    | 10  | 40  | ns   |

| t <sub>f(DA)</sub>      | Fall time of SDA signal                                                               | See Figure 2                                        | 1   | 80  | ns   |

| t <sub>r(CL1)</sub>     | Rise time of SCL signal after a repeated START condition and after an acknowledge bit |                                                     | 10  | 80  | ns   |

| t <sub>su(STO)</sub>    | Setup time for STOP condition                                                         | See Figure 2                                        | 160 |     | ns   |

| C <sub>(b)</sub>        | Capacitive load for each bus line                                                     | $C_{(b)}$ = total capacitance of one bus line in pF |     | 100 | pF   |

| t <sub>d(SP)</sub>      | Pulse duration of spikes that must be<br>suppressed by the input filter               |                                                     | 0   | 10  | ns   |

Because of the low supply voltage of 1.2 V and the wide temperature range of  $-40^{\circ}$ C to 125°C, the l<sup>2</sup>C system devices may not reach the maximum specification of l<sup>2</sup>C high-speed mode, and  $f_{(SCL)}$  may not reach 3.4 MHz. (1)

$V_{(SNSVDD/VREF)} \ge 1.6 V$ Capacitive load from 10 pF to 100 pF. (3)

(1) The First rising edge of the SCL signal after Sr and after each acknowledge bit.

Figure 2. Detailed I/O Timing for High-Speed Mode

TSC2013-Q1 SLVSC89A – JUNE 2014 – REVISED JULY 2014

www.ti.com

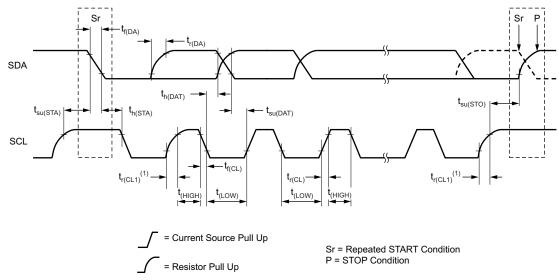

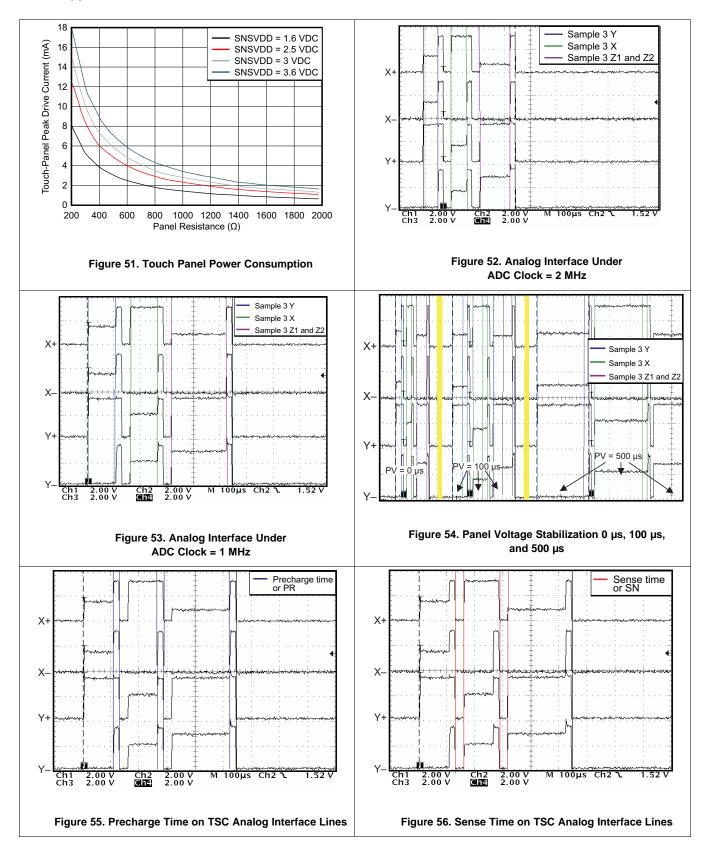

## 6.10 Typical Characteristics

At  $T_A = -40^{\circ}$ C to 125°C, SNSVDD/VREF = 1.6 V to 3 V, I/OVDD = 1.2 V to SNSVDD/VREF,  $f_{(ADC)} = f_{(OSC)} / 2$ , high-speed mode ( $f_{(SCL)} = 3.4$  MHz), 12-bit mode, and non-continuous AUX measurement, unless otherwise noted.

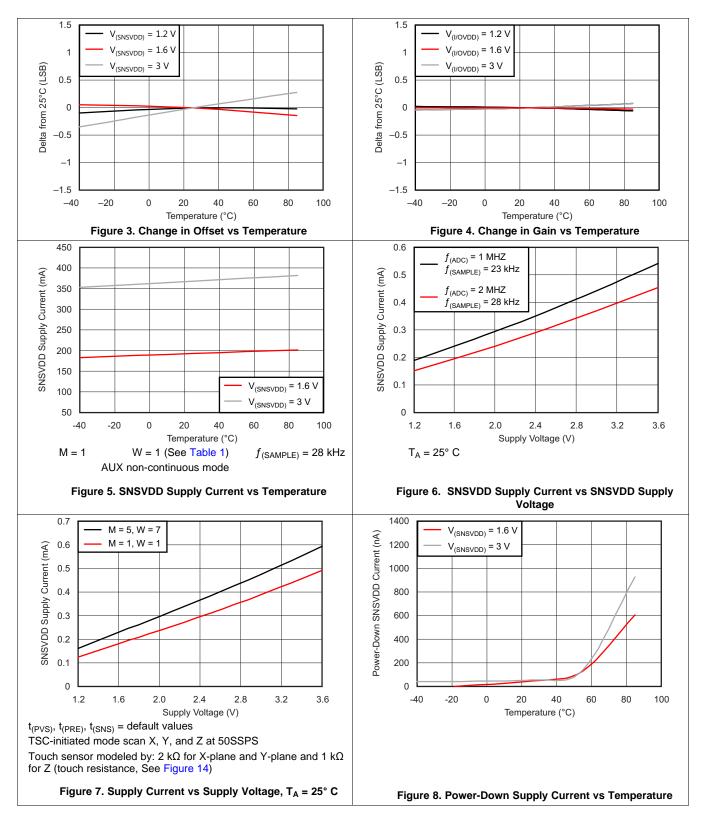

## **Typical Characteristics (continued)**

At  $T_A = -40^{\circ}$ C to 125°C, SNSVDD/VREF = 1.6 V to 3 V, I/OVDD = 1.2 V to SNSVDD/VREF,  $f_{(ADC)} = f_{(OSC)} / 2$ , high-speed mode ( $f_{(SCL)} = 3.4$  MHz), 12-bit mode, and non-continuous AUX measurement, unless otherwise noted.

## 7 Detailed Description

## 7.1 Overview

The TSC2013-Q1 device is an analog interface circuit for a human-interface touch-screen device. A registerbased architecture eases integration with microprocessor-based systems through a standard l<sup>2</sup>C bus. Registers and onboard state machines control all peripheral functions. The TSC2013-Q1 features include:

- Very low-power touch-screen controller

- Very small onboard footprint

- Flexible preprocessing which relieves the host from tedious routine tasks and saves resources for more critical tasks

- · Ability to work on very low supply voltage

- Minimal connection interface allows easiest isolation and reduces the number of dedicated I/O pins required

- Enhanced ESD protection

- Panel-current sensing

- Miniature device, yet complete; requires no external supporting components

## NOTE

Although the TSC2013-Q1 device can use an external reference, the SNSVDD/VREF pin can also be used as the reference.

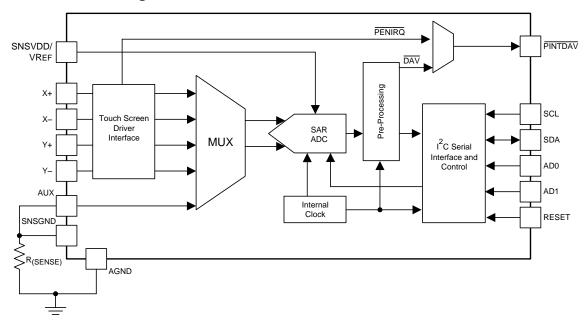

The TSC2013-Q1 device consists of the following blocks (see the *Functional Block Diagram* section):

- Touch-screen interface

- Auxiliary input (AUX)

- Acquisition-activity preprocessing

- Internal conversion clock

- I<sup>2</sup>C interface

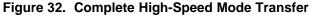

Communication with the TSC2013-Q1 device is through an I<sup>2</sup>C serial interface. The TSC2013-Q1 device is an I<sup>2</sup>C slave device. Therefore, data shifts into or out of the TSC2013-Q1 device under the control of the host microprocessor, which also provides the serial data clock.

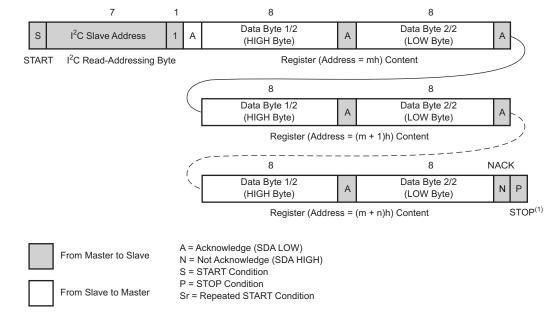

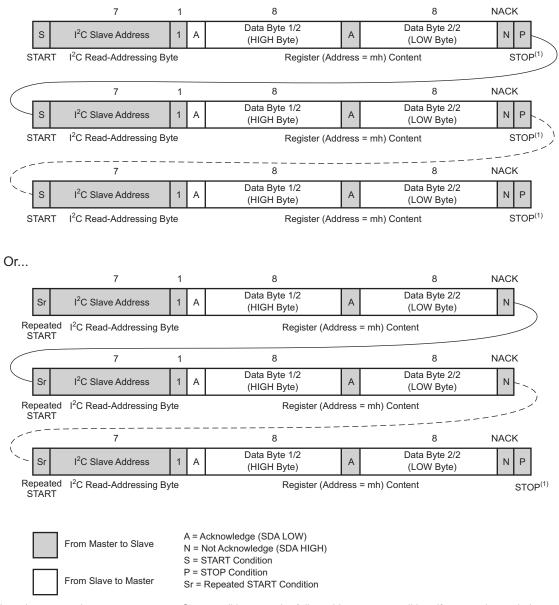

Writing to different registers in the TSC2013-Q1 device controls the TSC2013-Q1 device and device functions. The use of a simple command protocol (compatible with I<sup>2</sup>C) addresses these registers. This protocol can be an I<sup>2</sup>C write-address followed by multiple control bytes, or multiple combinations of control and data bytes for writing into different registers (two bytes each). To read from registers, write an I<sup>2</sup>C read-address to the TSC2013-Q1 device, followed by one or multiple sequential reads from the registers.

The host writes the address of the register to be read in control byte 0 with the register address and read-bit (as described in the previous paragraph). The register address serves as a pointer to the register map where the first read starts. This designated register address is static and a write to a register address does not need to occur again unless a new register address has overwritten it or after a TSC2013-Q1 reset (by a software reset or by the RESET pin).

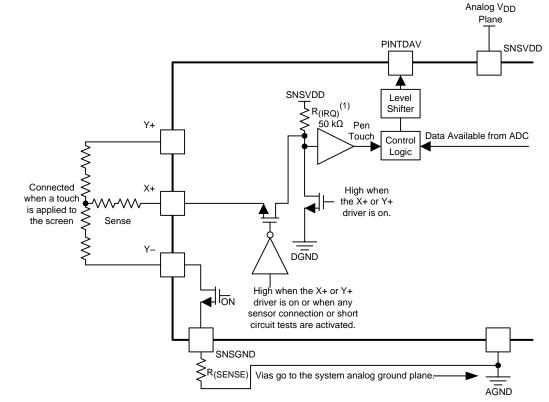

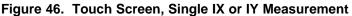

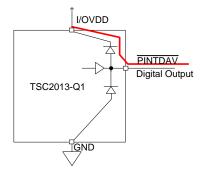

The touch-measurement result goes into the TSC2013-Q1 registers, from which the host may read it at any time. This preprocessing frees up the host in order to allocate resources to more-critical tasks. Two optional signals are also available from the TSC2013-Q1 device to indicate that data are available for the host to read. The PINTDAV pin is a programmable interrupt or status output pin. With the PINTDAV pin programmed as a DAV output, the pin indicates that an ADC conversion has completed and that data are available. With the PINTDAV pin programmed as a PENIRQ output, the pin indicates the detection of a touch on the touch screen. The status register of the TSC2013-Q1 device provides an extended status reading, including the state of the DAV and PENIRQ outputs, without the cost of any dedicated pin. See Figure 14 for a typical application of the TSC2013-Q1 device.

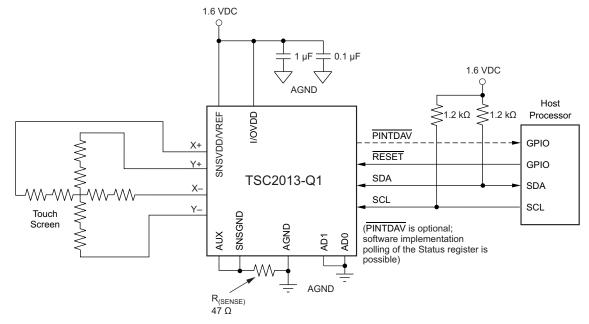

To detect two touches, add an external  $R_{(SENSE)}$  resistor as shown in Figure 14. The value of  $R_{(SENSE)}$  depends on the touch-panel resistance. The ratio between the lowest touch-panel resistance and  $R_{(SENSE)}$  should be approximately 4.5.

## **Overview (continued)**

Figure 14. Typical Circuit Configuration

## 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Touch-Screen Operation

A resistive touch screen operates by applying a voltage across a resistor network and measuring the change in resistance at a given point on the matrix where an input (stylus, pen, or finger) touches the screen. The change in the resistance ratio marks the location on the touch screen.

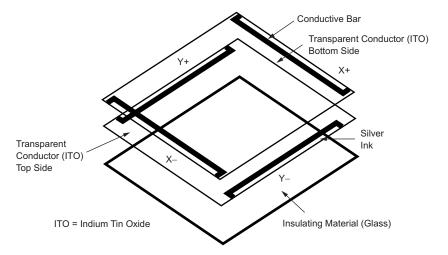

The TSC2013-Q1 device supports resistive 4-wire configurations as shown in Figure 15. The circuit determines location in two coordinate-pair dimensions, although addition of a third dimension for measuring pressure is possible.

## 7.3.2 4-Wire Touch Screen Measurements

Figure 15 shows construction of a typical four-wire touch screen. The screen consists of two transparent resistive layers separated by insulating spacers.

Figure 15. Four-Wire Touch Screen Construction

The four-wire touch-screen panel works by applying a voltage across the vertical or horizontal resistive network.

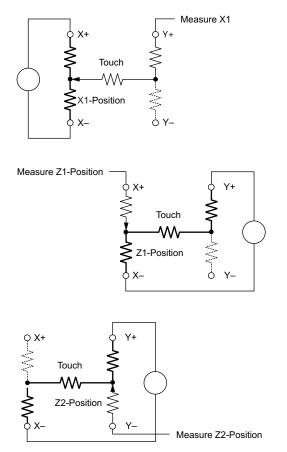

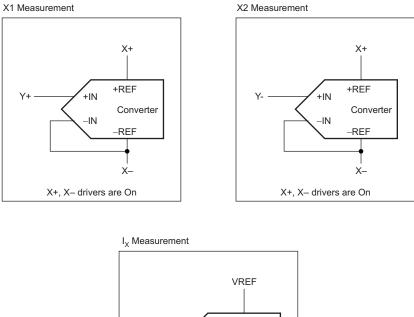

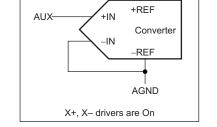

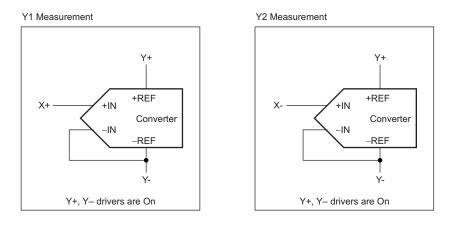

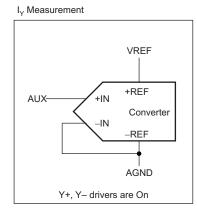

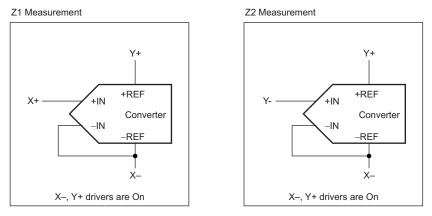

To determine a touch location, the TSC2013-Q1 device provides a set of eight data measurements (X1, X2, IX, Y1, Y2, IY, Z1, and Z2). Figure 17 through Figure 19 show the internal ADC configurations. Taking an X1 measurement involves activating the X+ and X- drivers and digitizing the voltage at Y+. The  $R_{(SENSE)}$  resistor must be connected as shown in Figure 14. The SNSGND and AUX pins connect to one end of  $R_{(SENSE)}$ , and the other end connects to the AGND pin.

The TSC2013-Q1 device can also measure touch pressure (Z). To determine a pen or finger touch, determination of the pressure of the *touch* is required. Generally, having very high performance for this test is not necessary. Therefore, TI recommends 10-bit resolution mode. Several different ways of performing this measurement are available. The TSC2013-Q1 device supports two methods. The first method requires knowing the X-plate resistance, the measurement of X1, and two additional cross-panel measurements (Z2 and Z1) of the touch screen (see Figure 16). Equation 1 calculates the touch resistance ( $R_{(TOUCH)}$ ).

$$R_{(TOUCH)} = R_{X(PLATE)} \times \frac{X1}{4096} \times \left(\frac{Z2}{Z1} - 1\right)$$

(1)

The second method requires knowing both the X-plate and Y-plate resistance, and the measurement of X1, Y1, and Z1. Equation 2 also calculates the touch resistance.

$$R_{(TOUCH)} = \frac{R_{X(PLATE)}}{4096} \left(\frac{4096}{Z1} - 1\right) - R_{Y(PLATE)} \times \left(1 - \frac{Y1}{4096}\right)$$

(2)

## Feature Description (continued)

Figure 16. Pressure Measurement

## Feature Description (continued)

Figure 17. X-Coordinate Differential-Triplet Measurement (X1, X2, IX)

## Feature Description (continued)

Figure 18. Y-Coordinate-Differential-Triplet Measurement (Y1, Y2, IY)

Figure 19. Z-Measurement (Z1, Z2)

When touching or pressing the touch panel with the drivers to the panel turned on, the voltage across the touch panel often overshoots and then slowly settles down (decays) to a stable DC value. This effect is a result of mechanical bouncing caused by vibration of the top-layer sheet of the touch panel when pressing the panel. Without accounting for this settling time, the converted value is in error. Therefore, introducing a delay between the time the driver for a particular measurement is turned on and the time a measurement is made is necessary.

Copyright © 2014, Texas Instruments Incorporated

## Feature Description (continued)

In some applications, external capacitors may be required across the touch screen for filtering noise picked up by the touch screen (such as noise generated by the LCD panel or back-light circuitry). The value of these capacitors provides a low-pass filter to reduce noise, but causes an additional settling-time requirement when the panel is touched.

The TSC2013-Q1 device offers several solutions to this problem. A programmable delay time is available that sets the delay between turning the drivers on and making a conversion. The TSC2013-Q1 device uses this delay, referred to as the *panel voltage-stabilization time*, in some of the device modes. In other modes, commands can cause the TSC2013-Q1 device to turn on the drivers only without performing a conversion. Issuing the command to perform a conversion occurs after allowing sufficient stabilization time.

The TSC2013-Q1 touch-screen interface can measure different data sets. Determination of these measurements is possible under three different modes of the ADC:

- TSMode1: conversion controlled by the TSC2013-Q1 device and initiated by the touchscreen controller (TSC)

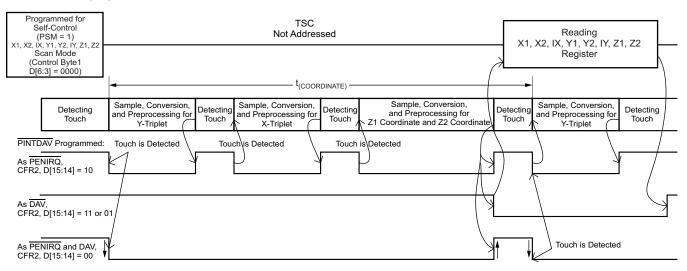

- <u>TSMode</u>2: conversion controlled by the TSC2013-Q1 device and initiated by the host responding to the PENIRQ signal

- TSMode3: conversion completely controlled by the host processor

### 7.3.3 Analog-to-Digital Converter

Figure 20 shows the analog inputs of the TSC2013-Q1 device. A multipexer provides the analog inputs (X, Y, and Z touch panel coordinates and auxiliary inputs) to the successive-approximation register (SAR) analog-todigital converter (ADC). The basis of ADC architecture is capacitive redistribution architecture, which inherently includes a sample-and-hold function.

(1) Untrimmed resistor; see the typical value in the table.

## Figure 20. Simplified Diagram of the Analog Input Section

## Feature Description (continued)

A unique configuration of low on-resistance switches allows an unselected ADC input channel to provide power and an accompanying pin to provide ground for driving the touch panel. By maintaining a differential input to the converter and a differential reference input architecture, negating errors caused by the on-resistance of the driver switches is possible.

Two ADC-control registers control the ADC. Several modes of operation are possible, depending on the bits set in the control registers. Programming of channel selection, scan operation, preprocessing, resolution, and conversion rate is through these registers. The following sections outline these modes for each type of analog input. The appropriate result register stores the conversion results.

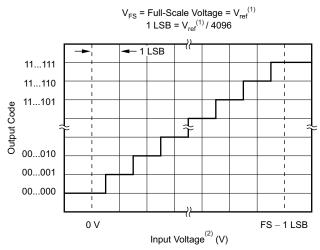

### 7.3.3.1 Data Format

The TSC2013-Q1 output data are in straight binary format as shown in Figure 21. Figure 21 shows the ideal output code for the given input voltage and does not include the effects of offset, gain, or noise.

- (1) Reference voltage at converter: +REF (–REF). See Figure 20.

- (2) Input voltage at converter, after multiplexer: +IN (–IN). See Figure 20.

Figure 21. Ideal Input Voltages and Output Codes

### 7.3.3.2 Reference

The TSC2013-Q1 device uses an external voltage reference applied to the SNSVDD/VREF pin. Using the SNSVDD/VREF pin as the reference voltage is possible because the upper reference voltage range is the same as the supply-voltage range.

### 7.3.3.3 Variable Resolution

The TSC2013-Q1 device provides either 10-bit or 12-bit resolution for the ADC. Lower resolution is often practical for measuring slow-changing signals such as touch pressure. Performing the conversions at lower resolution reduces the amount of time required for the ADC to complete the conversion process which also lowers power consumption.

## 7.3.3.4 Conversion Clock and Conversion Time

The TSC2013-Q1 device contains an internal clock (oscillator) that drives the internal state machines that perform the many functions of the part. This clock is divided down to provide a conversion clock for the ADC. The setting for the division ratio of this clock is in the ADC control register (see Configuration Register 0 (address = 0) [reset = 4000h for read; 0000h for write]). The ability to change the conversion clock rate allows the user to select the optimal values for resolution, speed, and power dissipation. Using the 4-MHz (oscillator) clock directly as the ADC clock (when the CL[1:0] bit is set to 0) limits the ADC resolution to 10 bits. Using higher resolutions at this speed does not result in more accurate conversions. Twelve-bit resolution requires that the CL bits 1 and 0 are set to 0 and 1, or 1 and 0 (respectively).

Copyright © 2014, Texas Instruments Incorporated

#### TSC2013-Q1 SLVSC89A – JUNE 2014 – REVISED JULY 2014

## Feature Description (continued)

Regardless of the conversion clock speed, the internal clock runs nominally at 3.8 MHz at a 3-V supply (SNSVDD) and slows down to 3.6 MHz at a 1.6-V supply. The conversion time of the TSC2013-Q1 device depends on several functions. The conversion clock speed plays an important role in the time required for a conversion to complete. However, proper sampling of the signal requires a certain number of internal clock cycles. Moreover, additional times (such as the panel voltage-stabilization time), can add significantly to the time it takes to perform a conversion. Conversion time can vary depending on the mode of use of TSC2013-Q1 device. This data sheet makes use of internal and conversion clock cycles throughout as the units used to describe the amount of time that many functions take. Take these times into account when considering the total system design.

## 7.3.3.5 Touch Detect

The PINTDAV pin can be programmed to generate an interrupt to the host. Figure 22 shows an example for a typical screen-touch situation. While in the power-down mode, the Y- driver is on and connects to GND. The internal pen-touch signal depends on whether or not the X+ input is low. A touch on the panel pulls the X+ input to ground through the touch screen and sets the internal pen-touch output to low because of the detection on the current path through the panel to ground, which initiates an interrupt to the processor. During the measurement cycles for X and Y-position, the device disconnects the X+ input, which eliminates any leakage current from the pullup resistor flowing through the touch screen, thus causing no errors.

(1) Untrimmed resistor; see the typical value in the table.

Figure 22. Example of a Pen-Touch Induced Interrupt via the PINTDAV Pin

Copyright © 2014, Texas Instruments Incorporated

## Feature Description (continued)

In modes where the TSC2013-Q1 device must detect whether or not a touch remains on the screen (for example, when doing a pen-touch-initiated X, Y, and Z conversion), the TSC2013-Q1 device must reset the drivers to connect the  $R_{(IRQ)}$  resistor again. Because of the high value of this pullup resistor, any capacitance on the touch screen inputs causes a long delay time, and may prevent the detection from occurring correctly. To prevent this possible delay, the TSC2013-Q1 device has a circuit that allows *prechargingd* any screen capacitance, so that the pullup resistor must not be the only source for the charging current. The setting for the time allowed for this precharge, as well as the time needed to sense if the screen touch remains, is in the configuration register.

This configuration underscores the need to use the minimum possible capacitor values on the touch-screen inputs. Capacitors can be used to reduce noise, but capacitors with too large a value increase the required precharge and sense times, as well as the panel voltage-stabilization time.

## 7.3.3.6 Preprocessing

The TSC2013-Q1 device offers an array of powerful preprocessing operations that reduce unnecessary traffic on the bus and reduce the host processor loading. This reduction is especially critical for the serial interface because of the slow bus speed and the high CPU bandwidth required for I<sup>2</sup>C communication.

All data-acquisition tasks are looking for specific data that meet certain criteria. Many of these tasks fall into a predefined range, while other tasks may be looking for a value in a noisy environment. If the host processor is to retrieve all these data for processing, the limited bus bandwidth quickly saturates, along with the host processor processing capability. In any case, reserving the host processor for more critical tasks rather than routine work is always necessary.

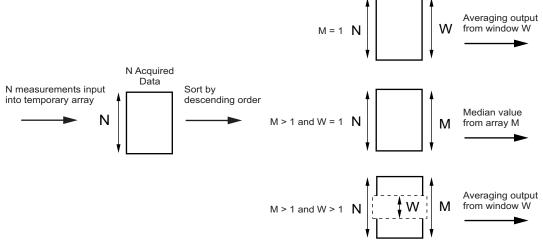

The preprocessing unit consists of two main functions which result in the combined MAV (median and averaging-value) filter: the median value filter (MVF) and the averaging-value filter (AVF).

### 7.3.3.6.1 Preprocessing—Median Value Filter and Averaging Value Filter

The first preprocessing function, a combined MAV filter, can operate independently as a median value filter (MVF), an averaging value filter (AVF), and a combined filter (MAV filter).

If the acquired signal source is noisy because of the digital switching circuit, evaluating the data without noise may be necessary. In this case, the median value filter (MVF) operation helps to discard noise. The first action is sorting the array of N converted results. The return value is either the middle (median value) of an array of M converted results, or the average value of a window size of W of converted results:

- **N** = the total number of converted results used by the MAV filter

- **M** = the median value filter size programmed

- **W** = the averaging window size programmed

If M is equal to 1, then N is equal to W. A special case is W equal to 1, which indicates a bypassed MAV filter. Otherwise, if W is greater than 1, averaging is the only function performed on these converted results. In either case, the return value is the averaged value of window size W of converted results.

If M is greater than 1 and W is equal to 1, then N is equal to M, meaning the only operating filter is the median value filter. The return value is the middle position converted result from the array of M converted results.

If M is greater than 1 and W is greater than 1, then N is equal to M. In this case, W is less than M. The return value is the averaged value of middle portion W of converted results out of the array of M converted results. Because the value of W is an odd number in this case, the calculation of the averaging value counts the middle-position converted result twice (averaging a total of W + 1 converted results).

## Feature Description (continued)

| M1 | МО | MEDIAN VALUE FILTER<br>M = | POSSIBLE AVERAGING WINDOW SIZE<br>W = |

|----|----|----------------------------|---------------------------------------|

| 0  | 0  | 1                          | 1, 4, 8, 16                           |

| 0  | 1  | 3                          | 1                                     |

| 1  | 0  | 7                          | 1, 3                                  |

| 1  | 1  | 15                         | 1, 3, 7                               |

## Table 1. Median Value Filter-Size Selection

## Table 2. Averaging Value Filter-Size Selection

|    |    |                              | ILTER SIZE SELECTION |  |  |

|----|----|------------------------------|----------------------|--|--|

| W1 | WO | M = 1 (Averaging Only) M > 1 |                      |  |  |

| 0  | 0  | 1                            | 1                    |  |  |

| 0  | 1  | 4                            | 3                    |  |  |

| 1  | 0  | 8                            | 7                    |  |  |

| 1  | 1  | 16                           | Reserved             |  |  |

The device uses the default MVF setting (median value filter with averaging bypassed) for any invalid MAV filter configuration. For example, if M1, M0, W1, and W0 equals 1, 0, 1, and 0 (respectively), the MAV filter will perform as if it were configured for 1, 0, 0, 0, median filter only with filter size of 7, and no averaging. The only exception is when M is greater than 1 and when W1 and W0 equal 1. Avoid using this reserved setting.

| М   | W   | INTERPRETATION          | N = | OUTPUT                                                                   |

|-----|-----|-------------------------|-----|--------------------------------------------------------------------------|

| = 1 | = 1 | Bypass both MAF and AVF | W   | The converted result                                                     |

| = 1 | > 1 | Bypass MVF only         | W   | Average of W converted results                                           |

| > 1 | = 1 | Bypass AVF only         | М   | Median of M converted results                                            |

| > 1 | > 1 | M > W                   | М   | Average of middle W of M converted results with the median counted twice |

The MAV filter is available for all analog inputs including the touch-screen inputs and the AUX measurement.

Figure 23. MAV Filter Operation

## 7.4 Device Functional Modes

## 7.4.1 Conversion Controlled by TSC2013-Q1 and Initiated by TSC2013-Q1 (TSMode 1)

In TSMode 1, before a pen-touch detection is possible, the TSC2013-Q1 device must be programmed with the PSM bit set to 1 and one of two scan modes:

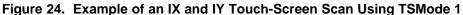

- 1. X-triplet, Y-triplet, Z-scan (converter function select bits C[3:0] = control byte 1 D[6:3] = 0000)

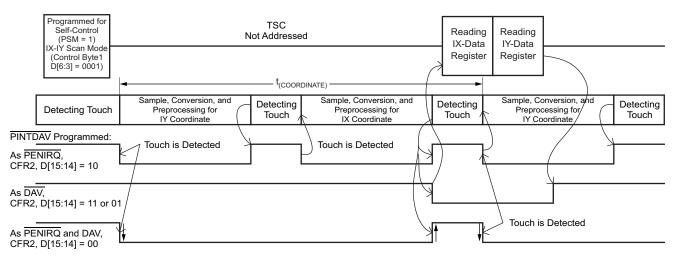

- 2. IX-IY scan (converter function select bits C[3:0] = control byte 1 D[6:3] = 0001).

See Table 7 for more information on the converter function-select bits.

On touching the touch panel, the internal pen-touch signal activates, lowering the PINTDAV output if programmed as PENIRQ. The TSC2013-Q1 device then executes the preprogrammed scan function without a host intervention.

## 7.4.1.1 IX-IY Scan

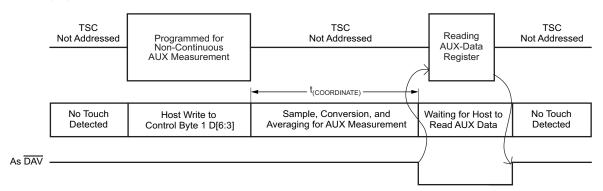

The TSC2013-Q1 device starts up the internal clock. The device then turns on the Y-drivers, and after a programmed panel voltage-stabilization time, the device powers up the ADC and converts the IY coordinate. With preprocessing selected, several conversions can occur. When data preprocessing is complete, a temporary register stores the IY coordinate result.

If the screen touch remains at this time, the device enables the X-drivers and the process repeats but measures the IX coordinate instead, storing the result in a temporary register.

Figure 24 shows a flowchart for this process. The time required to go through this process depends on the selected resolution, internal conversion clock rate, panel voltage-stabilization time, precharge and sense times, and the selection status of preprocessing. Use Equation 3 to calculate the time required to achieve a complete X and Y coordinate (sample set) reading.

$$\mathbf{t}_{(\text{COORDINATE})} = \frac{\mathbf{t}_{(\text{OH1})}}{f_{(\text{OSC})}} + 2 \times \left( \mathbf{t}_{(\text{PVS})} + \mathbf{t}_{(\text{PRE})} + \mathbf{t}_{(\text{SNS})} + \frac{\mathbf{t}_{d(\text{OH1})}}{f_{(\text{OSC})}} \right) + 2 \times \left( \mathbf{N} \times \left[ (\mathbf{B} + 2) \times \frac{f_{(\text{OSC})}}{f_{(\text{ADC})}} + \mathbf{t}_{c(\text{OH})} \right] \times \left[ \frac{1}{f_{(\text{OSC})}} \right] + \left[ \frac{\mathbf{t}_{(\text{PPRO})}}{f_{(\text{OSC})}} \right] \right)$$

where

- $t_{(COORDINATE)}$  = time to complete IX and IY coordinate reading

- N = number of measurements for MAV filter input, as given in Table 3 as N (For no MAV: M1 = M0 = W1 = W0 = 0)

- t<sub>(PVS)</sub> = panel voltage stabilization time, as listed in Table 10

- t<sub>(PRE)</sub> = precharge time, as listed in Table 10

- t<sub>(SNS)</sub> = sense time, as listed in Table 10

- B = number of bits of resolution

- f<sub>(OSC)</sub> = TSC onboard OSC clock frequency. See the *Electrical Characteristics* section for supply frequency (SNSVDD)

- $f_{(ADC)} = ADC$  clock frequency, as listed in Table 10

- t<sub>(OH1)</sub> = overhead time number 1 = 2.5 internal clock cycles

- $t_{d(OH1)}$  = total overhead time for  $t_{(PVS)}$ ,  $t_{(PRE)}$ , and  $t_{(SNS)}$  = 10 internal clock cycles

- t<sub>c(OH)</sub> = total overhead time for A-to-D conversion = 3 internal clock cycles

- t<sub>(PPRO)</sub> = preprocessor preprocessing time as listed in Table 4

(3)

## Table 4. Preprocessing Delay

|      |             | t <sub>(PPRO)</sub> = |                |  |

|------|-------------|-----------------------|----------------|--|

| M =  | W =         | FOR B = 12 BIT        | FOR B = 10 BIT |  |

| 1    | 1, 4, 8, 16 | 2                     | 2              |  |

| 3, 7 | 1           | 28                    | 24             |  |

| 7    | 3           | 31                    | 27             |  |

| 15   | 1           | 31                    | 29             |  |

| 15   | 3           | 34                    | 32             |  |

| 15   | 7           | 38                    | 36             |  |

## 7.4.1.2 X-Triplet, Y-Triplet, Z-Scan

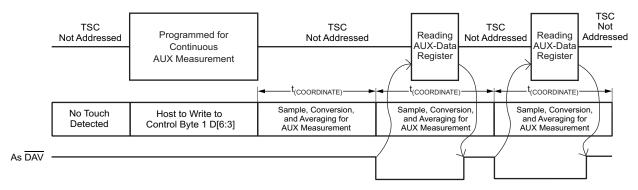

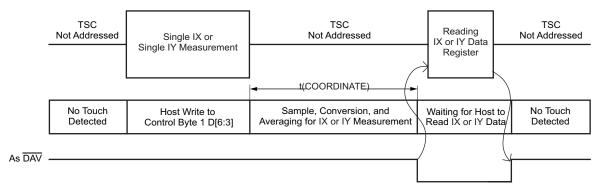

The TSC2013-Q1 device starts up the internal clock. The device then turns on the Y-drivers, and after a programmed panel voltage-stabilization time, powers up the ADC and converts the Y-triplet. With preprocessing selected, several conversions can occur. When data preprocessing is complete, temporary registers store the Y-triplet results.