# TSL2584TSV Light-to-Digital Device

## **General Description**

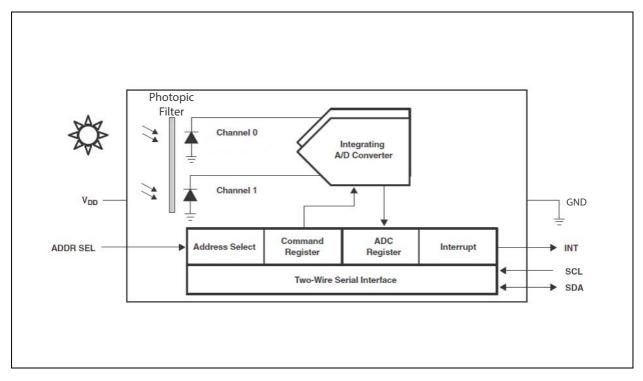

The TSL2584TSV is a very-high sensitivity light-to-digital converter that transforms light intensity into a digital signal output capable of direct l<sup>2</sup>C interface. The device combines one broadband photodiode (visible plus infrared), one infrared-responding photodiode, and a photopic infrared-blocking filter on a single CMOS integrated circuit. Two integrating ADCs convert the photodiode currents into a digital output that represents the irradiance measured on each channel. This digital output can be input to a microprocessor where illuminance (ambient light level) in lux is derived using an empirical formula to approximate the human eye response. The TSL2584TSV supports a traditional level style interrupt that remains asserted until the firmware clears it.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of TSL2584TSV, Light-to-Digital Device are listed below:

Figure 1: Added Value of Using TSL2584TSV

| Benefits                               | Features                                                                                                                                                                           |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Approximates Human Eye Response        | Dual Diode with Photopic Filter                                                                                                                                                    |

| Flexible Operation                     | Programmable Analog Gain and Integration Time                                                                                                                                      |

| Suited for Operation Behind Dark Glass | • 1,000,000: 1 Dynamic Range                                                                                                                                                       |

| Low Operating Overhead                 | <ul> <li>Programmable Upper and Lower Thresholds</li> <li>Programmable Persistence Filter</li> </ul>                                                                               |

| Low Power                              | <ul> <li>3.0 μA Sleep State</li> </ul>                                                                                                                                             |

| Industry standard two-wire interface   | <ul> <li>I<sup>2</sup>C Fast Mode Compatible Interface         <ul> <li>Data Rates up to 400 kbit/s</li> <li>Input Voltage Levels Compatible with 1.8–V Bus</li> </ul> </li> </ul> |

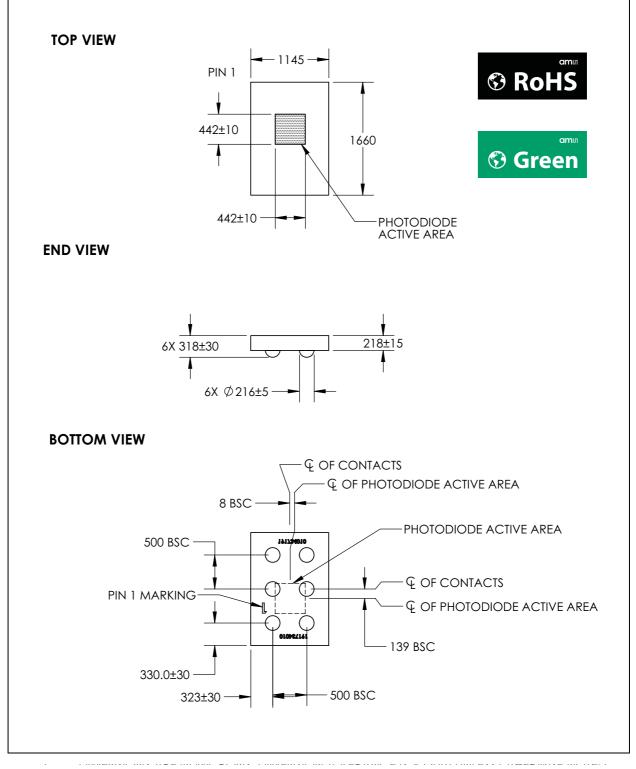

| Ultra-Small foot-print                 | <ul> <li>1.145 mm x 1.660 mm TSV (Through Silicon Via)</li> <li>0.218 mm height w/o solder balls</li> </ul>                                                                        |

| Unlimited Manufacturing Floor Life     | MSL1 Rated                                                                                                                                                                         |

## Applications

The TSL2584TSV applications include:

- Display Backlight Control

- Keyboard Illumination Control

- Printer Paper Detection

- Medical Diagnostics

## **Block Diagram**

The functional blocks of this device for reference are shown below:

Figure 2: TSL2584TSV Block Diagram

# amu

# **Detailed Description**

The TSL2584TSV contains two integrating analog-to-digital converters (ADC) that integrate currents from two photodiodes. Integration of both channels occurs simultaneously. Upon completion of the conversion cycle, the conversion result is transferred to the Channel 0 and Channel 1 data registers. The transfers are double-buffered to ensure that the integrity of the data is maintained. After the transfer, the device automatically begins the next integration cycle.

Communication with the device is accomplished through a standard, two-wire I<sup>2</sup>C serial bus. Consequently, the TSL2584TSV can be easily connected to a microcontroller or embedded controller. No external circuitry is required for signal conditioning. Because the output of the device is digital, the output is effectively immune to noise when compared to an analog signal.

The TSL2584TSV also supports an interrupt feature that simplifies and improves system efficiency by eliminating the need to poll a sensor for a light intensity value. The primary purpose of the interrupt function is to detect a meaningful change in light intensity. The concept of a meaningful change can be defined by the user both in terms of light intensity and time, or persistence, of that change in intensity. The device has the ability to define thresholds above and below the current light level. An interrupt is generated when the value of a conversion exceeds either of these limits.

## **Pin Assignment**

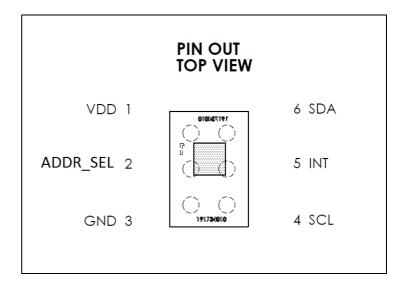

### The TSL2584TSV pin assignments are described below.

Figure 3: Pin Diagram

Package TSV - 6 Lead Through - Silicon VIA (Top View): Package drawing is not to scale.

Figure 4: Pin Description

| Pin Number | Pin Name        | Description                                              |

|------------|-----------------|----------------------------------------------------------|

| 1          | V <sub>DD</sub> | Supply voltage                                           |

| 2          | ADDR_SEL        | Address select – three-state.                            |

| 3          | GND             | Power supply ground. All voltages are referenced to GND. |

| 4          | SCL             | I <sup>2</sup> C serial clock input terminal             |

| 5          | INT             | Interrupt — open drain output (active low).              |

| 6          | SDA             | I <sup>2</sup> C serial data I/O terminal                |

# Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5: Absolute Maximum Ratings

| Parameter                                    | Min   | Max | Units | Comments                             |

|----------------------------------------------|-------|-----|-------|--------------------------------------|

| Supply voltage, V <sub>DD</sub>              |       | 3.8 | V     | All voltages are with respect to GND |

| Output terminal voltage V <sub>O</sub>       | -0.5  | 3.8 | V     |                                      |

| Output terminal current I <sub>O</sub>       | -1    | 20  | mA    |                                      |

| Storage temperature range, T <sub>STRG</sub> | -40   | 85  | °C    |                                      |

| ESD tolerance, human body model              | ±2000 |     | V     |                                      |

# **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

## Figure 6:

**Recommended Operating Conditions**

| Symbol          | Parameter                      | Min | Тур | Max | Units |

|-----------------|--------------------------------|-----|-----|-----|-------|

| V <sub>DD</sub> | Supply voltage                 | 2.7 | 3   | 3.6 | V     |

| T <sub>A</sub>  | Operating free-air temperature | -40 |     | 85  | °C    |

Figure 7:

Operating Characteristics, V<sub>DD</sub>=3V, T<sub>A</sub>=25°C (unless otherwise noted)

| Symbol            | Parameter                           | Conditions                                    | Min  | Тур | Max  | Units |

|-------------------|-------------------------------------|-----------------------------------------------|------|-----|------|-------|

|                   |                                     | Active                                        |      | 175 | 250  |       |

| I <sub>DD</sub>   | Supply Current                      | Sleep state - no l <sup>2</sup> C<br>activity |      | 3   | 10   | μA    |

| V <sub>OL</sub>   | INT, SDA output low voltage         | 3mA sink current                              | 0    |     | 0.4  | V     |

| VOL               | int, SDA output low voltage         | 0                                             |      | 0.6 | v    |       |

| I <sub>LEAK</sub> | Leakage current, SDA, SCL, INT pins |                                               | -5   |     | 5    | μΑ    |

| V <sub>IH</sub>   | SCL, SDA input high voltage         |                                               | 1.25 |     |      | V     |

| V <sub>IL</sub>   | SCL, SDA input low voltage          |                                               |      |     | 0.54 | V     |

### Figure 8:

## ALS Characteristics, V<sub>DD</sub>=3V, T<sub>A</sub>=25°C, AGAIN=16x, AEN=1(unless otherwise noted)<sup>(1)</sup>

| Parameter                                       | Conditions                                                                                     | Channel    | Min       | Тур         | Max            | Units                            |

|-------------------------------------------------|------------------------------------------------------------------------------------------------|------------|-----------|-------------|----------------|----------------------------------|

| Dark ADC count<br>value                         | E <sub>e</sub> = 0, AGAIN = 111x,<br>ITIME=0xB6 (200ms)                                        | CH0<br>CH1 | 0<br>0    | 1<br>1      | 3<br>3         | counts                           |

| ADC integration time step size                  | ATIME = 0xFF                                                                                   |            | 2.58      | 2.73        | 2.90           | ms                               |

| ADC integration<br>time steps <sup>(4)</sup>    |                                                                                                |            | 1         |             | 256            | steps                            |

| Full scale ADC count value                      | ITIME = 0xF6 (27ms)<br>ITIME = 0x6C (400ms)                                                    |            |           |             | 37887<br>65535 | counts                           |

| ADC count value                                 | White light<br>$E_e = 218 \mu W/cm^2$<br>ITIME = 0xF6 (27ms) <sup>(2)</sup>                    | CH0<br>CH1 | 2480      | 3100<br>223 | 3720           | counts                           |

| ADC Count value                                 | $λ_p = 850 \text{ nm}$<br>$E_e = 220 \mu\text{W/cm}^2$ ,<br>ITIME = 0xF6 (27ms) <sup>(3)</sup> | CH0        |           |             | 400            | counts                           |

| ADC count value<br>ratio: CH1/CH0               | White light <sup>(2)</sup>                                                                     |            | 0.036     | 0.072       | 0.108          |                                  |

| R <sub>e</sub><br>Irradiance<br>responsivity    | White light,<br>ITIME = 0xF6 (27 ms) <sup>(2)</sup>                                            | CH0<br>CH1 | 11.4      | 14.2<br>1.0 | 17.1           | counts/<br>(µW/cm <sup>2</sup> ) |

|                                                 | IGAIN = 8x                                                                                     | CH0<br>CH1 | 7<br>7    | 8<br>8      | 9<br>9         |                                  |

| Gain scaling,<br>relative to 1x gain<br>setting | IGAIN = 16x                                                                                    | CH0<br>CH1 | 15<br>15  | 16<br>16    | 17<br>17       | x                                |

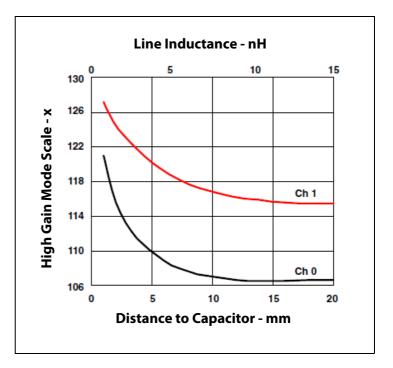

|                                                 | IGAIN = 111x<br>Decoupling capacitor 25 mm<br>from VDD pin <sup>(5)</sup>                      | CH0<br>CH1 | 97<br>100 | 107<br>115  | 115<br>125     |                                  |

#### Note(s) and/or Footnote(s):

1. Optical measurements are made using small-angle incident radiation from light-emitting diode optical sources. Visible white LEDs and infrared 850 nm LEDs are used for final product testing for compatibility with high-volume production.

2. The white LED irradiance is supplied by a white light-emitting diode with a nominal color temperature of 4000 K.

- 3. The 850 nm irradiance  $E_e$  is supplied by a GaAs light-emitting diode with the following typical characteristics: peak wavelength  $\lambda_p = 850$  nm and spectral halfwidth  $\Delta\lambda$ <sup>1/2</sup> = 42 nm.

- 4. The integration time  $T_{intr}$  is dependent on the internal oscillator frequency ( $f_{OSC}$ ) and on the number of integration cycles (ITIME) in the Timing Register as described in the register section. For nominal  $f_{OSC}$  = 750 kHz, nominal Tint = 2.7 ms x ITIME.

5. 111x gain is affected by the line inductance between the VDD pin and the decoupling capacitor.

# **Timing Characteristics**

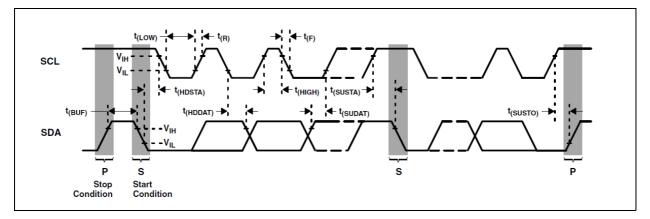

#### The timing characteristics of TSL2584TSV are given below.

Figure 9:

AC Electrical Characteristics,  $V_{DD} = 3 V$ ,  $T_A = 25 °C$  (unless otherwise noted)

| Parameter <sup>(1)</sup> | Description                                                                                     | Min   | Max | Units |

|--------------------------|-------------------------------------------------------------------------------------------------|-------|-----|-------|

| t <sub>(CONV)</sub>      | Conversion time                                                                                 | 2.7   | 688 | ms    |

| f <sub>(SCL)</sub>       | Clock frequency                                                                                 | 0     | 400 | kHz   |

| t <sub>(BUF)</sub>       | Bus free time between start and stop condition                                                  | 1.3   |     | μs    |

| t <sub>(HDSTA)</sub>     | Hold time after (repeated) start condition.<br>After this period, the first clock is generated. | 0.6   |     | μs    |

| t <sub>(SUSTA)</sub>     | Repeated start condition setup time                                                             | 0.6   |     | μs    |

| t <sub>(SUSTO)</sub>     | Stop condition setup time                                                                       | 0.6   |     | μs    |

| t <sub>(HDDAT)</sub>     | Data hold time                                                                                  | 0.043 | 0.9 | μs    |

| t <sub>(SUDAT)</sub>     | Data setup time                                                                                 | 100   |     | ns    |

| t <sub>(LOW)</sub>       | SCL clock low period                                                                            | 1.3   |     | μs    |

| t <sub>(HIGH)</sub>      | SCL clock high period                                                                           | 0.6   |     | μs    |

| t <sub>F</sub>           | Clock/data fall time                                                                            |       | 300 | ns    |

| t <sub>R</sub>           | Clock/data rise time                                                                            |       | 300 | ns    |

| C <sub>i</sub>           | Input pin capacitance                                                                           |       | 10  | pF    |

#### Note(s) and/or Footnote(s):

1. Specified by design and characterization; not production tested.

## **Timing Diagrams**

Figure 10: Parameter Measurement Information

# amu

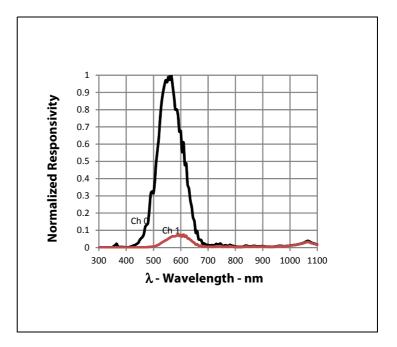

# Typical Operating Characteristics

Figure 11: Spectral Responsivity

**Spectral Responsivity:** Two channel response allows for tunable illuminance (lux) calculation regardless of transmissivity of glass.

Figure 12: 111x Gain Scale vs. Line Inductance

**111x Gain Scale vs. Line Inductance:** High gain mode (111x) dependency on the line inductance between the VDD pin and the decoupling capacitor.

## **Digital Interface**

Interface and control of the device is accomplished through a two-wire serial interface to a set of registers that provide access to device control functions and output data. The serial interface is compatible with the l<sup>2</sup>C bus, Fast-Mode. The device offers three slave addresses that are selectable via an external pin (ADDR SEL). The slave address options are shown in Figure 13.

Figure 13: Slave Address Selection

| ADDR SEL Terminal Level | 7-BIT Sla | ve Address |

|-------------------------|-----------|------------|

| GND                     | 0101001   | 0x29       |

| Float                   | 0111001   | 0x39       |

| V <sub>DD</sub>         | 1001001   | 0x49       |

Note(s) and/or Footnote(s):

1. The slave addresses are 7 bits. A read/write bit should be appended to the slave address by the master device to properly communicate with the slave device.

# amu

## **Register Description**

The device is controlled and monitored by sixteen registers and a command register accessed through the serial interface. These registers provide for a variety of control functions and can be read to determine results of the ADC conversions. The register set is summarized in Figure 14.

Figure 14: Register Map

| Address | Register Name | R/W             | Register Function                      |

|---------|---------------|-----------------|----------------------------------------|

|         | COMMAND       | W               | Specifies register address             |

| 00h     | CONTROL       |                 | Control of basic functions             |

| 01h     | TIMING        |                 | Integration time/gain control          |

| 02h     | INTERRUPT     |                 | Interrupt control                      |

| 03h     | THLLOW        | R/W             | Low byte of low interrupt threshold    |

| 04h     | THLHIGH       | - <b>Г</b> / VV | High byte of low interrupt threshold   |

| 05h     | THHLOW        |                 | Low byte of high interrupt threshold   |

| 06h     | тнннідн       |                 | High byte of high interrupt threshold  |

| 07h     | ANALOG        |                 | Analog control register                |

| 12h     | ID            |                 | Part number / Rev ID                   |

| 14h     | DATAOLOW      |                 | ADC Channel 0 - LOW data register      |

| 15h     | DATAOHIGH     |                 | ADC Channel 0 - HIGH data register     |

| 16h     | DATA1LOW      | R               | ADC Channel 1- LOW data register       |

| 17h     | DATA1HIGH     |                 | ADC Channel 1 - HIGH data register     |

| 18h     | TIMERLOW      |                 | Manual integration timer LOW register  |

| 19h     | TIMERHIGH     |                 | Manual integration timer HIGH register |

| 1Eh     | ID2           | R/W             | Supplemental identification            |

The mechanics of accessing a specific register depends on the specific  $l^2C$  protocol used. See the section on  $l^2C$  protocols, above. In general, the Command Register is written first to specify the specific control/status register for following read/write operations.

## **Command Register**

The Command Register specifies the address of the target register for subsequent read and write operations and contains eight bits as described in Figure 15. The command register defaults to 00h at power on.

Figure 15: Command Register

| 7   | 6     | 5      | 4       | 3 | 2 | 1 | 0 |

|-----|-------|--------|---------|---|---|---|---|

| CMD | TRANS | ACTION | ADDRESS |   |   |   |   |

| Fields      | Bits    | Description (Reset - 00h)                                                                                                                                                              |                                          |         |  |  |  |  |  |  |    |                                       |

|-------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------|--|--|--|--|--|--|----|---------------------------------------|

| CMD         | 7       | Select command register. Must write as                                                                                                                                                 | s 1 when addressing COMMAND register.    |         |  |  |  |  |  |  |    |                                       |

|             |         | Select type of transaction to follow in s                                                                                                                                              | subsequent data transfers:               |         |  |  |  |  |  |  |    |                                       |

|             |         | FIELD VALUE                                                                                                                                                                            | DESCRIPTION                              |         |  |  |  |  |  |  |    |                                       |

|             |         | 00                                                                                                                                                                                     | Repeated byte protocol transaction       |         |  |  |  |  |  |  |    |                                       |

| TRANGACTION | <i></i> |                                                                                                                                                                                        |                                          | <i></i> |  |  |  |  |  |  | 01 | Auto - increment protocol transaction |

| TRANSACTION | 6:5     | 10                                                                                                                                                                                     | Reserved - Do not use                    |         |  |  |  |  |  |  |    |                                       |

|             |         | 11                                                                                                                                                                                     | Special function - See description below |         |  |  |  |  |  |  |    |                                       |

|             |         | Transaction type 00 will repeatedly read the same register with each data access.<br>Transaction type 01 will provide an auto-increment function to read successive<br>register bytes. |                                          |         |  |  |  |  |  |  |    |                                       |

| Fields  | Bits |                                                                                                                                                                                                                                                           | Description                 | n (Reset - 00h)                                                                                                                                                                                                                             |  |  |  |

|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|         |      | Register Address/Special Function. This field selects the specific control or st register for following write and read commands according to Figure 14. Whe TRANSACTION field is set to 11b, this field specifies a special command funct outlined below. |                             |                                                                                                                                                                                                                                             |  |  |  |

|         |      | FIELD VALUE                                                                                                                                                                                                                                               | SPECIAL FUNCTION            | DESCRIPTION                                                                                                                                                                                                                                 |  |  |  |

|         |      | 00000                                                                                                                                                                                                                                                     | Reserved                    | Reserved                                                                                                                                                                                                                                    |  |  |  |

|         |      | 00001                                                                                                                                                                                                                                                     | Interrupt clear             | Clear any pending interrupt and is a write-once-to-clear bit                                                                                                                                                                                |  |  |  |

| ADDRESS | 4:0  | 00010                                                                                                                                                                                                                                                     | Stop manual<br>integration  | When the Timing Register is set to 00h, a<br>Byte command with the ADDRESS field<br>set to 0010b will stop a manual<br>integration. The actual length of the<br>integration cycle may be read in the<br>MANUAL INTEGRATION TIMER Register.  |  |  |  |

|         |      | 00011                                                                                                                                                                                                                                                     | Start manual<br>integration | When the Timing Register is set to 00h, a<br>Byte command with the ADDRESS field<br>set to 0011b will start a manual<br>integration. The actual length of the<br>integration cycle may be read in the<br>MANUAL INTEGRATION TIMER Register. |  |  |  |

|         |      | x11xx                                                                                                                                                                                                                                                     | Reserved                    | Reserved                                                                                                                                                                                                                                    |  |  |  |

## Control Register (00h)

The Control Register is used primarily to power the device up and down as shown in Figure 16.

Figure 16: Control Register.

| 7    | 6        | 5 | 4         | 3    | 2    | 1      | 0     |

|------|----------|---|-----------|------|------|--------|-------|

| Rese | Reserved |   | ADC_VALID | Rese | rved | ADC_EN | POWER |

| Field     | Bits | Description (Reset - 00h)                                                                                                                               |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved  | 7:6  | Reserved. Write as 0.                                                                                                                                   |

| ADC_INTR  | 5    | ADC Interrupt. Read only. Indicates that the device is asserting an interrupt.                                                                          |

| ADC_VALID | 4    | ADC Valid. Read only. Indicates that the ADC Channel has completed an integration cycle.                                                                |

| Reserved  | 3:2  | Reserved. Write as 0.                                                                                                                                   |

| ADC_EN    | 1    | ADC Enable. This field enables the two ADC Channels to begin integration.<br>Writing a 1 activates the ADC Channels, and writing a 0 disables the ADCs. |

| POWER     | 0    | Power On. Writing a 1 powers on the device, and writing a 0 turns it off.                                                                               |

#### Note(s) and/or Footnote(s):

1. ADC\_EN and POWER must be asserted before the ADC changes will operate correctly. After POWER is asserted, a 2-ms delay is required before asserting ADC\_EN.

2. The device registers should be configured before ADC\_EN is asserted.

## Timing Register (01h)

The Timing Register controls the internal integration time of the ADC Channels in 2.7 ms increments. The TIMING register defaults to 00h at power on.

Figure 17: Timing Register

| 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|

| ITIME |   |   |   |   |   |   |   |

| Field | Bits | Description (Reset = 00h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |          |  |  |  |

|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--|--|--|

|       |      | <ul> <li>Integration Cycles. Specifies the integration time in 2.7-ms intervals. Time is expressed as a 2's complement number. So, to quickly work out the correct value to write: <ul> <li>(Step 1) Determine the number of 2.7-ms intervals required</li> <li>(Step 2) Take the 2's complement.</li> </ul> </li> <li>Example: For a 1 × 2.7-ms interval, 0xFF should be written. For 2 × 2.7-ms intervals, 0xFE should be written. The maximum integration time is 688.5 ms (00000001b).</li> <li>Writing a 0x00 to this register is a special case and indicates manual timing mode. See CONTROL and MANUAL INTEGRATION TIMER Registers for other device options related to manual integration.</li> </ul> |                    |          |  |  |  |

| ITIME | 7:0  | INTEG_CYCLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIME               | VALUE    |  |  |  |

| TTIVE |      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Manual integration | 0000000  |  |  |  |

|       |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.7 ms             | 1111111  |  |  |  |

|       |      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.4 ms             | 1111110  |  |  |  |

|       |      | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51.3 ms            | 11101101 |  |  |  |

|       |      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 99.9 ms            | 11011011 |  |  |  |

|       |      | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 199.8 ms           | 10110110 |  |  |  |

|       |      | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 399.6 ms           | 01101100 |  |  |  |

|       |      | 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 688.5 ms           | 0000001  |  |  |  |

#### Note(s) and/or Footnote(s):

1. The Byte protocol cannot be used when ITIME is greater than 127 (for example ITIME[7] = 1) since the upper bit is set aside for write transactions in the COMMAND register.

## Interrupt Register (02h)

The Interrupt Register controls the extensive interrupt capabilities of the device. The open-drain interrupt pin is active low and requires a pull-up resistor to V<sub>DD</sub> in order to pull high in the inactive state. The Interrupt Register provides control over when a meaningful interrupt will occur. The concept of a meaningful change can be defined by the user both in terms of light intensity and time, or persistence of that change in intensity. The value must cross the threshold (as configured in the Threshold Registers 03h through 06h) and persist for some period of time as outlined in Figure 18.

When a level Interrupt is selected, an interrupt is generated whenever the last conversion results in a value outside of the programmed threshold window. The interrupt is active-low and remains asserted until cleared by writing an 11 in the TRANSACTION field in the COMMAND register.

#### Figure 18: Interrupt Control Register

| 7        | 6         | 5    | 4 | 3 | 2   | 1    | 0 |

|----------|-----------|------|---|---|-----|------|---|

| Reserved | INTR_STOP | INTR |   |   | PER | SIST |   |

| Field     | Bits | Description (Reset = 00h)                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved  | 7    | Reserved. Write as 0.                                                                                                                                                                                                                                                                                                                                                                         |

| INTR_STOP | 6    | Stop ADC Integration on Interrupt. When high, ADC integration will stop<br>once an interrupt is asserted. To resume operation (1) de-assert ADC_EN<br>using CONTROL register, (2) clear interrupt using COMMAND register, and (3)<br>re-assert ADC_EN using CONTROL register.<br><b>Note</b> : Use this bit to isolate a particular condition when the sensor is<br>continuously integrating. |

| INTR      | 5:4  | INTR Control Select. This field determines mode of interrupt logic according to Figure 19, below.                                                                                                                                                                                                                                                                                             |

| PERSIST   | 3:0  | Interrupt Persistence. Controls rate of interrupts to the host processor as shown in Figure 20, below.                                                                                                                                                                                                                                                                                        |

#### Note(s) and/or Footnote(s):

1. Interrupts are based on the value of Channel 0 only.

## Figure 19: Interrupt Control Select

| INTR Field Value | Read Value                |  |  |

|------------------|---------------------------|--|--|

| 00               | Interrupt output disabled |  |  |

| 01               | Level Interrupt           |  |  |

| 10               | Reserved                  |  |  |

| 11               | Reserved                  |  |  |

#### Note(s) and/or Footnote(s):

1. Field value of 11 may be used to test interrupt connectivity in a system or to assist in debugging interrupt service routine software.

Figure 20: Interrupt Persistence Select

| Persist Field Value | Interrupt Persist Function               |

|---------------------|------------------------------------------|

| 0000                | Every ADC cycle generates interrupt      |

| 0001                | Any value outside of threshold range     |

| 0010                | 2 integration time periods out of range  |

| 0011                | 3 integration time periods out of range  |

| 0100                | 4 integration time periods out of range  |

| 0101                | 5 integration time periods out of range  |

| 0110                | 6 integration time periods out of range  |

| 0111                | 7 integration time periods out of range  |

| 1000                | 8 integration time periods out of range  |

| 1001                | 9 integration time periods out of range  |

| 1010                | 10 integration time periods out of range |

| 1011                | 11 integration time periods out of range |

| 1100                | 12 integration time periods out of range |

| 1101                | 13 integration time periods out of range |

| 1110                | 14 integration time periods out of range |

| 1111                | 15 integration time periods out of range |

## Interrupt Threshold Registers (03h-06h)

The Interrupt Threshold Registers store the values to be used as the high and low trigger points for the comparison function for interrupt generation. If the value generated by Channel 0 crosses below or is equal to the low threshold specified, an interrupt is asserted on the interrupt pin. If the value generated by Channel 0 crosses above the high threshold specified, an interrupt is asserted on the interrupt pin. Registers THLLOW and THLHIGH provide the low byte and high byte, respectively, of the lower interrupt threshold. Registers THHLOW and THHHIGH provide the low and high bytes, respectively, of the upper interrupt threshold. The high and low bytes from each set of registers are combined to form a 16-bit threshold value. The interrupt threshold registers default to 00h on power up.

## Figure 21: Interrupt Threshold Registers

| Register | Address | Bits | Description                                    |  |  |

|----------|---------|------|------------------------------------------------|--|--|

| THLLOW   | 3h      | 7:0  | ADC Channel 0 lower byte of the low threshold  |  |  |

| THLHIGH  | 4h      | 7:0  | ADC Channel 0 upper byte of the low threshold  |  |  |

| THHLOW   | 5h      | 7:0  | ADC Channel 0 lower byte of the high threshold |  |  |

| THHHIGH  | 6h      | 7:0  | ADC Channel 0 upper byte of the high threshold |  |  |

#### Note(s) and/or Footnote(s):

1. Since two 8-bit values are combined for a single 16-bit value for each of the high and low interrupt thresholds, the Byte protocol should not be used to write to these registers. Any values transferred by the Byte protocol with the MSB set would be interpreted as the COMMAND field and stored as an address for subsequent read/write operations and not as the interrupt threshold information as desired. The Write Word protocol should be used to write byte-paired registers. For example, the THLLOW and THLHIGH registers (as well as the THHLOW and THHHIGH registers) can be written together to set the 16-bit ADC value in a single transaction.

## Analog Register (07h)

The Analog Register provides eight bits of control to the analog block. These bits control the analog gain settings of the device.

Figure 22: Analog Register

| 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0   |

|---|----------|---|---|---|---|---|-----|

|   | Reserved |   |   |   |   |   | AIN |

| Field    | Bits | Description (Reset = 00h)                                                              |            |  |  |  |

|----------|------|----------------------------------------------------------------------------------------|------------|--|--|--|

| Reserved | 7:2  | Reserved. Write as 0.                                                                  |            |  |  |  |

|          |      | Gain Control. Sets the analog gain of the device according to the following Figure 23. |            |  |  |  |

|          | 1:0  | FIELD VALUE                                                                            | GAIN VALUE |  |  |  |

| GAIN     |      | 00                                                                                     | 1×         |  |  |  |

|          |      | 01                                                                                     | 8×         |  |  |  |

|          |      | 10                                                                                     | 16×        |  |  |  |

|          |      | 11                                                                                     | 111×       |  |  |  |

## ID Register (12h)

The ID Register provides the value for both the part number and silicon revision number for that part number. It is a read-only register whose value never changes.

Figure 23: ID Register

| 7 | 6      | 5 | 4 | 3 | 2  | 1   | 0 |

|---|--------|---|---|---|----|-----|---|

|   | PARTNO |   |   |   | RE | VNO |   |

| Field  | Bits | Description                                   |

|--------|------|-----------------------------------------------|

| PARTNO | 7:4  | Part Number Identification: field value 1001b |

| REVNO  | 3:0  | Revision number identification                |

# ADC Channel Data Registers (14h-17h)

The ADC Channel data are expressed as 16-bit values spread across two registers. The ADC Channel 0 data registers, DATA0LOW and DATA0HIGH provide the lower and upper bytes, respectively, of the ADC value of Channel 0. Registers DATA1LOW and DATA1HIGH provide the lower and upper bytes, respectively, of the ADC value of Channel 1. All Channel data registers are read-only and default to 00h on power up.

Figure 24: ADC Channel Data Registers

| Register  | Address | Bits | Description              |

|-----------|---------|------|--------------------------|

| DATAOLOW  | 14h     | 7:0  | ADC Channel 0 lower byte |

| DATA0HIGH | 15h     | 7:0  | ADC Channel 0 upper byte |

| DATA1LOW  | 16h     | 7:0  | ADC Channel 1 lower byte |

| DATA1HIGH | 17h     | 7:0  | ADC Channel 1 upper byte |

#### Note(s) and/or Footnote(s):

1. The Read Word protocol can be used to read byte-paired registers. For example, the DATA0LOW and DATA0HIGH registers (as well as the DATA1LOW and DATA1HIGH registers) may be read together to obtain the 16-bit ADC value in a single transaction.

The upper byte data registers can only be read following a read to the corresponding lower byte register. When the lower byte register is read, the upper eight bits are strobed into a shadow register, which is read by a subsequent read to the upper byte. The upper register will read the correct value even if additional ADC integration cycles end between the reading of the lower and upper registers.

## Manual Integration Timer Registers (18h-19h)

The Manual Integration Timer Registers provide the number of cycles in 10.9 µs increments that occurred during a manual start/stop integration period. The timer is expressed as a 16-bit value across two registers. See CONTROL and TIMING Registers for further instructions in configuring a manual integration. The maximum time that can be derived without an overflow is 714.3ms.

Figure 25: Manual Integration Timer Registers

| 7 | 6 | 5 | 4    | 3          | 2 | 1 | 0 |

|---|---|---|------|------------|---|---|---|

|   |   |   | 11/1 | <b>IER</b> |   |   |   |

| Register  | Address | Bits | Description (Reset = 00h)           |

|-----------|---------|------|-------------------------------------|

| TIMERLOW  | 18h     | 7:0  | Manual Integration Timer lower byte |

| TIMERHIGH | 19h     | 7:0  | Manual Integration Timer upper byte |

## ID2 Register (1Eh)

The ID2 Register provides the means to identify the device as TSL2584TSV. Although this is a W/R register, it is strongly advised that this register not be written to. Any value written to this register could adversely affect the performance of the device.

Figure 26: ID2 Register

| 7   | 6 | 5 | 4 | 3        | 2 | 1 | 0 |

|-----|---|---|---|----------|---|---|---|

| ID2 |   |   |   | Reserved |   |   |   |

| Field    | Bits | Description                                         |

|----------|------|-----------------------------------------------------|

| ID2      | 7    | This bit will be set (1) for all TSL2584TSV devices |

| Reserved | 6:0  | Reserved                                            |

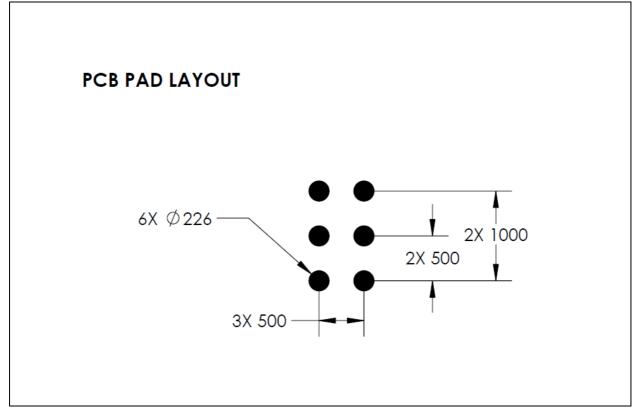

## **PCB Pad Layout**

Figure 27: Suggested TSV Package PCB Layout

#### Note(s) and/or Footnote(s):

1. All linear dimensions are in microns.

2. This drawing is subject to change without notice.

3. Underfill is recommended for PCB assembly.

# Package Drawings & Markings

### Note(s) and/or Footnote(s):

- 1. Dimensions are in microns.

- 2. Dimension tolerance is 25um unless otherwise noted.

- 3. This drawing is subject to change without notice.

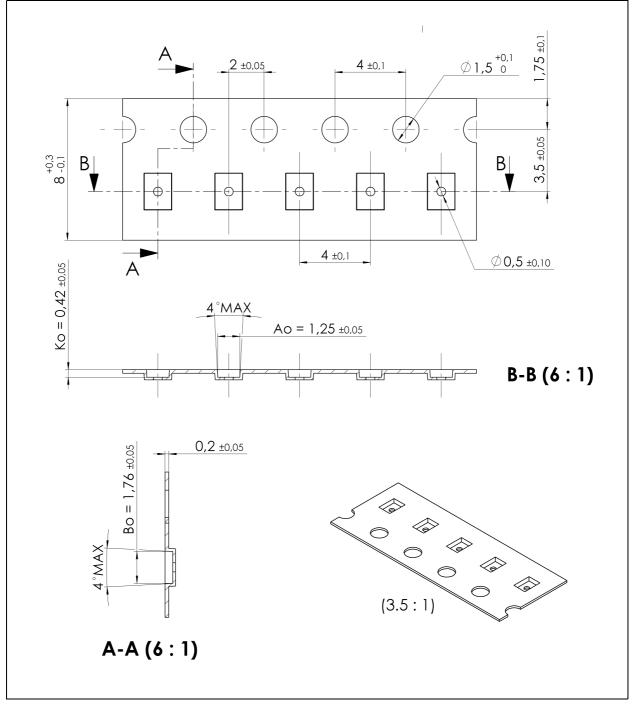

## Tape & Reel Information

Figure 29: TSL2584TSV – Carrier Tape & Reel Information

#### Note(s) and/or Footnote(s):

- 1. All linear dimensions are in millimeters.

- 2. The dimensions in this drawing are for illustration purposes only. Dimensions of an actual carrier may vary slightly.

- 3. Symbols on drawing  $A_0$ ,  $B_0$ , and  $K_0$  are defined in ANSI EIA standard 481-B 2001.

- 4. Each reel is 178 millimeters in diameter and contains 3500 parts.

- 5. Packaging tape and reel conform to the requirements of EIA 481-B.

- 6. In accordance with EIA standard, device pin1 is located next to the sprocket holes in the tape.

- 7. This drawing is subject to change without notice.

# Soldering & Storage Information

## **Soldering Information**

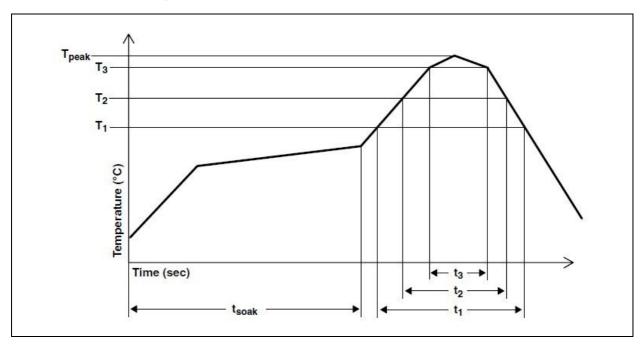

The reflow profile specified here describes expected maximum heat exposure of devices during the solder reflow process of the device on a PCB. Temperature is measured at the top of the device. Devices should be limited to one pass through solder reflow profile. It is recommended after solder reflow that underfill is used for increased robustness.

Figure 30: Solder Reflow Profile

| Symbol            | Parameter                                              | Device               |

|-------------------|--------------------------------------------------------|----------------------|

|                   | Average temperature gradient in preheating             | 2.5 °C/sec           |

| t <sub>soak</sub> | Soak time                                              | 2 to 3 minutes       |

| t <sub>1</sub>    | Time above 217 °C (T <sub>1</sub> )                    | Max 60 sec           |

| t <sub>2</sub>    | Time above 230 °C (T <sub>2</sub> )                    | Max 50 sec           |

| t <sub>3</sub>    | Time above T <sub>peak</sub> - 10 °C (T <sub>3</sub> ) | Max 10 sec           |

| T <sub>peak</sub> | Peak temperature in reflow                             | 260 °C (-0 °C/+5 °C) |

|                   | Temperature gradient in cooling                        | Max -5 °C/sec        |

#### Figure 31: Solder Reflow Profile Graph

Note(s) and/or Footnote(s):

1. Not to scale - for reference only.

## **Storage Information**

## Moisture Sensitivity

Optical characteristics of the device can be adversely affected during the soldering process by the release and vaporization of moisture that has been previously absorbed into the package. Devices are dry packed in a sealed aluminized envelope called a moisture-barrier bag with silica gel to protect them from ambient moisture during shipping, handling, and storage before use.

## Floor Life

This package has been assigned a moisture sensitivity level of MSL 1. As a result, the floor life of the devices removed from the moisture barrier bag is unlimited from the time the bag was opened, provided that the devices are stored under the following conditions:

- Floor Life: Unlimited

- Ambient Temperature: < 30°C

- Relative Humidity: < 85%

If the floor life or the temperature/humidity conditions have been exceeded, the devices must be rebaked prior to solder reflow or dry packing.

## **Rebaking Instructions**

When the shelf life or floor life limits have been exceeded, rebake at 50°C for 12 hours.

# **Ordering & Contact Information**

Figure 32: Ordering Information

| Ordering Code | Interface                                           | Delivery Form | Delivery Quantity |

|---------------|-----------------------------------------------------|---------------|-------------------|

| TSL2584TSV    | I <sup>2</sup> C V <sub>bus</sub> = 1.8 V Interface | Tape & Reel   | 3500 pcs          |

Buy our products or get free samples online at: www.ams.com/ICdirect

Technical Support is available at: www.ams.com/Technical-Support

Provide feedback about this document at: www.ams.com/Document-Feedback

For further information and requests, e-mail us at: ams\_sales@ams.com

For sales offices, distributors and representatives, please visit: www.ams.com/contact

#### Headquarters

ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten Austria, Europe

Tel: +43 (0) 3136 500 0

Website: www.ams.com

# RoHS Compliant & ams Green Statement

**RoHS:** The term RoHS compliant means that ams AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

**ams Green (RoHS compliant and no Sb/Br):** ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams AG knowledge and belief as of the date that it is provided. ams AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams AG and ams AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

# amu

# **Copyrights & Disclaimer**

Copyright ams AG, Tobelbader Strasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams AG are covered by the warranty and patent indemnification provisions appearing in its General Terms of Trade. ams AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams AG for each application. This product is provided by ams AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

# **Document Status**

| Document Status          | Product Status  | Definition                                                                                                                                                                                                                                                                     |  |  |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Product Preview          | Pre-Development | Information in this datasheet is based on product ideas in<br>the planning phase of development. All specifications are<br>design goals without any warranty and are subject to<br>change without notice                                                                       |  |  |

| Preliminary Datasheet    | Pre-Production  | Information in this datasheet is based on products in the<br>design, validation or qualification phase of development.<br>The performance and parameters shown in this document<br>are preliminary without any warranty and are subject to<br>change without notice            |  |  |

| Datasheet                | Production      | Information in this datasheet is based on products in<br>ramp-up to full production or full production which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade                                |  |  |

| Datasheet (discontinued) | Discontinued    | Information in this datasheet is based on products which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade, but these products have been superseded and<br>should not be used for new designs |  |  |

# **Revision Information**

| Changes from 1-01 (2014-Aug-12) to current revision 1-02 (2015-Mar-19) | Page |

|------------------------------------------------------------------------|------|

| Updated Figure 1                                                       | 1    |

| Updated Figure 2                                                       | 2    |

| Updated Figure 13                                                      | 10   |

| Updated notes under Figure 27                                          | 22   |

| Added Tape and Reel Information                                        | 24   |

| Updated Soldering Information                                          | 25   |

| Updated Figure 31                                                      | 27   |

#### Note(s) and/or Footnote(s):

1. Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

2. Correction of typographical errors is not explicitly mentioned.

## **Content Guide**

- 1 General Description

- 1 Key Benefits & Features

- 2 Applications

- 2 Block Diagram

- **3** Detailed Description

- 4 Pin Assignment

- 5 Absolute Maximum Ratings

- 6 Electrical Characteristics

- 8 Timing Characteristics

- 8 Timing Diagrams

- 9 Typical Operating Characteristics

- 10 Digital Interface

### 11 Register Description

- 12 Command Register

- 14 Control Register (00h)

- 15 Timing Register (01h)

- 16 Interrupt Register (02h)

- 18 Interrupt Threshold Registers (03h-06h)

- 19 Analog Register (07h)

- 19 ID Register (12h)

- 20 ADC Channel Data Registers (14h-17h)

- 21 Manual Integration Timer Registers (18h-19h)

- 21 ID2 Register (1Eh)

- 22 PCB Pad Layout

- 23 Package Drawings & Markings

- 24 Tape & Reel Information

- 25 Soldering & Storage Information

- 25 Soldering Information

- 26 Storage Information

- 26 Moisture Sensitivity

- 26 Floor Life

- 26 Rebaking Instructions

- 27 Ordering & Contact Information

- 28 RoHS Compliant & ams Green Statement

- 29 Copyrights & Disclaimer

- 30 Document Status

- 31 Revision Information